Patents

Literature

60results about How to "Little latency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System and method for performing client-centric load balancing of multiple globally-dispersed servers

InactiveUS7653700B1Improve performanceLittle latencyMultiple digital computer combinationsData switching networksDomain nameIp address

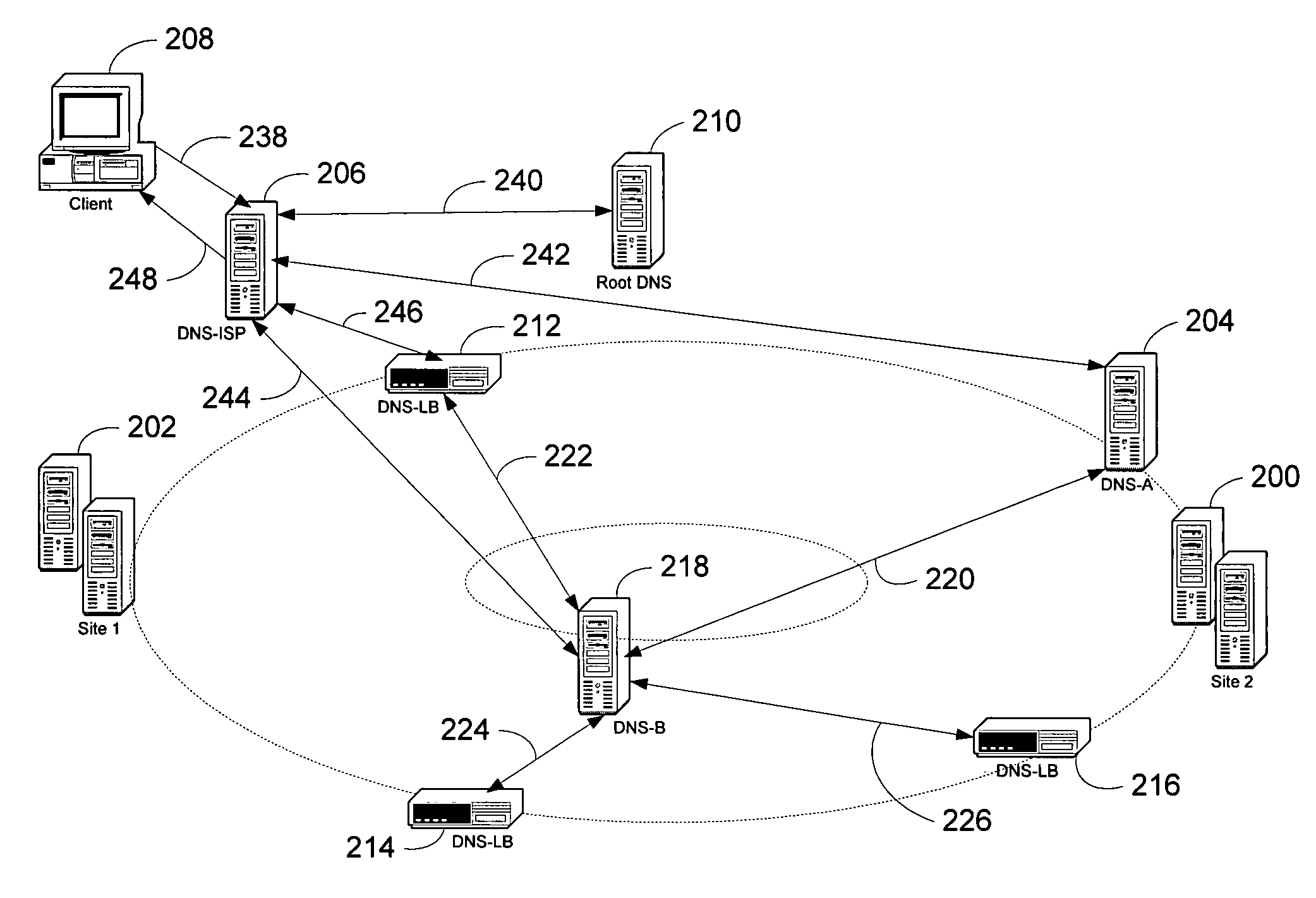

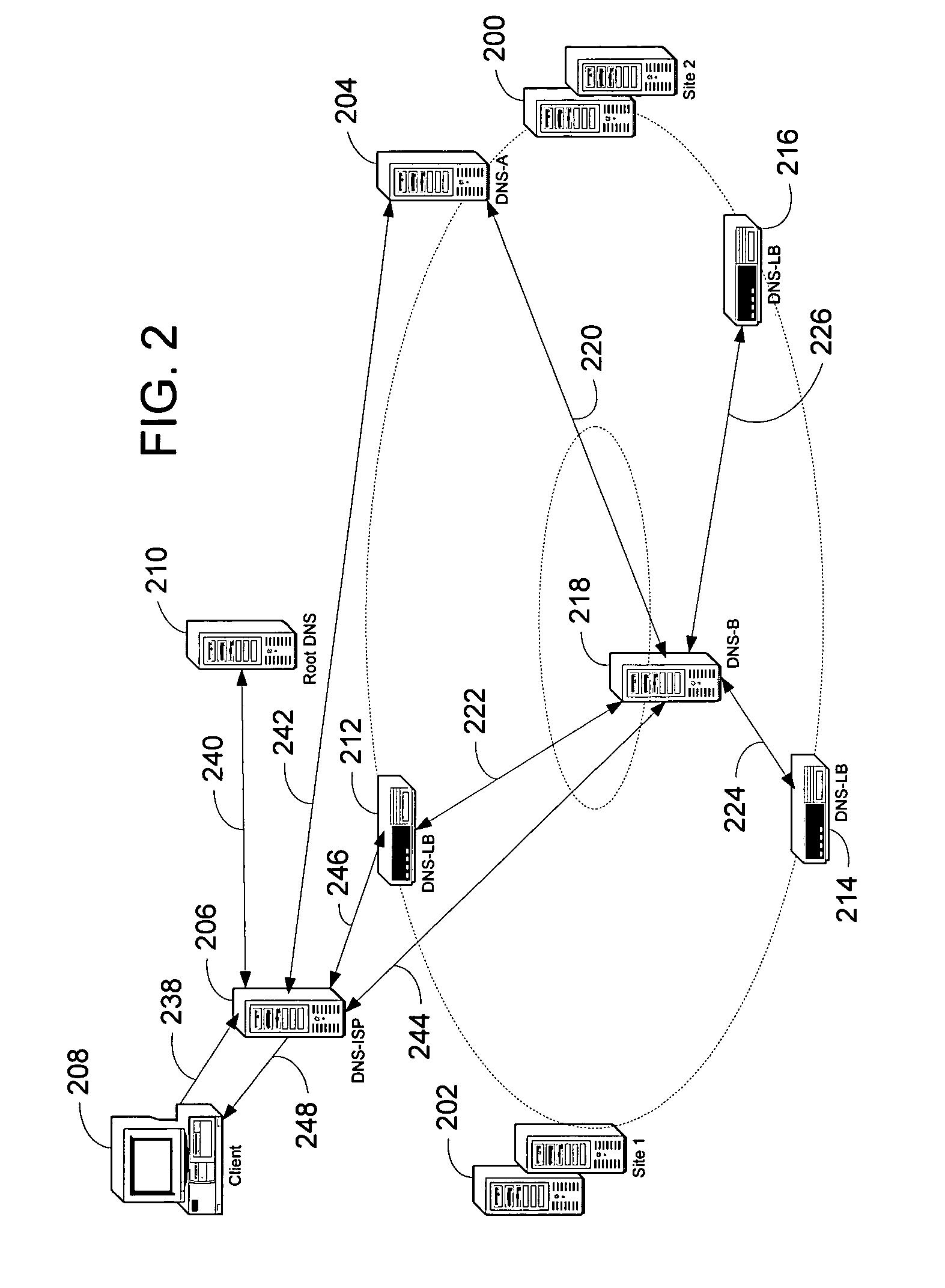

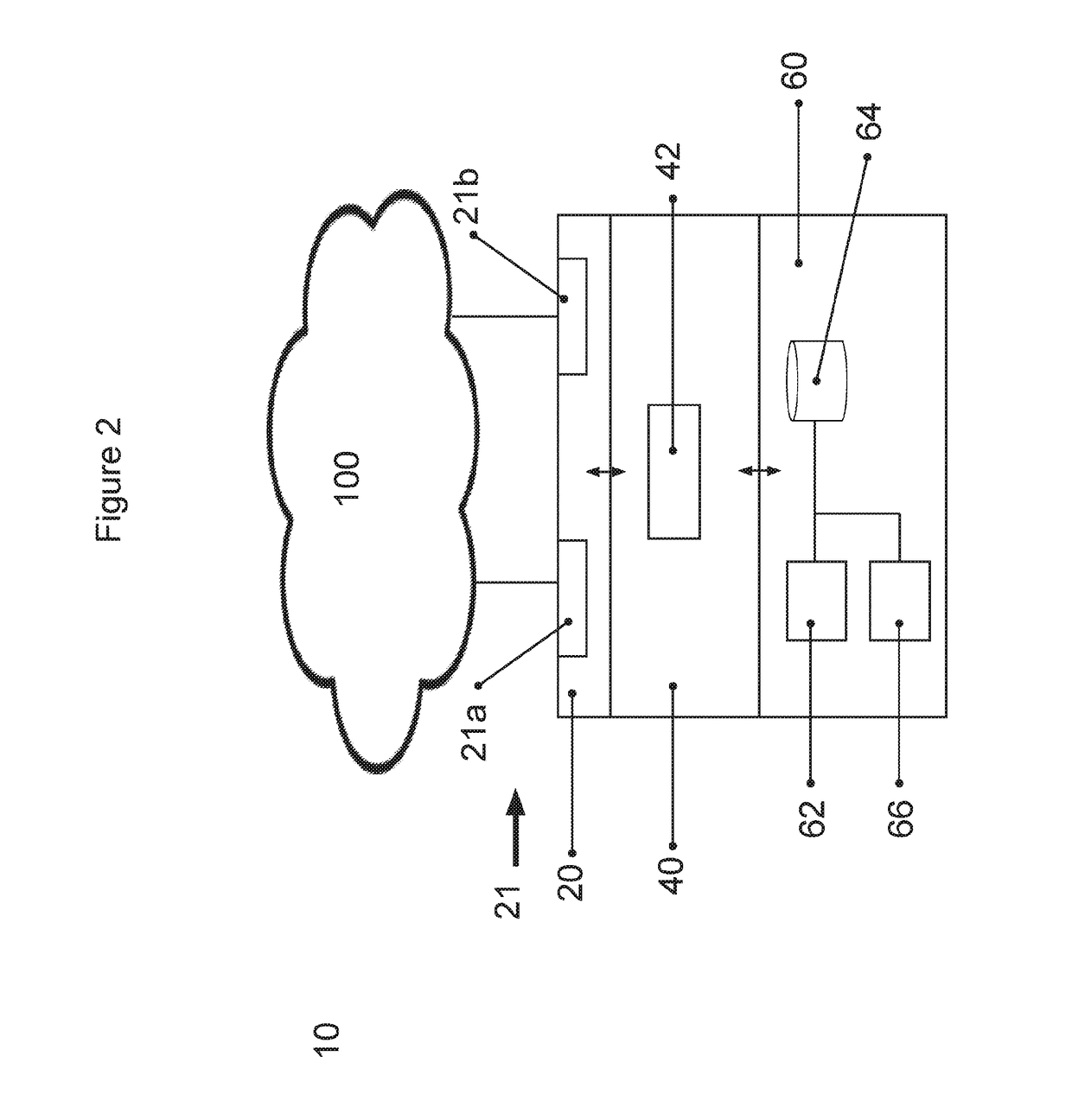

Presented is a system and a method for load balancing multiple globally-dispersed servers based on client-centric performance criteria. The infrastructure of the system includes load balancing domain name servers (DNS-LBs) deployed in close physical proximity to the Internet service providers' points of presence. The DNS-LBs are then able to monitor the performance of the servers from a location close to the clients, which allows the DNS-LBs to select a server that will yield the best performance from that location for the client. A second level of the infrastructure utilizes domain name servers (DNS-Bs) that are deployed on the Internet backbones and regional provides. The authoritative domain name servers (DNS-As) for the servers to be load balanced refer all name queries to these DNS-Bs. The DNS-Bs then refer the queries to one of the DNS-LBs based on a mapping of the DNS-ISP address to its physically proximate DNS-LB. The DNS-LB then returns the IP address of the server that will provide the best performance from that location.

Owner:MICROSOFT TECH LICENSING LLC

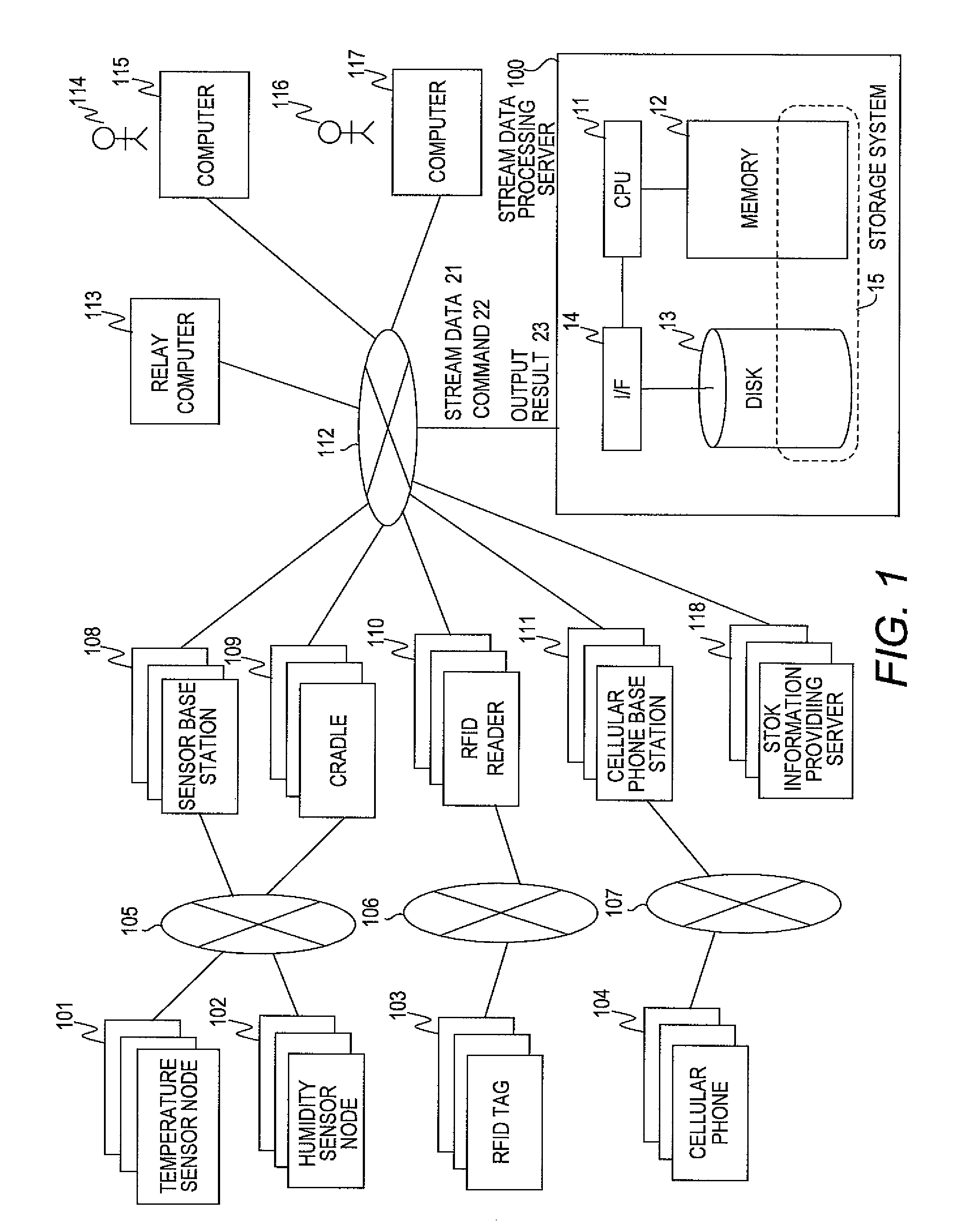

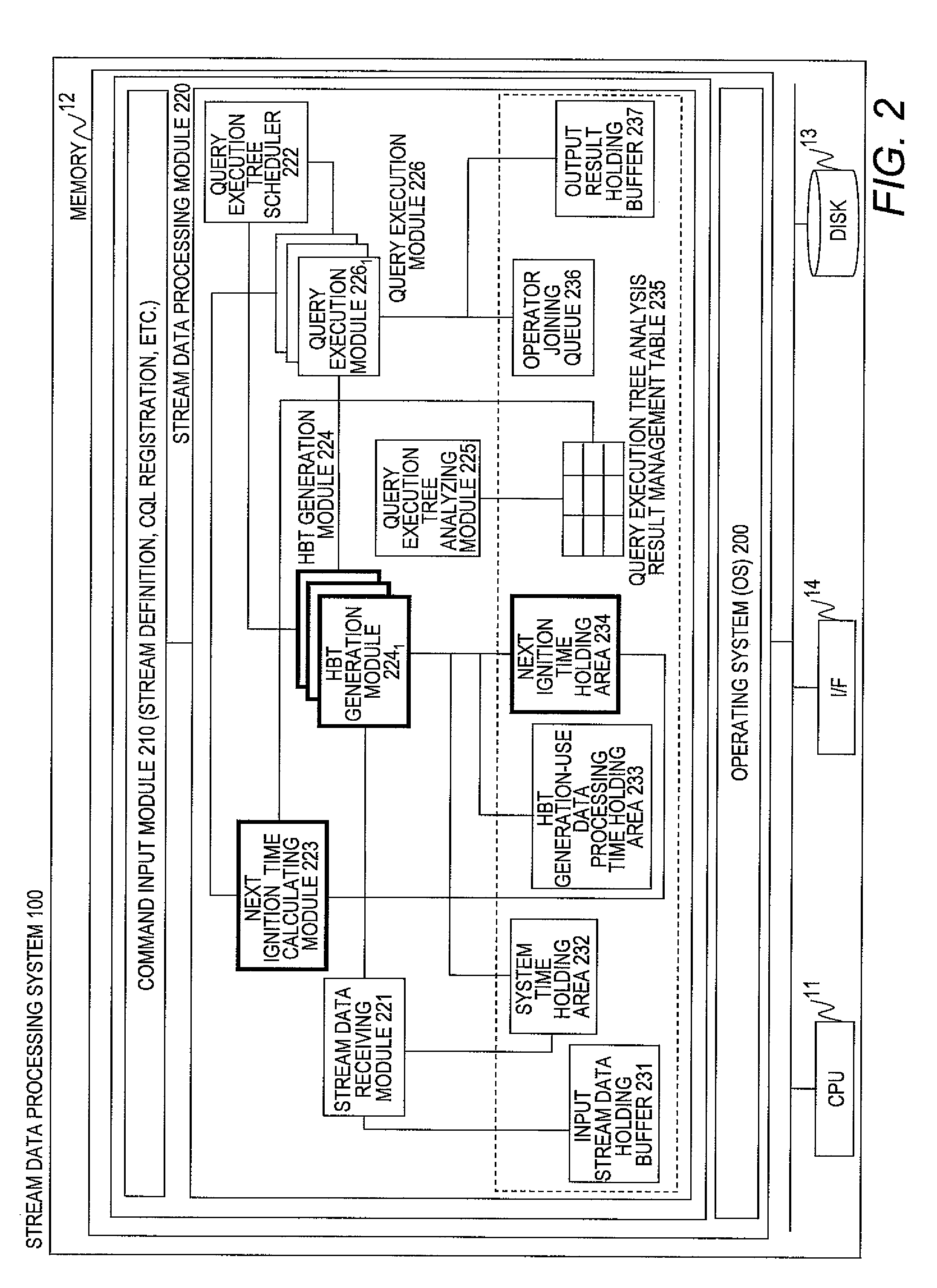

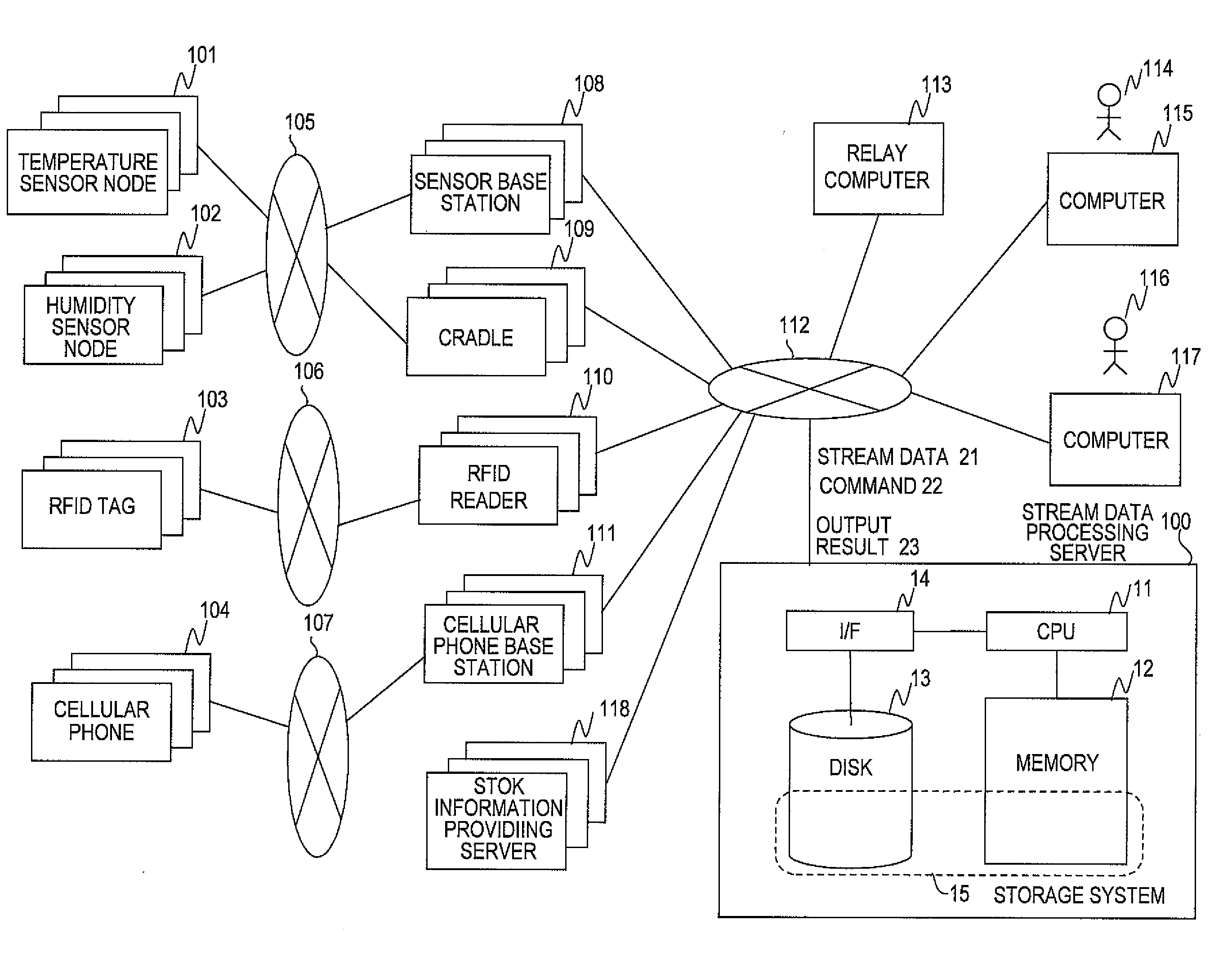

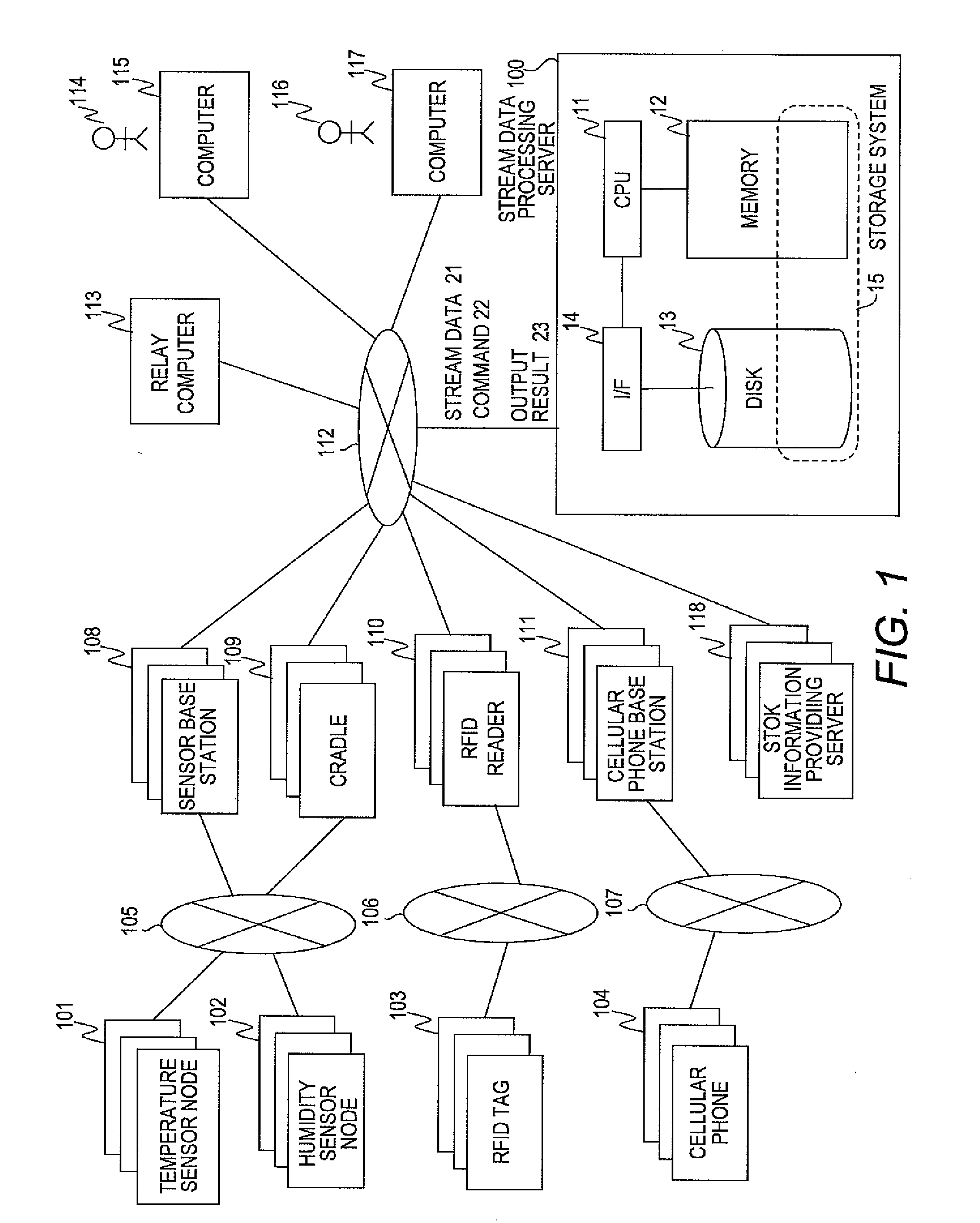

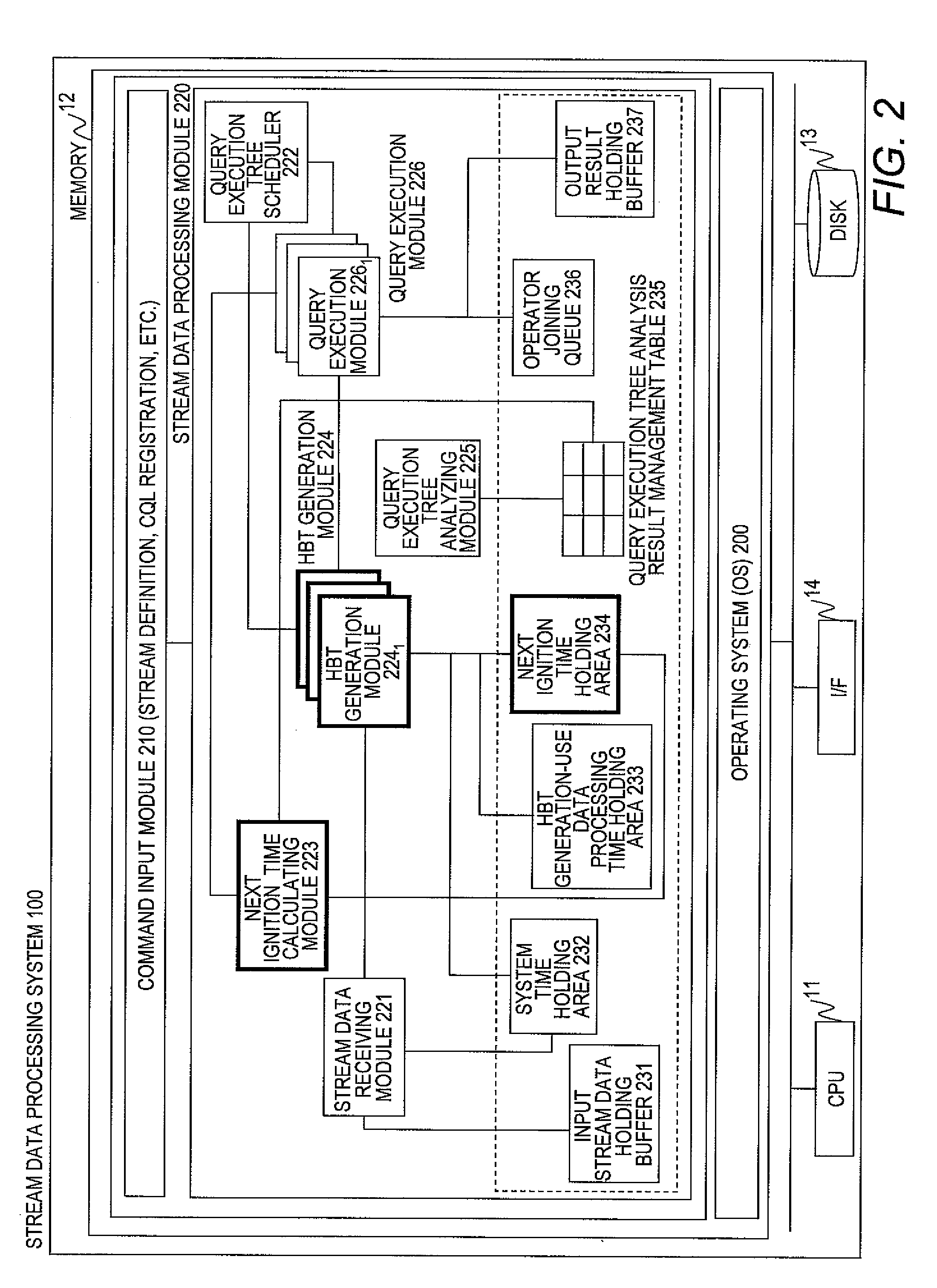

Machine-readable medium for storing a stream data processing program and computer system

InactiveUS8095690B2Increase loadReduce throughputFinanceDigital data processing detailsStreaming dataTime information

Owner:HITACHI LTD

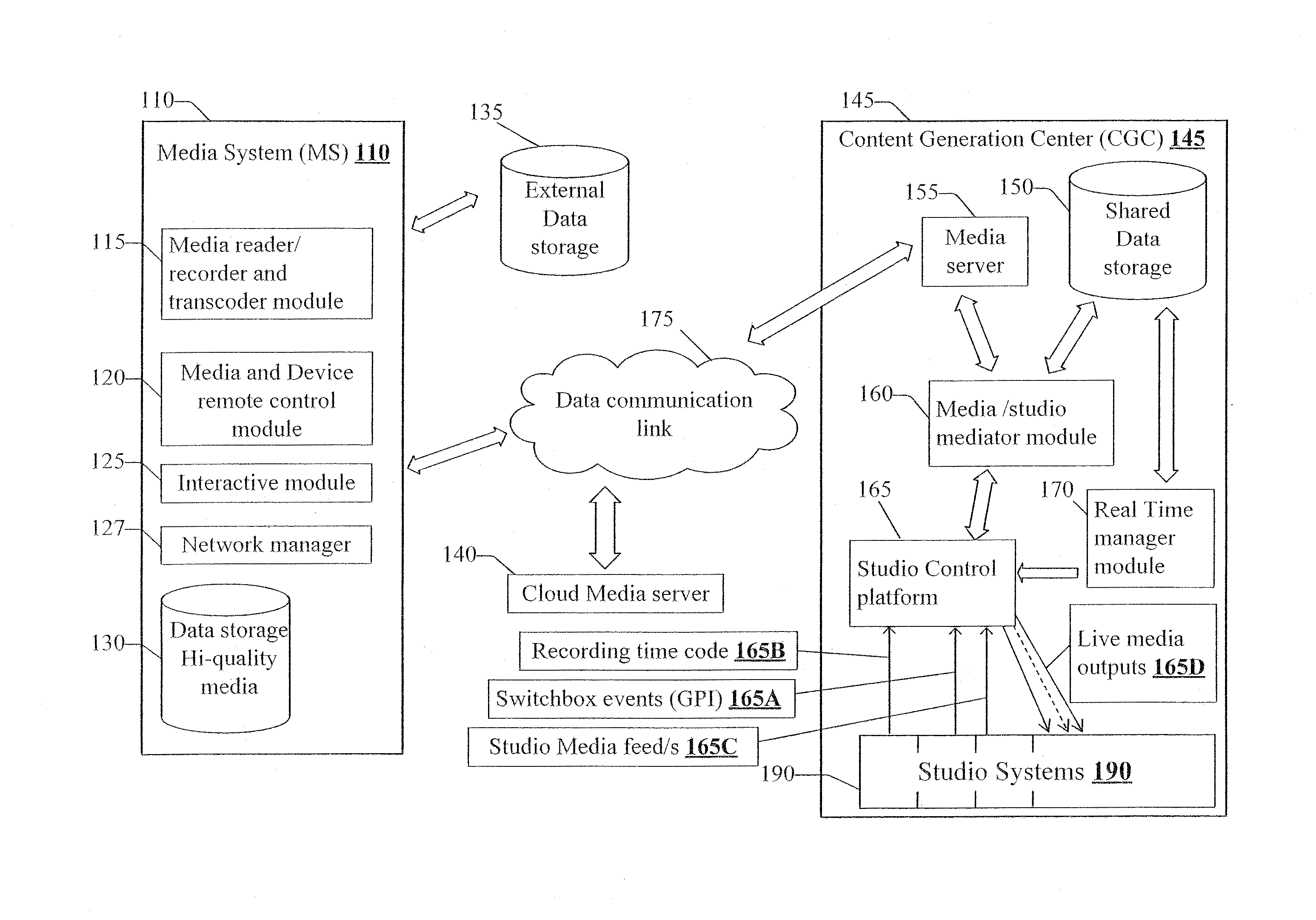

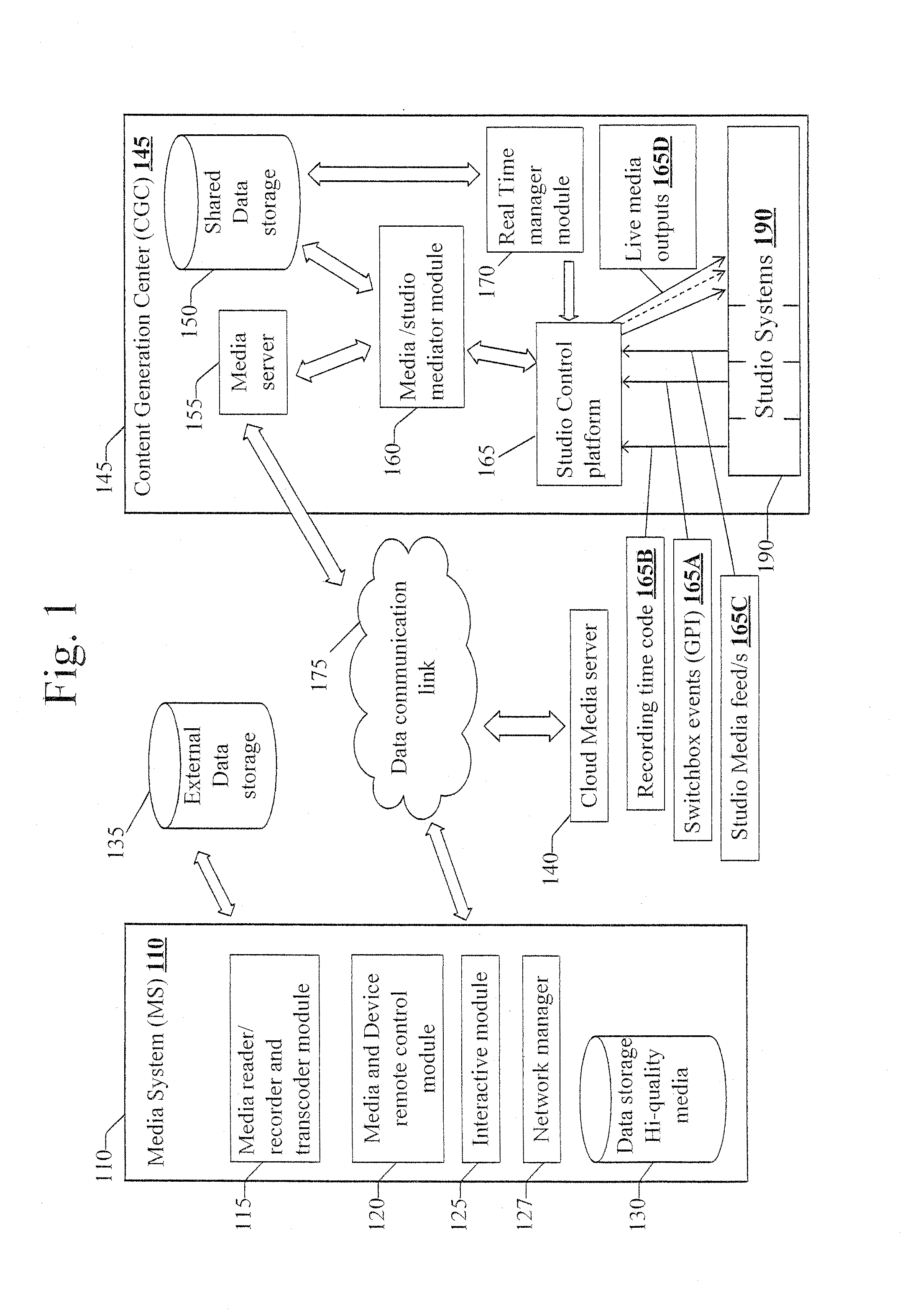

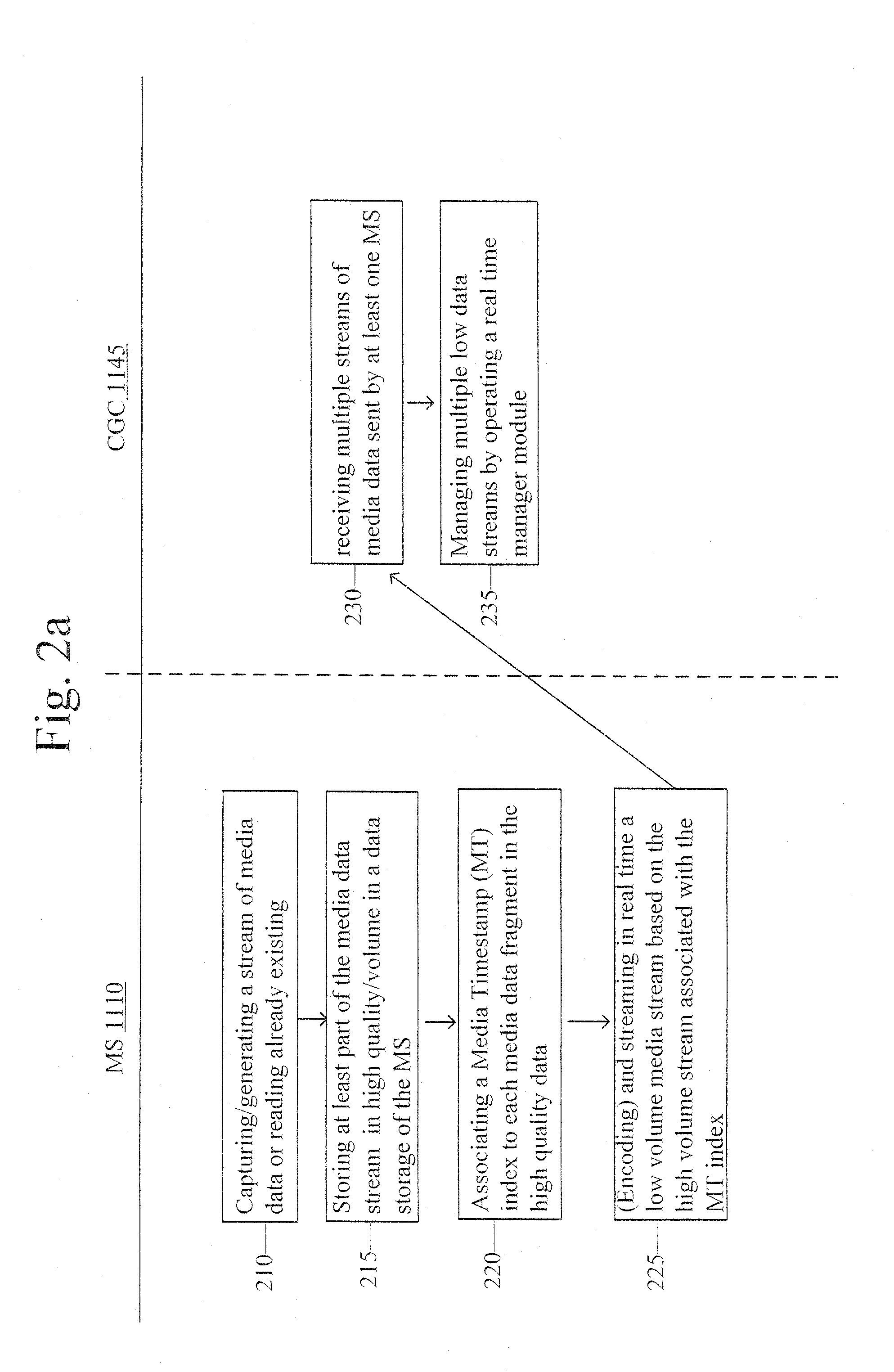

Method and system for central utilization of remotely generated large media data streams despite network bandwidth limitations

ActiveUS20130290557A1Quality improvementImprove practicalityElectronic editing digitised analogue information signalsMultiple digital computer combinationsData streamComputer network

A computerized method for integrating media streams from a multiplicity of media systems over at least one network into a single media product at high media technical quality, the method comprising the steps of, at certain media systems from among the multiplicity thereof: a. Generating a low volume (LV) media stream representation from a high volume media stream, where the low volume stream's bit-rate is different from the high volume stream's bit-rate; b. streaming the low volume media stream to a content generation center via a data communication network; c. Maintaining high volume local data as a high volume media stream in a storage medium coupled to at least one of the media systems; and d. maintaining mapping information between the low volume stream and the high volume local data for enabling access to media portions in the high volume media stream storage, which correspond based on LV stream time.

Owner:MOBILATV

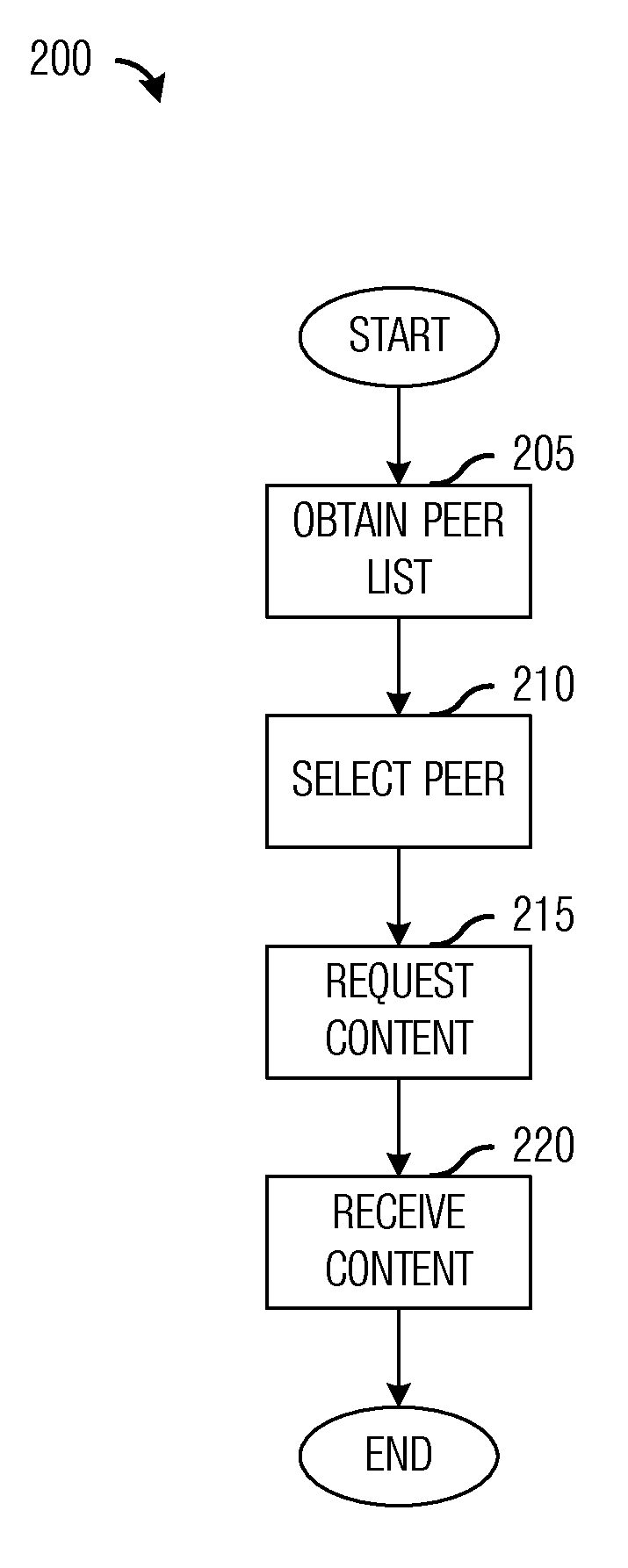

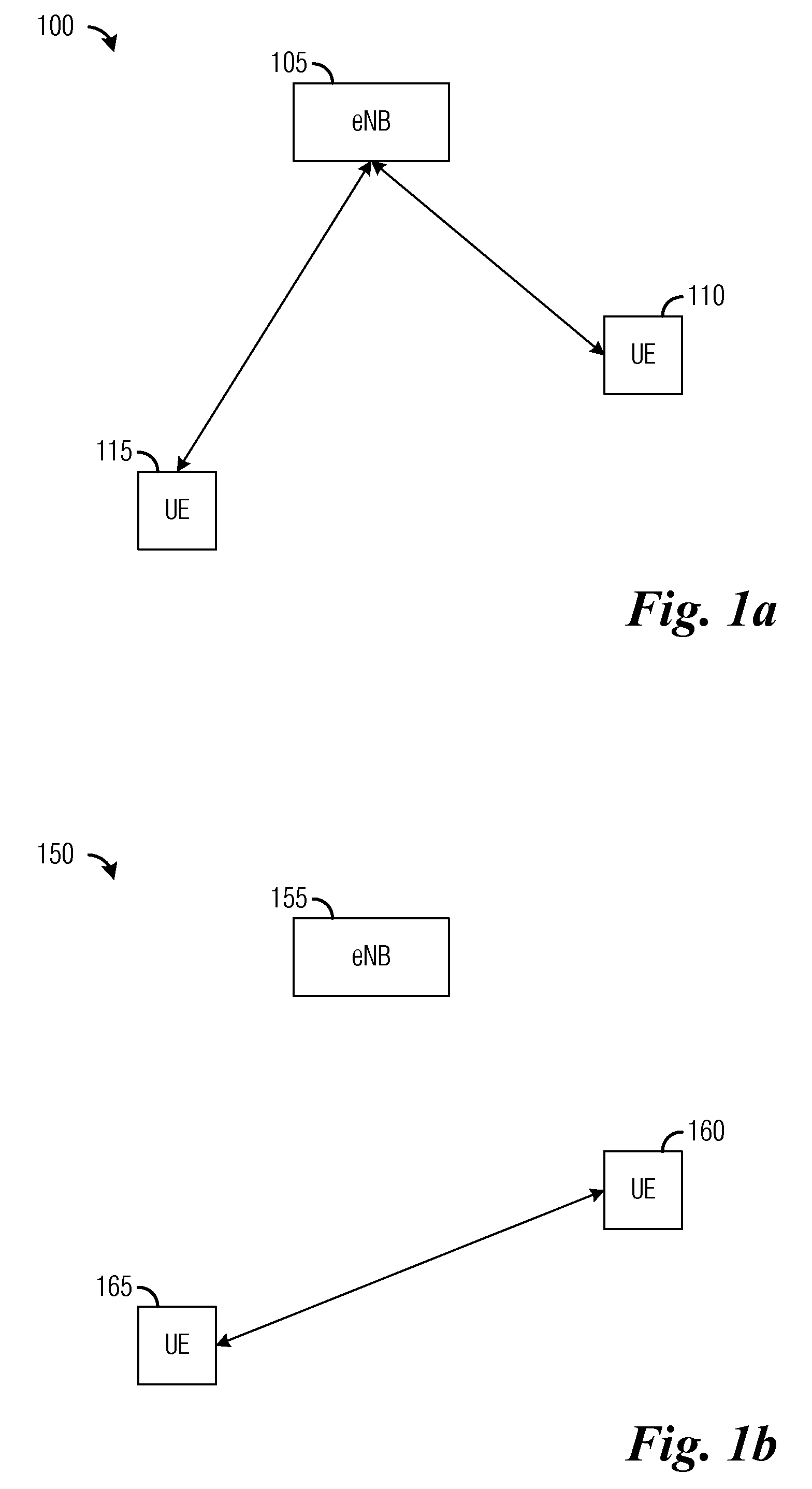

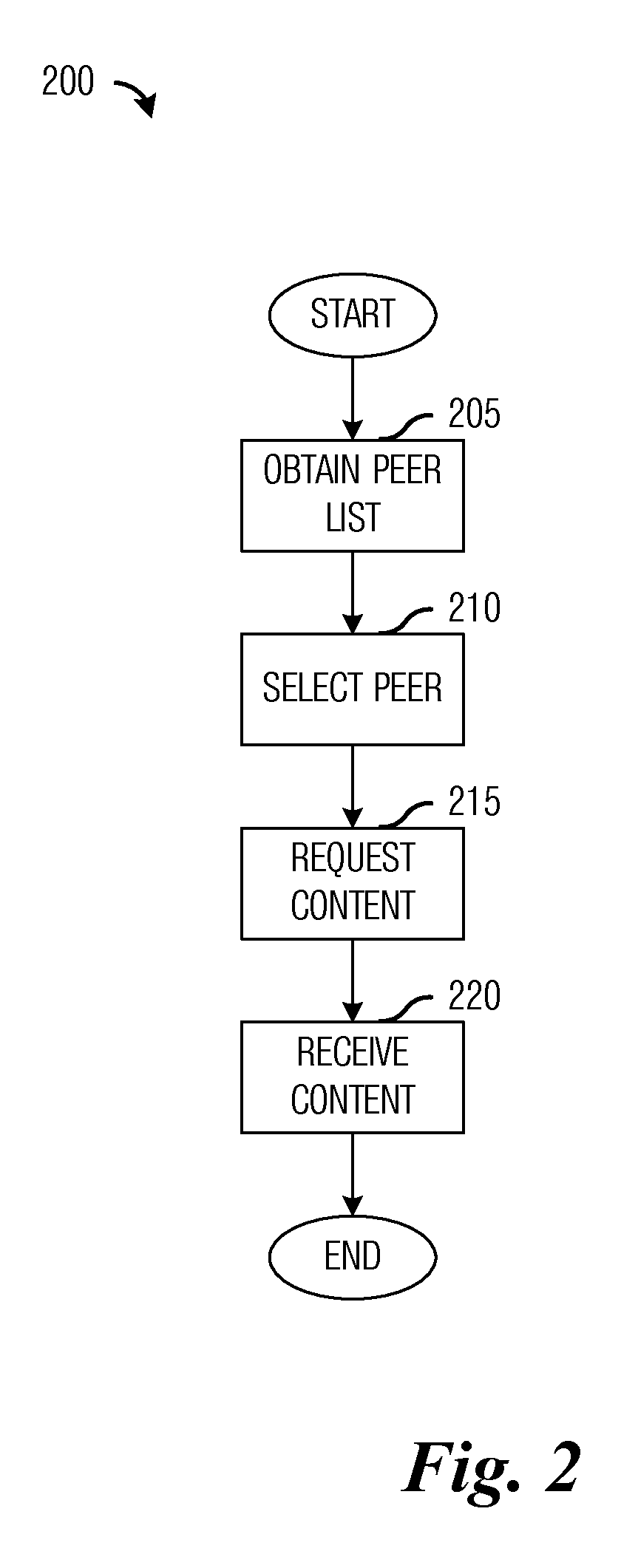

System and Method for Peer to Peer Communications in Cellular Communications Systems

InactiveUS20120290650A1Reduce spectrum loadReduce contentionAssess restrictionConnection managementCellular communication systemsCommunication control

A system and method for peer-to-peer communications in cellular communications systems are provided. A method for communications device operations includes receiving a peer list at a communications device, where the peer list includes a list of reachable communications devices and device-to-device (D2D) capability information of the reachable communications devices, selecting a peer from the peer list, sending a content request comprising an indication of a content to a communications controller serving the communications device, and receiving the content from the peer over a channel established by the communications controller.

Owner:HUAWEI TECH CO LTD

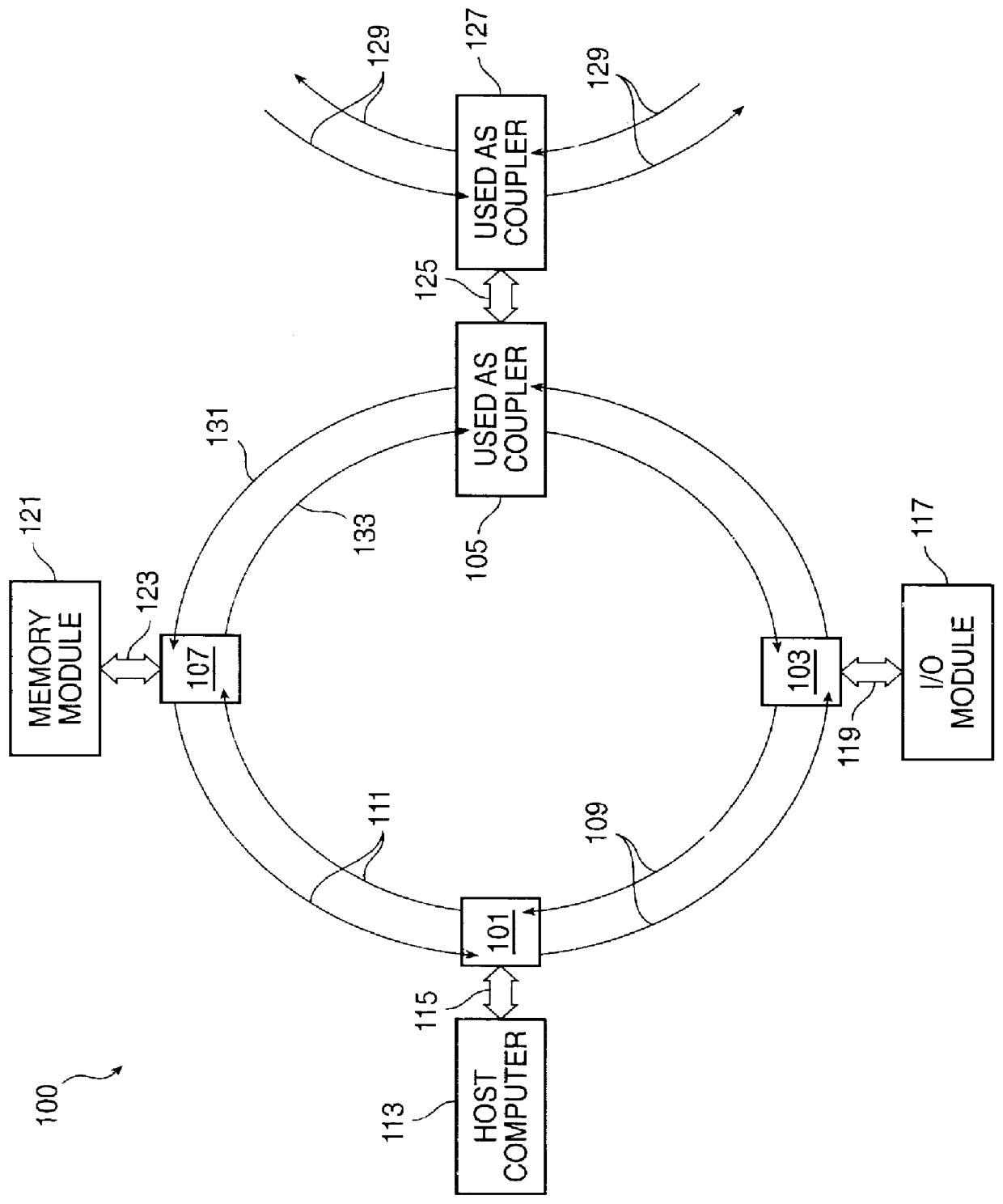

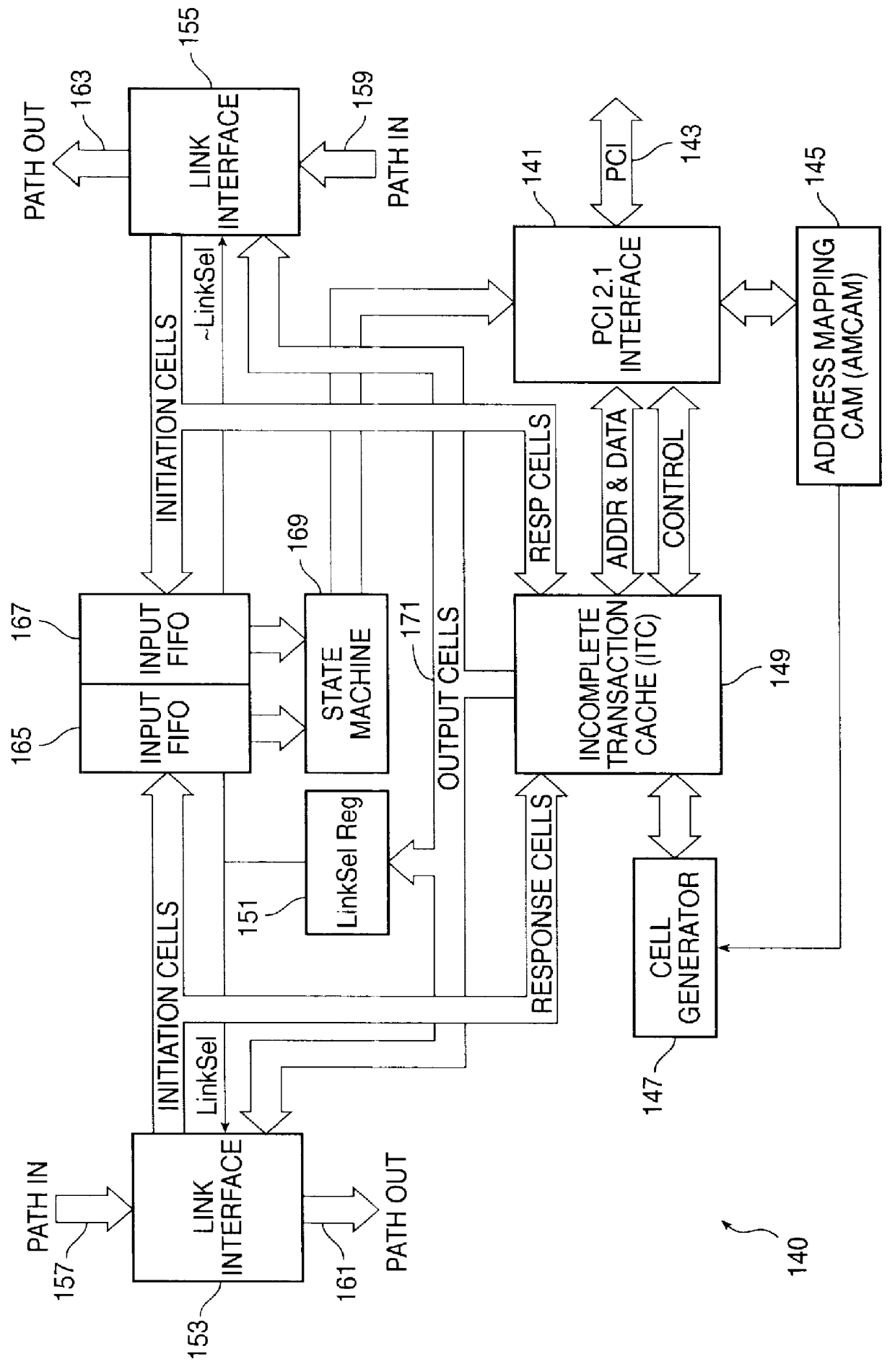

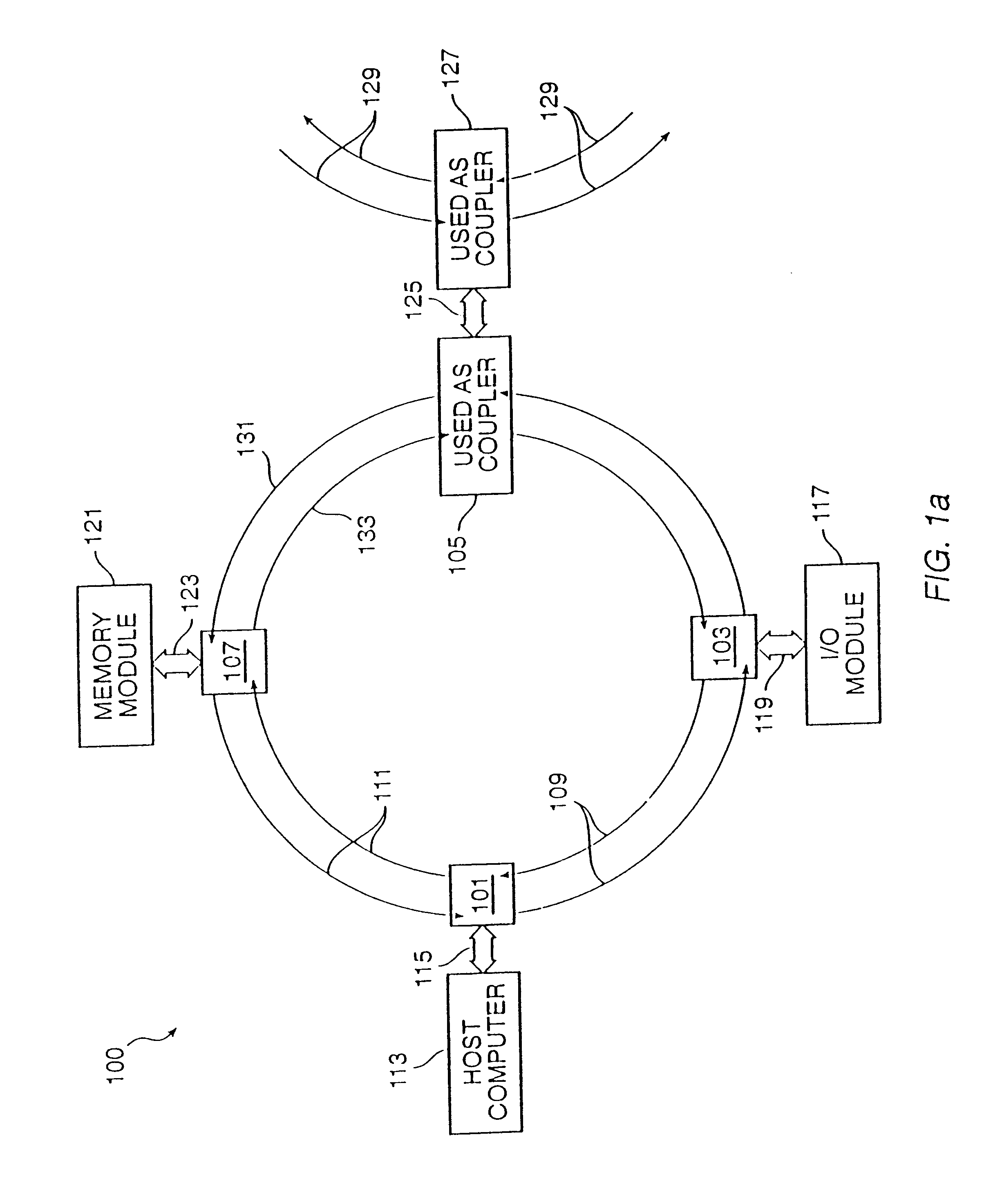

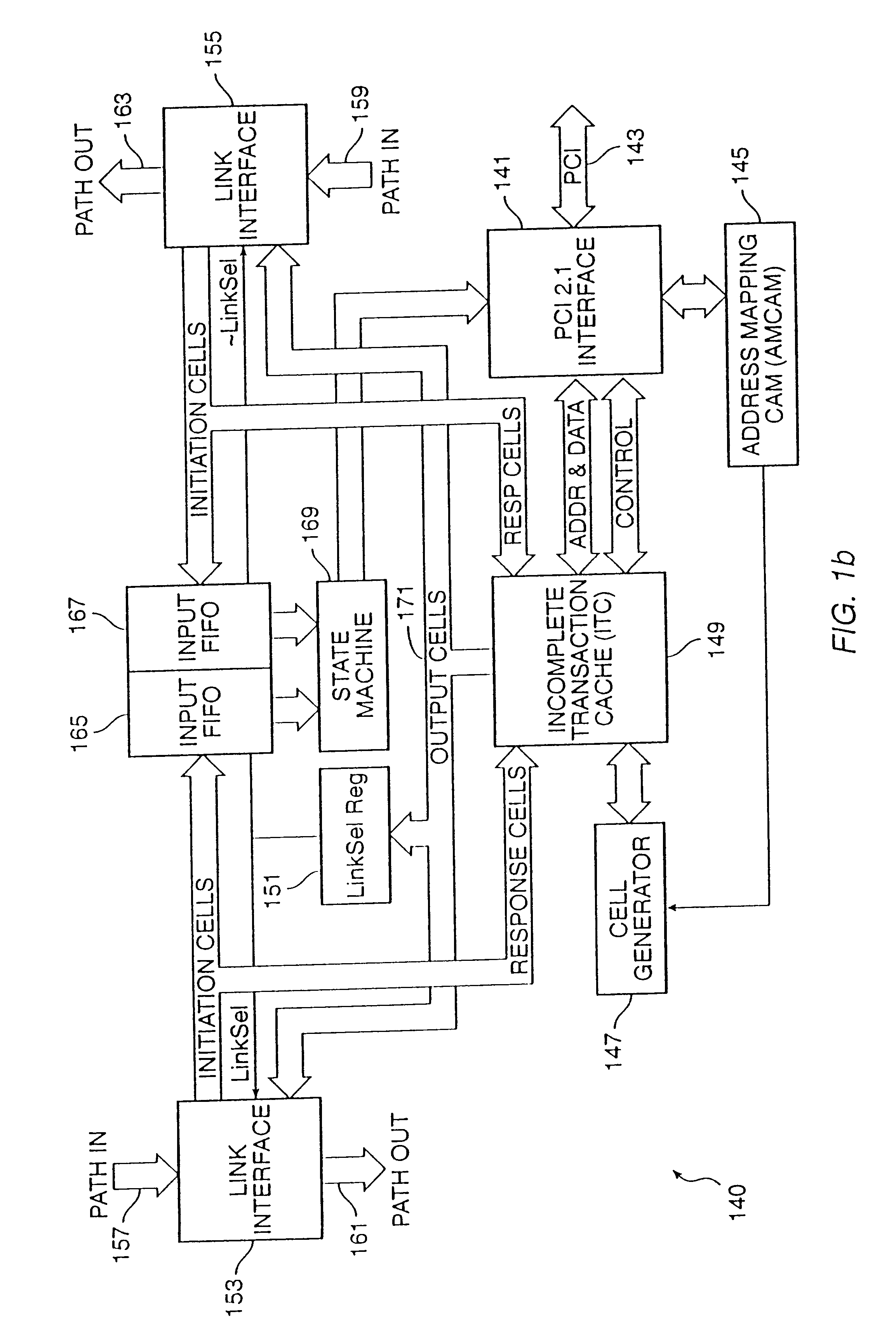

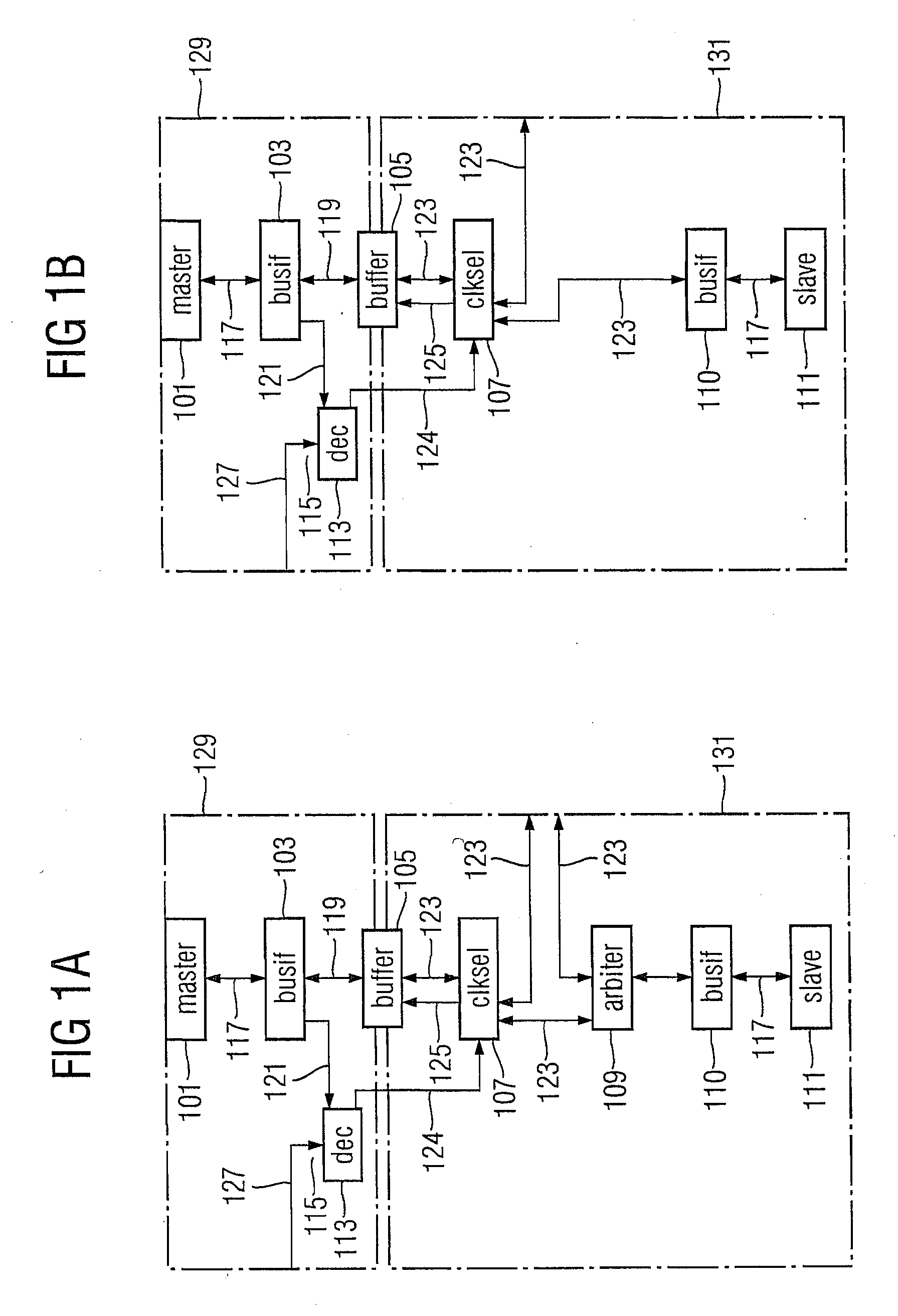

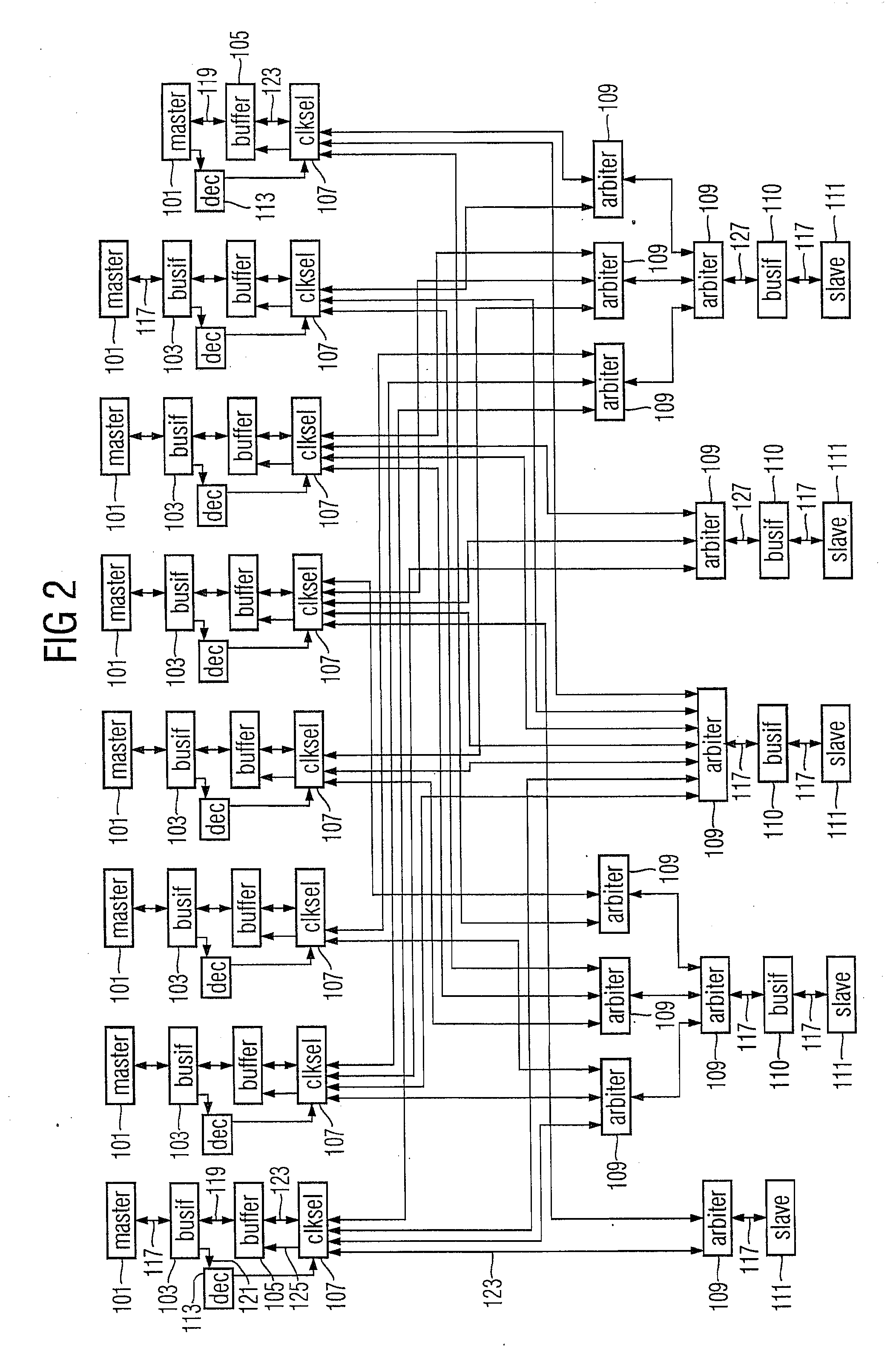

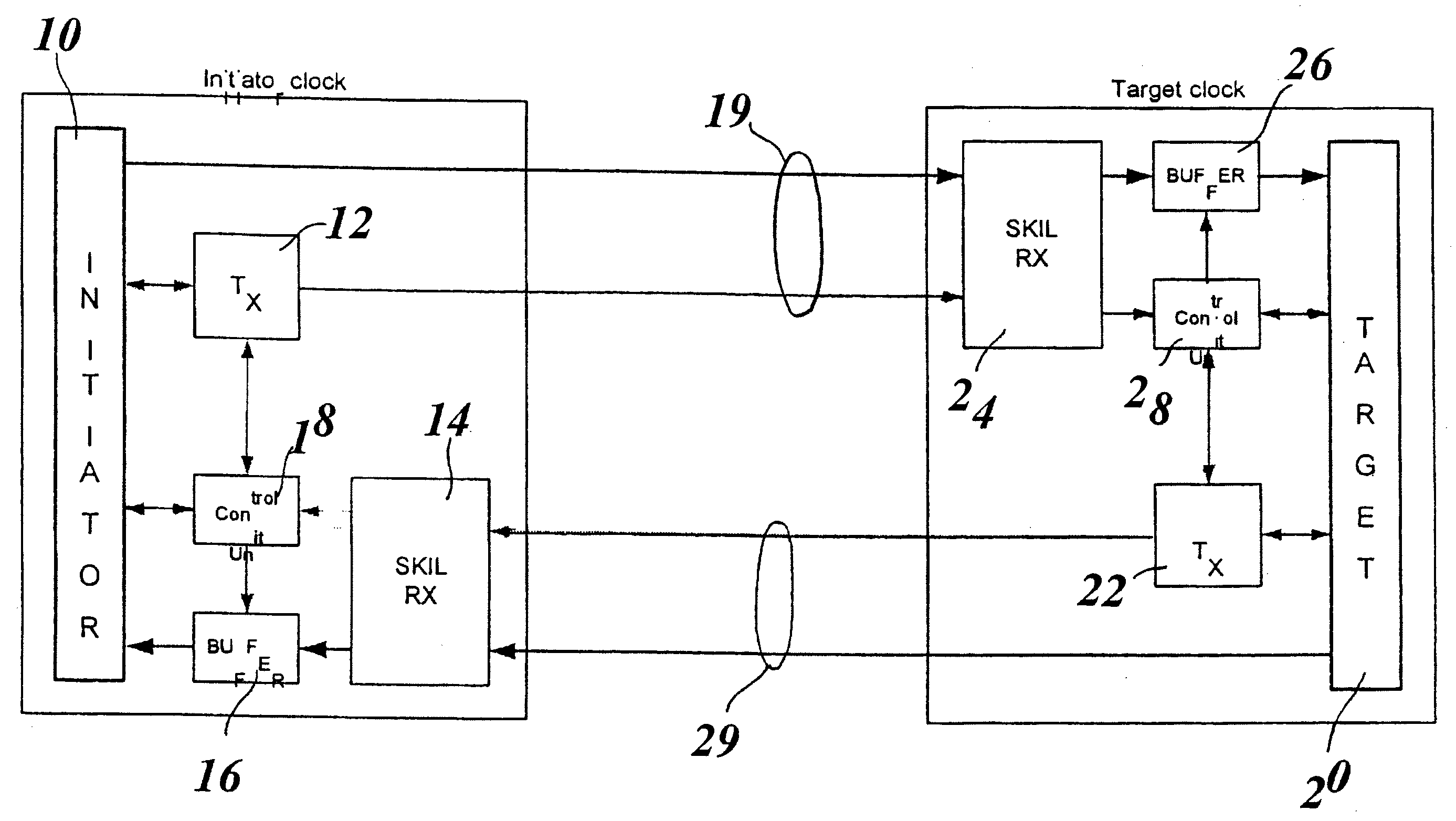

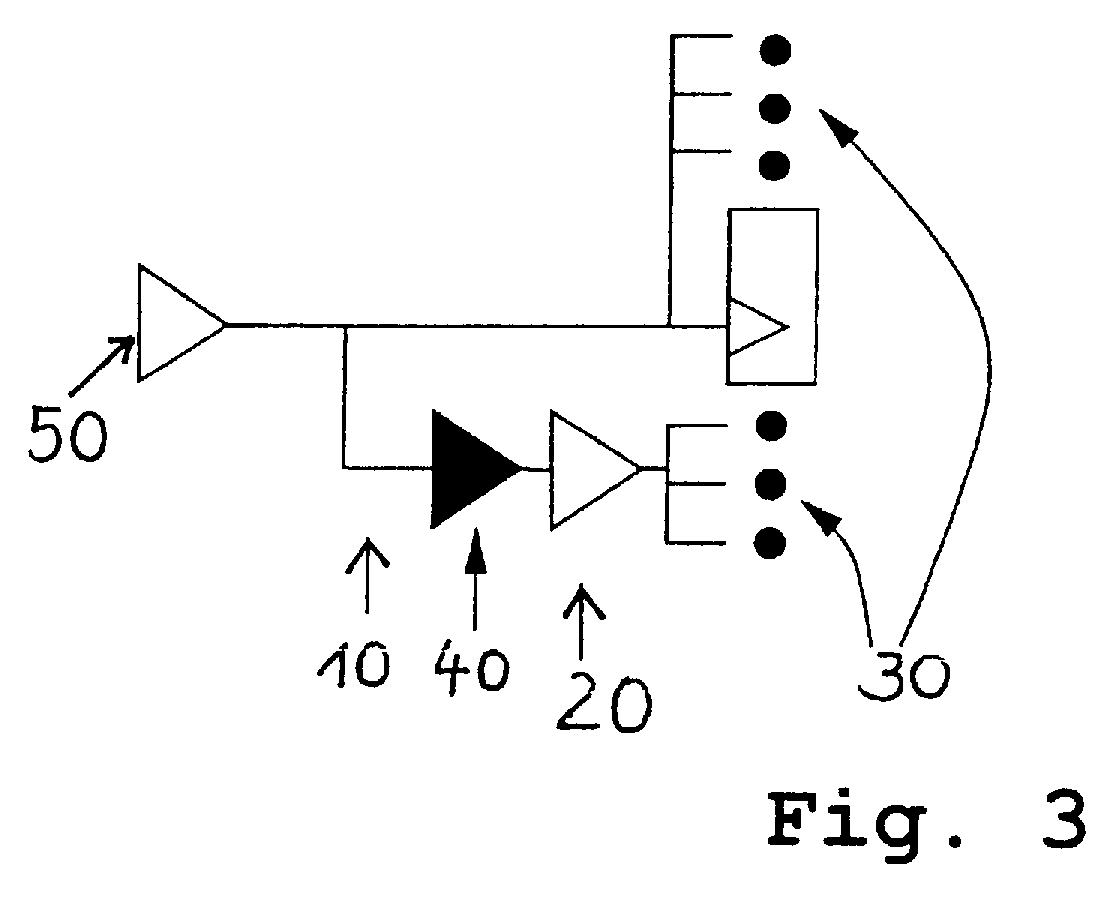

Method and apparatus for a fault tolerant, software transparent and high data integrity extension to a backplane bus or interconnect

InactiveUS6091705AIncrease speedLittle latencyError preventionFrequency-division multiplex detailsData integrityProcessor register

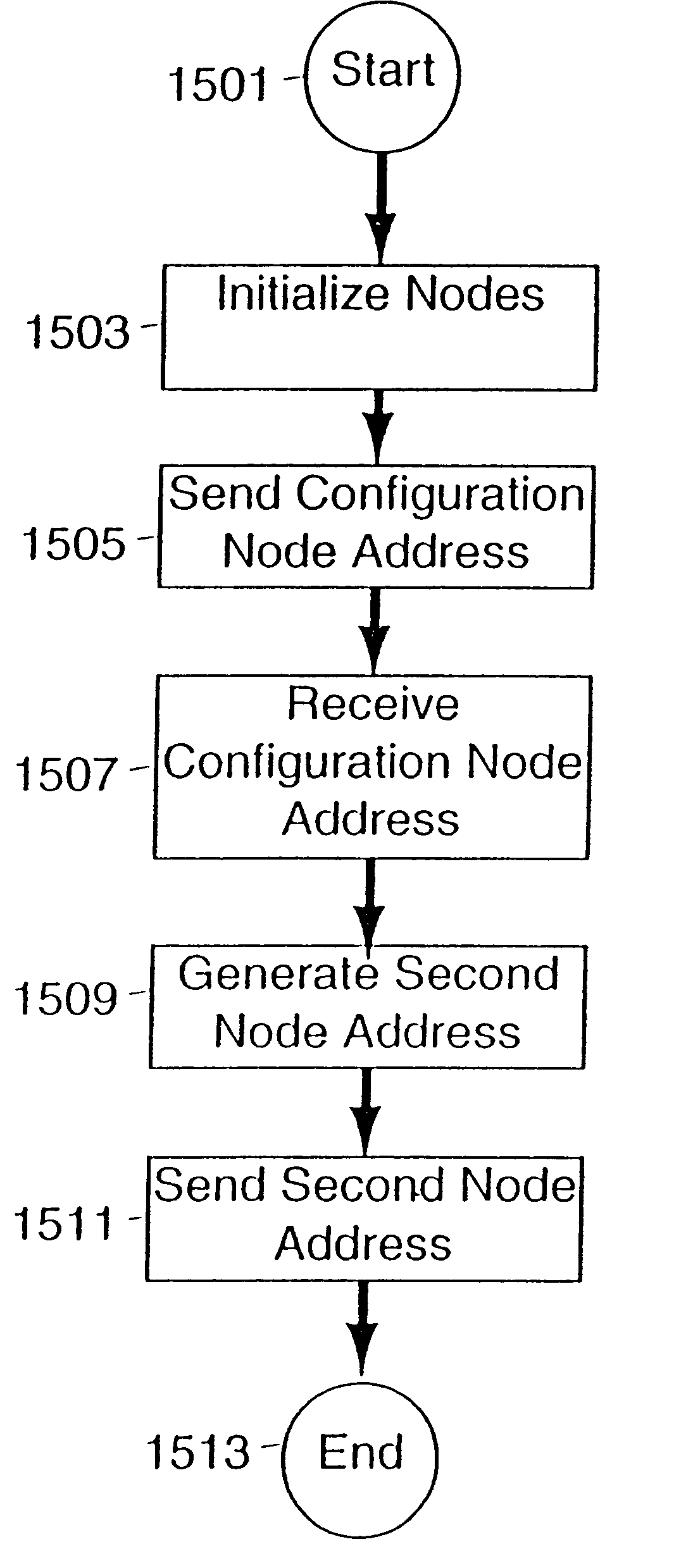

The disclosure relates to apparatus and methods that provide a system interconnect for transporting cells between nodes on a dual counter-rotating ring network, including a link selection register for selecting the shortest path to a destination node, use of a fault tolerant frequency reference to synchronize node clocks, interconnect initialization, multi-ring topologies along with an addressing schema and ring-to-ring couplers. The disclosure also discusses flow control of cells leaving nodes, coupling cells from one ring to another, and use of such an interconnect as a bus replacement.

Owner:AVAGO TECH INT SALES PTE LTD

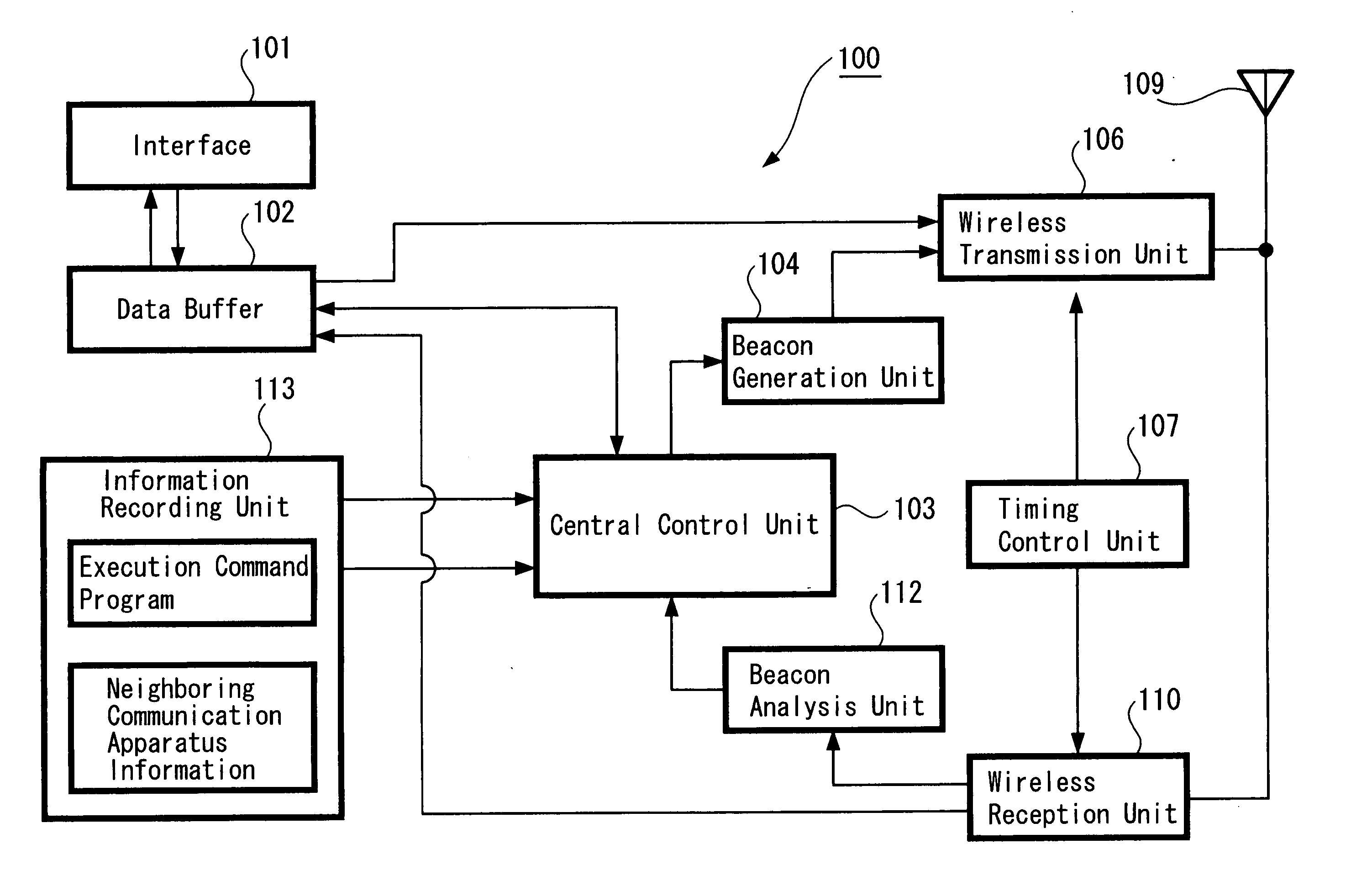

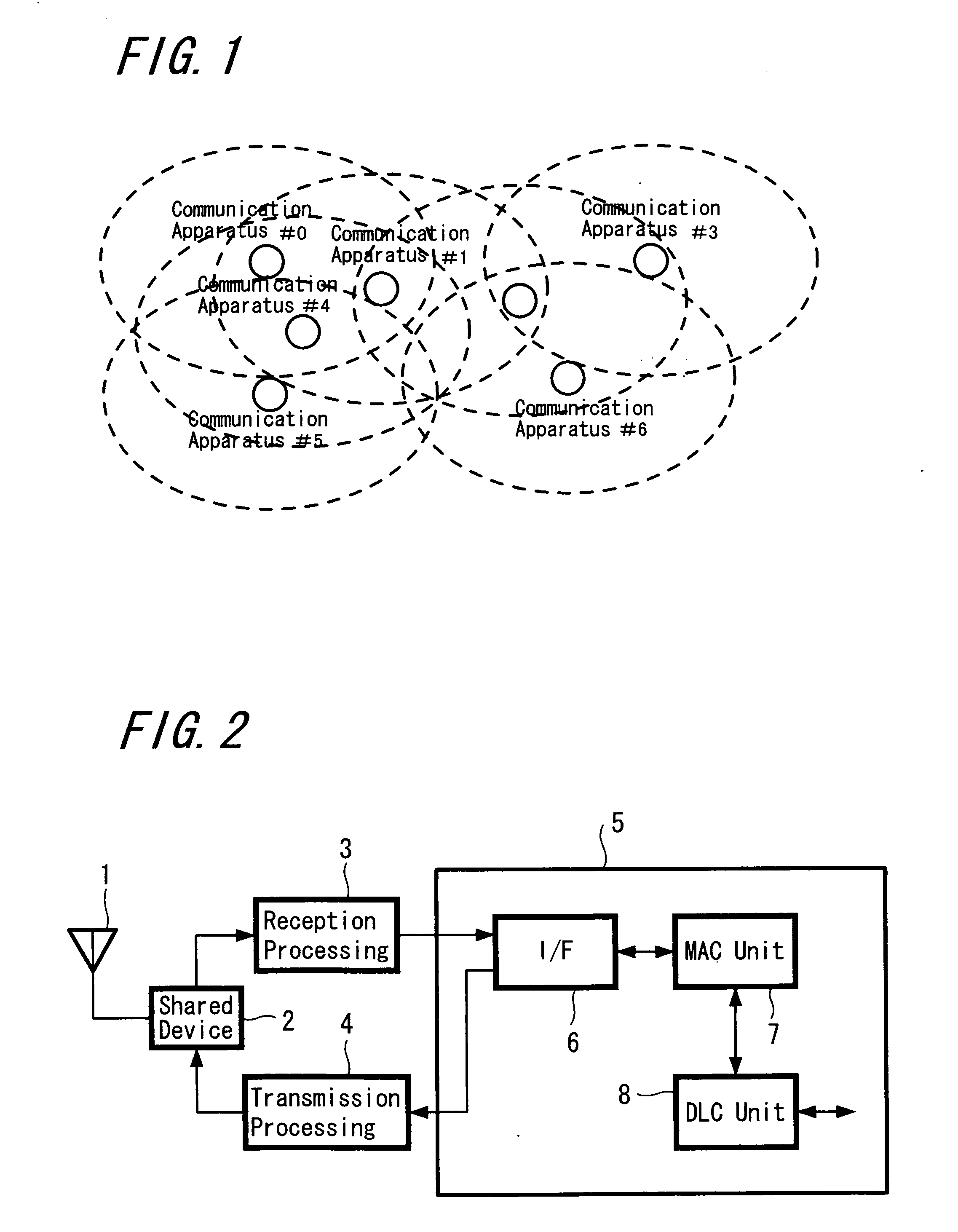

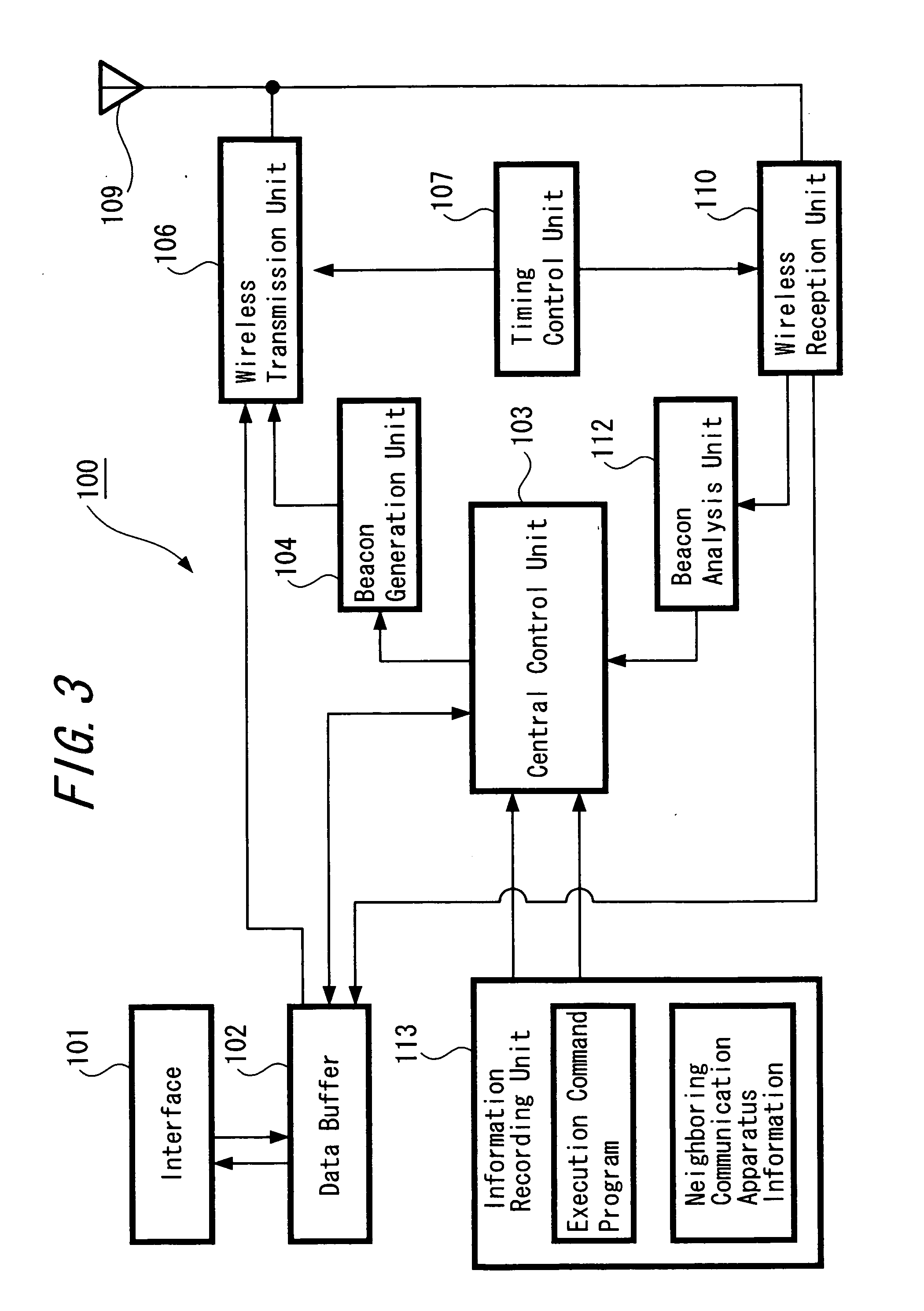

Communication method, communication device, and computer program

ActiveUS20060234740A1Excellent communication method and communicationLittle latencyNetwork traffic/resource managementNetwork topologiesData transmissionReal-time computing

In order to solve a problem of an accumulation on the transmission side, a delay on the reception side, and the like at the time of transmission in a communication system such as a wireless LAN system, each communication station in a network transmits a beacon in which information with respect to the network is written and sets a state in which a reception operation is performed during periods of time before and after the transmission of the beacon signal when performing access control not to make communication timing of a packet collide with that of another station by detecting a signal transmitted from another station. With performing such processing, a system can be formed based on minimum level of transmission and reception operation when transmission and reception data does not exist in each communication station in the network, and also a data transfer can be performed with latency as small as possible in a minimum necessary level of transmission and reception operation by making a transition of a transmission and reception state in accordance with a fluctuating volume of transmission and reception data.

Owner:SONY CORP

Machine-readable medium for storing a stream data processing program and computer system

InactiveUS20100106853A1Little latencyLimited amount of timeFinanceDigital data processing detailsStreaming dataTime information

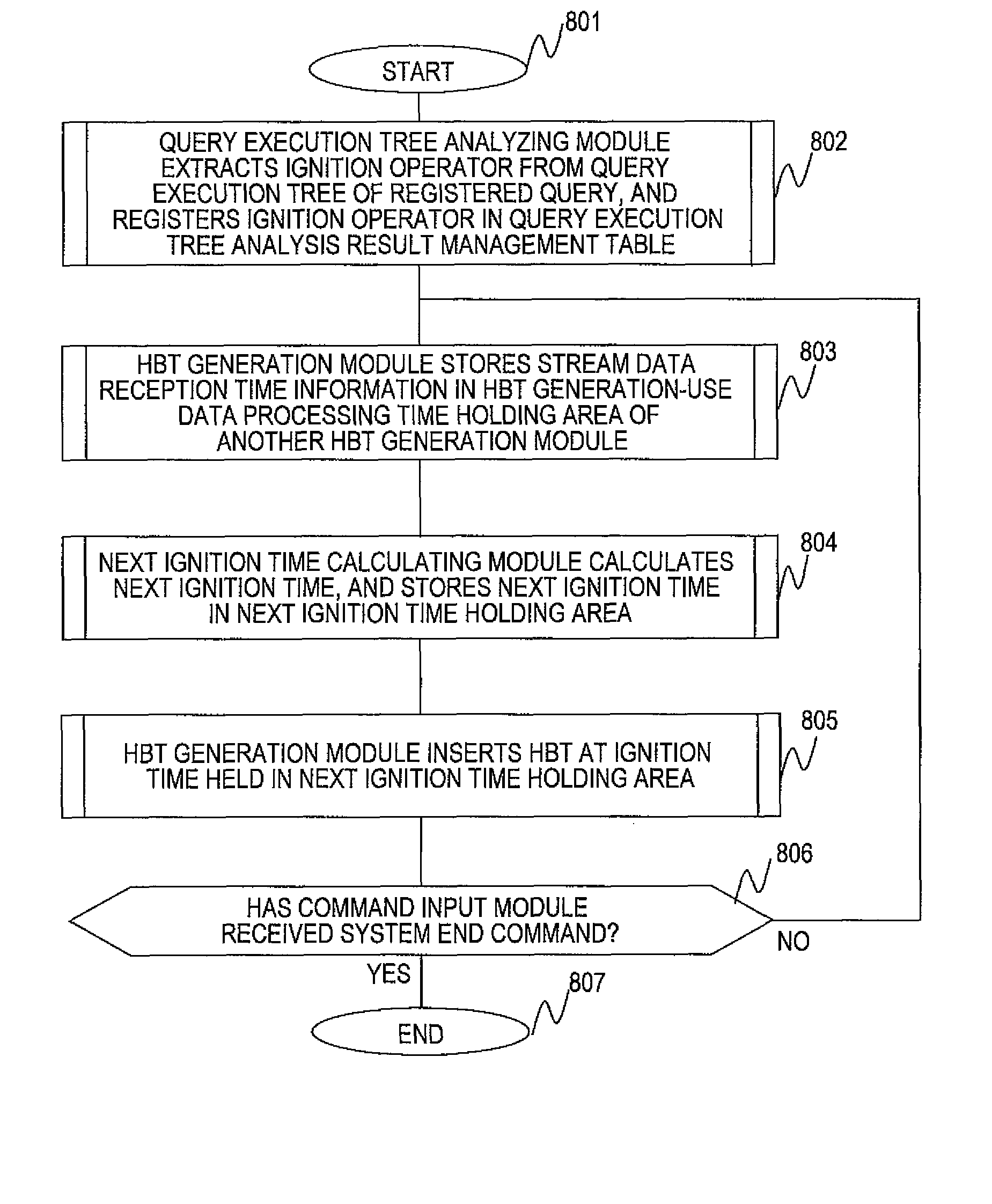

In a stream data processing method in which part of stream data is defined as a processing target and the time control information which indicates the advance of the time is inserted into the stream data, time information of the received stream data is stored in a next ignition time holding area as an ignition time. A processing module for generating the time control information at a time different from the time of reception of the stream data is extracted out of a query that indicates how the stream data is to be processed. Based on the extracted processing module and the time information indicating the time of the reception of the stream data, the ignition time is calculated and stored in the next ignition time holding area. The time generation module inserts the time control information at the ignition time held in the next ignition time holding area.

Owner:HITACHI LTD

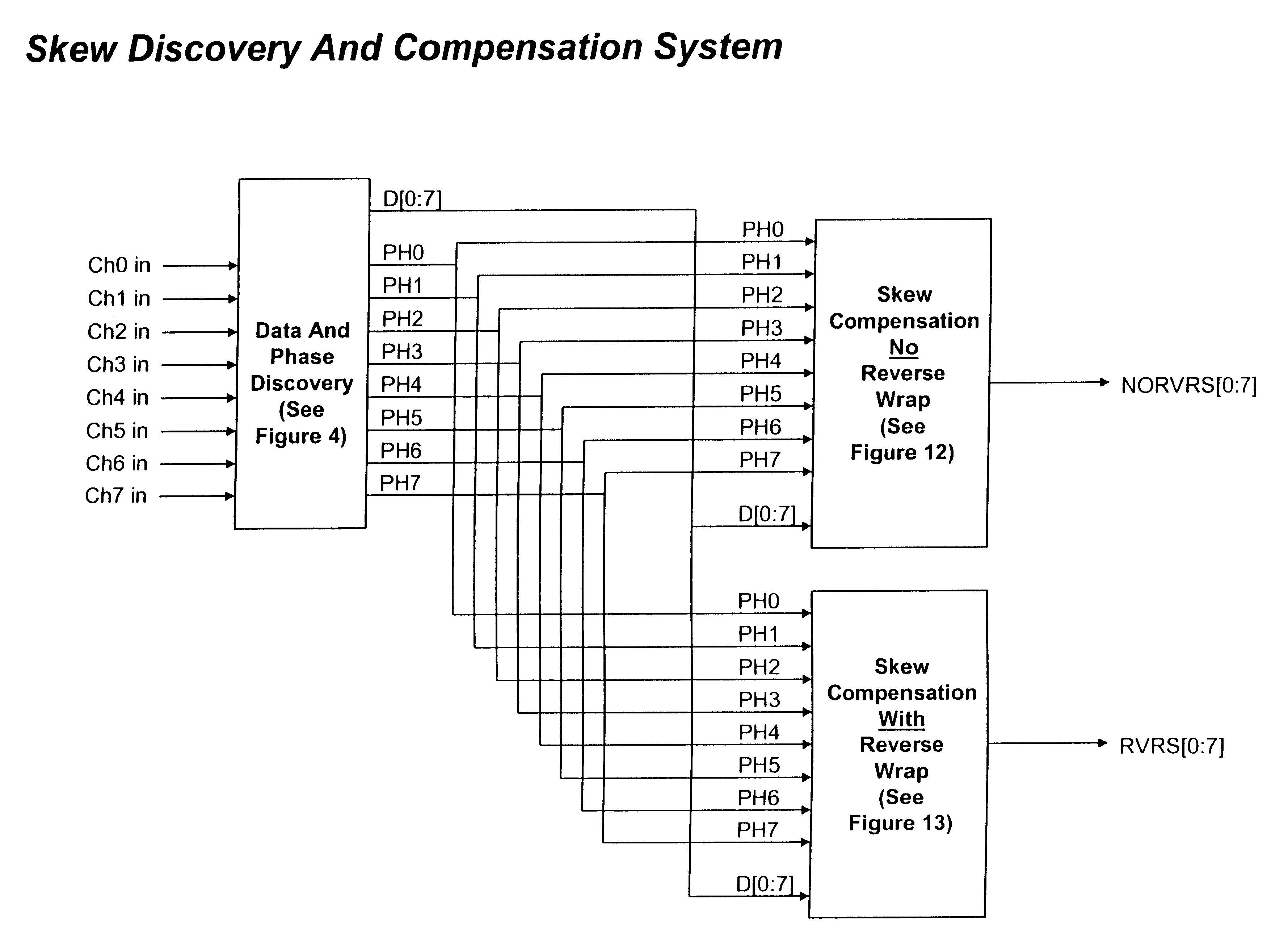

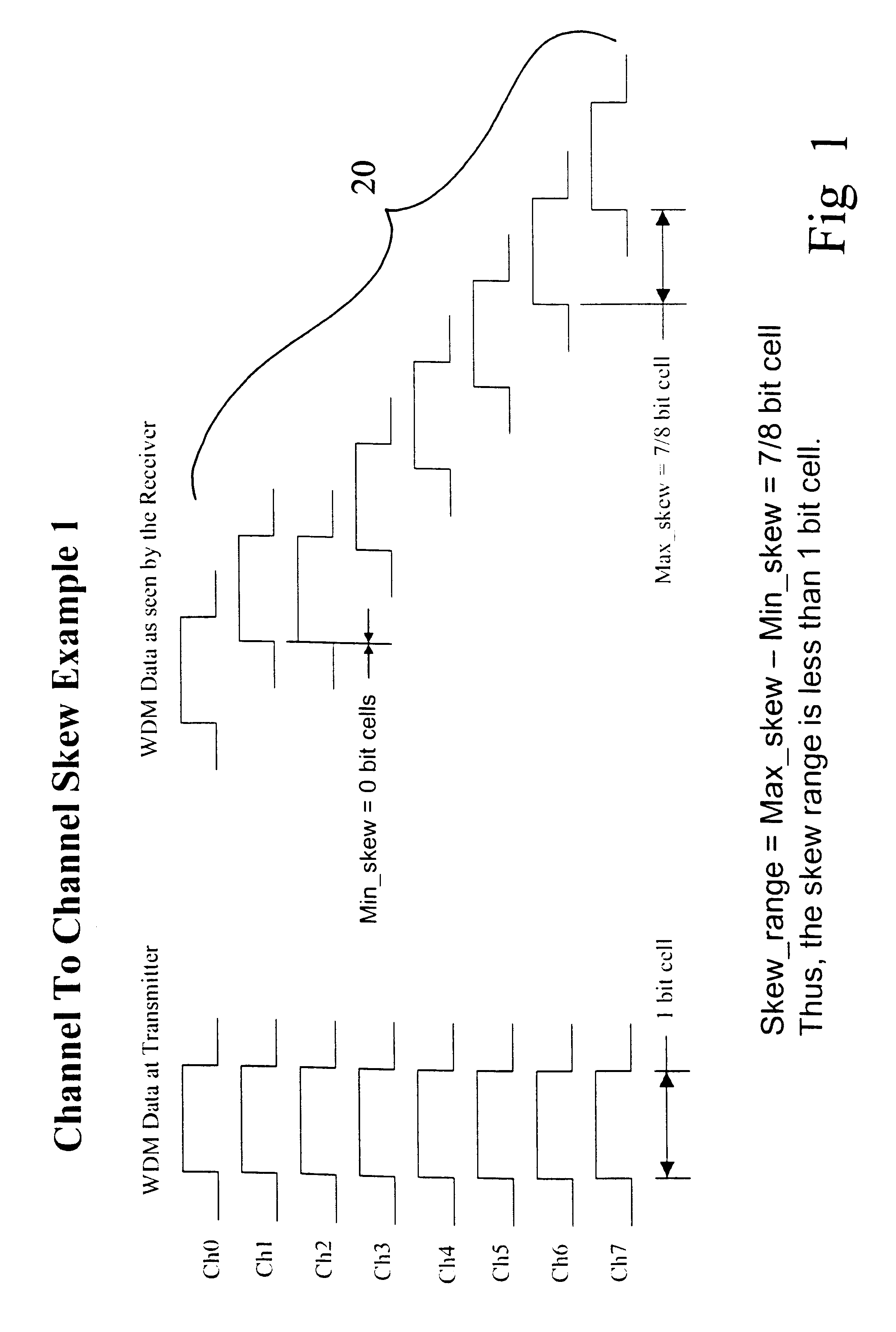

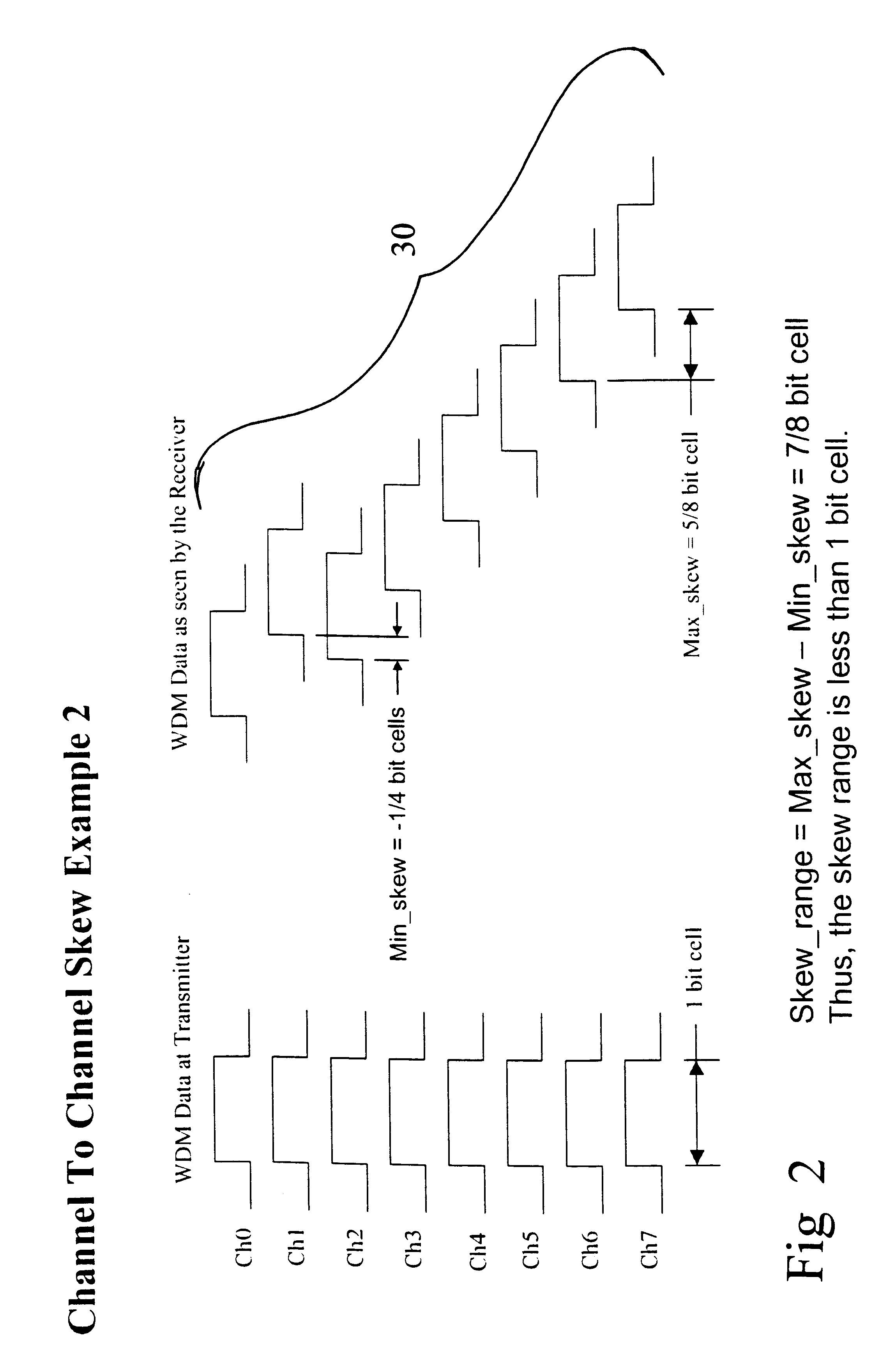

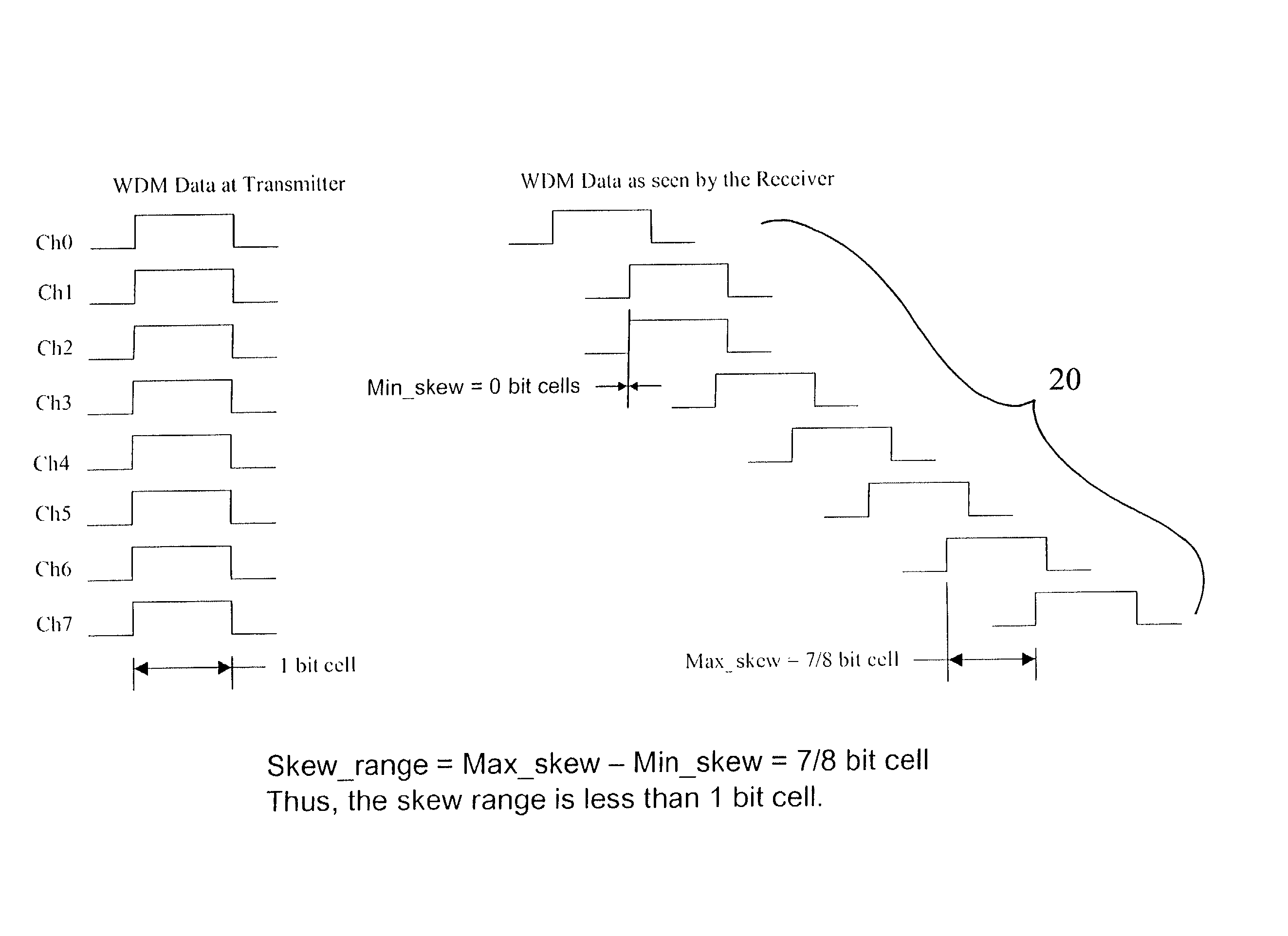

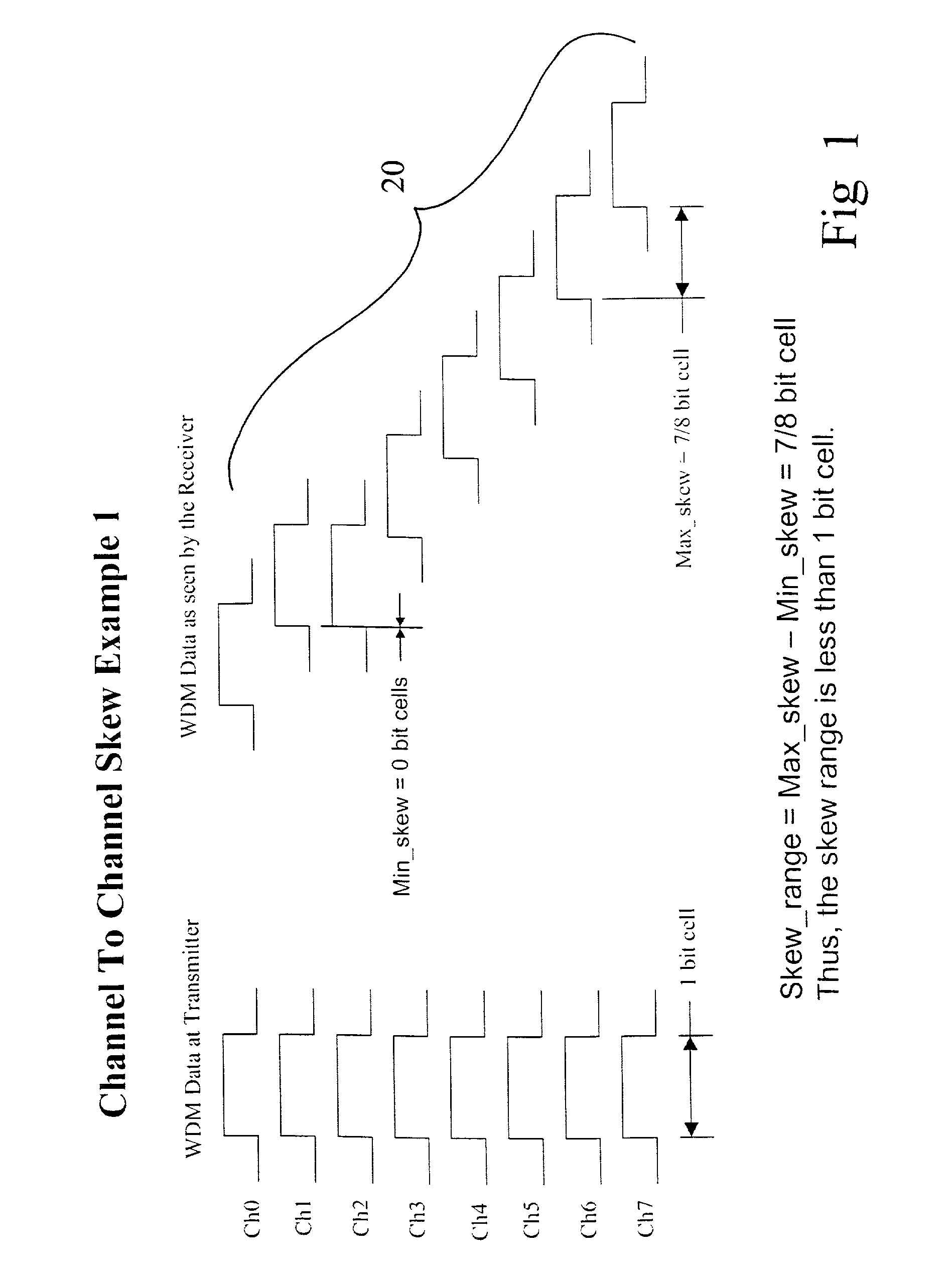

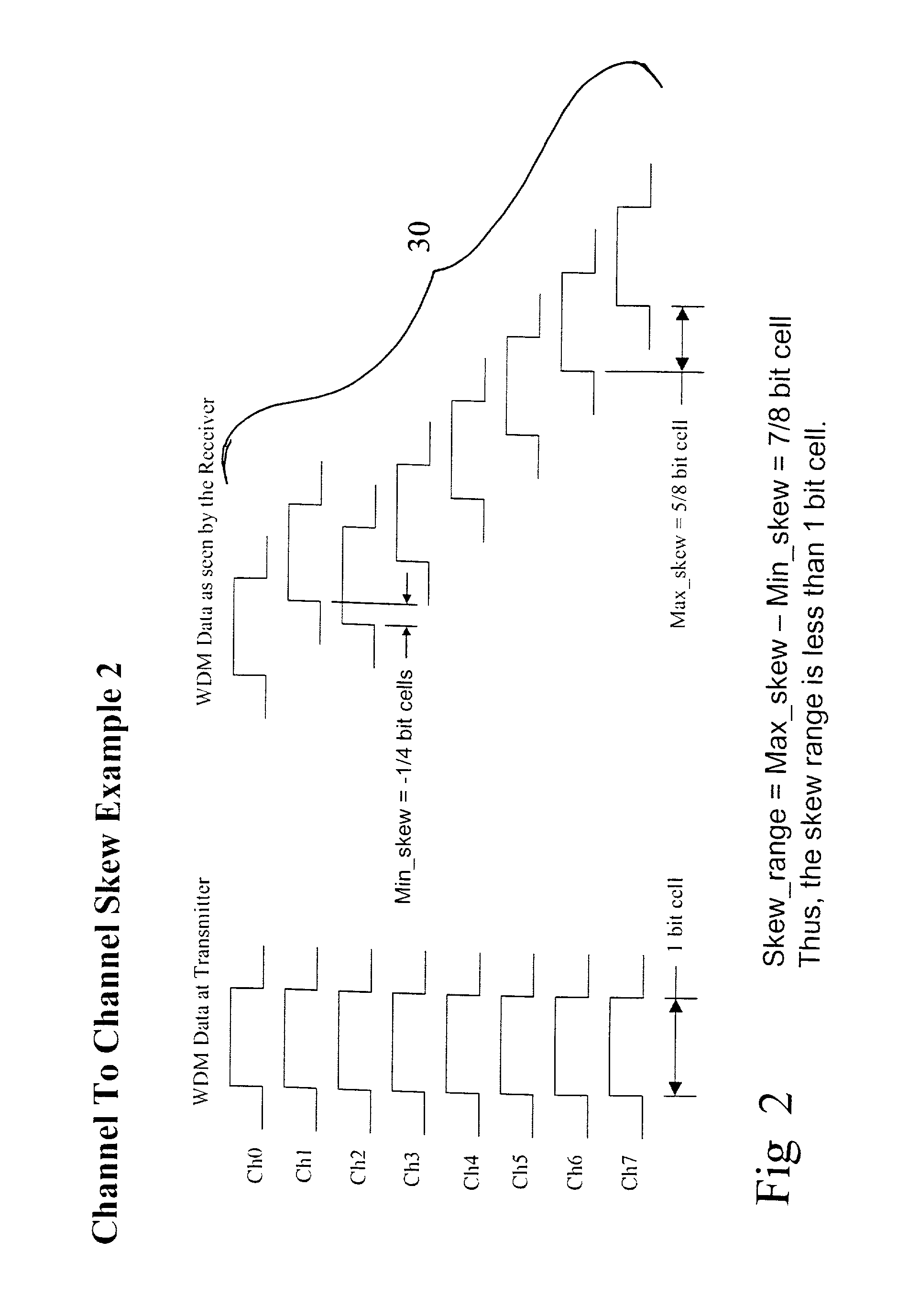

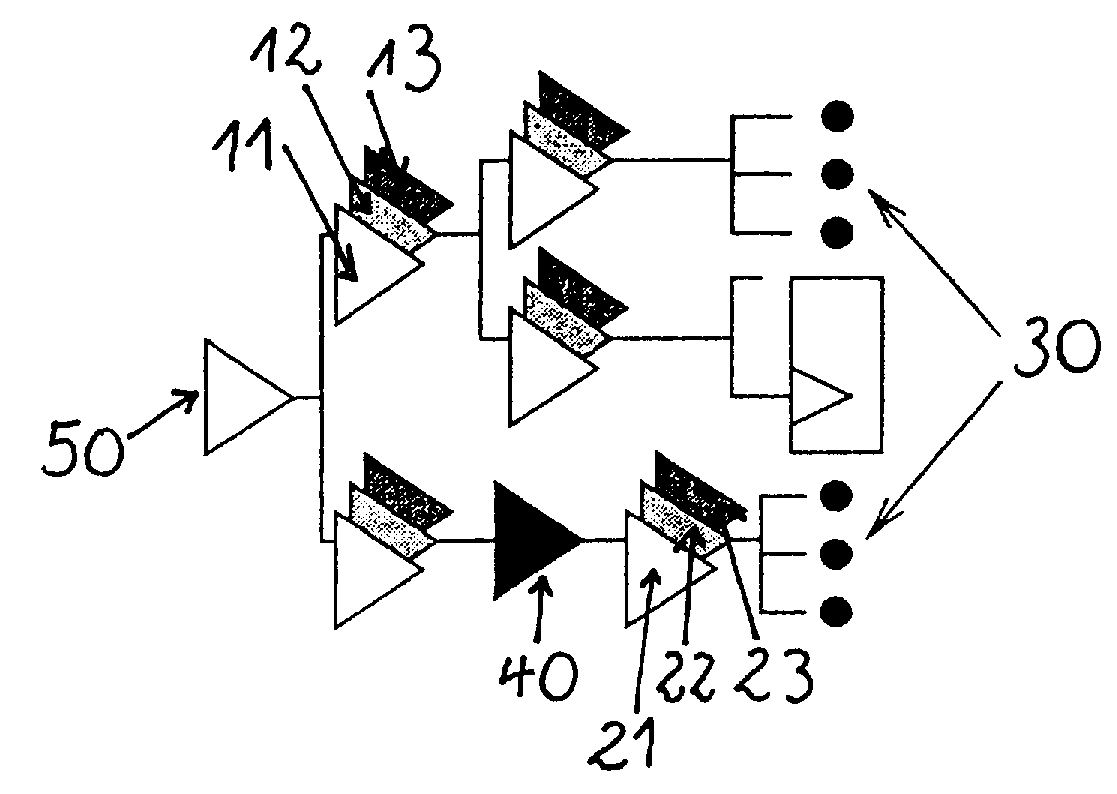

Skew discovery and compensation for WDM fiber communications systems using 8b10b encoding

InactiveUS6735397B2Eliminate needLittle latencyChannel dividing arrangementsWavelength-division multiplex systemsFiberData stream

This invention uses fiber characteristics combined with knowledge of the 8b10b code to discover and compensate for skew between parallel data streams, caused by chromatic dispersion, in a WDM system allowing the receiver to recover both the data and timing of the data streams as they were originally launched. This skew discovery and compensation does not require the insertion or deletion of any control symbols to / from the original 8b10b streams, and does not require the use of a training or sample sequence.

Owner:OMRON MANAGEMENT CENT OF AMERICA

Memory controller with external refresh mechanism

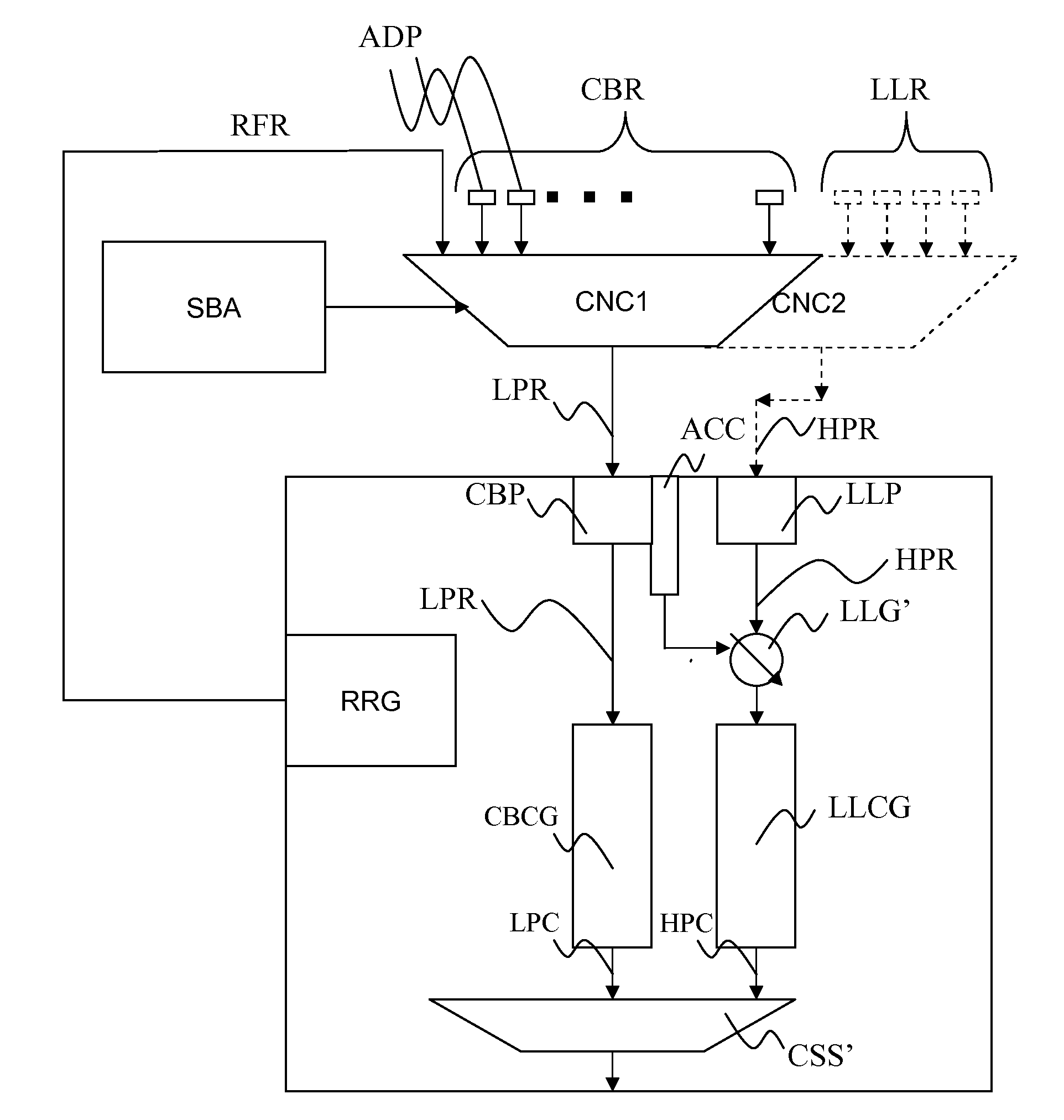

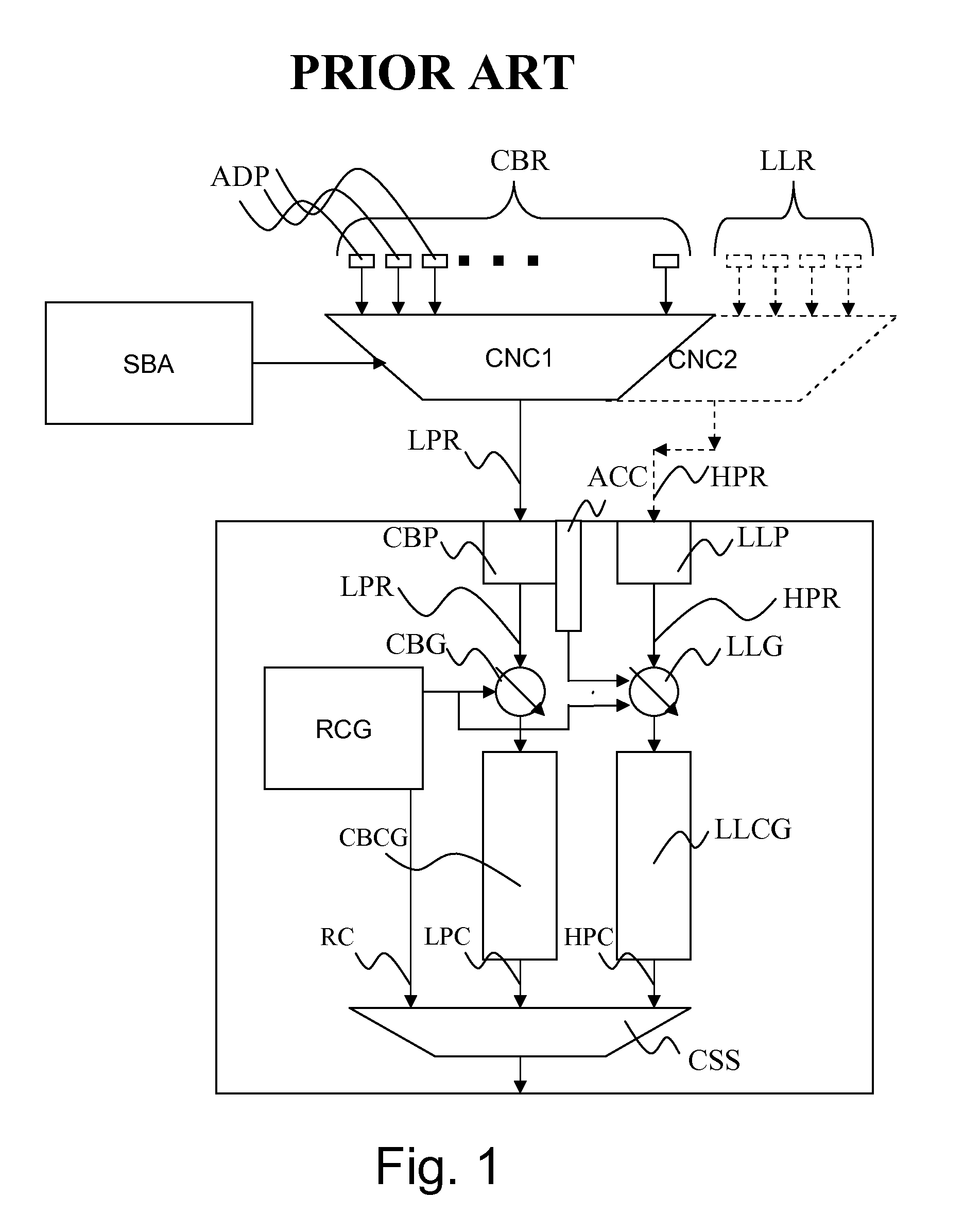

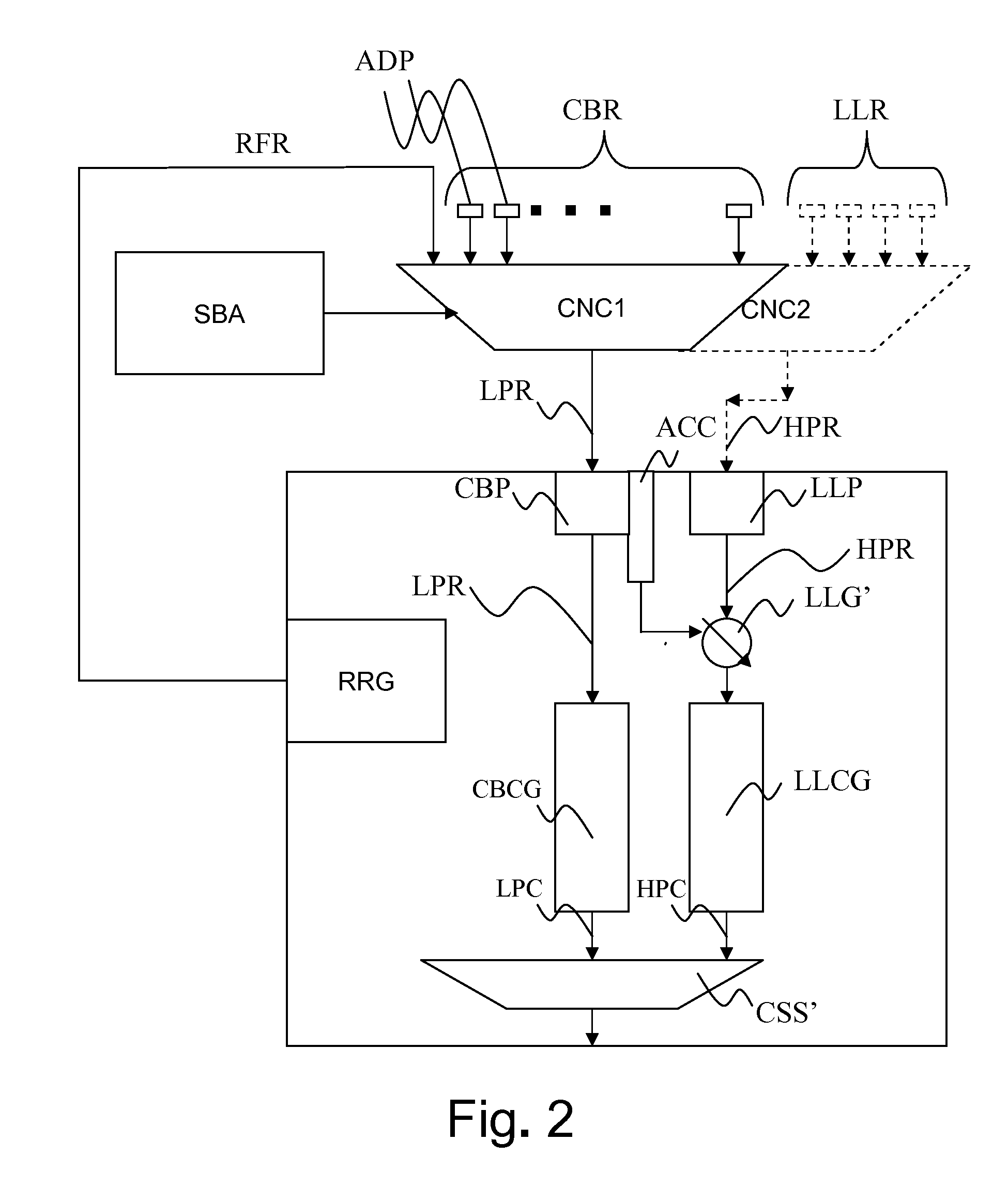

ActiveUS20110113204A1Arbitration is simplifiedEfficient use ofMemory systemsMemory controllerLower priority

The invention relates to a memory controller for use in a System-on-Chip, wherein the System-on-Chip comprises a plurality of agents and an off-chip volatile memory. The memory controller comprises a first port (CBP) for receiving low-priority requests (CBR) for access to the volatile memory from a first-subset of the plurality of agents and a second port (LLP) for receiving high-priority requests (LLR) for access to the volatile memory from a second-subset of the plurality of agents, wherein the memory controller is configured for arbitrating between the high-priority requests (LLR) and the low-priority requests (CBR), wherein the memory controller is configured for receiving refresh requests (RFR) for the volatile memory via the first port (CBP), wherein the refresh requests (RFR) are time-multiplexed with the low-priority requests (CBR), wherein the memory controller is configured for treating the low-priority requests (CBR) and the refresh requests (RFR) the same. The effect is that the arbitration between the different requests is rendered less complex. In embodiments of the memory controller there is also an average latency reduction for the high-priority requests. The invention further relates to a System-on-Chip comprising the memory controller, to a method of a refresh request generator for use in such System-on-Chip. The invention also relates to a method of controlling access of a System-on-Chip to a volatile memory, wherein the System-on-Chip comprises a plurality of agents which need access to the volatile memory, and to a computer program product comprising instructions for causing a processor to perform such method.

Owner:NXP BV

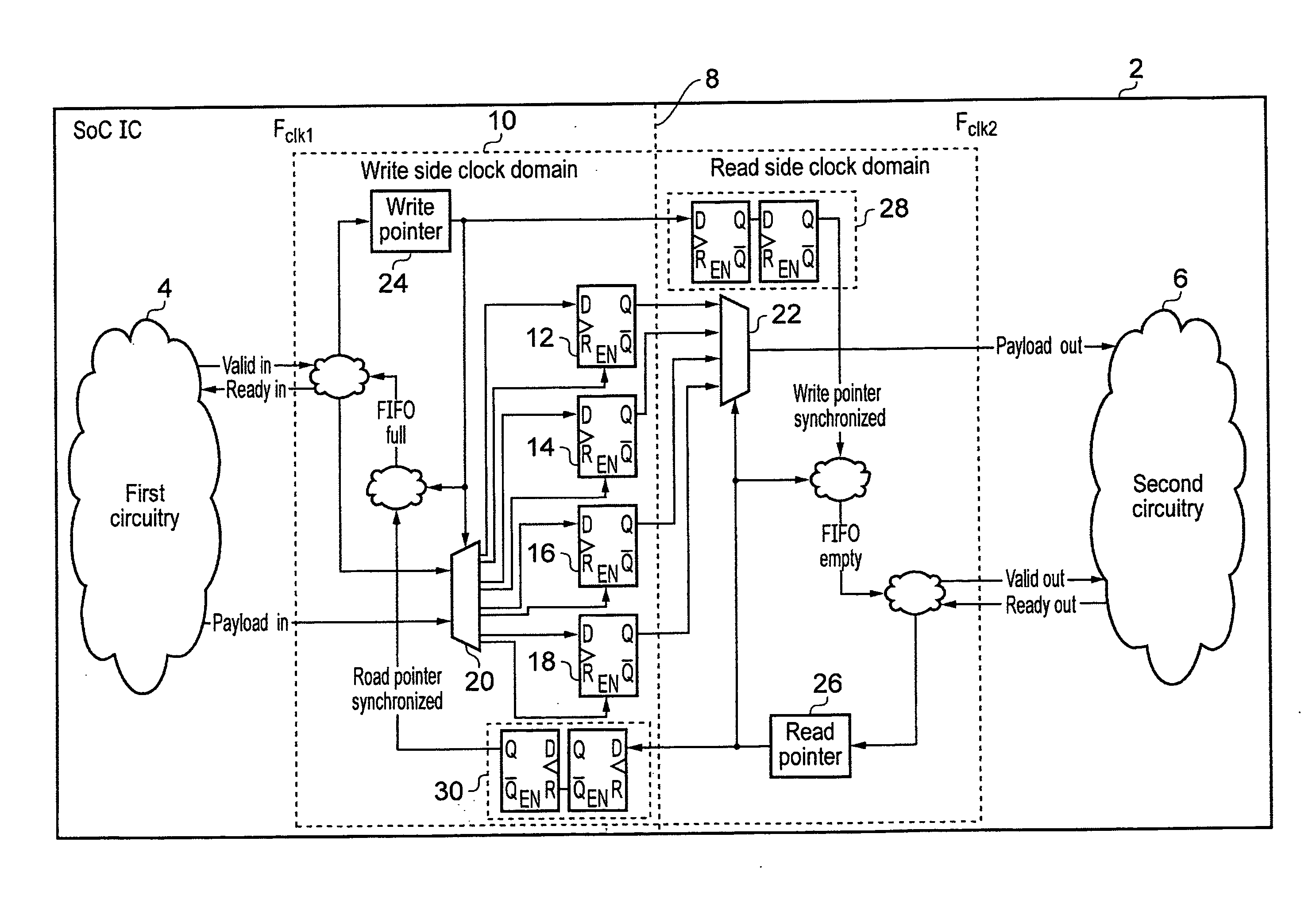

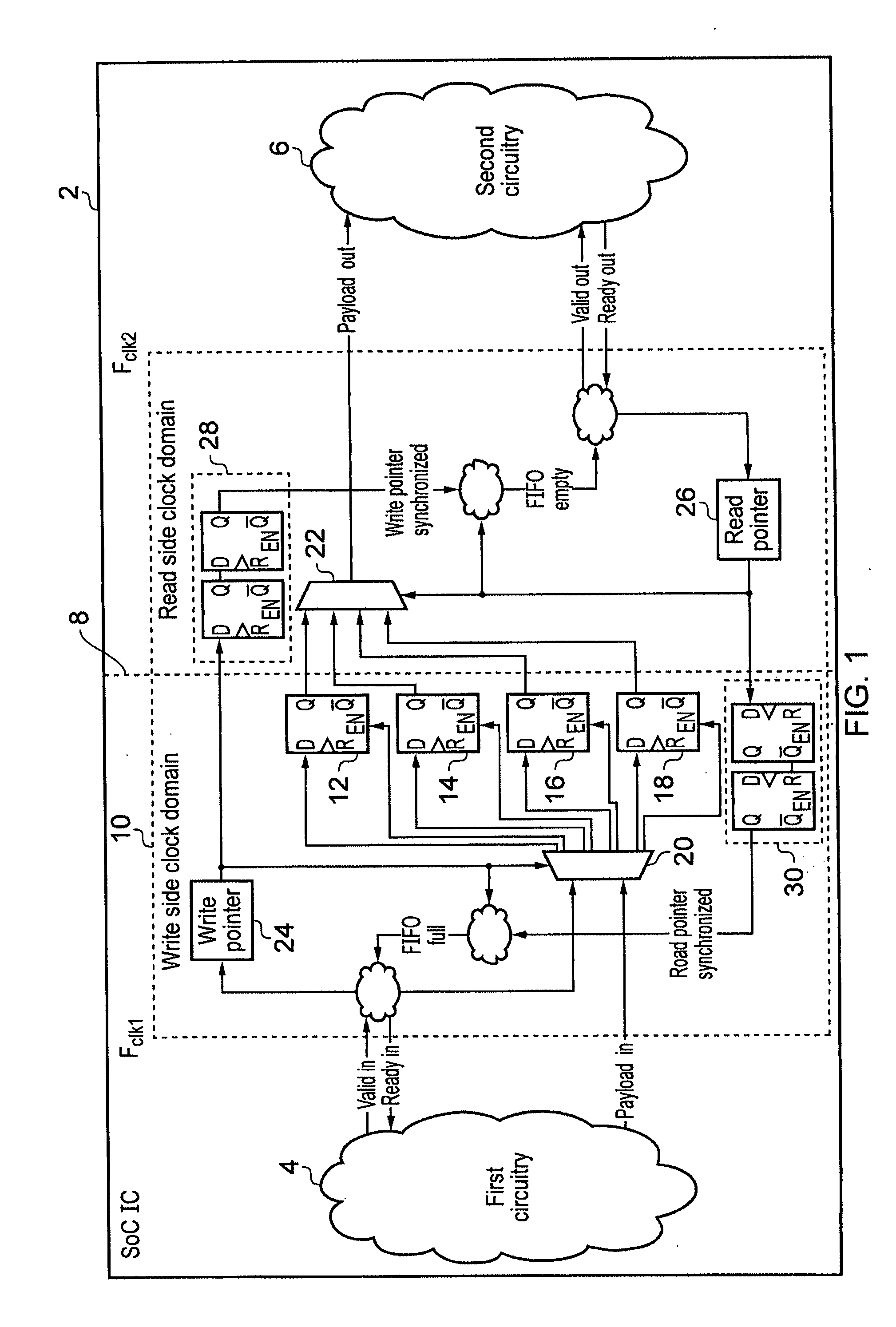

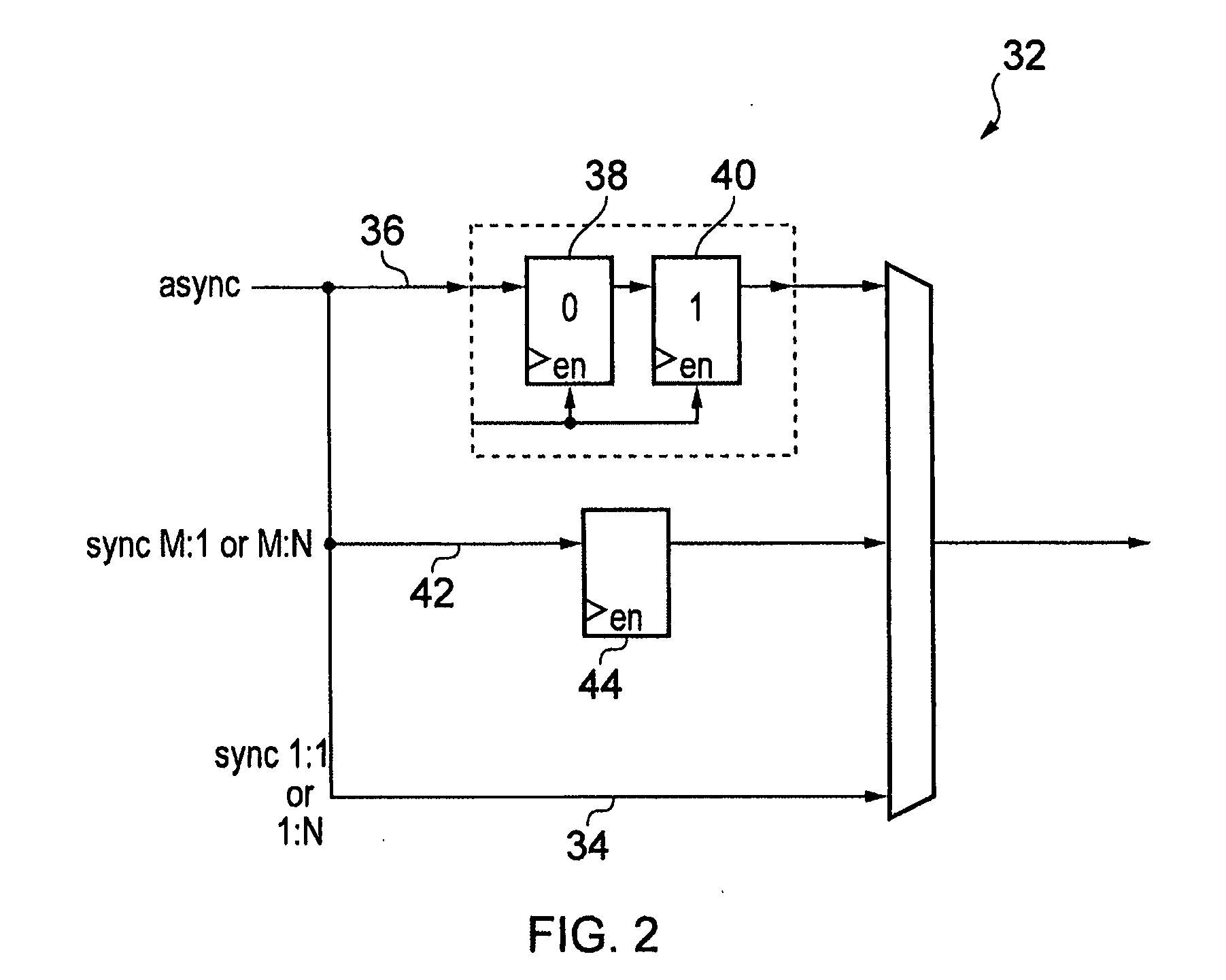

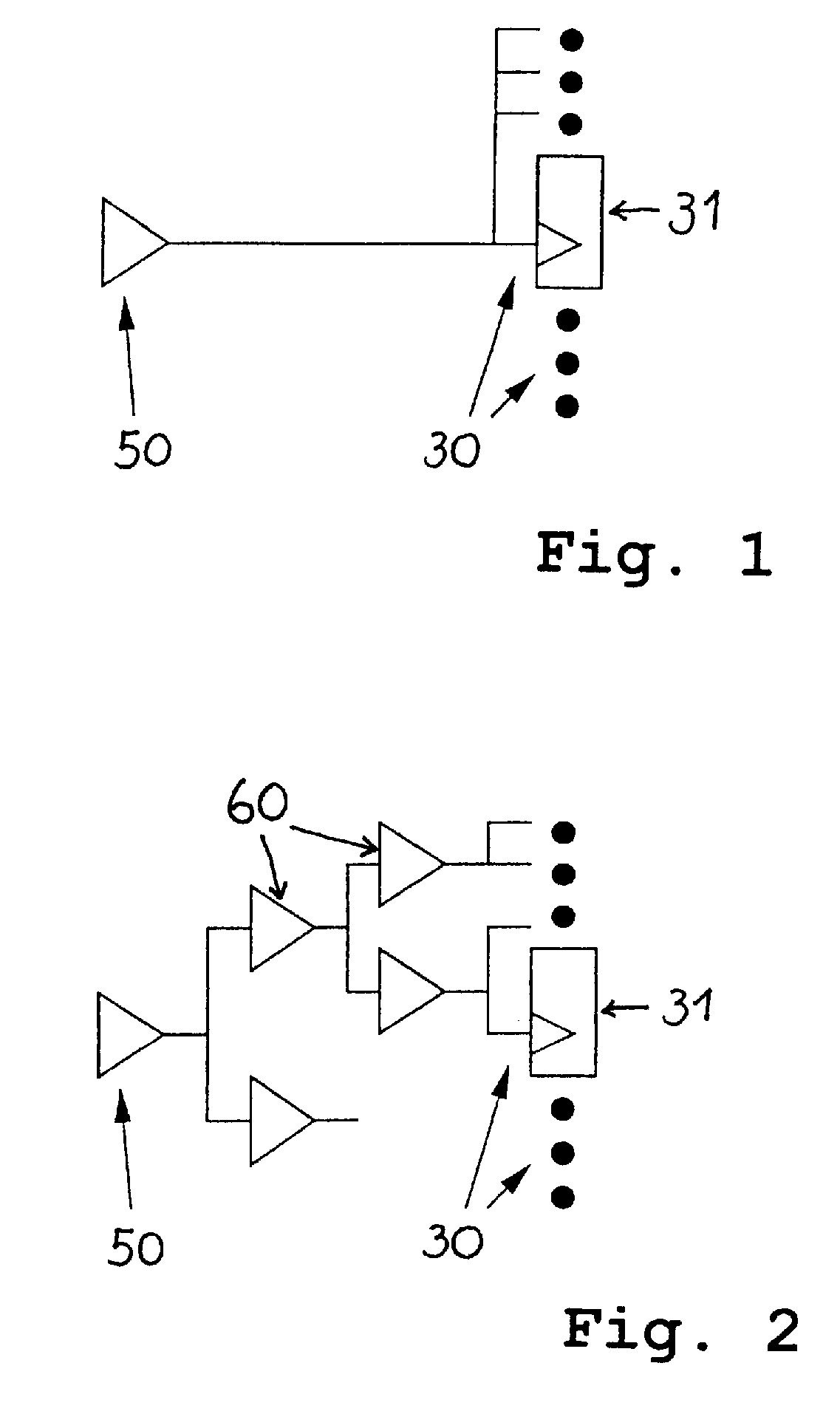

Synchronising between clock domains

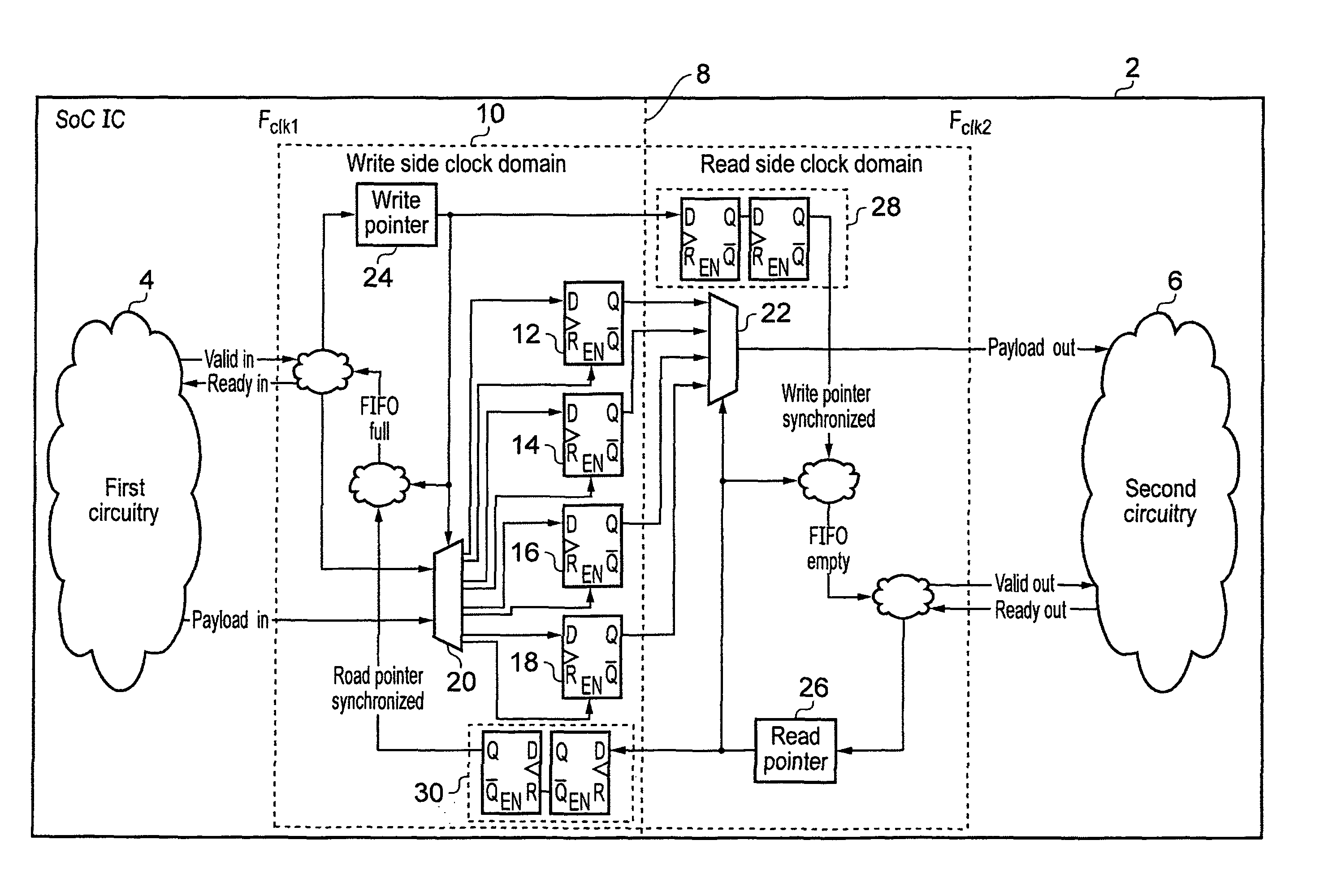

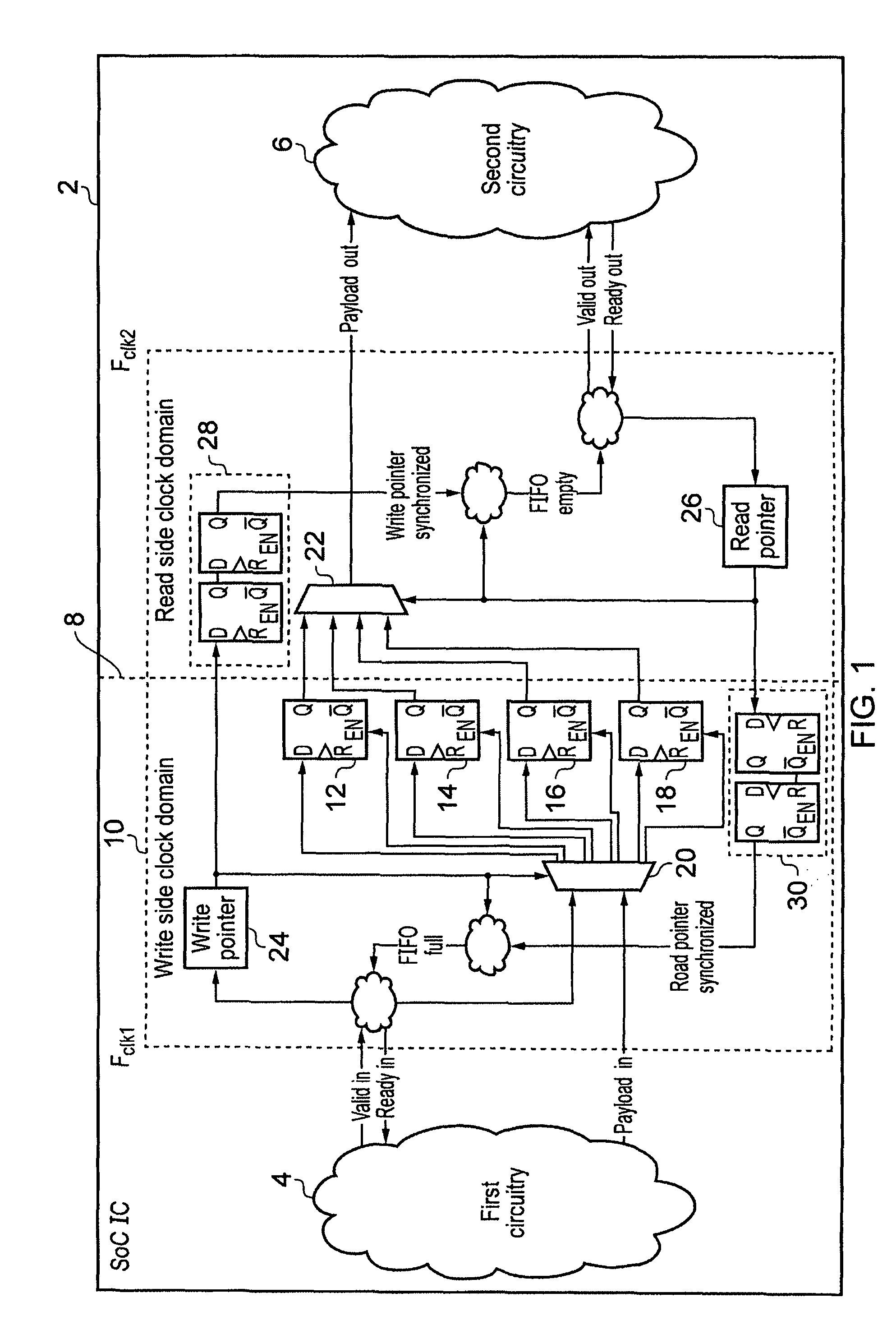

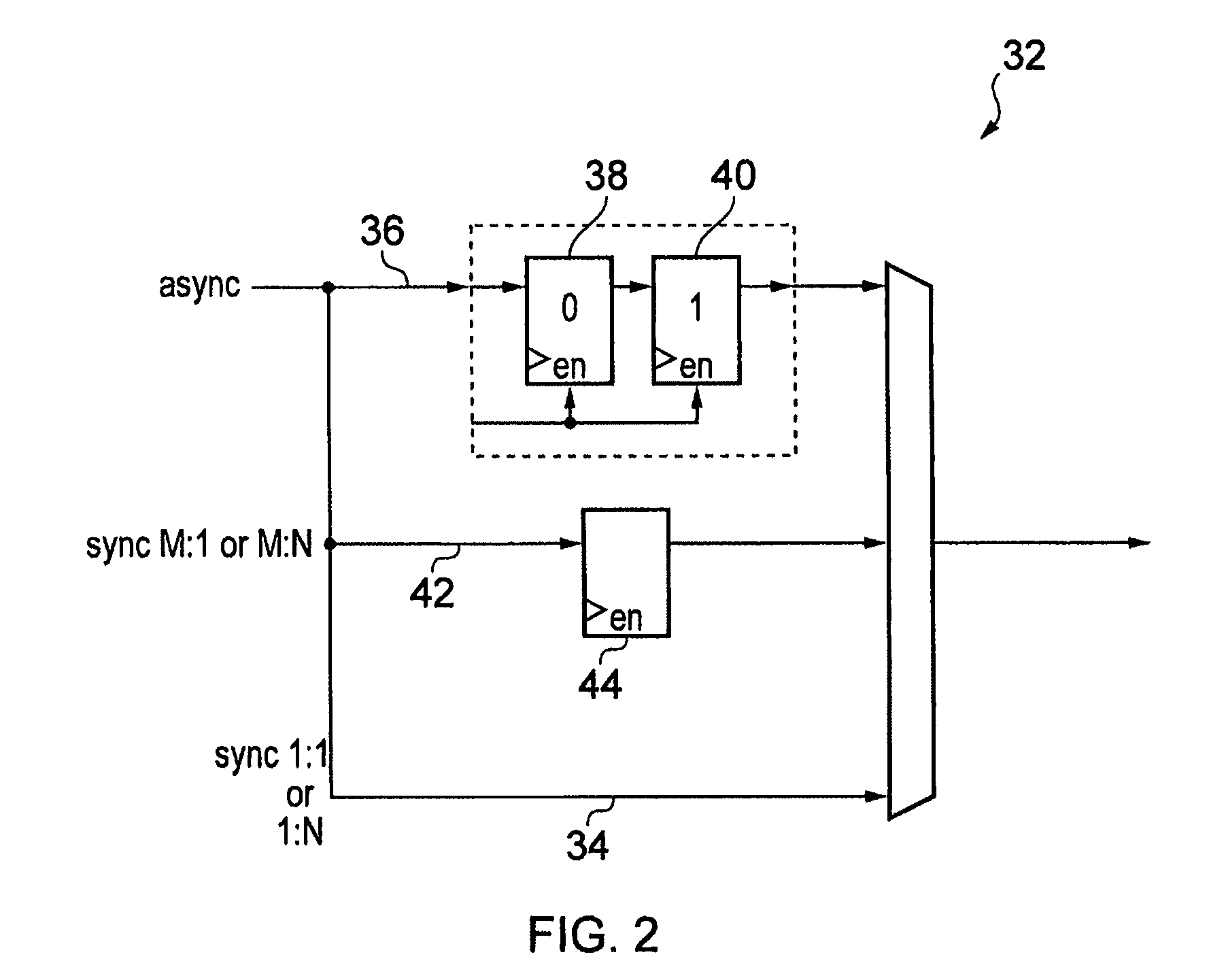

ActiveUS20110116337A1Reduce hardware overheadIncrease in synchronisation delayDigital storageGenerating/distributing signalsProcessor registerClock rate

An integrated circuit 2 is provided with multiple clock domains separated by a clock boundary 8. Data values are passed across the clock boundary 8 using a first-in-first-out memory (FIFO), a read pointer and a write pointer for the FIFO are passed across the clock boundary 8 and must be synchronised to the receiving clock frequency. The clocks being used on either side of the clock boundary 8 may be switched and have a variable relationship therebetween. Multiple synchronisation paths are provided within pointer synchronising circuitry 32 which are used depending upon the particular relationship between the clocks on either side of the clock boundary 8. A pre-switch pointer value is held in a transition register 44 until a post-switch pointer value is available from the new synchronising path 36 when a switch in clock mode is made which requires an increase in synchronisation delay.

Owner:ARM LTD

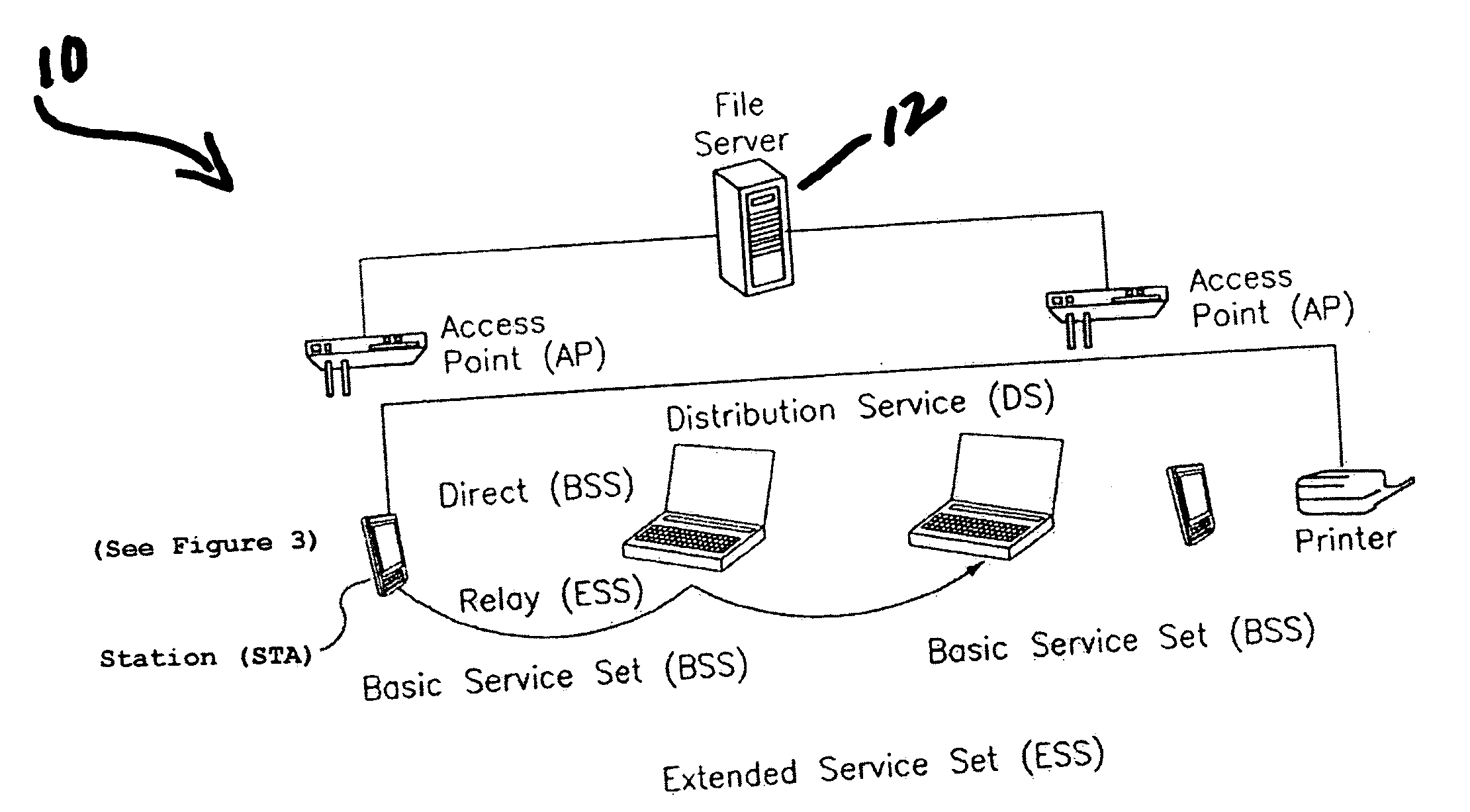

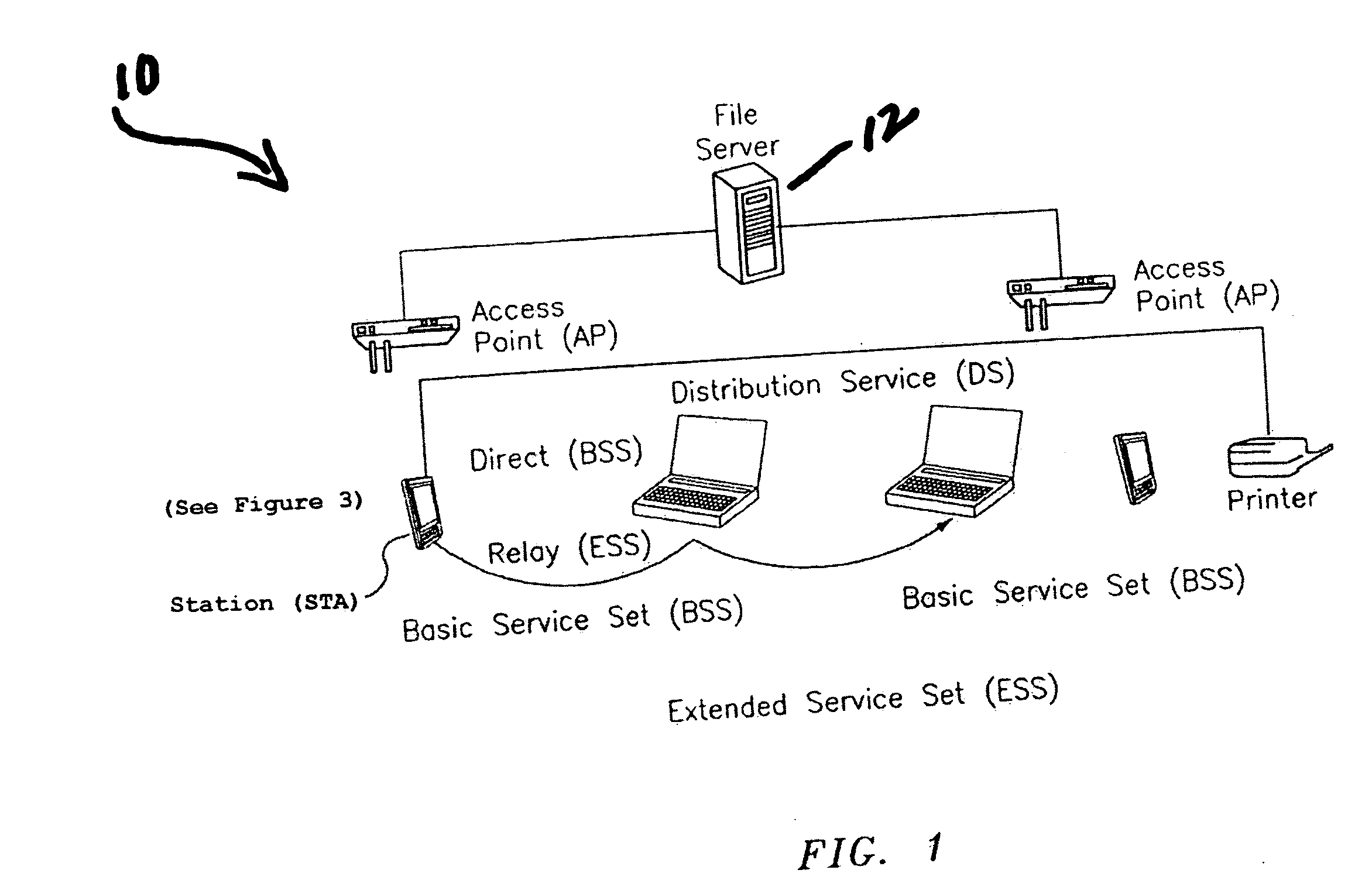

Method and apparatus for detecting trends in received signal strength

InactiveUS20080032628A1Reduce power consumptionAvoid large data transfersRadio/inductive link selection arrangementsRadio transmissionRadio coverageTelecommunications

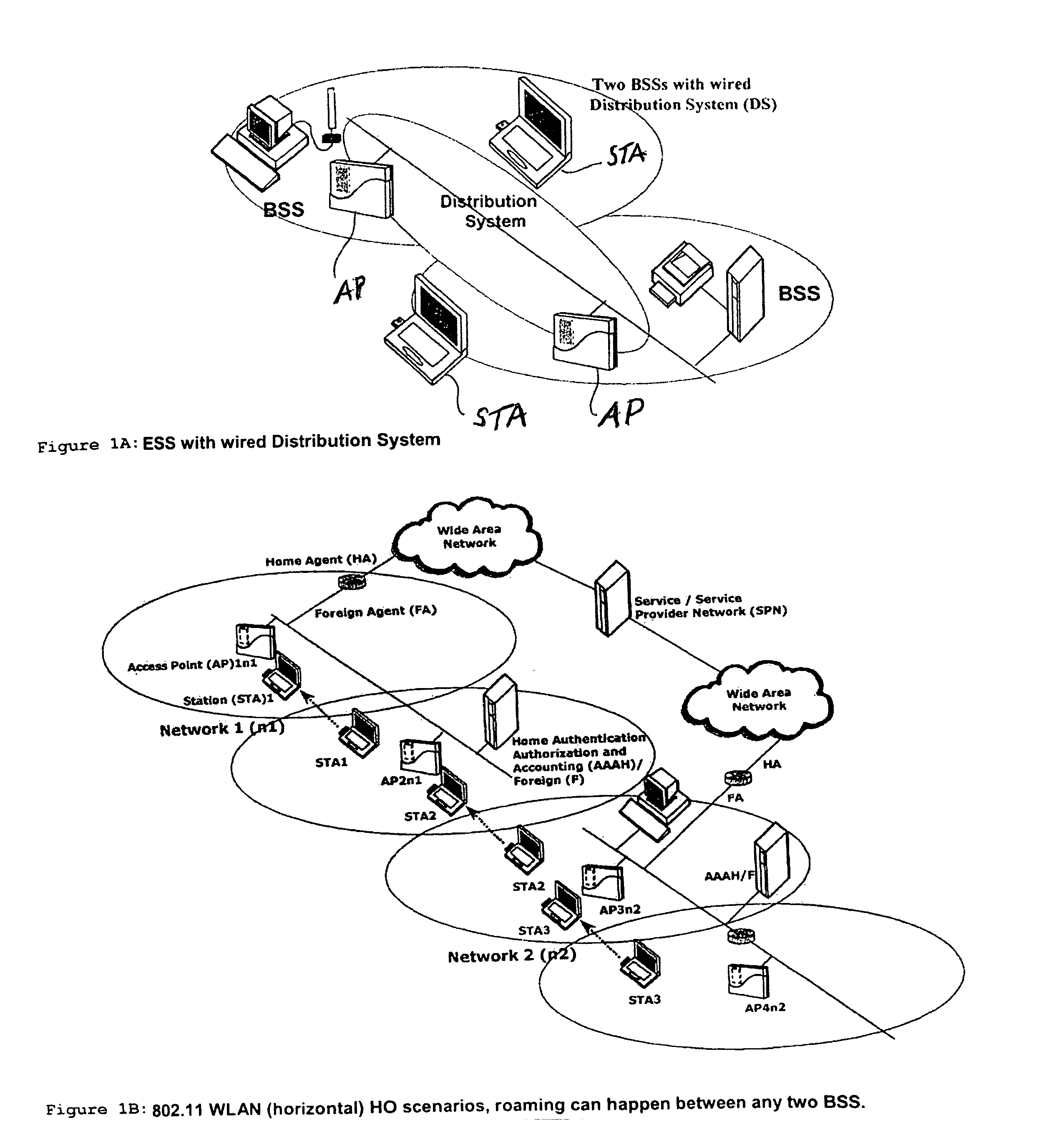

The present invention provides a new and unique method and apparatus for detecting in a short-range communication device, such as a WLAN station (STA), the trend in WLAN signal strength based on one or more characteristics, e.g. received signal strength values and current time of their observation, by fitting a generalized linear model to the values. Based on the detected trend, three things can be inferred: 1) WLAN radio coverage available for STA is strengthening, 2) WLAN radio coverage available for STA is stationary, or 3) WLAN radio coverage available for STA is weakening.

Owner:NOKIA CORP

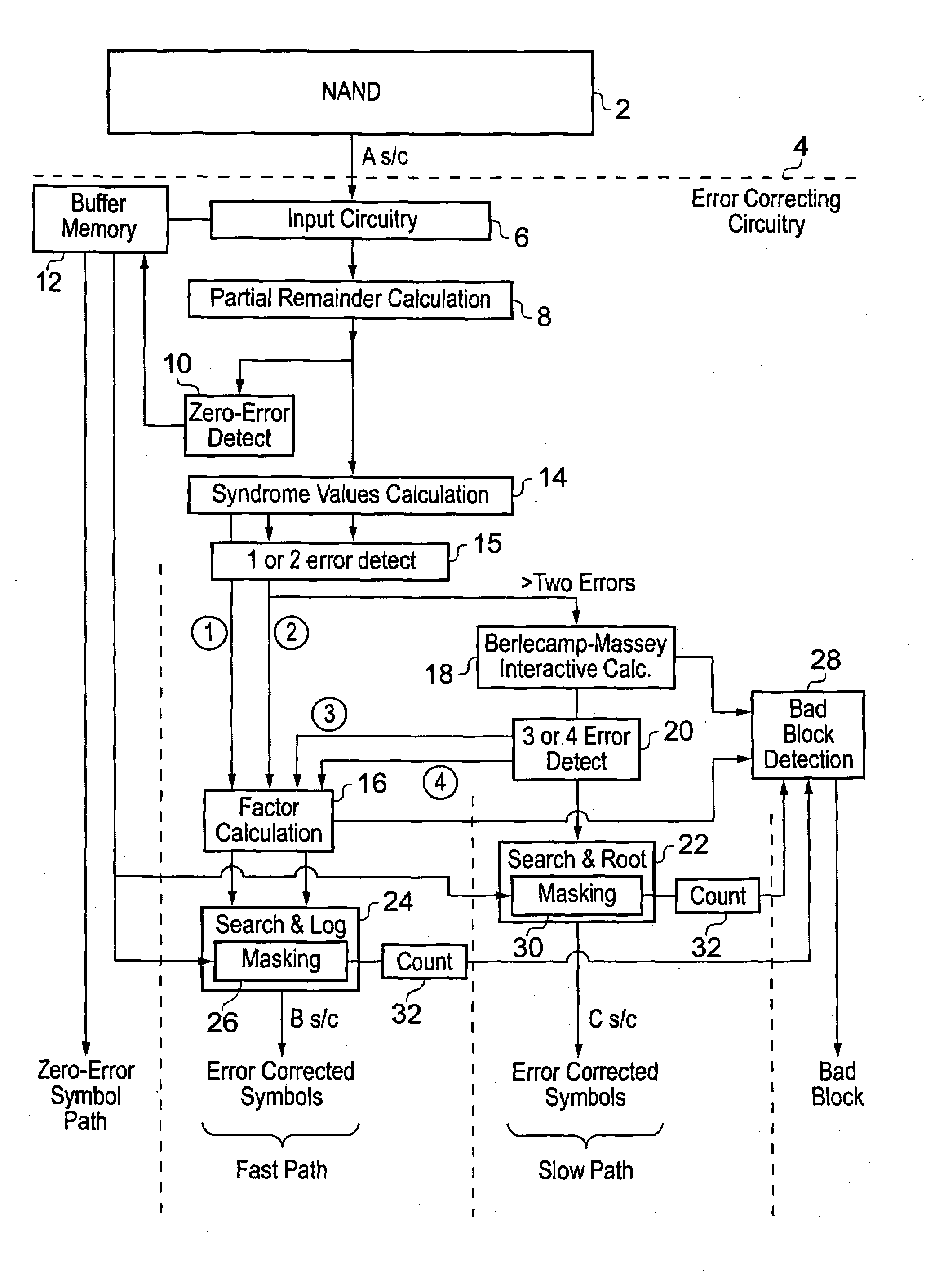

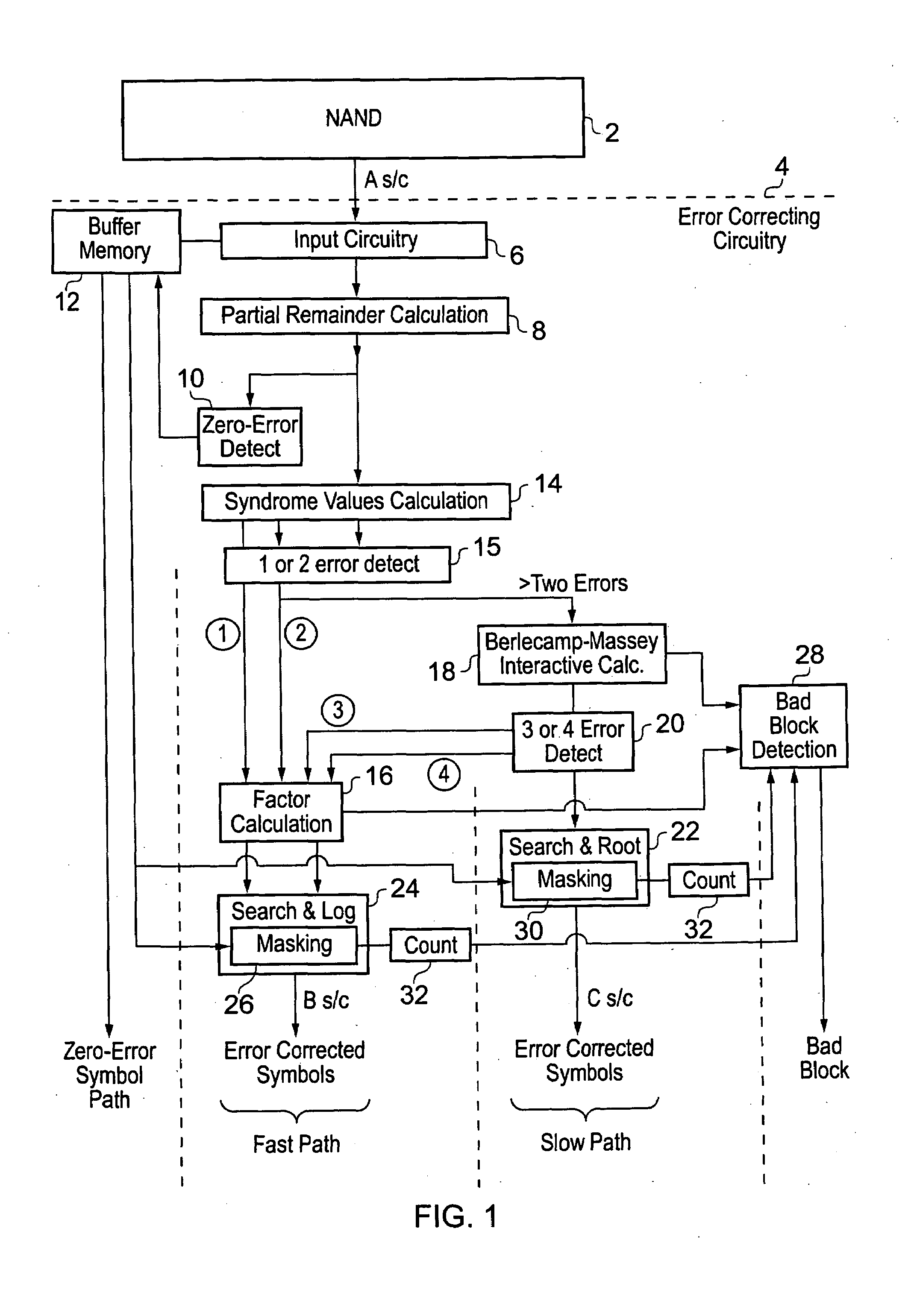

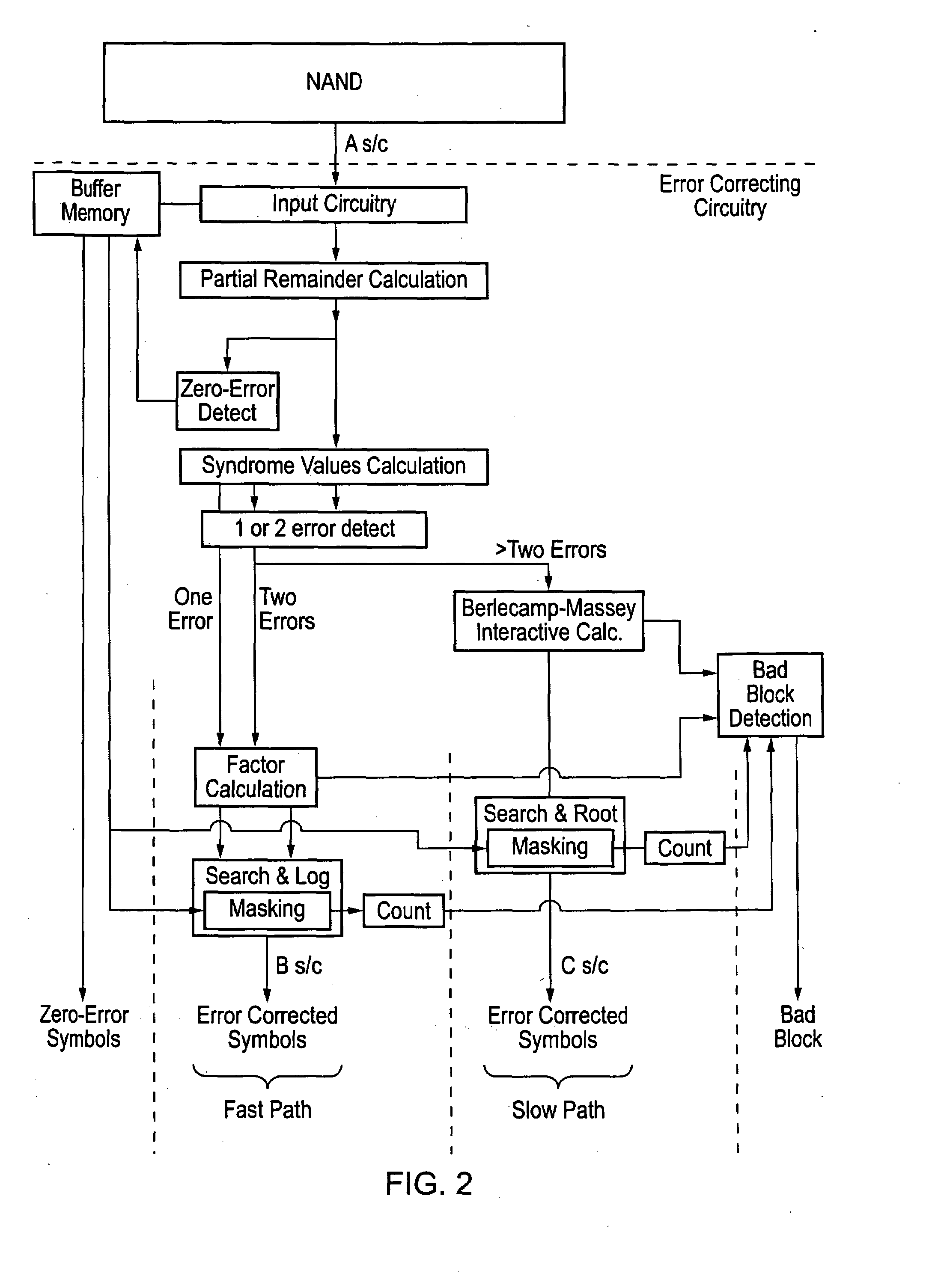

Memory controller for NAND memory using forward error correction

InactiveUS20100332942A1High degree of error tolerance/detectionLittle latencyFault responseStatic storageFast pathForward error correction

A memory controller 4 for a NAND memory array 2 includes error detecting circuitry having input circuitry 6, fast zero-error detecting circuitry 10, fast-path error correcting circuitry 16, 24, slow-path error correcting circuitry 18, 22 and fast-bad-block detecting circuitry 28.

Owner:ARM LTD

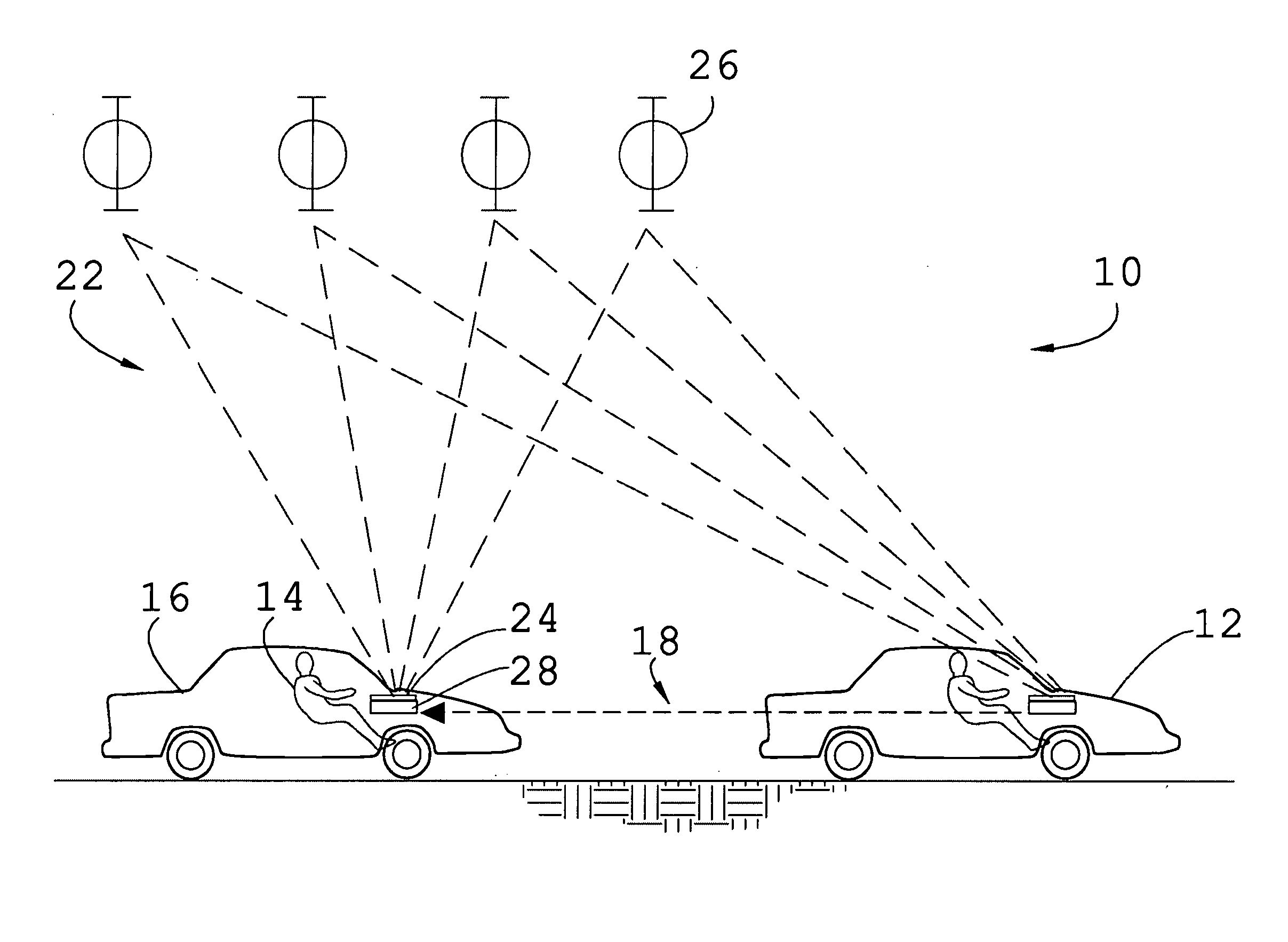

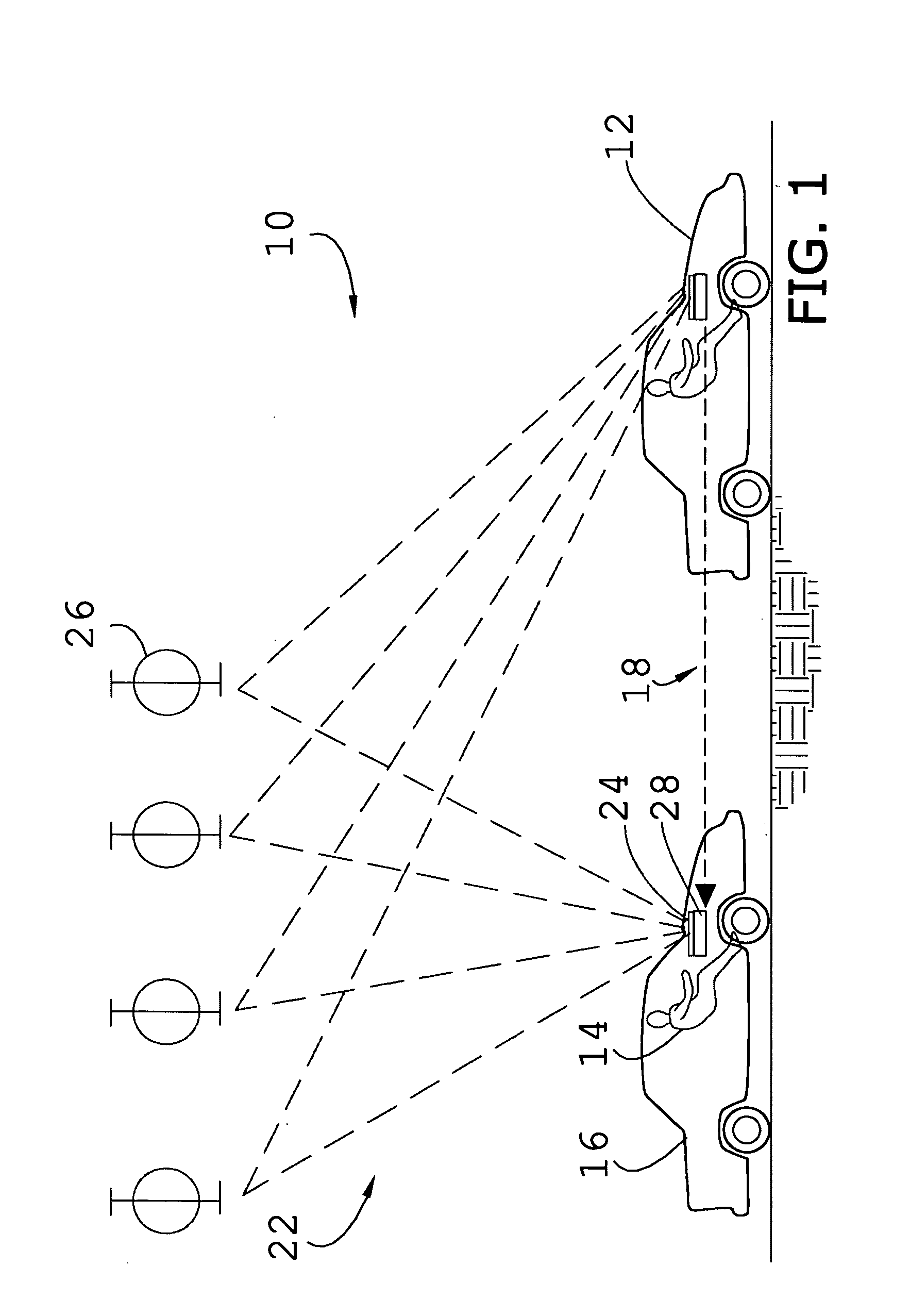

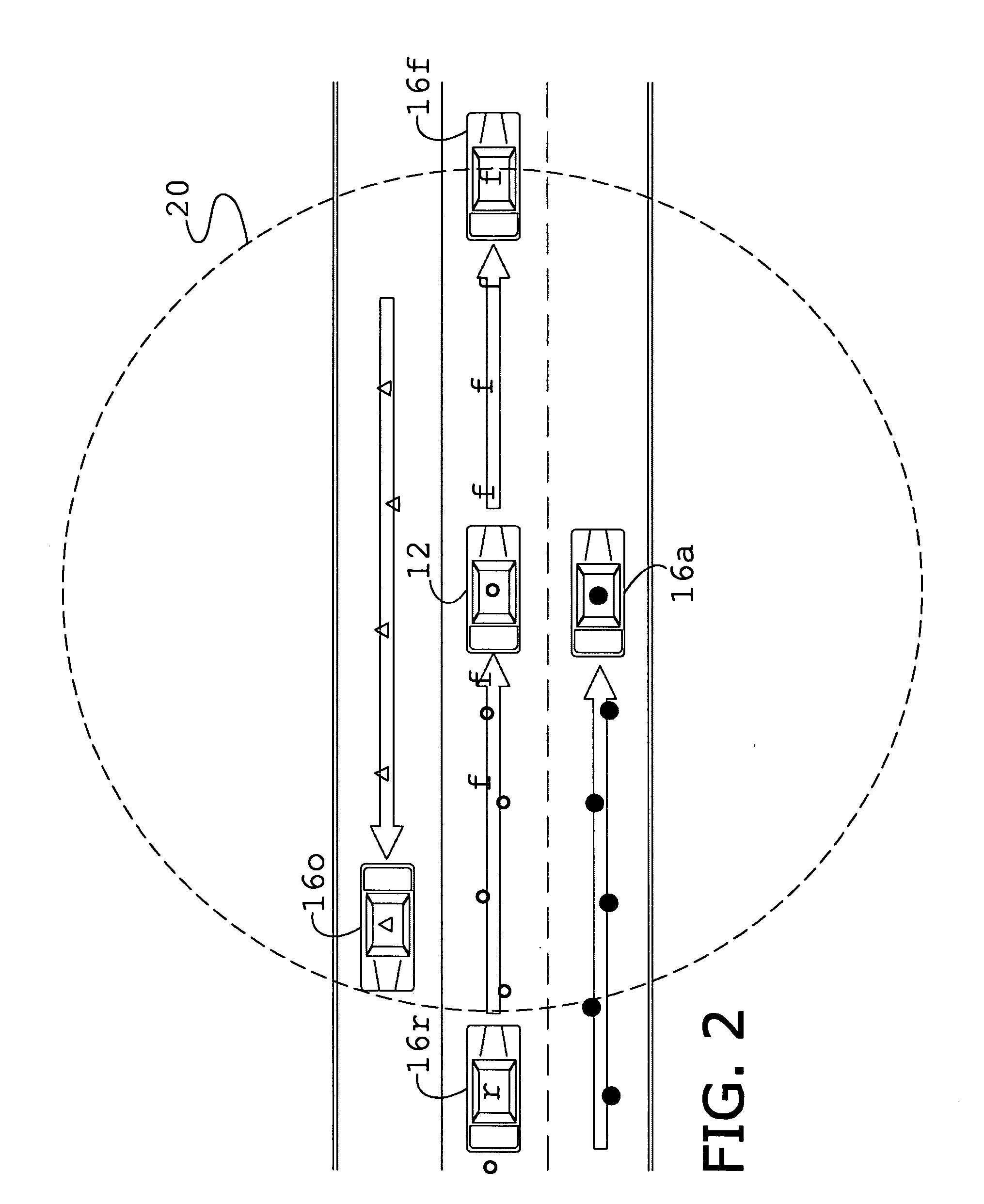

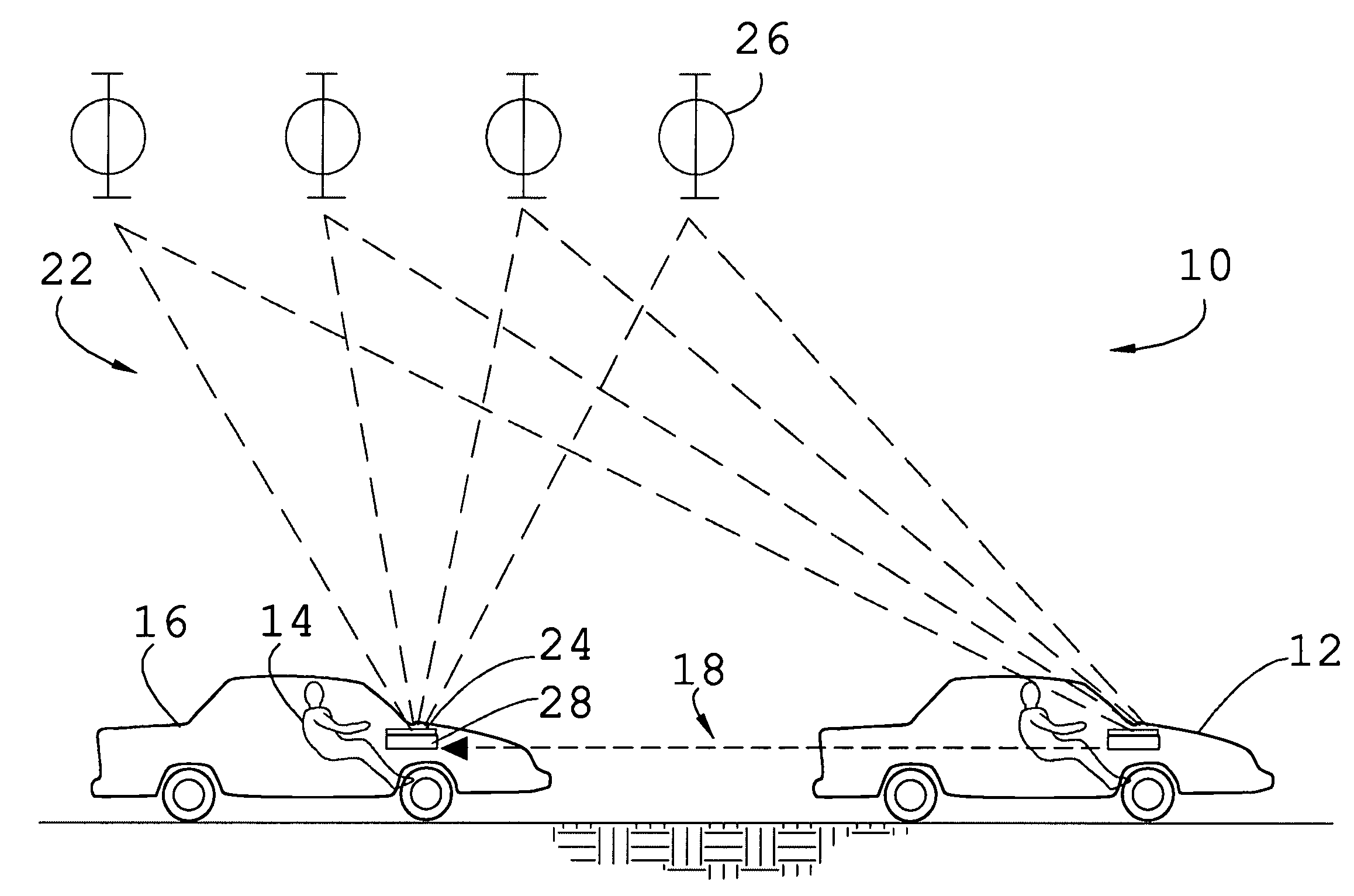

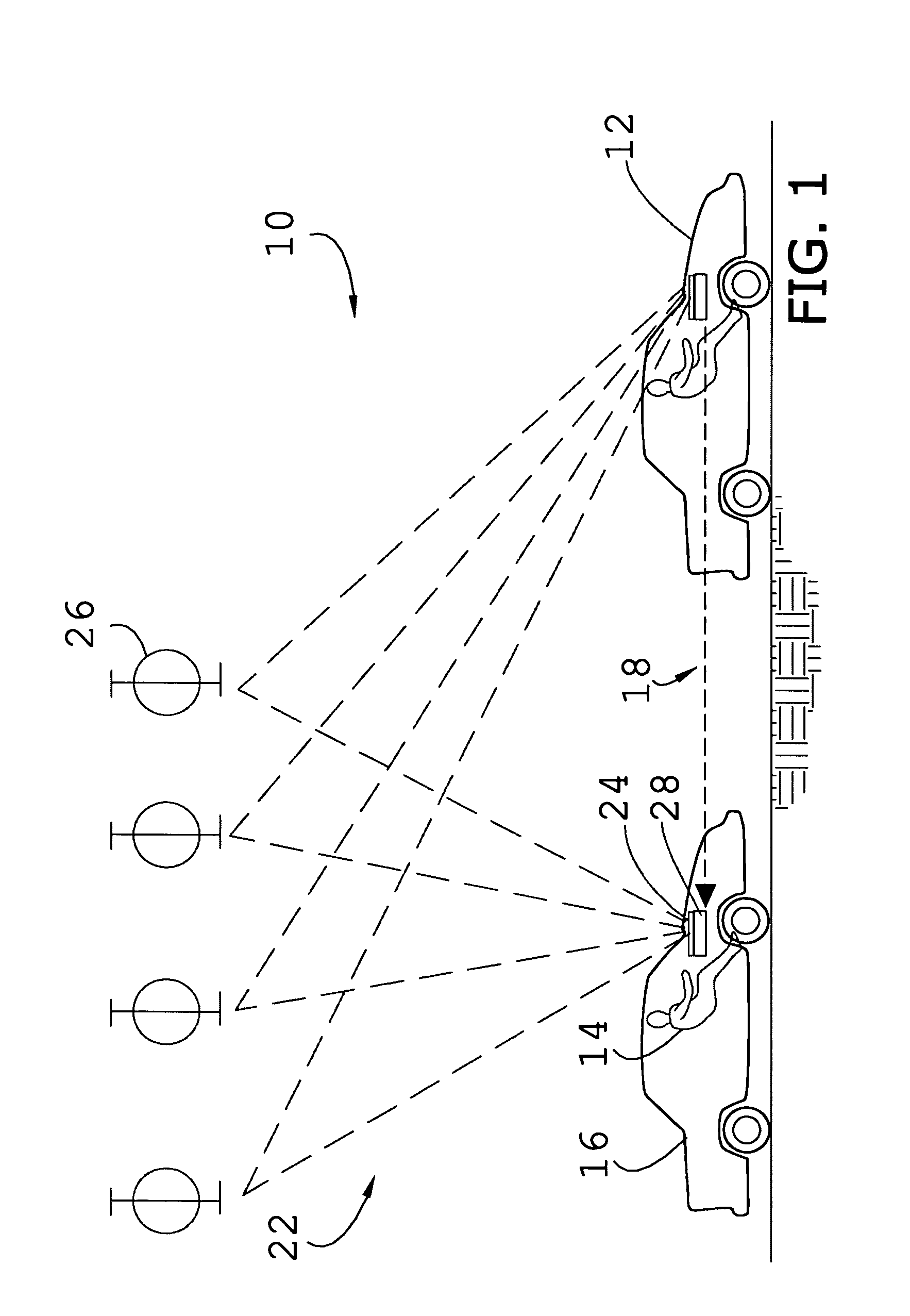

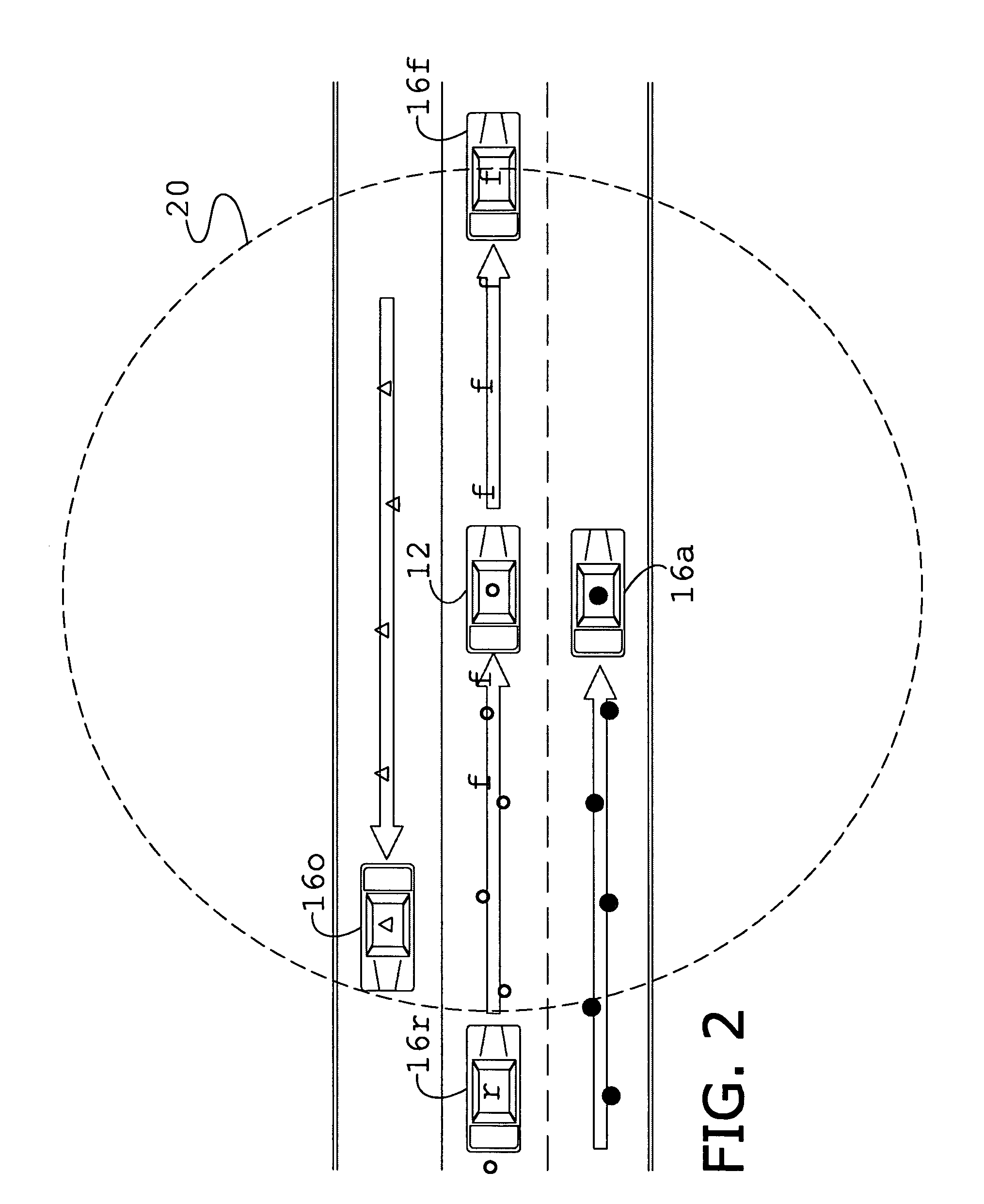

Inter vehicular ad hoc routing protocol and communication system

InactiveUS20070198140A1High penetration distance within an event lifetimeLittle latencyRegistering/indicating working of vehiclesRoad vehicles traffic controlCommunications systemInter vehicle communication

A routing protocol and inter-vehicle communication system adapted for use with a traveling host vehicle, and at least one traveling remote vehicle, includes a locator sub-system configured to determine a plurality of current position coordinates for the host and remote vehicles. The preferred system is configured to store trail coordinates, derive vehicular headings and trail polygons from the trail coordinates, and effect the directional multi-hop propagation of a message by comparing current position coordinates, trail coordinates, headings and / or trail polygons of the host and remote vehicles.

Owner:GM GLOBAL TECH OPERATIONS LLC

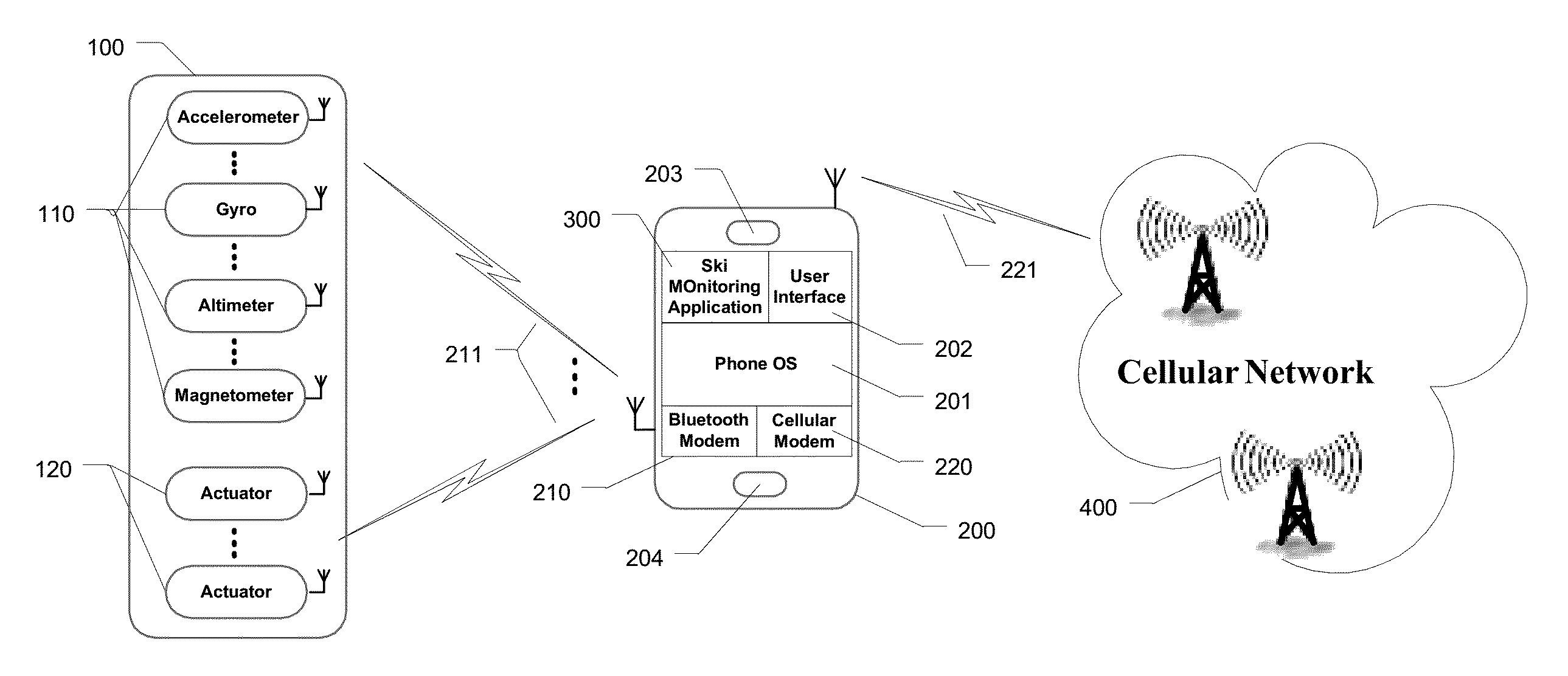

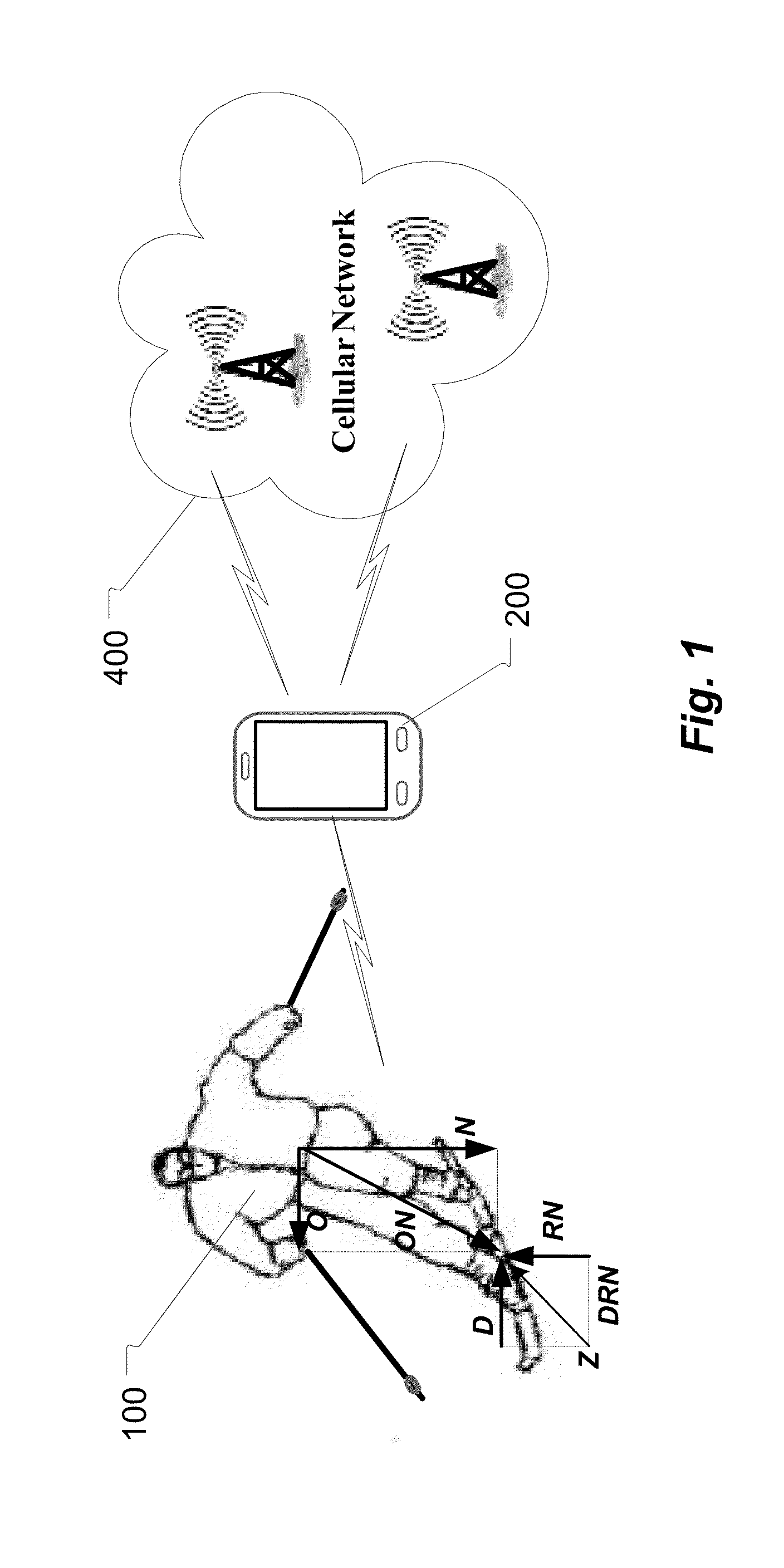

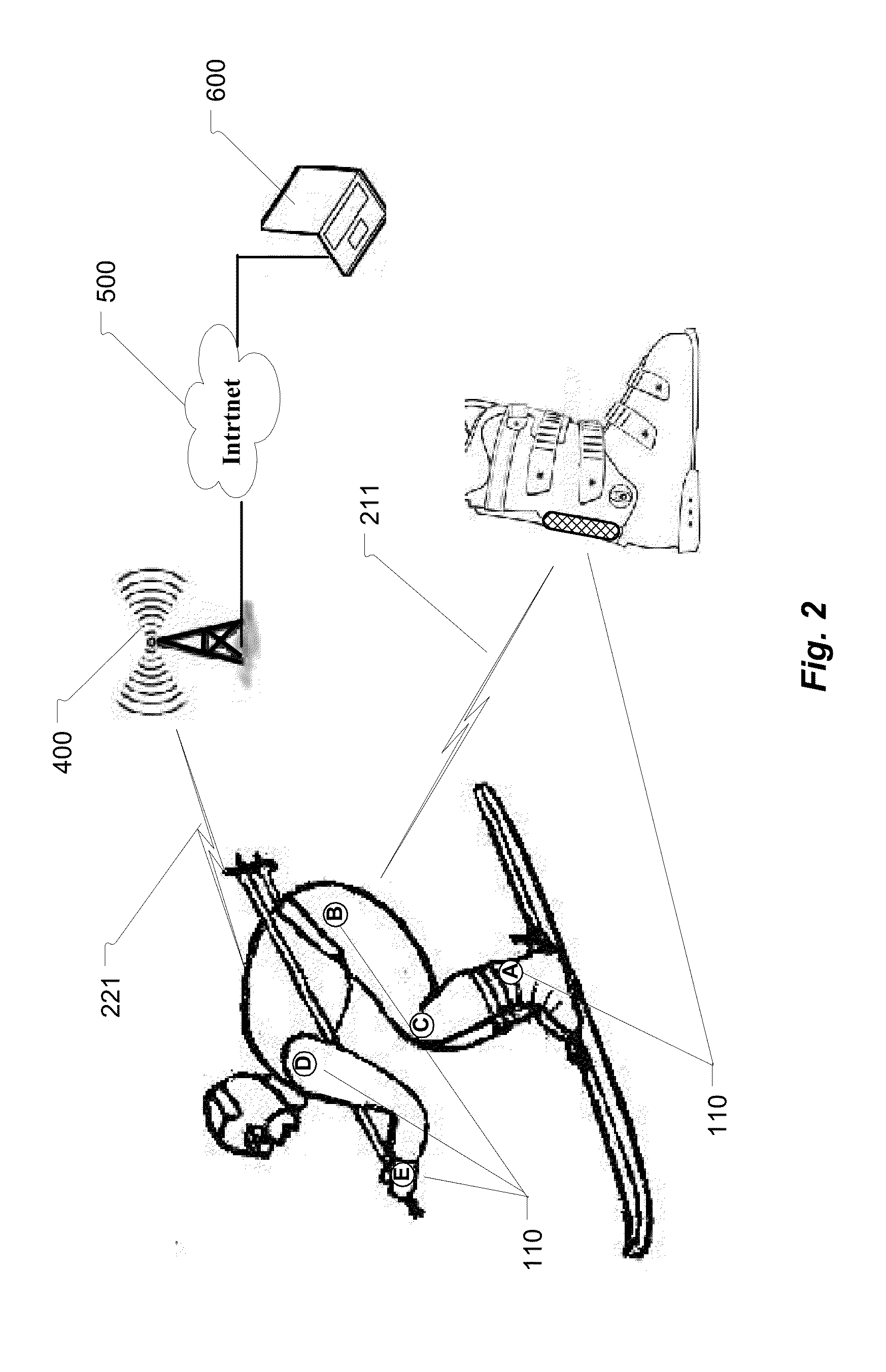

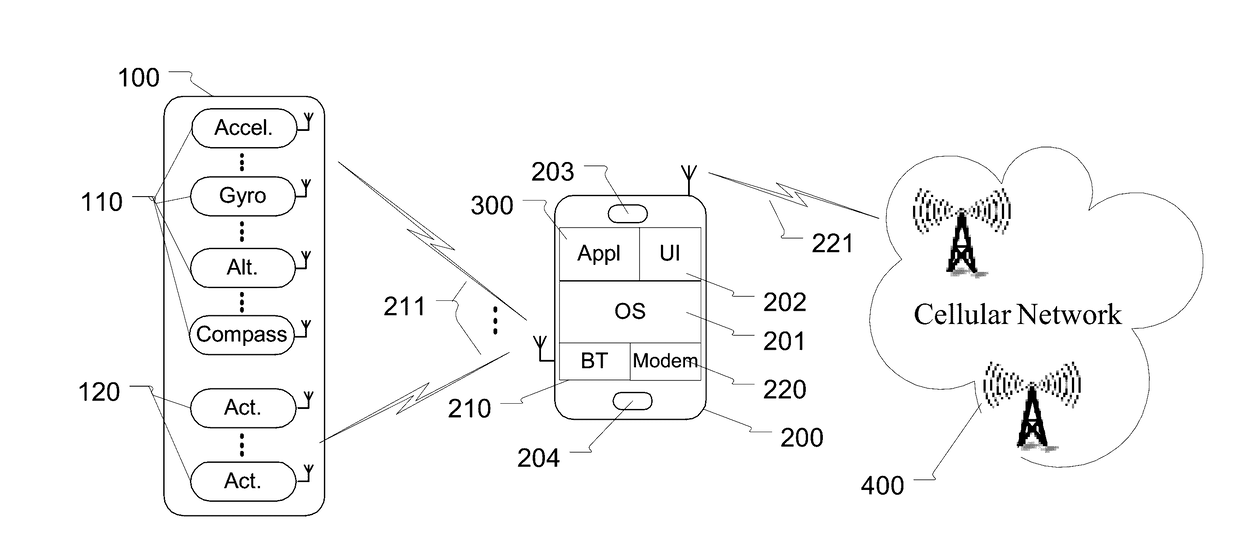

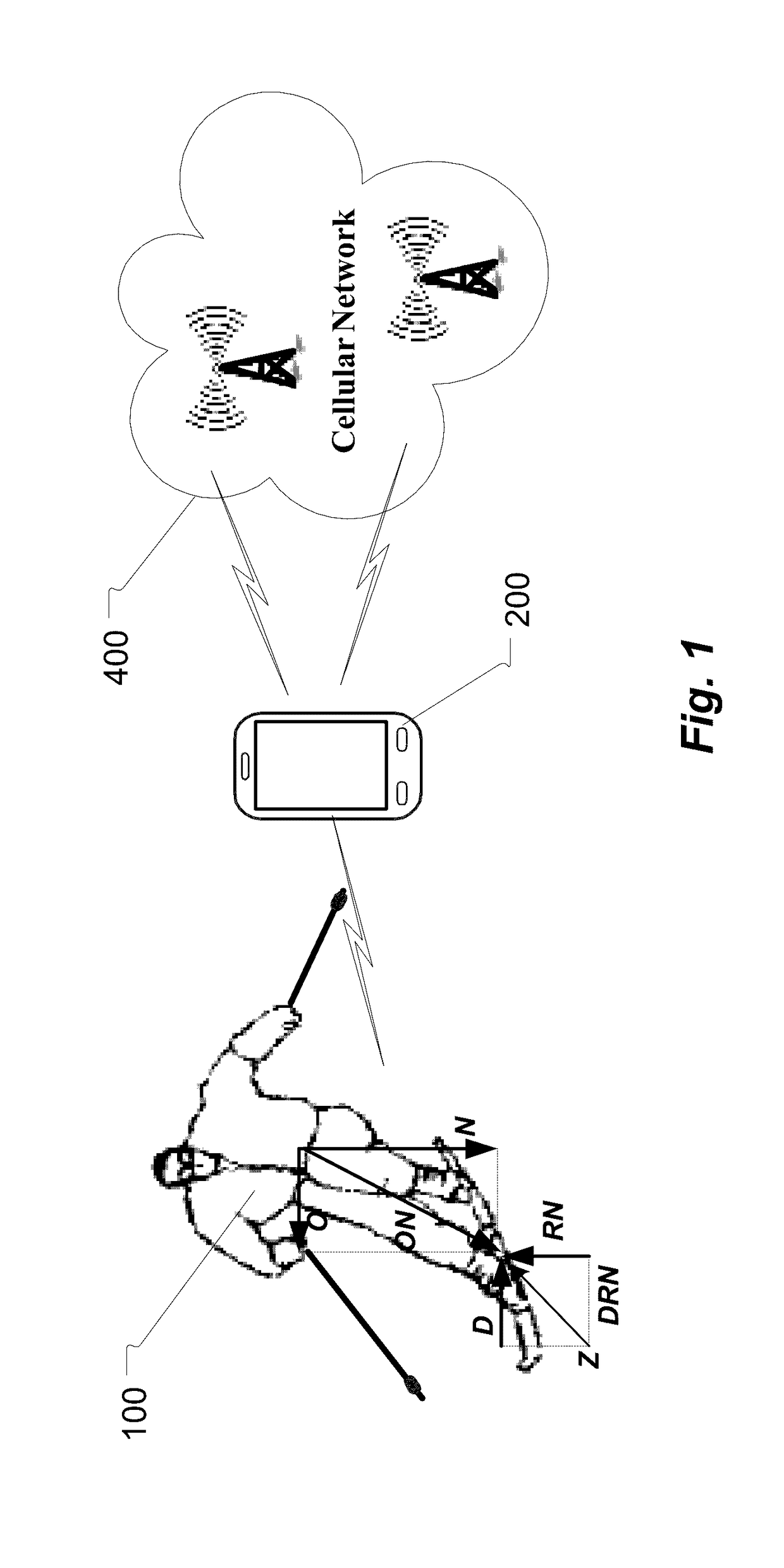

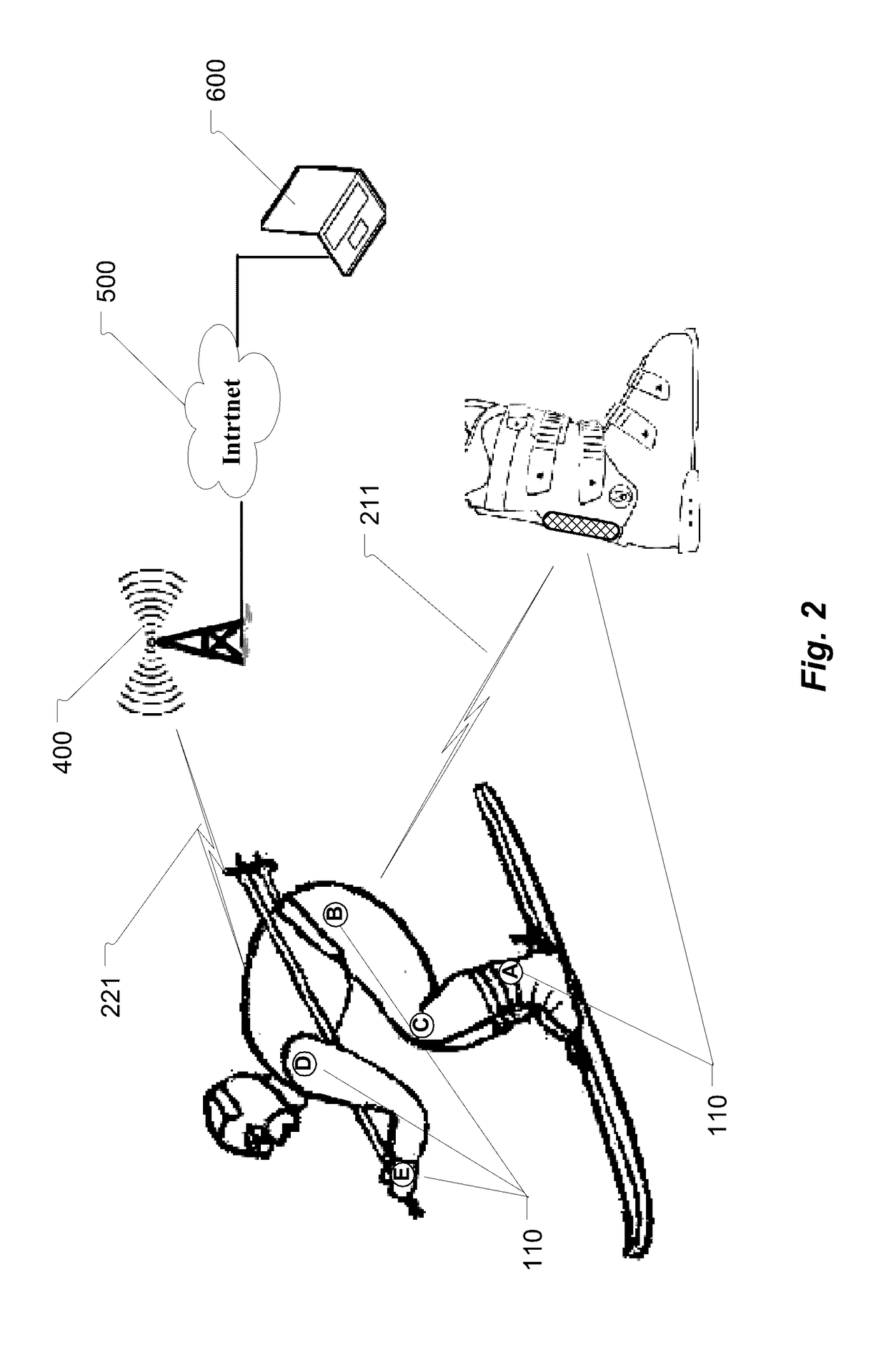

Wireless Hierarchical Heterogeneous Pico-Net for Ski Control Systems

InactiveUS20150249482A1Easy to useLower latencyPhysical therapies and activitiesNear-field transmissionCurrent sensorStructure of Management Information

A wireless hierarchical heterogonous pico-net providing communication between smart-phone based analysis and control application and multiplicity of sensors and actuators embedded in the ski equipment is described. The topology of this pico-net comprises two layers of hierarch, where the first layer is configured as a Bluetooth wireless network using a Round-Robin scheduling method and consisting of a single master and up-to seven slaves, and the second layer of the hierarchy is configured as a sub-nets consisting of multiplicity of sensors and actuators and communicating internally using ANT personal area network (PAN) wireless interface, or via a digital wire interface. Such network topology provides deterministic latency of a hierarchy a single-hop Bluetooth network, irrespective of the numbers of sensors and actuators embedded within each sub-net of the second layer of hierarchy. The network latency is upper-bounded by the number of slaves in the first layer of hierarch, Furthermore, the Round-Robin scheduling method is supplemented with the gating-off the slave RF transmission when the slave has no data to send, or when the difference between current sensor samples and the previous sensor sample is smaller then predefined threshold. Such discontinued transmission lowers slave power consumption system interference.

Owner:IPCOMM

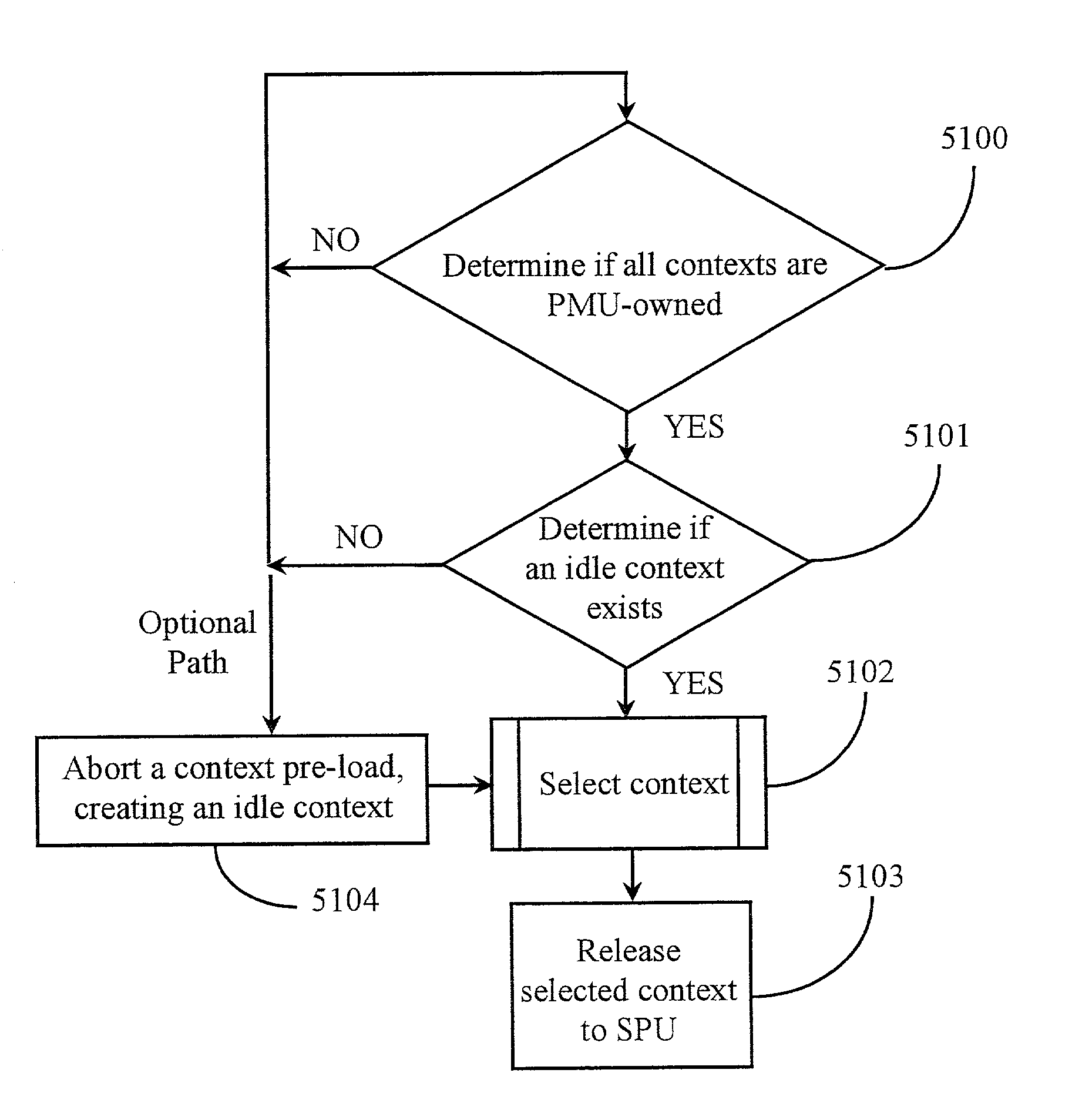

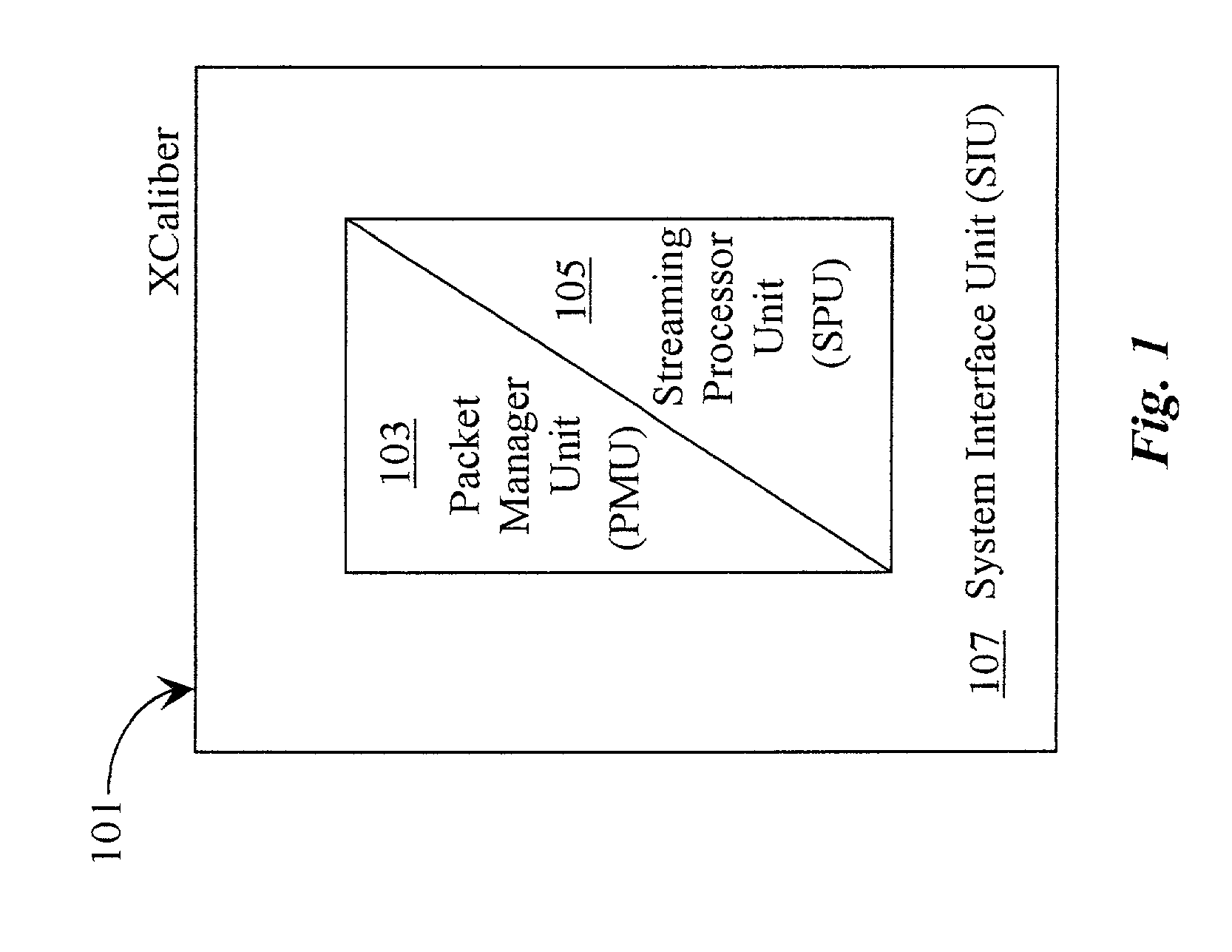

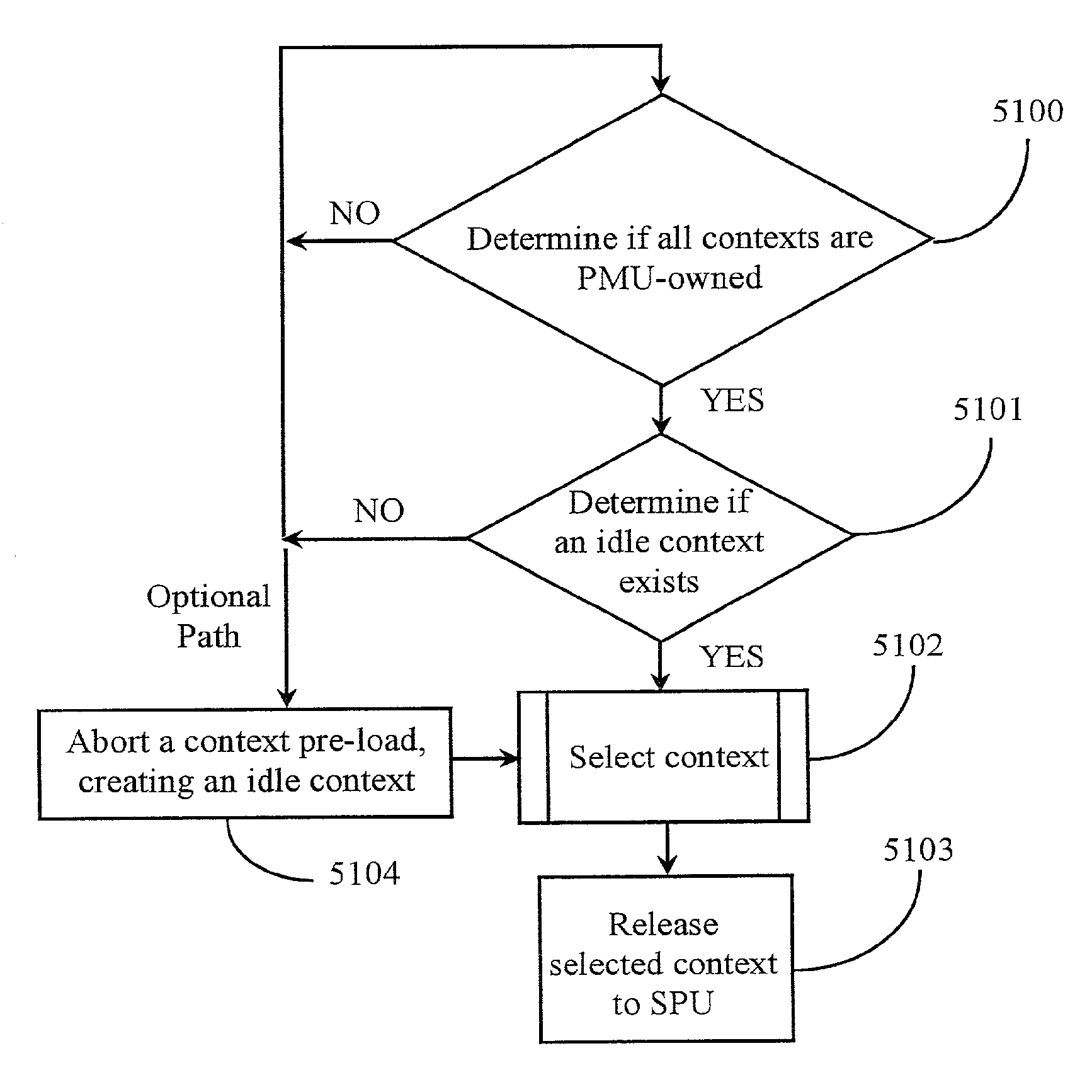

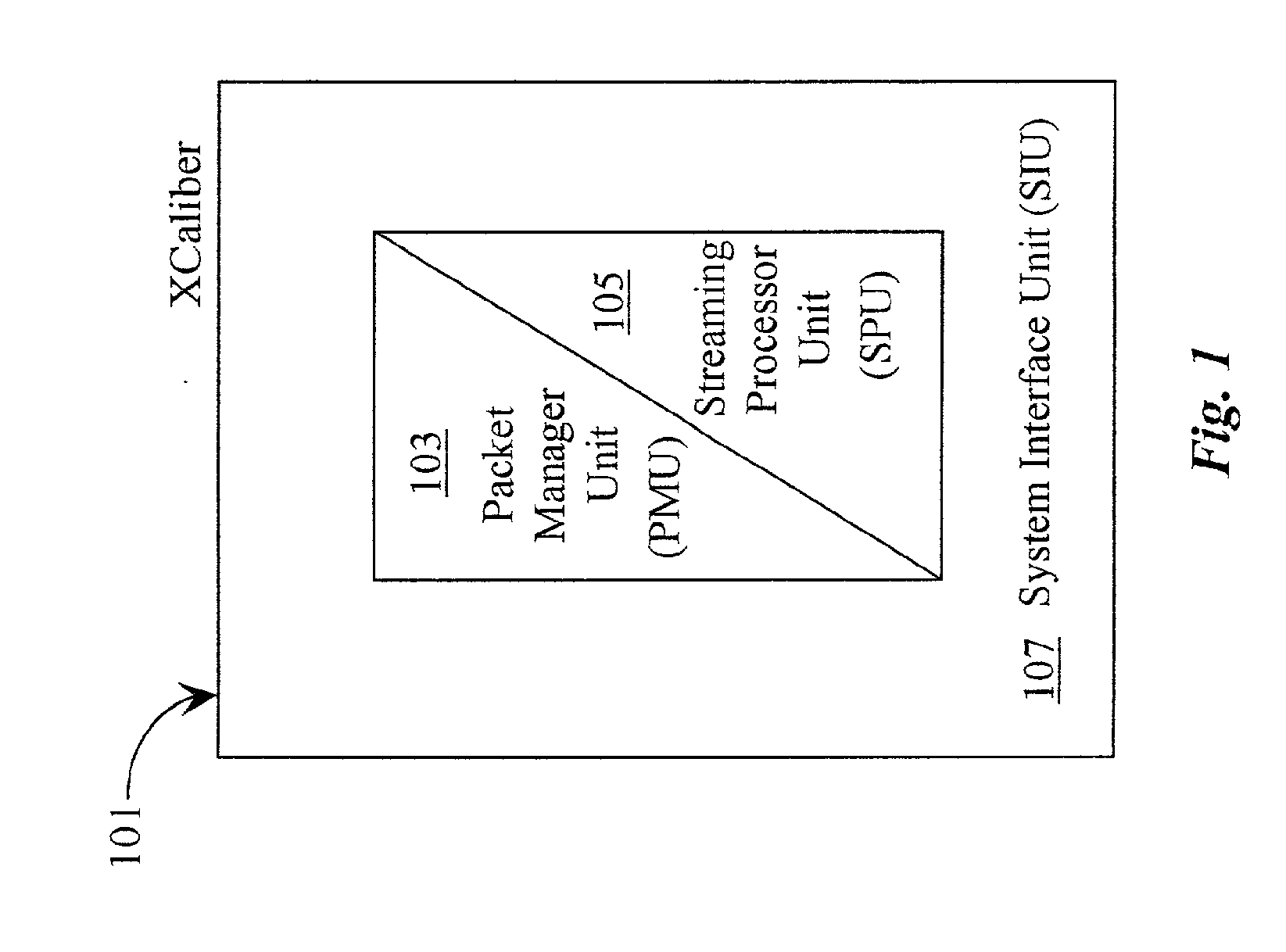

Context selection and activation mechanism for activating one of a group of inactive contexts in a processor core for servicing interrupts

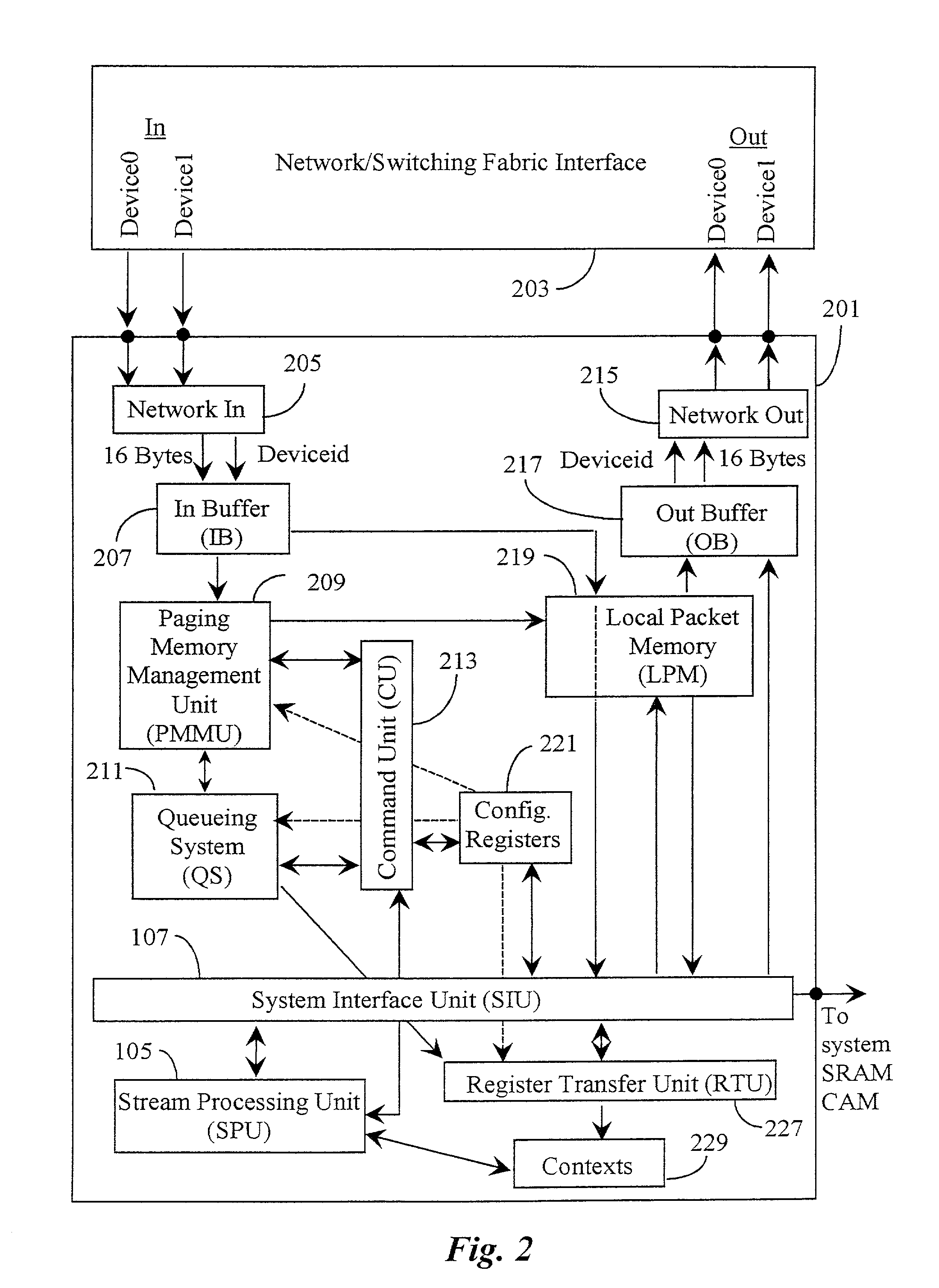

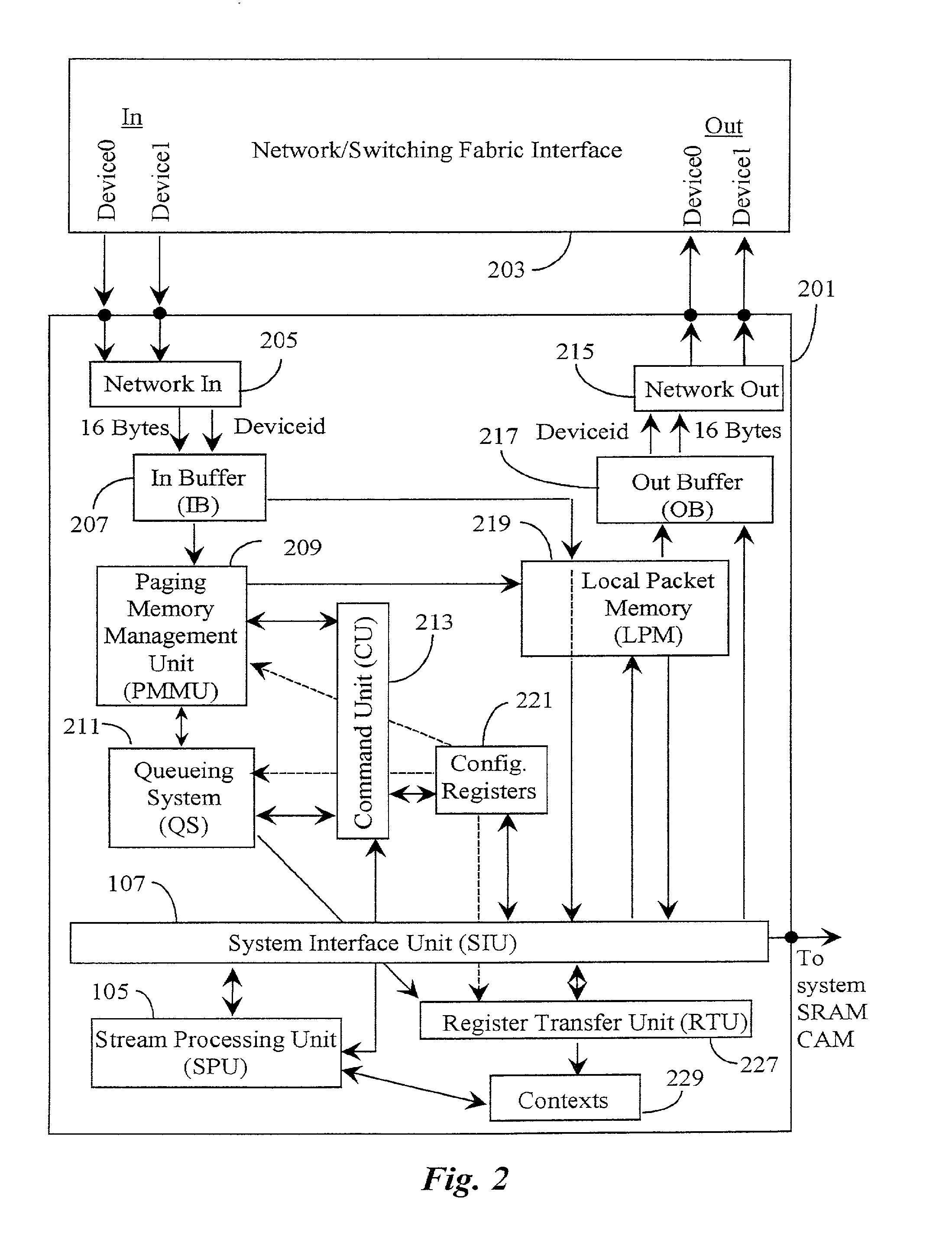

InactiveUS7165257B2Little latencySuppress eventDigital computer detailsData switching networksMultiple contextData pack

A logic system in a data packet processor is provided for selecting and releasing one of a plurality of contexts. The selected and released context is dedicated for enabling the processing of interrupt service routines corresponding to interrupts generated in data packet processing and pending for service. The system comprises, a first determination logic for determining control status of all of the contexts, a second determination logic for determining if a context is idle or not, a selection logic for selecting a context and a context release mechanism for releasing the selected context. Determination by the logic system that all contexts are singularly owned by an entity not responsible for packet processing and that at least one of the contexts is idle, triggers immediate selection and release of an idle one of the at least one idle contexts to an entity responsible for packet processing.

Owner:ARM FINANCE OVERSEAS LTD

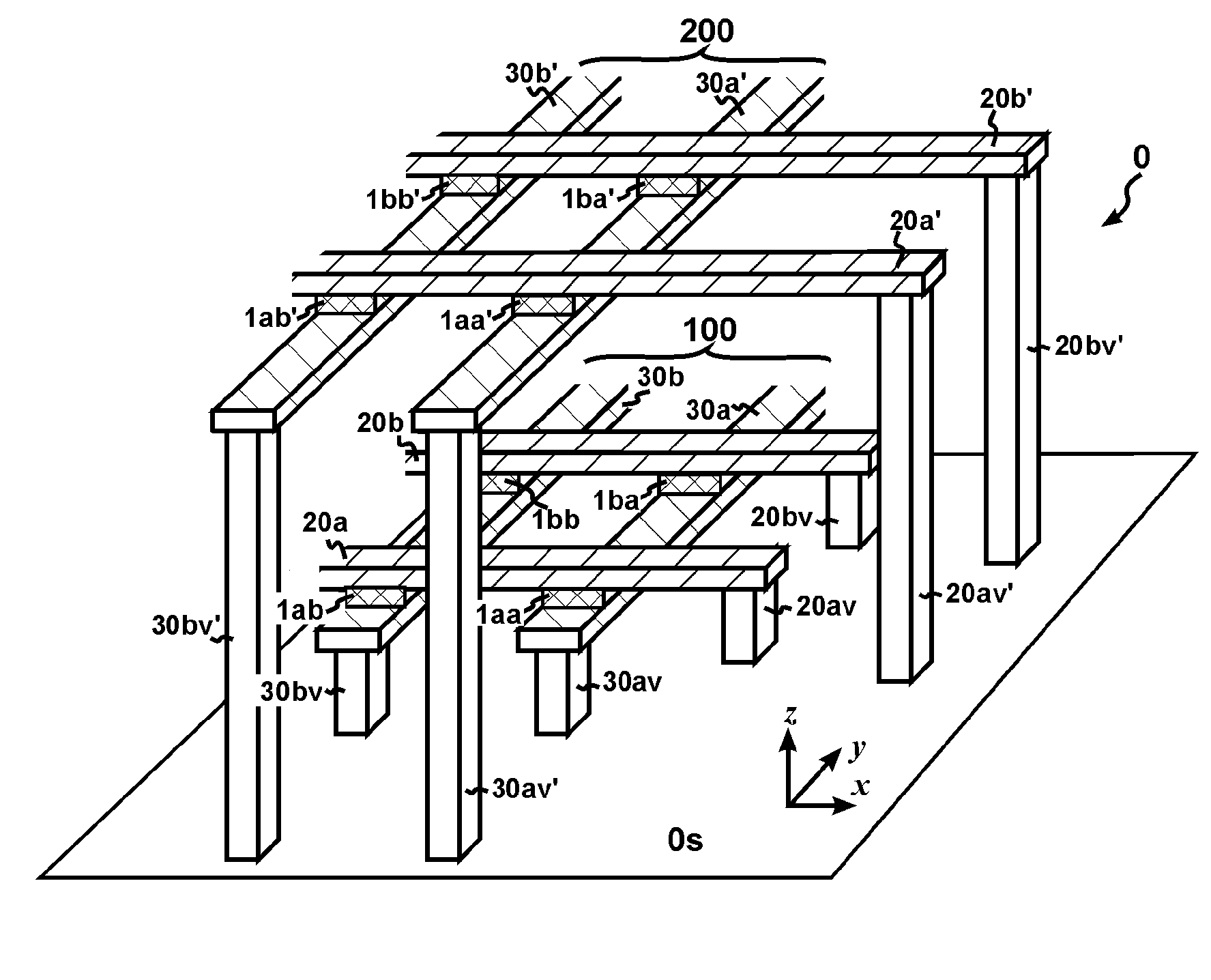

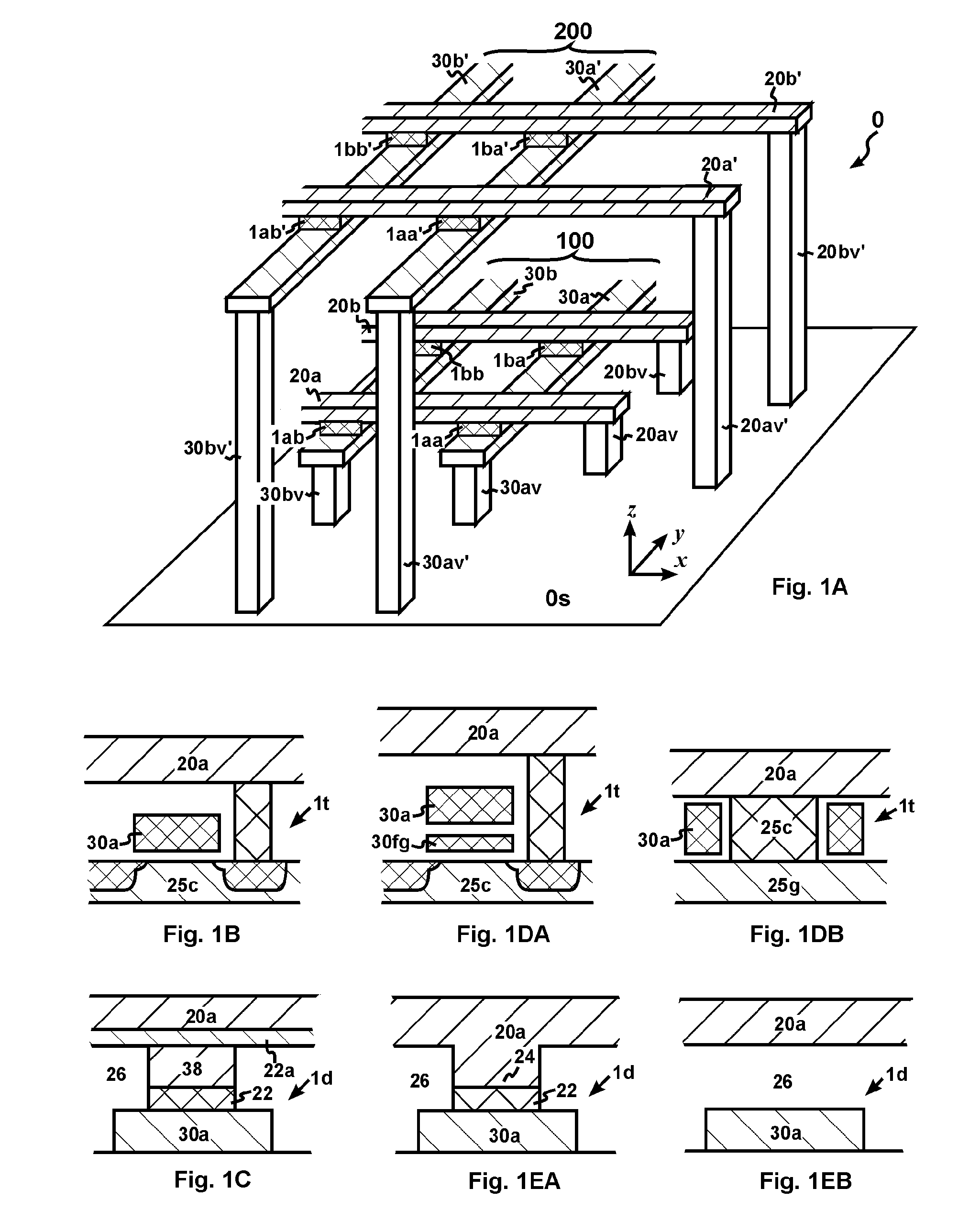

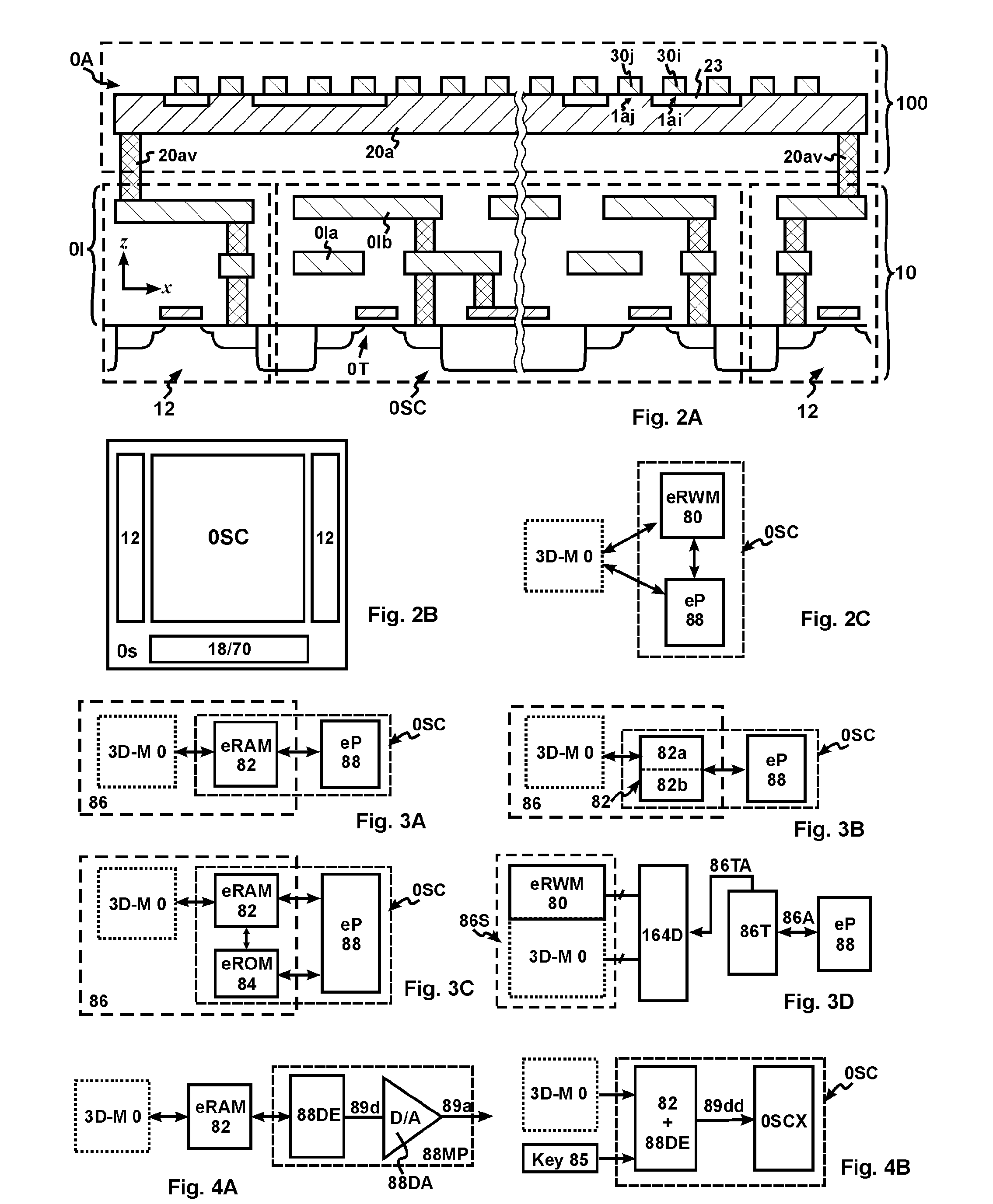

Three-Dimensional Memory Cells

InactiveUS20070170520A1Easy to integrateImprove manufacturing yieldTransistorSolid-state devicesComputer scienceRead-only memory

Owner:ZHANG GUOBIAO

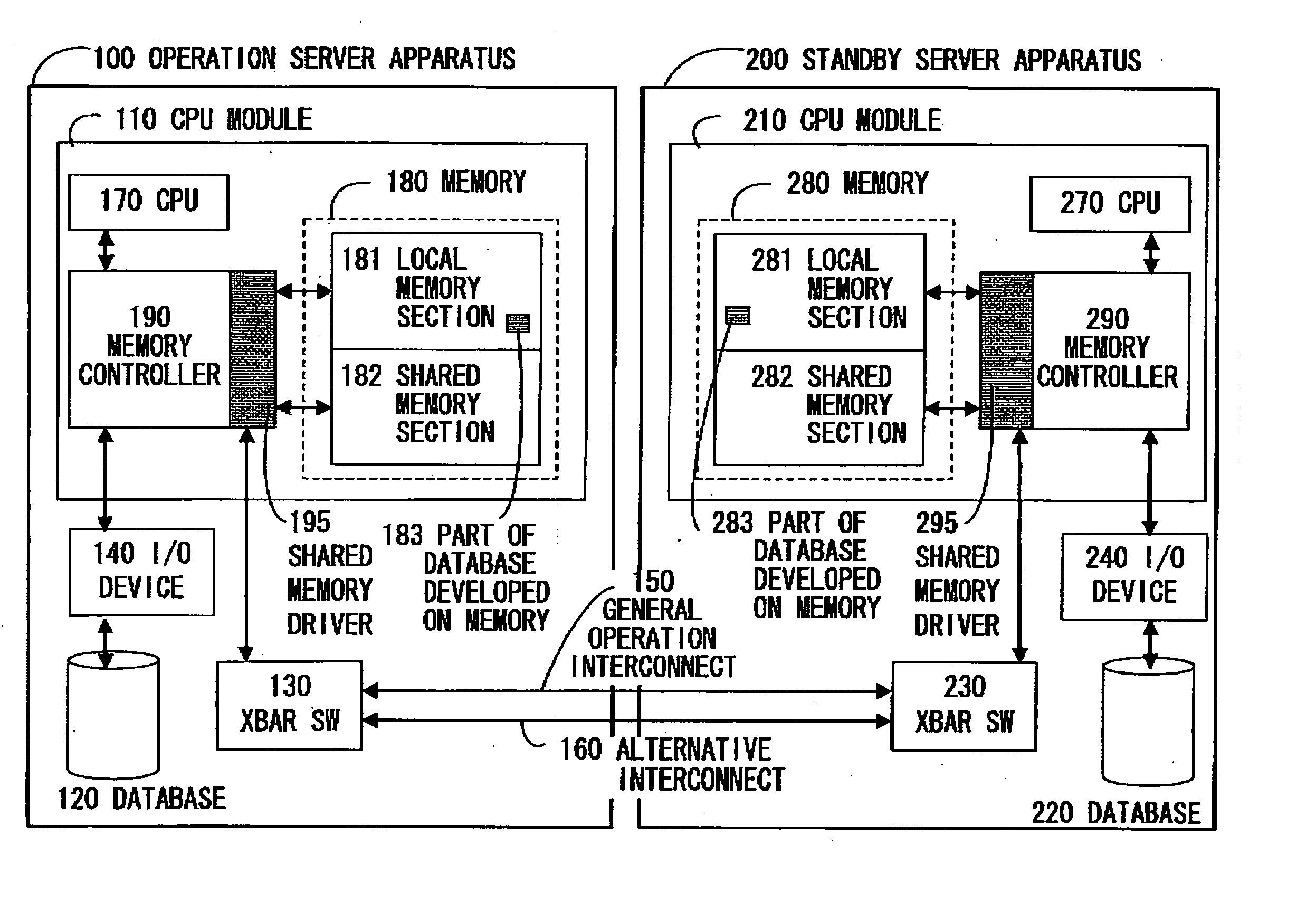

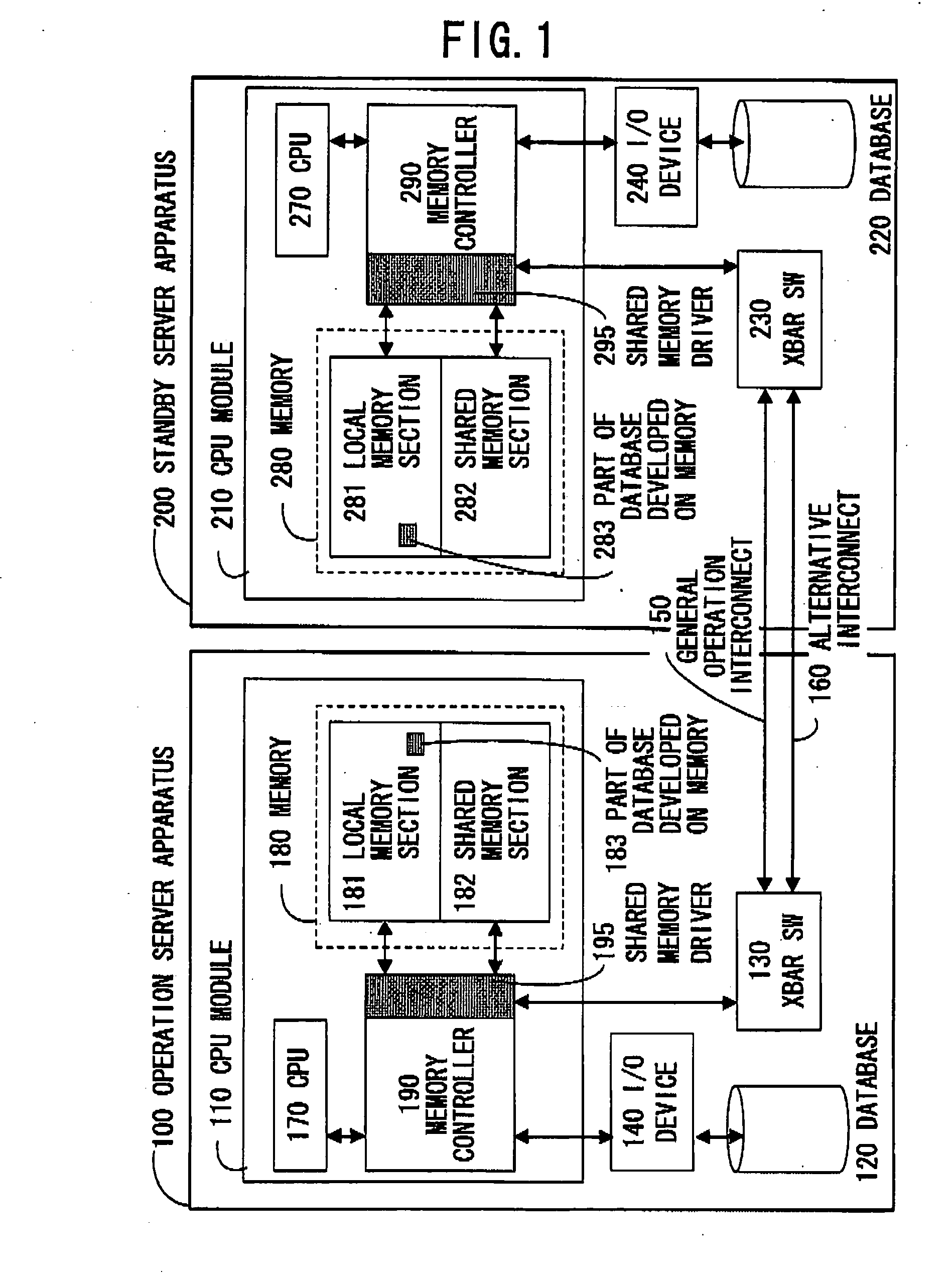

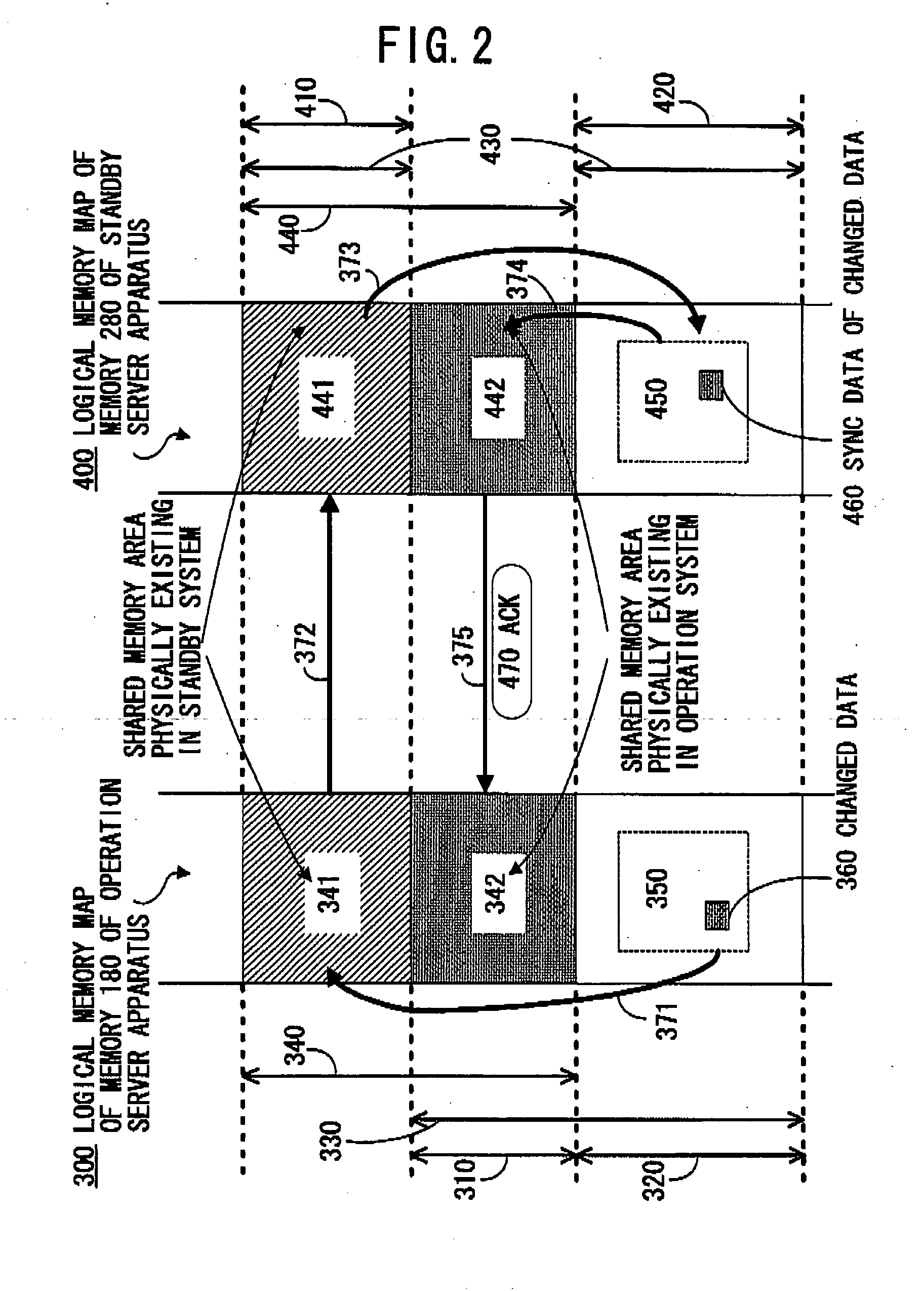

Data mirror cluster system, method and computer program for synchronizing data in data mirror cluster system

InactiveUS20050229022A1Increase speedReduce data volumeMemory adressing/allocation/relocationSpecial data processing applicationsOperational systemCluster systems

Server apparatuses that configure a data mirror cluster system include databases, shared memories, and memory controllers, respectively. The server apparatuses are connected by interconnects and can directly access communication partner's shared memories via the memory controllers, respectively. One of the server apparatuses operates as an operation server apparatus and the other operates as a standby server apparatus. The memory controller of the operation system updates the database and writes changed data to the shared memory of the standby system. The memory controller of the standby system updates the database of the standby system according to the changed data written to the shared memory of the standby system.

Owner:NEC CORP

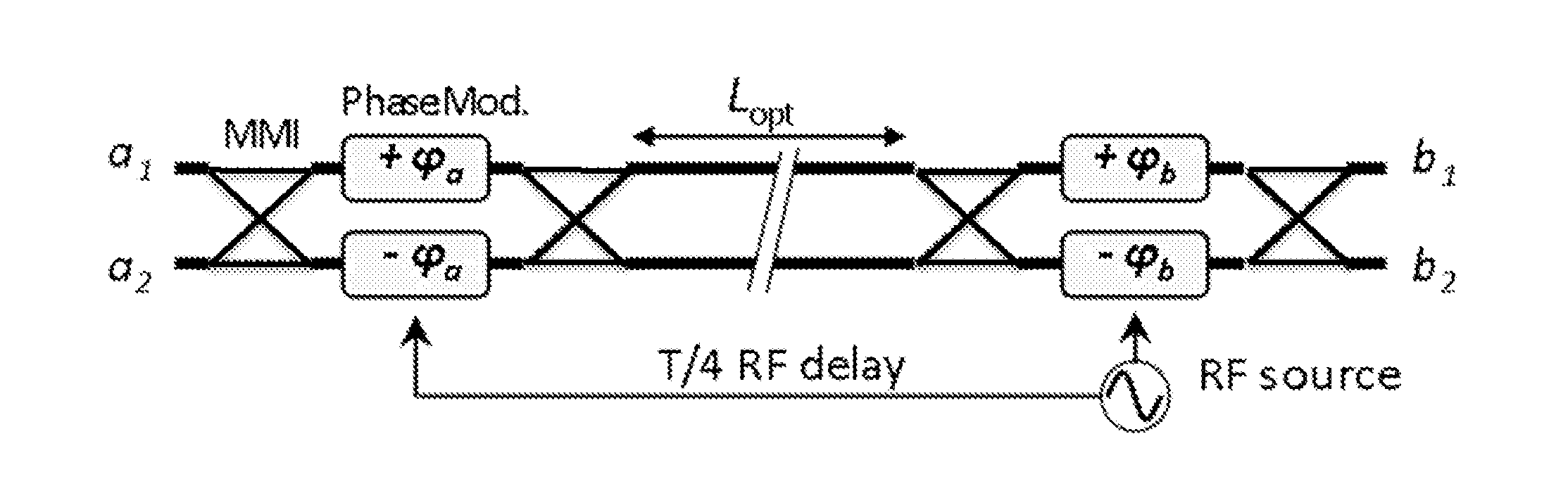

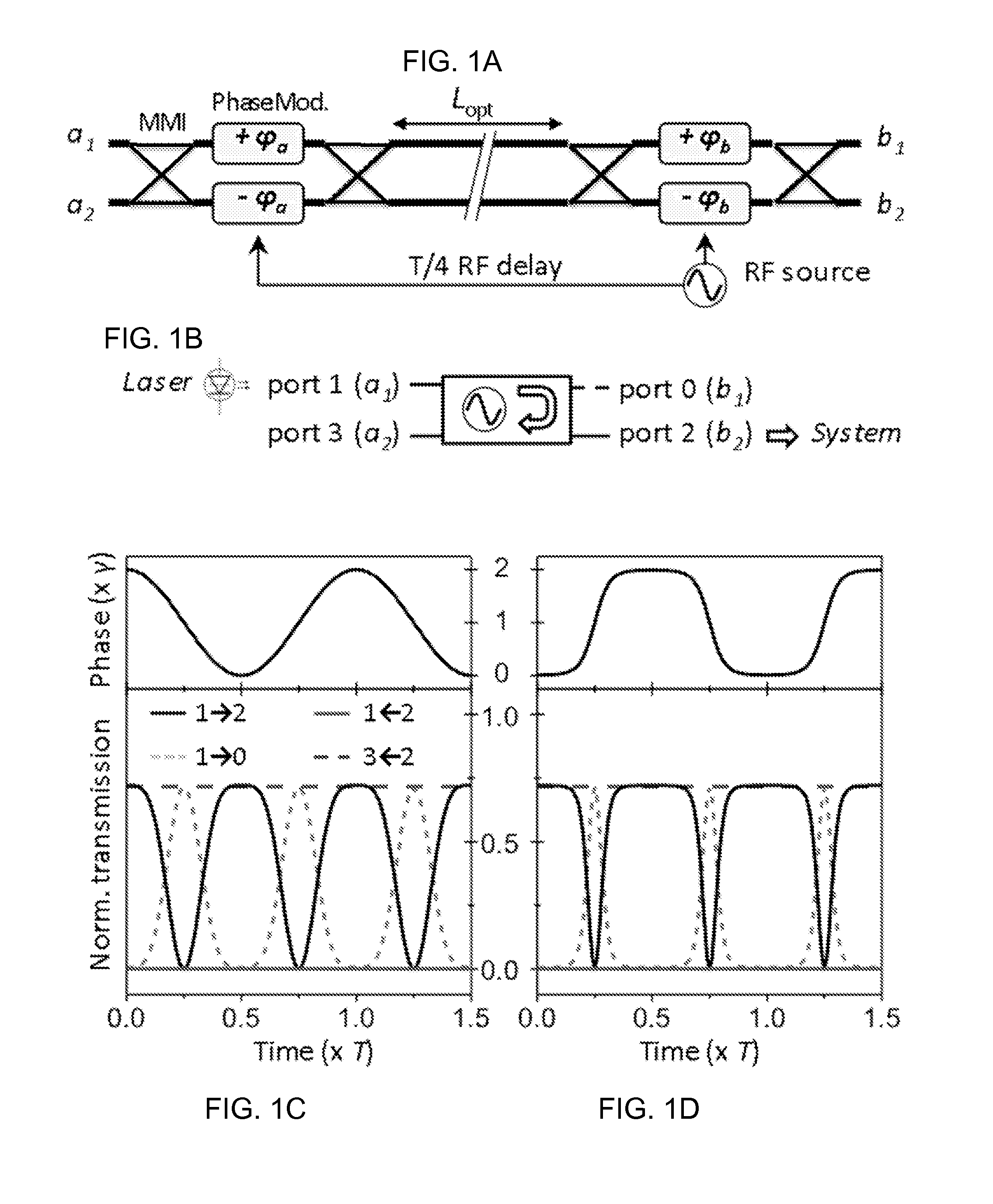

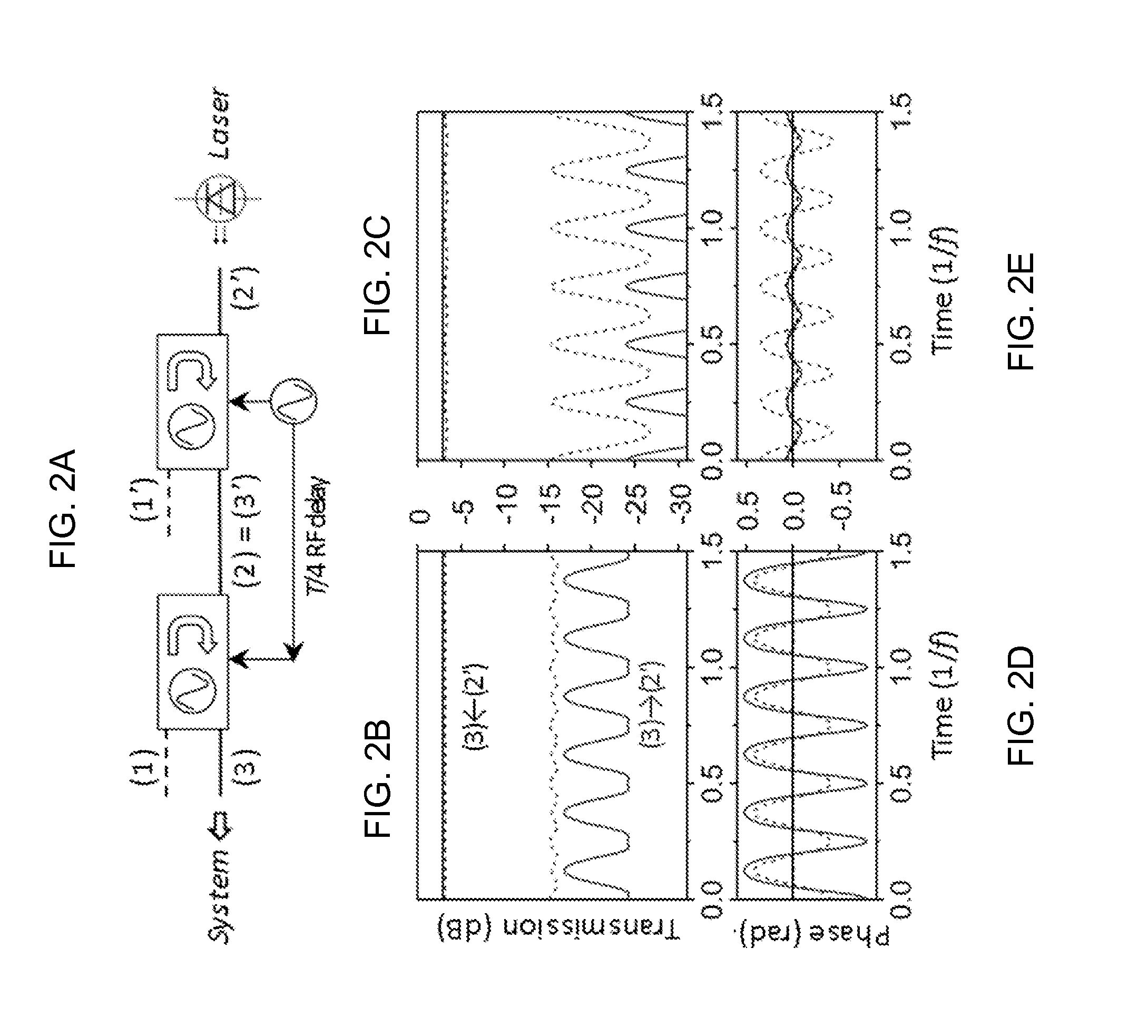

Broadband optical isolator using phase modulators and mach-zehnder interferometers

InactiveUS20140334764A1Increase operating frequencyReduce complexityOptical light guidesNon-linear opticsBeam splitterMach–Zehnder interferometer

Optical devices that do not employ magneto-optics materials or non-linear effects to achieve non-reciprocal light propagation. The optical devices are compatible with the fabrication of monolithic photonic integrated circuits such as silicon-on-insulator planar lightwave circuits. In particular the devices use demonstrated passive (beam-splitters, waveguides) and active (phase modulators) components to achieve non-reciprocal light propagation. The devices can be used as non-reciprocal optical modulators or optical isolators when driven by a periodic radio frequency (RF) electric source.

Owner:NOKIA SOLUTIONS & NETWORKS OY

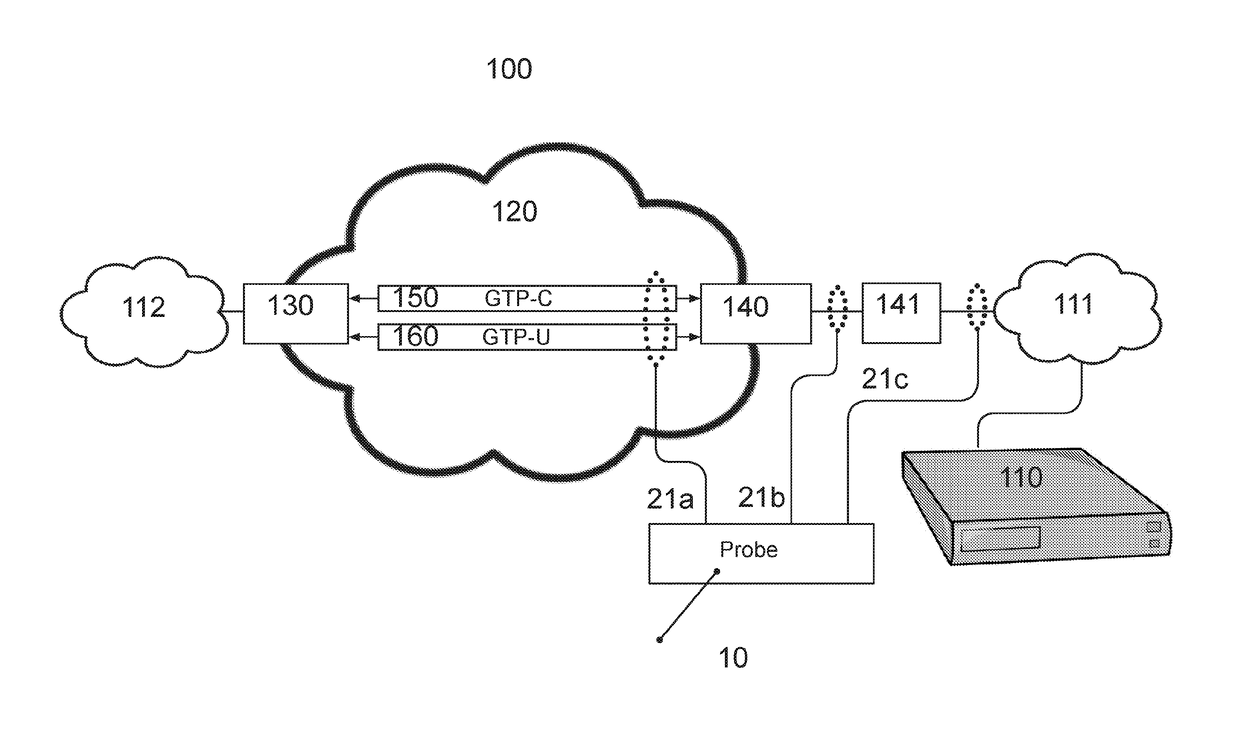

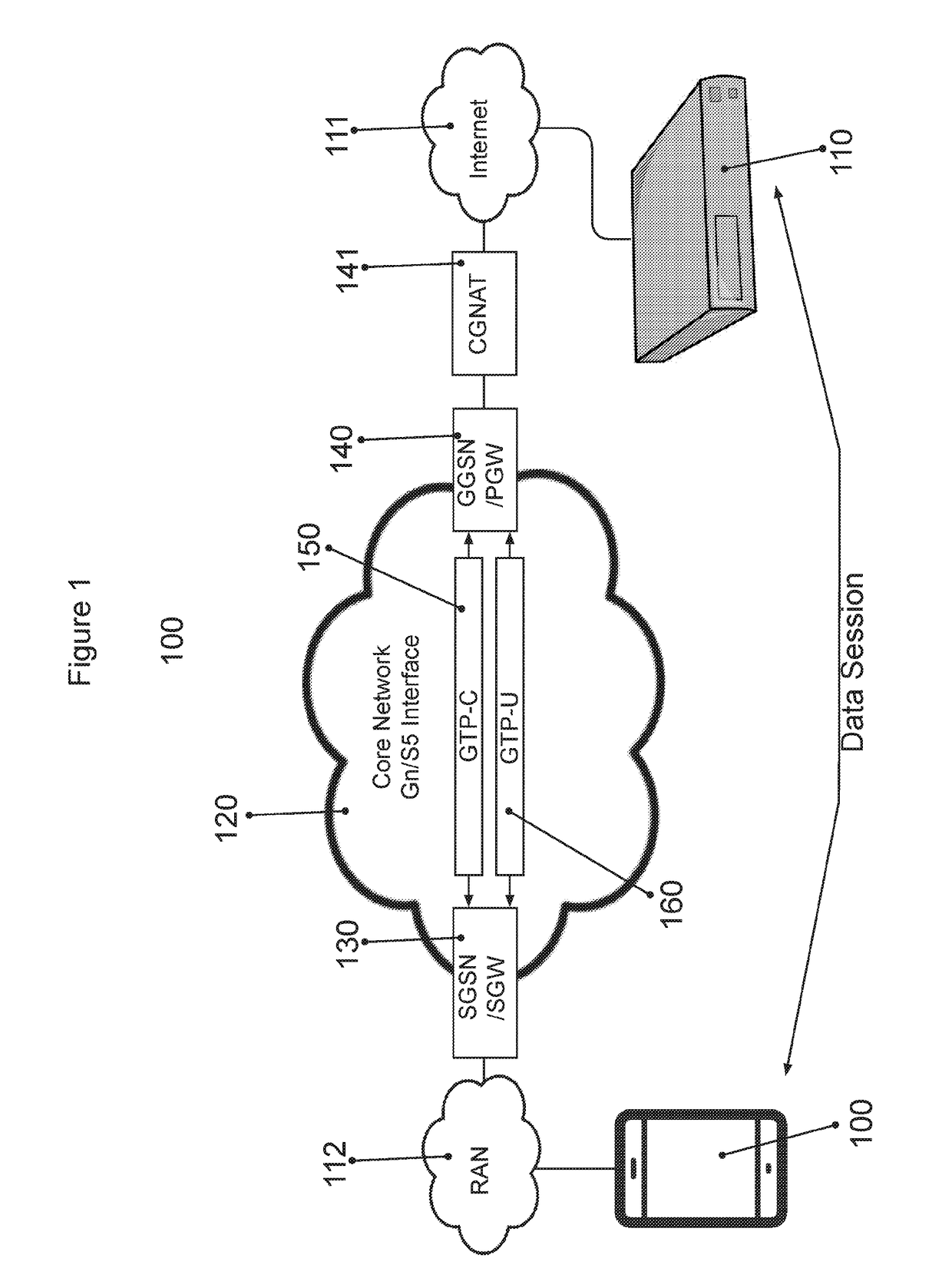

Data Retention Probes and Related Methods

ActiveUS20170373953A1Reduce overheadIncrease speedWeb data retrievalWireless network protocolsTTEthernetTelecommunications network

A data retention probe for a packet-switched, mobile telecommunications network employs interfaces to connect to interfaces carrying traffic on a mobile network side of a gateway node and on a global internet side of the gateway node. A FPGA creates for each packet at least one fingerprint of one or more fields that are unchanged as part of the address translation performed by the gateway node and to create informative metadata for those packets. A processing unit: (1) receives from the FPGA the fingerprints and metadata and maintains flow records for each flow of packets seen on each side of the gateway node; and (2) compares the fingerprints and, where a match is found, determines those packets to be part of the same communication session and creates a record correlating internal IP address or a subscriber identifier to external IP address and port number.

Owner:TELESOFT TECH

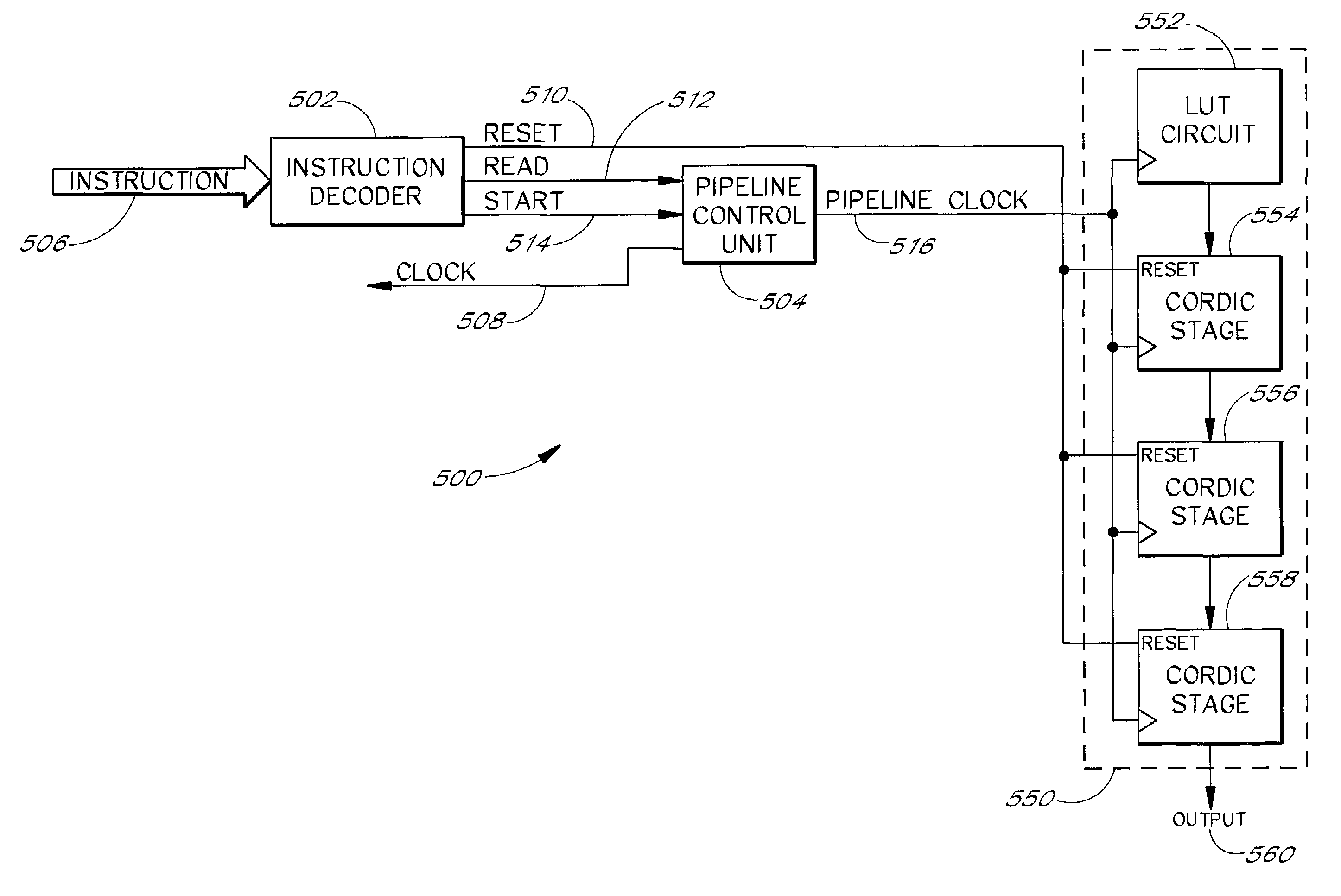

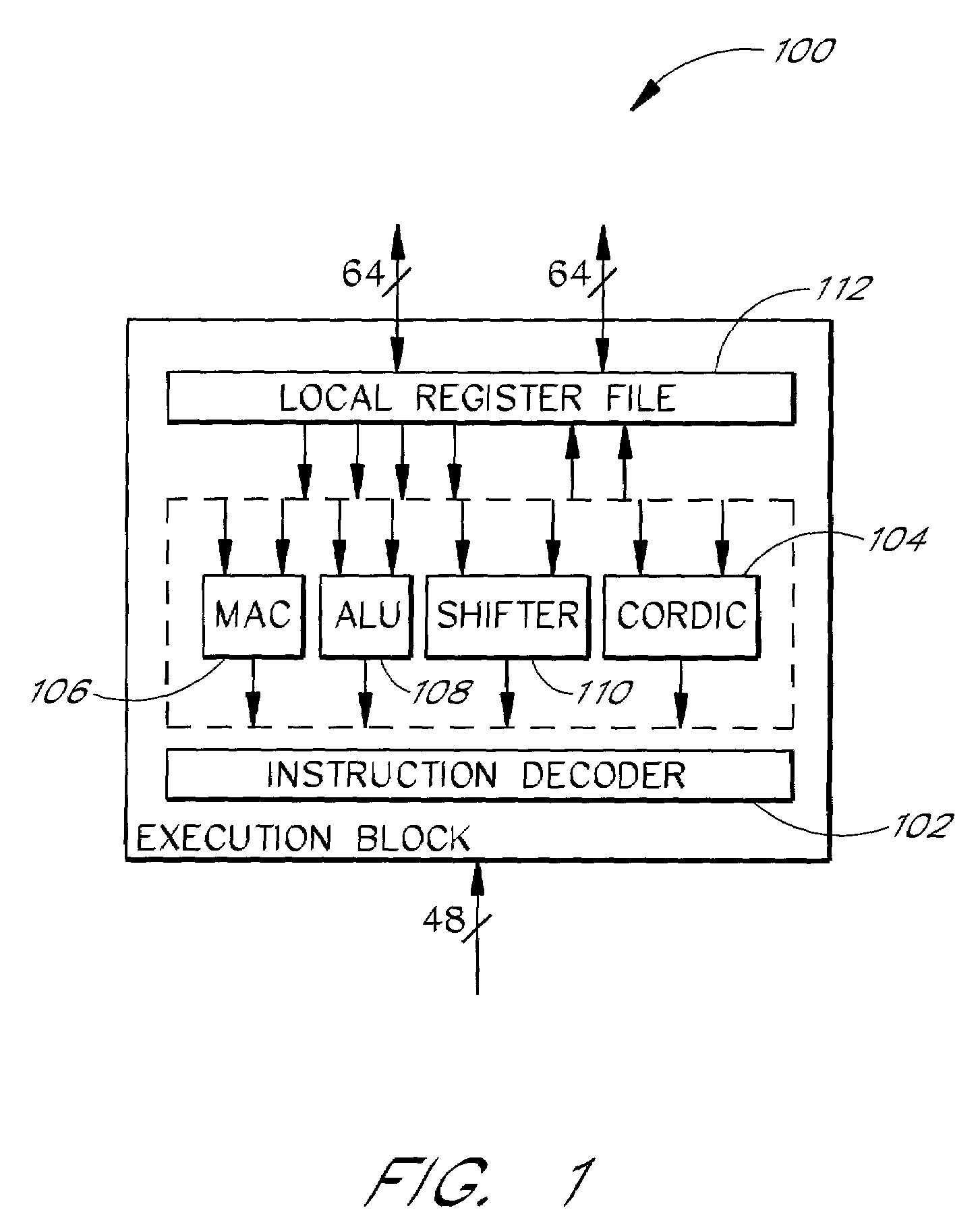

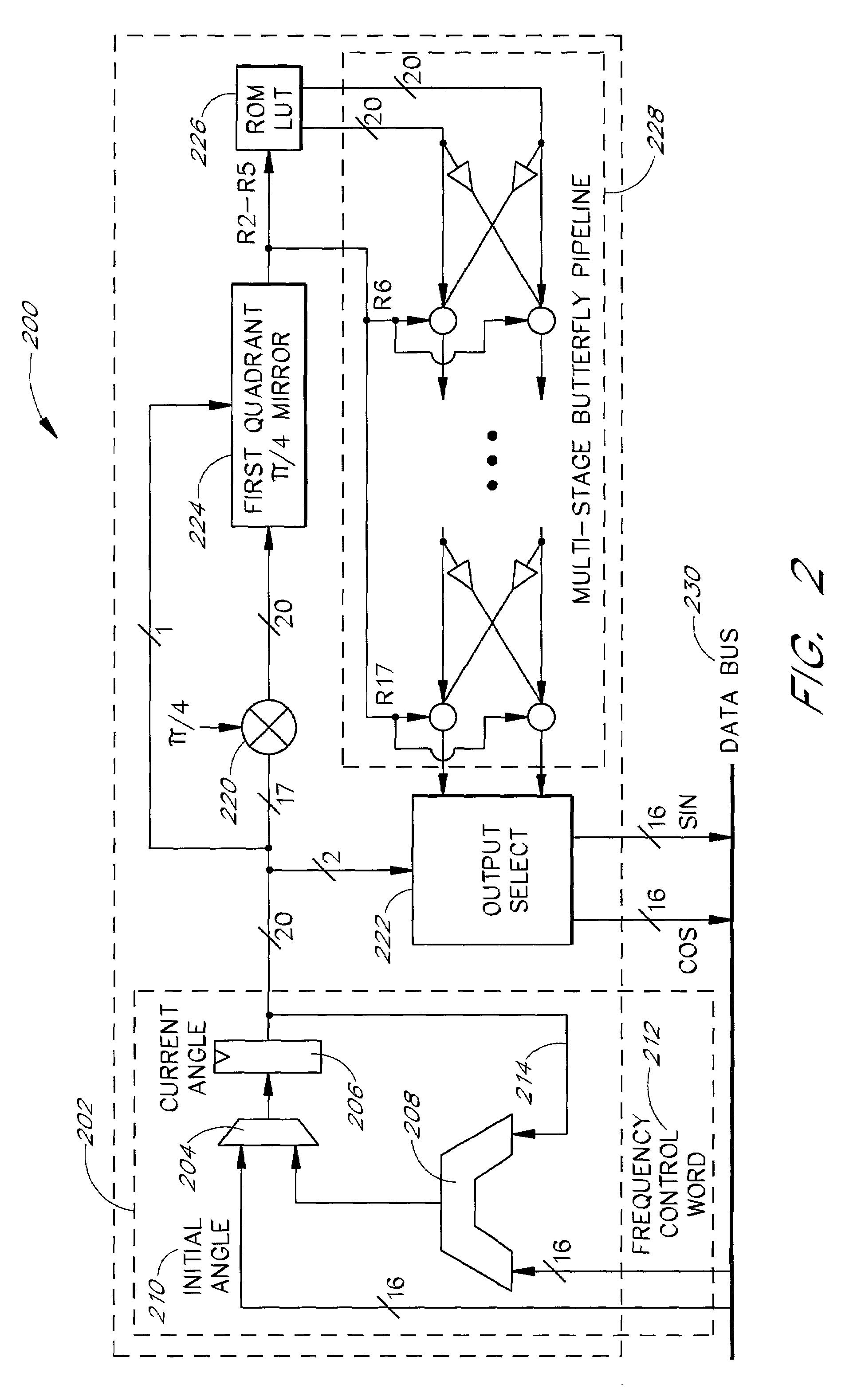

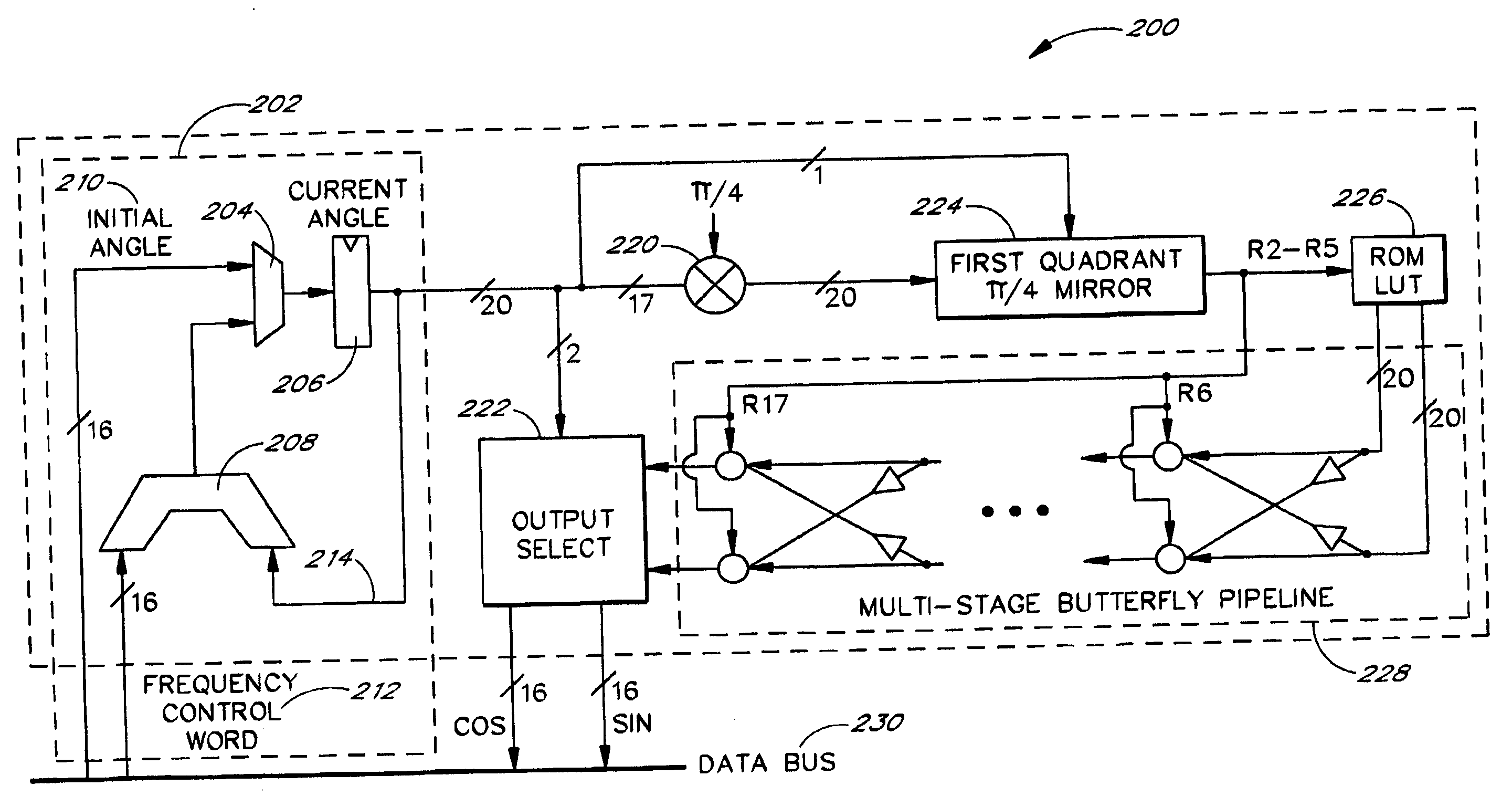

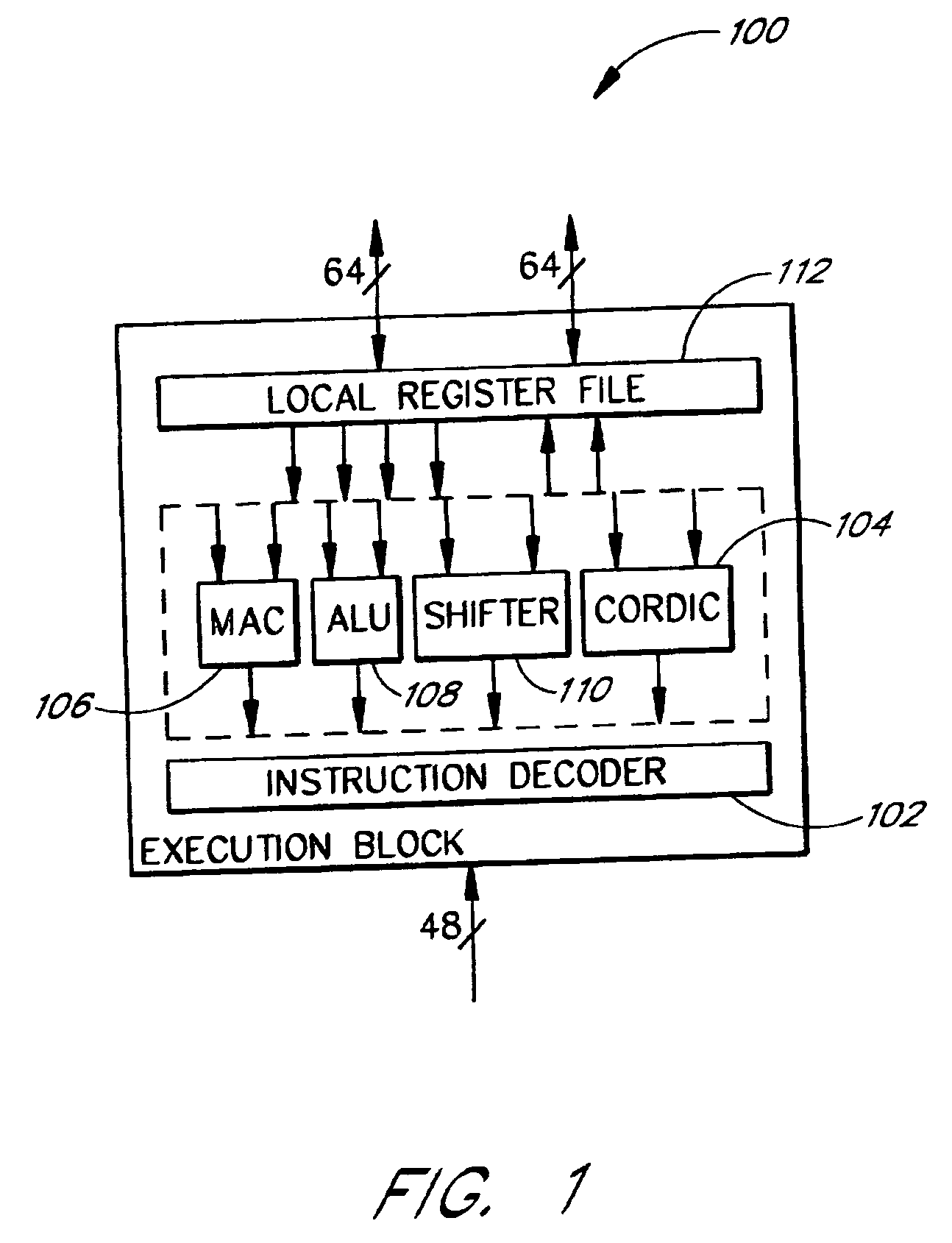

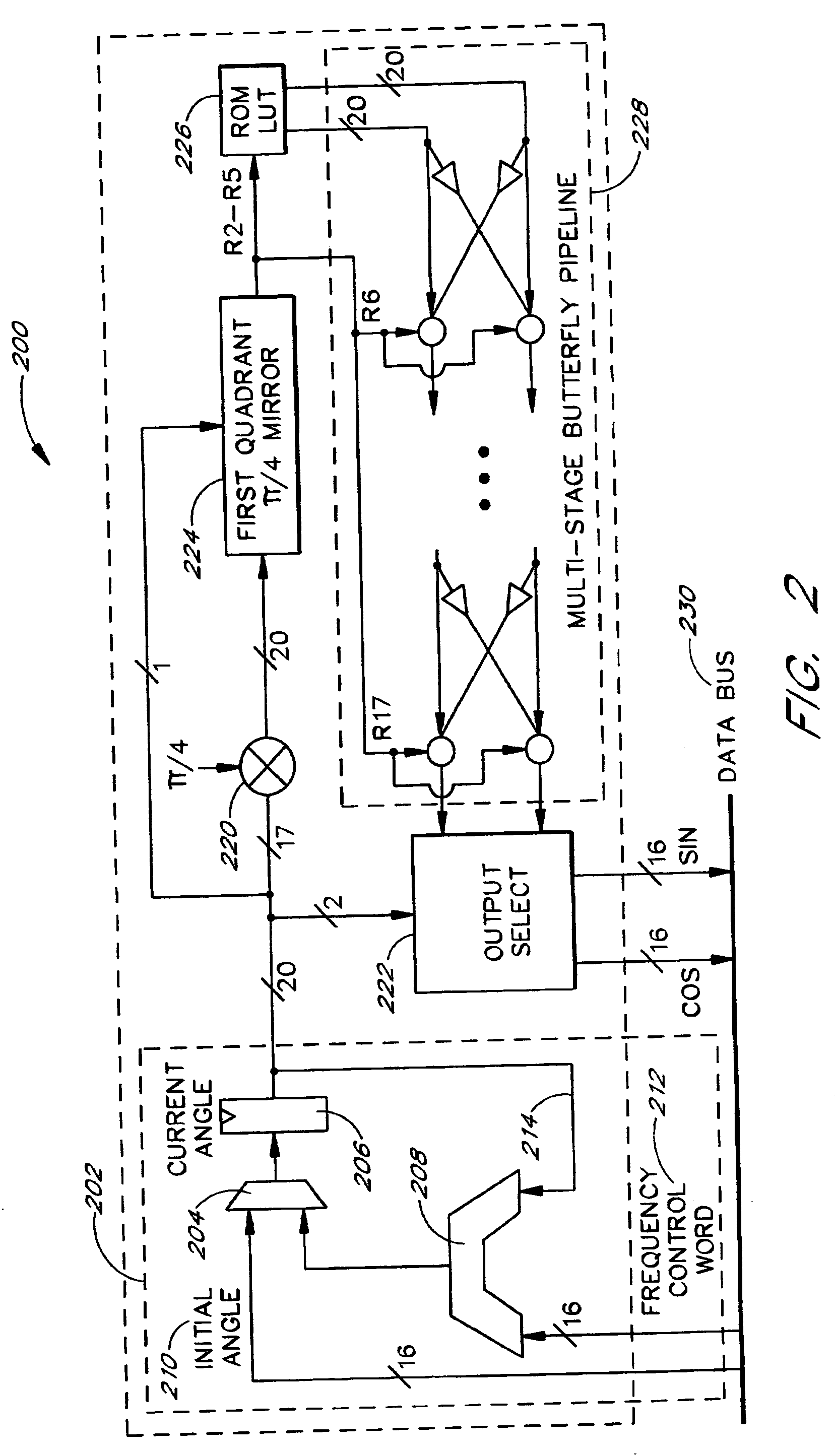

Hardware function generator support in a DSP

InactiveUS7031992B2Quickly and efficiently process CORDIC algorithm in pipelineLittle overheadSpeech analysisConcurrent instruction executionLine tubingParallel computing

The present invention relates to digital signal processors with an integrated module configured to compute a Coordinate Rotation Digital Computer (CORDIC) in a pipeline. The pipelined module can advantageously complete computation of one CORDIC computation for each clock pulse applied to the CORDIC module, thereby providing a CORDIC computation for each clock pulse. One embodiment advantageously computes a first portion of a computation with a lookup table and a second portion in accordance with a CORDIC algorithm. Advantageously, data in a CORDIC pipeline is automatically advanced in response to read instructions and can be automatically advanced from the beginning of the pipeline to the end of the pipeline to reinitialize the pipeline. This allows information to be retrieved from the CORDIC pipeline with relatively little overhead. The automatic starting and stopping of the CORDIC pipeline advantageously allows the retrieval of computations from efficient pipeline architectures on an as-needed basis.

Owner:QUARTICS

Synchronising between clock domains

ActiveUS8301932B2Lower latencyLittle latencyGenerating/distributing signalsTransmission path multiple useProcessor registerClock rate

An integrated circuit 2 is provided with multiple clock domains separated by a clock boundary 8. Data values are passed across the clock boundary 8 using a first-in-first-out memory (FIFO), a read pointer and a write pointer for the FIFO are passed across the clock boundary 8 and must be synchronized to the receiving clock frequency. The clocks being used on either side of the clock boundary 8 may be switched and have a variable relationship therebetween. Multiple synchronization paths are provided within pointer synchronizing circuitry 32 which are used depending upon the particular relationship between the clocks on either side of the clock boundary 8. A pre-switch pointer value is held in a transition register 44 until a post-switch pointer value is available from the new synchronizing path 36 when a switch in clock mode is made which requires an increase in synchronization delay.

Owner:ARM LTD

Method and apparatus for a fault tolerant software transparent and high data integrity extension to a backplane bus or interconnect

InactiveUS6212161B1Increase speedLittle latencyError preventionFrequency-division multiplex detailsData integrityProcessor register

The disclosure relates to apparatus and methods that provide a system interconnect for transporting cells between nodes on a dual counter-rotating ring network, including a link selection register for selecting the shortest path to a destination node, use of a fault tolerant frequency reference to synchronize node clocks, interconnect initialization, multi-ring topologies along with an addressing schema and ring-to-ring couplers. The disclosure also discusses flow control of cells leaving nodes, coupling cells from one ring to another, and use of such an interconnect as a bus replacement.

Owner:PLX TECHNOLOGY

Context selection and activation mechanism for activating one of a group of inactive contexts in a processor core for servicing interrupts

InactiveUS20070256079A1Little latencySuppress eventDigital computer detailsData switching networksBiological activationPacket processing

A logic system in a data packet processor is provided for selecting and releasing one of a plurality of contexts. The selected and released context is dedicated for enabling the processing of interrupt service routines corresponding to interrupts generated in data packet processing and pending for service. The system comprises, a first determination logic for determining control status of all of the contexts, a second determination logic for determining if a context is idle or not, a selection logic for selecting a context and a context release mechanism for releasing the selected context. Determination by the logic system that all contexts are singularly owned by an entity not responsible for packet processing and that at least one of the contexts is idle, triggers immediate selection and release of an idle one of the at least one idle contexts to an entity responsible for packet processing.

Owner:ARM FINANCE OVERSEAS LTD

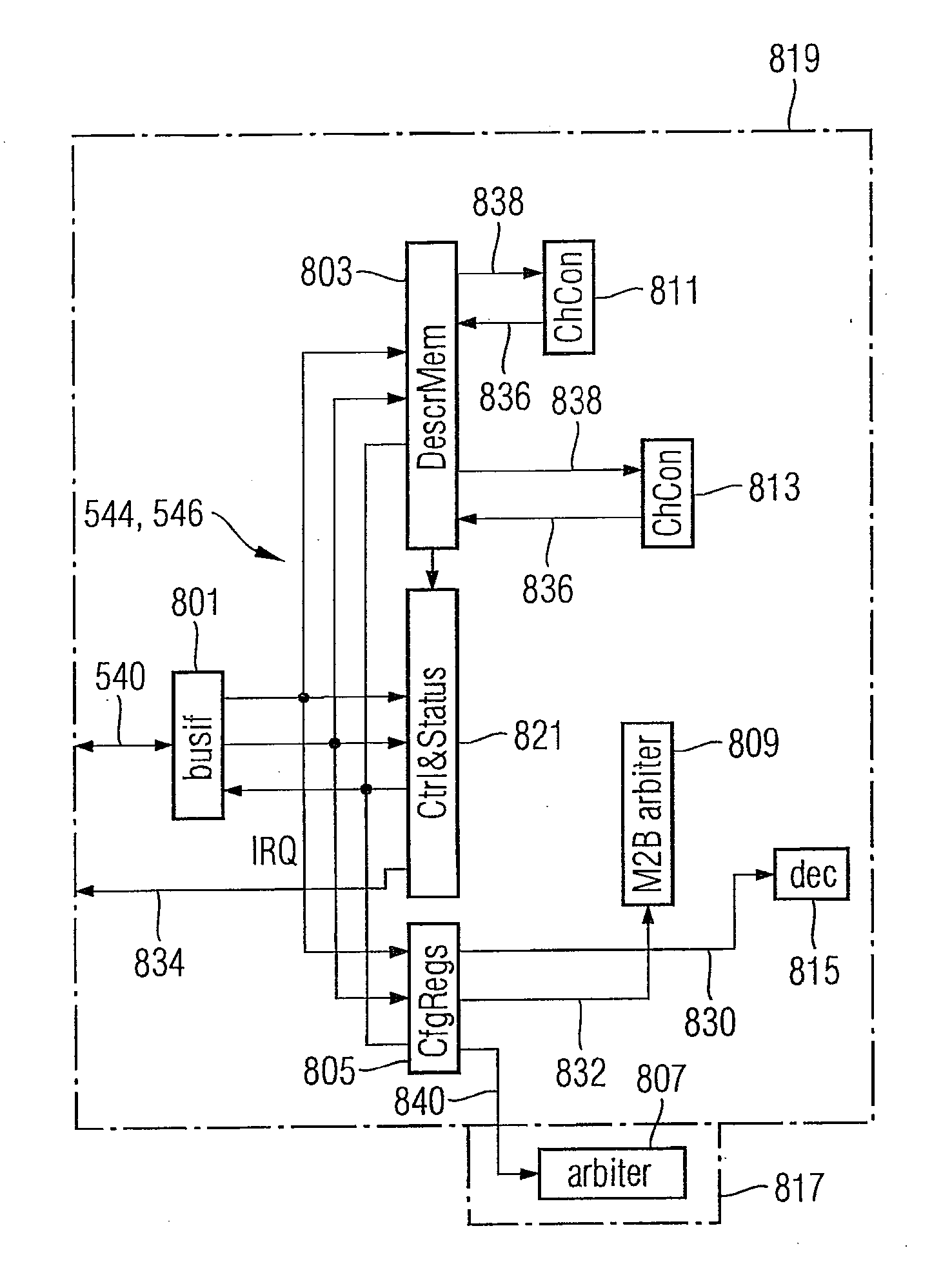

Memory and Memory Communication System

ActiveUS20070283077A1Little latencyImprove throughputDigital storageMemory systemsCommunications systemParallel computing

A memory system includes a selection element for selecting a selectable access rate from a plurality of access rates and a memory element for providing or for accepting data at the selectable access rate.

Owner:MAXLINEAR INC

Skew discovery and compensation for WDM fiber communications systems using 8b10b encording

InactiveUS20020131105A1Eliminate needLittle latencyChannel dividing arrangementsWavelength-division multiplex systemsFiberData stream

This invention uses fiber characteristics combined with knowledge of the 8b10b code to discover and compensate for skew between parallel data streams, caused by chromatic dispersion, in a WDM system allowing the receiver to recover both the data and timing of the data streams as they were originally launched. This skew discovery and compensation does not require the insertion or deletion of any control symbols to / from the original 8b10b streams, and does not require the use of a training or sample sequence.

Owner:OMRON MANAGEMENT CENT OF AMERICA

Inter vehicular ad hoc routing protocol and communication system

InactiveUS7546182B2High penetration distance within an event lifetimeLittle latencyRegistering/indicating working of vehiclesRoad vehicles traffic controlCommunications systemInter vehicle communication

A routing protocol and inter-vehicle communication system adapted for use with a traveling host vehicle, and at least one traveling remote vehicle, includes a locator sub-system configured to determine a plurality of current position coordinates for the host and remote vehicles. The preferred system is configured to store trail coordinates, derive vehicular headings and trail polygons from the trail coordinates, and effect the directional multi-hop propagation of a message by comparing current position coordinates, trail coordinates, headings and / or trail polygons of the host and remote vehicles.

Owner:GM GLOBAL TECH OPERATIONS LLC

Wireless hierarchical heterogeneous pico-net for ski control systems

InactiveUS9673864B2Easy to useLower latencyPhysical therapies and activitiesEnergy efficient ICTCurrent sensorWireless data

A wireless hierarchical heterogonous pico-net providing communication between smart-phone based analysis and control application and multiplicity of sensors and actuators embedded in the ski equipment is described. The topology of this pico-net comprises two layers of hierarch, where the first layer is configured as a Bluetooth wireless network using a Round-Robin scheduling method and consisting of a single master and up-to seven slaves, and the second layer of the hierarchy is configured as a sub-nets consisting of multiplicity of sensors and actuators and communicating internally using ANT personal area network (PAN) wireless interface, or via a digital wire interface. Such network topology provides deterministic latency of a hierarchy a single-hop Bluetooth network, irrespective of the numbers of sensors and actuators embedded within each sub-net of the second layer of hierarchy. The network latency is upper-bounded by the number of slaves in the first layer of hierarch, Furthermore, the Round-Robin scheduling method is supplemented with the gating-off the slave RF transmission when the slave has no data to send, or when the difference between current sensor samples and the previous sensor sample is smaller then predefined threshold. Such discontinued transmission lowers slave power consumption system interference.

Owner:IPCOMM

Hardware function generator support in a DSP

InactiveUS20060282489A1Quickly and efficiently process CORDIC algorithmEfficient retrievalDigital data processing detailsSpeech analysisParallel computingInit

The present invention relates to digital signal processors with an integrated module configured to compute a Coordinate Rotation Digital Computer (CORDIC) in a pipeline. The pipelined module can advantageously complete computation of one CORDIC computation for each clock pulse applied to the CORDIC module, thereby providing a CORDIC computation for each clock pulse. One embodiment advantageously computes a first portion of a computation with a lookup table and a second portion in accordance with a CORDIC algorithm. Advantageously, data in a CORDIC pipeline is automatically advanced in response to read instructions and can be automatically advanced from the beginning of the pipeline to the end of the pipeline to reinitialize the pipeline. This allows information to be retrieved from the CORDIC pipeline with relatively little overhead The automatic starting and stopping of the CORDIC pipeline advantageously allows the retrieval of computations from efficient pipeline architectures on an as-needed basis.

Owner:QUARTICS

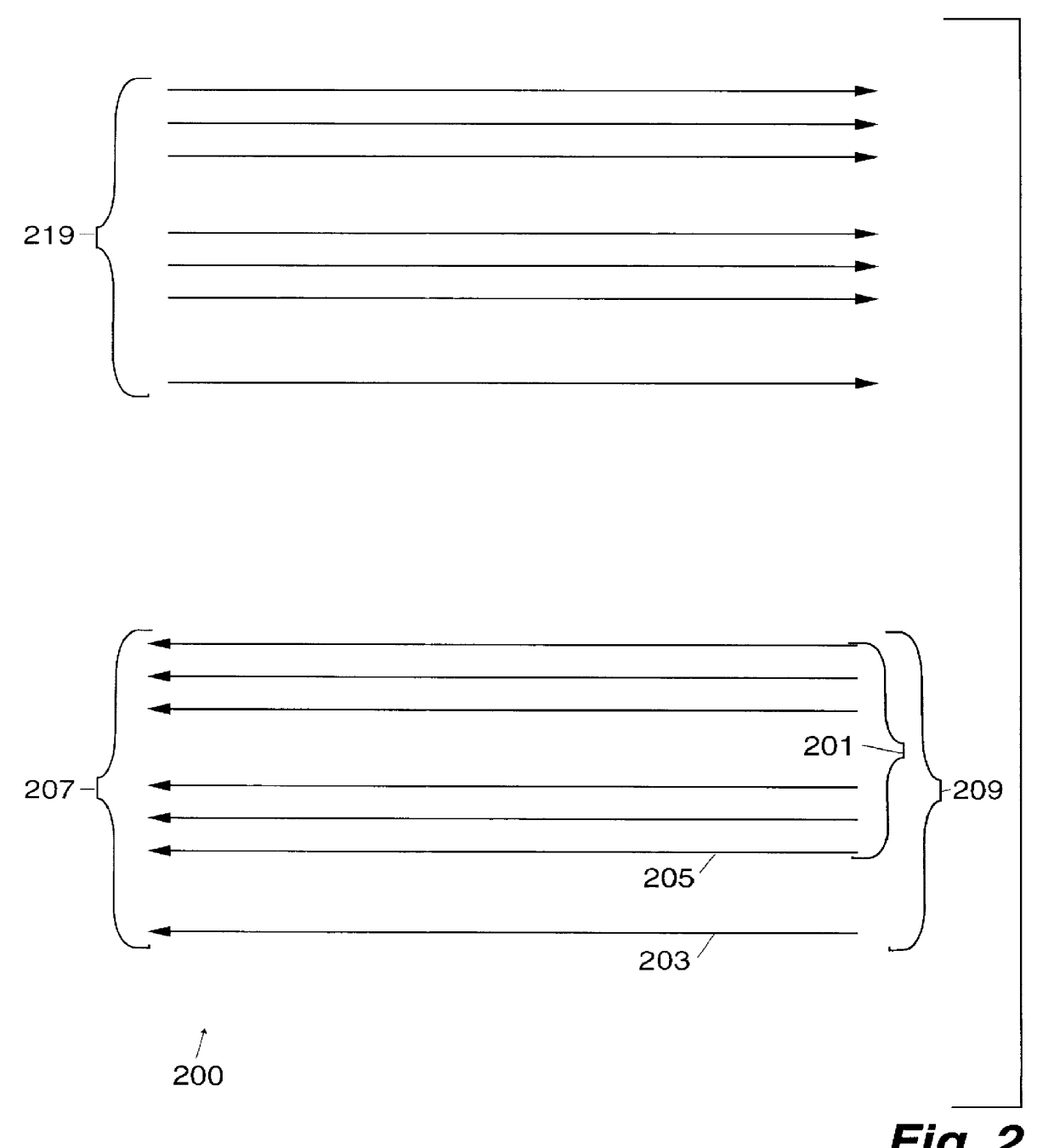

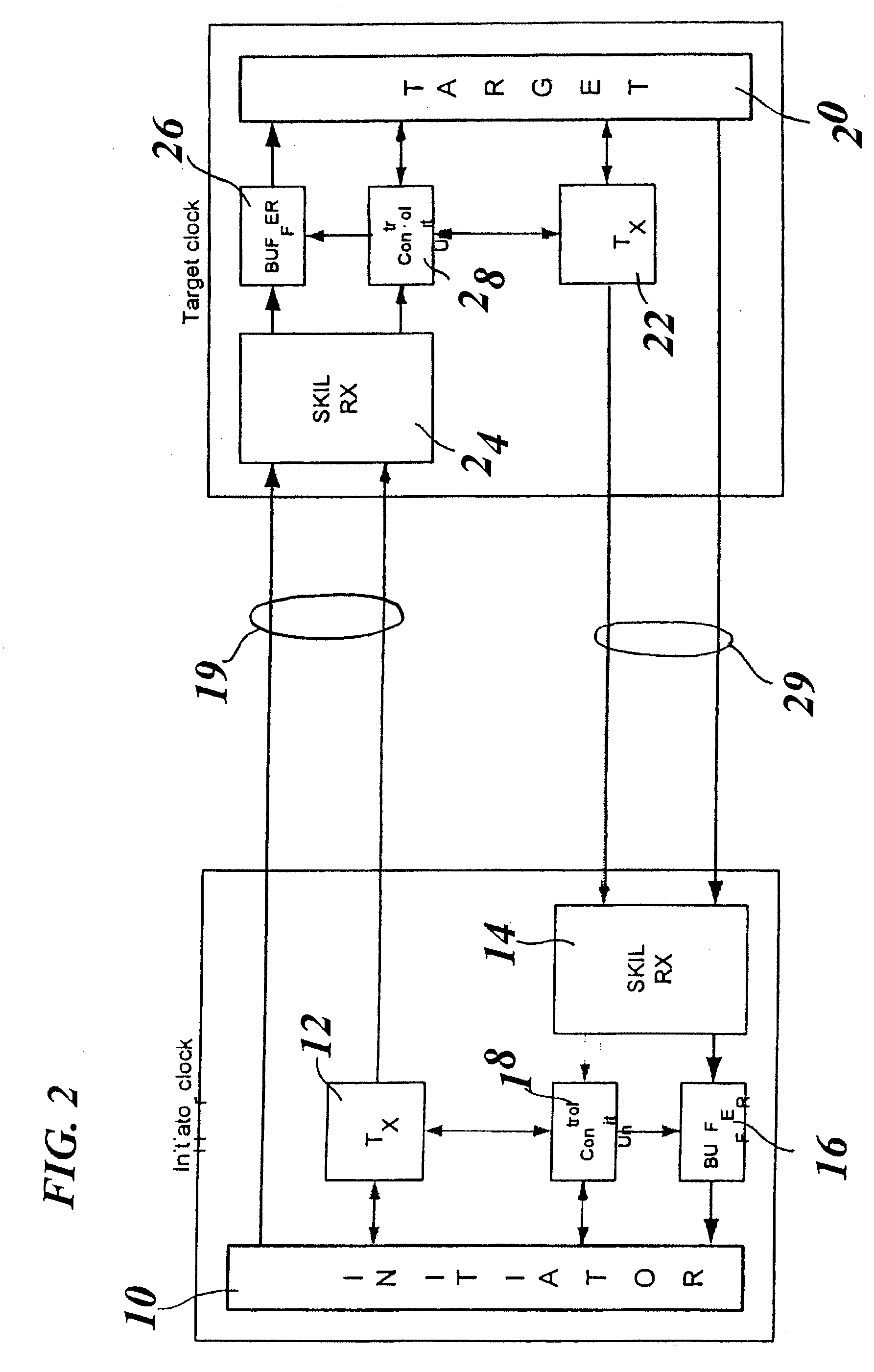

Method and system for full-duplex mesochronous communications and corresponding computer program product

ActiveUS20080294803A1Reduce areaEasy to meetError preventionFrequency-division multiplex detailsData streamControl signal

Data transport is provided in a communication network such as a Network-on-Chip arrangement via full-duplex mesochronous links between routers. Request signals and response signals are exchanged between these routers acting alternatively as an initiator and a target operating in respective clock domains at opposite ends of respective full-duplex mesochronous links. The request initiator flow control signals are monitored at the target end of the link while the response target flow control signals are monitored at the initiator end of the link. The monitoring action involves ascertaining if a request has been granted at the initiator end of the link and if a response has been granted at the target end of said link thus correspondingly managing the data flow over the link.

Owner:STMICROELECTRONICS SRL

Method and computer system for optimizing the signal time behavior of an electronic circuit design

InactiveUS7844931B2High degreeReduce power levelCAD circuit designSpecial data processing applicationsAlgorithmClock tree

A method and program for designing an electronic circuit, especially a clock tree and a sub-clock tree, within a set of sinks with given target arrival time windows, preferably on an integrated circuit. The clock tree and the sub-clock tree are preferably connected through one or multiple fixed circuits which must not be altered, cloned or removed. Several alternative implementations of the at least one logic structure are built and for each of the several alternative implementations data is stored. A set of configurations is built, each configuration comprising a combination of the one or several alternative implementations and each configuration satisfying the target arrival time windows at the complete set of sinks. A configuration is selected according to an evaluation of the data, preferably latency data, for constructing the configuration. No manual interaction is needed and a configuration with minimum latencies is provided.

Owner:TAIWAN SEMICON MFG CO LTD