Hardware function generator support in a DSP

a function generator and hardware technology, applied in the field of digital signal processing, can solve the problems of limited function and data resolution, large amount of data stored in a rom lookup table that can quickly surpass practical size and cost limitations, and typical software implementations of function generation are relatively slow. , to achieve the effect of efficiently retrieving information, quick and efficient processing of cordic algorithm in pipeline, and low overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Although this invention is described in terms of certain preferred embodiments, other embodiments that are apparent to those of ordinary skill in the art, including embodiments which do not provide all of the benefits and features set forth herein, are also within the scope of this invention. Accordingly, the scope of the present invention is defined only by reference to the appended claims.

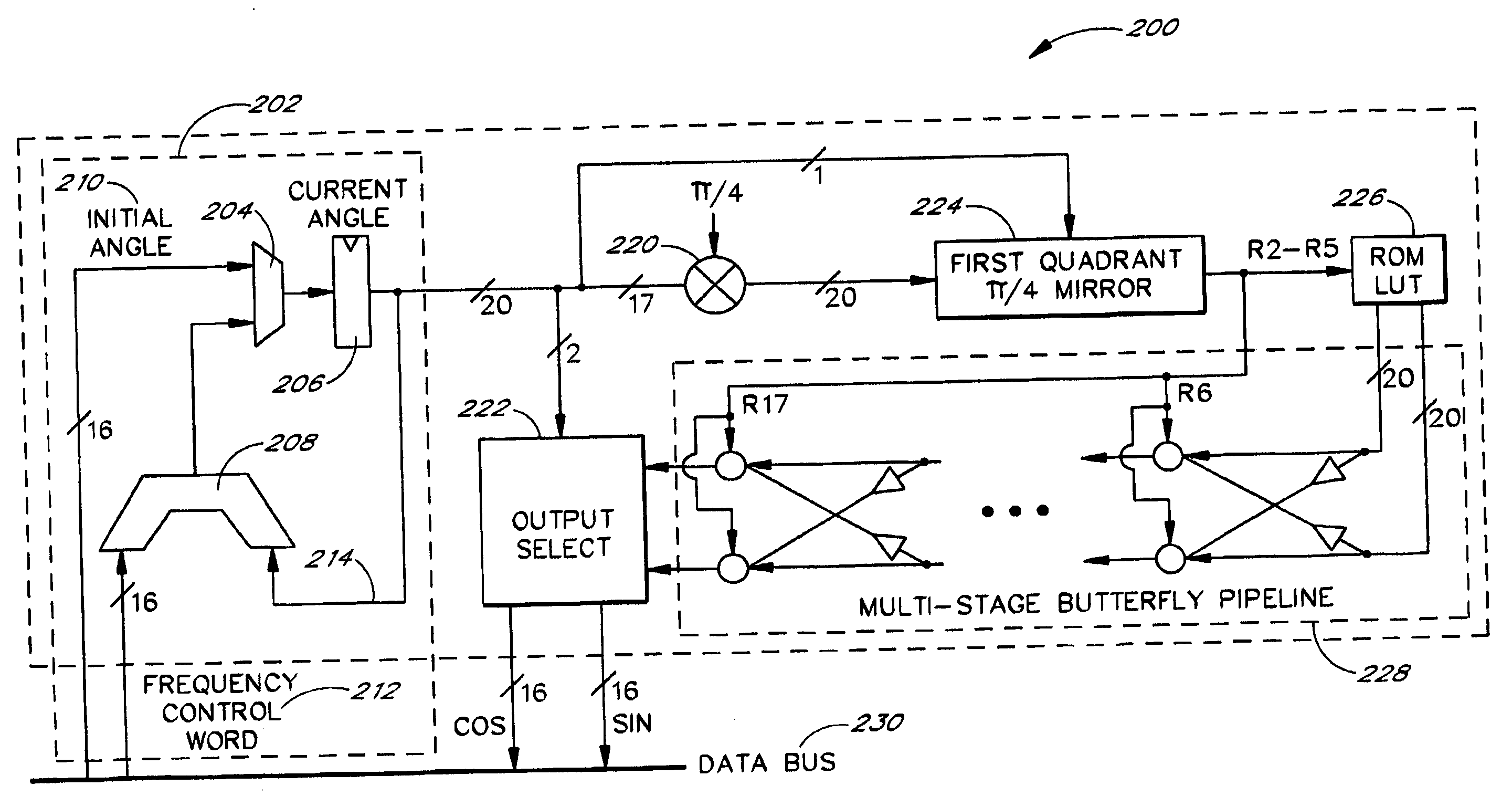

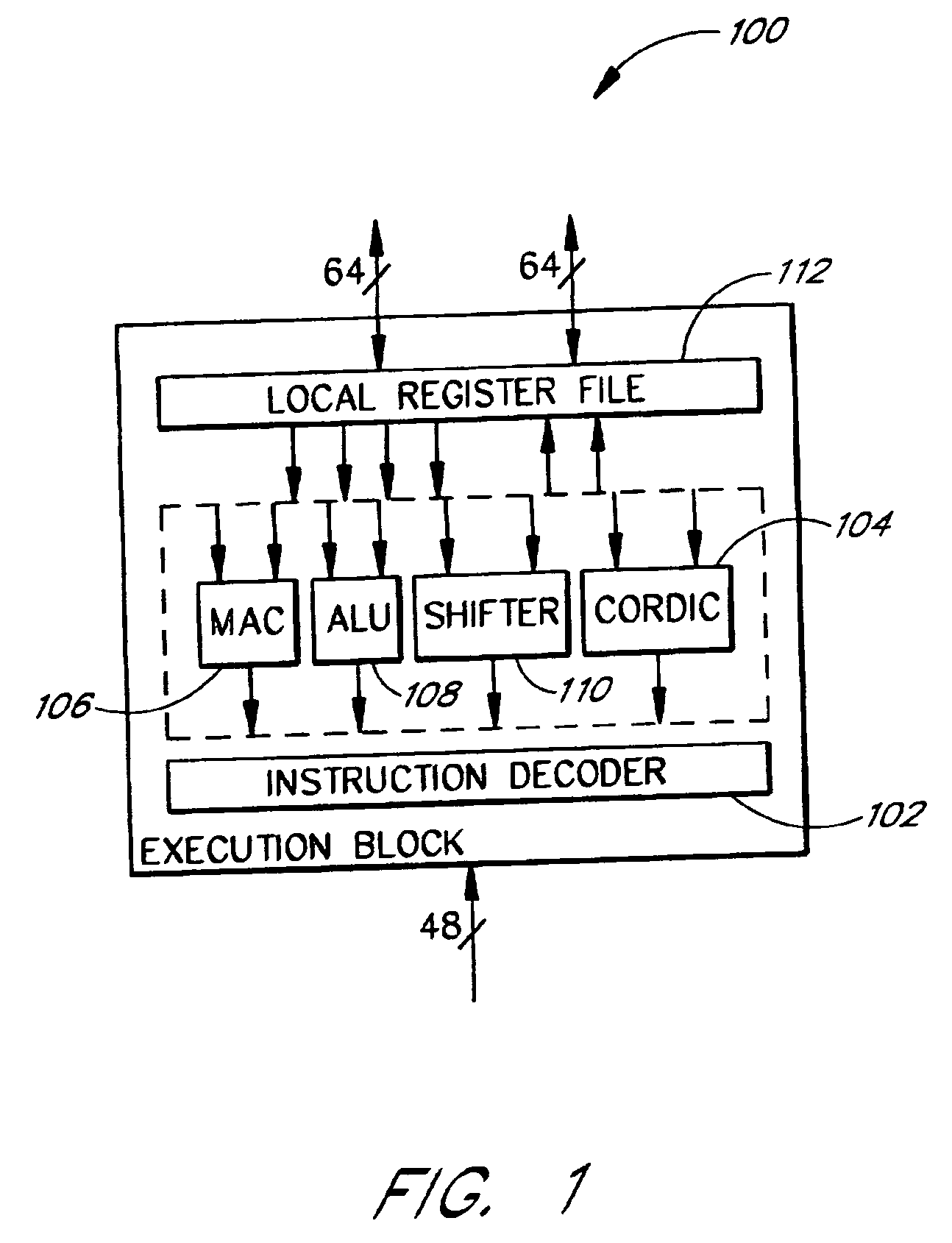

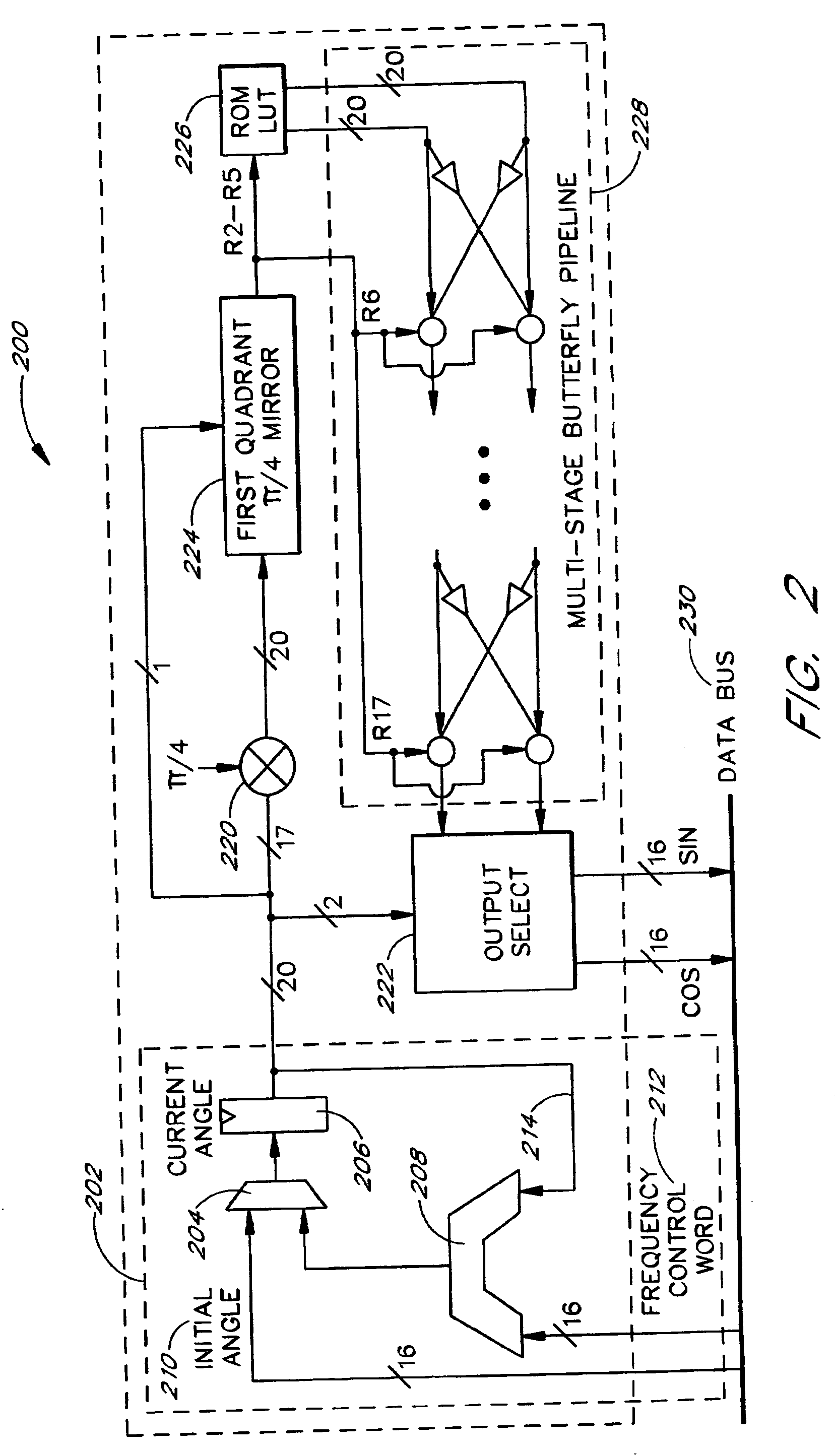

[0029] One use of a Coordinate Rotation Digital Computer (CORDIC) algorithm is to generate functions such as trigonometric, logarithmic, hyperbolic and linear functions. Another use of the CORDIC algorithm is to convert between Polar and Cartesian coordinates. The CORDIC algorithm performs vector coordinate rotations using simple iterative shifts and add / subtract operations. The general (Givens') rotation transform expressed in Equations 1A and 1B rotates a vector by an angle φ.

x′=x cos φ−y sin φ

y′=y cos φ+x sin φ. Eqs. 1A and 1B

[0030] The transform can be rearranged as shown in Equat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More