Wiring delay deviation fast calibration method of arbitration-type PUF based on FPGA

A technology of delay deviation and calibration method, applied in CAD circuit design, instrument, calculation, etc., can solve the problems of power consumption, high power consumption, multi-time and other problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

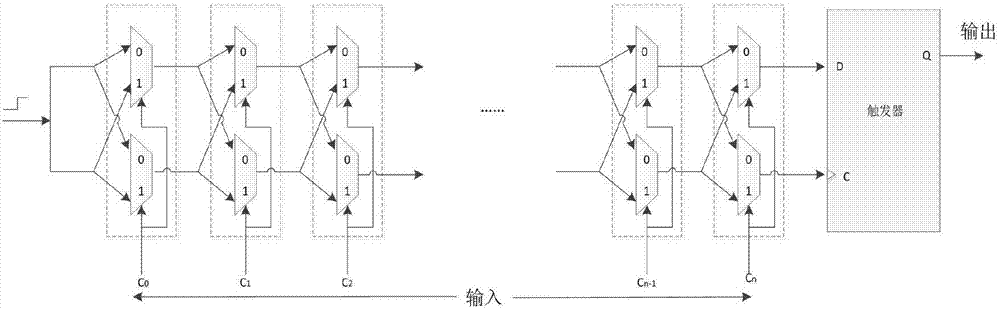

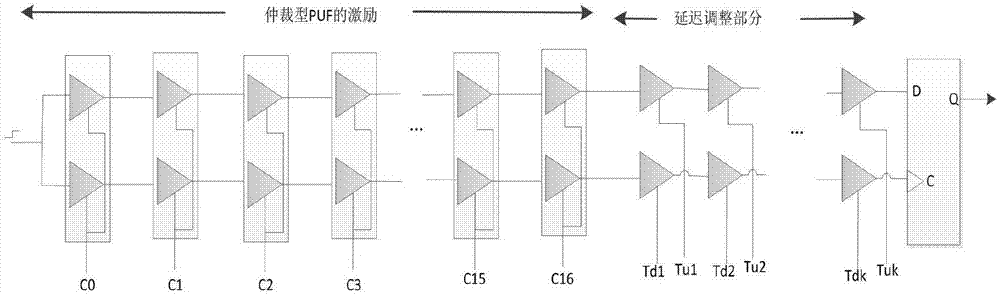

Image

Examples

Embodiment Construction

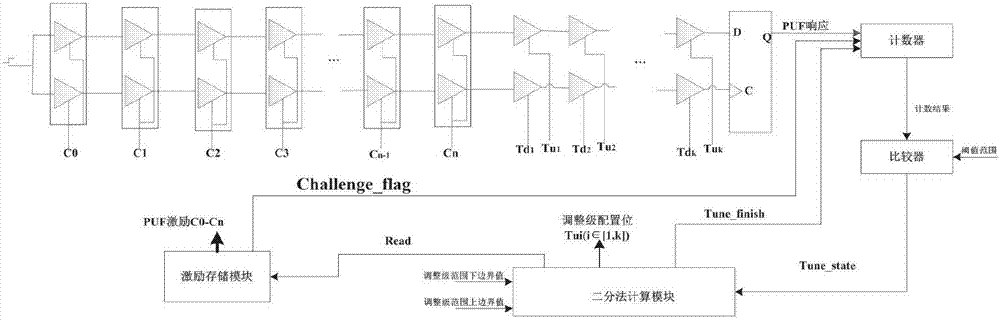

[0033] By adopting the method for fast calibration of the FPGA-based arbitration type PUF wiring delay deviation of the present invention, the schematic diagram of its circuit structure is as follows image 3 shown. The adjustment range of the adjustment level can be selected according to the needs, and the automatic adjustment of the delay of the single signal channel can be carried out, and the automatic adjustment of the delay of two signal channels can also be carried out at the same time. In this method, the adjustment range is set to [0,40], and the automatic adjustment circuit is implemented on the upper signal channel.

[0034] Using the FPGA-based arbitration-type PUF wiring delay quick calibration method of the present invention, the basic steps for automatically adjusting the add-on delay are as follows:

[0035] Step 1: Measure the randomness of the distribution of 0 and 1 in the PUF response values of the two boundary values of the adjustment level, and deter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More