Patents

Literature

45results about How to "Simplify interface design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

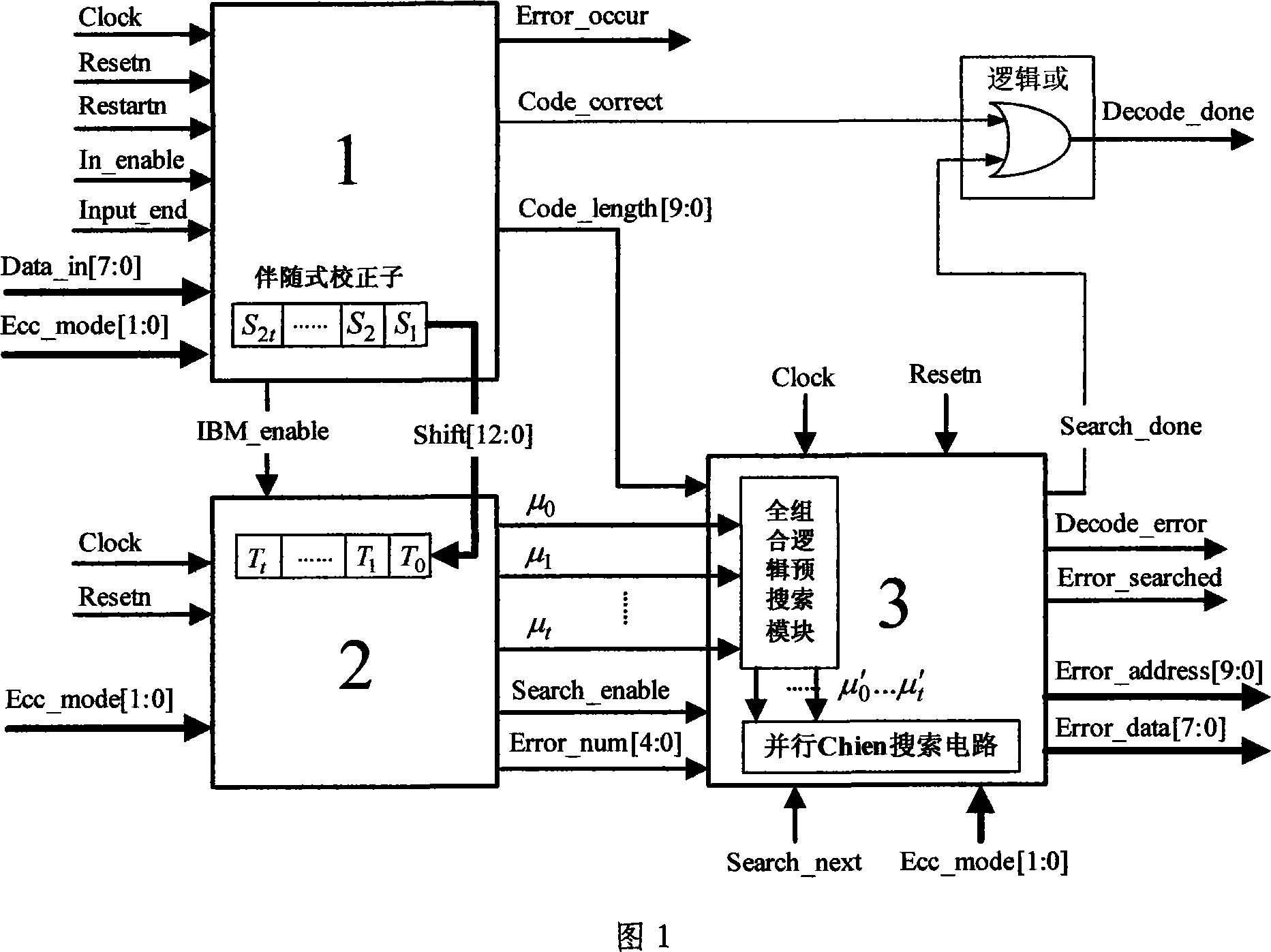

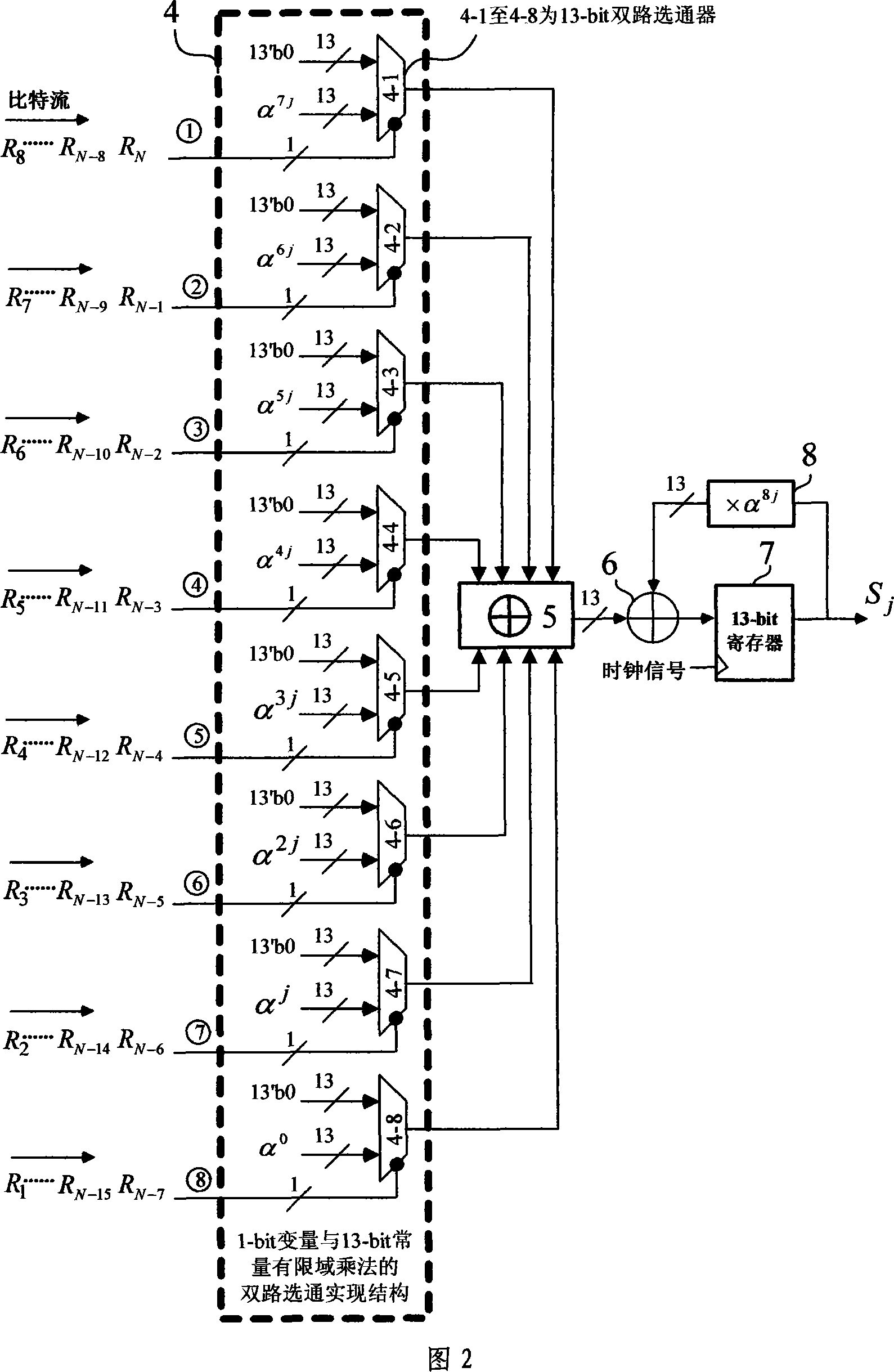

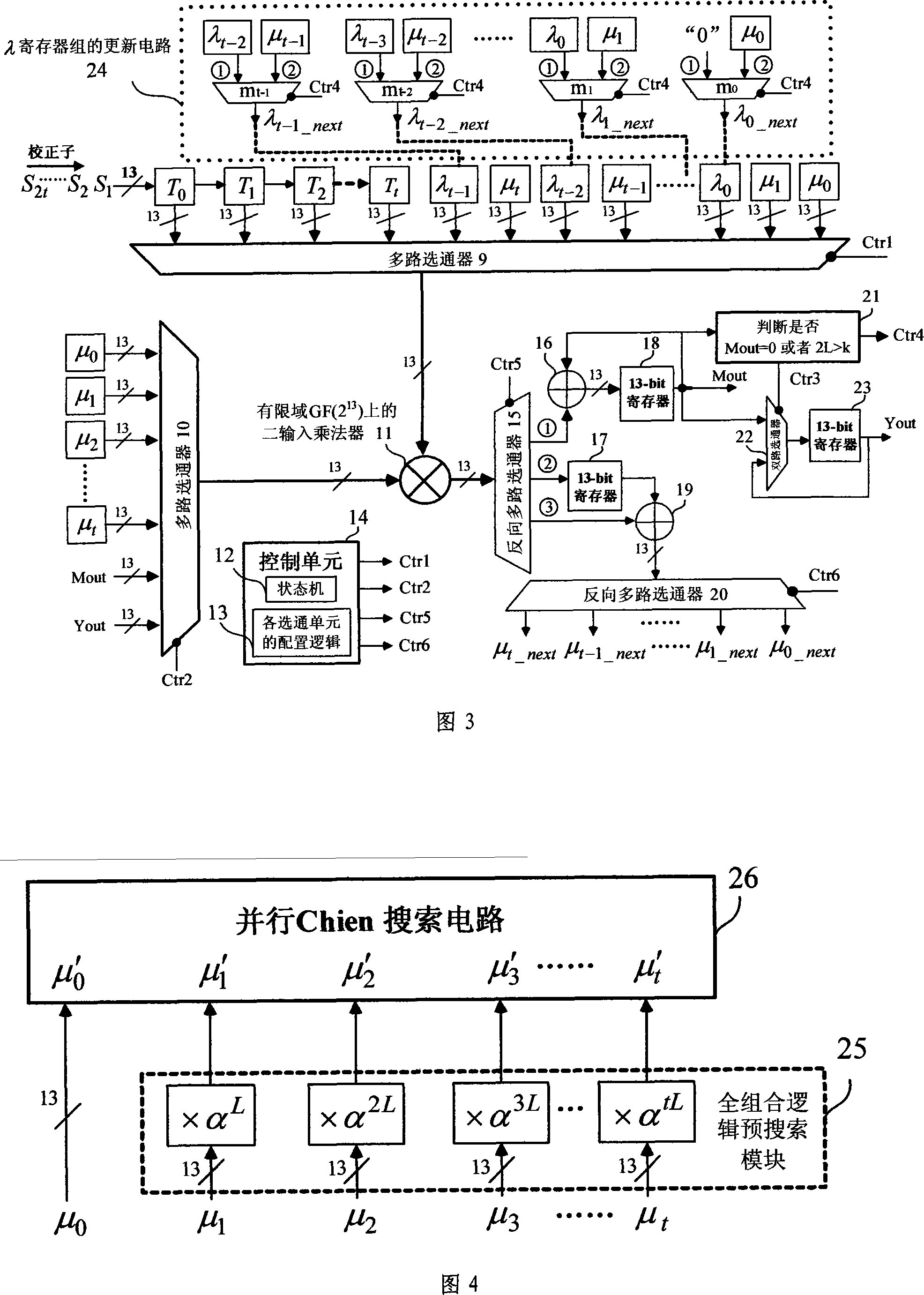

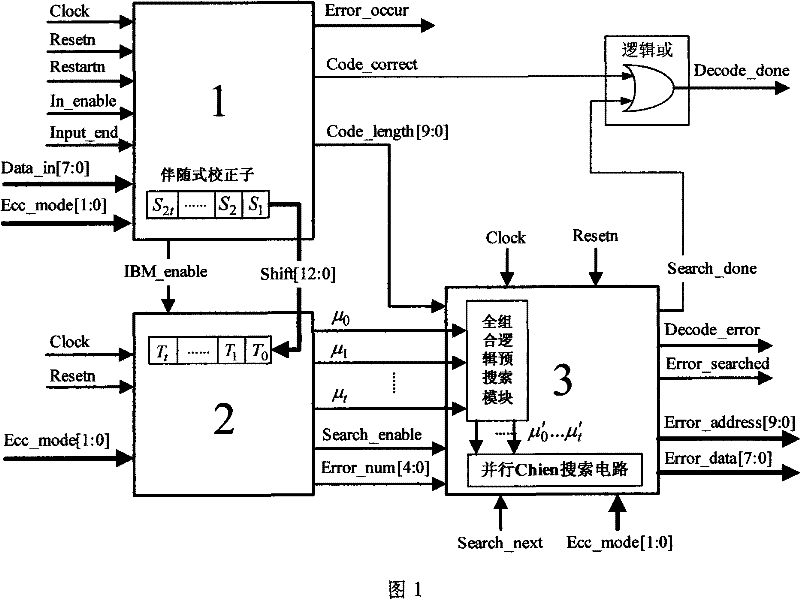

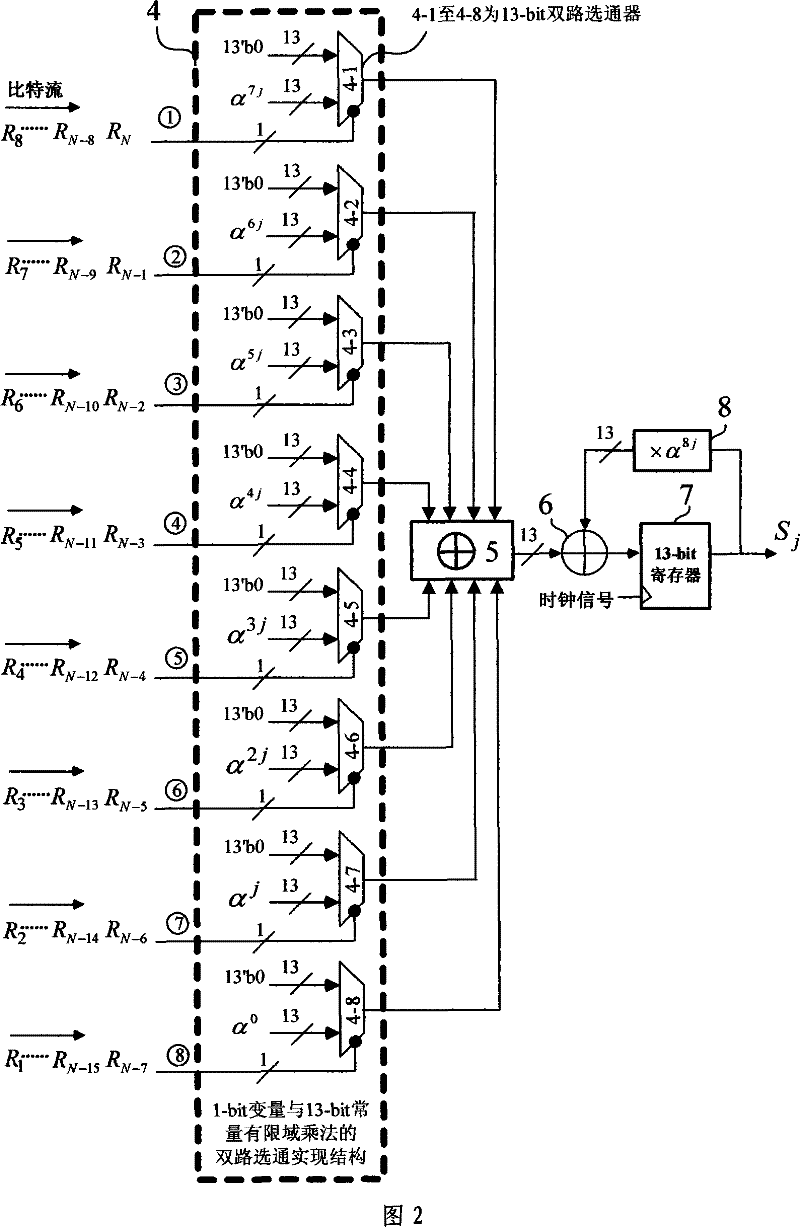

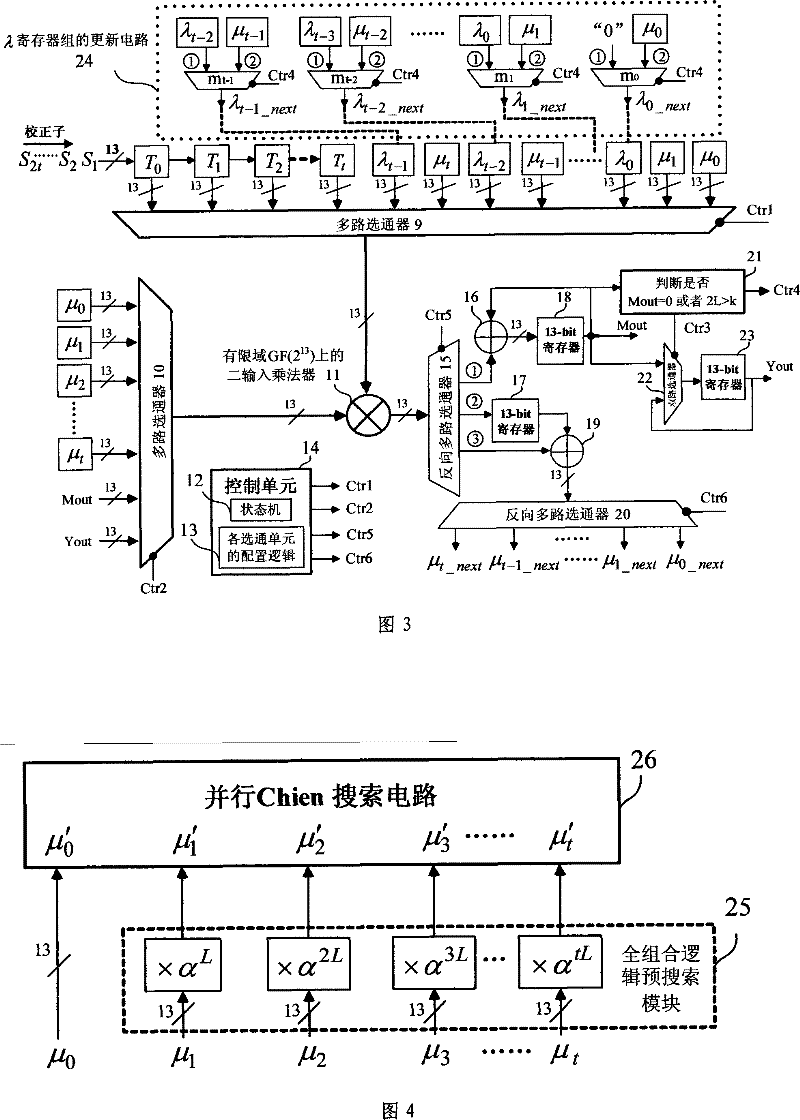

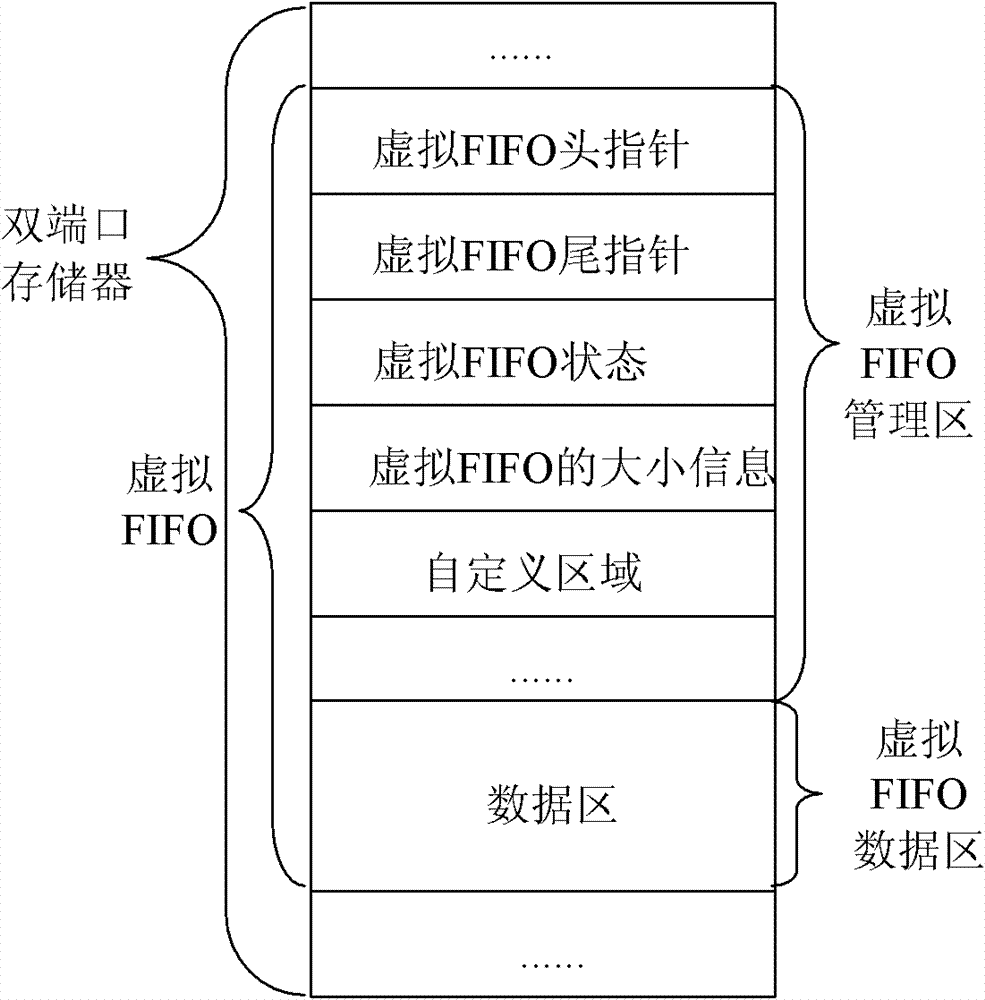

Area compact type BCH paralleling decoding circuit supporting pre searching

A compact BCH parallel decoding circuit which supports preview search works on a finite field GF(2<13>). The parallel decoding circuit comprises a syndrome arithmetic circuit(1), a realizing circuit(2)with multiple shoots in one round for IBM wrong position multinomial iterative computation in the finite field GF(2<13>), a wrong address search circuit(3) provided with a totally combined logic pre-search module and a multifunctional configurable data interface(27)of an encoder. Compared with prior art, the decoding circuit has the advantages that the hardware is of low degree of complexity, the circuit area is compact and the decoding circuit is low in cost; data throughput is high and wrong address research is quick; the interface is simple in design and is practical and multi-functional; correcting performance can be flexibly configured according to the length of the check element and is free from the change of the code length.

Owner:NATIONZ TECH INC

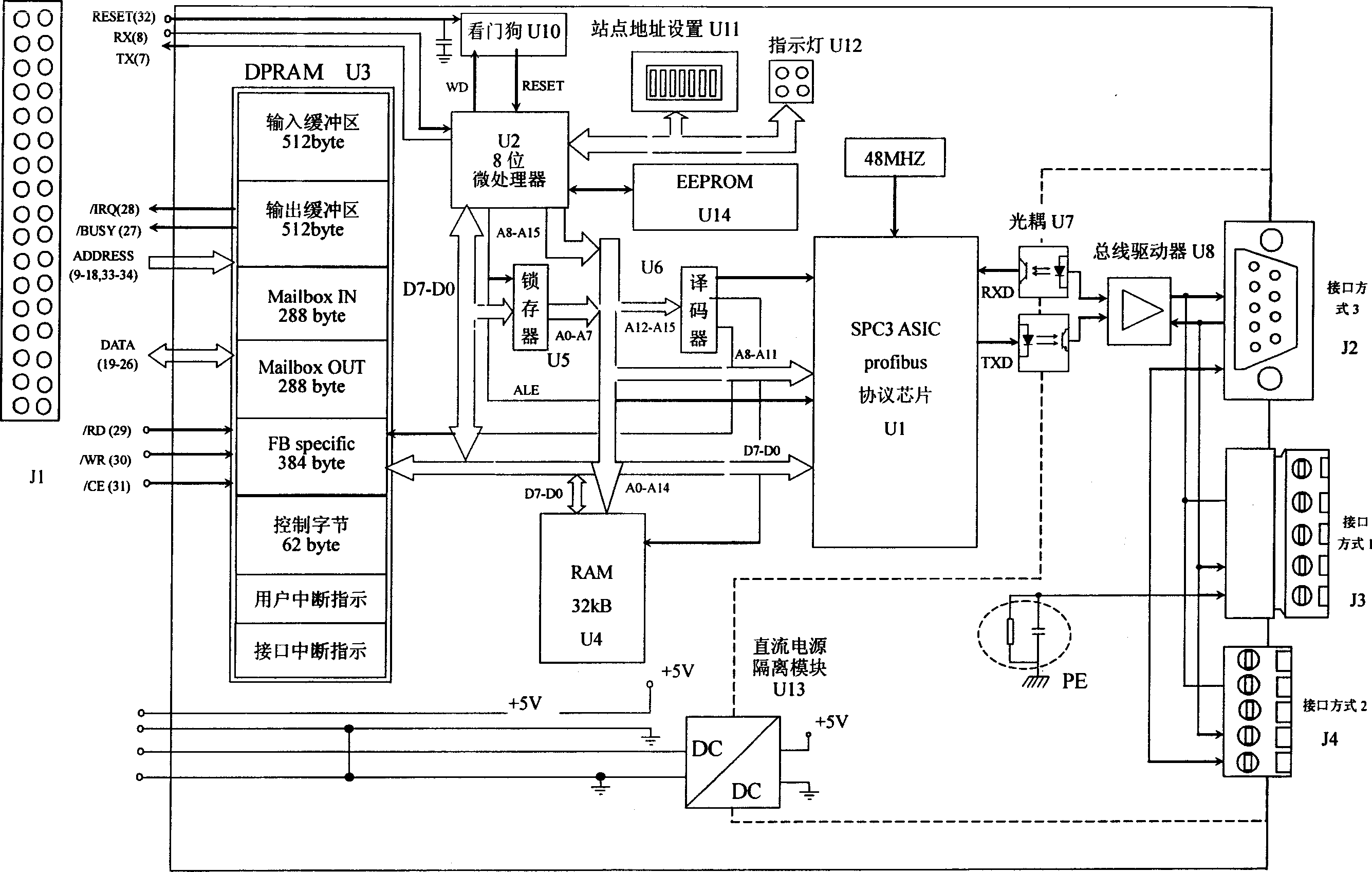

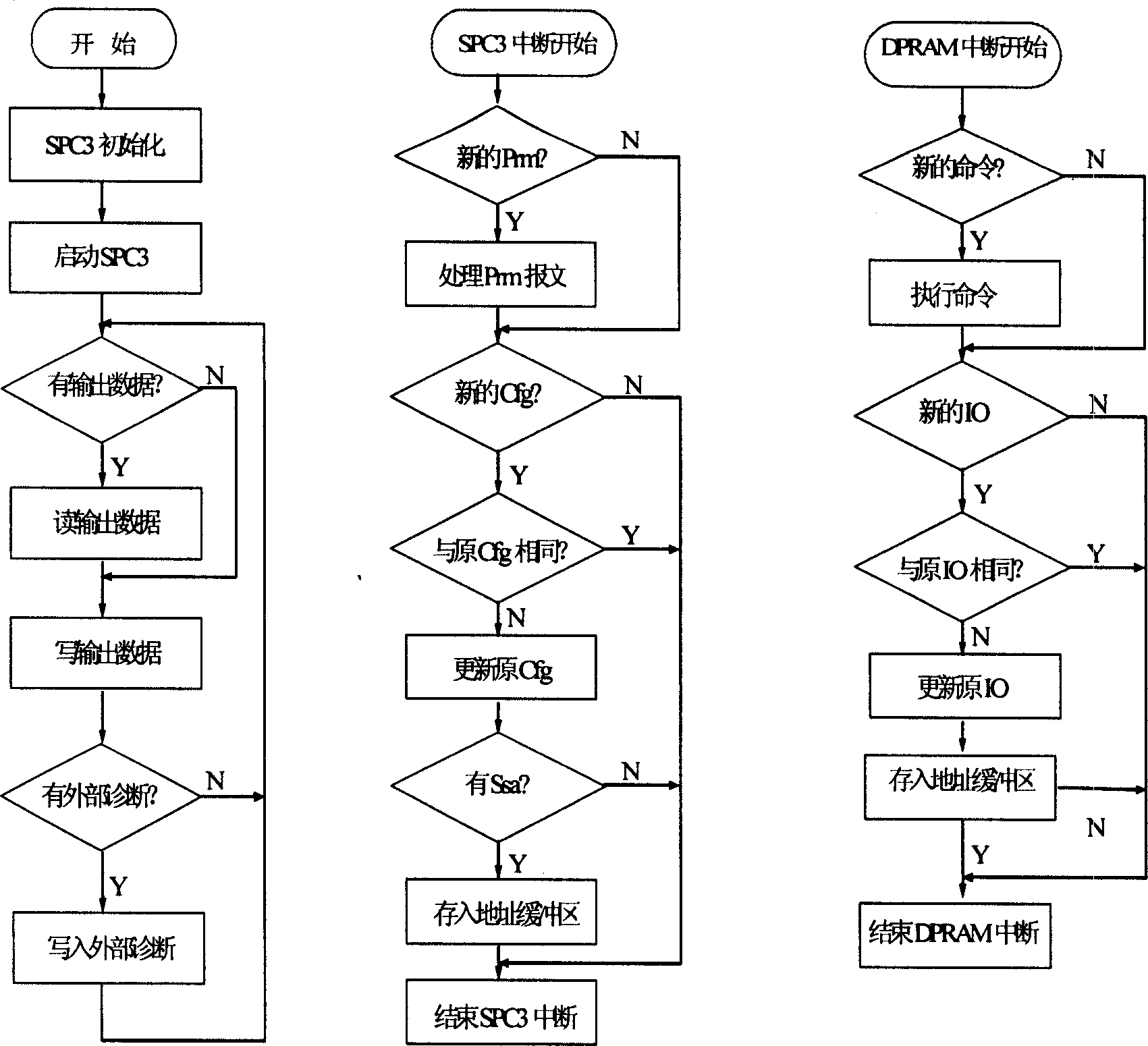

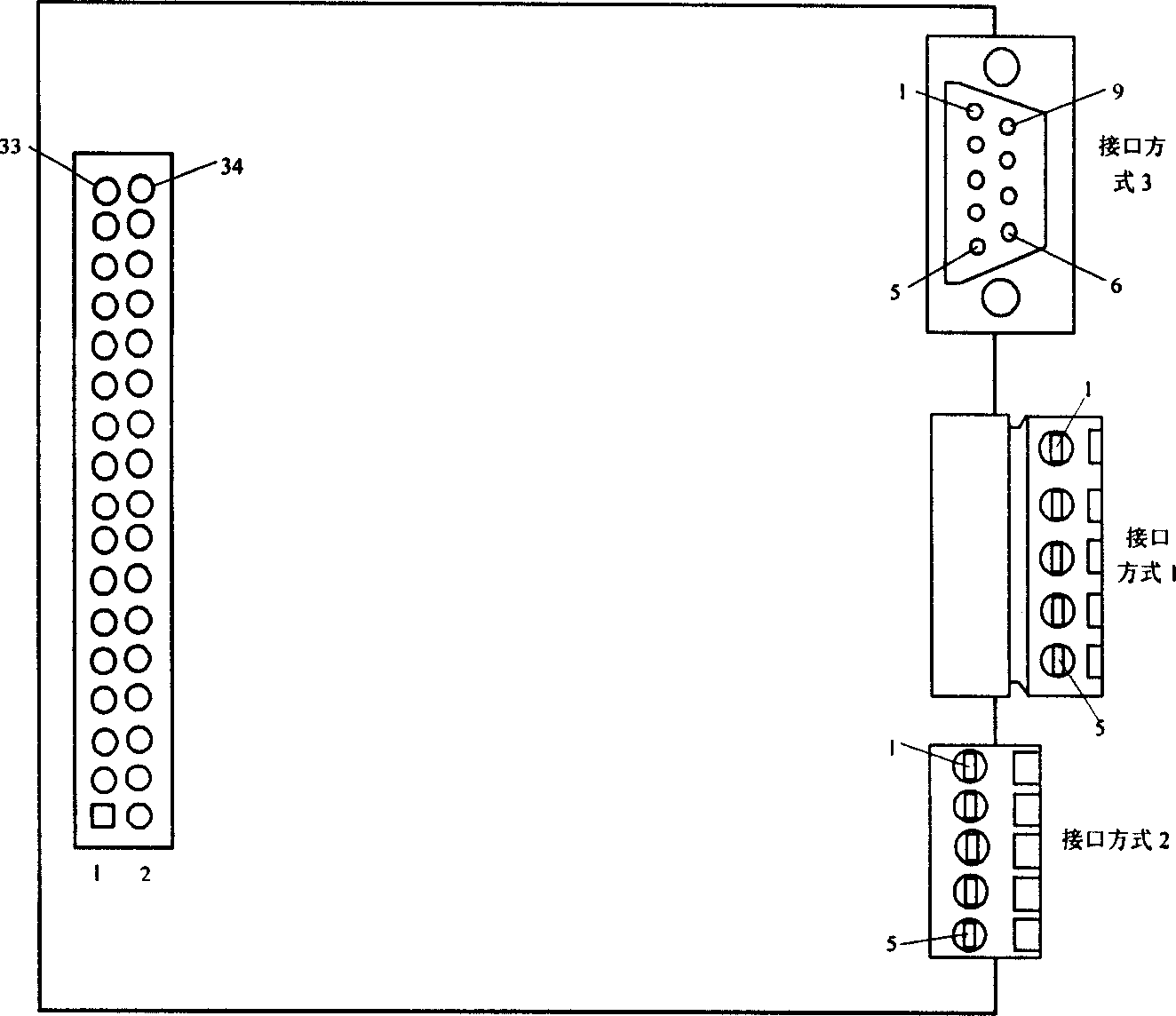

Embedded field bus protocol interface device and implementation method

InactiveCN1801020AReduce distractionsReliable communicationTransmissionTotal factory controlComputer moduleMovement control

The invention discloses a flush-type on-site bus protocol interface device and method, which connects instrument or equipment with PROFBUS to accomplish DP passive station communication function in the on-site PROFBUS. One end of interface mode exchanges data with 8-byte or 16-byte microprocessor as intelligent controller through two-port RAM or asynchronous serial port of TTL electrical level, which can be embedded in the circuit of intelligent instrument equipment; the other end displays standard Profibus-DP passive station interface, which communicates with other equipments through the switch-in bus of Profibus-DP passive station. The invention is fit for Profibus interface of high speed and moving control device, which brings significant social and economical benefit.

Owner:HEBEI UNIV OF TECH

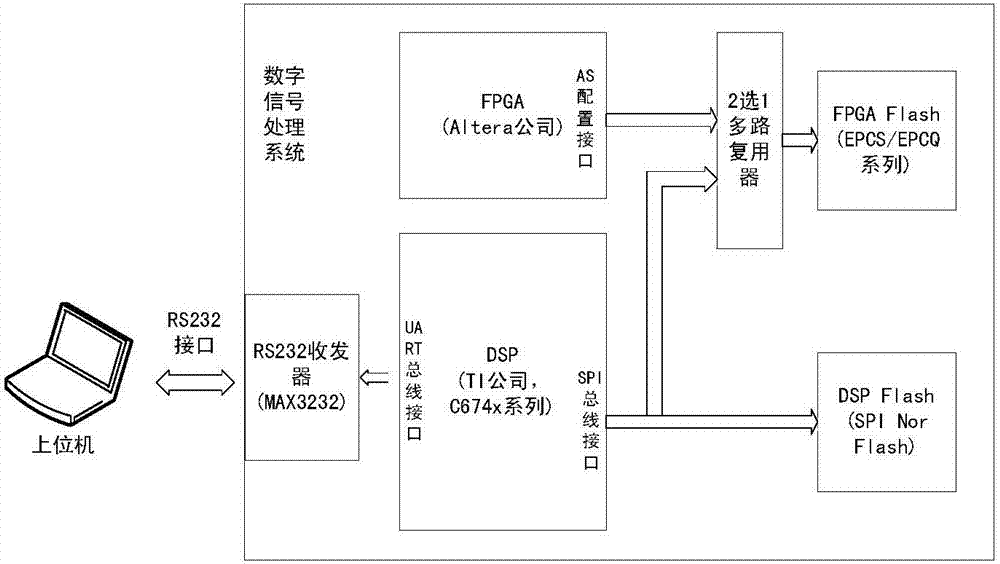

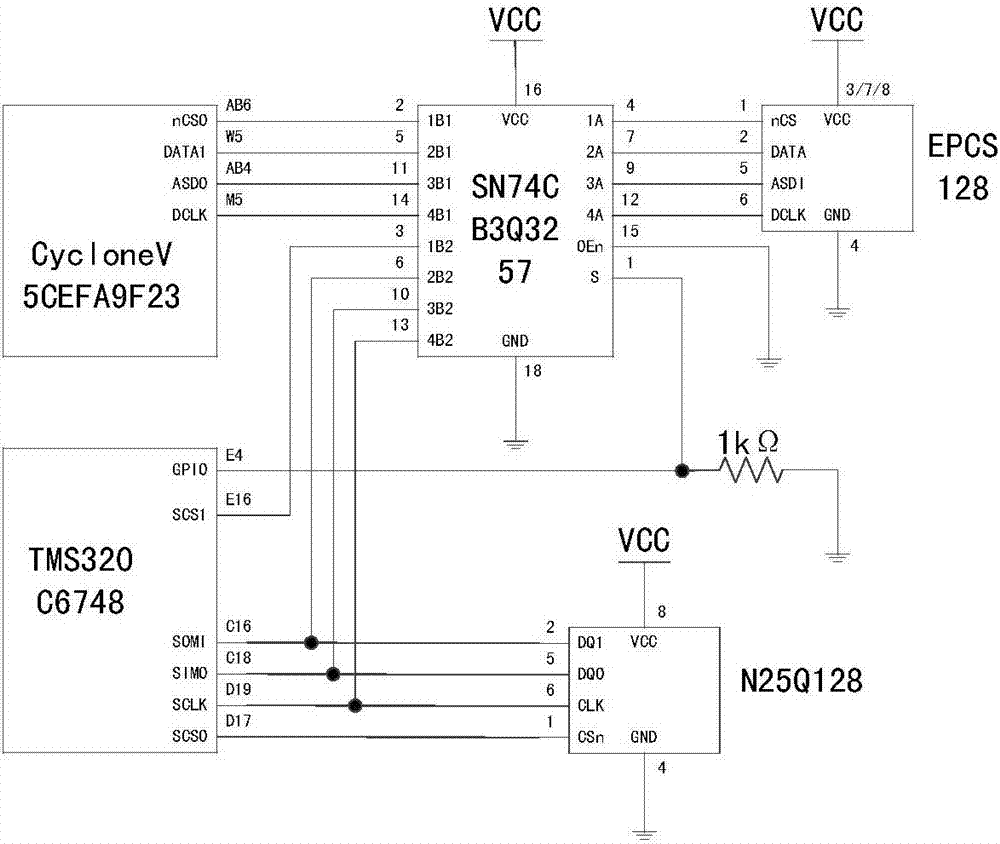

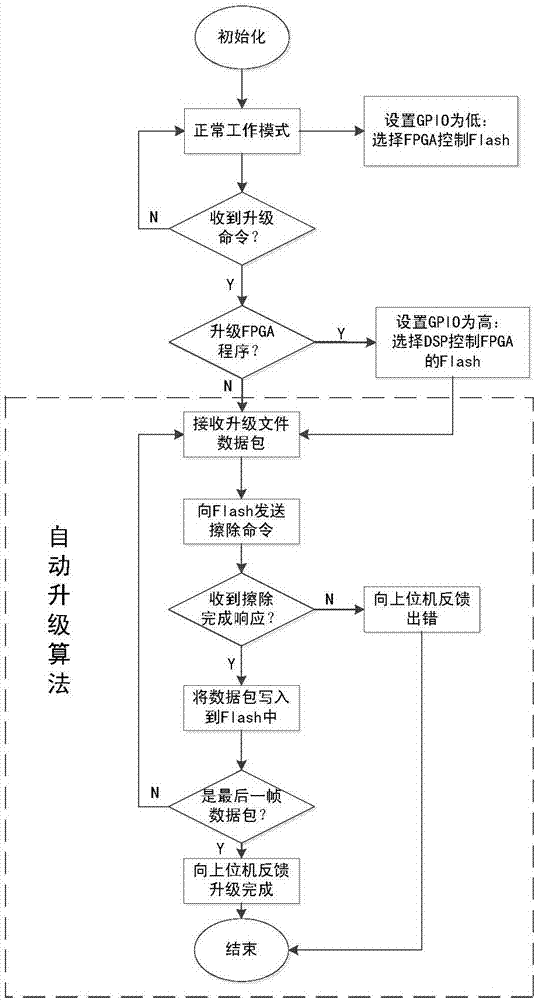

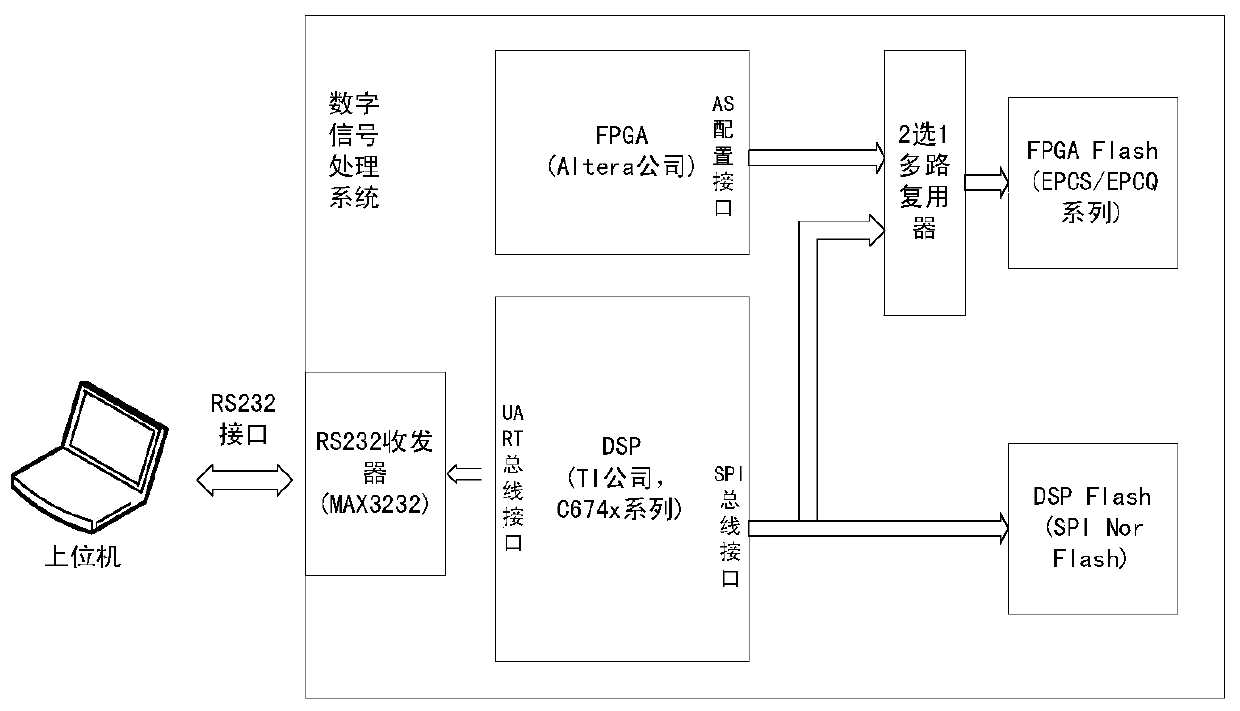

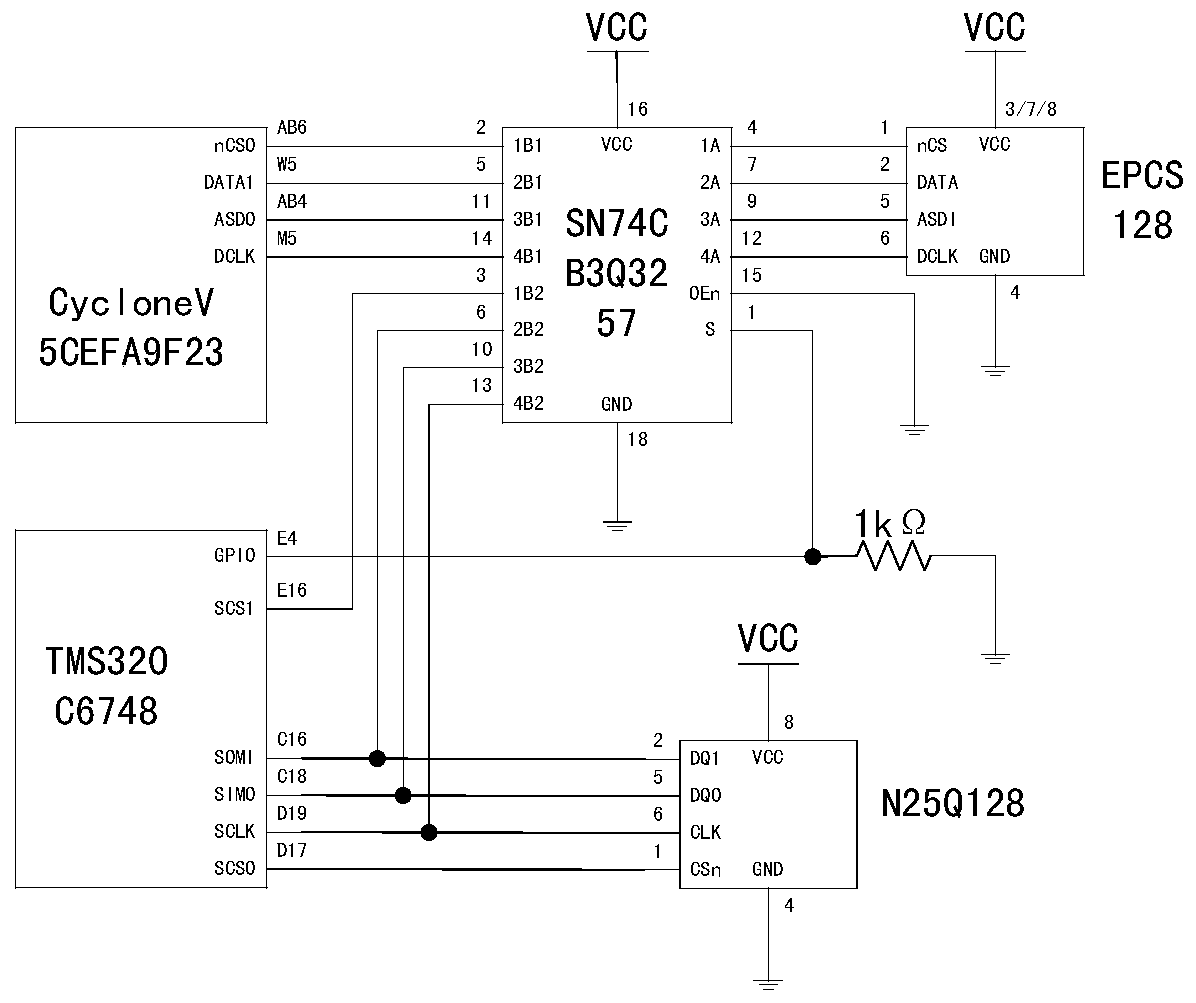

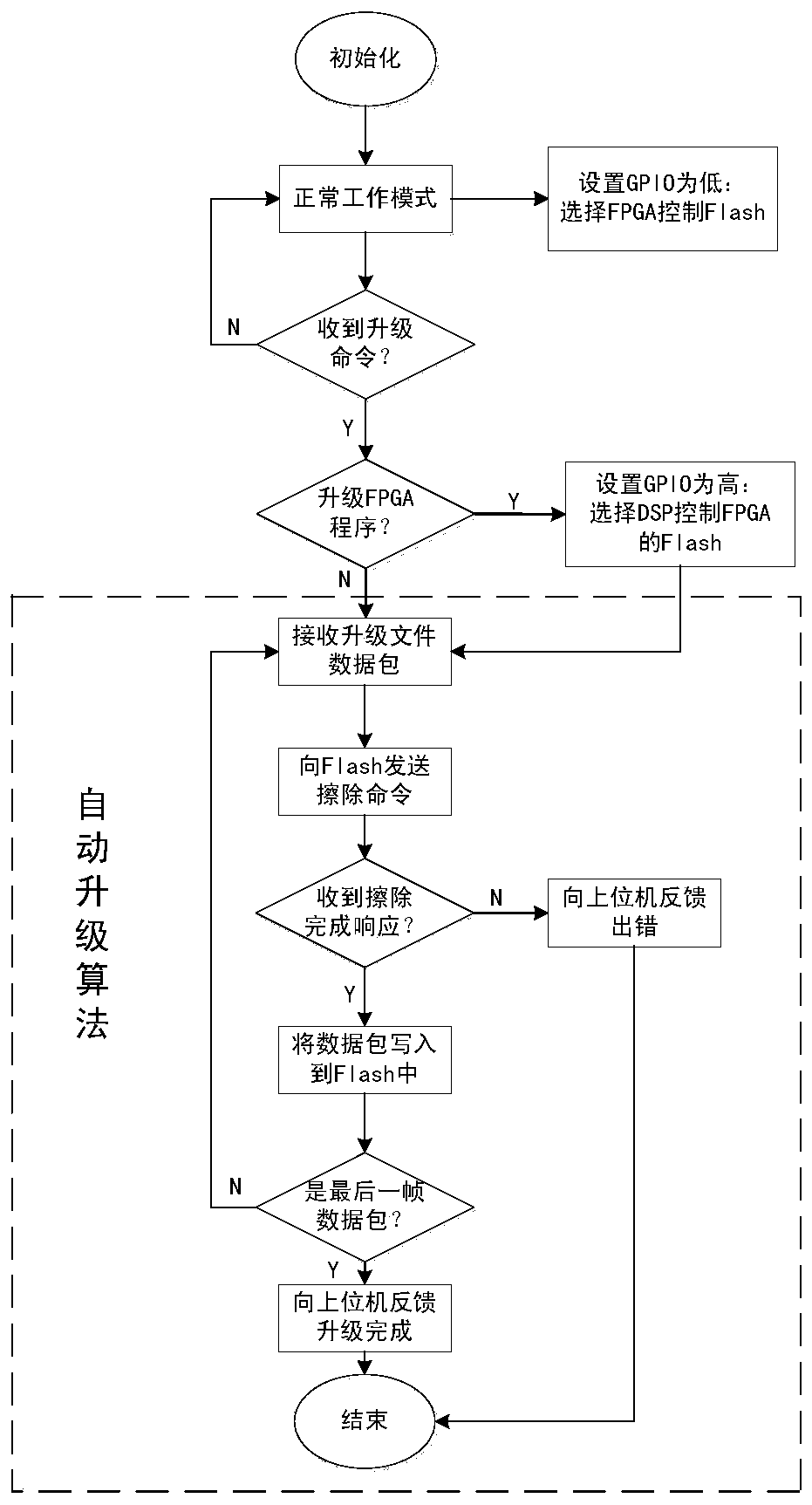

DSP (digital signal processor) and FPGA (field programmable gate array) system on-line updating method

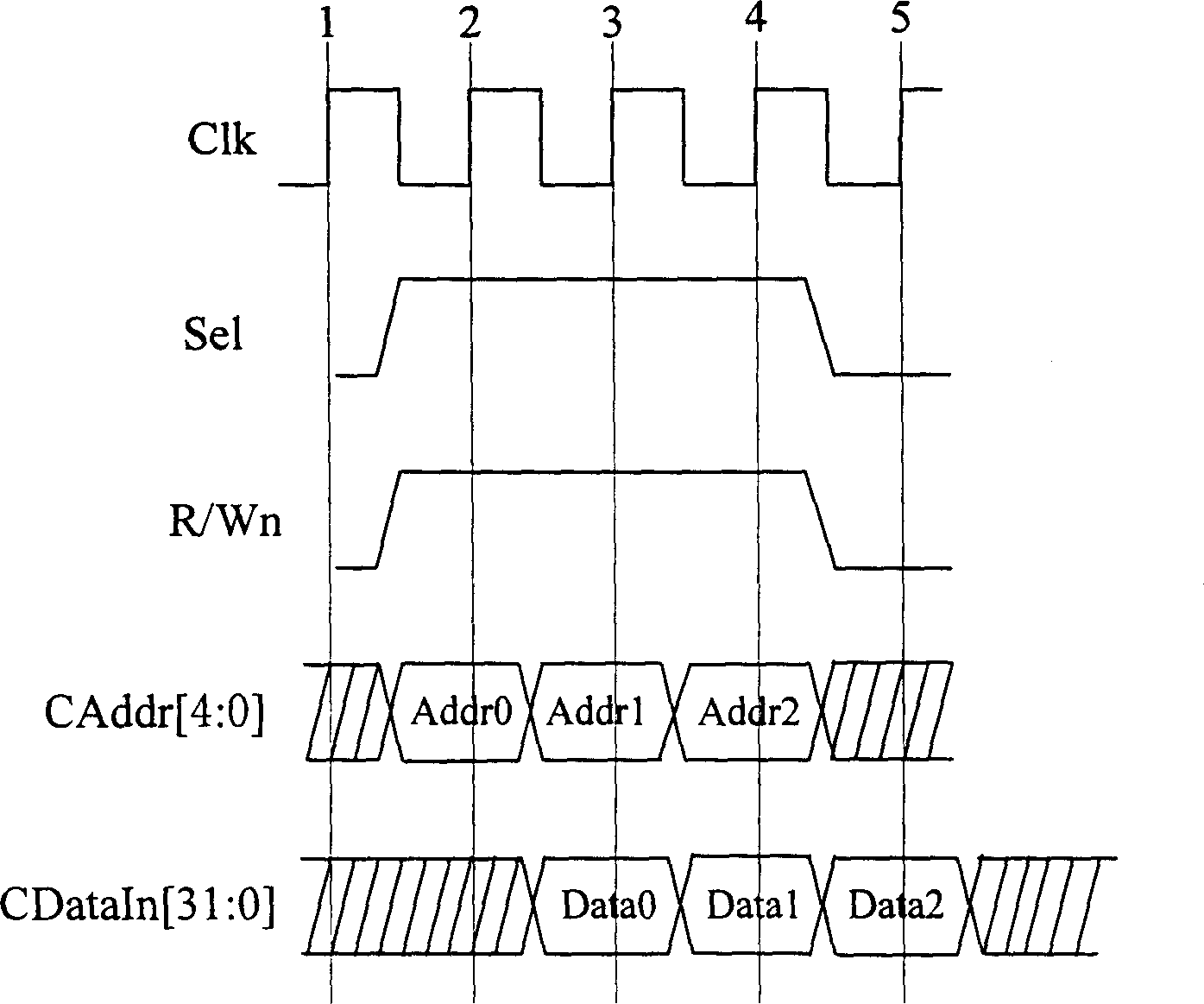

ActiveCN106909425AReduce Design ComplexitySimple interfaceSoftware engineeringProgram loading/initiatingFpga field programmable gate arrayMultiplexer

The invention discloses a DSP (digital signal processor) and FPGA (field programmable gate array) system on-line updating method, which is used for solving the problem of program online updating of a DSP and FPGA digital signal processing system. The method has the technical scheme that through a universal serial bus interface, the interconnection between a host computer and a DSP is completed; a DSP and FPGA program file to be updated is transmitted to the DSP; a Flash memory of the DSP or the FPGA is controlled to be updated by a DSP automatic updating algorithm; one group of SPI interface bus of the DSP is used for completing the hardware connection and erasing and writing of two Flashes; the bus address coding is completed through a multiplexer; the bus conflict is avoided. The program updating of the two chips of DSP and FPGA is simultaneously completed under the condition without dismounting the equipment; the interface is simple; the software and hardware design complexity is low; a simple and effective method is provided for the online updating of the digital signal processing system.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

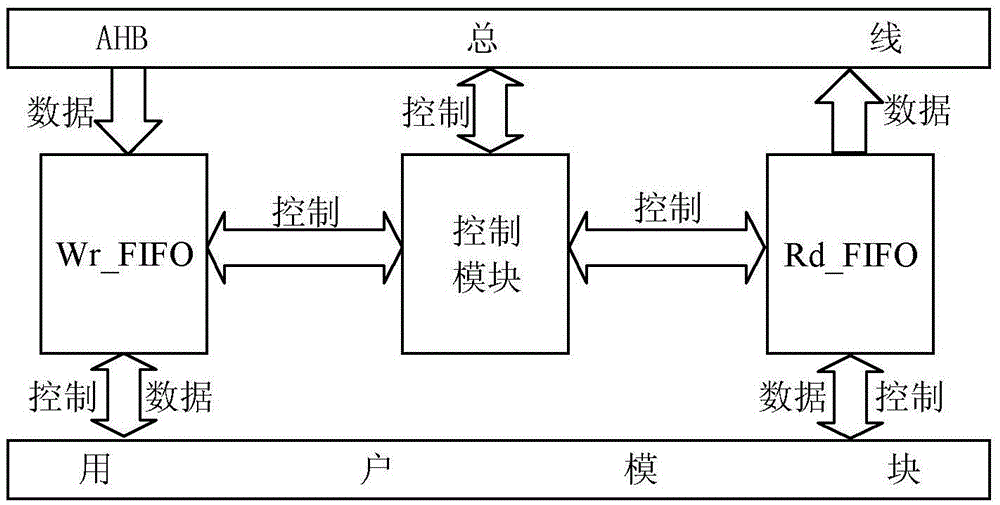

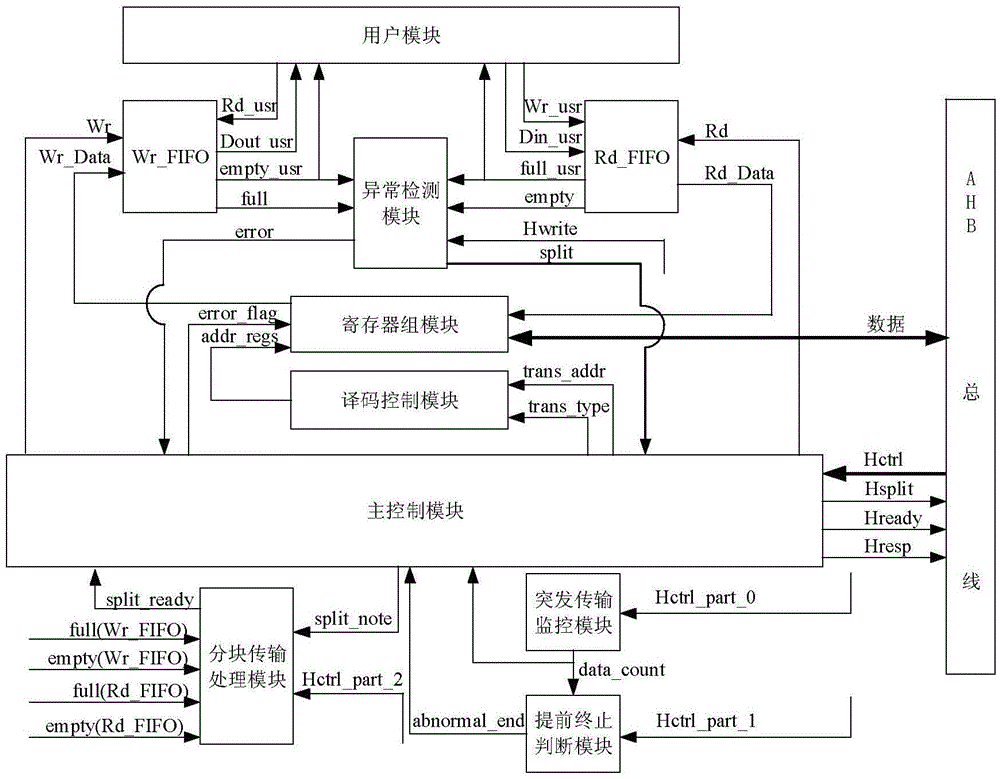

AHB interface system for stream data transmission

InactiveCN105573951AMeet Timing RequirementsVersatilityElectric digital data processingData streamBurst transmission

Aiming to solve the problem that an IP module cannot be matched with an on-chip bus of an SOC (System On Chip) because current methods cannot provide a universal interface, the invention provides an AHB interface system for stream data transmission. The AHB interface system for stream data transmission comprises a master control module, a register set module, a decoding control module, an abnormality detection module, a burst transmission monitoring module, an early termination judgment module, a block transmission processing module, an Rd_FIFO module (read FIFO module) and a Wr_FIFO module (write FIFO module) . The AHB interface system for stream data transmission is applied to the field of integrated circuits.

Owner:HARBIN UNIV OF SCI & TECH

Pipeline magnetic flux leakage detection system and data acquisition device and method

ActiveCN106770623AHigh speed transmissionReal-time transmissionMaterial magnetic variablesSupply managementData acquisition

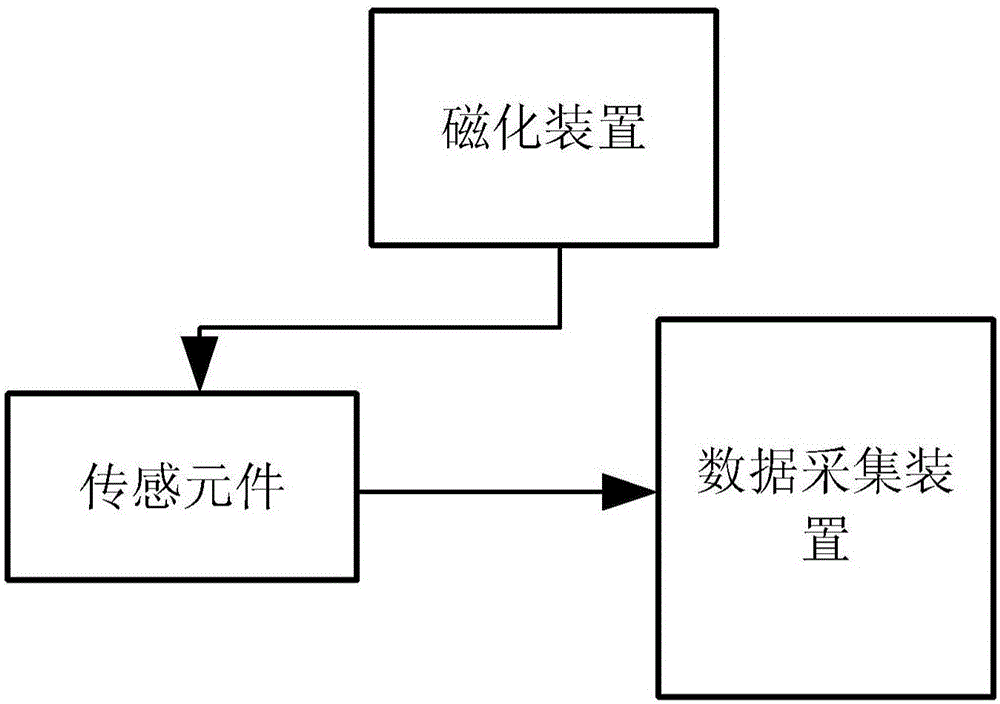

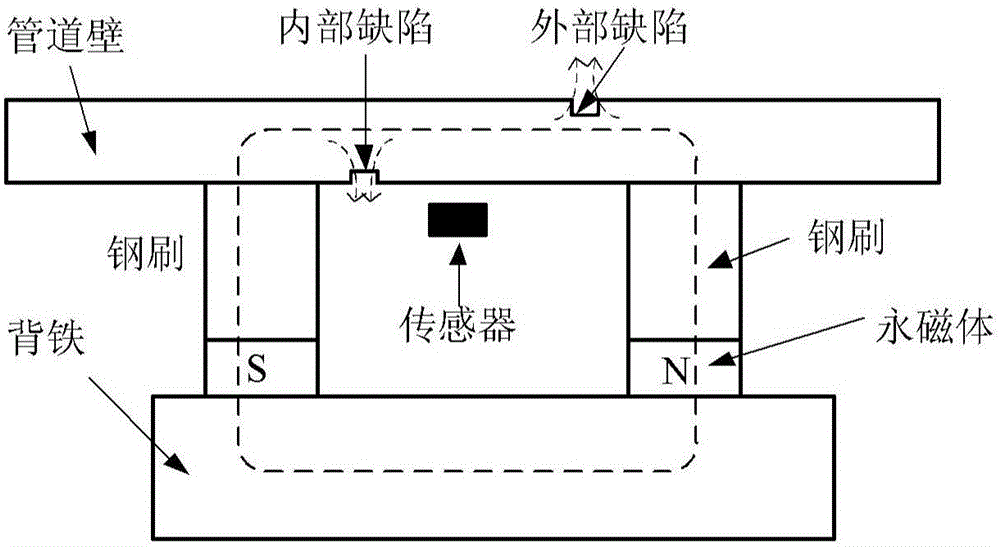

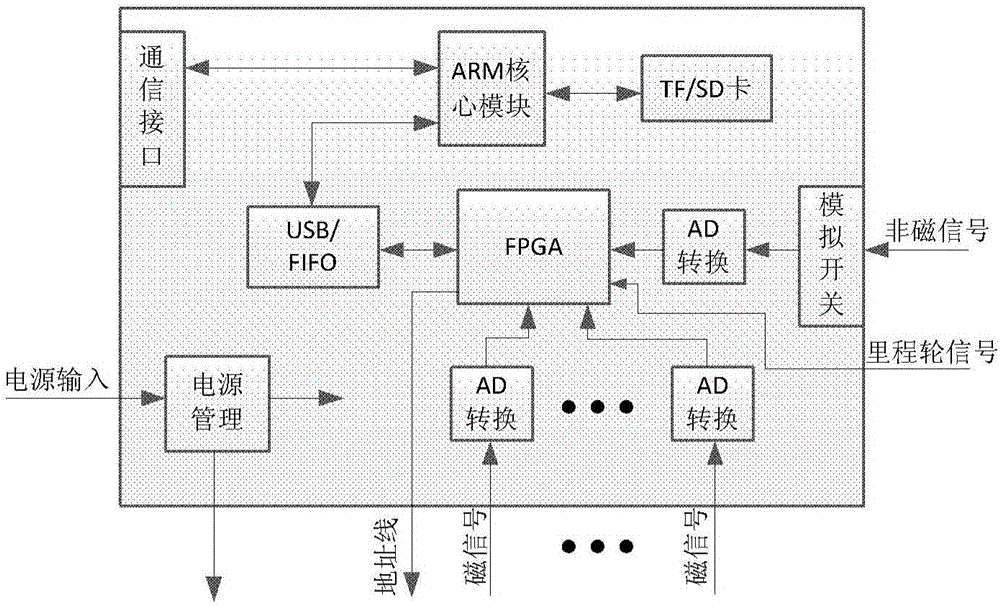

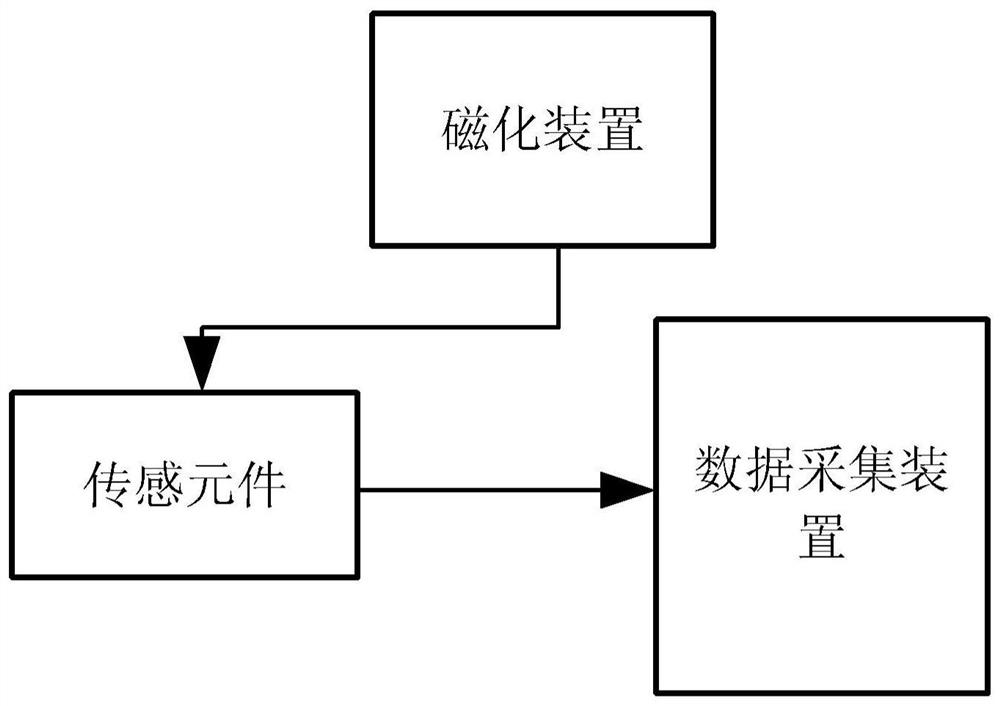

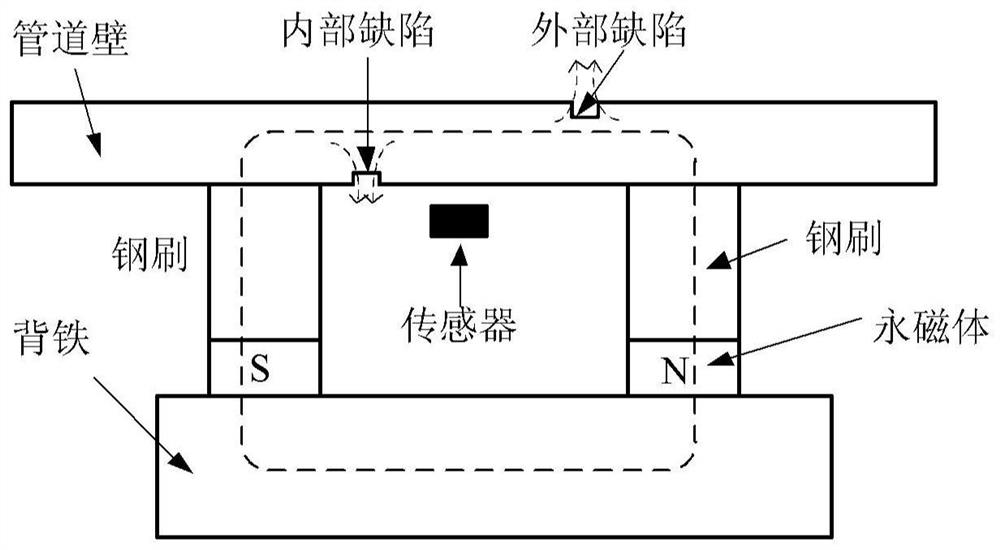

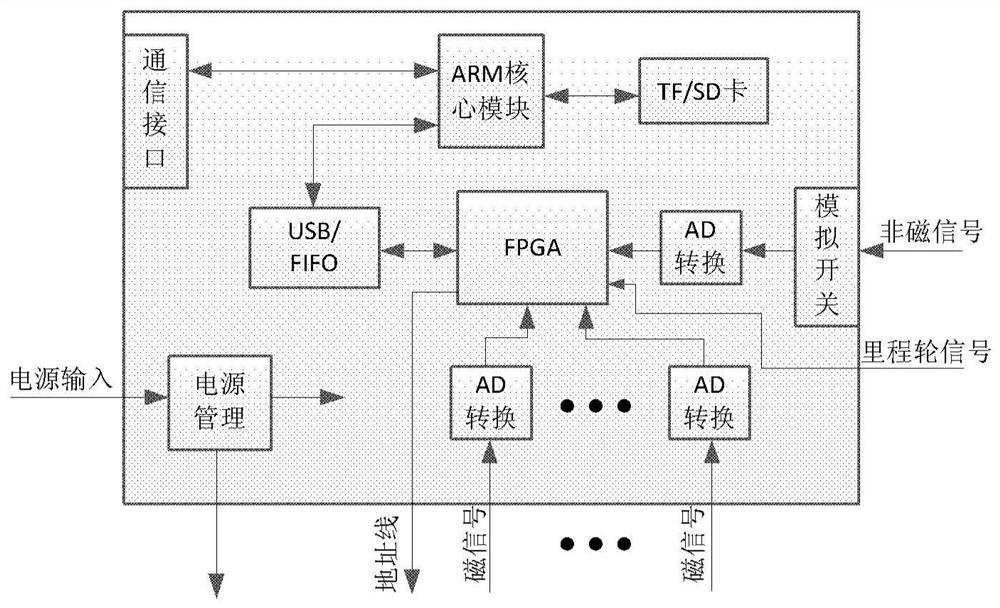

The invention provides a pipeline magnetic flux leakage detection system and a data acquisition device and method. The pipeline magnetic flux leakage detection system comprises a magnetizing device, a sensing member and the data acquisition device, wherein the sensing element is used for detecting a magnetic signal which is a magnetic flux leakage signal of a magnetic field; the data acquisition device comprises an ARM core module, a storage medium, an FPGA, an AD conversion device, a USB / FIFO conversion device and a power supply management module; the ARM core module is used for storing data acquired by the FPGA to the storage medium; the AD conversion device is used for performing analog-to-digital conversion on the magnetic signal received from the sensing member; the FPGA is used for transmitting the acquired magnetic data to the ARM core module through the USB / FIFIO conversion device according to the magnetic data acquired by the magnetic signal through compression; and the USB / FIFIO conversion device is used for data transmission between the ARM core module and the FPGA.

Owner:CHINA SPECIAL EQUIP INSPECTION & RES INST

Service interface processing device and method

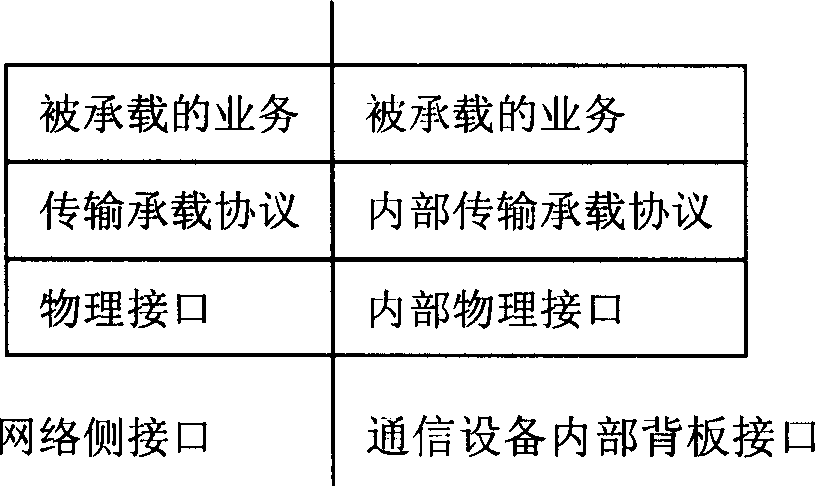

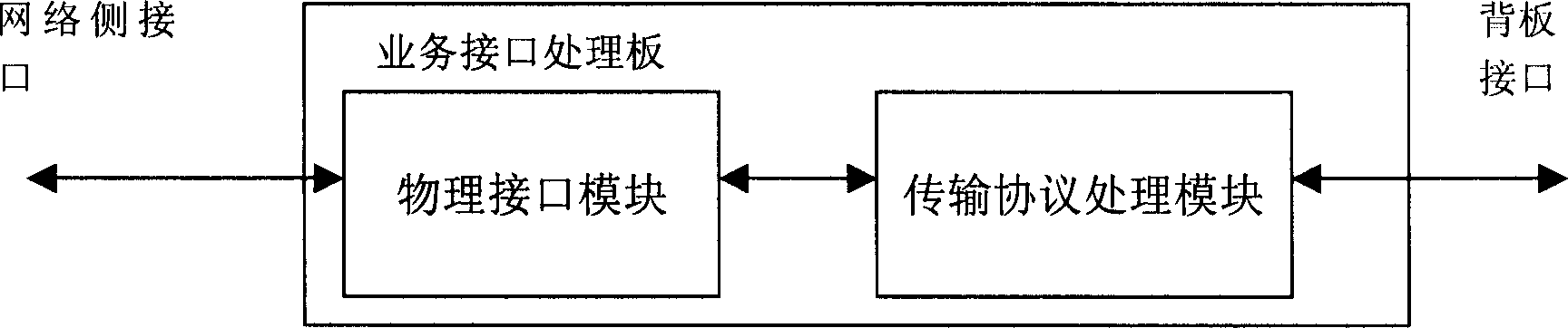

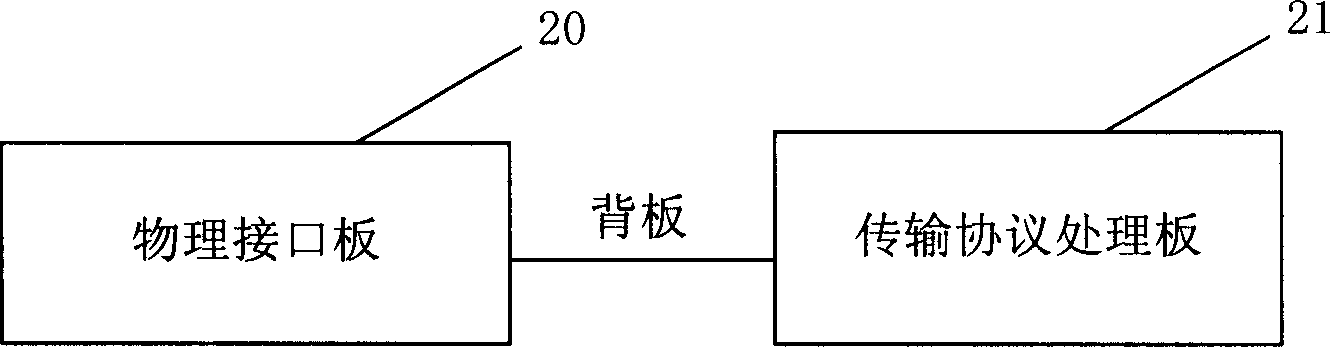

ActiveCN1791121ASimplify interface designMeeting the Needs for Variety and Development SpeedTransmissionBusiness dataPhysical interface

The invention discloses a treatment device for business interface, which comprises: a physical interface board to treat the business data between communication device and external network, and a transmission protocol treatment board connected to former board by a back board to treat the business data treated by former board according to its transmission protocol and obtain need business data or package the business data to be transmitted according to its transmission protocol to transmit to external network by former board. This invention just needs to exploit again the opposite software when protocol changes to meet market request for diversity and exploit speed.

Owner:HUAWEI TECH CO LTD

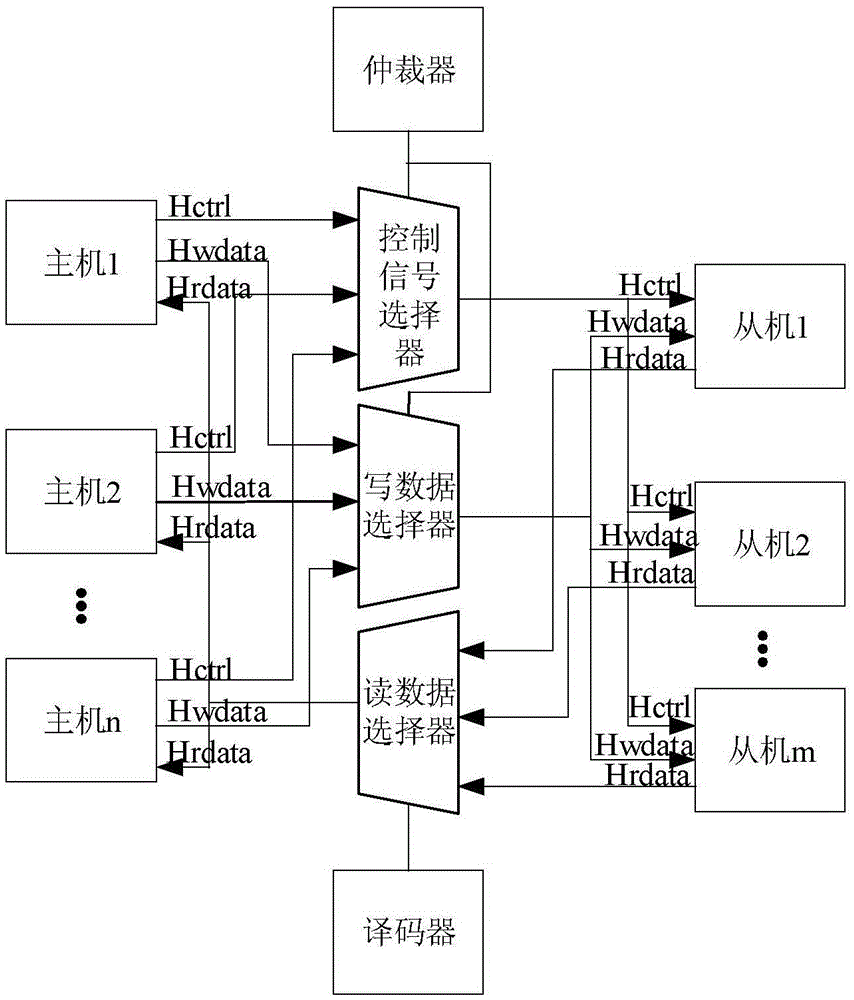

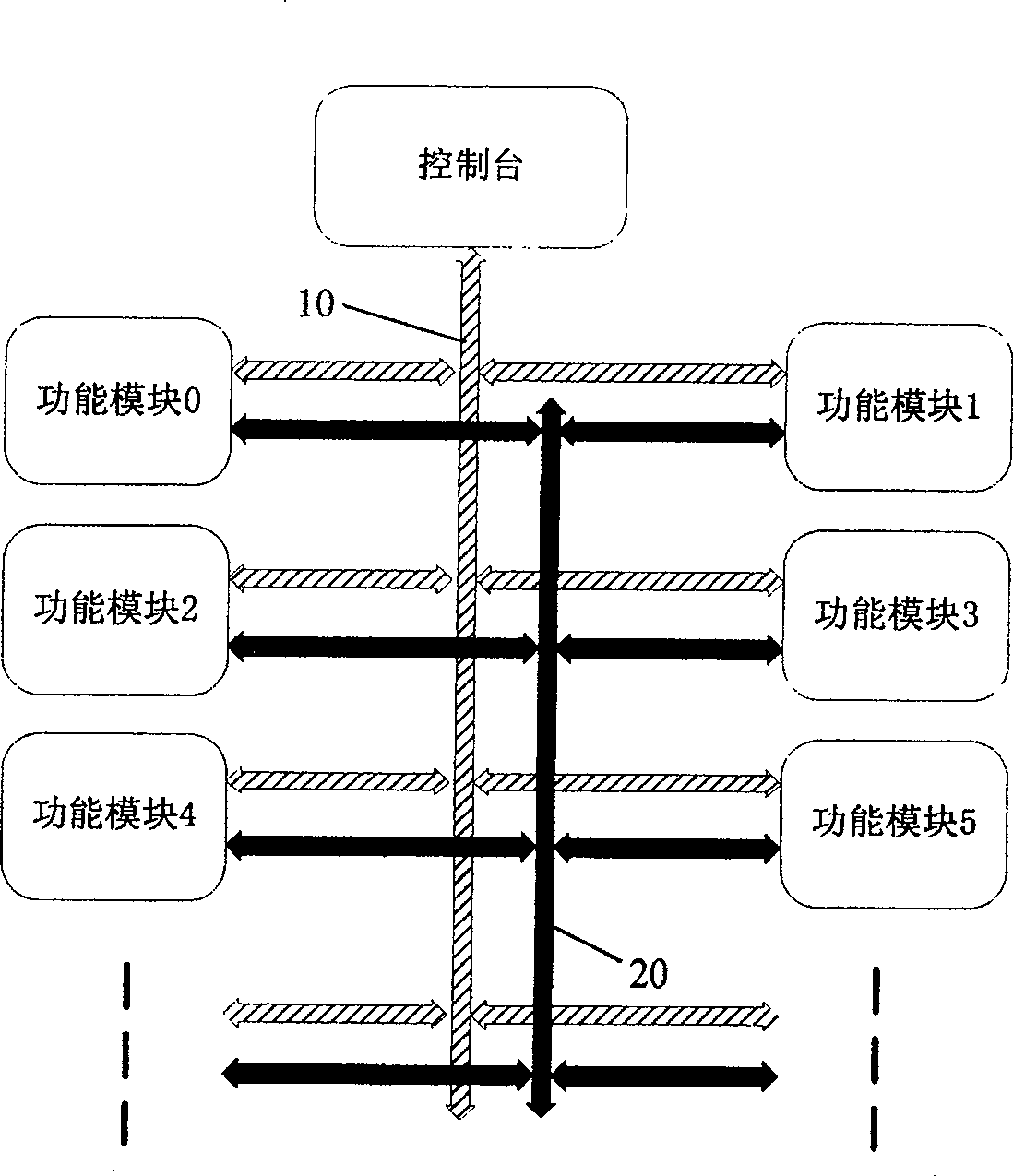

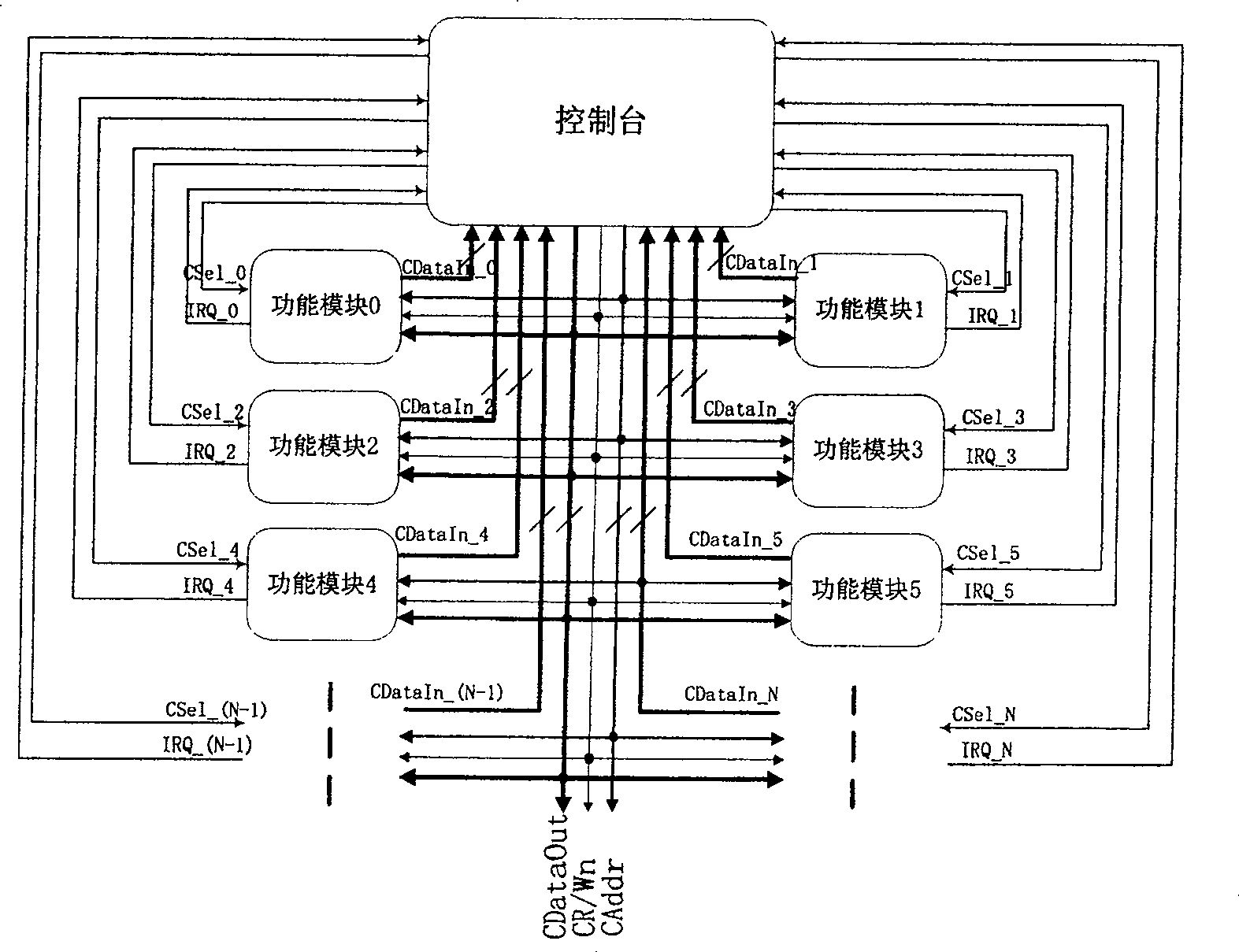

On-chip system

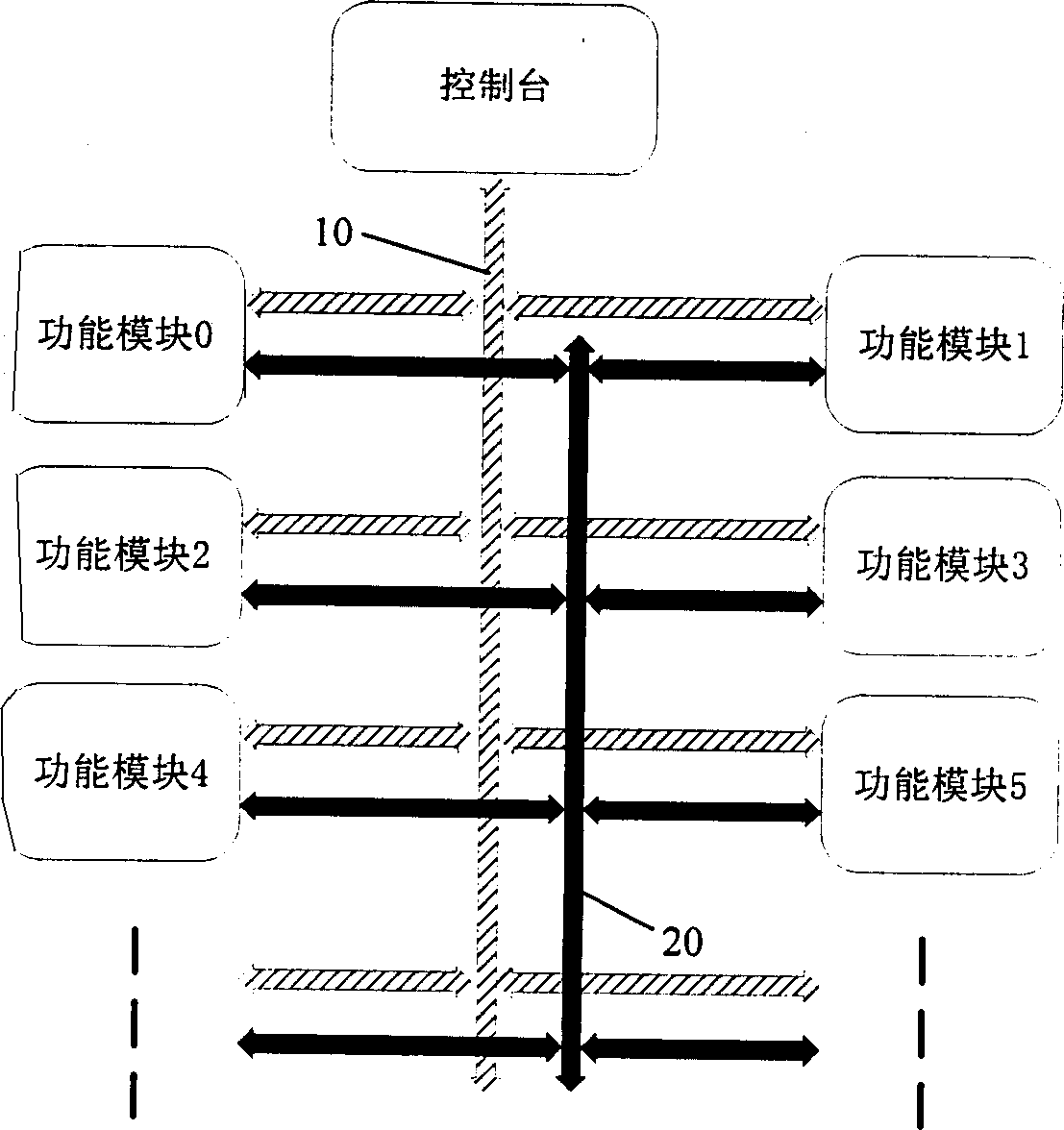

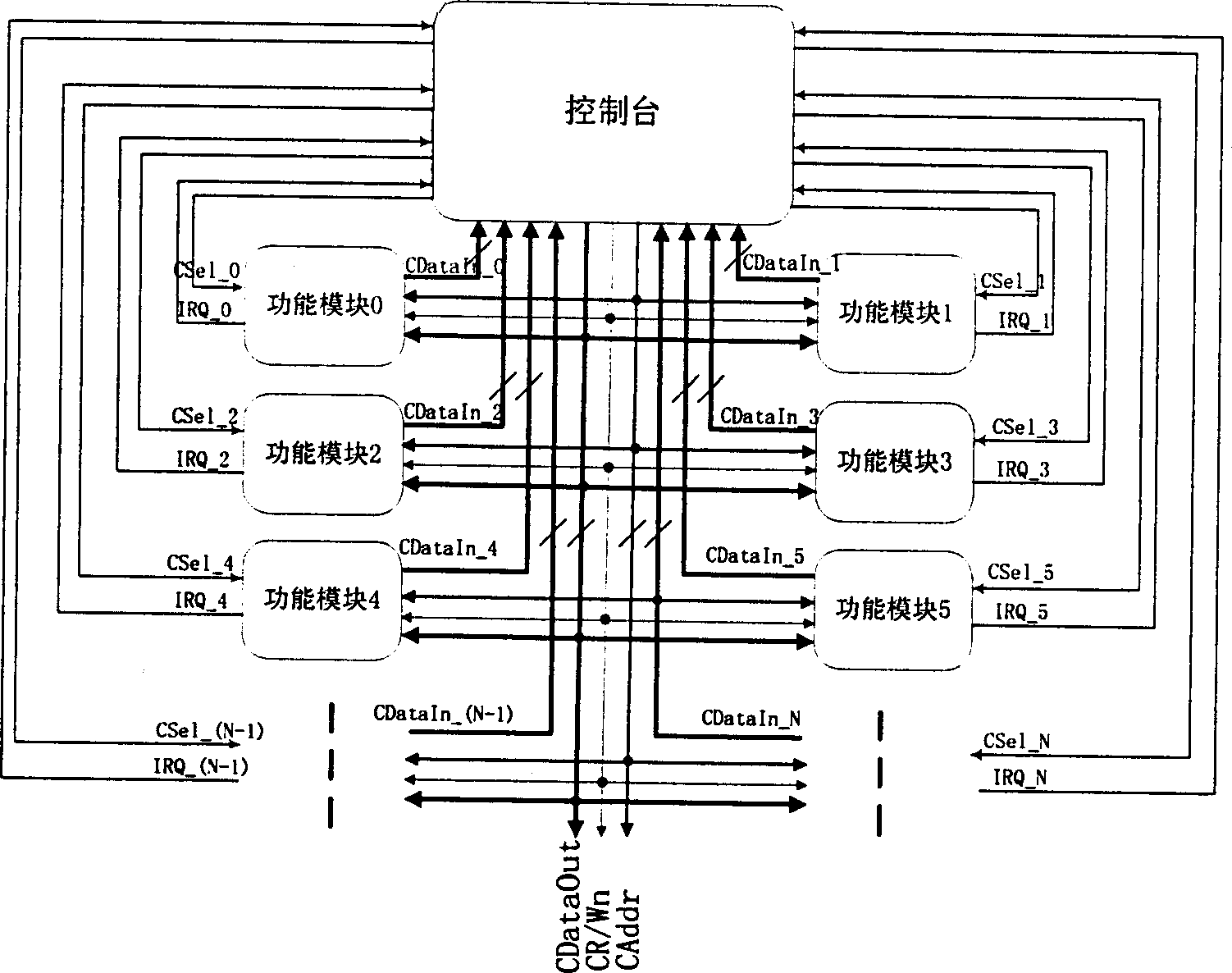

ActiveCN1783044ASimplify interface designSuitable designElectric digital data processingEmbedded systemInterface design

The on-chip system includes several functional modules connected with internal bus including two independent transmission channels, including one control / state channel for transmitting control / state information and one data channel for transmitting other data except control / state information. Each of the control / state channel and the data channel has separate data bus, address bus and control bus. The kernel of the present invention is to design on-chip system bus in the strategy of separate control / state channel and data channel, which have different topologic structures and communication protocols. The present invention has greatly simplified interface design of functional modules inside the system and increased total system communication bandwidth, and is especially suitable for on-chip system design with compact data interaction.

Owner:SUGON INFORMATION IND

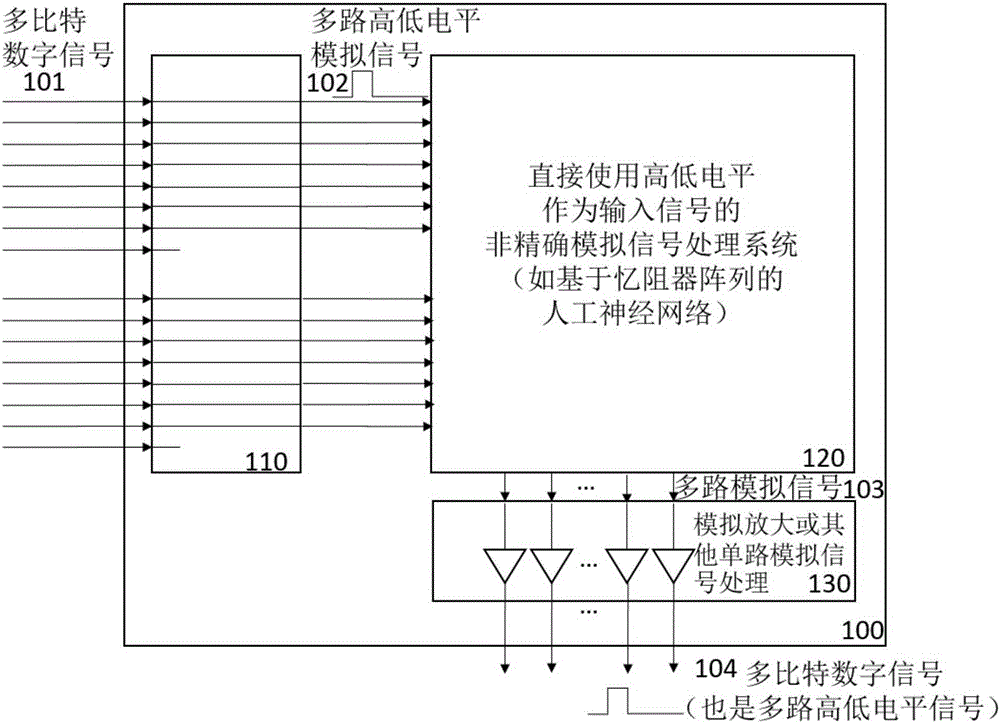

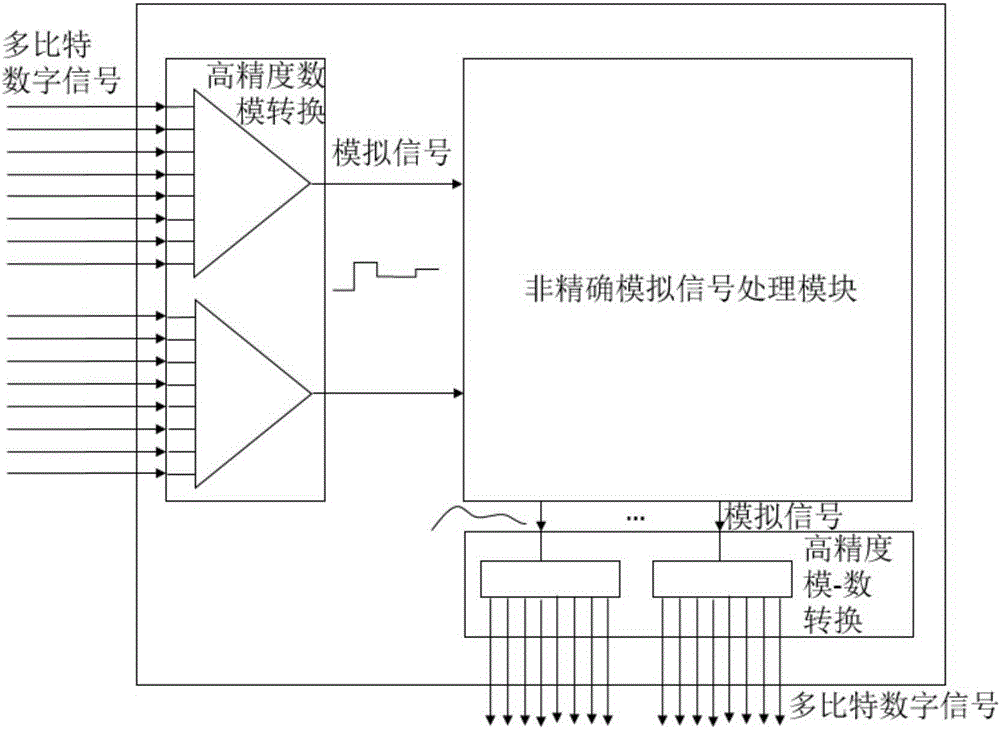

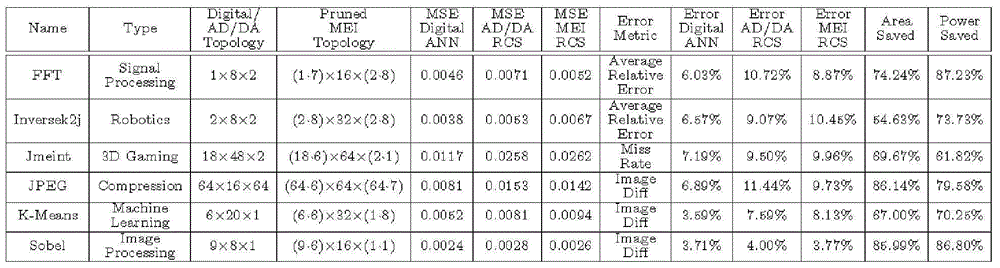

Digital-analog mixed signal processing system for imprecise computation

ActiveCN105184365AReduced area and power overheadSimplify interface designPhysical realisationInterface designDigital input

The invention discloses a digital-analog mixed signal processing system for imprecise computation, comprising an input module used for decomposing A B-bit digital input signals into A*B single-bit high- and low-level signals and sending the high- and low-level signals to a signal processing module as analog input signals, the signal processing module used for calculating the analog input signals to obtain C analog output signals and sending the analog output signals to an output module, and the output module used for converting the analog output signals into D high- and low-level signals and outputting the D high- and low-level signals as E F-bit digital signals, wherein D, E and F are natural numbers, and D=E*F. The digital-analog mixed signal processing system for imprecise computation has the advantages as follows: the area and power consumption of a computing system on a conversion interface are reduced effectively, and interface design is greatly simplified; and the area is reduced by more than 50%, the energy consumption is reduced by more than 60%, and the application space of the system of the type is significantly improved.

Owner:TSINGHUA UNIV

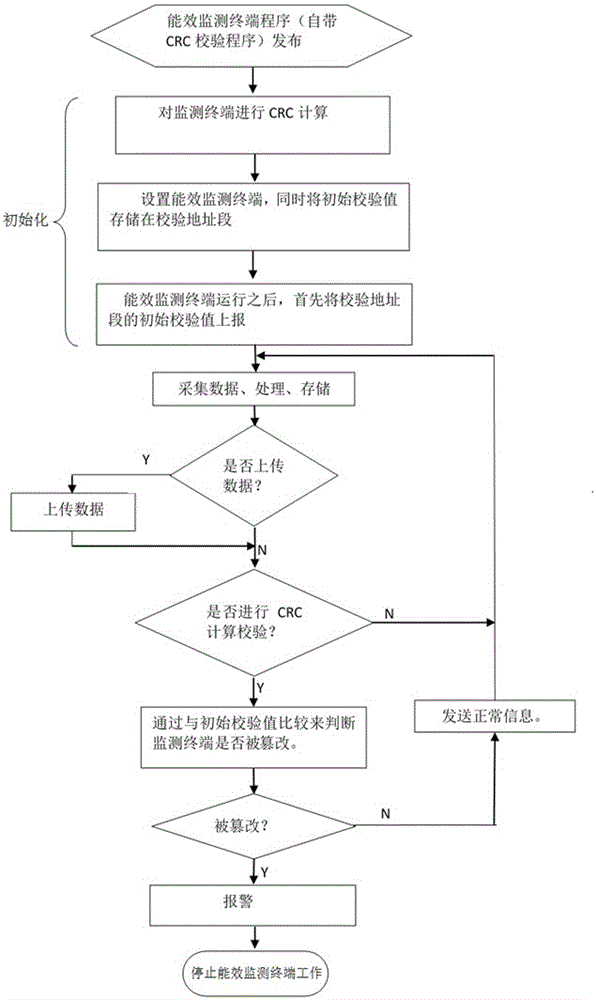

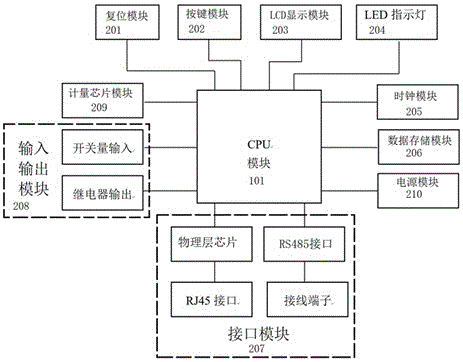

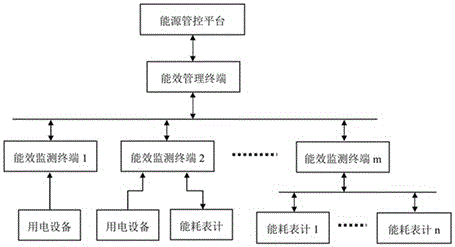

Security energy efficiency monitoring terminal based on tamper-proof technology and monitoring method of security energy efficiency monitoring terminal

InactiveCN105844901AGuaranteed accuracyEnsure safetyTransmission systemsTamper resistanceData acquisition

The invention relates to a security energy efficiency monitoring terminal based on a tamper-proof technology and a monitoring method of the security energy efficiency monitoring terminal, and belongs to the field of energy efficiency monitoring and management. According to the monitoring method, due to three steps of initialization, data acquisition and verification, the accuracy of energy efficiency data acquisition is guaranteed; the monitoring terminal performs CRC calculation, compares whether a CRC calculation result is matched with an initial verification value to judge whether data are maliciously tampered, so as to guarantee the security of energy efficiency data. By the adoption of a dynamic tamper-proof technology, CRC calculation verification is conducted regularly, and the result is submitted for system networking verification. Once a program is found to be tampered, a user calls the police immediately and ends the operation of the terminal. The security energy efficiency monitoring terminal can be effectively prevented from being illegally tampered when guaranteeing the accuracy and the instantaneity of the energy efficiency data. The shortcoming of low information security of the conventional monitoring terminal is overcome.

Owner:ELEFIRST SCI & TECH +1

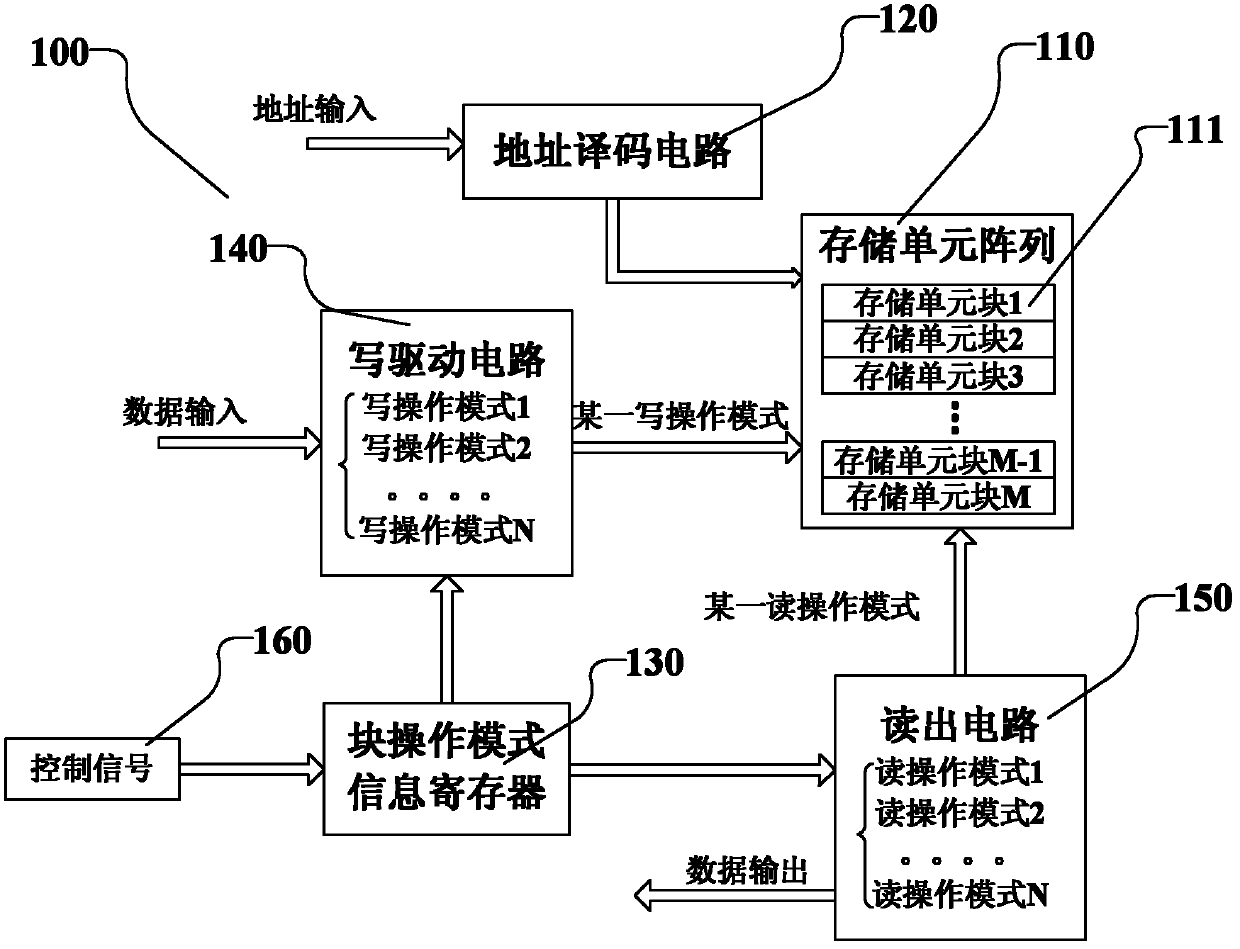

Non-volatile random access memory and operation method thereof

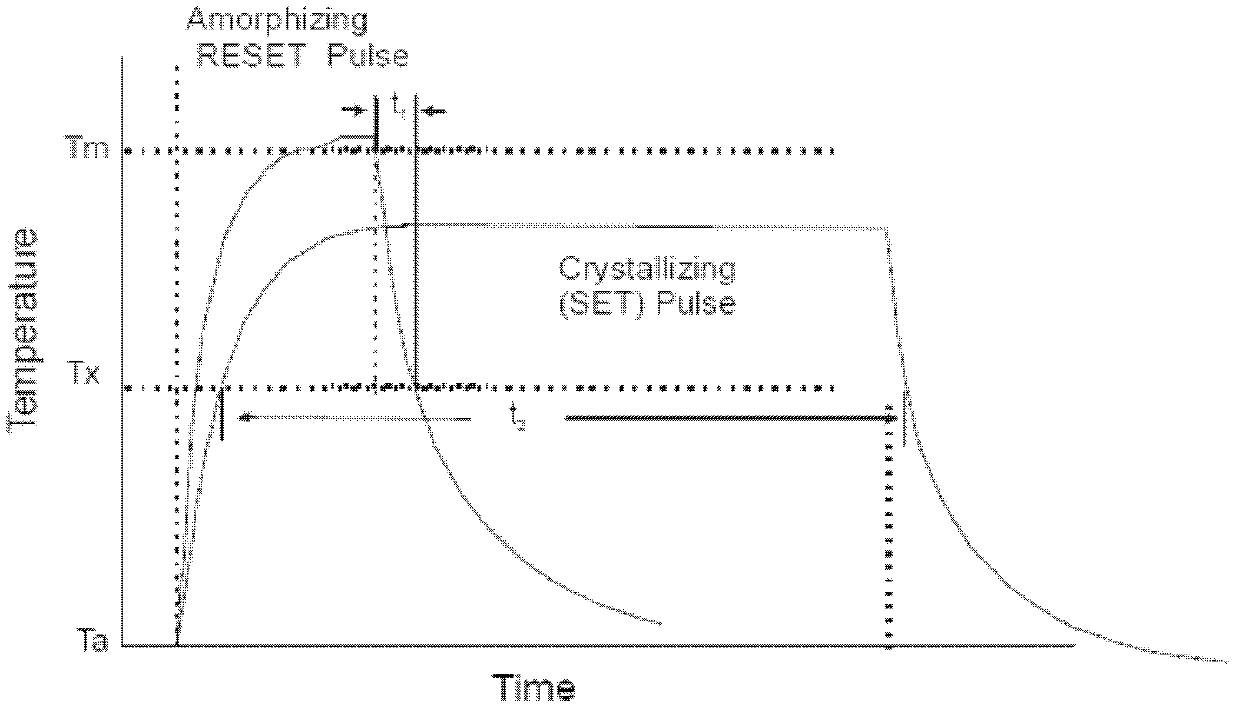

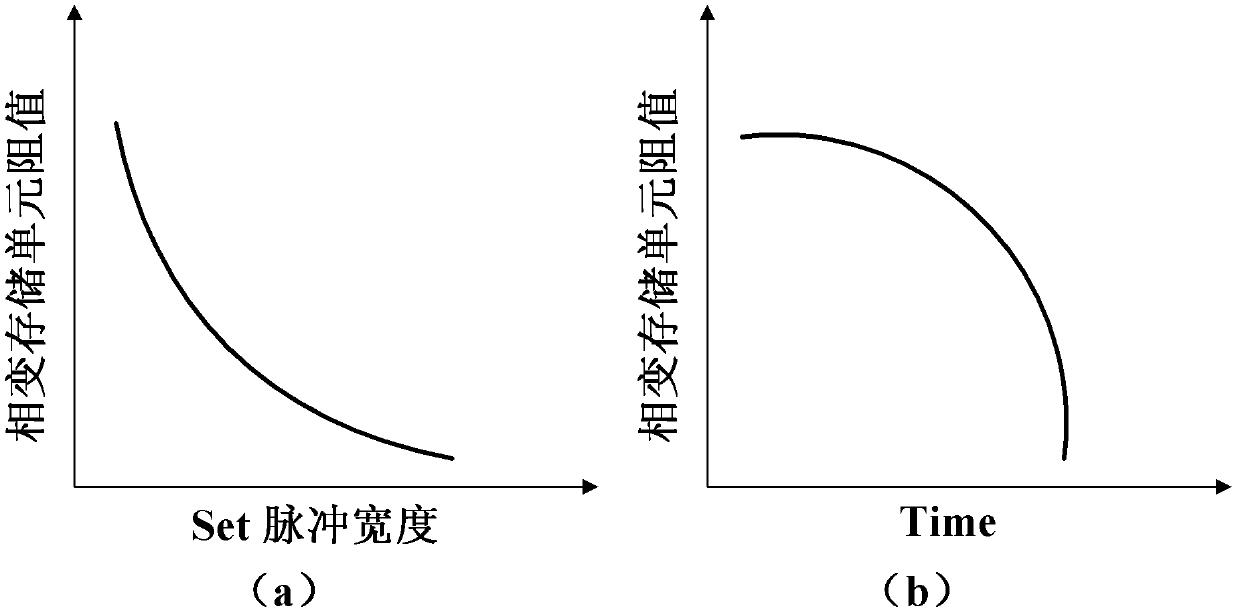

ActiveCN102890963AMeet different needsHigh speedRead-only memoriesDigital storageComputer architecturePhase-change memory

The invention provides a non-volatile random access memory (100) and an operation method thereof. The non-volatile random access memory (100) comprises a memory cell array (110) composed of multiple memory cell blocks (111), and a peripheral circuit connected to the memory cell array (110). The peripheral circuit comprises an address decoding circuit (120) for selecting the corresponding memory cell block according to address input information, a block operation-mode information register (130) for storing operation mode information of all the memory cell blocks (111) and carrying out re-writing under the action of a control signal (160), a writing driving circuit (140) for outputting a writing operation mode to the memory cell array (110) according to the operation mode information stored in the block operation-mode information register (130), and a reading circuit (150) for outputting a reading operation mode to the memory cell array (110) according to the operation mode information stored in the block operation-mode information register (130). The non-volatile random access memory is compatible with two phase change memories having different operation modes, simplifies an interface design, saves a design area, reduces power consumption and improves a speed.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

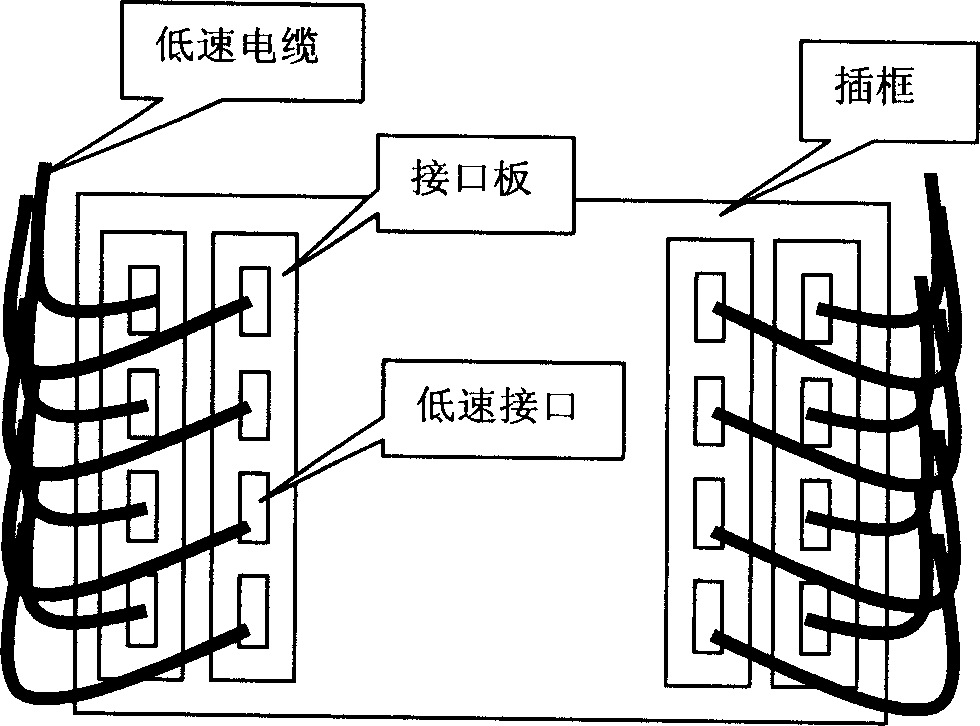

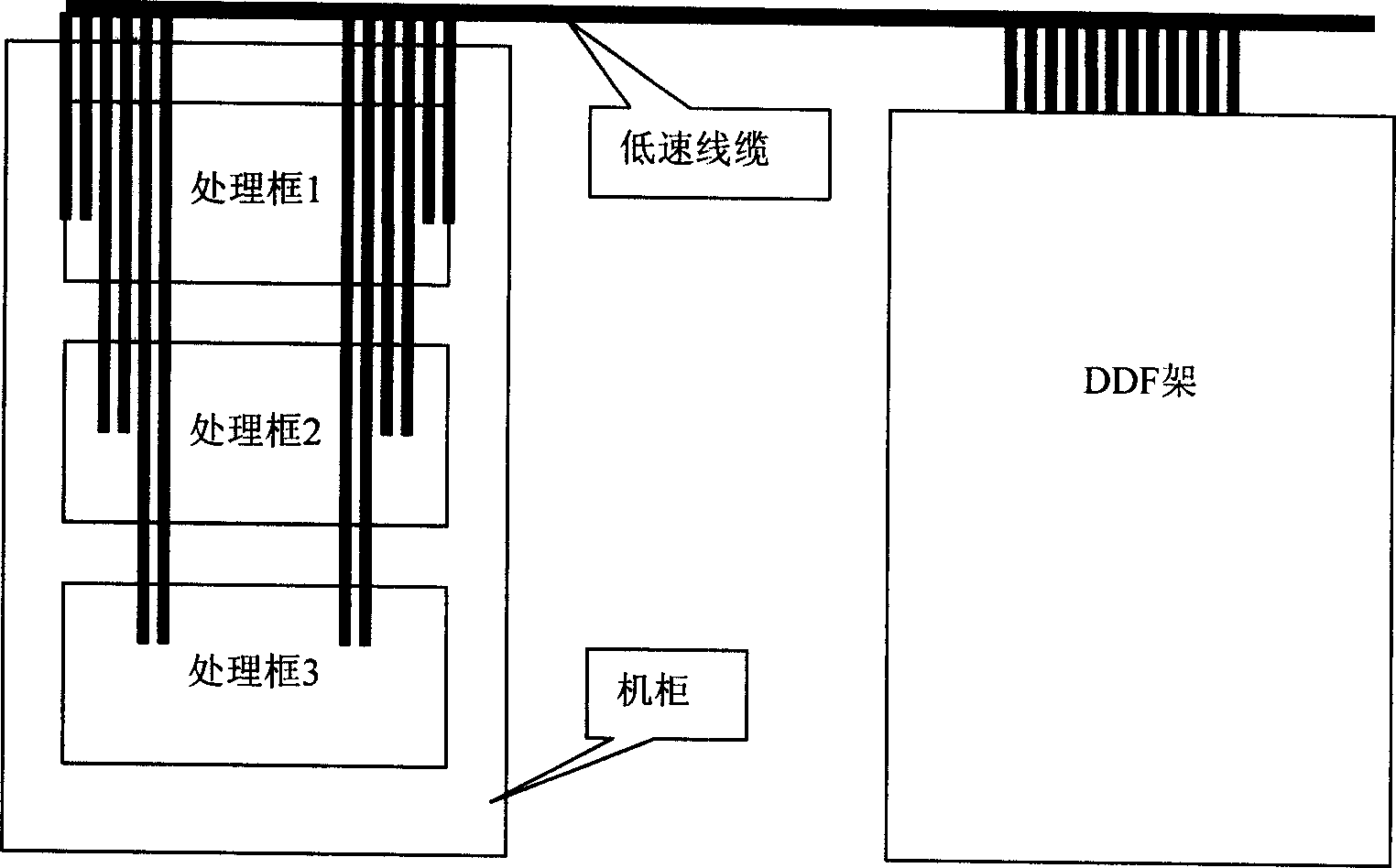

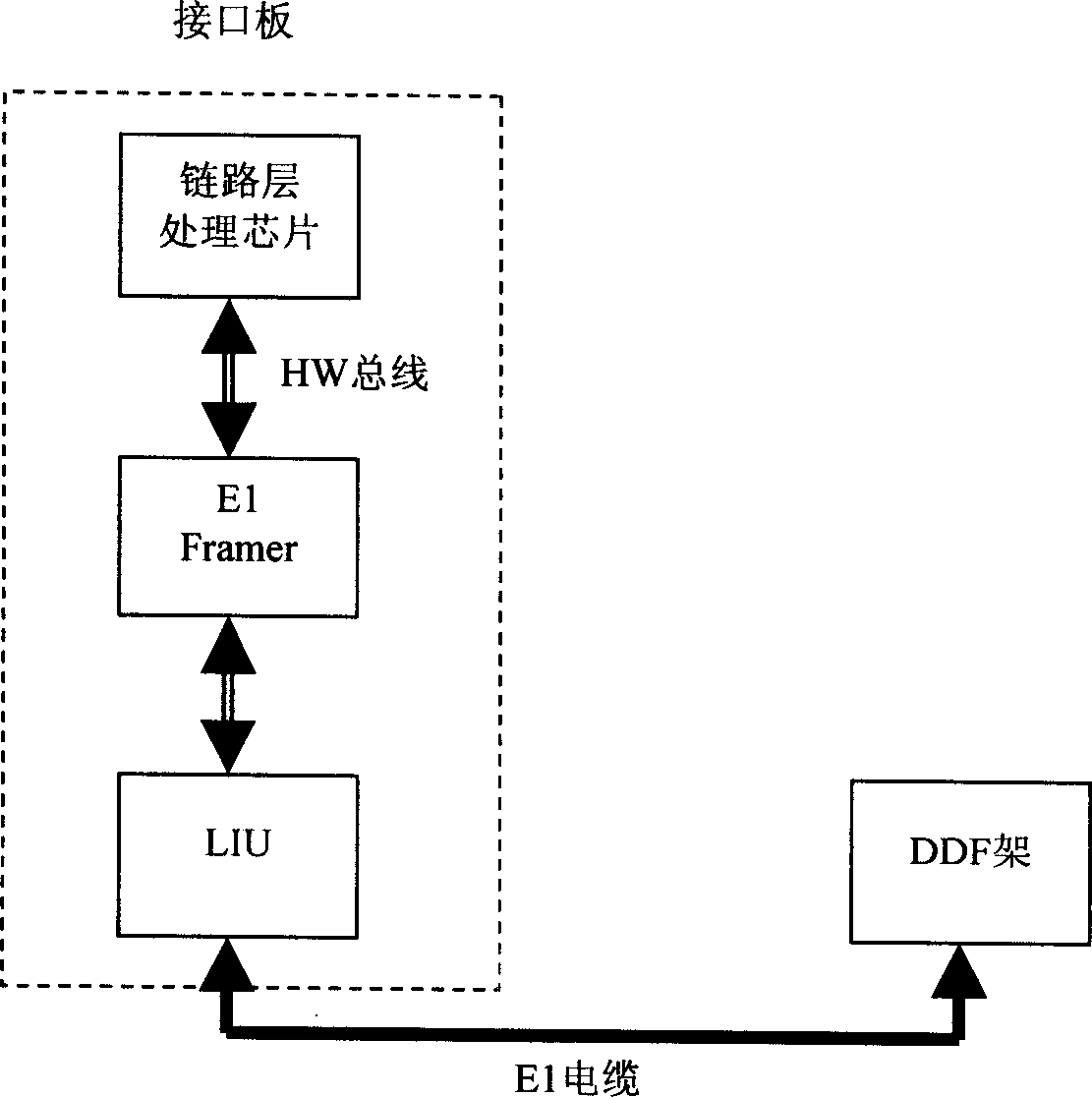

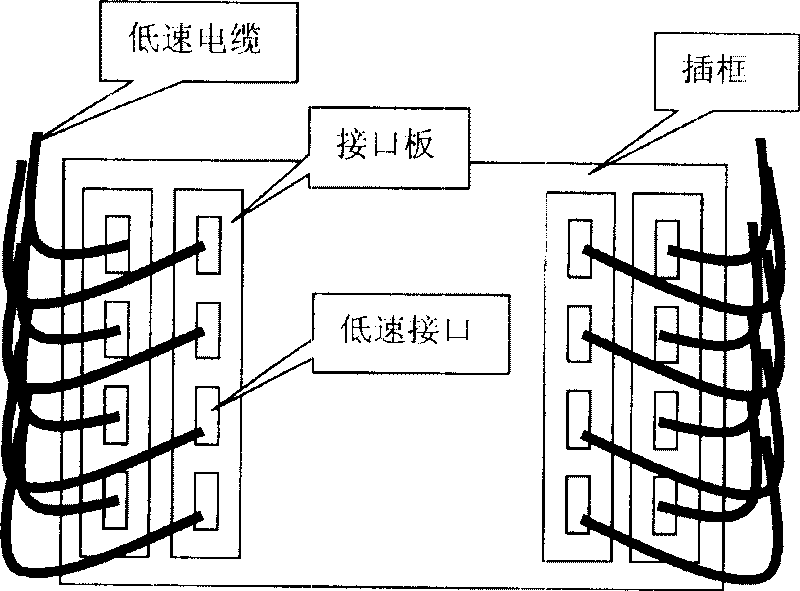

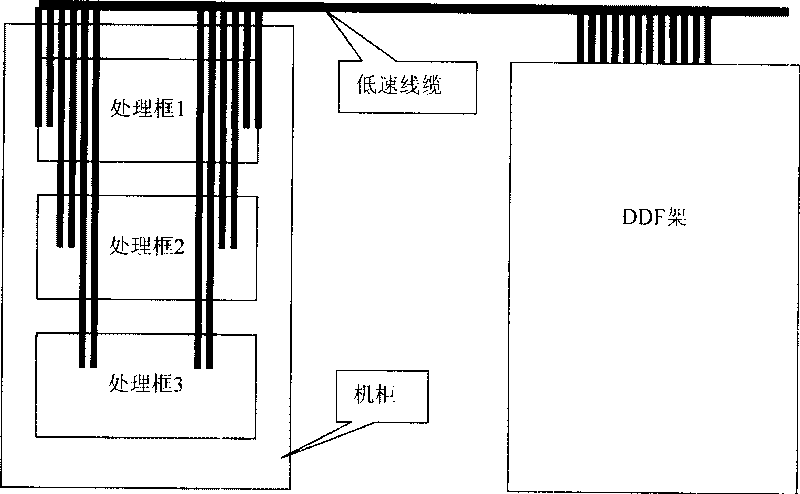

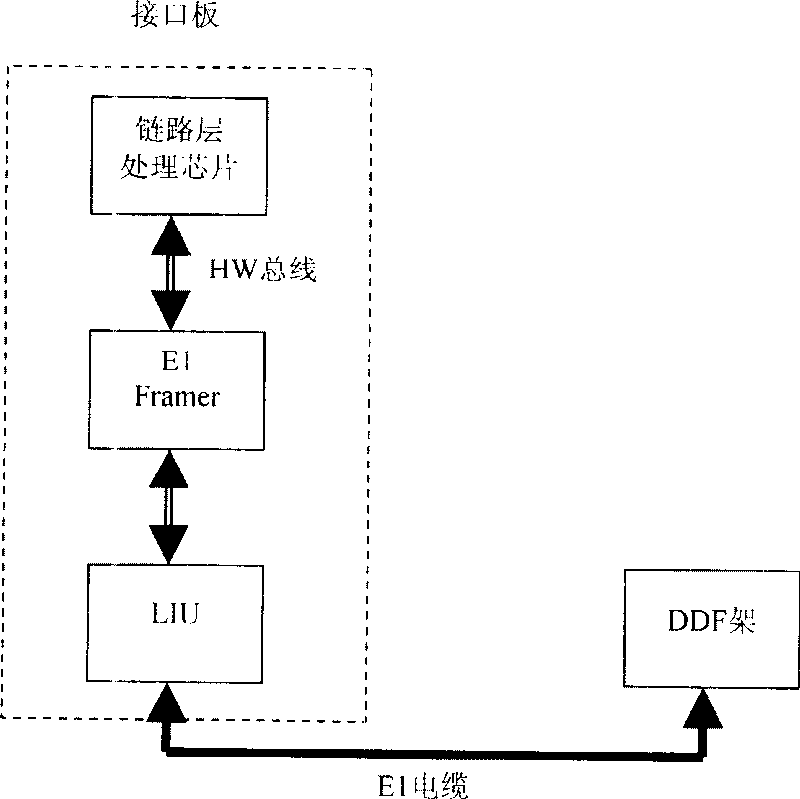

Low-speed chain circuit data transmission apparatus and method in telecommunication apparatus

ActiveCN1866970ASimplify interface designImprove reliabilityTime-division multiplexTransmissionData transmissionInterface design

The invention relates to a data transmitter in low-speed chain circuit and relative method. Wherein, said device comprises a low-speed chain circuit interface frame, a service processing frame, and a DDF support; said method comprises: the service data of service processing frame via high-speed chain circuit is transmitted to the low-speed chain circuit interface frame; the low-speed chain circuit interface frame processes said bus data to be transmitted to the DDF support via low-speed chain circuit. With said invention, the interface design of service processing frame can be simplified to improve the reliability of telecommunication equipment.

Owner:HUAWEI TECH CO LTD

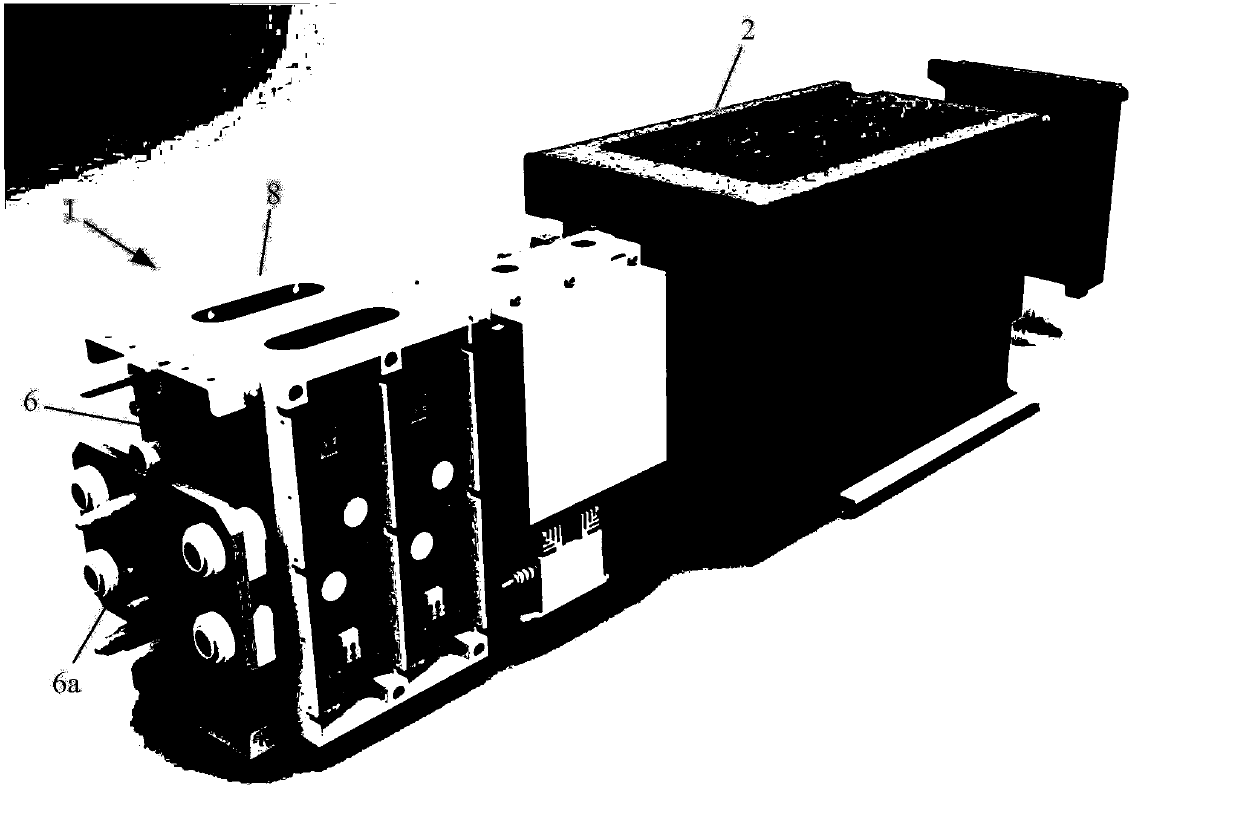

A high voltage module for power electronic traction transformer

ActiveCN110890831ACompact structureGuaranteed isolationPrinted circuit board receptaclesCooling/ventilation/heating modificationsThermodynamicsBusbar

The invention provides a high-voltage module for a power electronic traction transformer, and the high-voltage module comprises: an insulating housing, wherein the upper, lower, left and right surfaces of the insulating housing are all closed, at least one part of the rear surface is an open surface, and the outer side edges of the front surface and the rear surface are respectively provided witha concentric-square-shaped groove structure; an internal frequency conversion machine core, wherein the internal frequency conversion machine core and the insulating shell are of a nested structure, and the internal frequency conversion module at least comprises a water-cooling heat dissipation assembly, an IGBT assembly, a busbar, a driving assembly, a direct-current capacitor, a control part anda water-electricity integrated rapid plug-pull connector, the water-electricity integrated rapid plug-pull connector is led out from the rear surface, the water-cooling heat dissipation assembly is located in the middle of the high-voltage module and divides high-voltage module into a left area and a right area, cascade side high-voltage IGBTs and inversion side high-voltage IGBTs in the IGBT assembly are arranged on the two sides of the water-cooling heat dissipation assembly respectively, and the IGBT assembly, the busbar and the IGBT driving assembly are sequentially arranged outwards fromthe left side to the right side of the water-cooling heat dissipation assembly.

Owner:CSR ZHUZHOU ELECTRIC LOCOMOTIVE RES INST

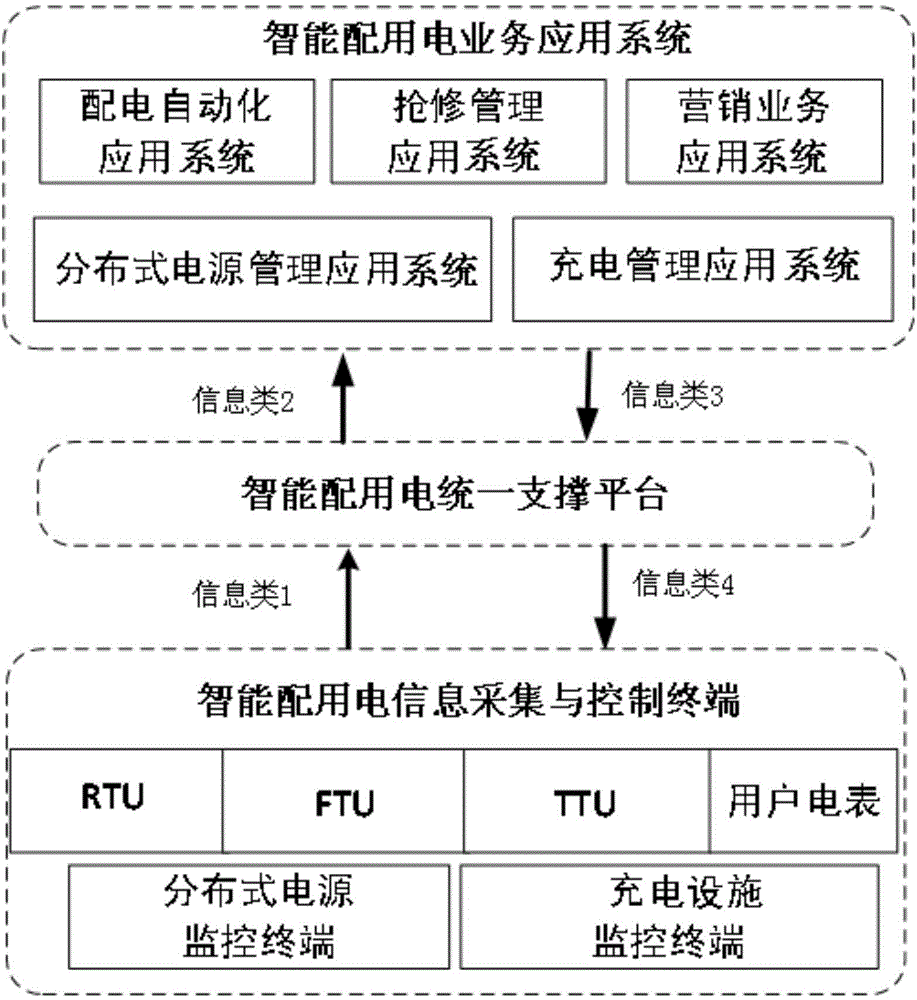

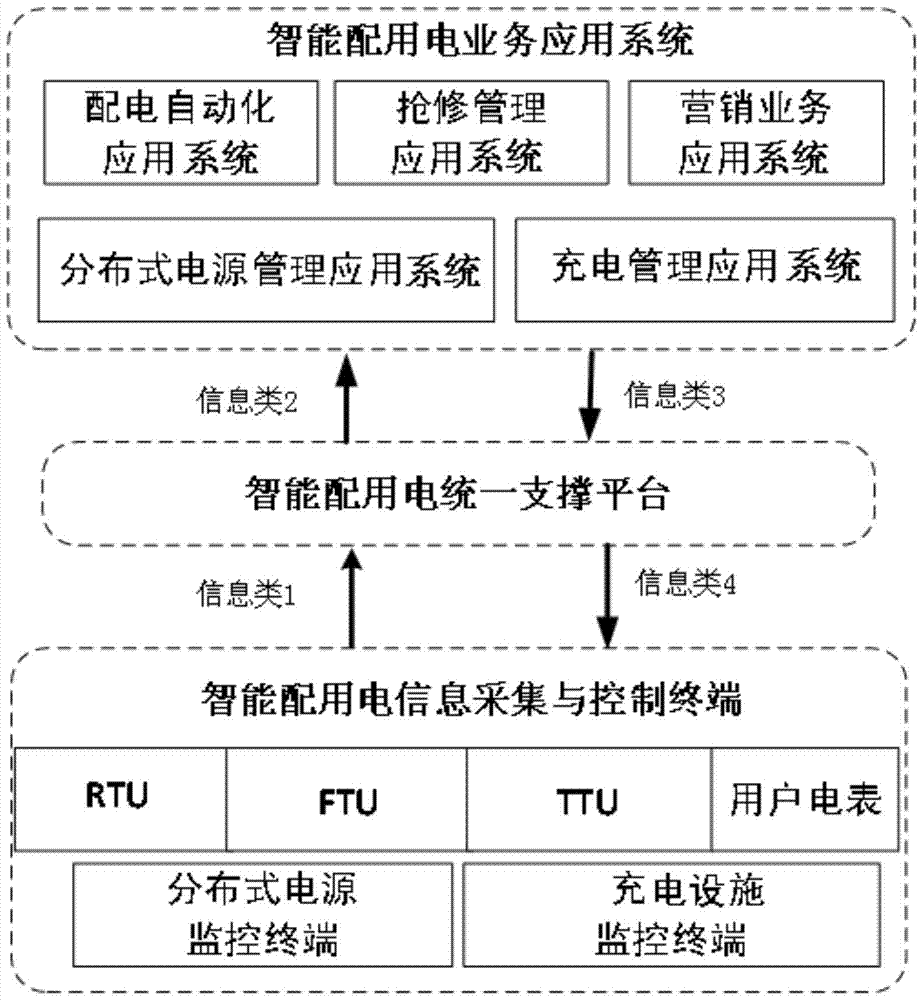

Integrative information interaction method for intelligent power distribution and utilization

ActiveCN104953706AImprove interaction efficiencyEliminate data heterogeneityCircuit arrangementsData informationKnowledge management

The invention discloses an integrative information interaction method for intelligent power distribution and utilization. Data information of various types is collected to form an information class 1, which is sent to an intelligent power distribution and utilization unified supporting platform. Information in the information class 1 is analyzed and verified and is converted to another format by the intelligent power distribution and utilization unified supporting platform, so as to form an information class 2 which is sent to intelligent power distribution and utilization business application systems. Information that is needed is extracted from the information class 2 and is utilized to form control decision information. The control decision information formed by all the business application systems is sent, as an information class 3, to the intelligent power distribution and utilization unified supporting platform. Information in the information class 3 is analyzed and classified in order to form, in accordance with the classification, an information class 4 which is sent to intelligent power distribution and utilization information acquisition and control terminals. Information that is needed is extracted from the information class 4 by each terminal and is utilized. The invention realizes information interaction and compatibility of different business application systems.

Owner:STATE GRID CORP OF CHINA +5

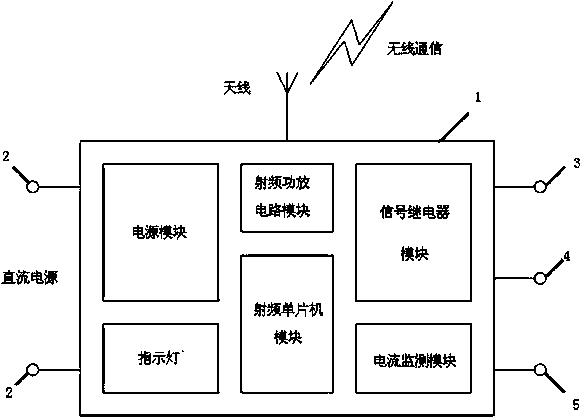

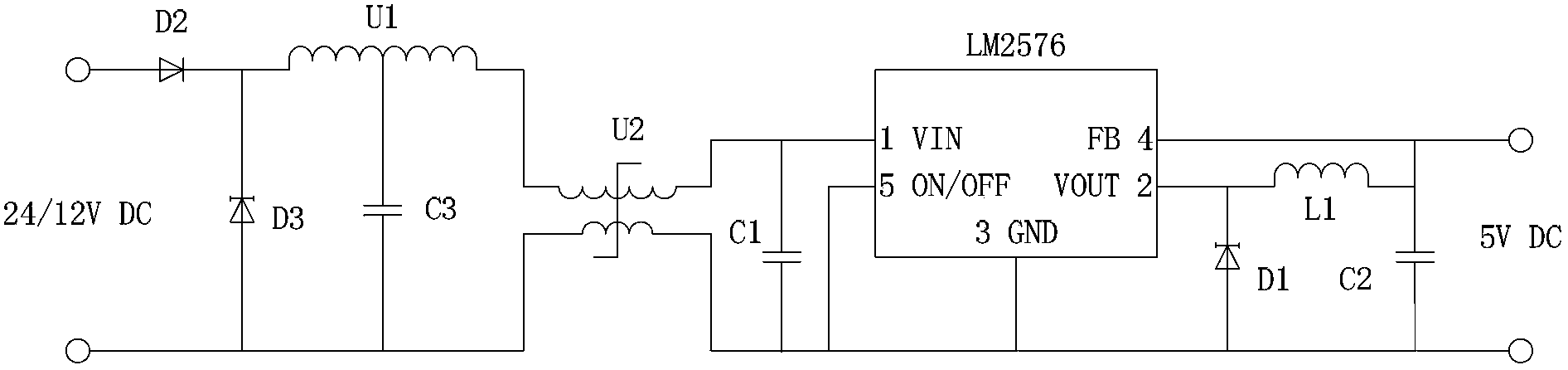

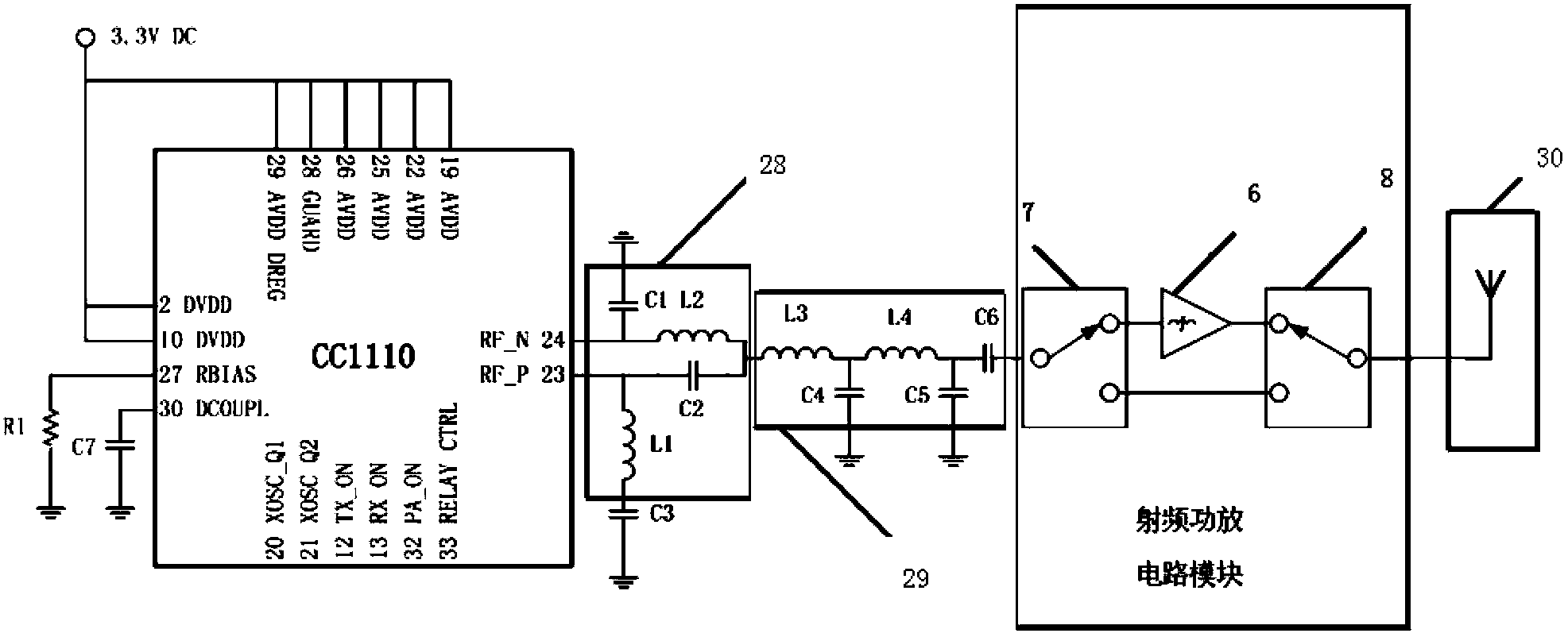

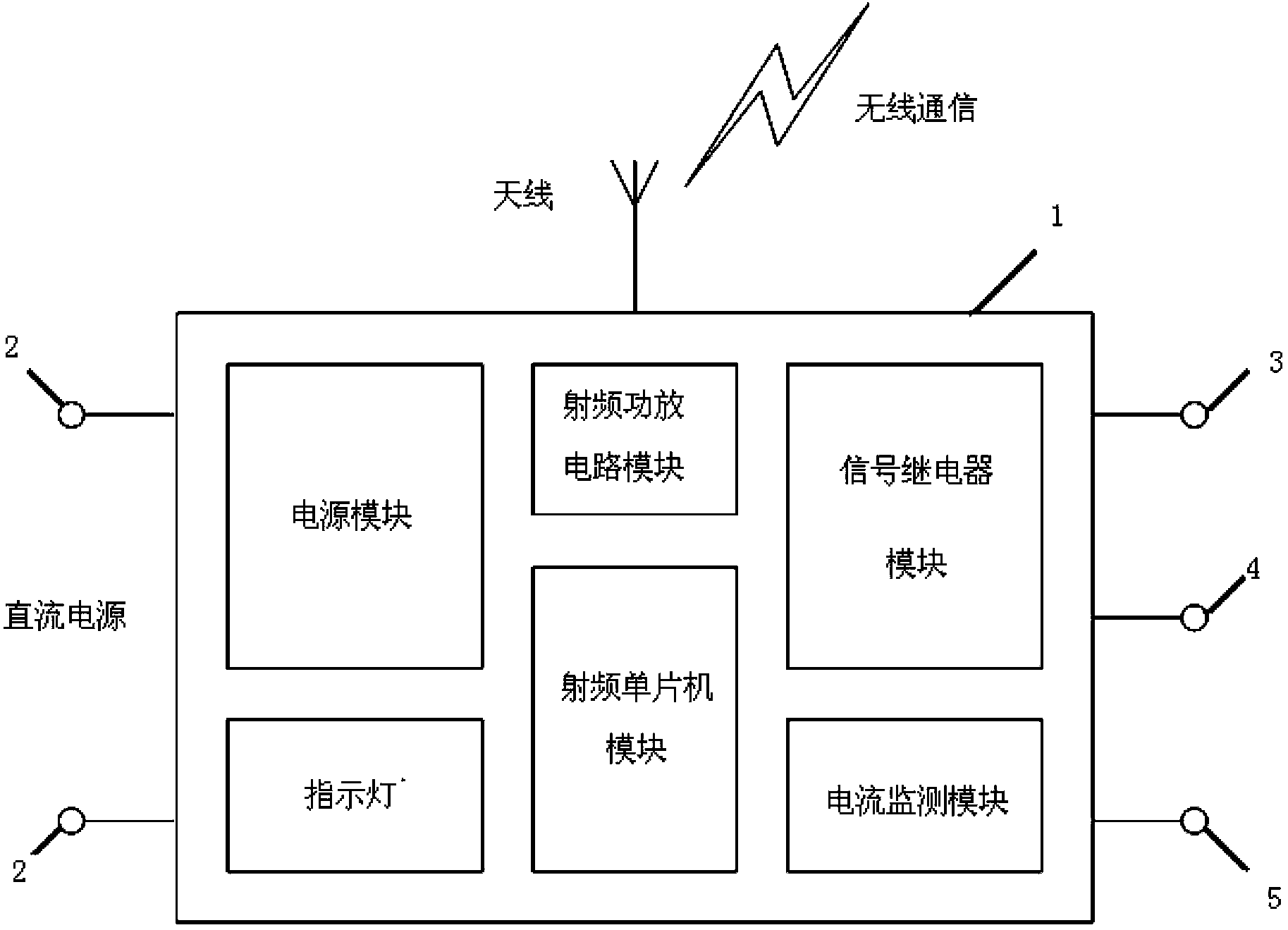

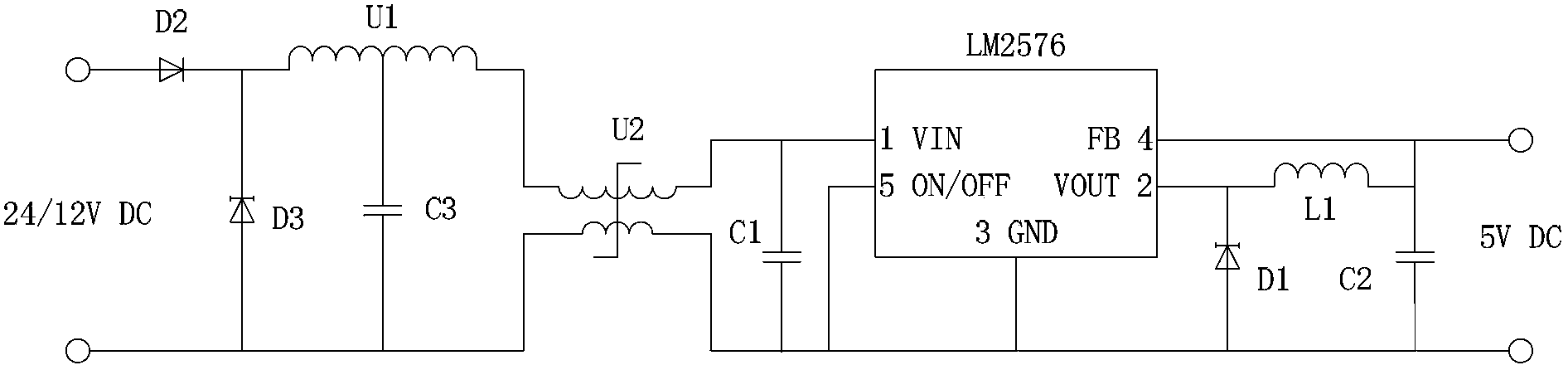

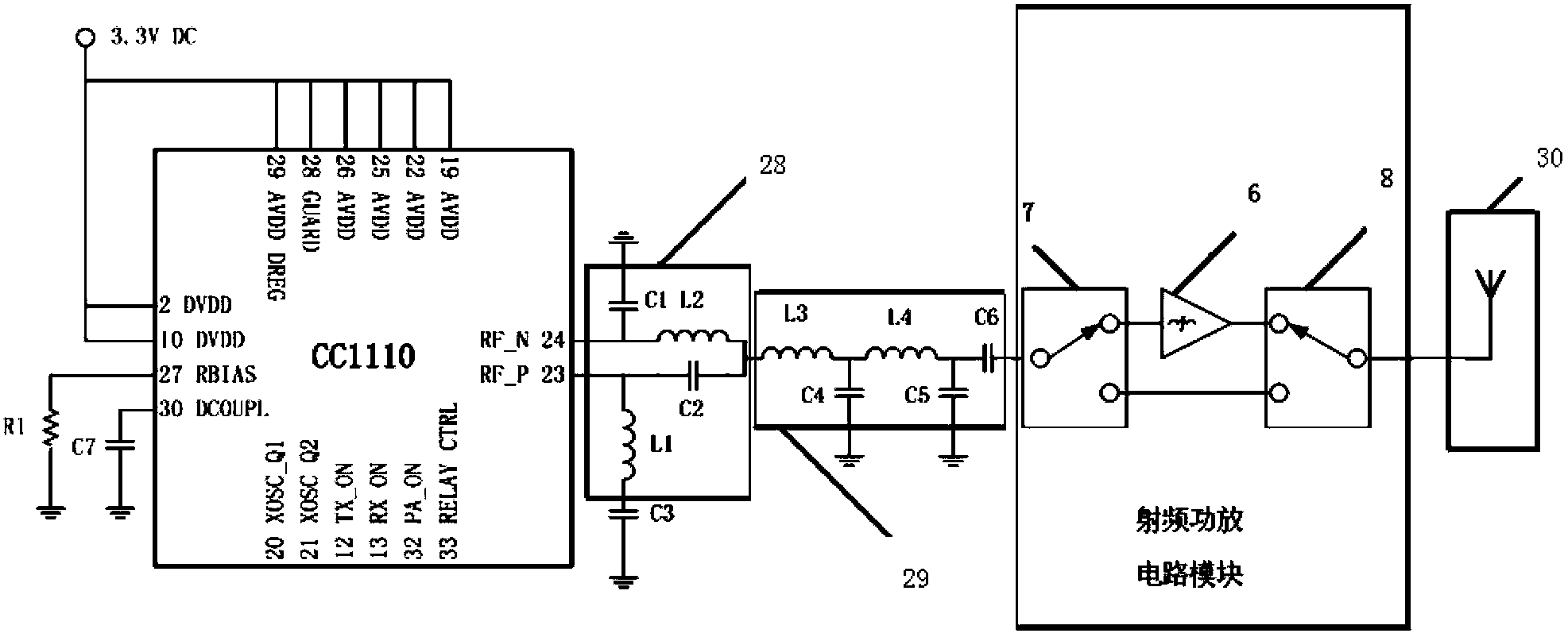

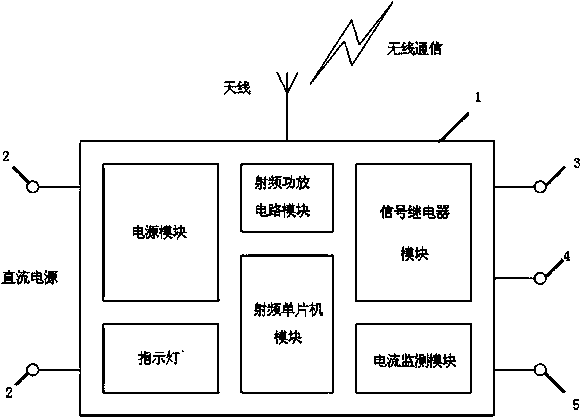

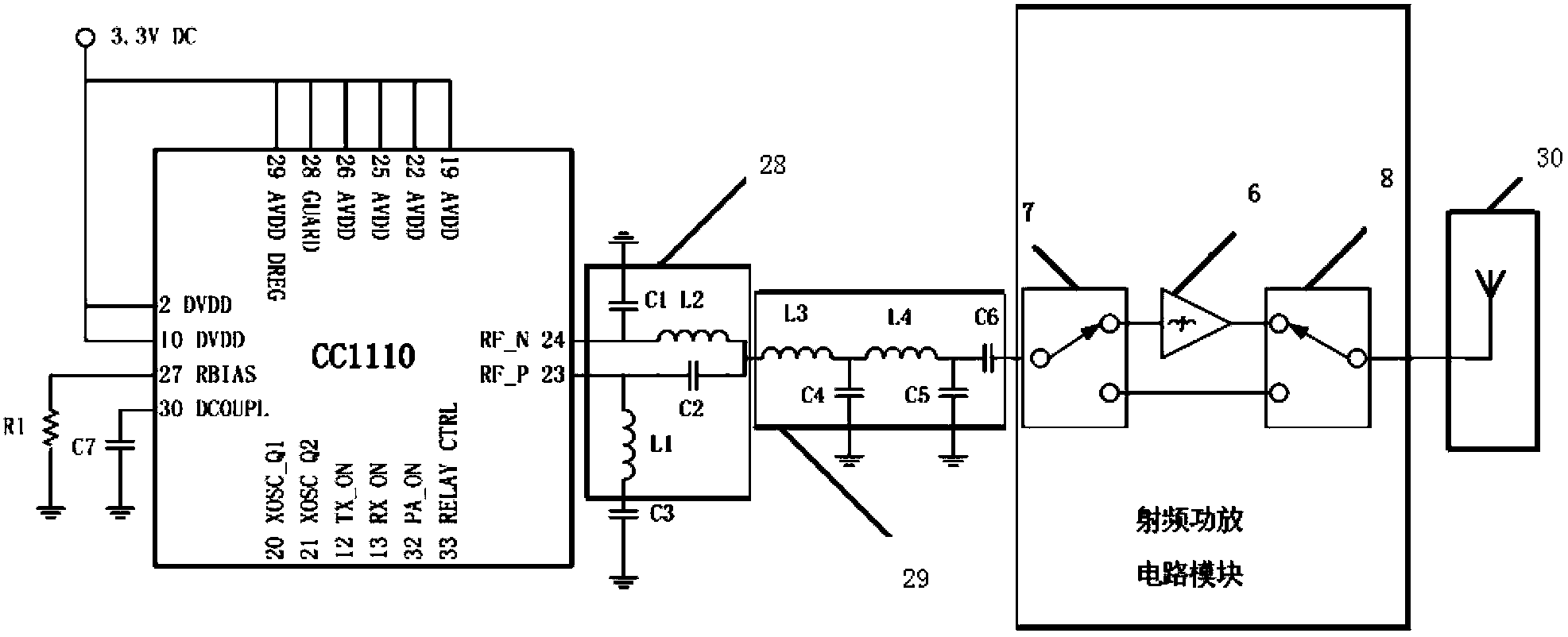

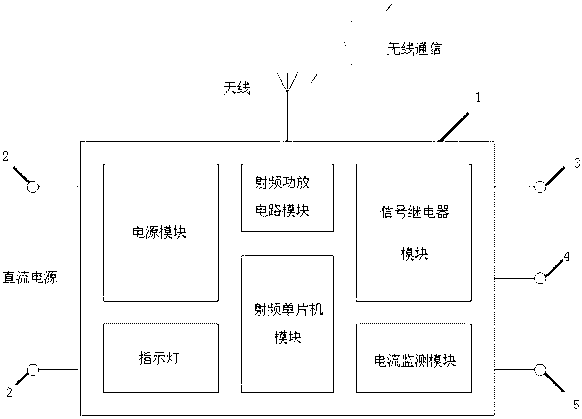

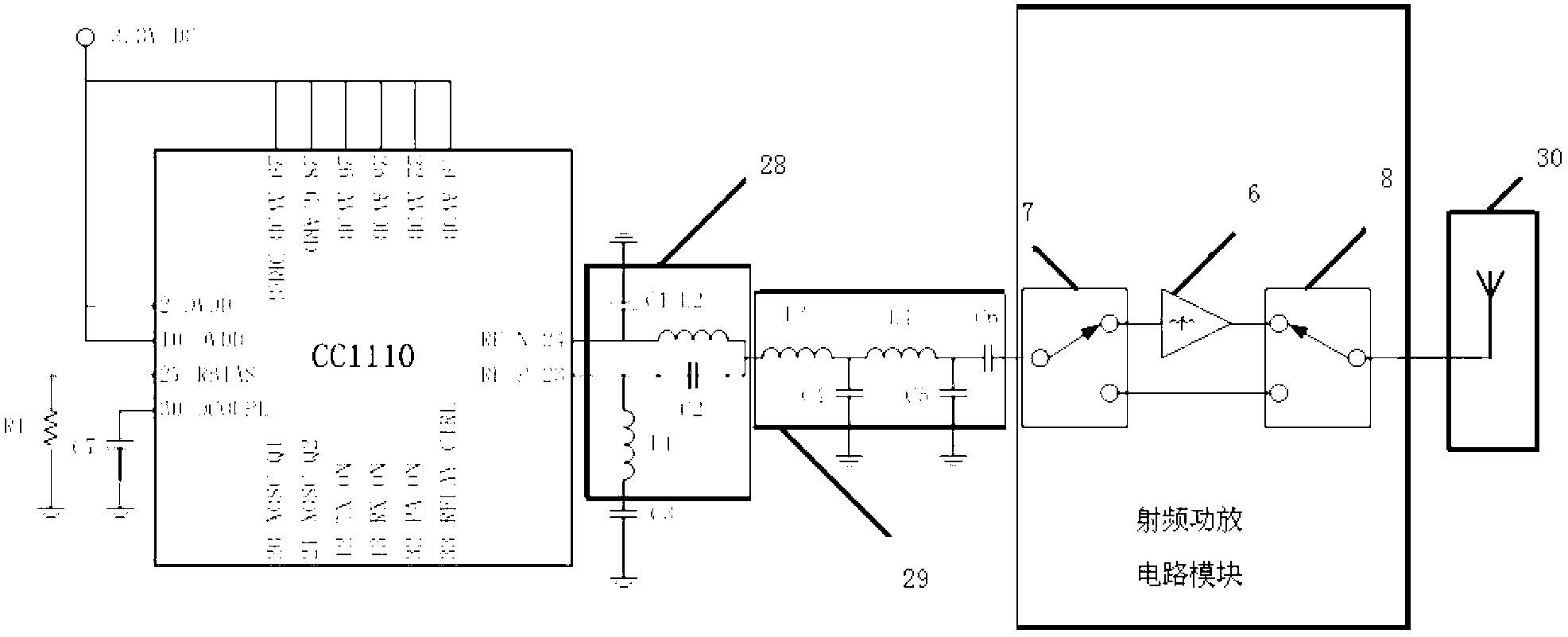

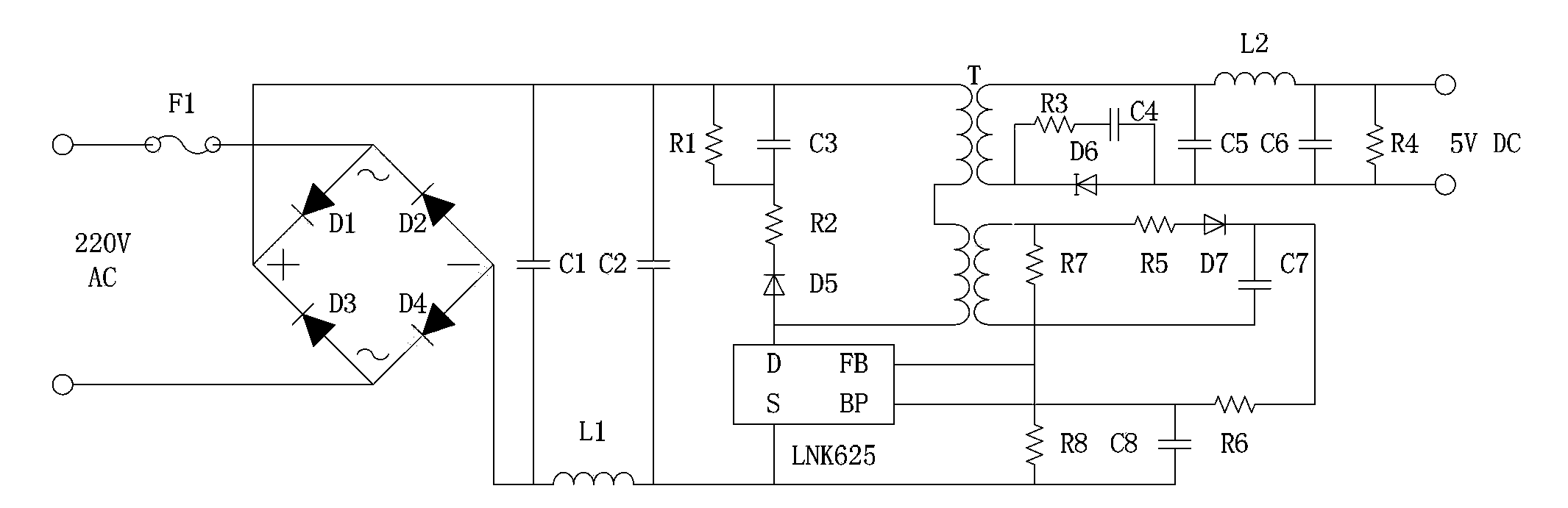

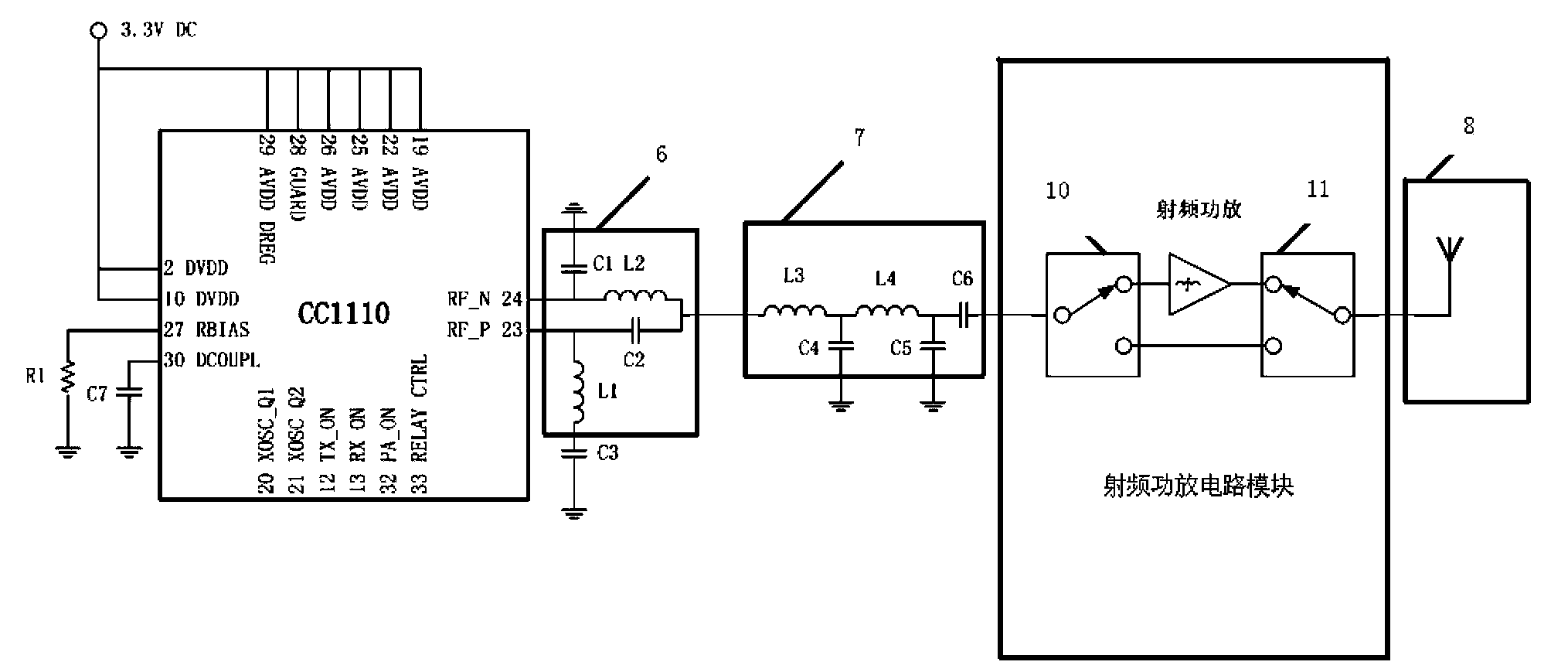

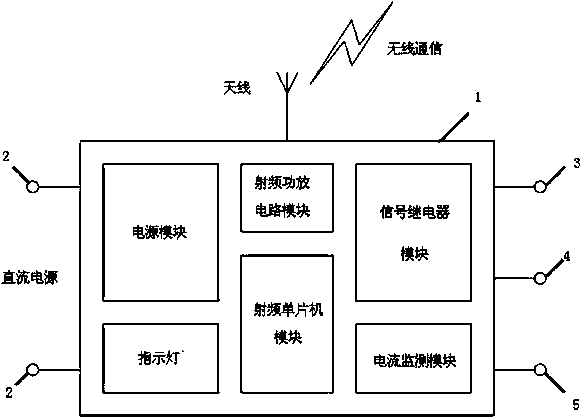

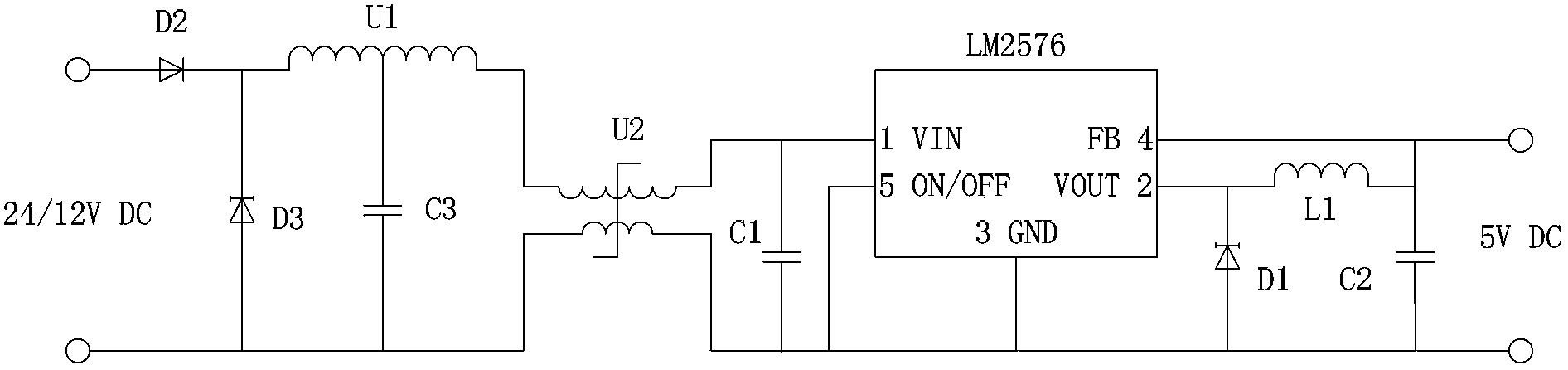

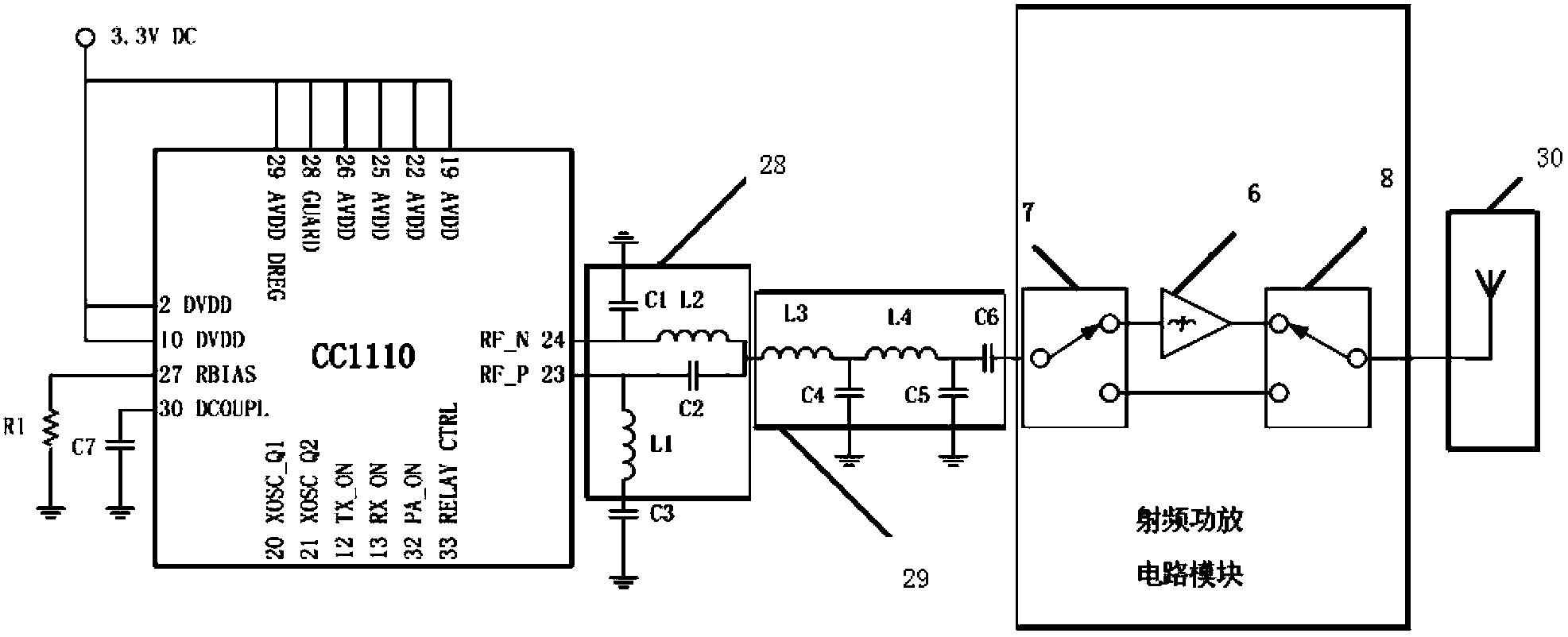

Wireless communication signal relay system

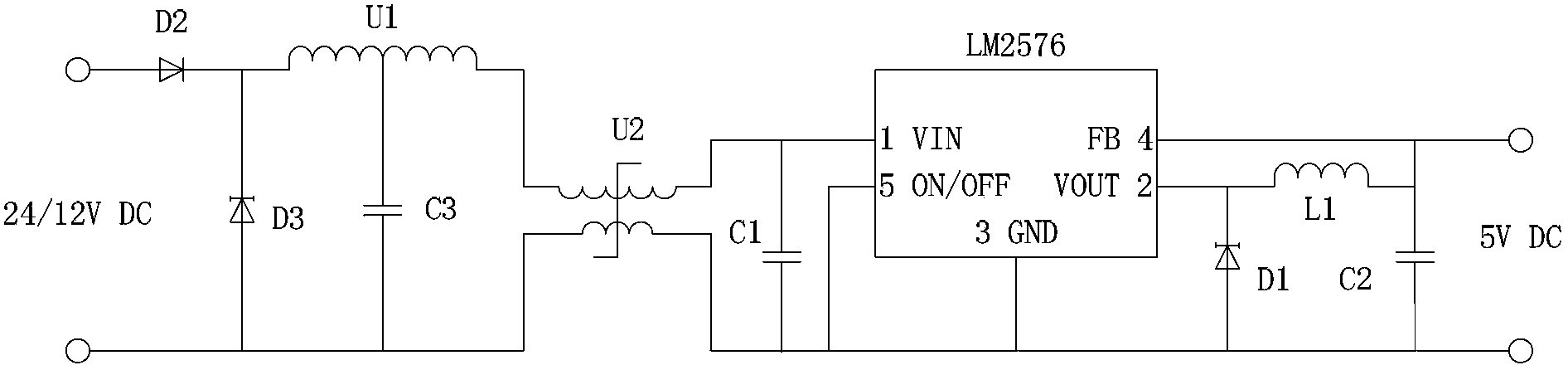

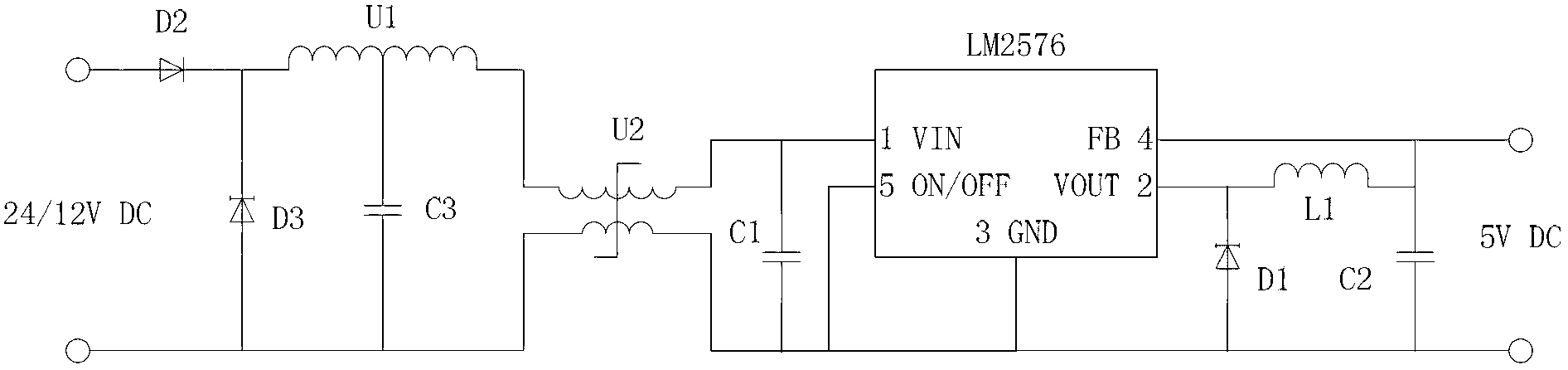

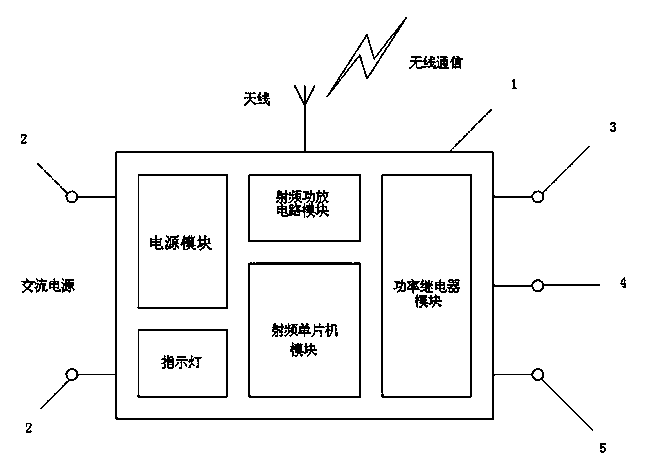

InactiveCN103543671ALow costLong transmission distanceProgramme controlTransmission systemsRadio frequencyVIT signals

The invention discloses a wireless communication signal relay system. The system is characterized by comprising a shell, a power input terminal, a relay output terminal, an indicator light, a radio frequency single-chip microcomputer module, a power module, a signal relay module, and a remote control center. The power input terminal is used for being connected with a direct current power supply. A common terminal pin, a normally open terminal pin and a normally closed terminal pin of the relay output terminal are used for being connected with loads. The system has the advantages that on or off of the signal relay is controlled through wireless packets monitored and the current state of the signal relay or power consumption of the loads is fed back to the remote control center in a wireless manner.

Owner:TAIZHOU FUCCESSO ELECTRONICS TECH

Wireless signal relay system capable of realizing wireless control

InactiveCN103543665ARealize automatic controlLow costProgramme controlTransmission systemsMicrocontrollerWireless control

The invention discloses a wireless signal relay system capable of realizing wireless control. The wireless signal relay system capable of realizing wireless control comprises a shell, a power input terminal, a relay output terminal, an indicator lamp, a radiofrequency singlechip module, a power module, a signal relay module and a remote control center, wherein the power input terminal of the wireless signal relay system capable of realizing wireless control is connected with a direct-current power source; and a common terminal pin, a normally open terminal pin and a normally closed terminal pin of the relay output terminal are connected with a load. On the one hand, the wireless signal relay system capable of realizing wireless control can control switch-on or switch-off of a signal relay according to a monitored wireless packet, and on the other hand, the current status of the signal relay or the power consumption of the load is wirelessly fed back to the remote control center.

Owner:TAIZHOU FUCCESSO ELECTRONICS TECH

Wireless signal relay system capable of automatically controlling and monitoring

InactiveCN103543670ARealize automatic controlLow costProgramme controlTransmission systemsMicrocontrollerAutomatic control

The invention discloses a wireless signal relay system capable of automatically controlling and monitoring. The wireless signal relay system is characterized by comprising a shell, power source input terminals, a relay output terminal, an indicating lamp, a radio-frequency single chip microcomputer module, a power source module, a signal relay module and a remote control center. The signal source terminals of the wireless signal relay system are connected with a direct-current power source. A common port pin, a normally-open-end pin and a normally-closed-end pin of the relay output terminal are connected with a load. The wireless signal relay system controls on or off of a signal relay according to monitored wireless packets, and wirelessly feeds current state or load power dissipation of the signal relay back to the remote control center.

Owner:TAIZHOU FUCCESSO ELECTRONICS TECH

Wireless signal relay and using method thereof

The invention discloses a wireless signal relay, which is characterized by comprising a shell, a power input terminal, a relay output terminal, an indicating lamp, a radio frequency singlechip module, a power module and a signal relay module, wherein the power input terminal of the wireless signal relay is connected with a direct current power supply; and a common end pin, a normally open end pin and a normally closed end pin of the relay output terminal are connected with a load. The wireless signal relay can control switch-on and switch-off of the signal relay according to a monitored wireless packet and wirelessly feed back the current state of the signal relay or the power consumption of the load to a remote control center.

Owner:TAIZHOU FUCCESSO ELECTRONICS TECH

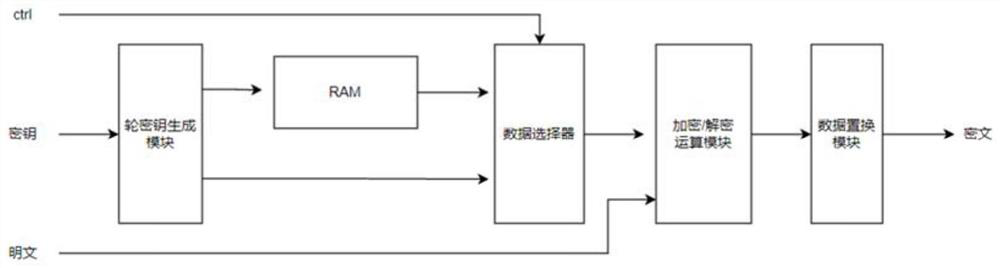

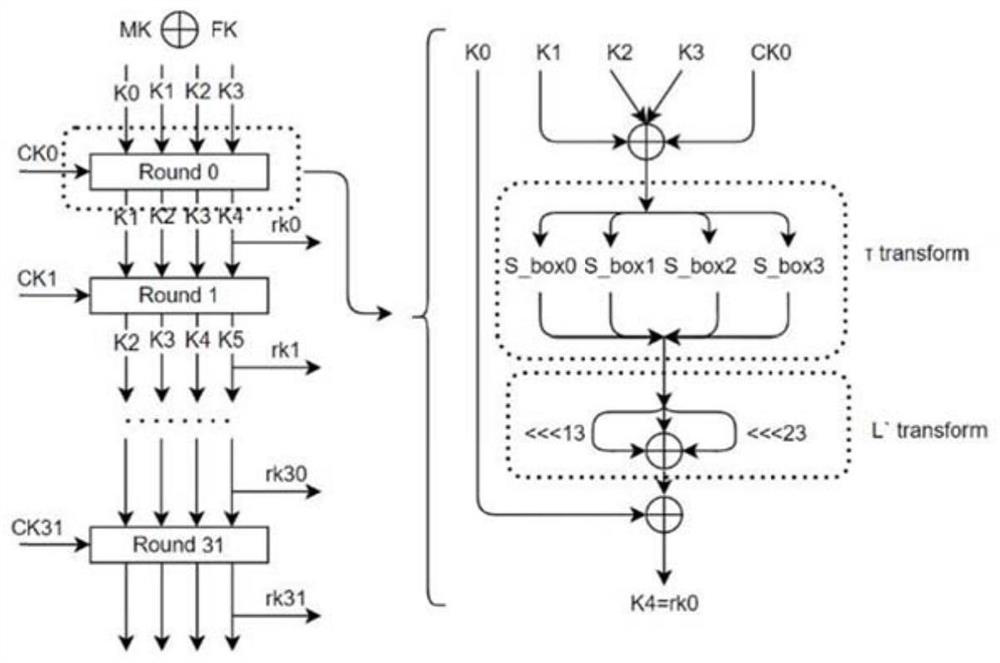

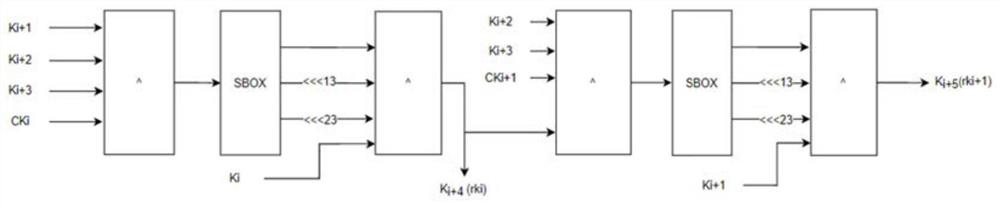

High-speed SM4 cryptographic algorithm circuit suitable for mobile equipment

ActiveCN113949504ATotal Iteration Rounds ReductionReduce the number of seriesKey distribution for secure communicationEncryption apparatus with shift registers/memoriesAlgorithmEncryption decryption

The invention discloses a high-speed SM4 cryptographic algorithm circuit suitable for mobile equipment, and belongs to the field of digital circuits. The high-speed SM4 cryptographic algorithm circuit comprises a round key generation module, an RAM module, a data selector module and an encryption / decryption operation module. The round key generation module and the encryption / decryption operation module both adopt a two-degree expansion structure, iteration steps are basically consistent, each round of calculation generates two rounds of results, and the total iteration round can be reduced by half. In addition, the circuit is optimized on the basis of a two-degree expansion structure, the number of stages of the gate circuit is reduced, and the operation speed is effectively increased. According to the SM4 cryptographic algorithm, the round key generation circuit module and the encryption / decryption operation circuit module adopt a parallel architecture to realize the SM4 cryptographic algorithm, the working speed is high, the calculation time is short, the total processing round of the design circuit is a constant, and side channel attacks can be effectively resisted.

Owner:CHINA JILIANG UNIV

A kind of online upgrading method of dsp and fpga system

ActiveCN106909425BReduce Design ComplexitySimple interfaceSoftware engineeringComputer architectureEngineering

The invention discloses an online upgrading method for DSP and FPGA systems, which is used to solve the problem of online upgrading of programs in DSP and FPGA digital signal processing systems. The technical solution is to complete the interconnection between the upper computer and the DSP processor through the universal serial bus interface, and transfer the DSP and FPGA program files that need to be upgraded to the DSP processor, and the automatic upgrade algorithm of the DSP controls the flash memory of the DSP or FPGA. upgrade. A set of SPI interface bus of DSP is used to complete the hardware connection and erasing of two Flash, and the bus address decoding is completed through a multiplexer to avoid bus conflicts. The present invention simultaneously completes program upgrades of two chips, DSP and FPGA, without dismantling equipment, has simple interface, and low complexity of software and hardware design, and provides a simple and effective method for online upgrade of digital signal processing systems.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

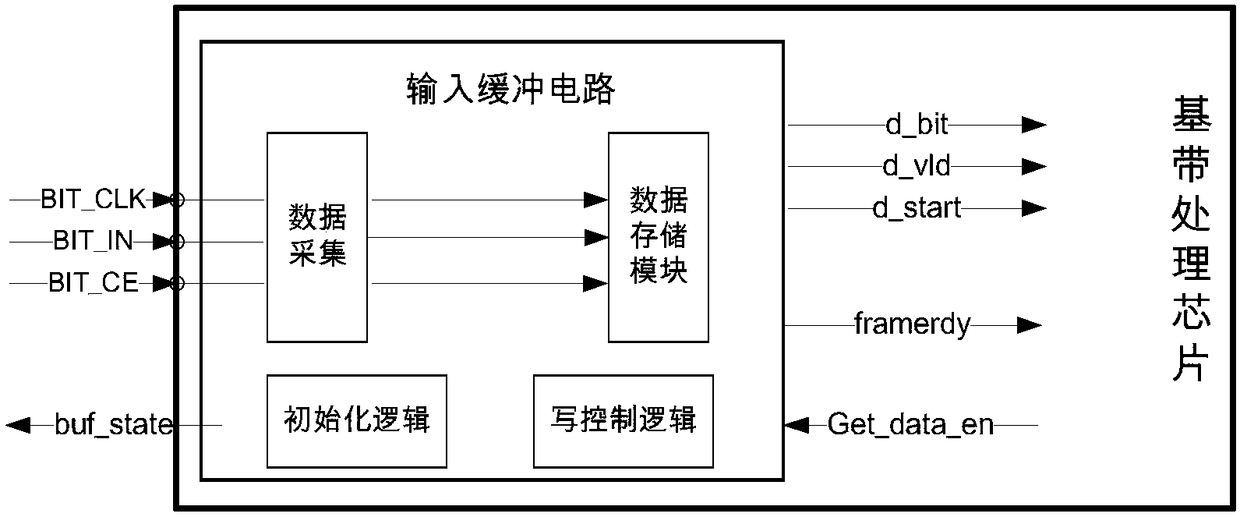

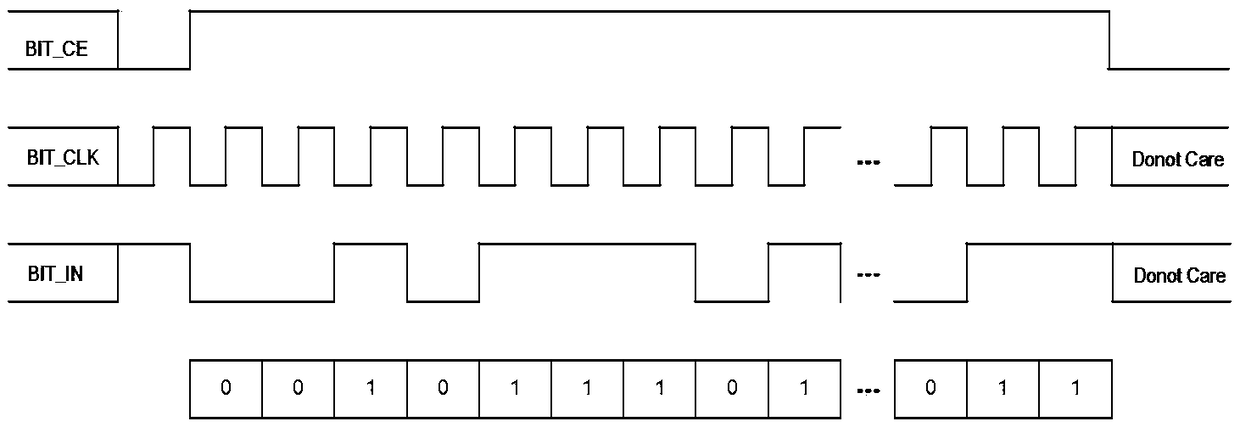

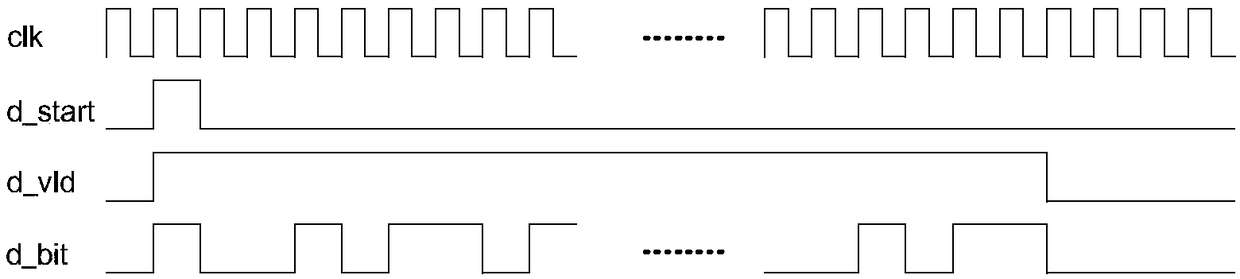

Baseband Chip Input Buffer Method

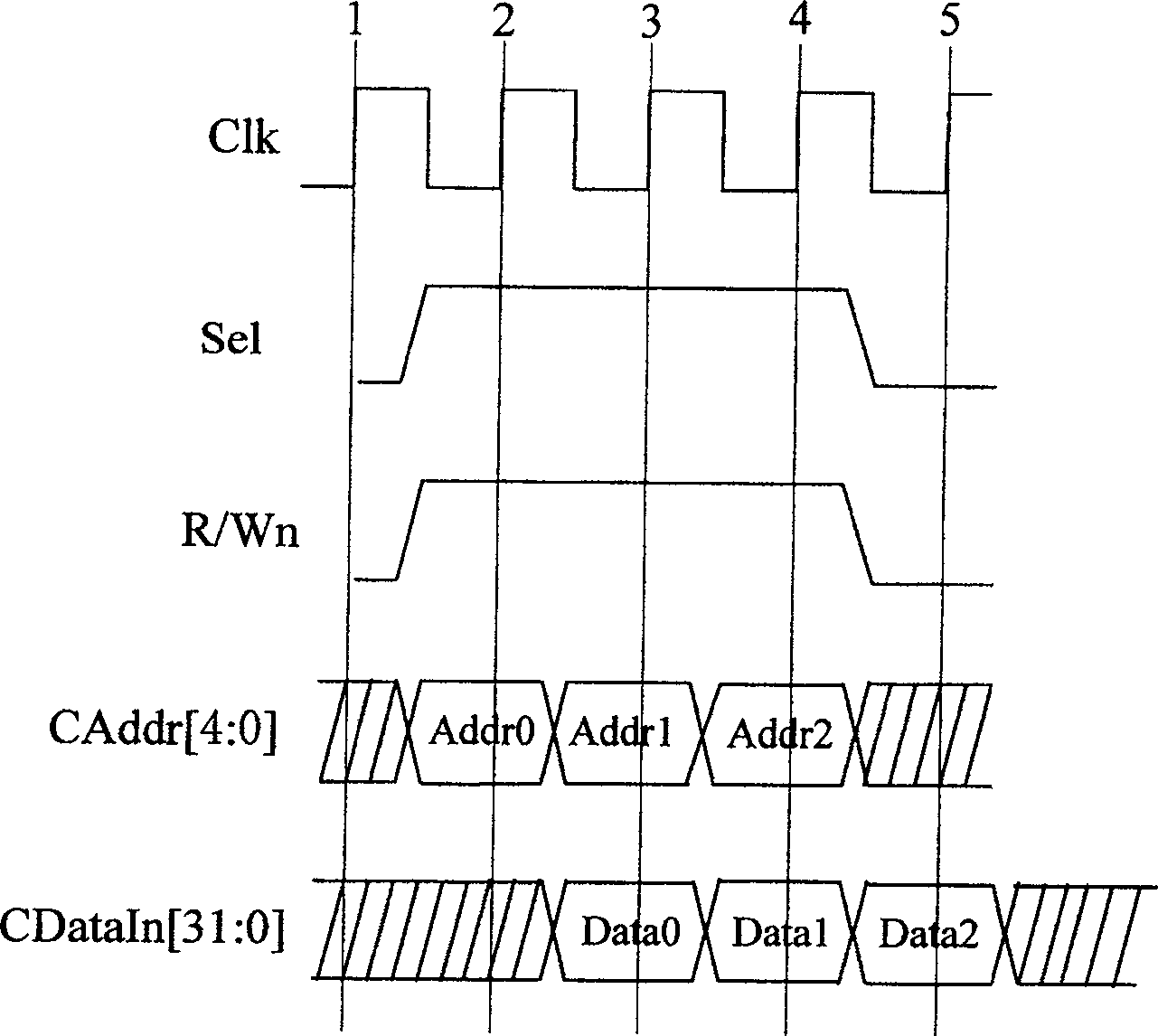

ActiveCN106021144BReduce occupancySimple interface timingElectric digital data processingData acquisitionIntra-frame

The invention puts forward a baseband chip input buffer method, and aims to provide the baseband chip input buffer method which exhibit simple interface time series and high robustness and restorability. The baseband chip input buffer method is realized through the following technical scheme: a telemetering transfer frame externally input by a baseband processing chip is serially input into a data acquisition circuit through three single-ended wires according to a transmission rule of interframe dispersing and intra-frame continuity, and a clock hop edge is detected by a multipoint detection way; acquisition data is written into a data storage module according to an arrangement rule under the control of a control logic module, and a high-level index signal is output when data storage content in the data storage module exceeds a preset threshold; a later-level processing module connected with an input buffer circuit detects the high-level index signal, a request pulse is given to the input buffer circuit according to a matching situation of a modulation rate and a processing rate; and if the input buffer circuit outputs data currently, the request is not responded, and otherwise, one frame of data is read from the data storage module to be serially output according to an appointed output format.

Owner:10TH RES INST OF CETC

Area compact type BCH paralleling decoding circuit supporting pre searching

A compact BCH parallel decoding circuit which supports preview search works on a finite field GF(2<13>). The parallel decoding circuit comprises a syndrome arithmetic circuit(1), a realizing circuit(2)with multiple shoots in one round for IBM wrong position multinomial iterative computation in the finite field GF(2<13>), a wrong address search circuit(3) provided with a totally combined logic pre-search module and a multifunctional configurable data interface(27)of an encoder. Compared with prior art, the decoding circuit has the advantages that the hardware is of low degree of complexity, the circuit area is compact and the decoding circuit is low in cost; data throughput is high and wrong address research is quick; the interface is simple in design and is practical and multi-functional; correcting performance can be flexibly configured according to the length of the check element and is free from the change of the code length.

Owner:NATIONZ TECH INC

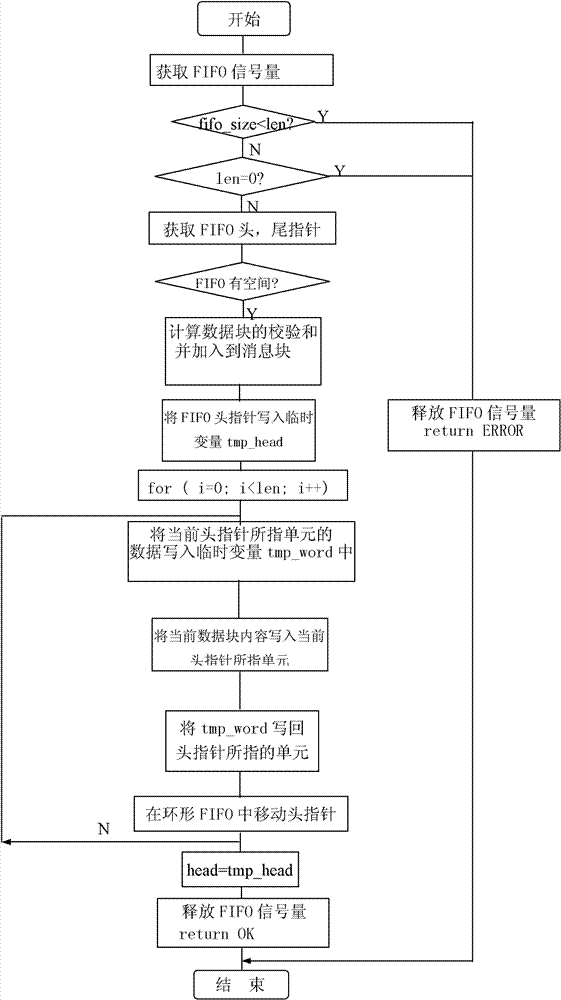

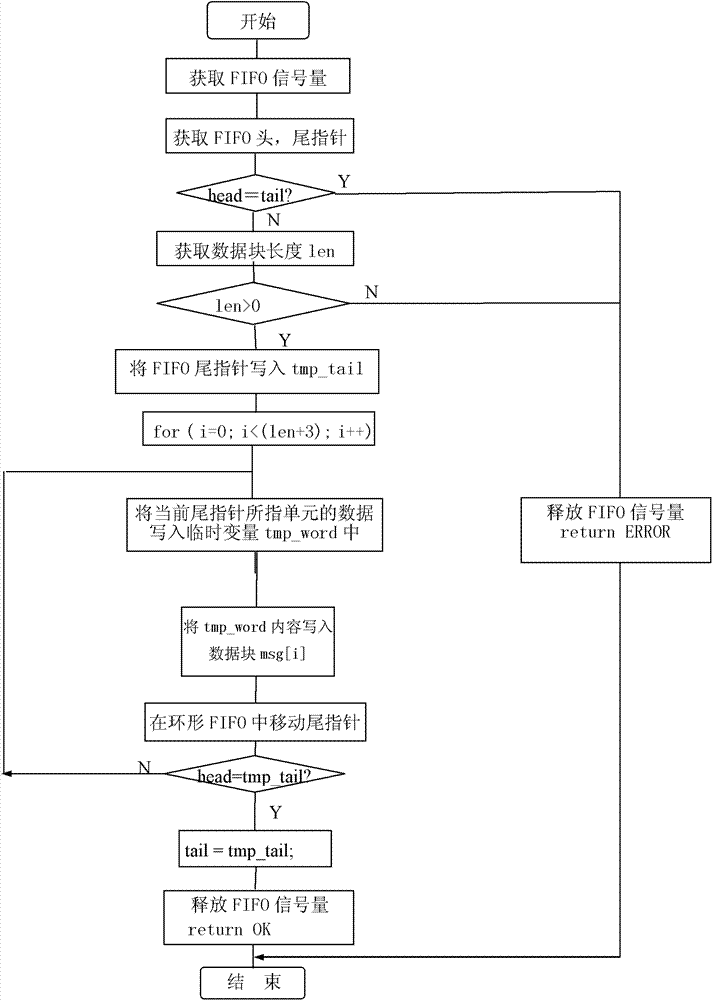

Method for dual-port virtual FIFO (first in first out) data exchange

ActiveCN102147786BMature design technologyEase of physical implementationDigital computer detailsElectric digital data processingParallel computingOnboard computer

The invention proposes a method for dual-port virtual FIFO (first in first out) data exchange, which comprises the following steps: (1) obtaining FIFO semaphores; (2) judging the relationship between the length of a data block to be sent and the length of the FIFO; (3) obtaining a head pointer and a tail pointer of the FIFO (first in first out); judging whether the length of the data block is less than the length of the current space to be written in of the FIFO through the obtained head pointer and the obtained tail pointer; and if yes, carrying out the step (4); (4) calculating the check sum of the data block; (5) sequentially writing in the length of the data block, the data block and the check sum at a position pointed by the current head pointer and moving the head pointer; and (6) releasing the FIFO semaphores. The method for the dual-port virtual FIFO data exchange is suitable for data exchange among multiprocessor systems in an airborne computer.

Owner:AVIC NO 631 RES INST

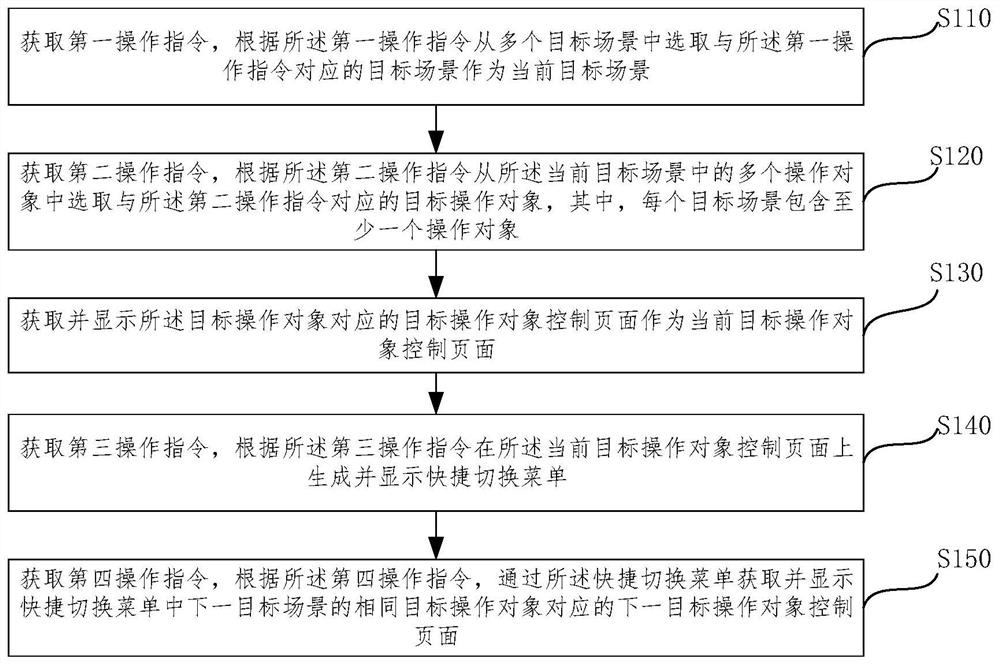

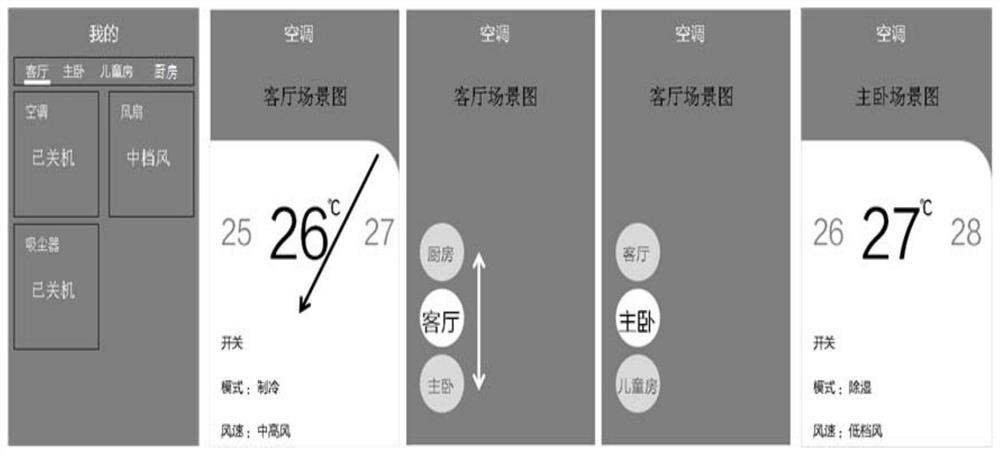

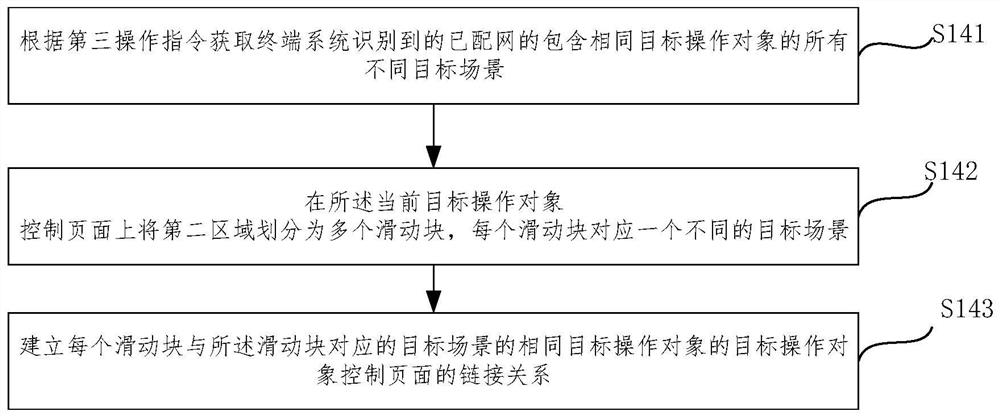

A page switching method and device

ActiveCN110647270BFlexible switchingEasy to switchExecution for user interfacesSpecial data processing applicationsSoftware engineeringMultiple applications

Owner:GREE ELECTRIC APPLIANCES INC

An integrated information interaction method for intelligent power distribution and utilization

ActiveCN104953706BImprove interaction efficiencyEliminate data heterogeneityCircuit arrangementsElectricityDecision taking

The invention discloses an integrated information interaction method for intelligent power distribution and utilization, which collects various types of data information to form information category 1, and transmits it to a unified support platform for intelligent power distribution and utilization; the unified support platform for intelligent power distribution and utilization completes the information category After the analysis, verification and format conversion of the information in 1, the information class 2 is sent to the intelligent power distribution business application system; the information required by each is extracted from the information class 2 and used to form its own control decision information; The control decisions formed by each business application system are sent to the unified support platform for intelligent power distribution as information category 3; the information in information category 3 is analyzed and classified in turn, and information category 4 is formed by category and sent to the intelligent power distribution and consumption information collection and control terminals; each terminal extracts the information it needs from the information category 4 and uses it. The invention realizes the information interaction and compatibility of different business application systems.

Owner:STATE GRID CORP OF CHINA +5

Pipeline magnetic flux leakage detection system, data acquisition device and method

ActiveCN106770623BHigh speed transmissionReal-time transmissionMaterial magnetic variablesData acquisitionData shipping

The invention provides a pipeline magnetic flux leakage detection system and a data acquisition device and method. The pipeline magnetic flux leakage detection system comprises a magnetizing device, a sensing member and the data acquisition device, wherein the sensing element is used for detecting a magnetic signal which is a magnetic flux leakage signal of a magnetic field; the data acquisition device comprises an ARM core module, a storage medium, an FPGA, an AD conversion device, a USB / FIFO conversion device and a power supply management module; the ARM core module is used for storing data acquired by the FPGA to the storage medium; the AD conversion device is used for performing analog-to-digital conversion on the magnetic signal received from the sensing member; the FPGA is used for transmitting the acquired magnetic data to the ARM core module through the USB / FIFIO conversion device according to the magnetic data acquired by the magnetic signal through compression; and the USB / FIFIO conversion device is used for data transmission between the ARM core module and the FPGA.

Owner:CHINA SPECIAL EQUIP INSPECTION & RES INST

Wireless communication power relay system

InactiveCN103543663ARealize automatic controlLow costProgramme controlTransmission systemsRemote controlSingle chip

The invention discloses a wireless communication power relay system. The system is characterized by comprising a shell, a power input terminal, a relay output terminal, an indicator light, a radio frequency single-chip microcomputer module, a power module, a power relay module, and a remote control center. The power input terminal is used for being connected with an alternating current power supply. A common terminal pin, a normally open terminal pin and a normally closed terminal pin of the relay output terminal are used for being connected with loads. The system has the advantages that on or off of the power relay is controlled through wireless packets monitored and the current state of the power relay is fed back to the remote control center in a wireless manner.

Owner:TAIZHOU FUCCESSO ELECTRONICS TECH

On-chip system

ActiveCN100485648CSimplify interface designSuitable designElectric digital data processingSystems designInterface design

The on-chip system includes several functional modules connected with internal bus including two independent transmission channels, including one control / state channel for transmitting control / state information and one data channel for transmitting other data except control / state information. Each of the control / state channel and the data channel has separate data bus, address bus and control bus. The kernel of the present invention is to design on-chip system bus in the strategy of separate control / state channel and data channel, which have different topologic structures and communication protocols. The present invention has greatly simplified interface design of functional modules inside the system and increased total system communication bandwidth, and is especially suitable for on-chip system design with compact data interaction.

Owner:SUGON INFORMATION IND

Wireless signal relay system

InactiveCN103543673ARealize automatic controlLow costProgramme controlTransmission systemsControl signalRemote control

The invention discloses a wireless signal relay system. The system is characterized by comprising a shell, a power input terminal, a relay output terminal, an indicator light, a radio frequency single-chip microcomputer module, a power module, a signal relay module, and a remote control center. The power input terminal is used for being connected with a direct current power supply. A common terminal pin, a normally open terminal pin and a normally closed terminal pin of the relay output terminal are used for being connected with loads. The system has the advantages that on and off of the signal relay is controlled through wireless packets monitored and the current state of the signal relay or power consumption of the loads is fed back to the remote control center in a wireless manner.

Owner:TAIZHOU FUCCESSO ELECTRONICS TECH

Low-speed chain circuit data transmission apparatus and method in telecommunication apparatus

ActiveCN1866970BSimplify interface designImprove reliabilityTime-division multiplexTransmissionLow speedInterface design

The invention relates to a data transmitter in low-speed chain circuit and relative method. Wherein, said device comprises a low-speed chain circuit interface frame, a service processing frame, and aDDF support; said method comprises: the service data of service processing frame via high-speed chain circuit is transmitted to the low-speed chain circuit interface frame; the low-speed chain circuitinterface frame processes said bus data to be transmitted to the DDF support via low-speed chain circuit. With said invention, the interface design of service processing frame can be simplified to improve the reliability of telecommunication equipment.

Owner:HUAWEI TECH CO LTD

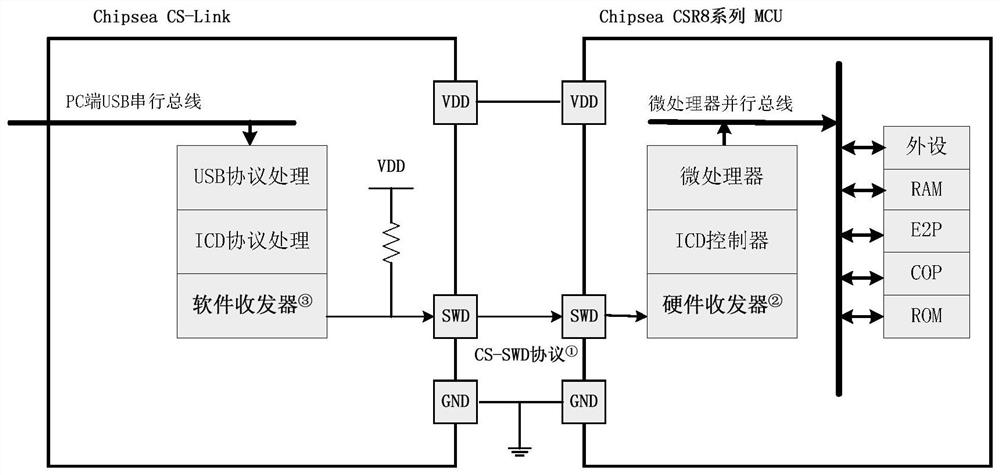

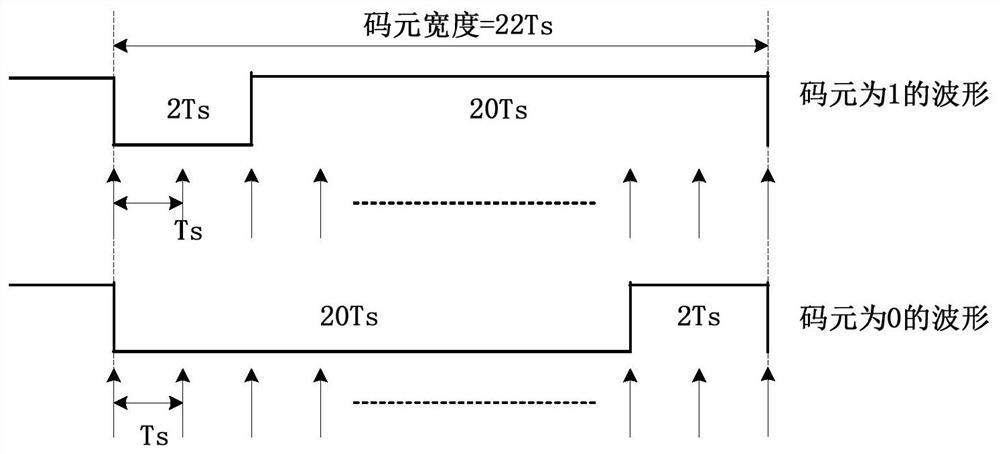

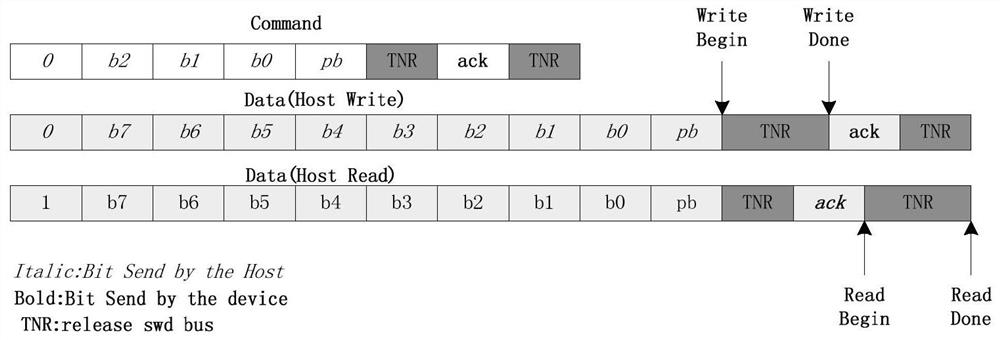

A single-wire interface method for on-chip debugging

ActiveCN107748805BEasy accessSimplify interface designSoftware testing/debuggingDesign optimisation/simulationComputer architectureEngineering

The invention discloses a single-line interface method for on-chip debugging. The method is realized by a hardware part and a software part, the hardware part is realized by a microprocessor, the microprocessor has a single-line interface, and the microprocessor performs signal encoding and decoding through digital logic Finally, serial-to-parallel conversion is performed to obtain a parallel control bus, which is finally combined with the microprocessor bus to control the on-chip peripherals of the MCU through a single-wire interface. The software part encodes and decodes the signal through the underlying functions of the software, and then passes the converted byte information to the upper layer as a function parameter, and finally passes it to the PC through the USB protocol.

Owner:HEFEI CHIPSEA ELECTRONICS TECH CO LTD