AHB interface system for stream data transmission

A technology of data stream transmission and bus interface, which is applied in the direction of electrical digital data processing and instruments, and can solve the problems of failure to provide

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

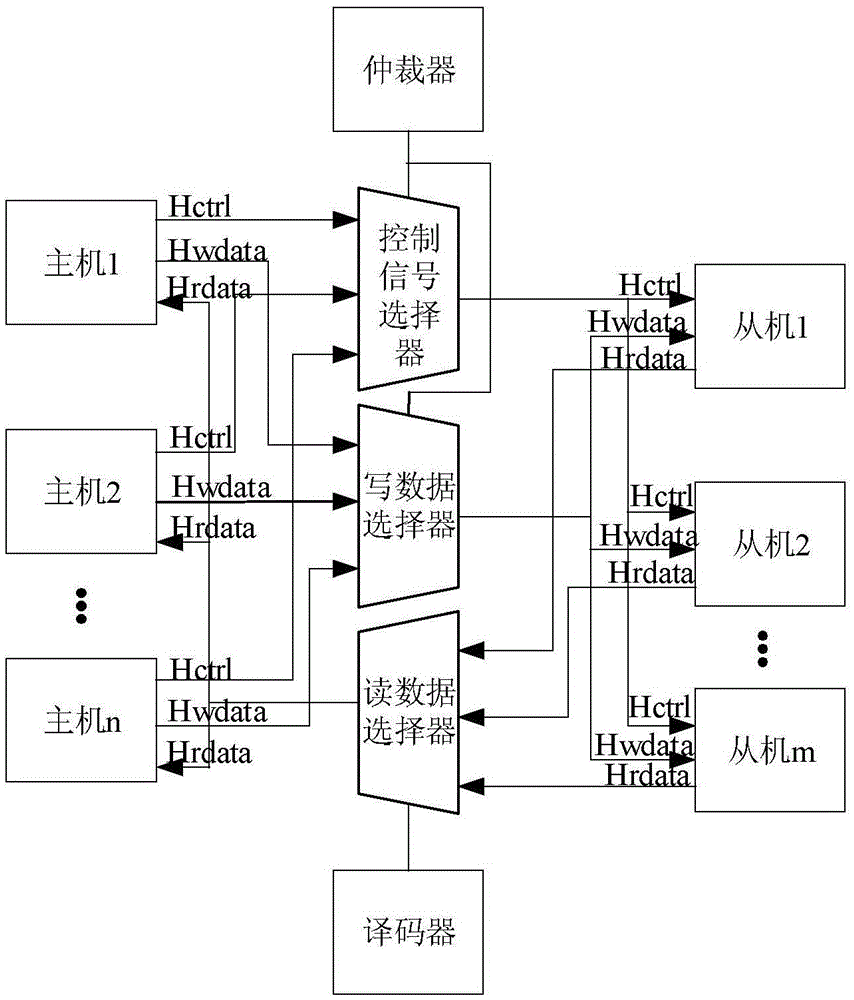

[0022] Specific implementation mode one: as figure 1 As shown, the AHB bus protocol is designed based on the interconnection scheme of the central multiplexer. The interconnection modules include a master, a slave, an arbiter, and a decoder. The structural diagram of the system is shown in figure 1 shown. The AHB bus supports the communication mode of multi-master and multi-slave. The arbiter determines the master that has obtained the ownership of the AHB bus, and sends control signals and writes data to the slave by controlling the multiplexer. The decoder determines that a certain slave data is valid, and sends the valid data to the master through the multiplexer.

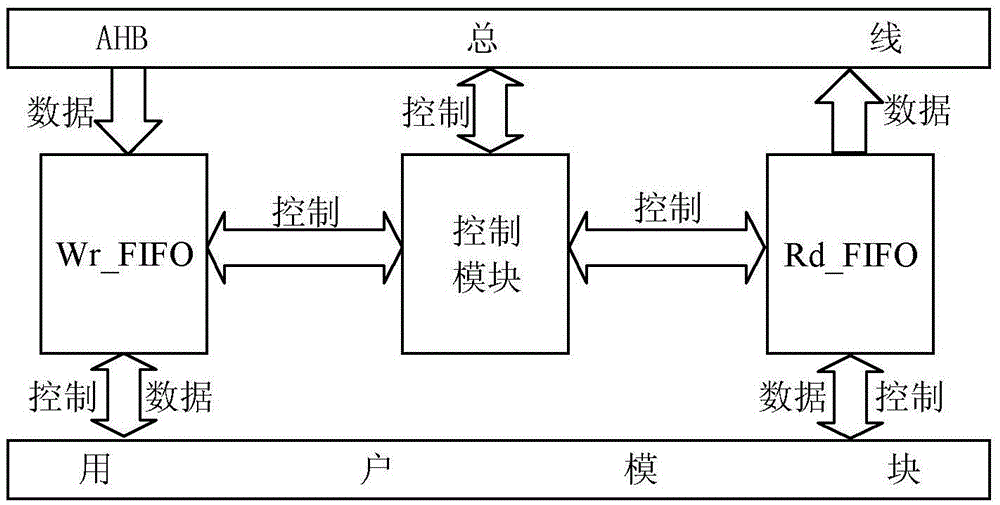

[0023] Such as figure 2 As shown in the schematic diagram of the slave system description in this design, FIFO is selected as the general interface for data transmission. The bus selects the slave and the transmission mode between the slave and the slave by sending control signals. Rd_FIFO writes data to s...

specific Embodiment approach 2

[0044] Specific implementation mode two: the difference between this implementation mode and specific implementation mode one is:

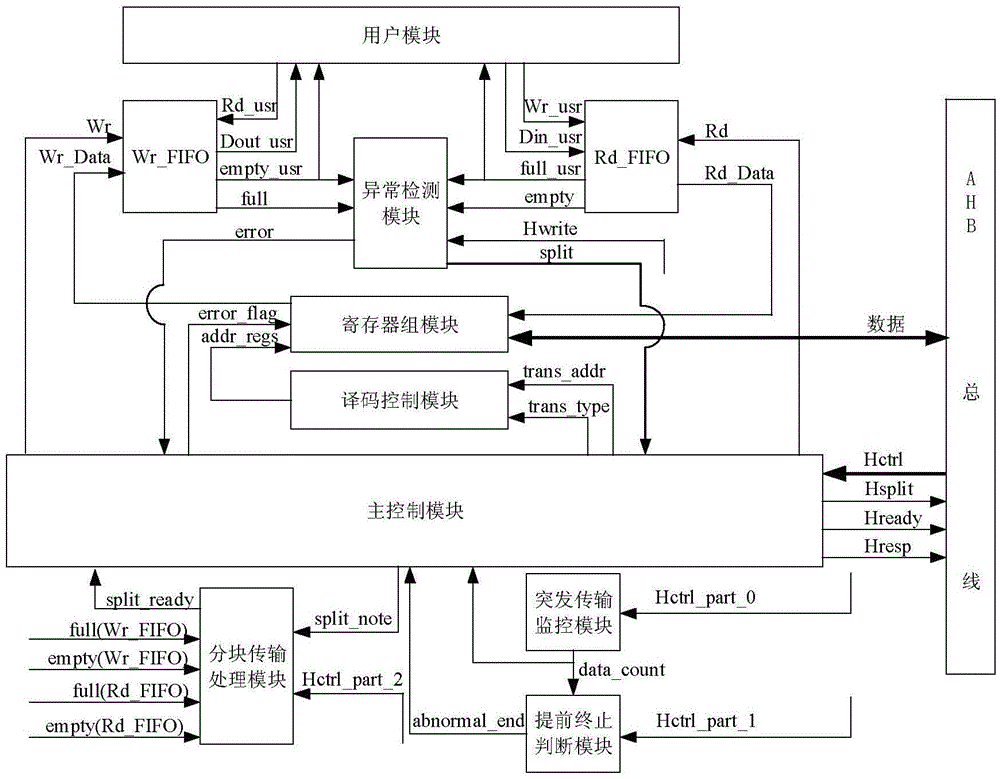

[0045] Figure 4 For the design of the main control module of the system, the jump conditions between the states in the figure can be queried in Table 2 according to the labels.

[0046] The input of the main control module is the control signal sent by the AHB bus to the slave and the detection results of each module, and the output is the response of the slave and the control signal of each module;

[0047] The main control module is in the idle state, waiting for transmission; if the slave is selected for transmission and the transmission type is nonseq and indicates read / write and the slave is ready, then jump to the trans state; if the slave is ready to complete the block For transmission, jump to the hsplit state; if the Rd_FIFO module and the Wr_FIFO module are both empty during the read transmission, or if the Wr_FIFO module and the Rd_FI...

specific Embodiment approach 3

[0058] Specific embodiment three: the difference between this embodiment and specific embodiment one or two is: the input of the register group module is the data, error information, register read enable signal and Rd_FIFO module sent by the AHB bus to the slave. Read data, the output data is the data sent by the slave to the AHB bus and the data to be written sent by the register group module to the Wr_FIFO module; the control information is defined as the error response of the slave, so that the host can make the correct response according to the type of error transmission;

[0059] The register group module controls the read and write operations of the register group according to the address signal: when performing a write operation, the address can be used as the enable information of the register group, so that the corresponding register can be written into data; when performing a read operation, the address indicates the register location information , the corresponding ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More