Interface structure and configuration method of FPGA (field programmable gate array) chip

An interface structure and chip technology, applied in instruments, computer control, simulators, etc., can solve the problems of limited number of input and output units, large area of input and output units, unfavorable small size of chips, etc. Effects of timing requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

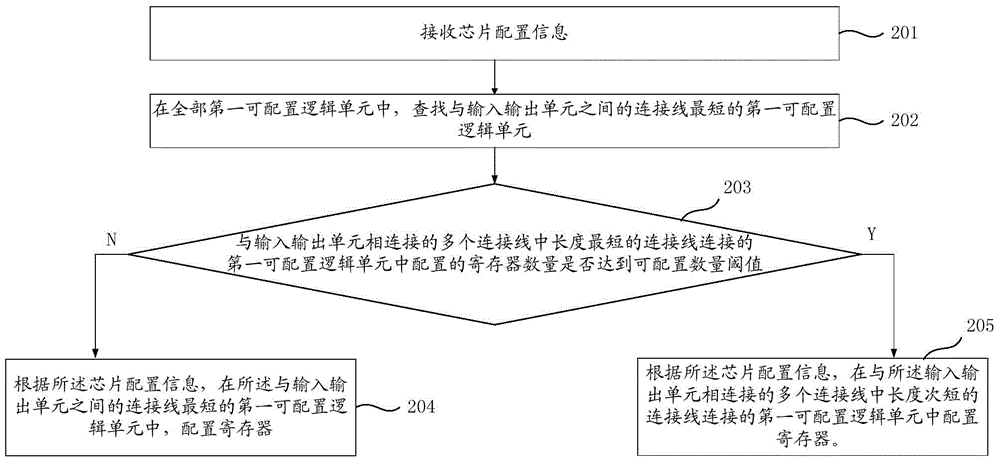

[0024] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

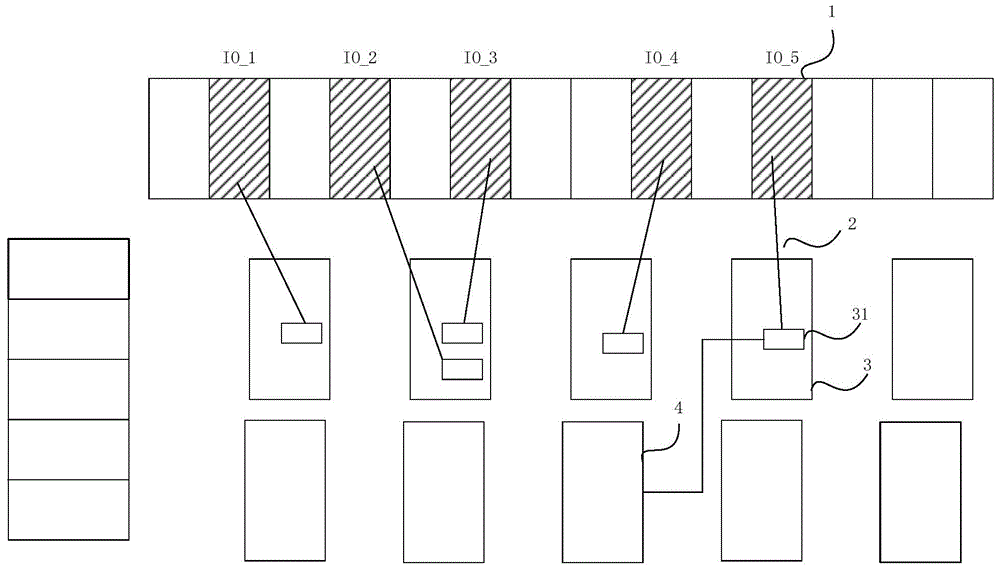

[0025] figure 1 It is a schematic diagram of the interface structure of the FPGA chip provided by the embodiment of the present invention. As shown in the figure, the interface structure of the FPGA chip includes: an input-output (IO) unit 1 , a connection line 2 and a first configurable logic unit 3 .

[0026] The input and output unit 1 is connected to an external chip or circuit, and is used to receive chip configuration information sent from the outside; wherein, the chip configuration information is information used to configure each logic unit inside the FPGA chip.

[0027] The connection line 2 is used to connect the input and output unit 1 and each unit inside the FPGA chip, including the first configurable logic unit 3 or the second configurable logic unit 4; in addition, between each unit inside the FPGA chi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More