Patents

Literature

224results about "Delay compensation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

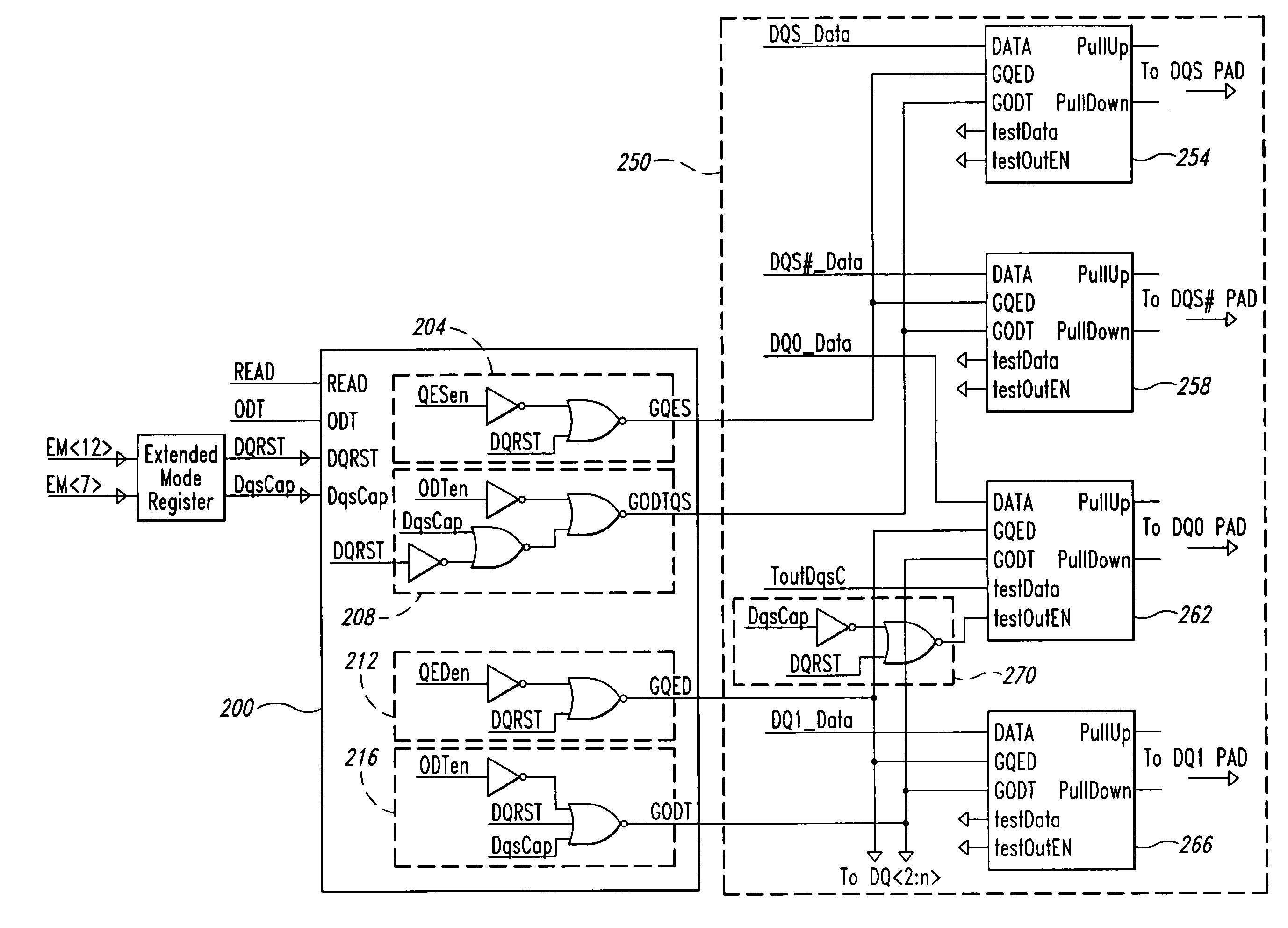

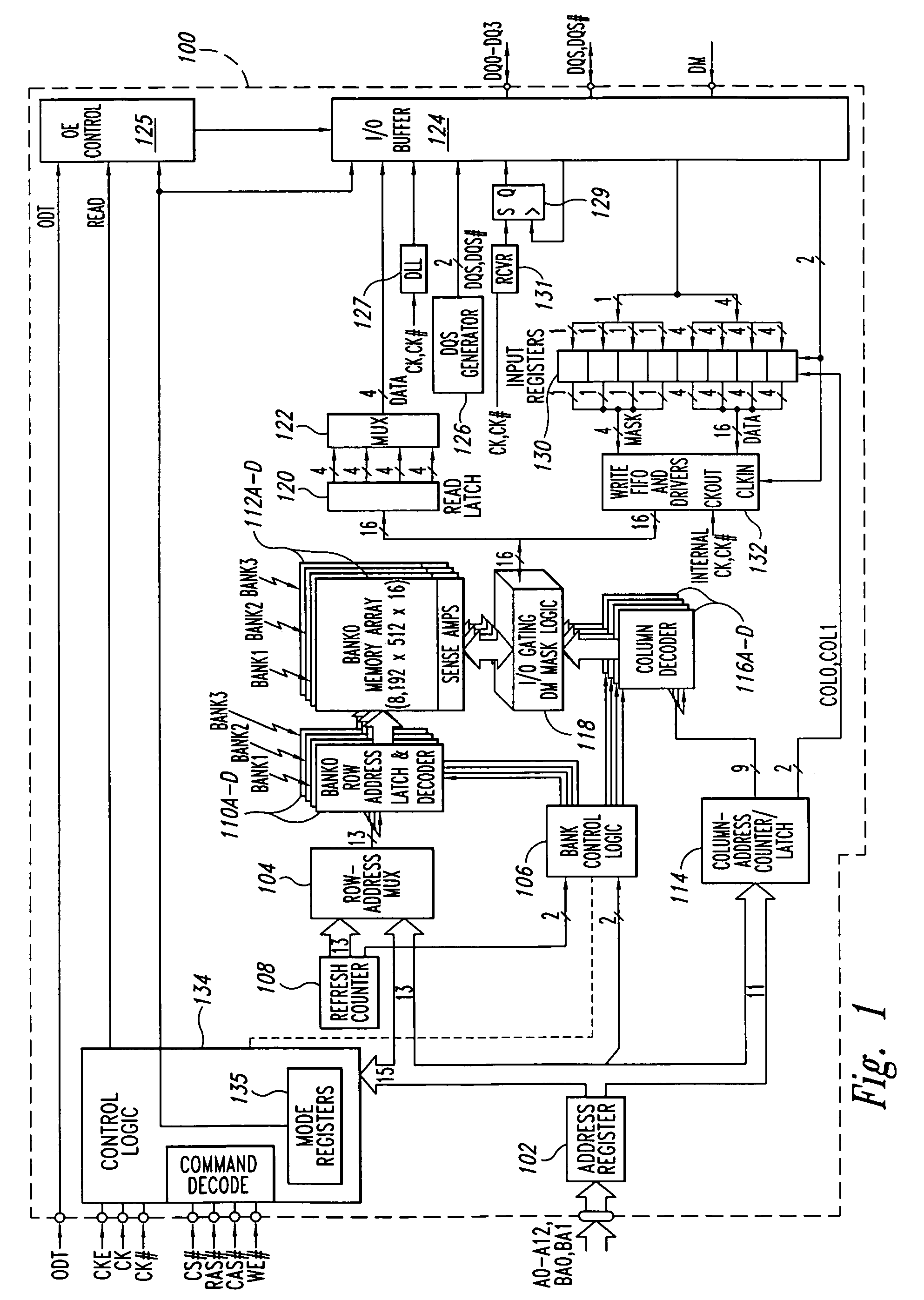

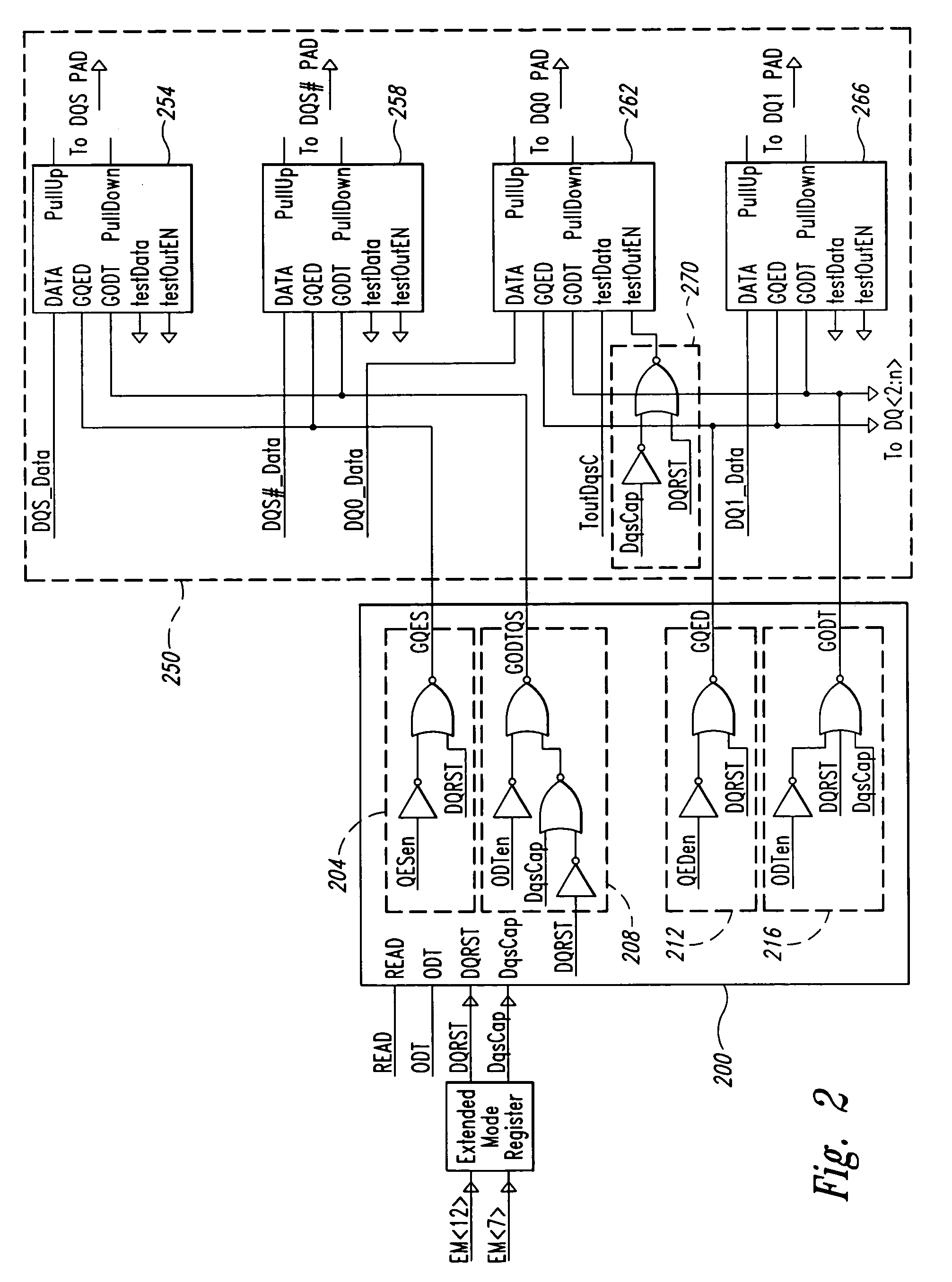

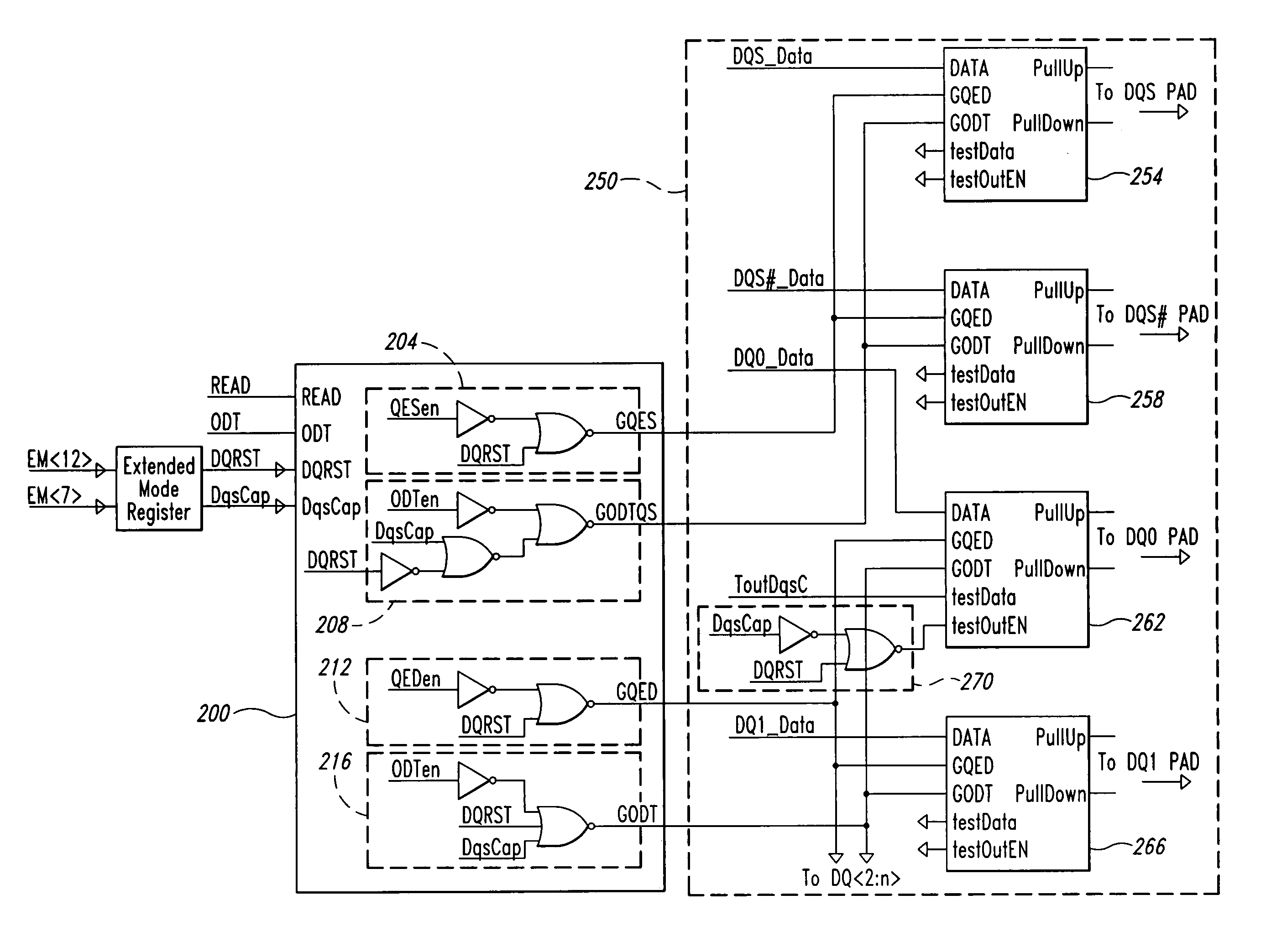

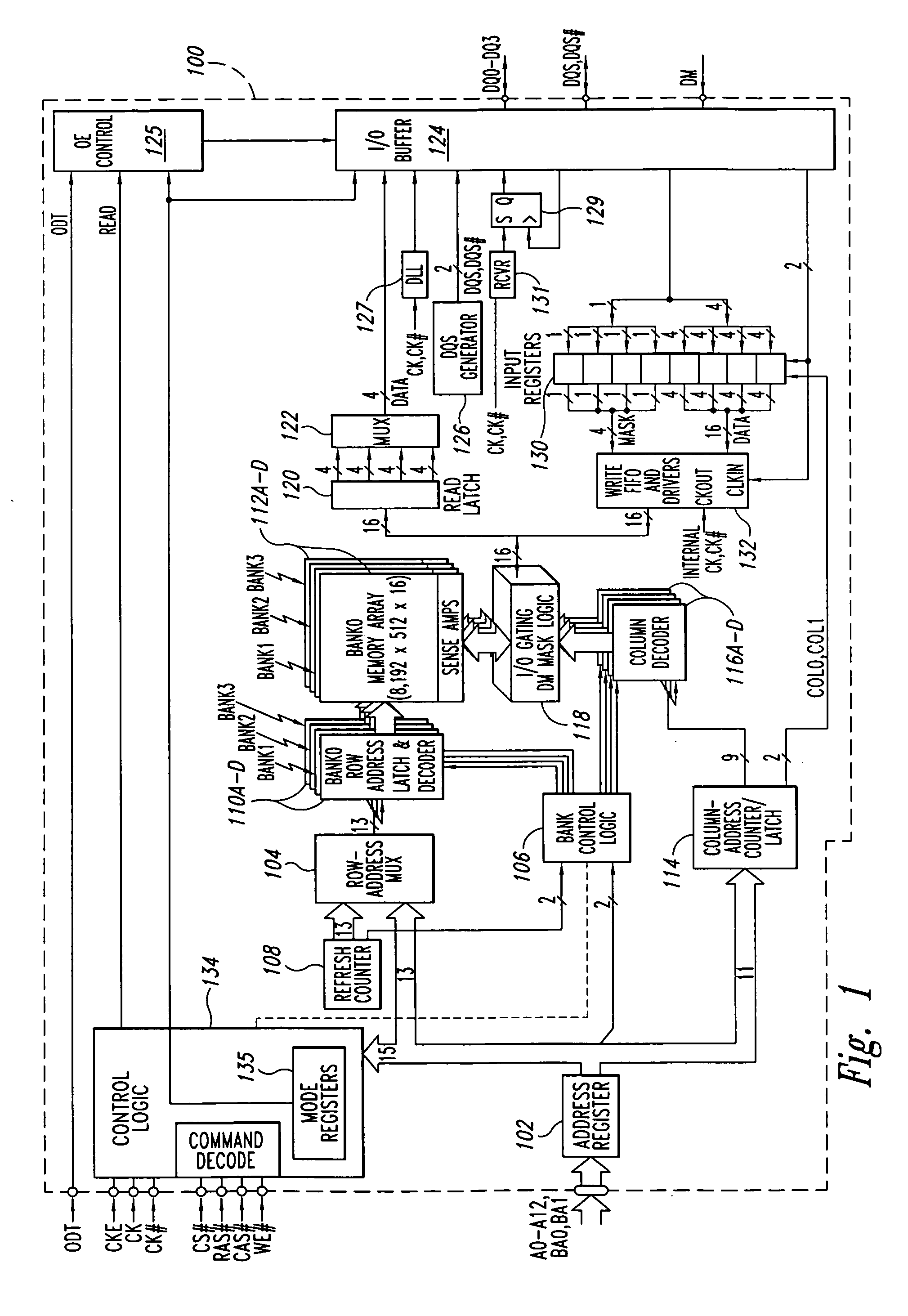

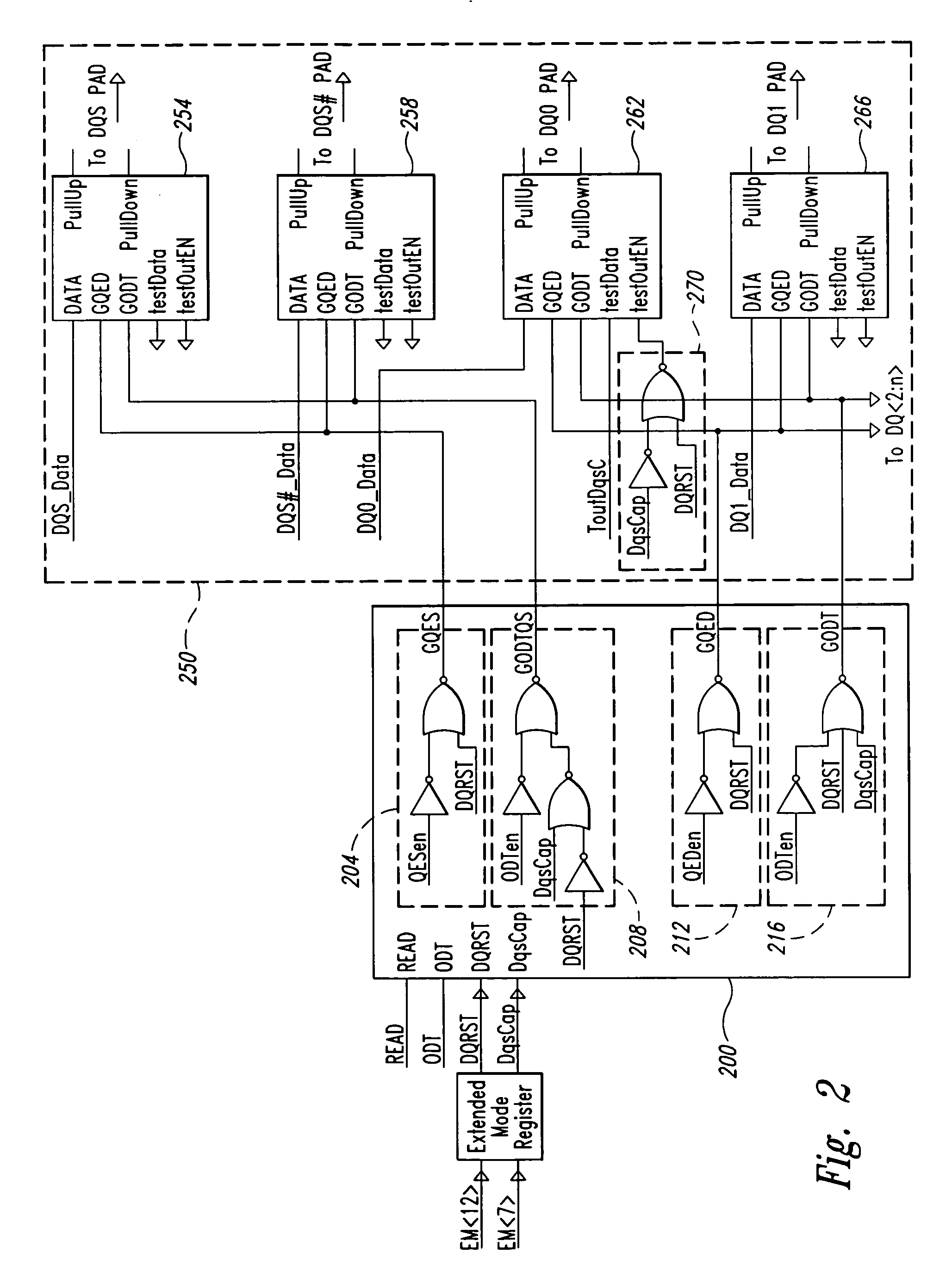

Apparatus and method for independent control of on-die termination for output buffers of a memory device

An apparatus and method providing independent control of on-die termination (ODT) of output buffers. The ODTs for the buffer circuits of an input / output (I / O) buffer can be enabled and disabled in response to an ODT control signal. Additionally, the ODTs for a first set of the buffer circuits can be enabled and disabled responsive to the ODT control signal and the ODT for at least one of a second set of the buffer circuits is disabled.

Owner:ROUND ROCK RES LLC

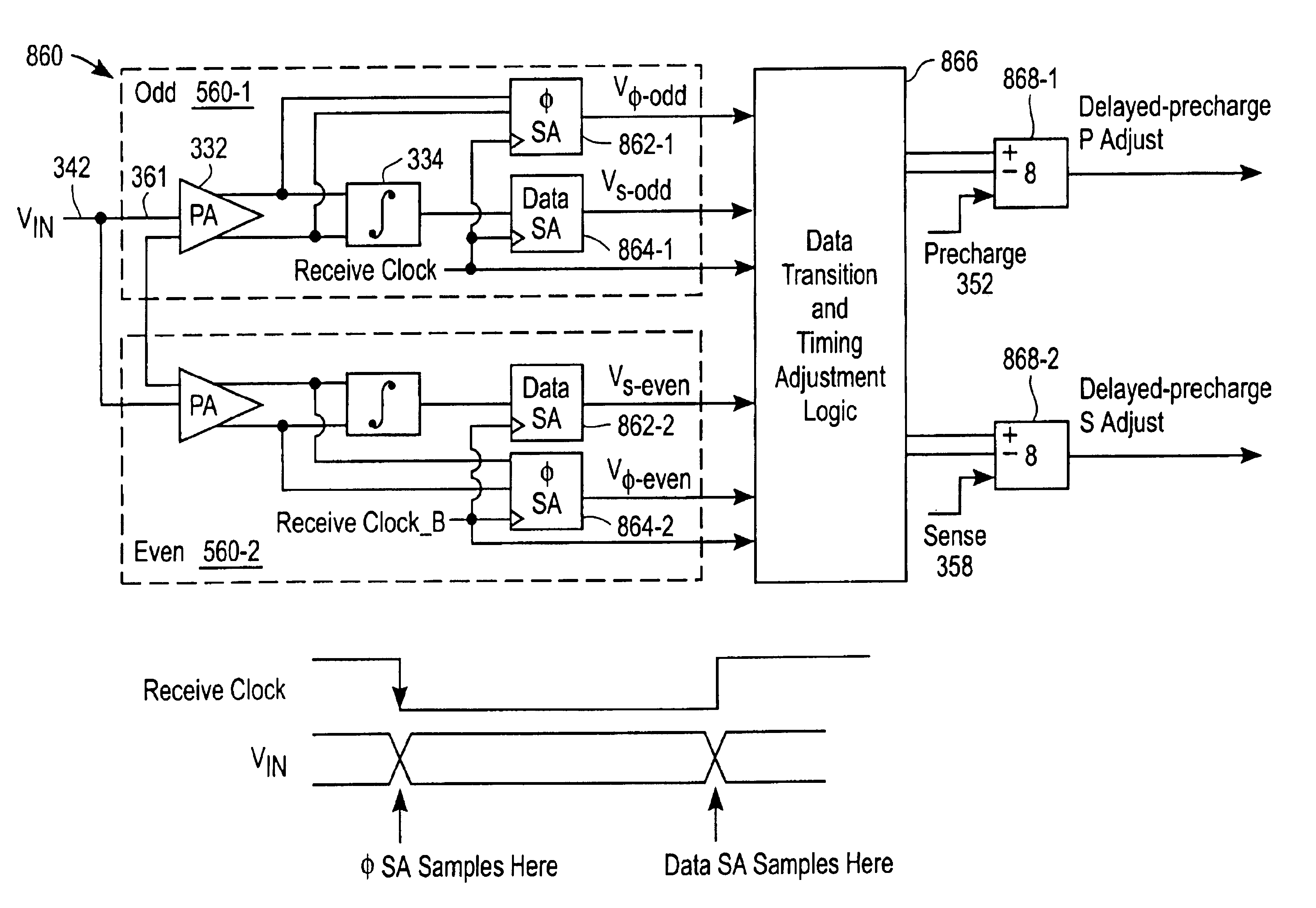

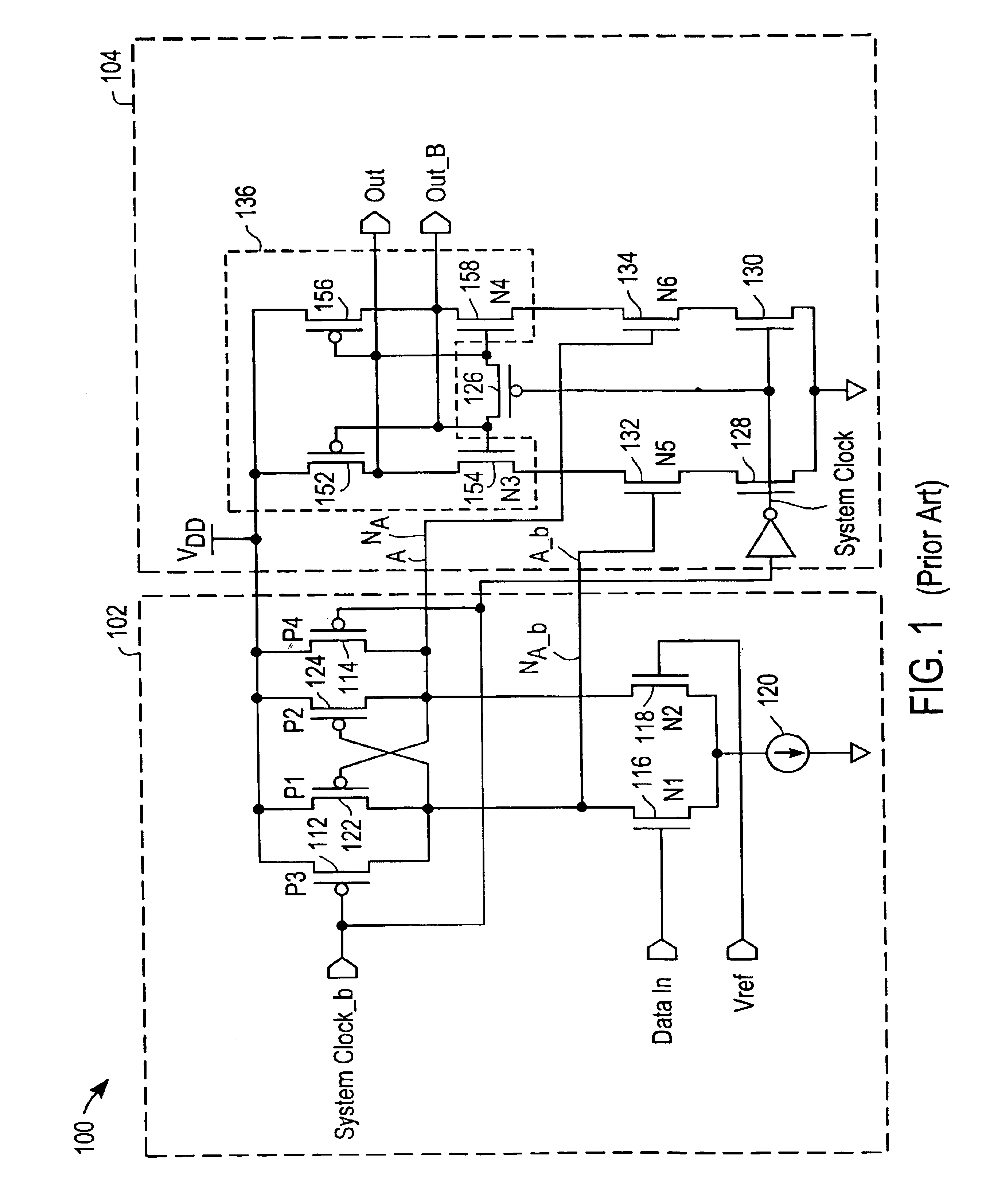

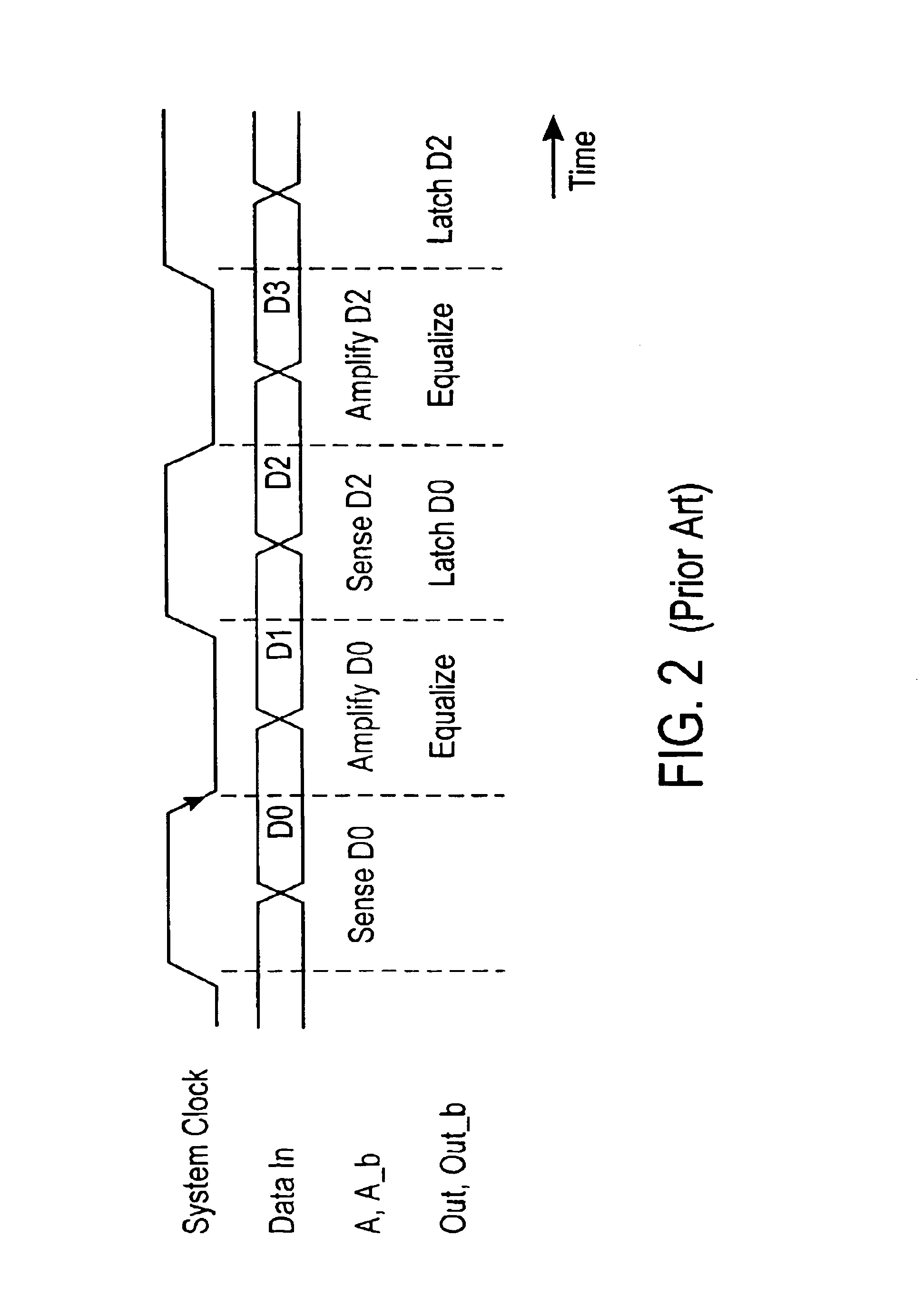

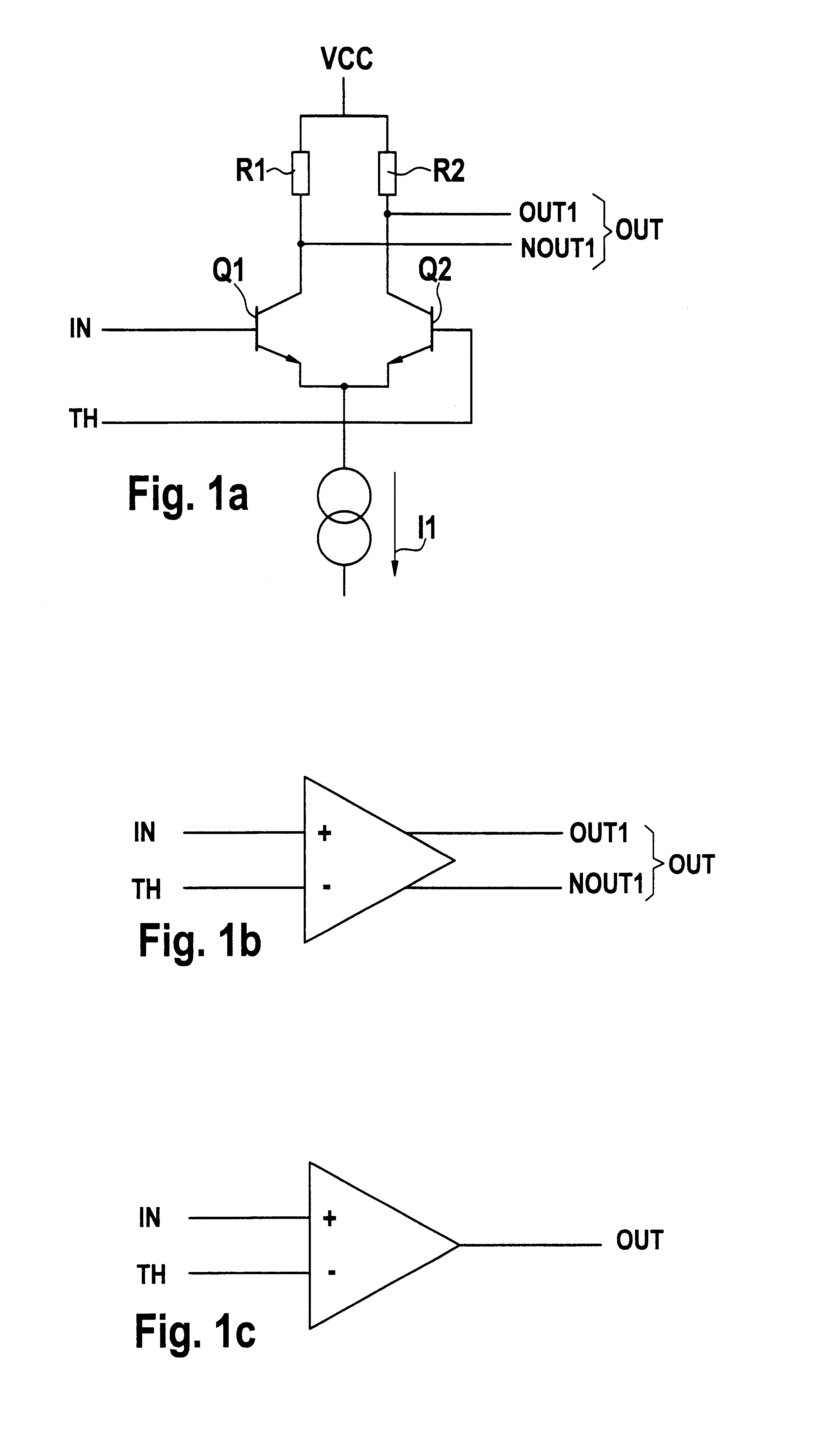

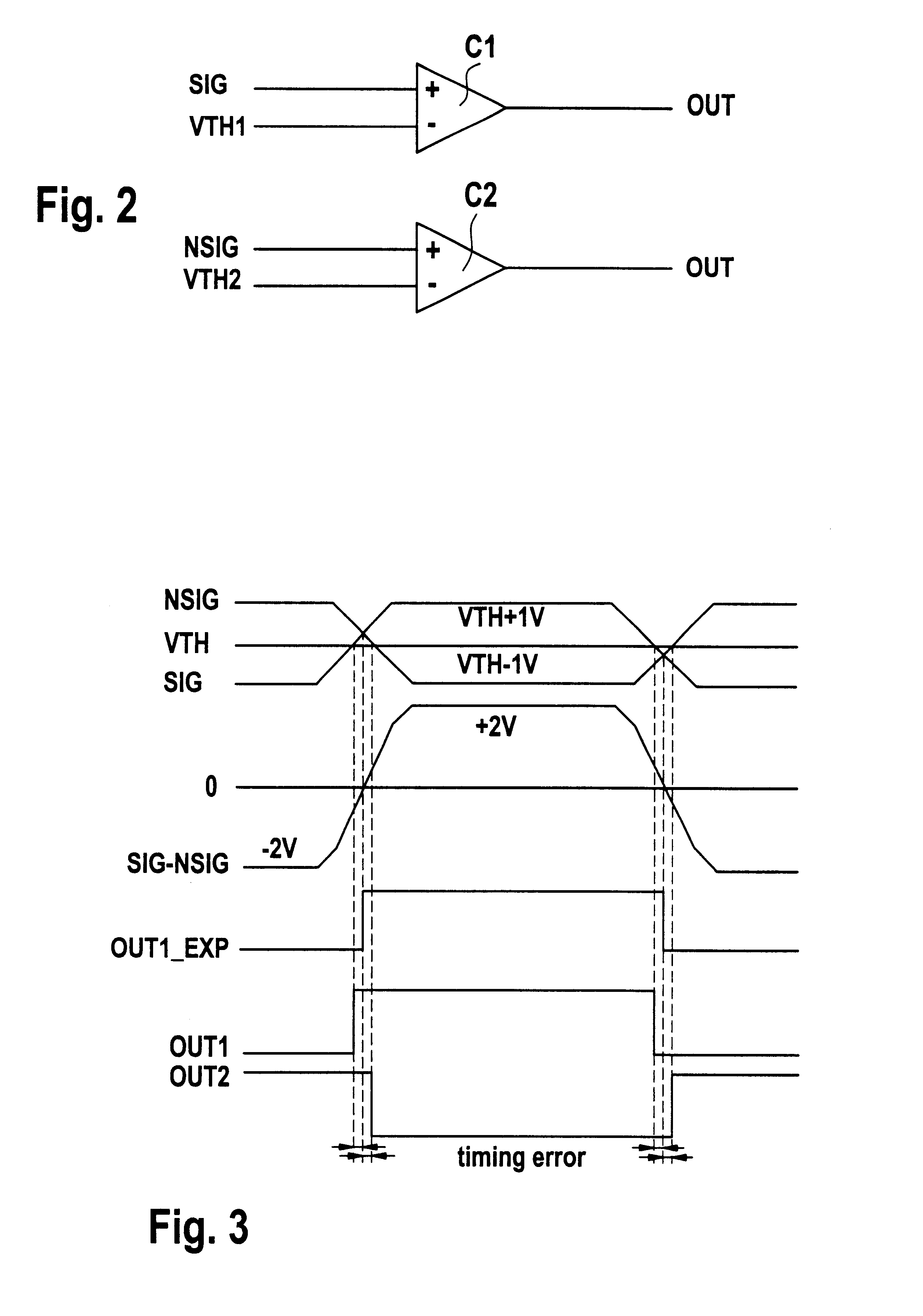

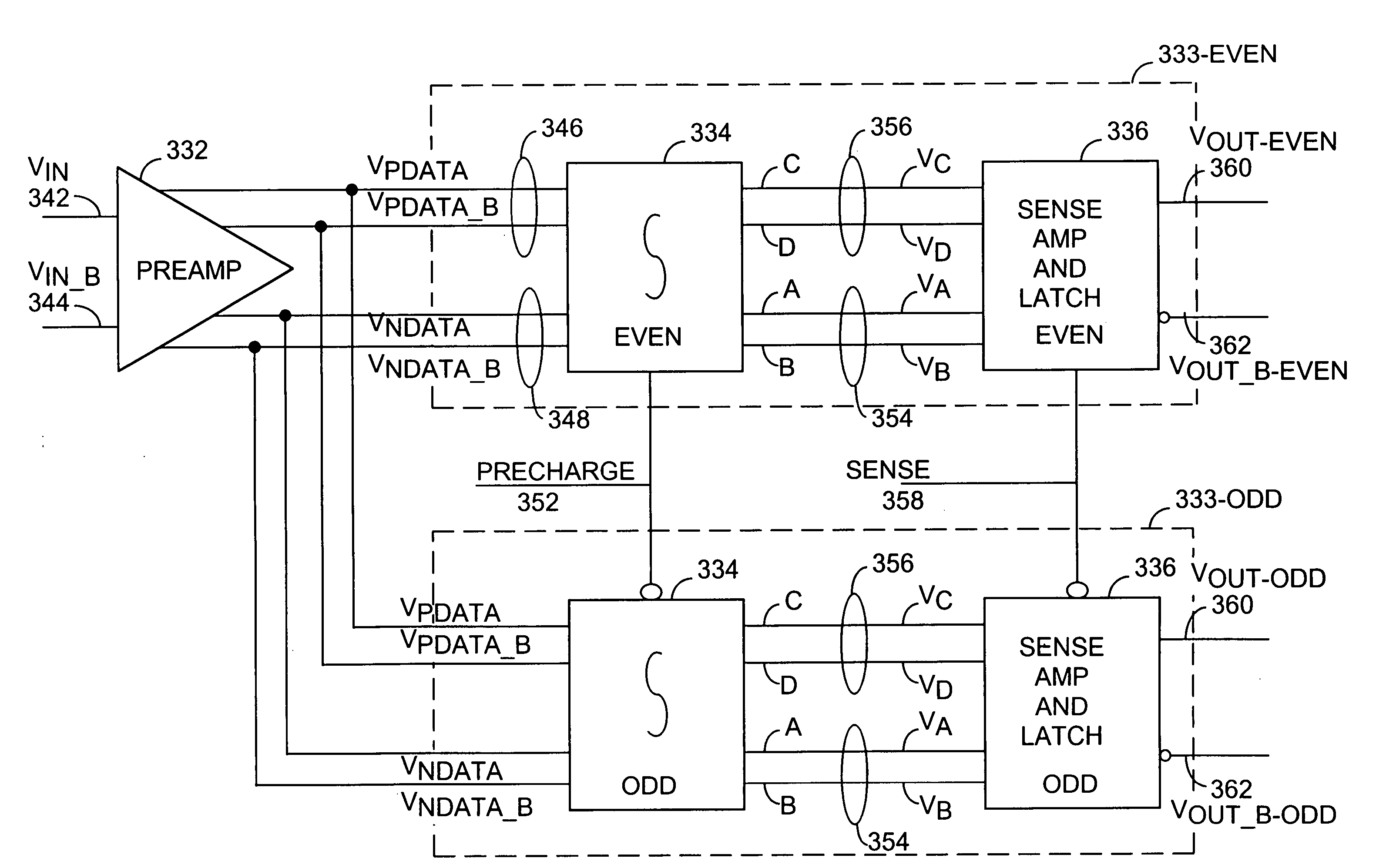

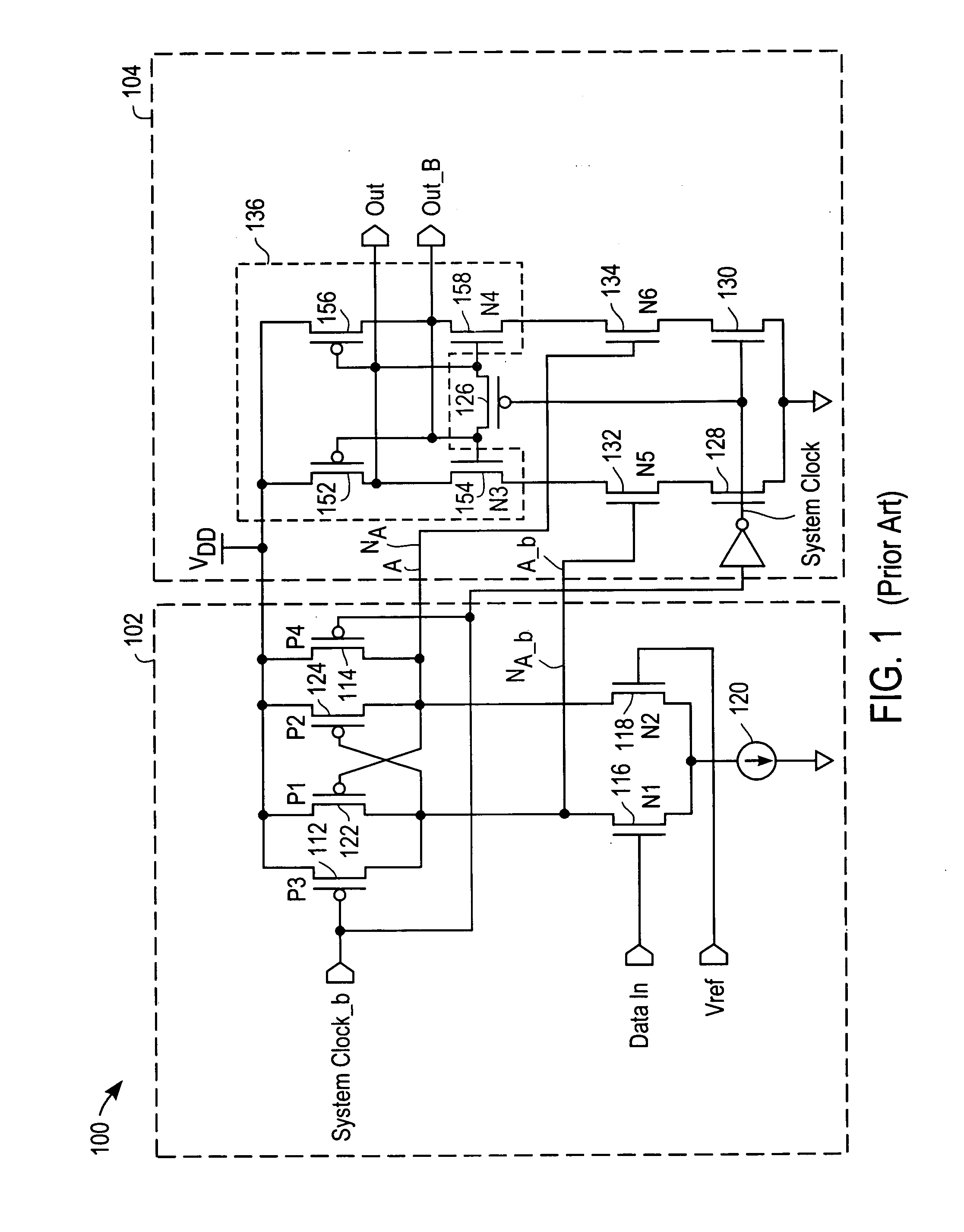

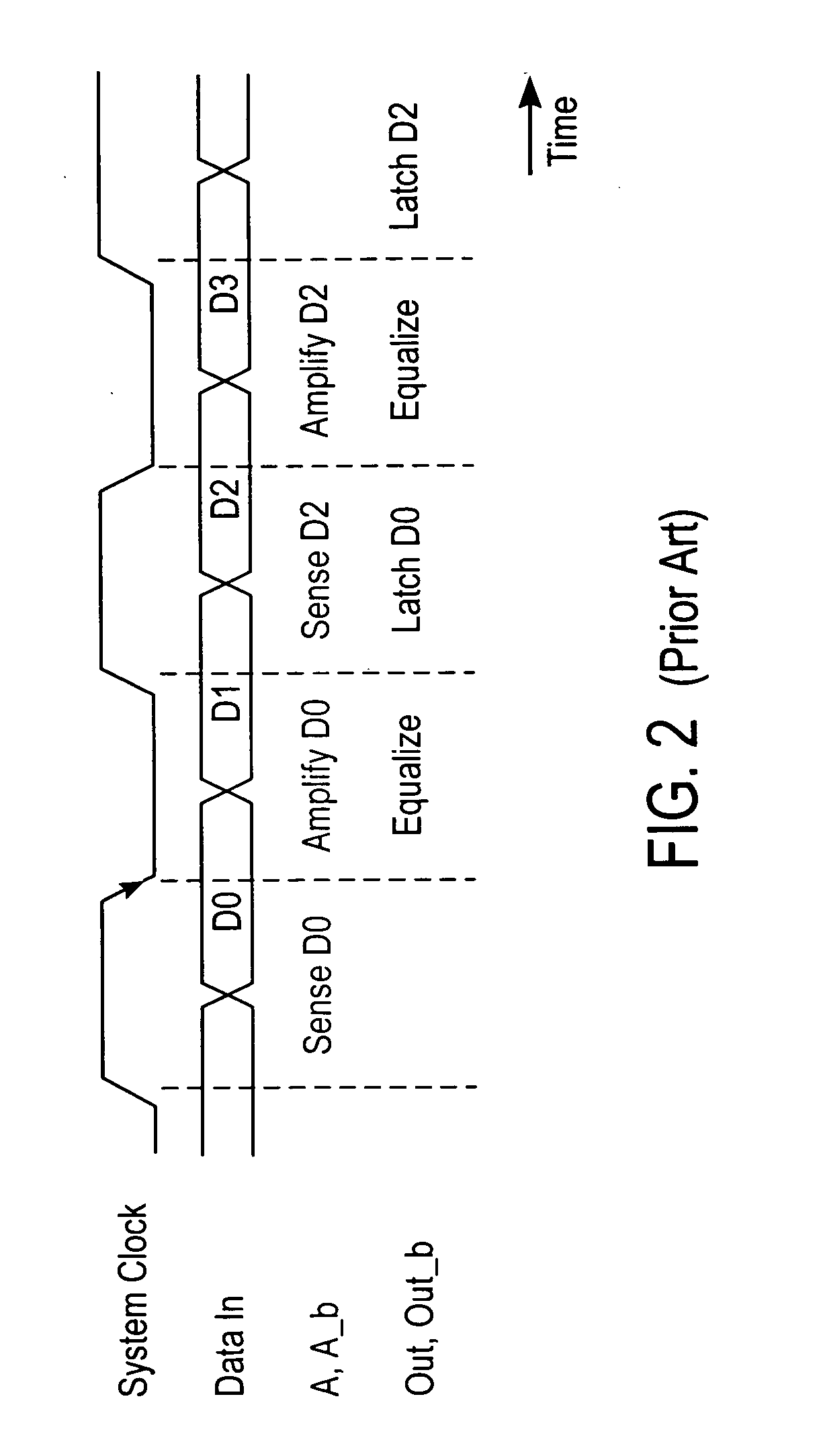

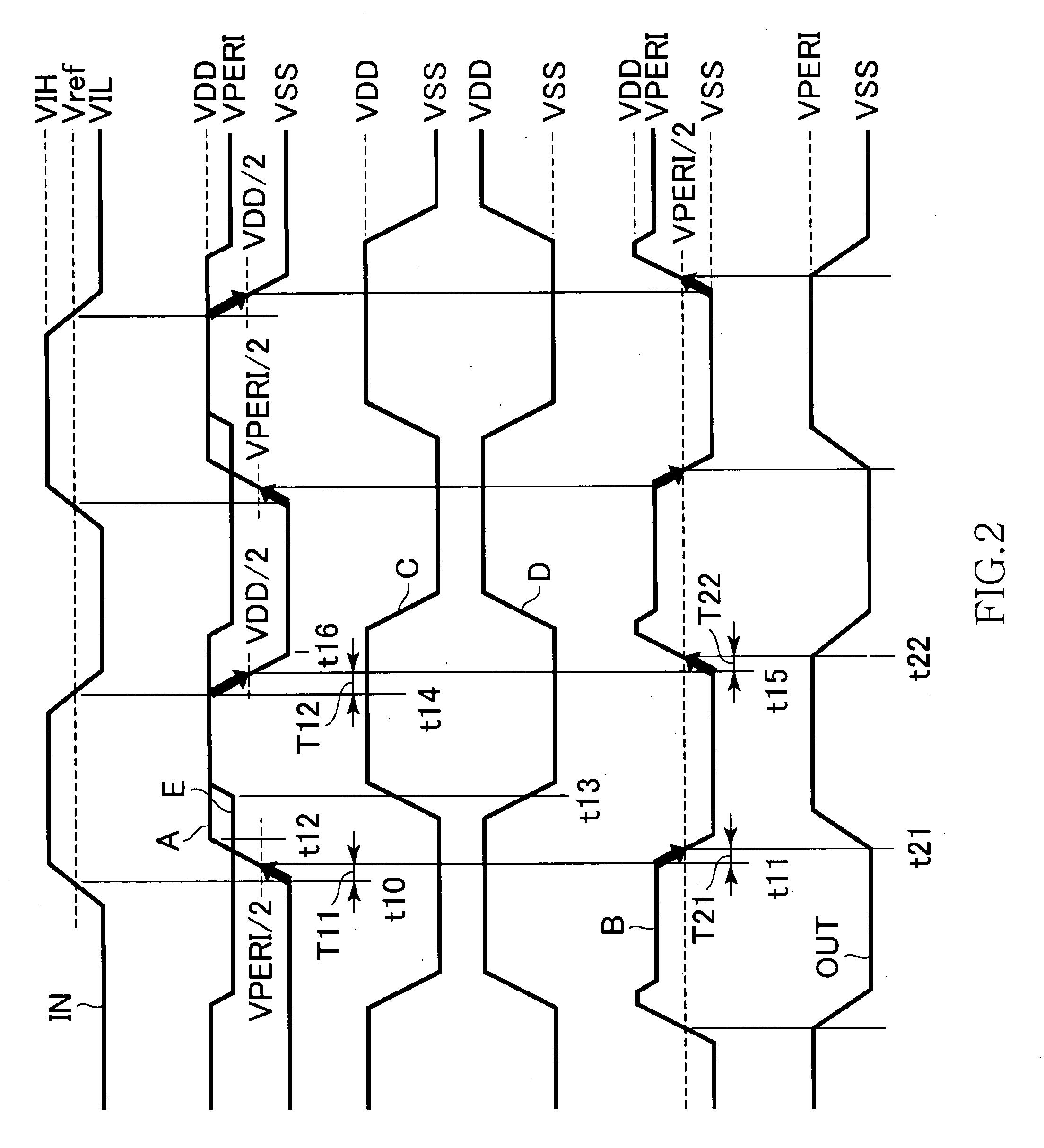

Method and apparatus for receiving high speed signals with low latency

InactiveUS6965262B2Reduces input-to-output latencyReduce static power consumptionDigital differential analysersDigital storageIntegratorAudio power amplifier

An apparatus and method for receiving high-speed signals having a wide common-mode range with low input-to-output latency. In one embodiment, the receiver includes an integrator to accumulate charge in accordance with an input signal during an integration time interval to produce an output voltage. A sense amplifier samples and converts the output voltage of the integrator to a logic signal; and a latch stores the logic signal. In an alternate embodiment, a preamplifier conditions the input signal prior to being integrated. In another embodiment using multiple receivers, circuitry is added to the receiver to compensate for timing errors associated with the distribution of the timing signals. In yet another embodiment, the integrator is coupled to an equalization circuit that compensates for intersymbol interference. In another embodiment, another circuit compensates for accumulated voltage offset errors in the integrator.

Owner:RAMBUS INC

Apparatus and method for independent control of on-die termination for ouput buffers of a memory device

An apparatus and method providing independent control of on-die termination (ODT) of output buffers. The ODTs for the buffer circuits of an input / output (I / O) buffer can be enabled and disabled in response to an ODT control signal. Additionally, the ODTs for a first set of the buffer circuits can be enabled and disabled responsive to the ODT control signal and the ODT for at least one of a second set of the buffer circuits is disabled.

Owner:ROUND ROCK RES LLC

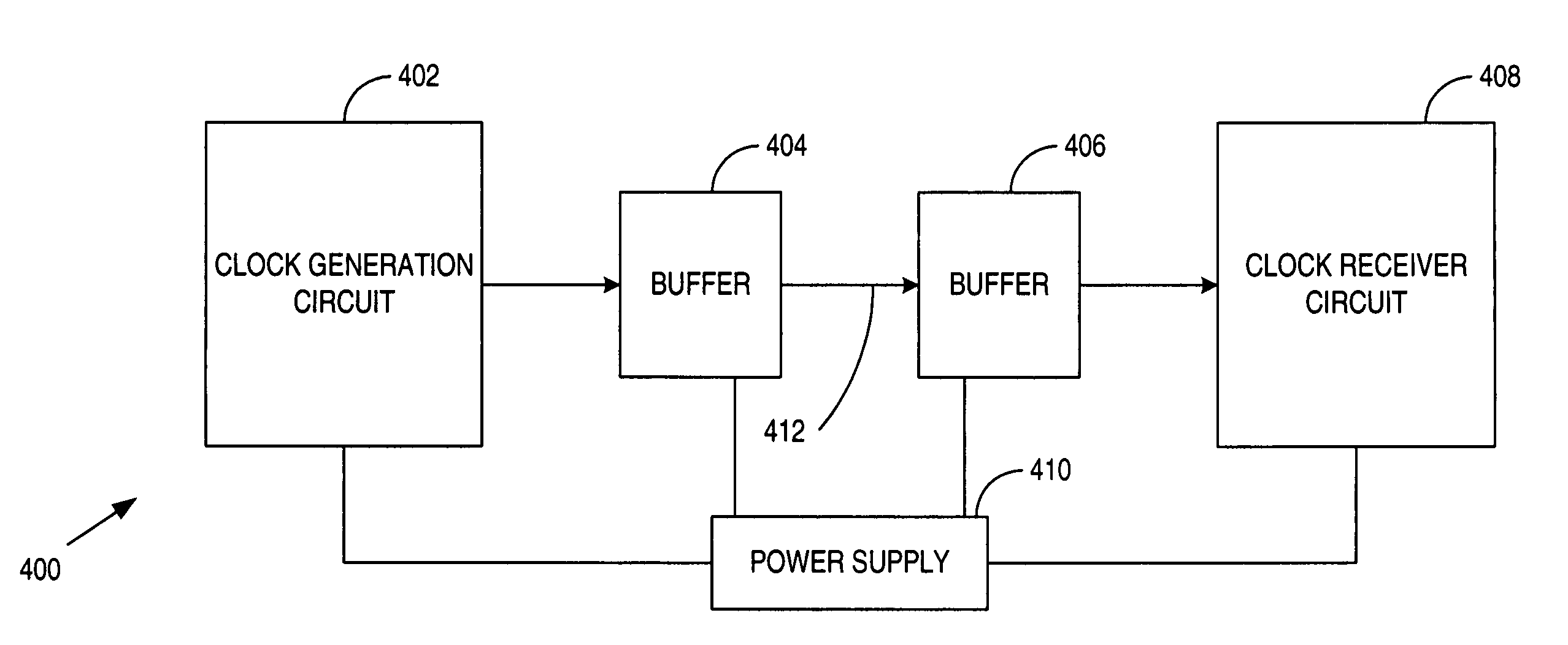

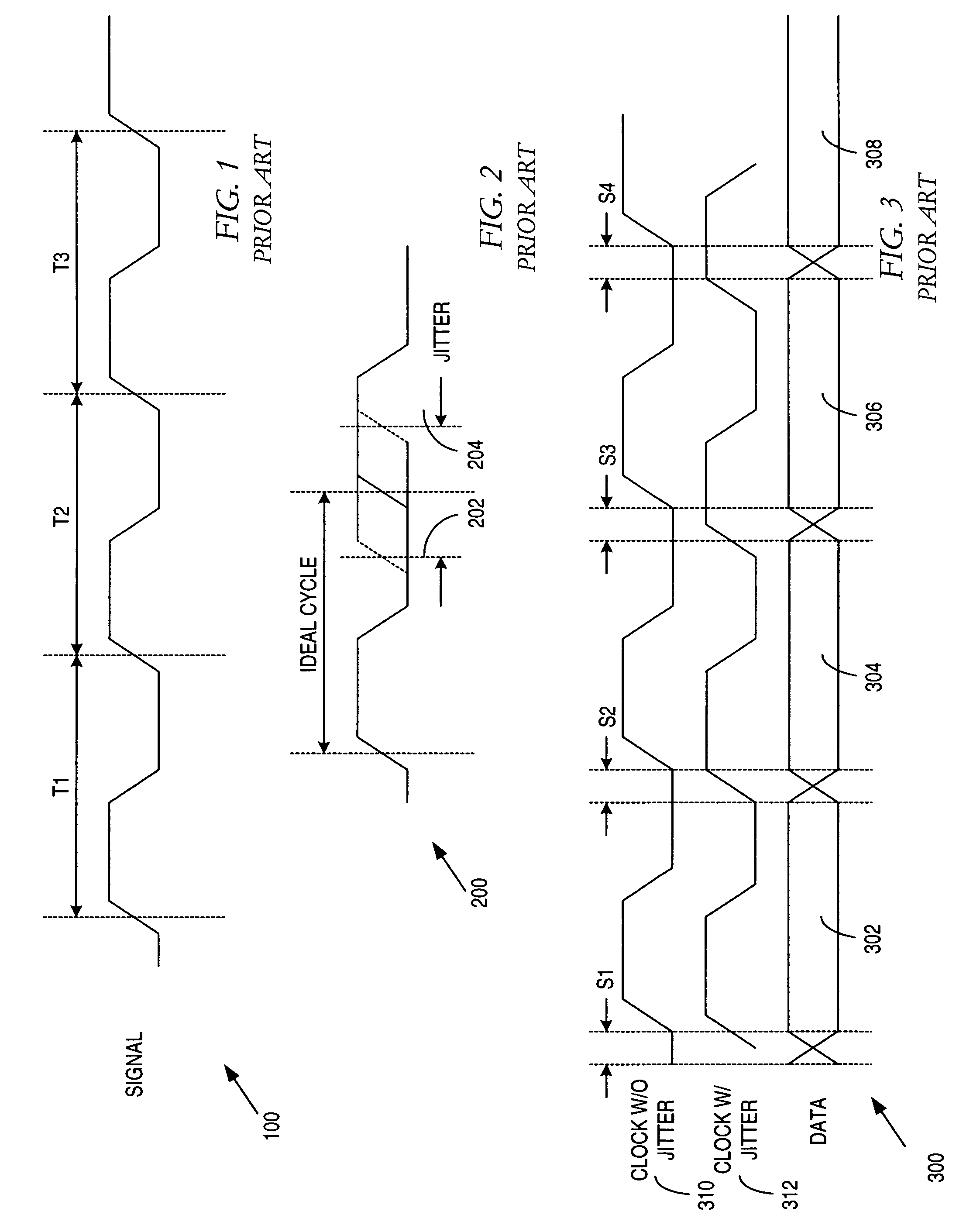

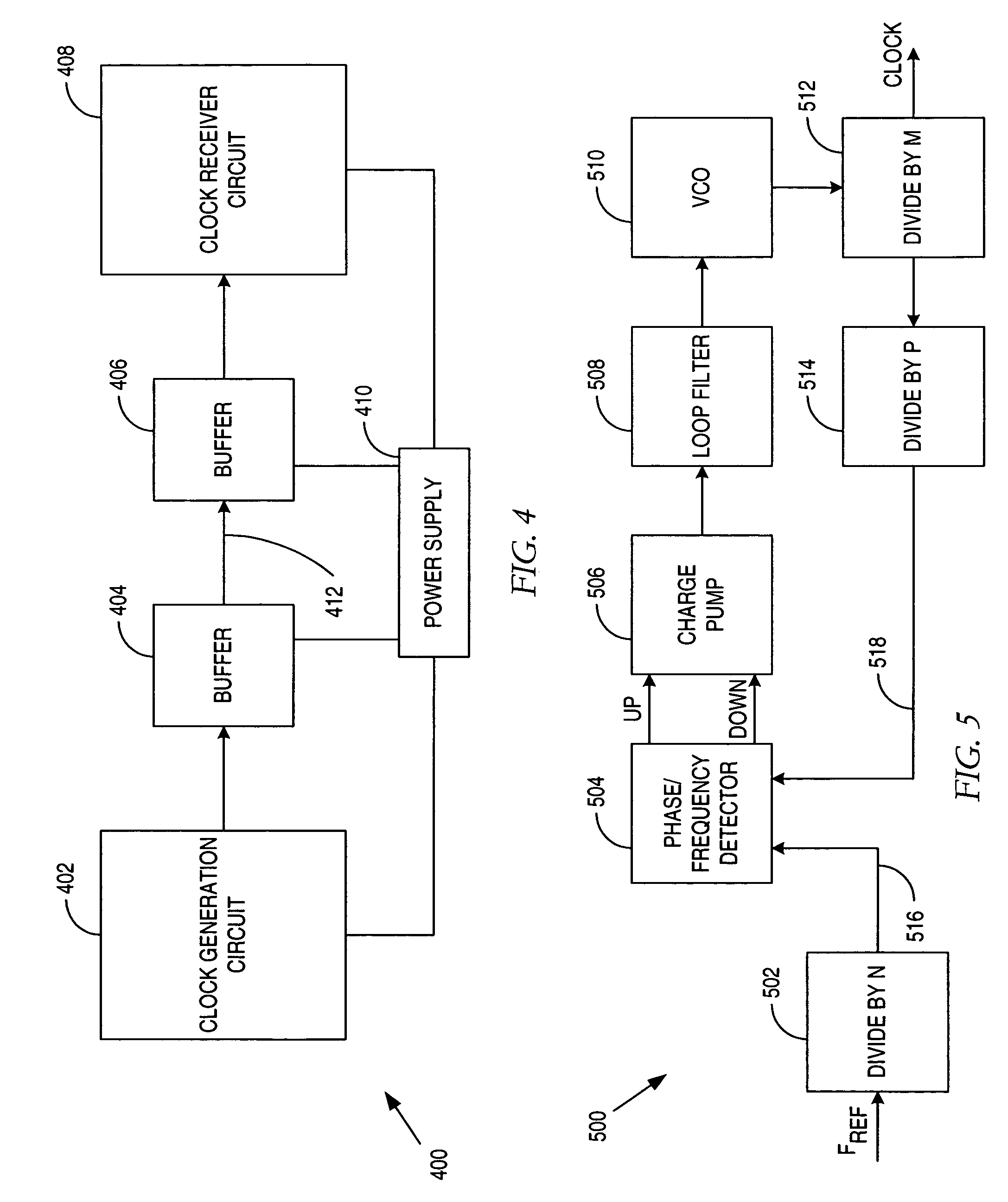

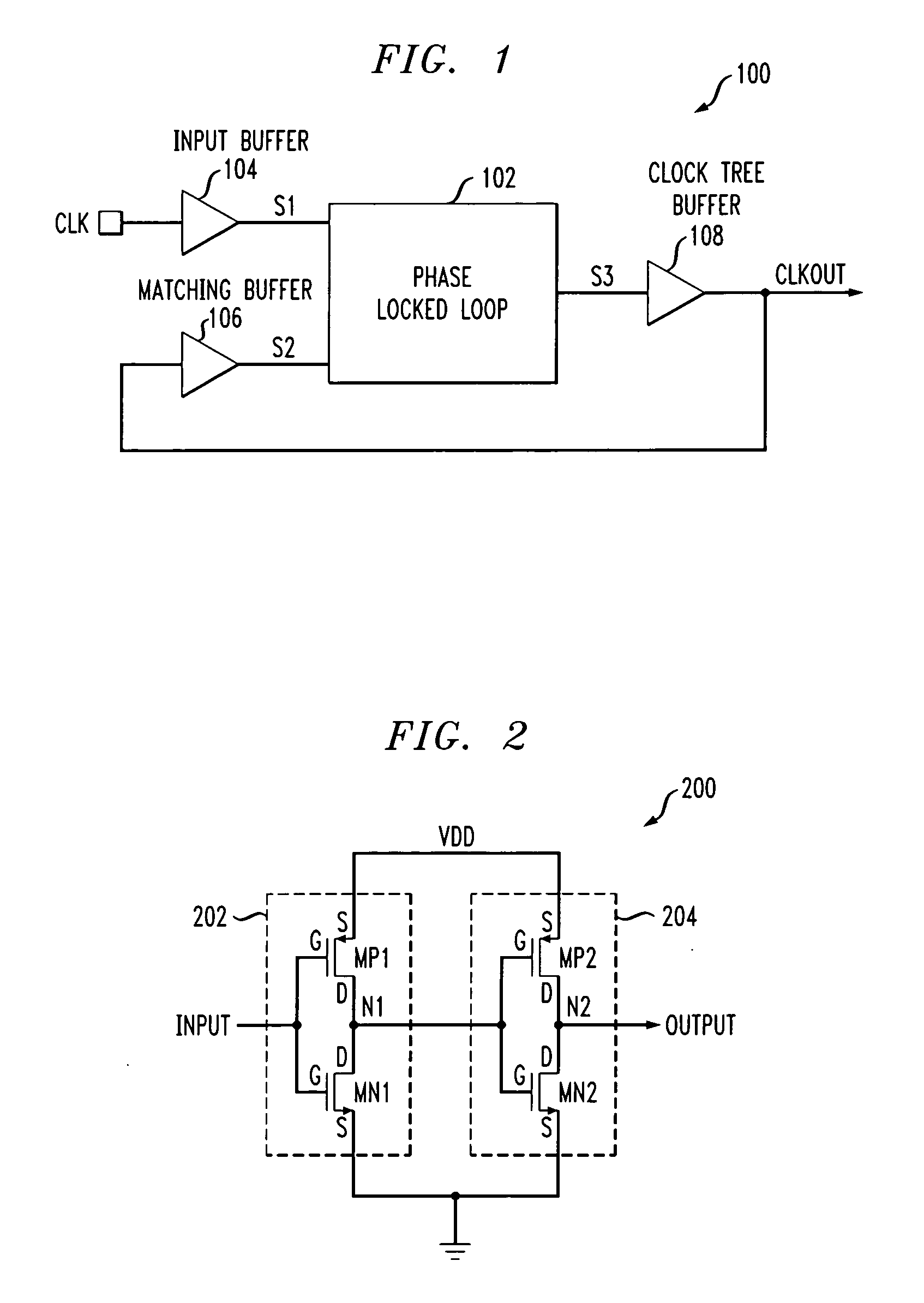

Method and apparatus for a reference clock buffer system

ActiveUS7142005B1Reduces power-supplyReduces noise-induced jitterPulse automatic controlElectronic switchingData bufferCross coupled

Owner:XILINX INC

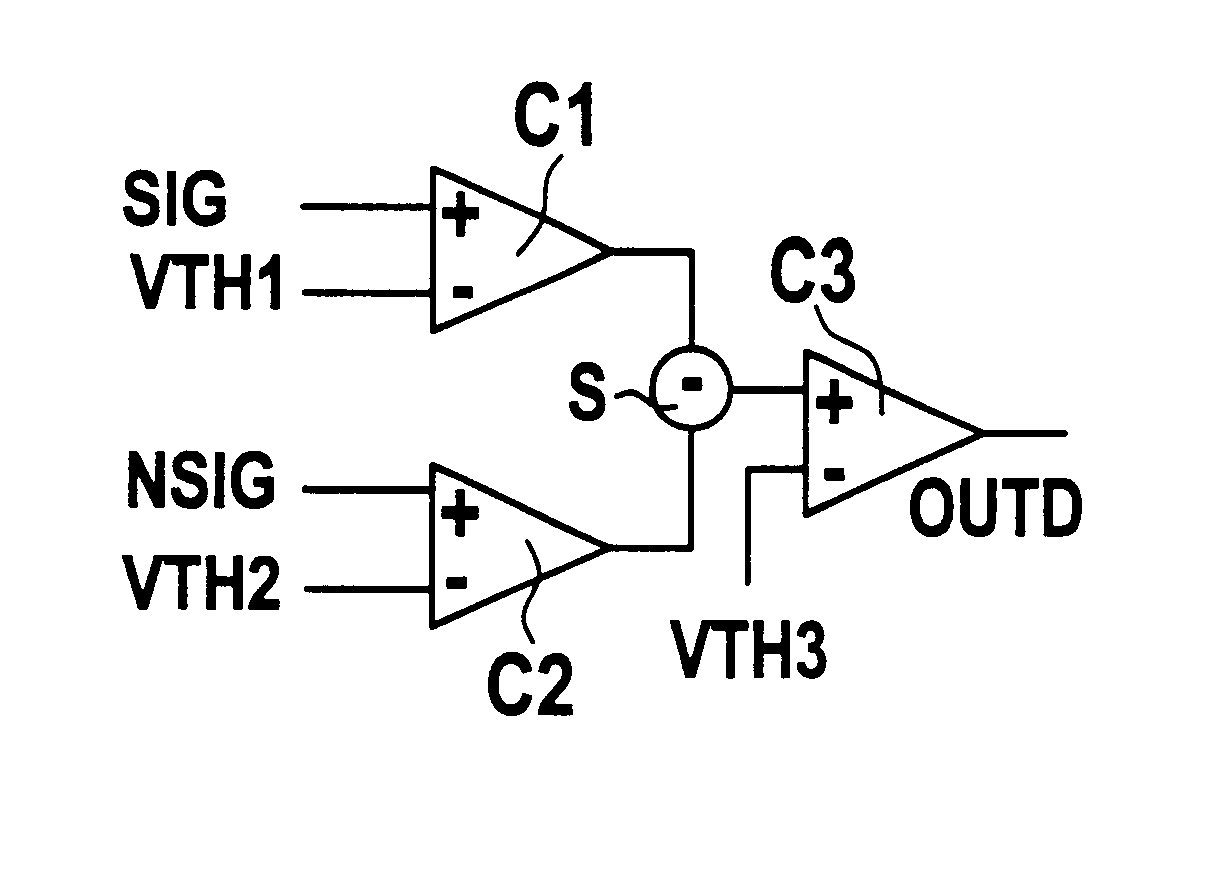

Circuit for providing a logical output signal in accordance with crossing points of differential signals

InactiveUS6448806B1Increase currentMinimal numberMultiple input and output pulse circuitsDigital circuit testingAudio power amplifierDifferential signaling

A circuit provides an output signal in accordance with crossing points of a differential signal, which includes a normal input signal and a complementary input signal. The circuit includes a first amplifier for amplifying a first signal difference between the normal input signal and a first threshold value, and for providing as a first output signal the amplified first signal difference. The circuit includes a second amplifier for amplifying a second signal difference between the complementary input signal and a second threshold value, and for providing as a second output signal the amplified second signal difference. The circuit also includes a first comparator for providing a first logical level when a third signal difference between the first output signal and the second output signal is greater than a third threshold value, and for providing a second logical level when the third signal difference is smaller than the third threshold value.

Owner:ADVANTEST CORP

Method and apparatus for receiving high speed signals with low latency

InactiveUS20060061405A1Reduce signal delayDigital differential analysersDigital storageIntegratorAudio power amplifier

An apparatus and method for receiving high-speed signals having a wide common-mode range with low input-to-output latency. In one embodiment, the receiver includes an integrator to accumulate charge in accordance with an input signal during an integration time interval to produce an output voltage. A sense amplifier samples and converts the output voltage of the integrator to a logic signal; and a latch stores the logic signal. In an alternate embodiment, a preamplifier conditions the input signal prior to being integrated. In another embodiment using multiple receivers, circuitry is added to the receiver to compensate for timing errors associated with the distribution of the timing signals. In yet another embodiment, the integrator is coupled to an equalization circuit that compensates for intersymbol interference. In another embodiment, another circuit compensates for accumulated voltage offset errors in the integrator.

Owner:RAMBUS INC

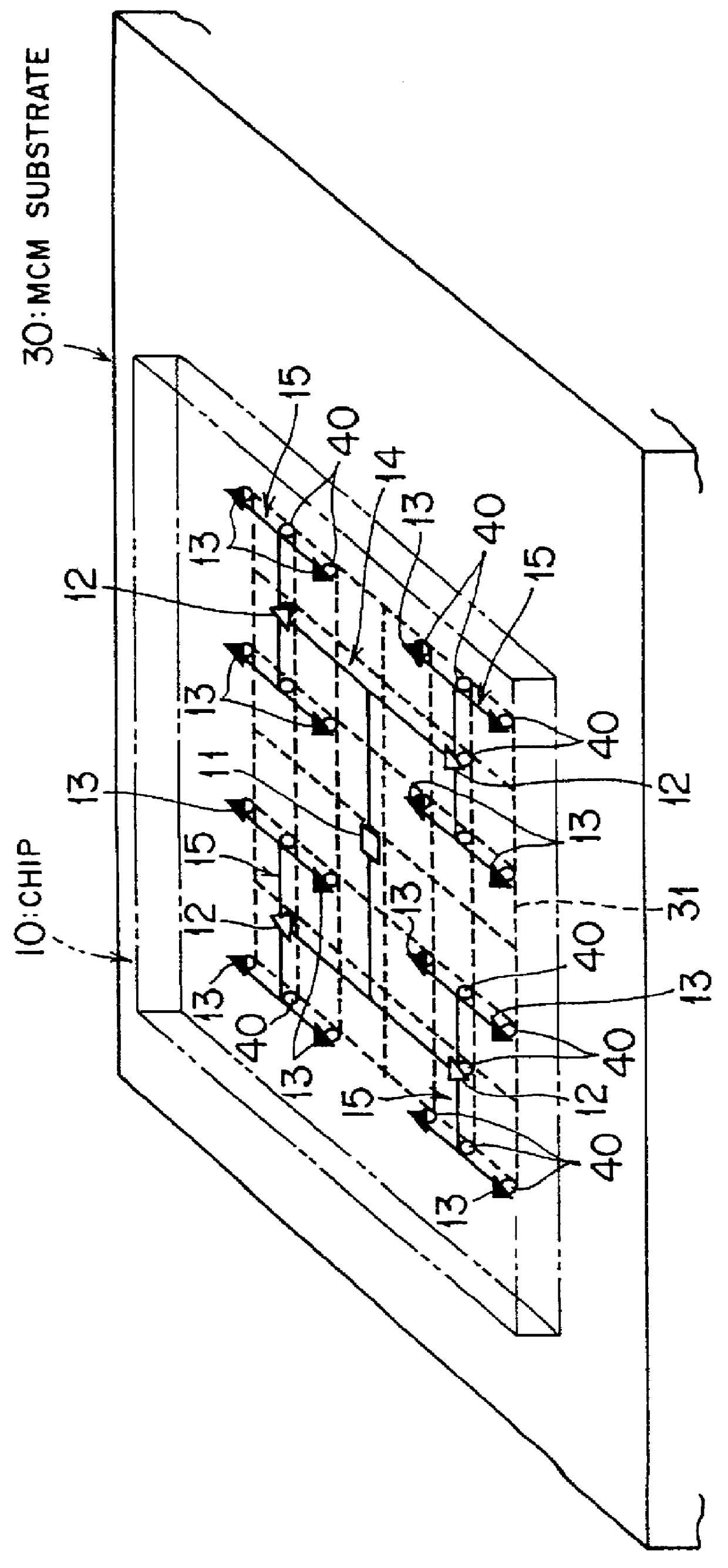

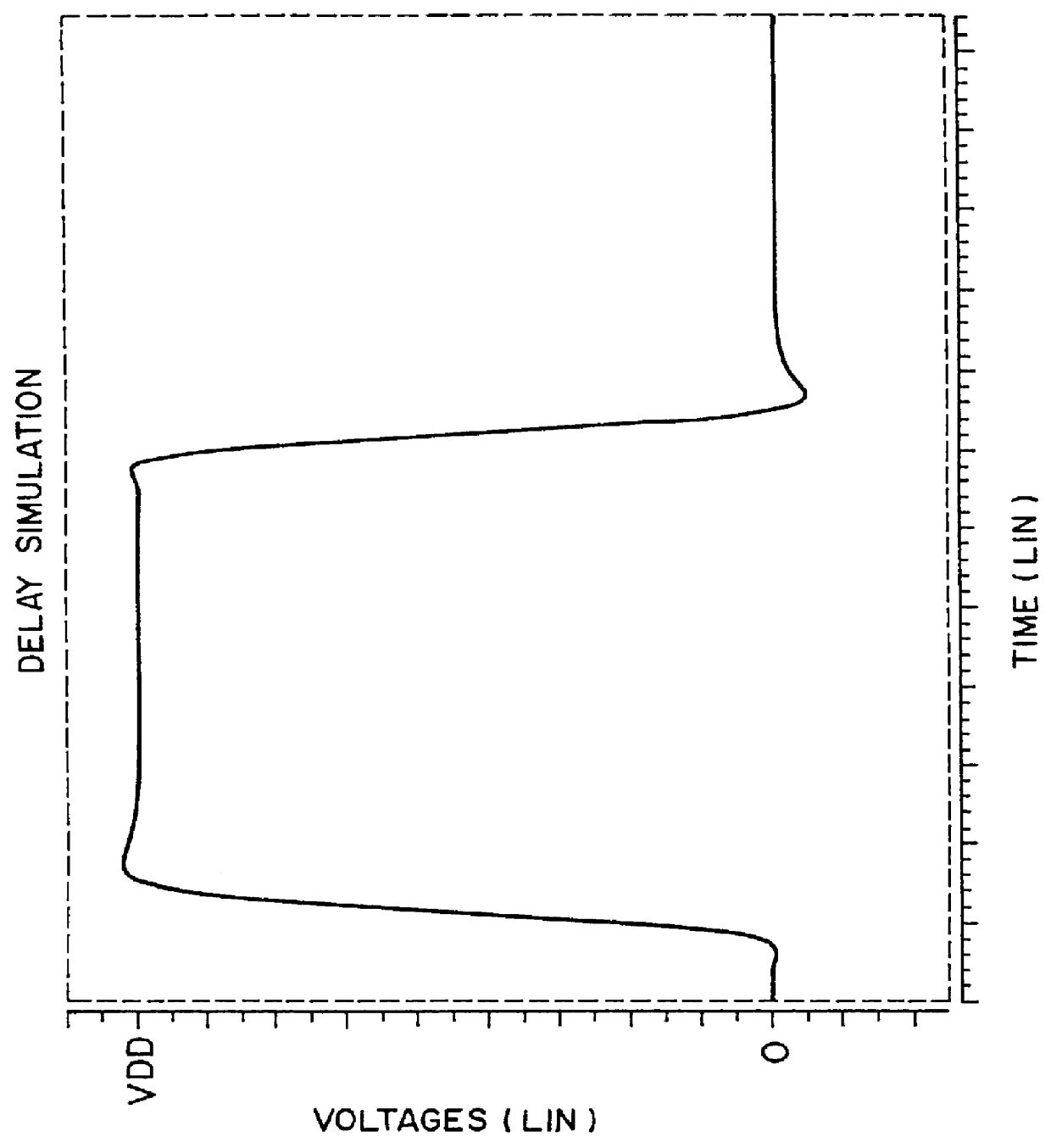

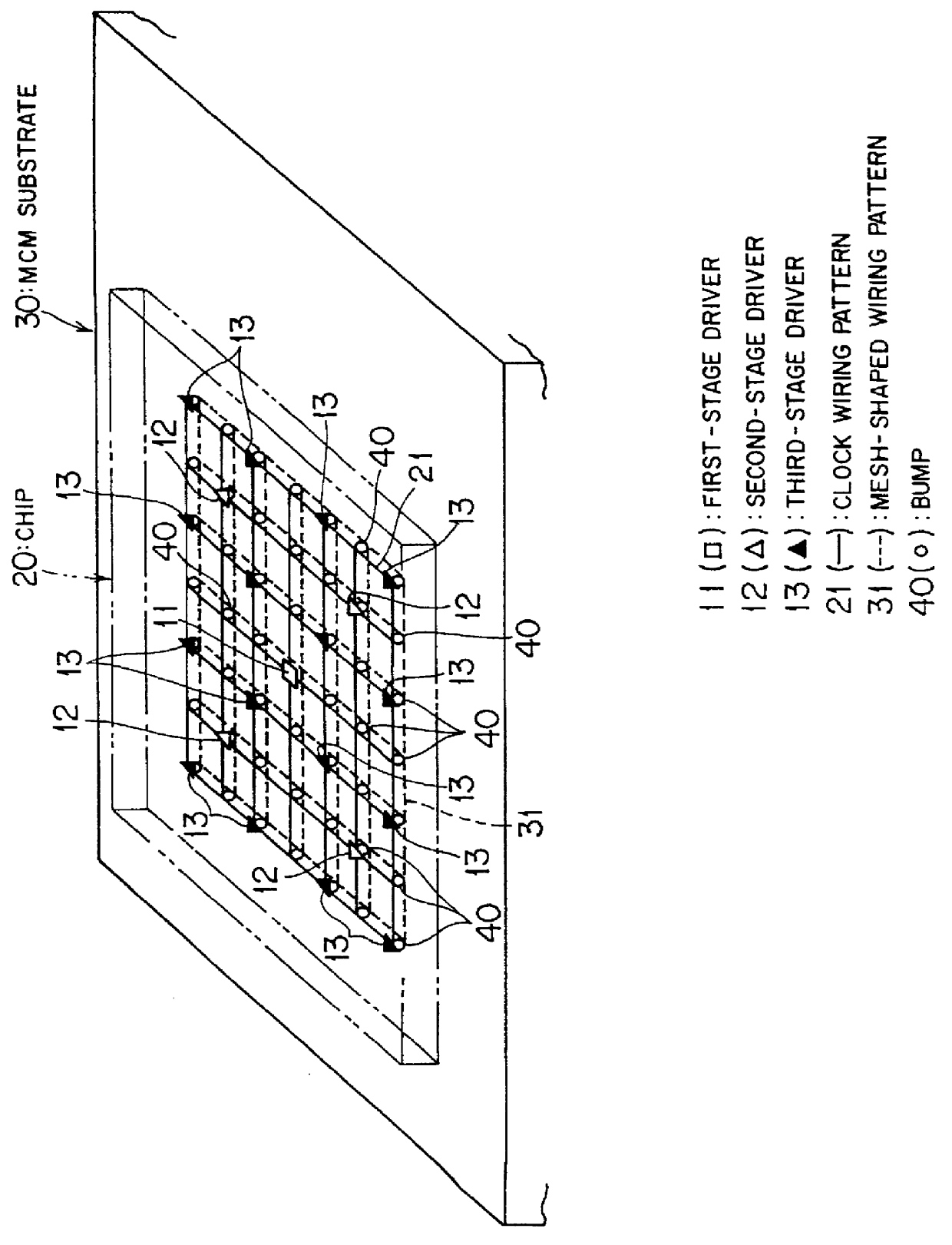

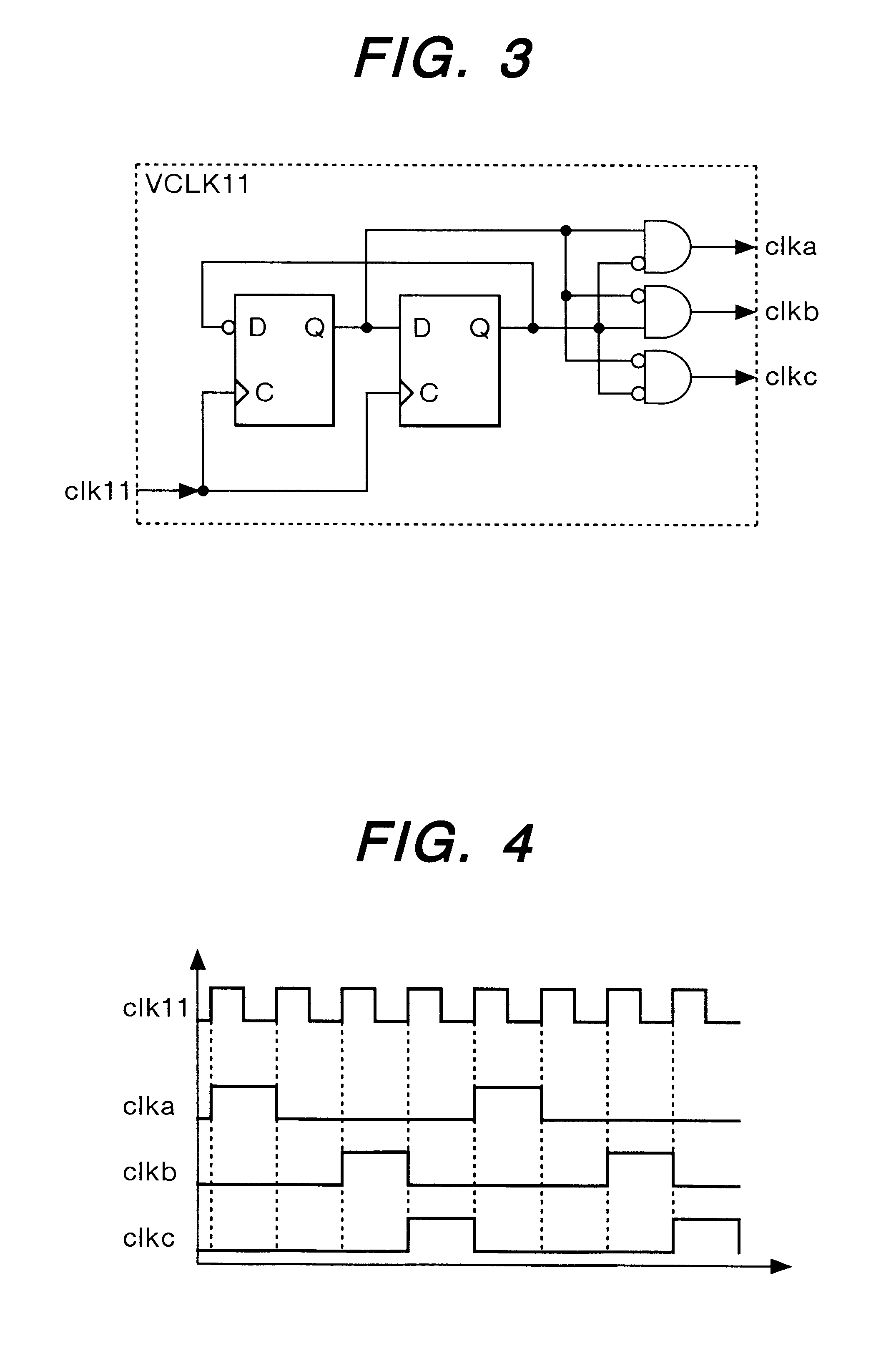

Clock distribution circuit in a semiconductor integrated circuit

InactiveUS6037820AElectric pulse generatorDelay compensationElectrical resistance and conductanceComputer module

A clock distribution circuit reliably reduces clock skew, while preventing the waveform of a clock signal from rounding, which would otherwise occur due to an increase in resistance, and preventing instability of the clock signal, which would otherwise occur due to an increase in inductance, thereby realizing ideal clock distribution. In the clock distribution circuit, a clock wiring pattern for distributing the clock signal is formed on a chip, and a wiring pattern whose resistance is lower than the clock wiring pattern is formed on a substrate, on which the chip is mounted, in such a way as to be connected to the clock wiring pattern at a plurality of locations. The clock distribution circuit is applied to semiconductor integrated circuits such as LSIs built in multichip modules.

Owner:FUJITSU LTD

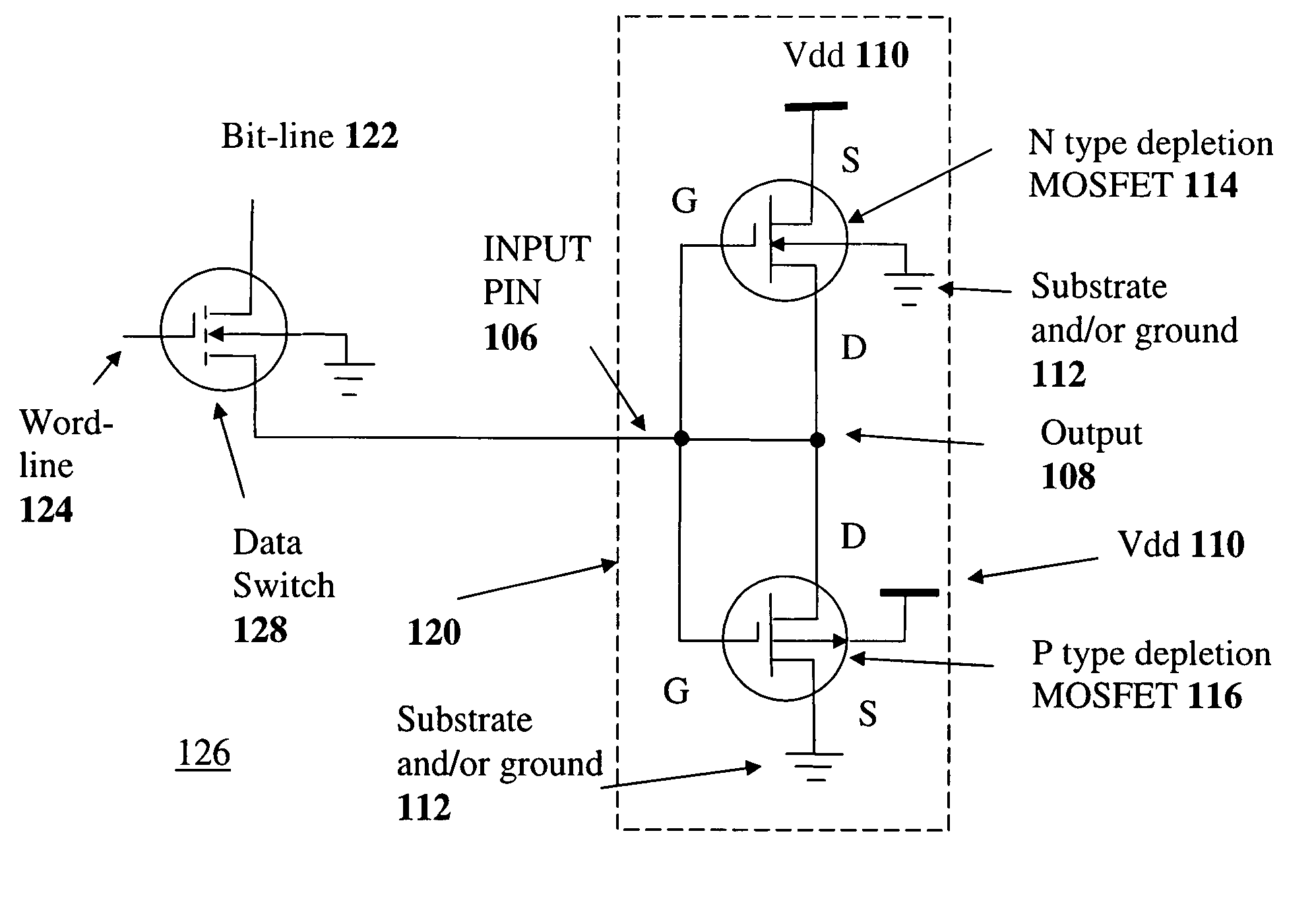

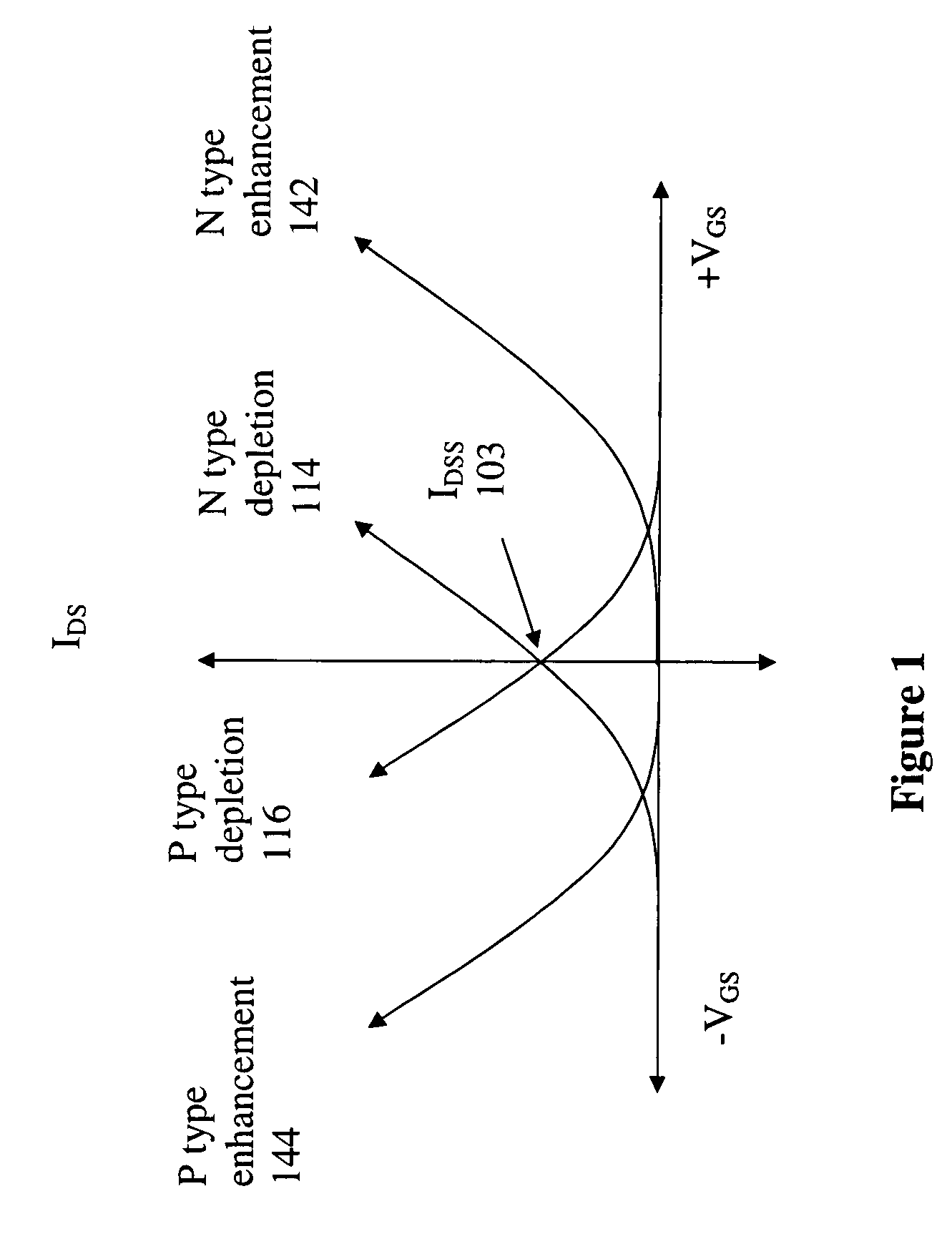

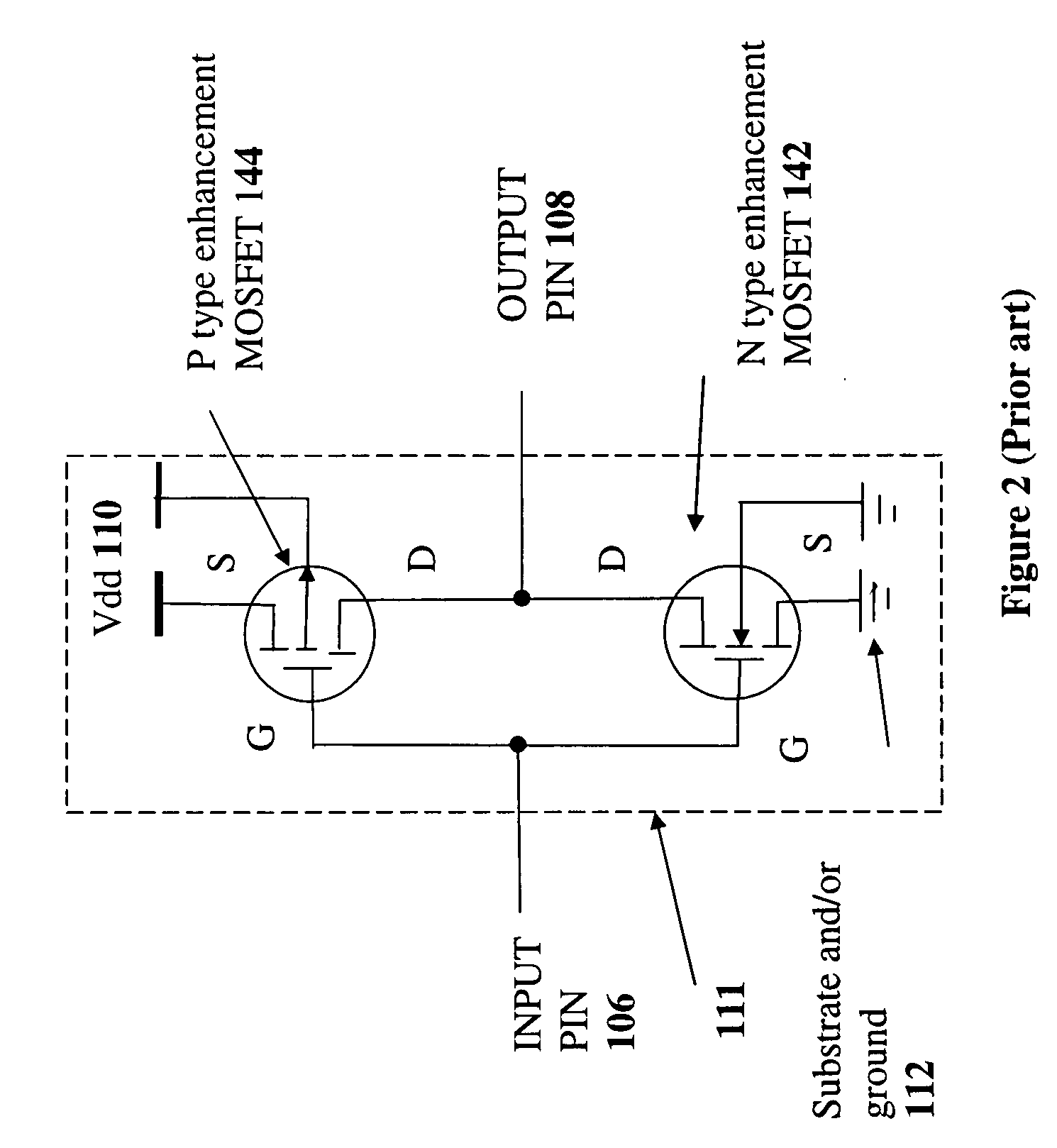

Depletion-mode mosfet circuit and applications

ActiveUS20080175045A1TransistorLogic circuits characterised by logic functionCMOSStatic random-access memory

Positive logic circuits, systems and methods using MOSFETs operated in a depletion-mode, including electrostatic discharge protection circuits (ESD), non-inverting latches and buffers, and one-to-three transistor static random access memory cells. These novel circuits supplement enhancement-mode MOSFET technology and are also intended to improve the reliability of the complementary metal-oxide-semiconductor (CMOS) integrated circuit (IC) products.

Owner:LIN WEN T

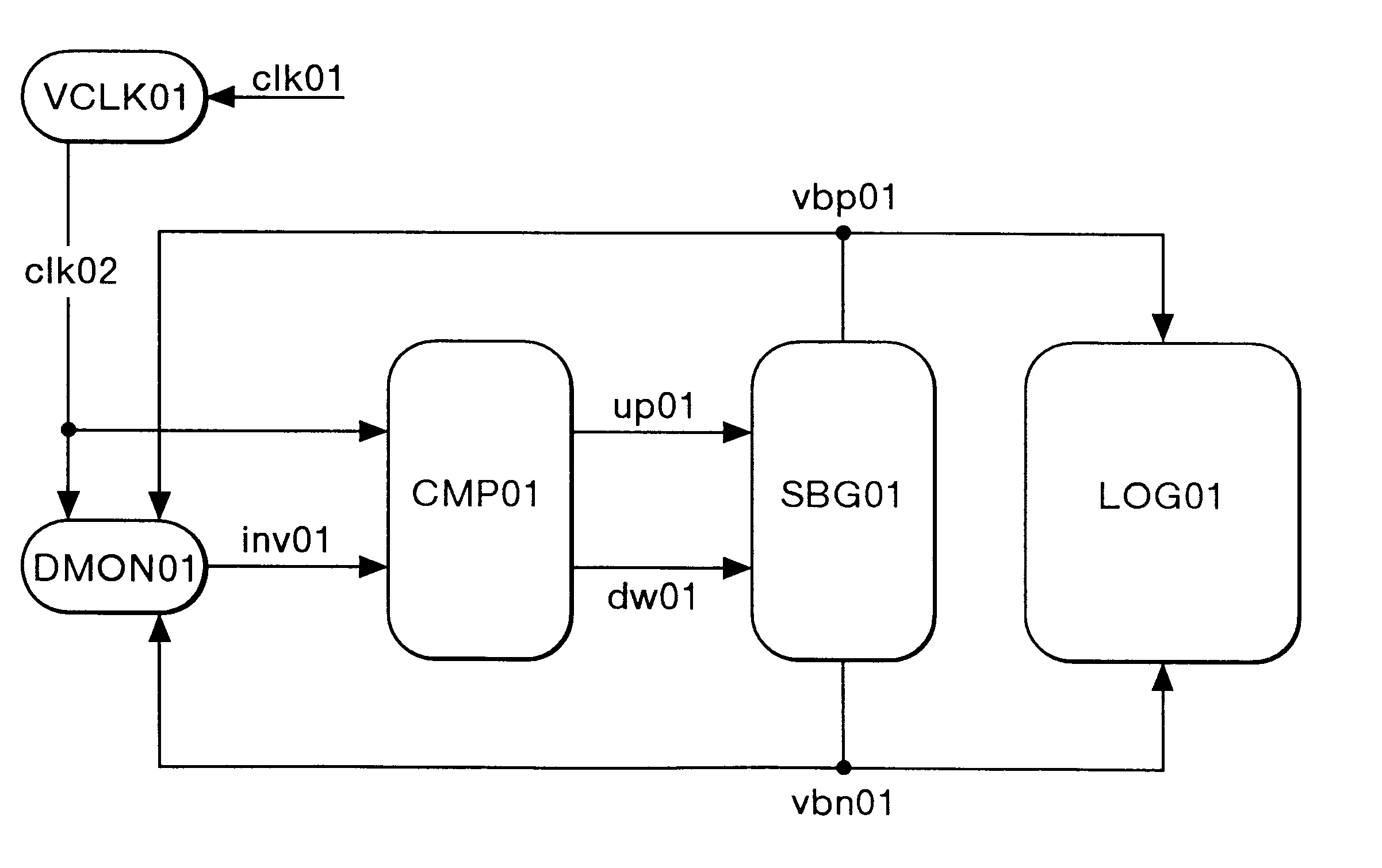

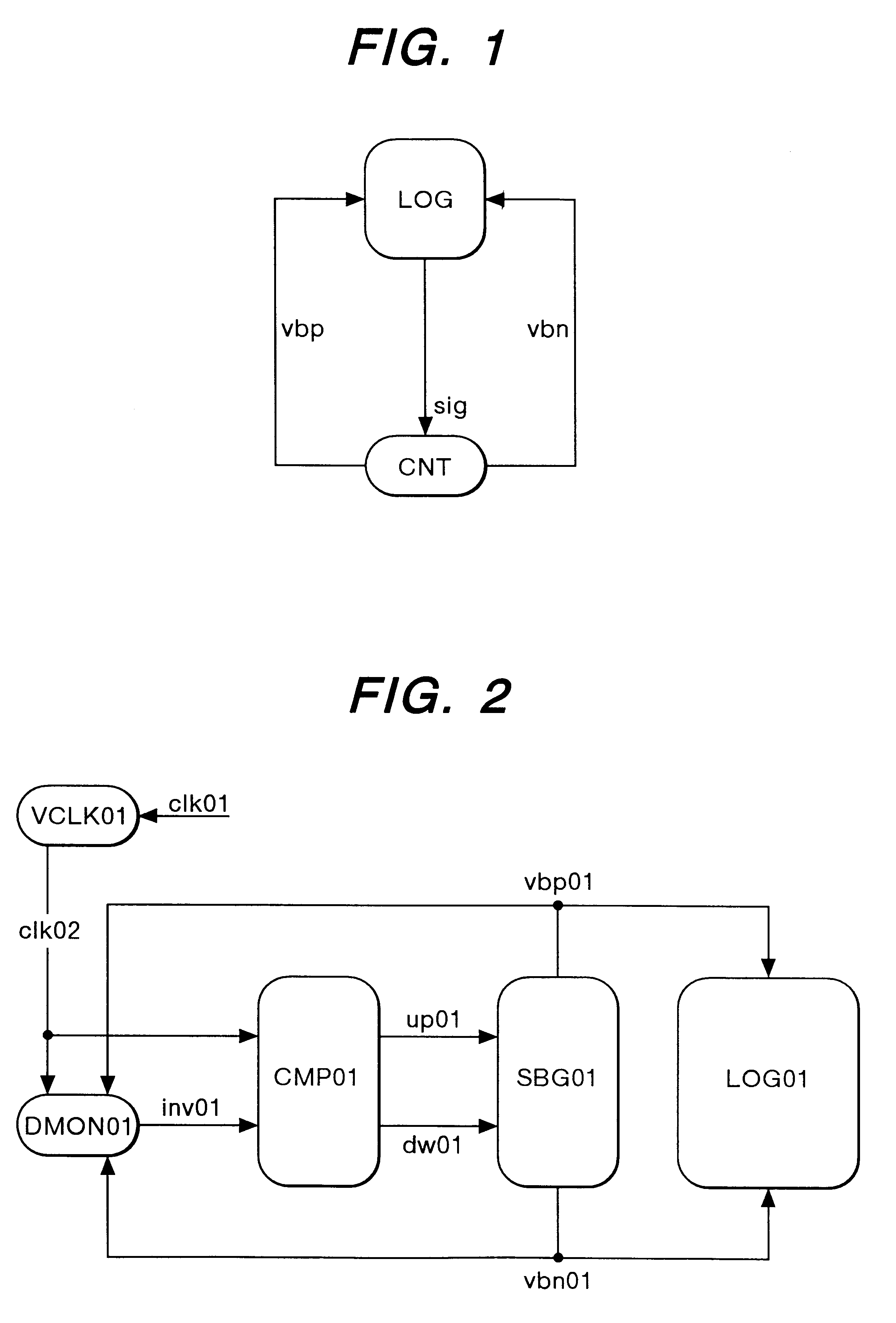

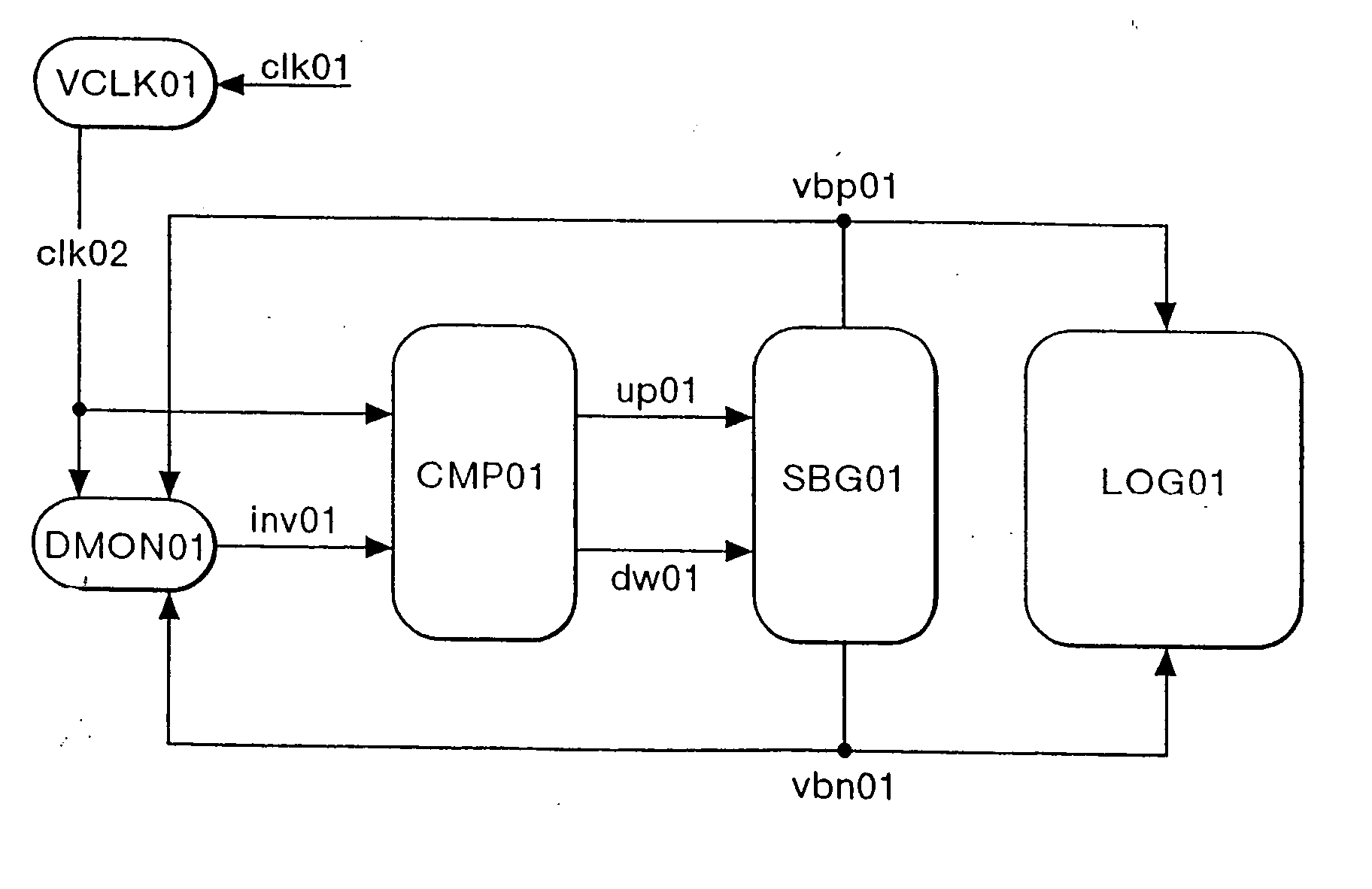

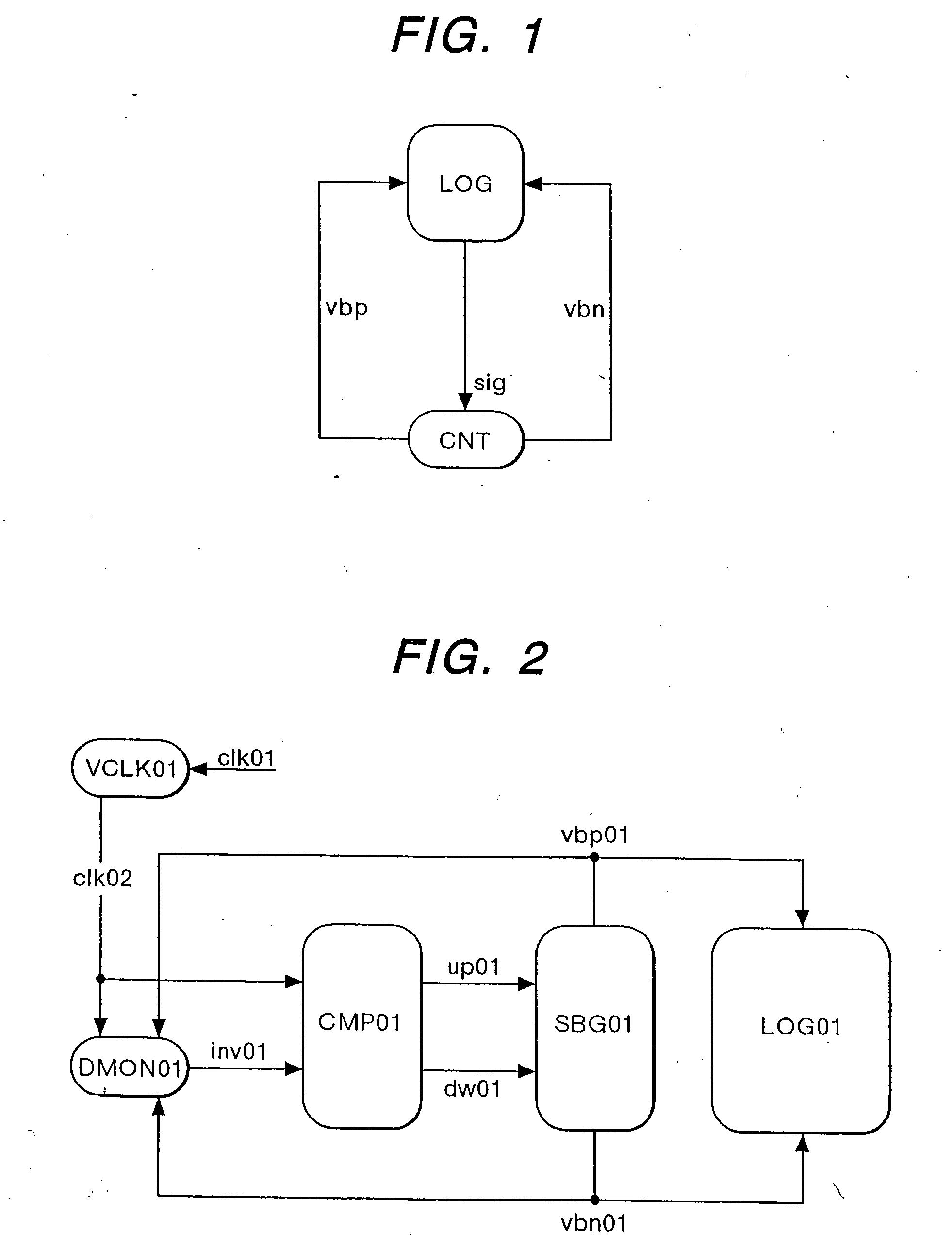

Semiconductor integrated circuit device

InactiveUS6489833B1Accurate detectionHigh speedLogic circuits coupling/interface using field-effect transistorsDelay compensationControl signalEngineering

A semiconductor integrated circuit device includes a logic circuit, a digital-to-analog converter generating a substrate bias for controlling a threshold voltage of an MIS transistor of the logic circuit, a voltage control circuit outputting a control signal in accordance with a delay signal, and a delay detector, including a circuit which monitors variations in operating speed of the delay detector. The delay detector receives the clock signal and outputs the delay signal. The voltage control circuit receives the delay signal and outputs the control signal according to a delay indicated by the delay signal. The digital-to-analog converter receives the control signal from the voltage control circuit and generates a voltage according to the control signal. The operating speed of each of the logic circuits and the delay detector is controlled by a voltage supplied from the digital-to-analog converter.

Owner:RENESAS ELECTRONICS CORP

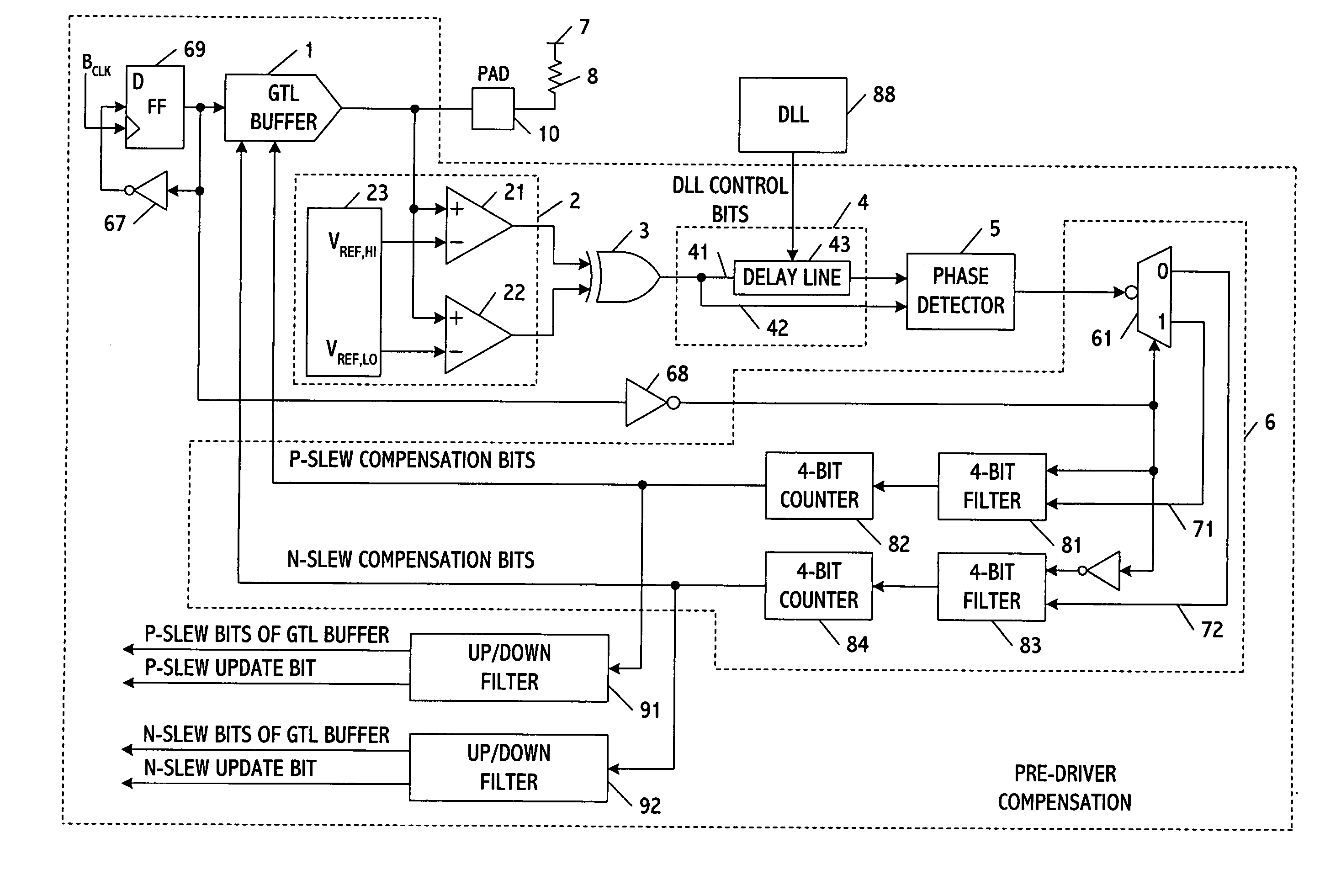

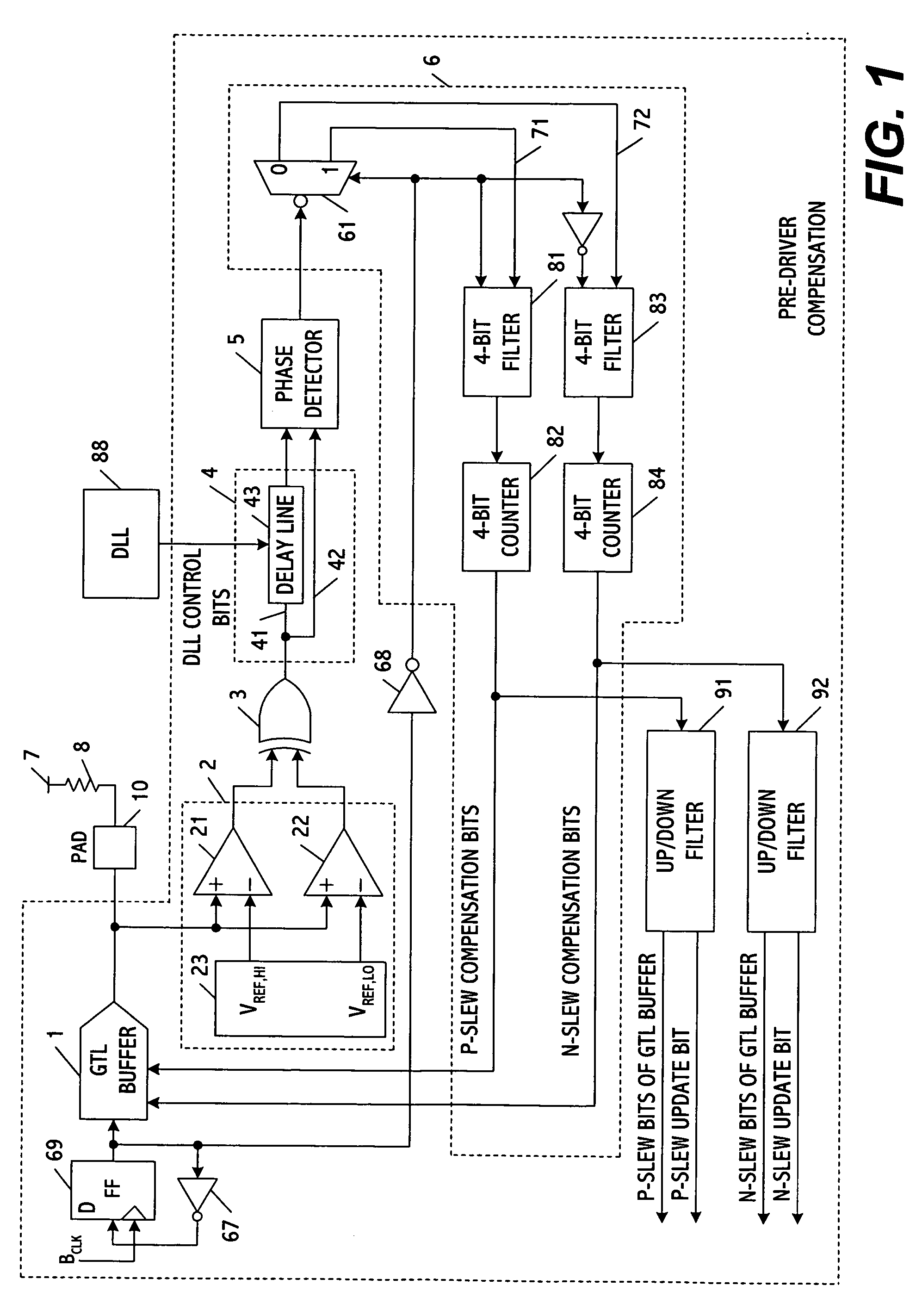

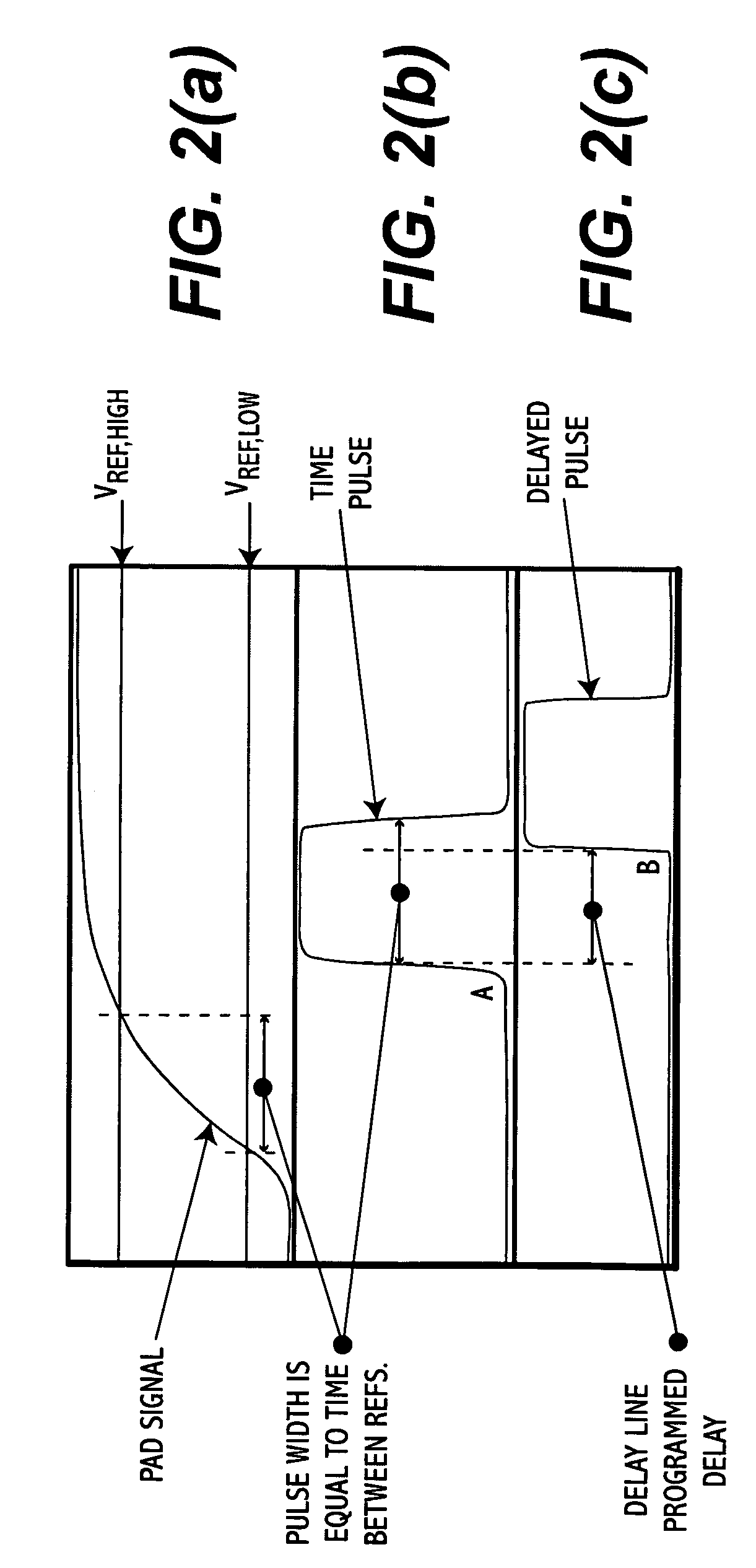

Closed-loop independent DLL-controlled rise/fall time control circuit

A system and method for processing signals determines rise and fall times of a driving signal, compares the rise and fall times to desired values, and independently controls the rise and fall times to equal the desired values. The rise and fall times may be controlled by generating one or more first correction bits based on a difference between the rise time and a corresponding one of the desired values, generating one or more second correction bits based on a difference between the fall time and a corresponding one of the desired values, and then separately applying the bits to independently control the rise and fall times of the driving signal. The driving signal may be an I / O signal or another type of signal.

Owner:TAHOE RES LTD

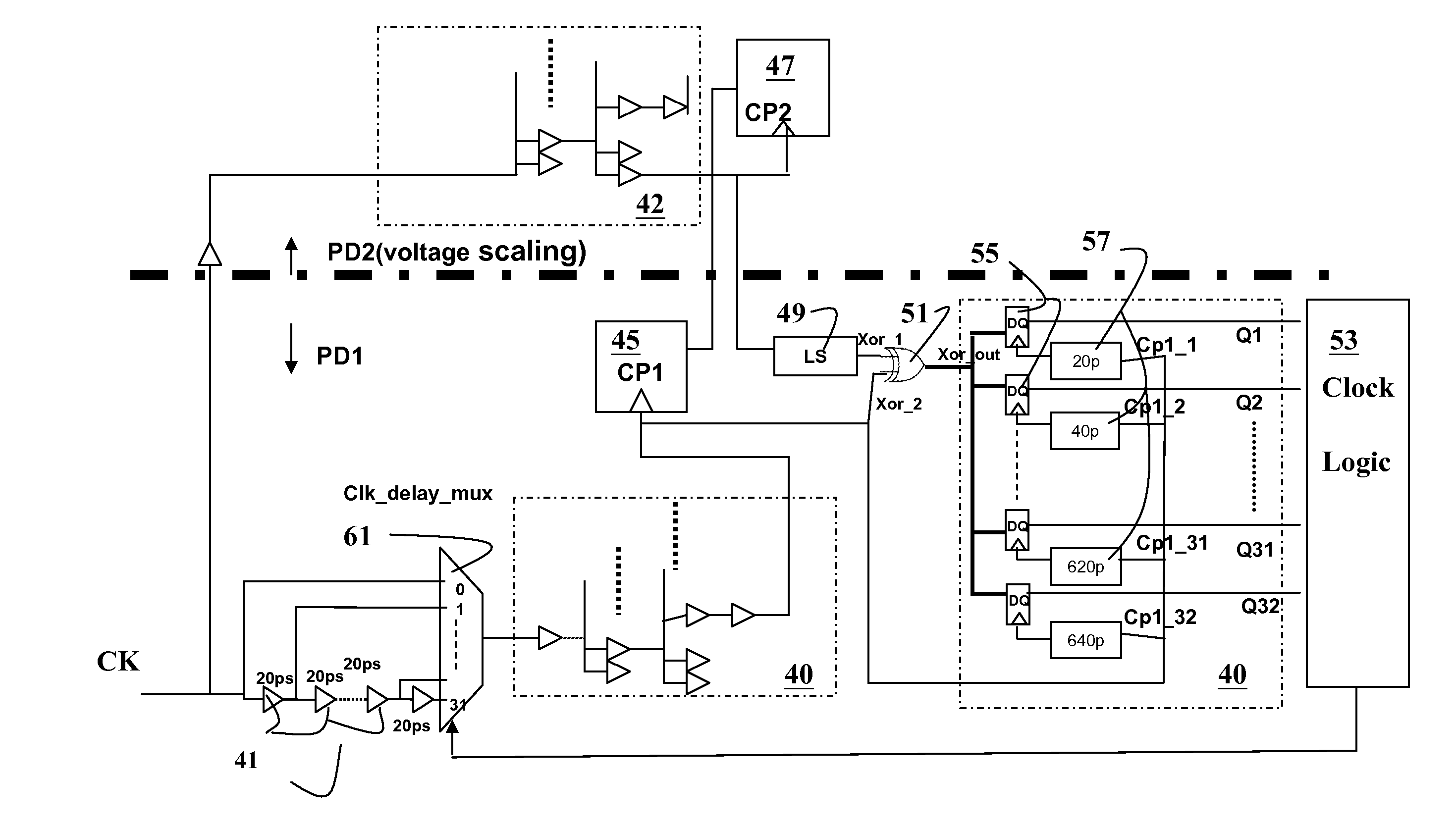

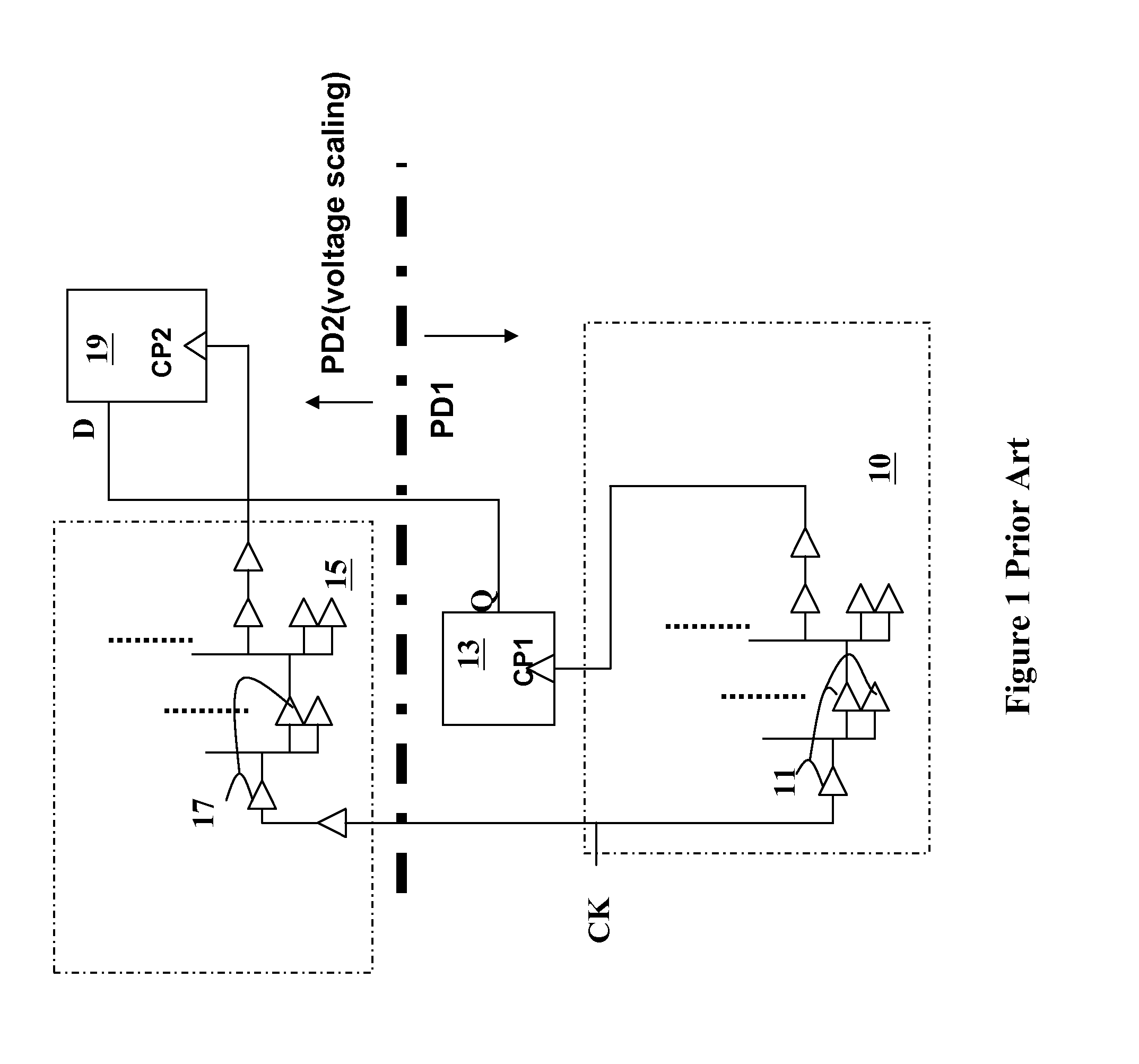

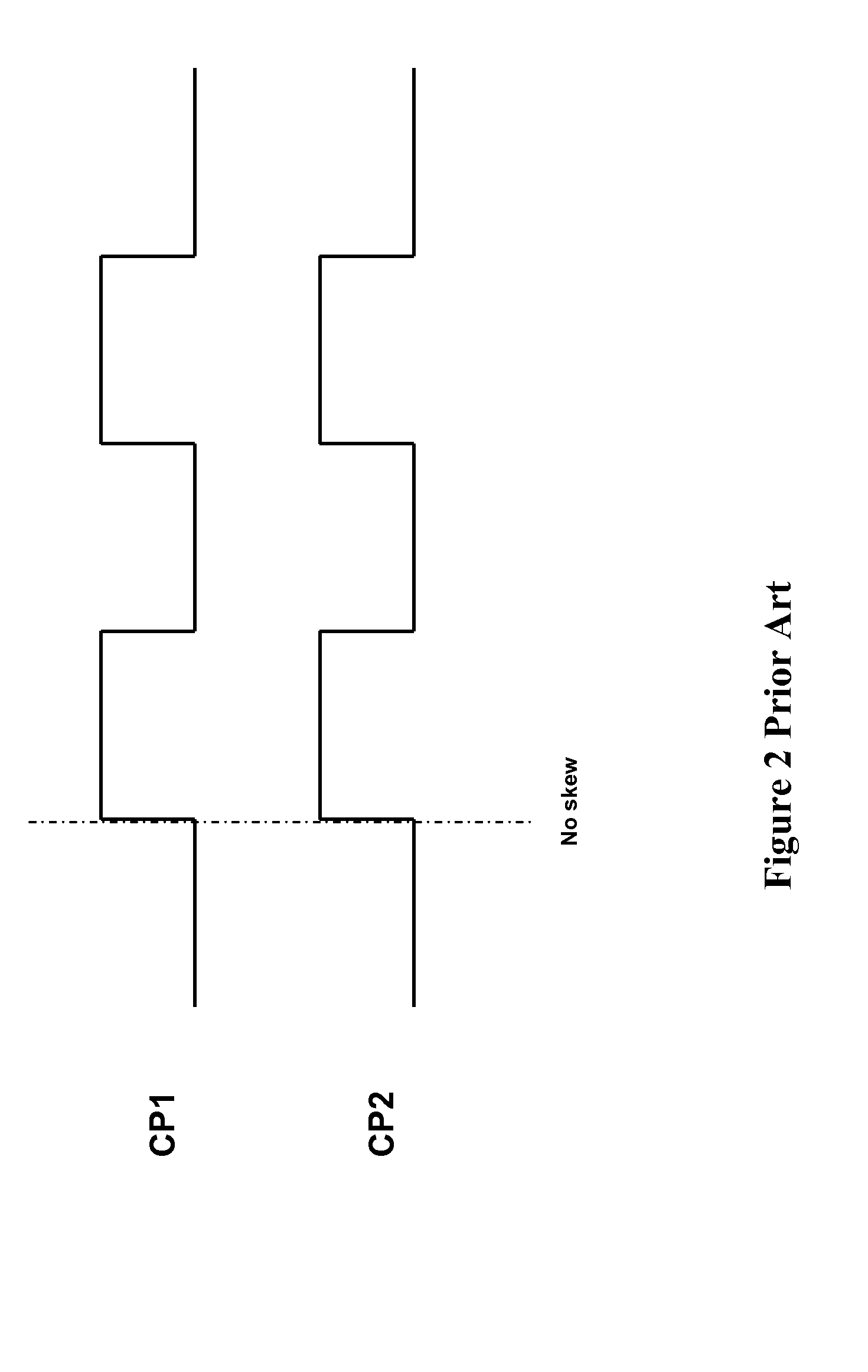

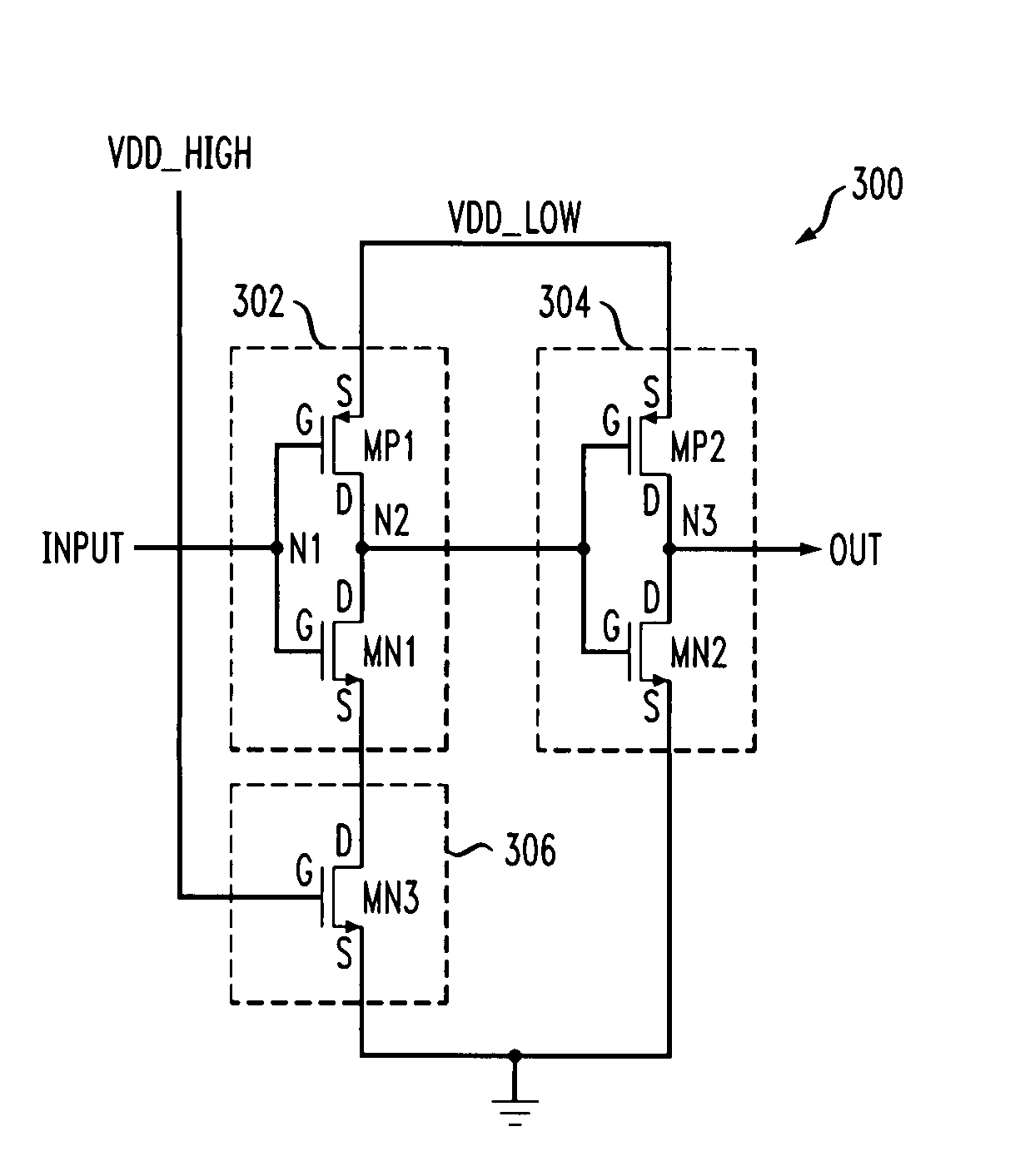

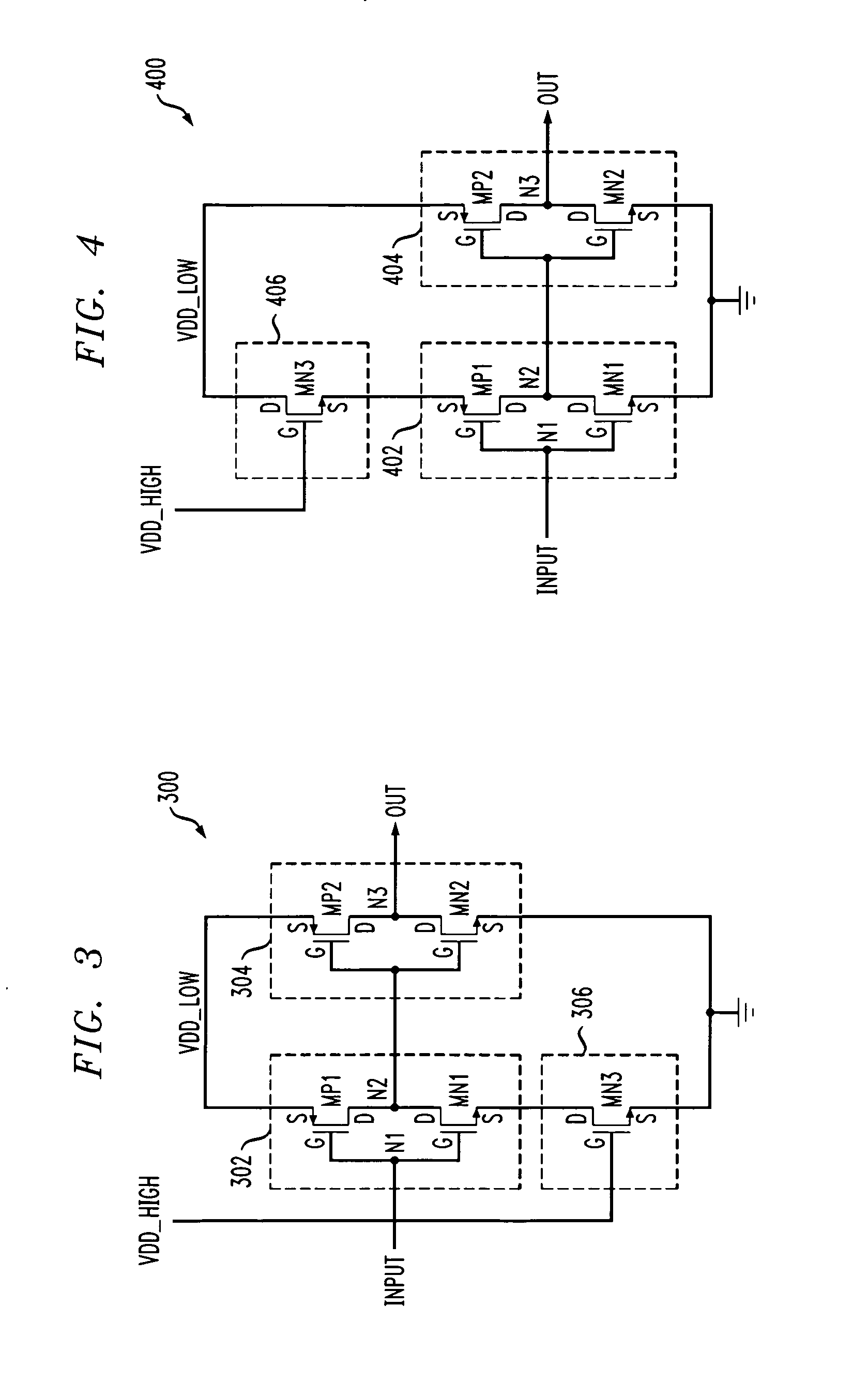

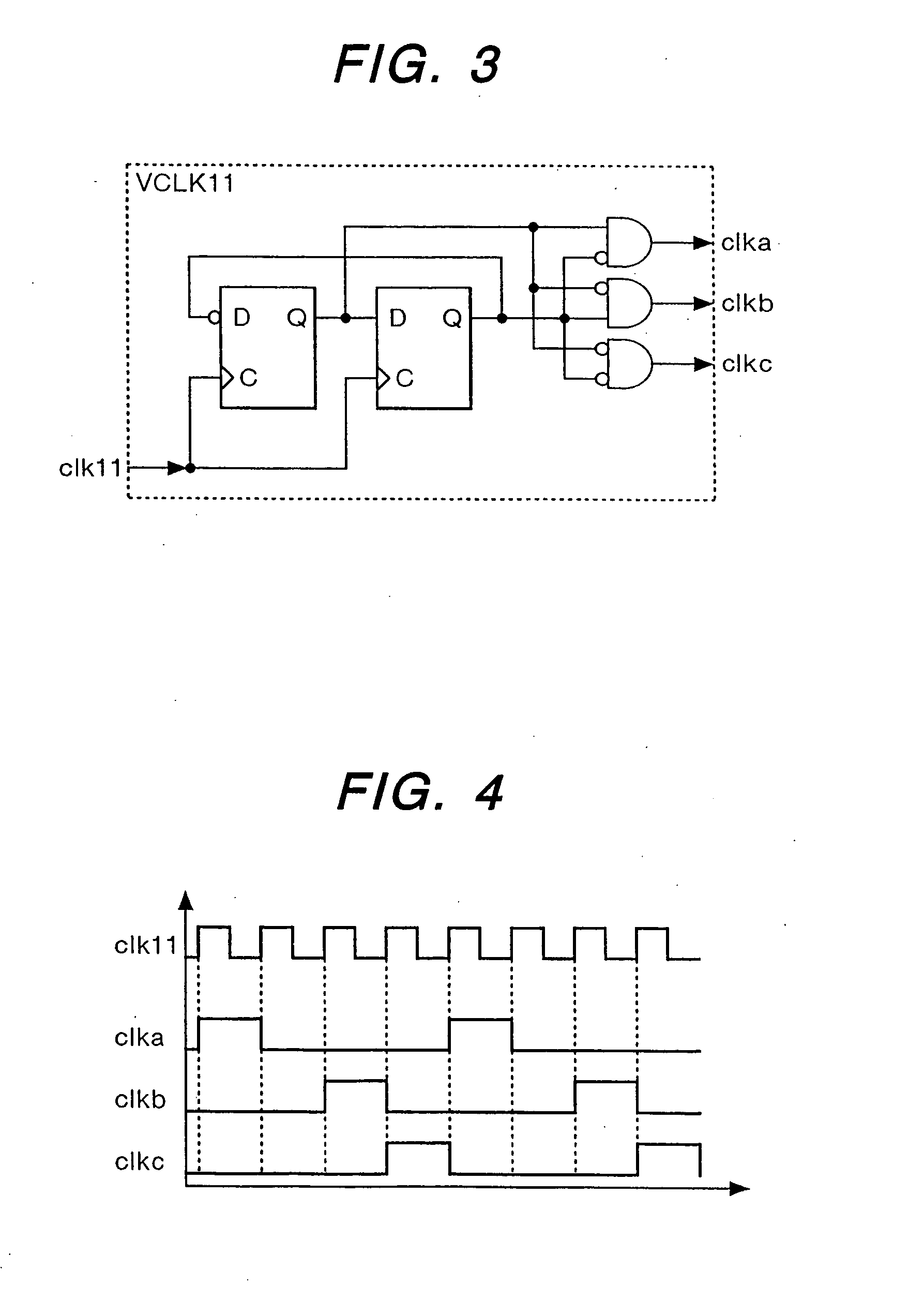

Circuit and Method for Clock Skew Compensation in Voltage Scaling

InactiveUS20100090738A1Pulse automatic controlElectric pulse generatorVoltage regulationPower domains

Circuit and methods for automatic clock skew compensation in circuits having two power domains. When one of the power domains is operated with a lowered supply voltage, lowering the supply voltage tends to slow the clock pulse and produces clock skew. Circuitry is provided for selectively delaying the clock pulse in one of the power domains to reduce the clock skew by comparing the clock pulses, and then automatically delaying the clock pulse in one of the domains by a delay determined to minimize the skew. A method is provided where the clock skew between two clock pulses is determined and the delay needed in one of the clock pulses to reduce the skew is determined by sampling the clock skew using a plurality of delays at multiples of a minimum delay, and then automatically delaying the one clock pulse by selecting an appropriate delay. The method may be iterated.

Owner:TAIWAN SEMICON MFG CO LTD

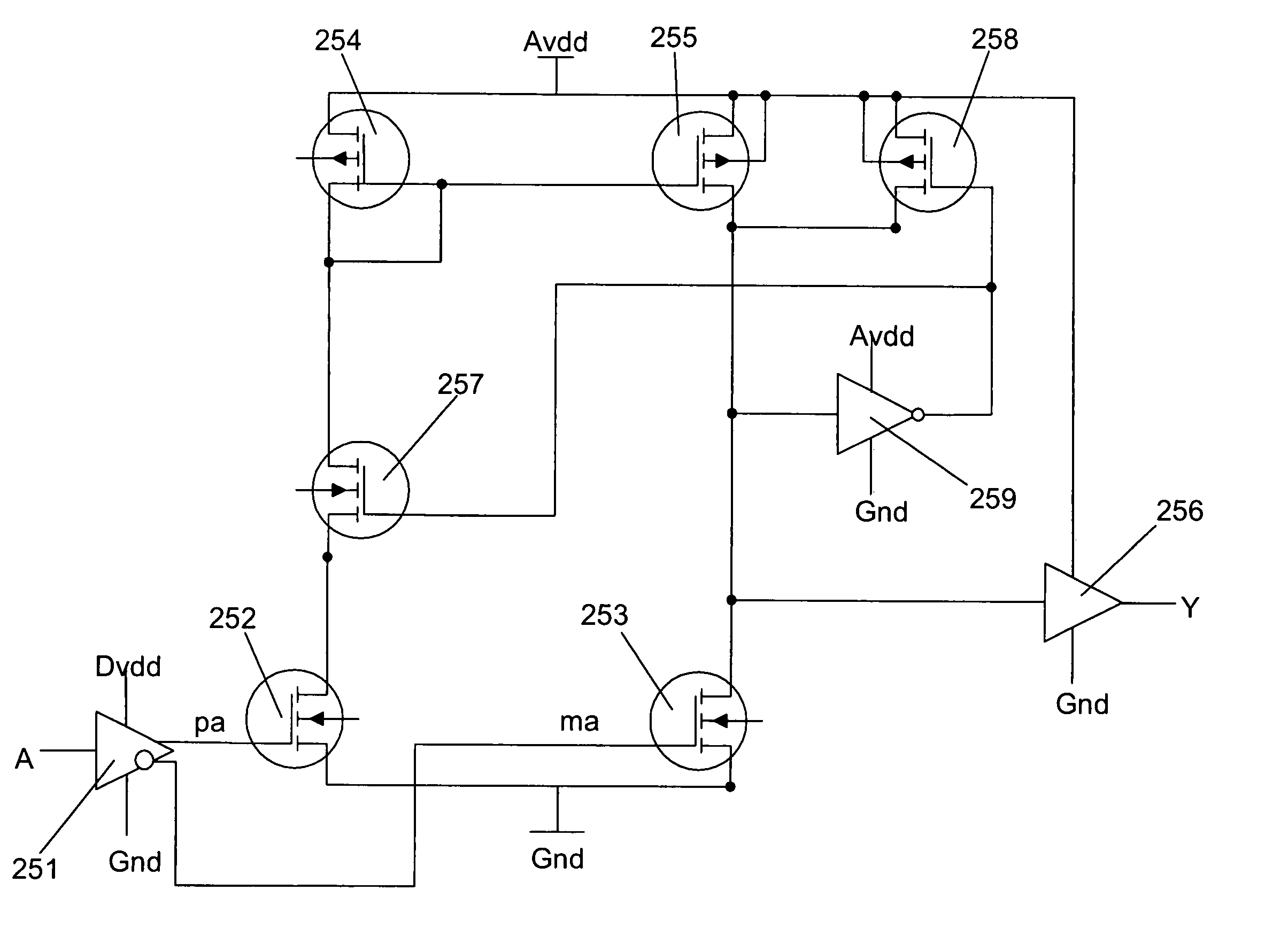

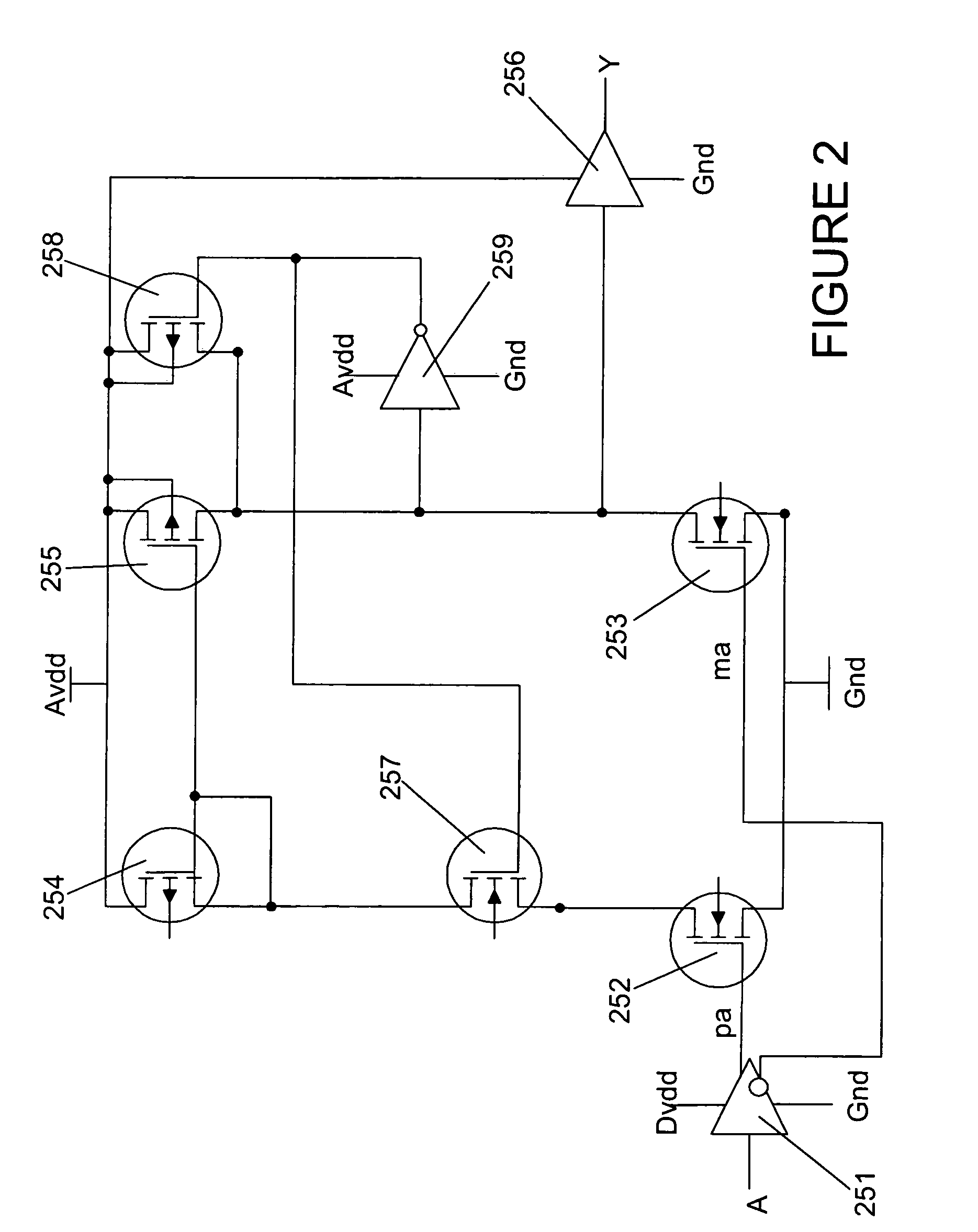

Zero-bias-power level shifting

ActiveUS7205819B2Power reduction by control/clock signalPulse automatic controlEngineeringSteady state

A circuit for voltage level translation with zero static current is disclosed for interfacing devices at one supply voltage with devices at another supply voltage. The translation is achieved by using a modified current mirror circuit such that the current mirror is effectively turned off when the output reaches a steady state condition.

Owner:VIA TECH INC

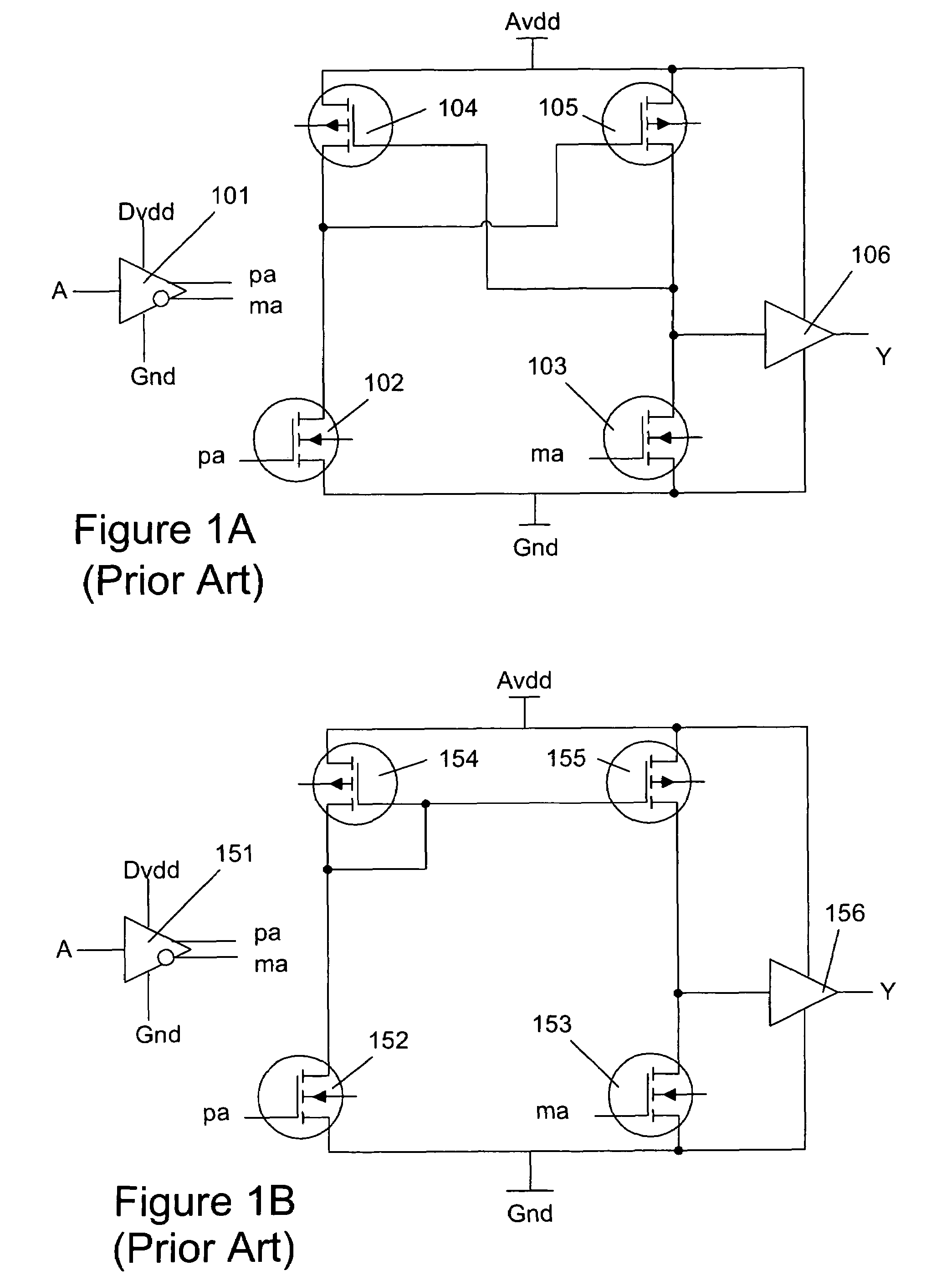

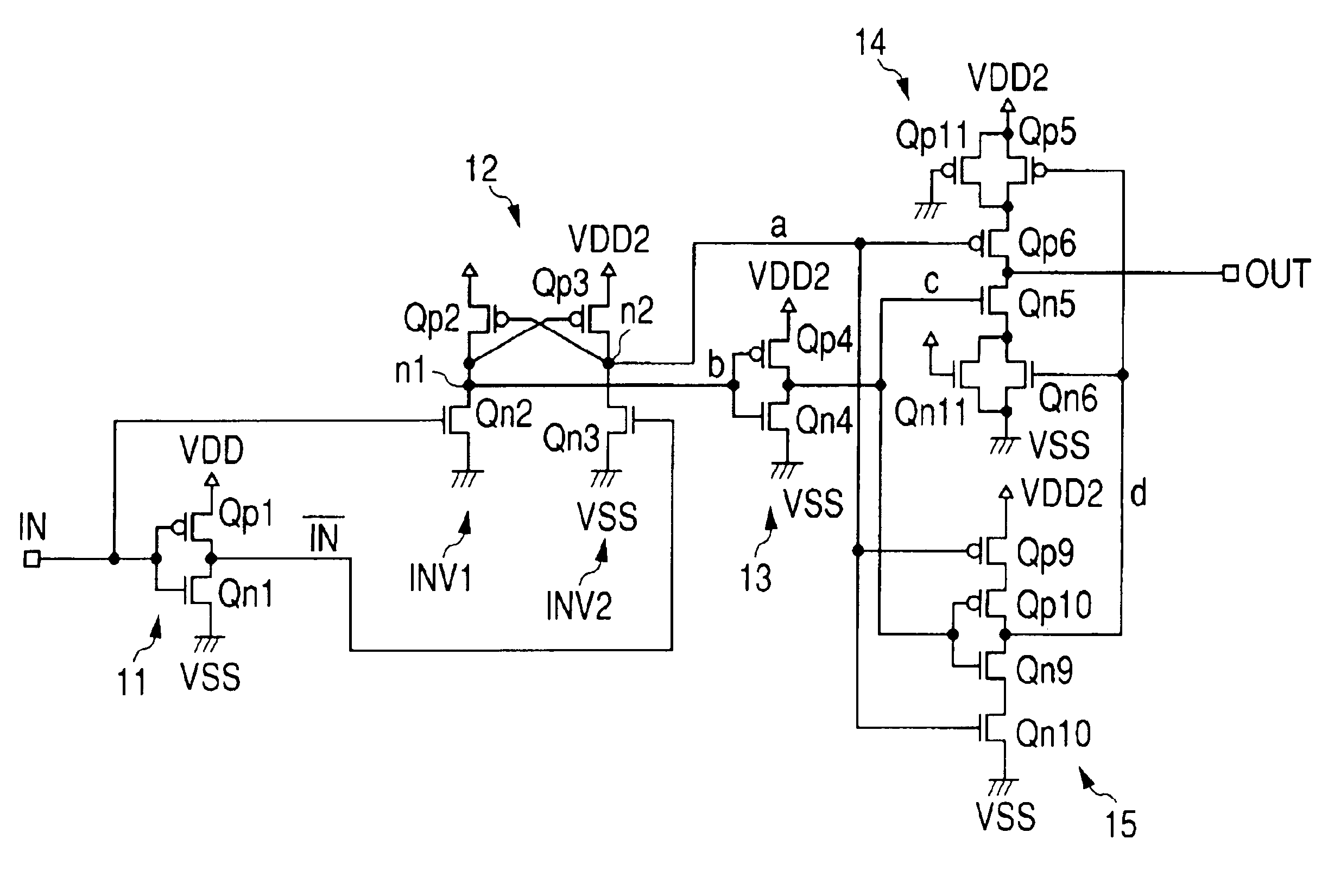

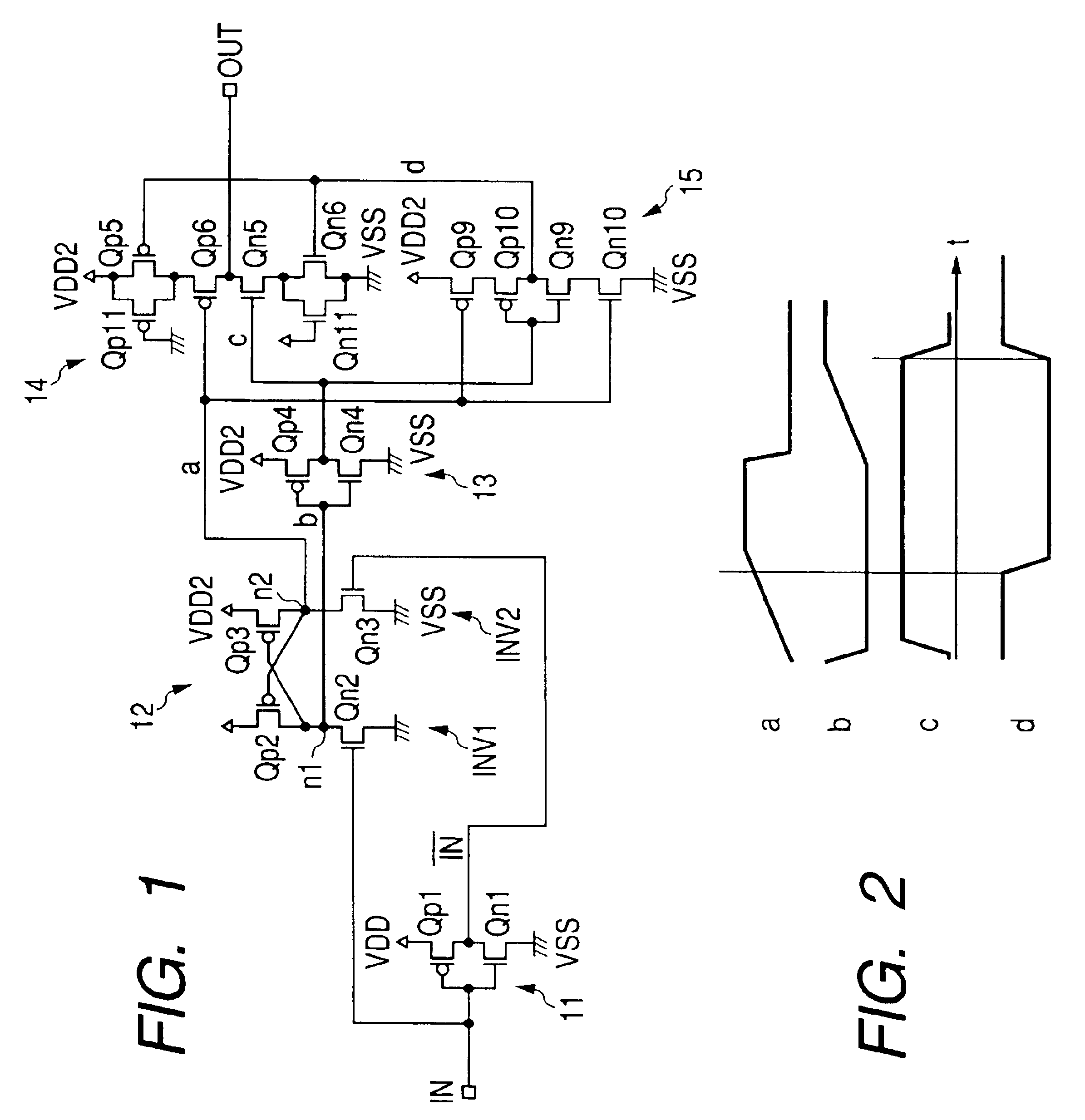

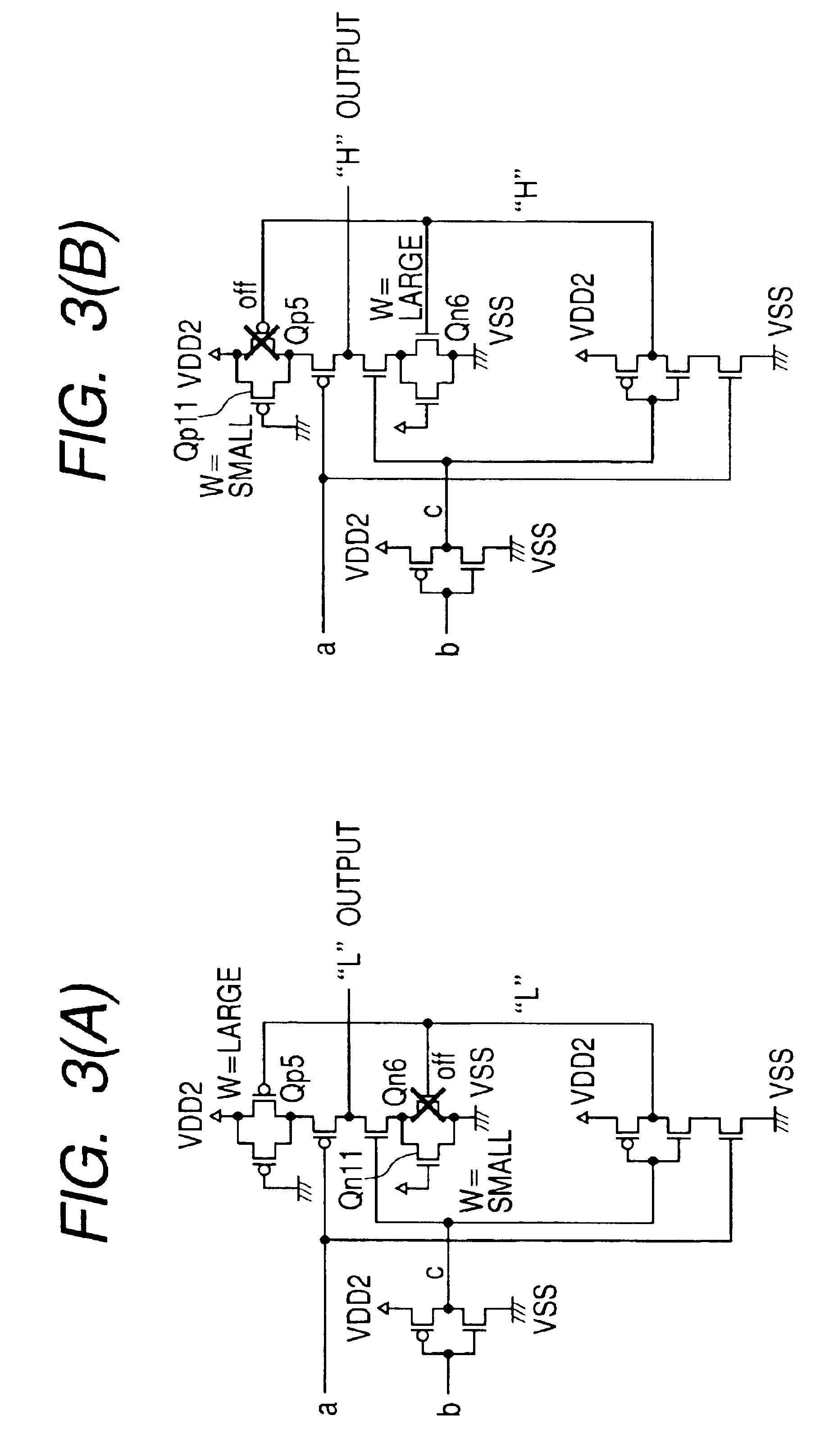

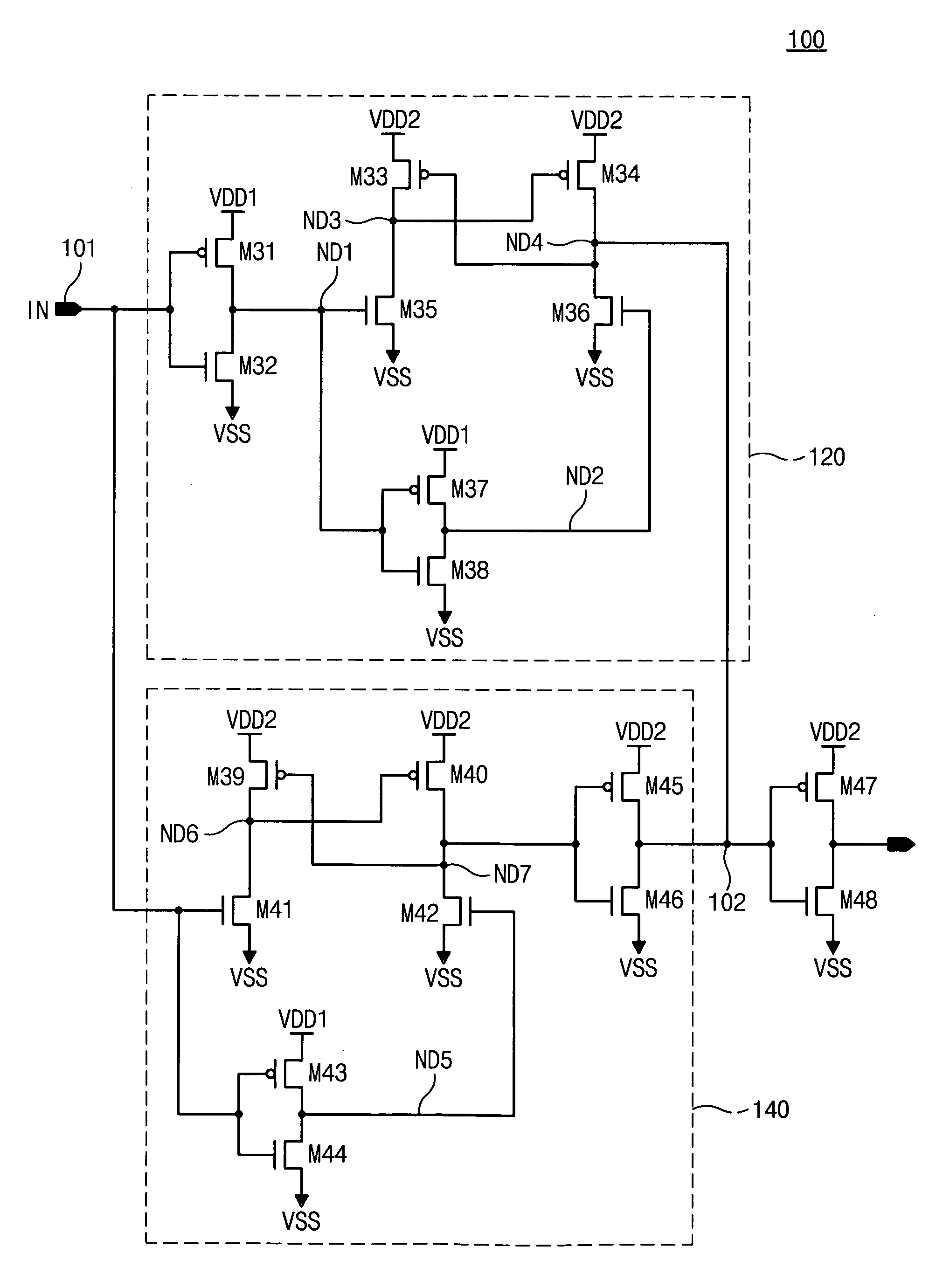

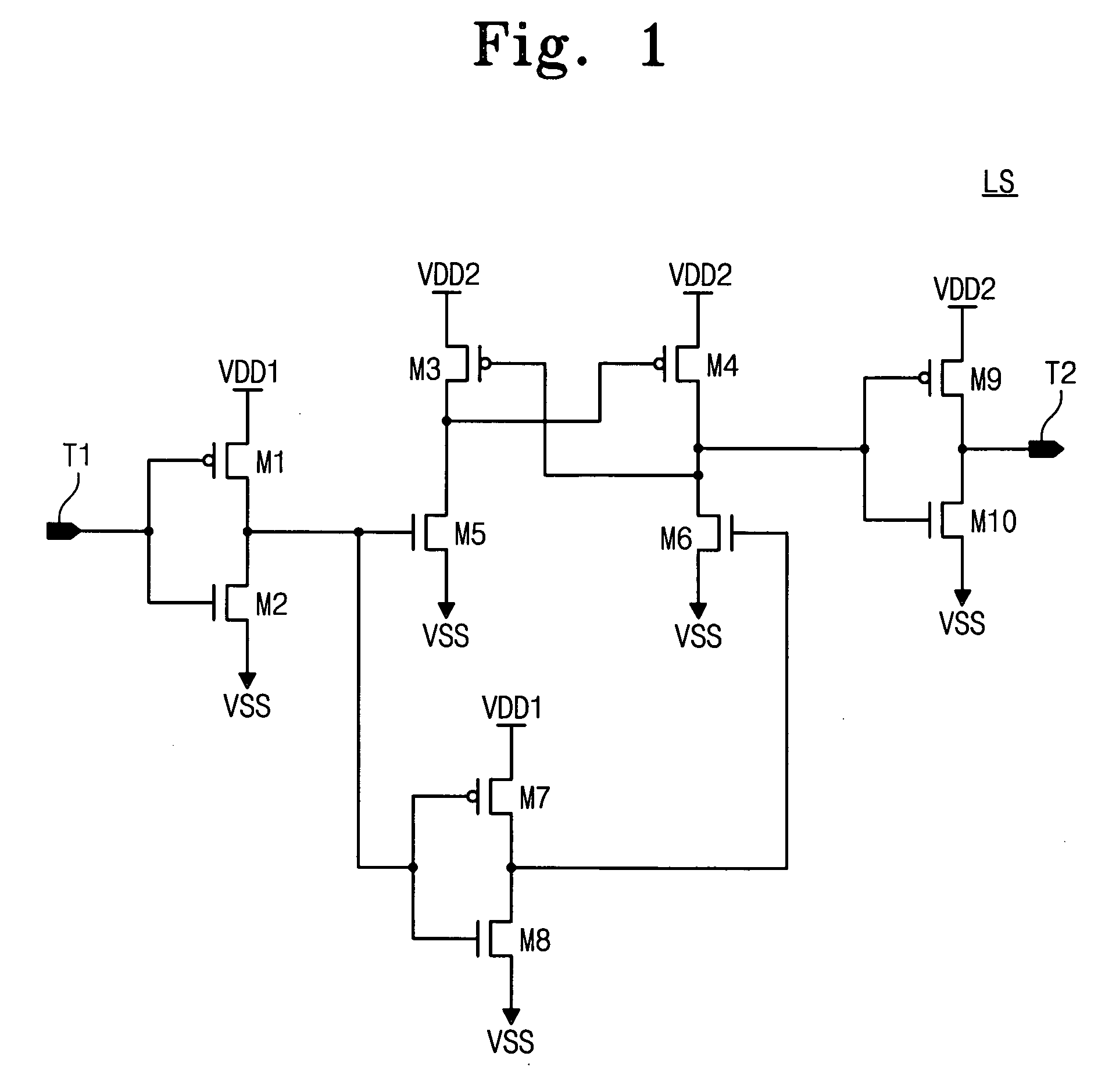

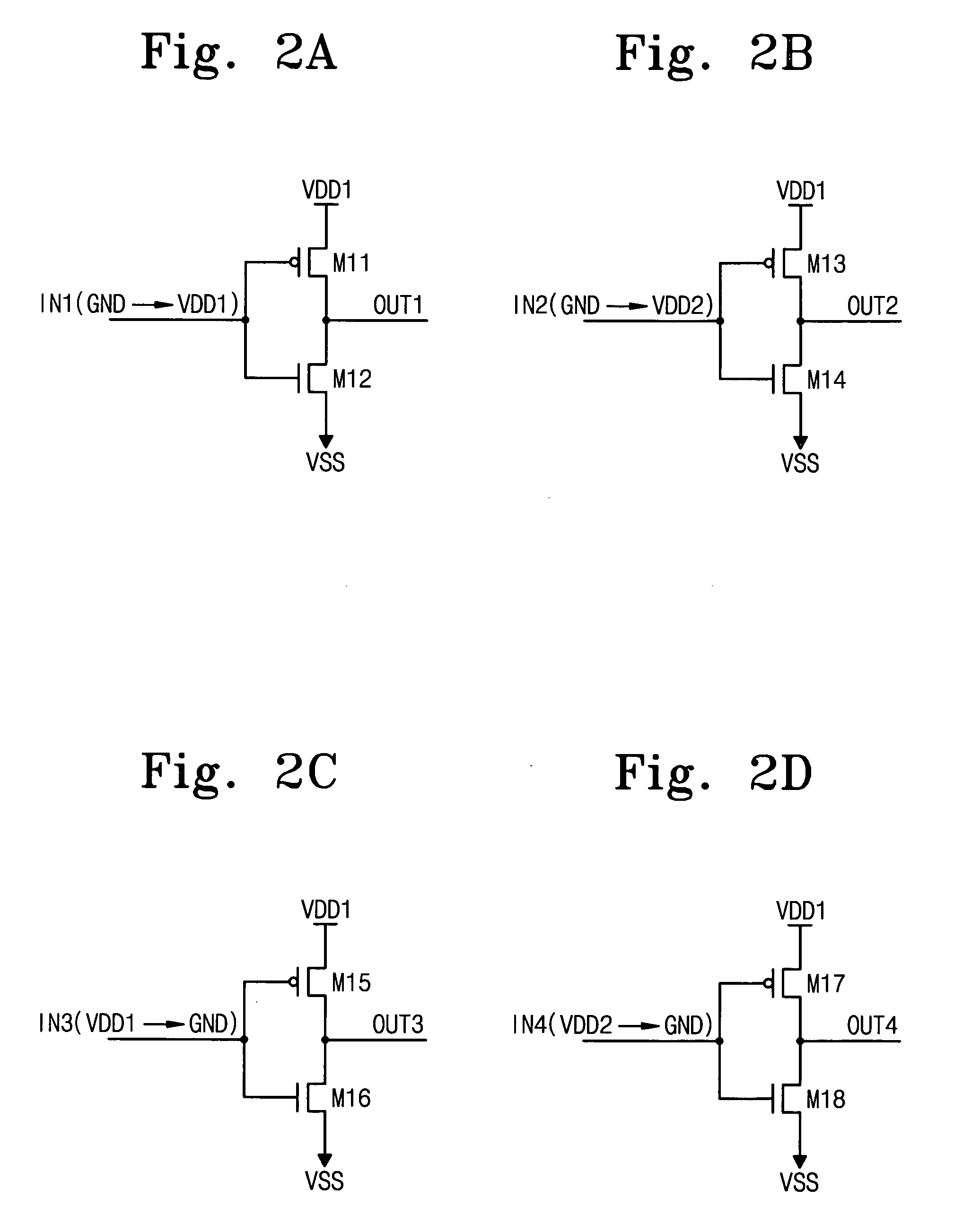

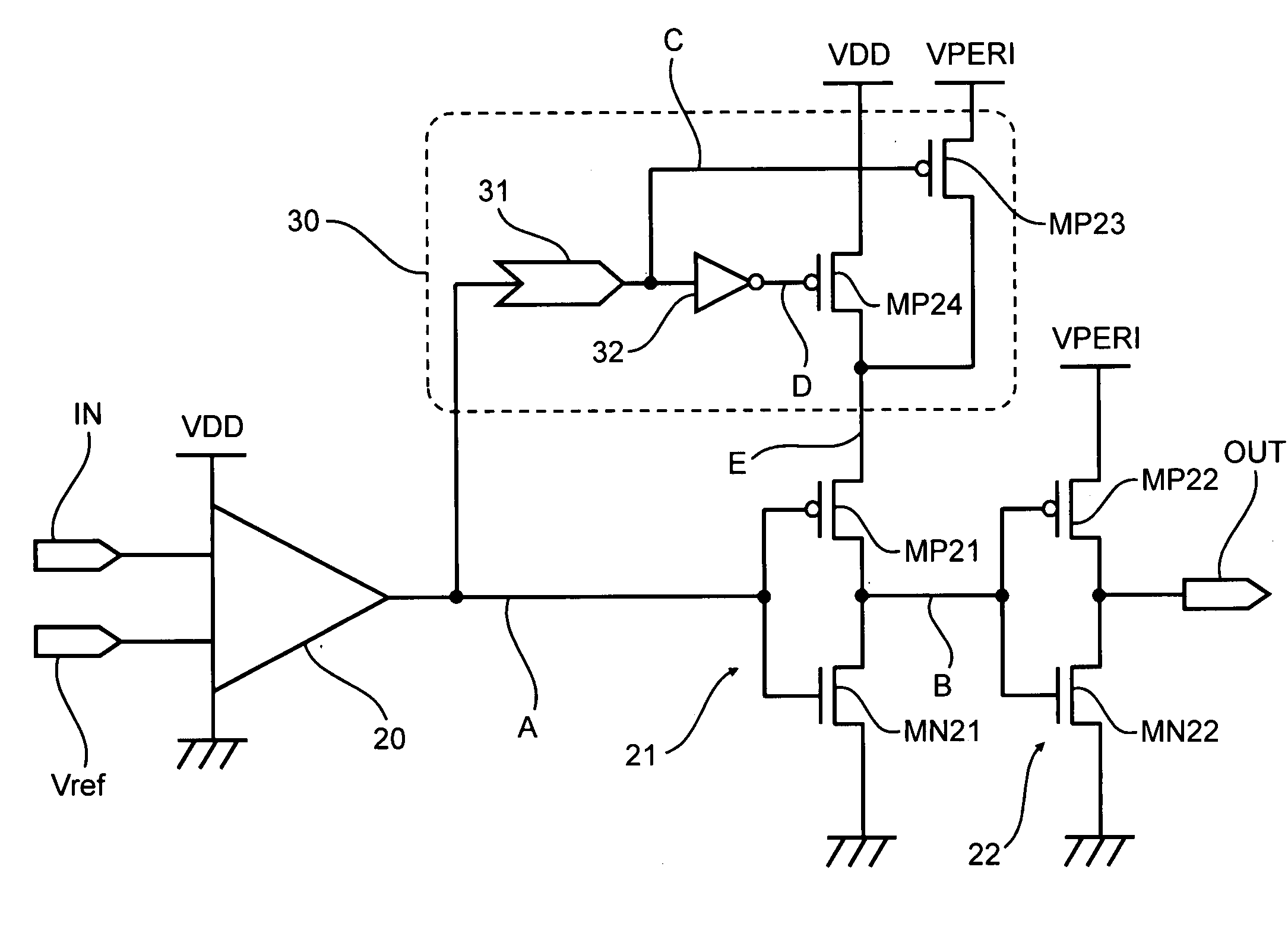

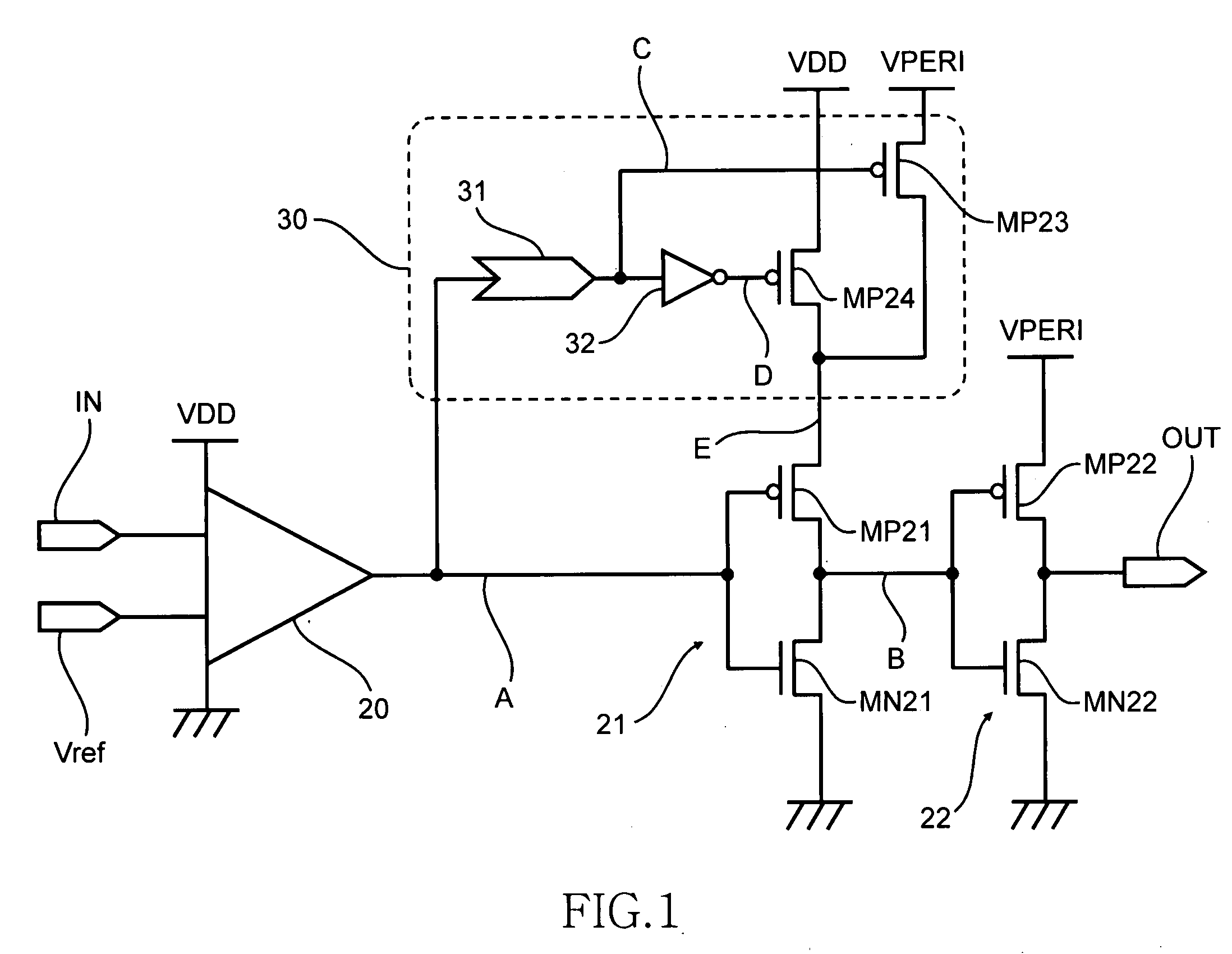

Level shift circuit and semiconductor integrated circuit

A level conversion circuit is composed of a level shift circuit for supplying a level-converted signal in the same phase as the input signal and a signal in the reverse phase thereto and a follow-up circuit responsive to the earlier of the output signals of the level shift circuit for generating an output signal, wherein the follow-up circuit consists of an inverter circuit in which two p-channel type MOS transistors and two n-channel type MOS transistors are connected in series between a first voltage terminal and a second voltage terminal, of which one pair is used as input transistors and the remaining pair of transistors are subjected to feedback based on the output signal of the level shift circuit to be quickly responsive to the next variation.

Owner:RENESAS ELECTRONICS CORP +1

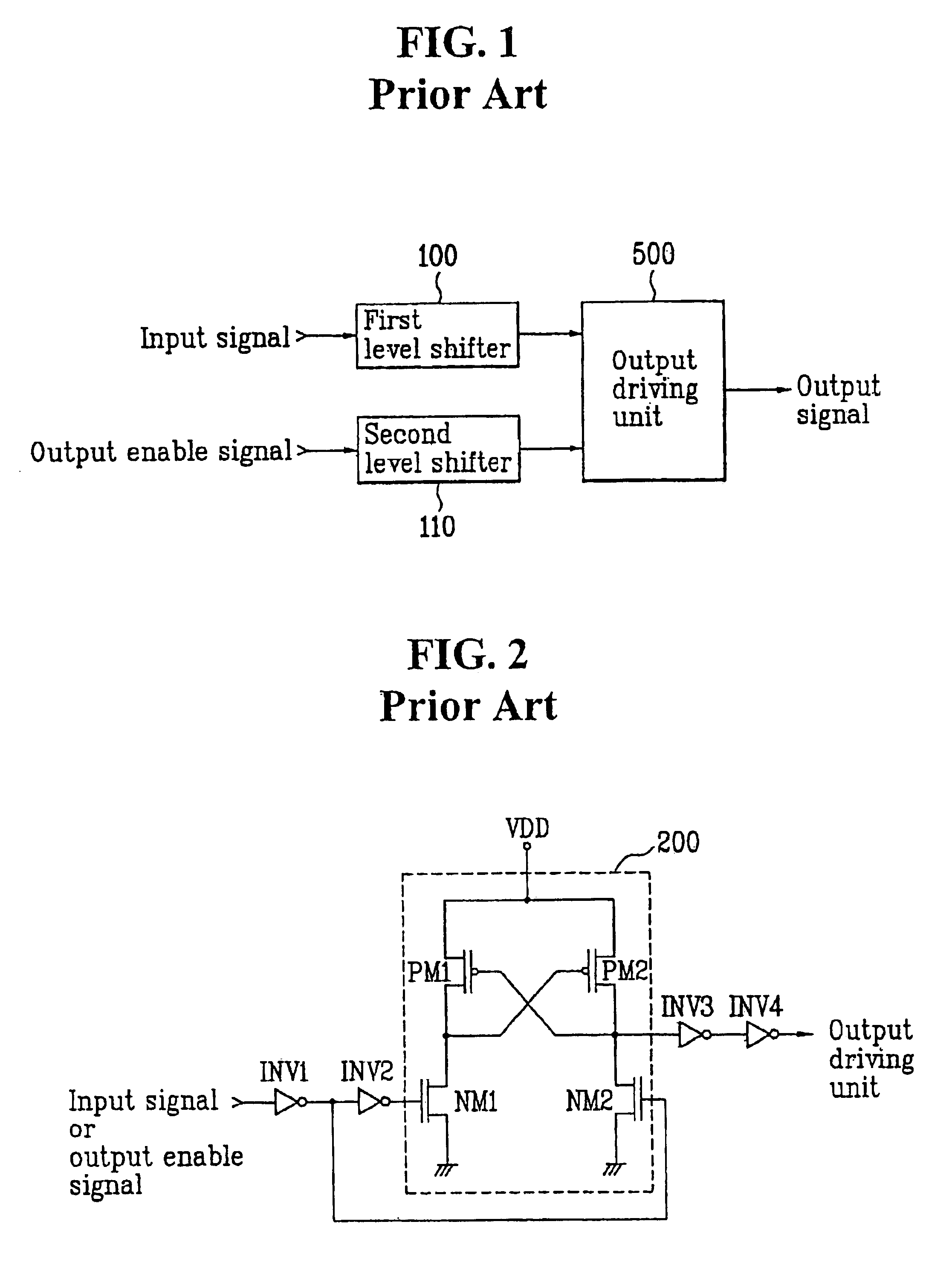

Voltage conversion circuit with stable transition delay characteristic

ActiveUS20060261851A1Pulse automatic controlElectric pulse generatorLevel shiftingElectrical and Electronics engineering

A voltage conversion circuit changes an input signal of a first voltage into an output signal of a second voltage. The circuit includes an input terminal receiving an input signal, an output terminal generating an output signal, and first and second level-shifting units connected in parallel between the input and output terminals. The first and second level-shifting units have different transition delay characteristics, enabling rising and falling transition delays to be variable in the same ratio when the first and second voltages are changed.

Owner:SAMSUNG ELECTRONICS CO LTD

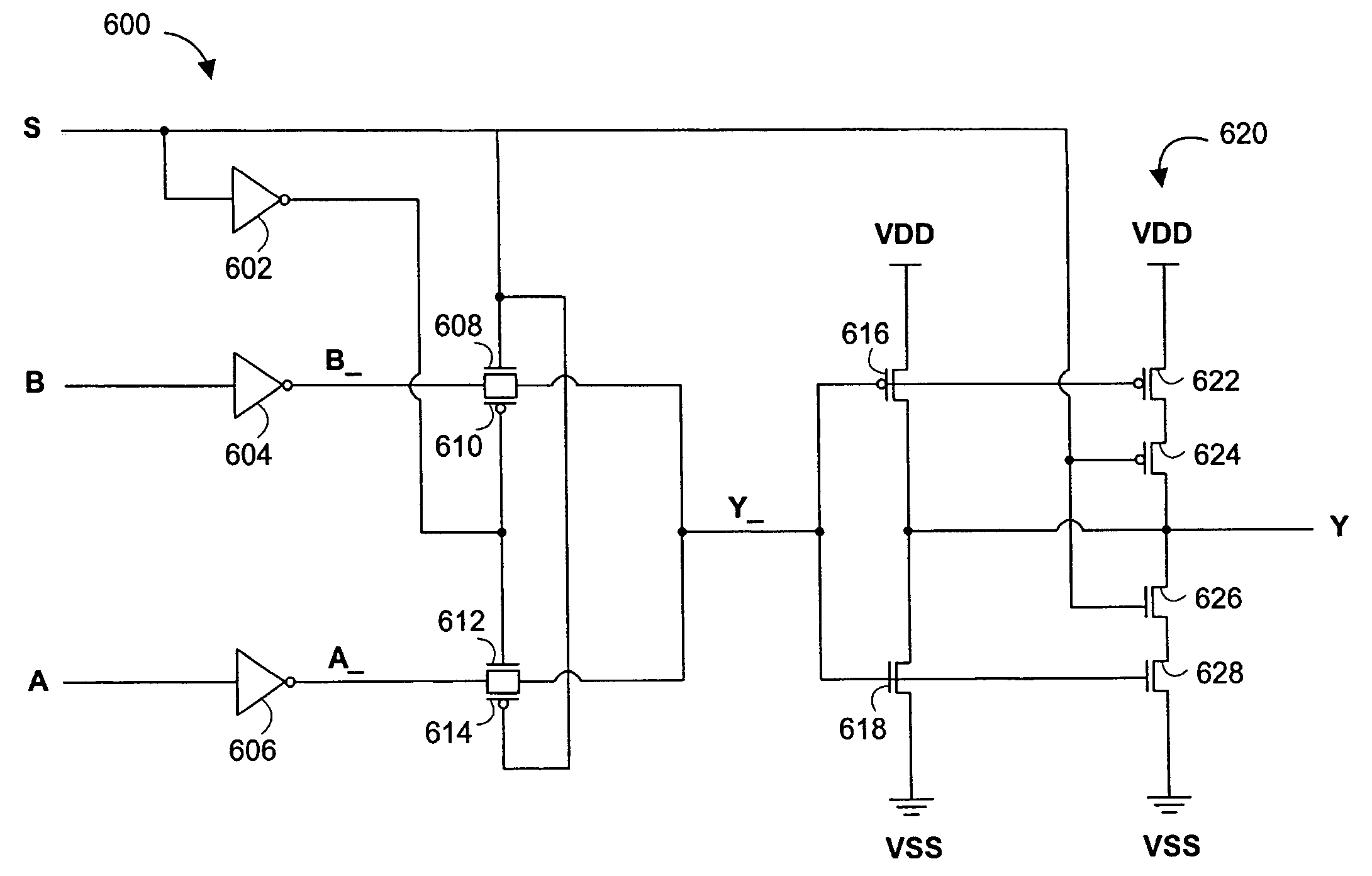

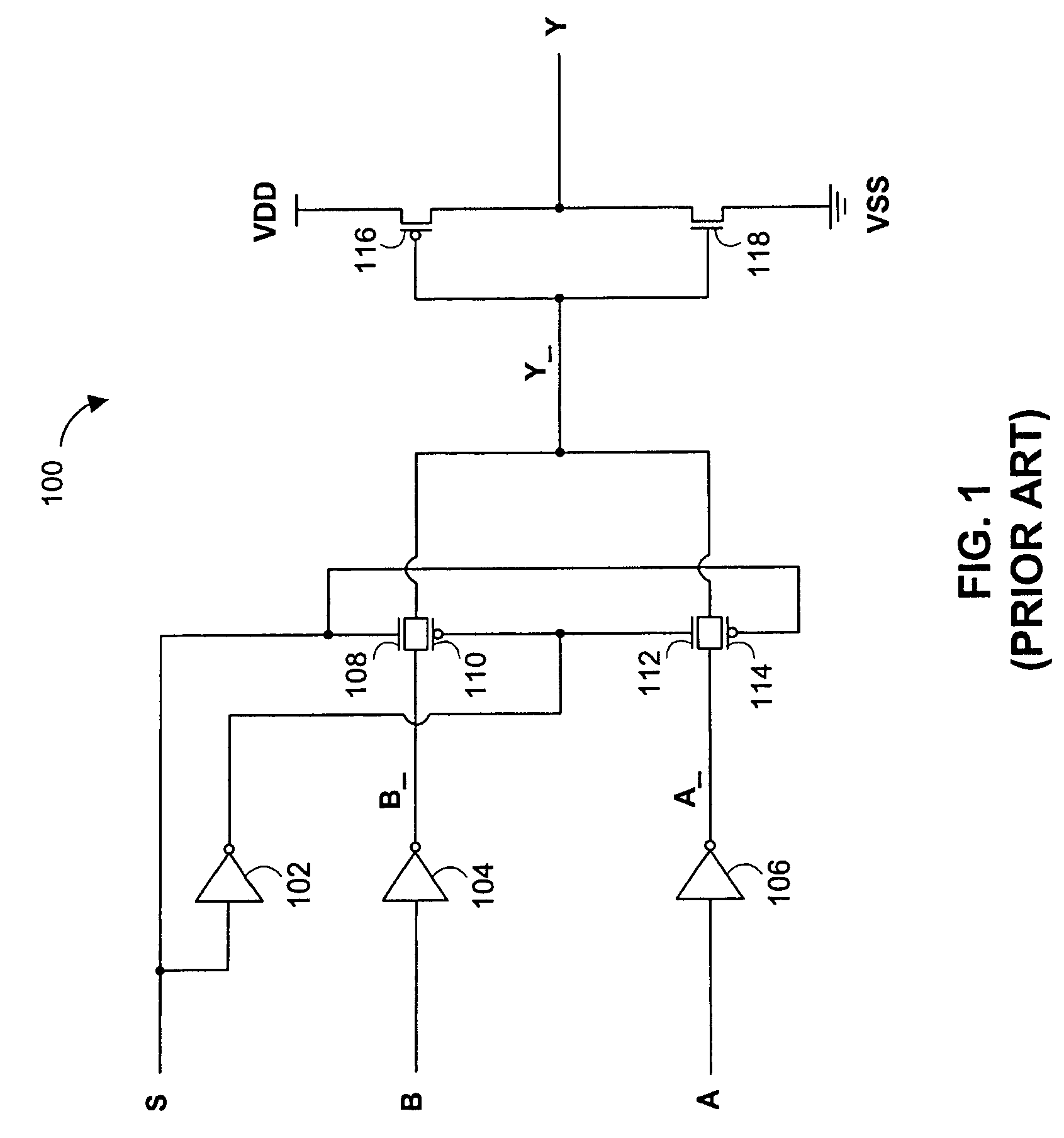

Time-balanced multiplexer switching methods and apparatus

ActiveUS7525341B1Time-balanced multiplexer switchingChange is minimalElectronic switchingDelay compensationMultiplexerEngineering

Methods and apparatus are provided for time-balanced switching of multiplexer circuits. An embodiment of the invention includes a transistor chain coupled to the output of the multiplexer circuit. The transistor chain preferably delays transitions that would otherwise occur relatively quickly, to match the timing of transitions that occur relatively slowly. The timing of relatively slow transitions is left unaltered. The invention advantageously allows all selector input transitions to yield a data output transition with a substantially constant delay.

Owner:MARVELL ISRAEL MISL

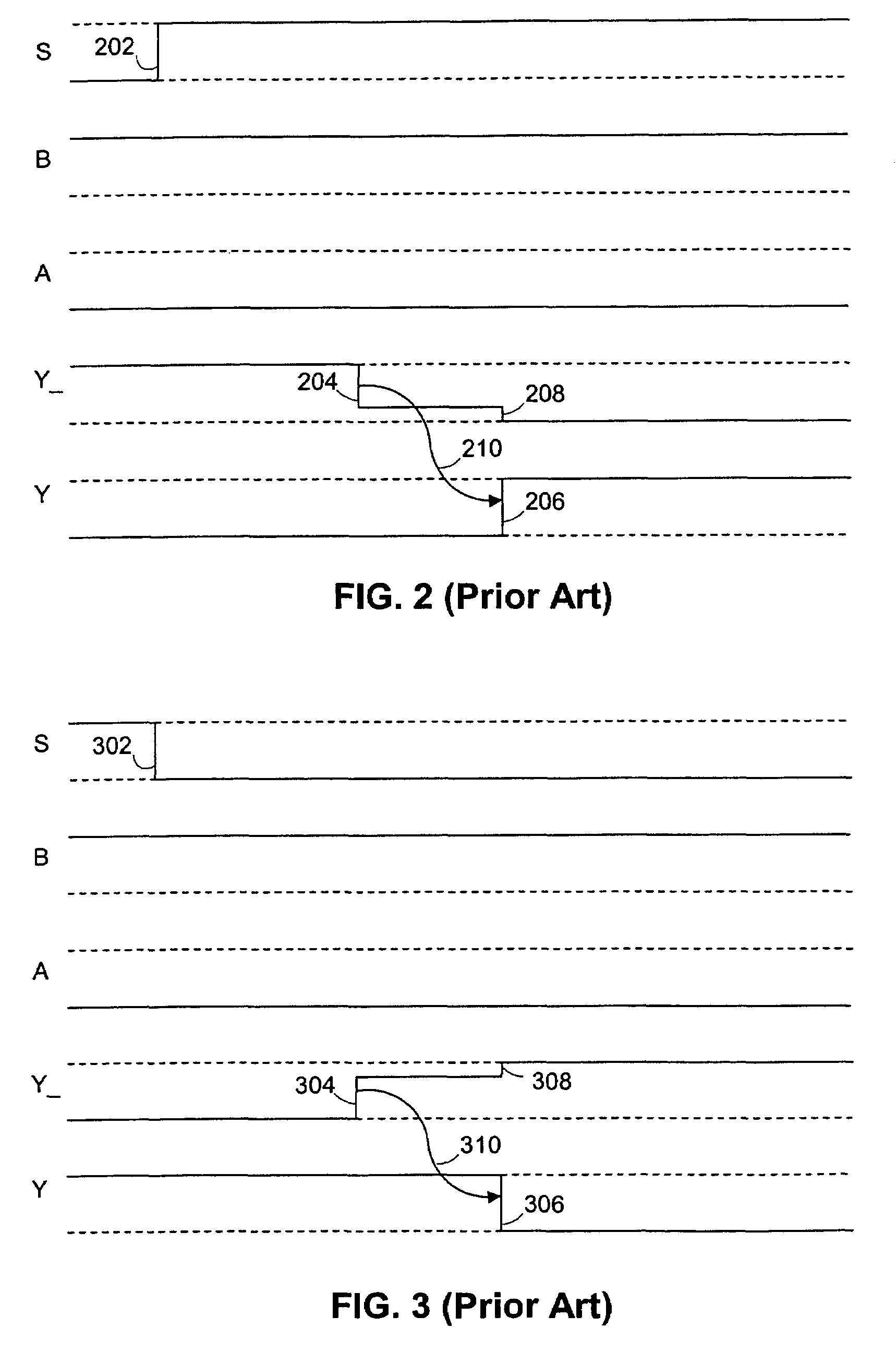

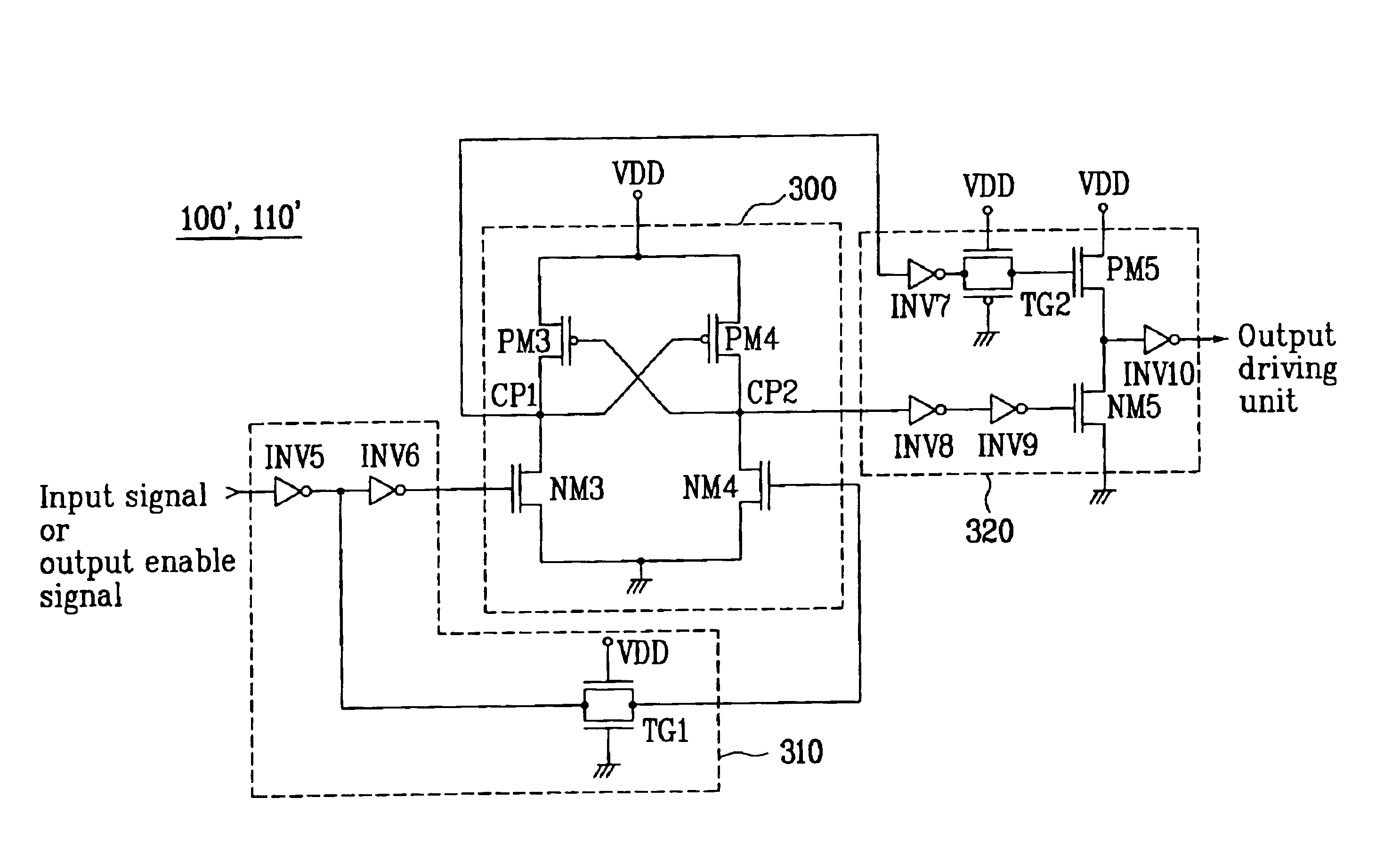

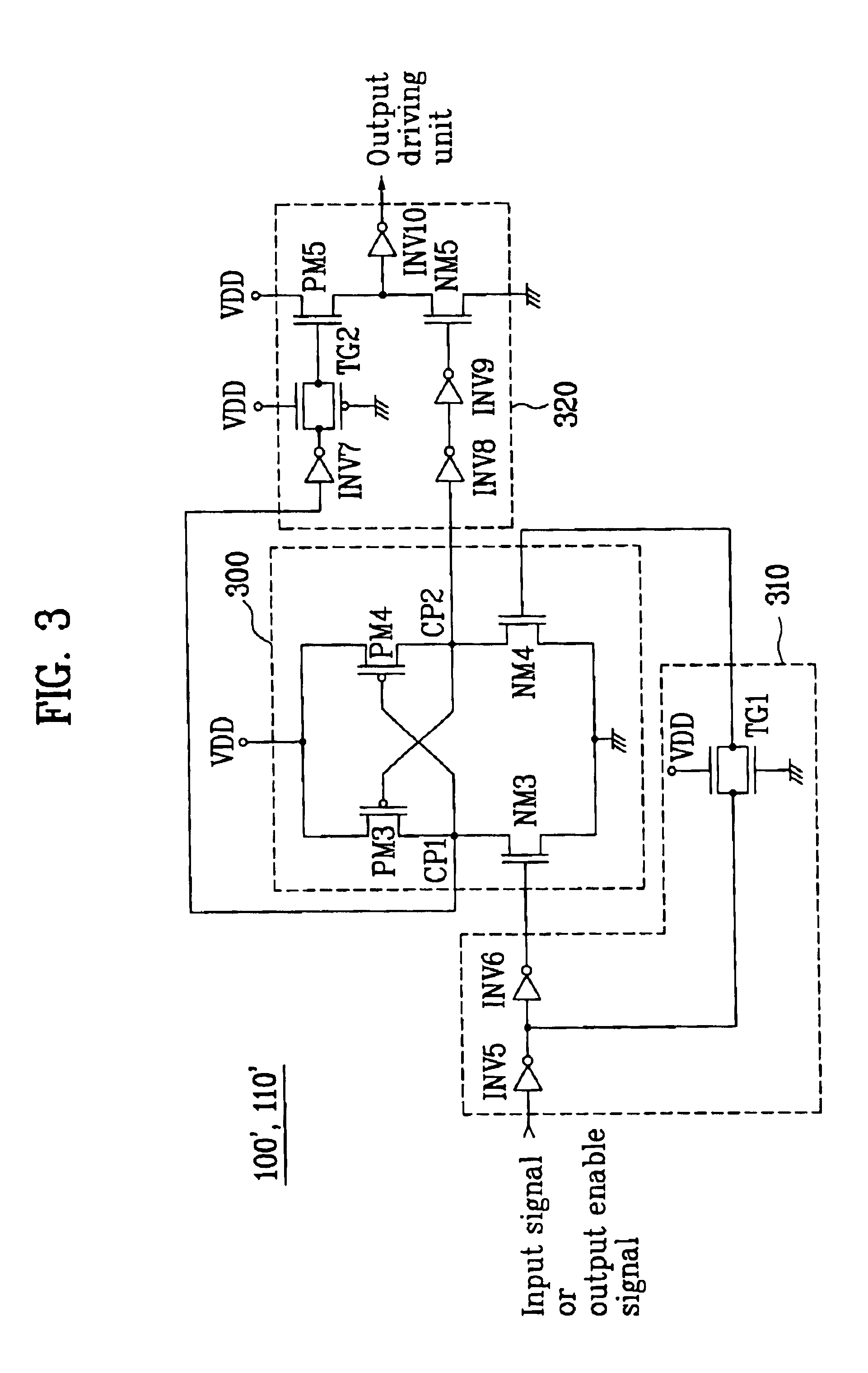

Output driving circuit for maintaining I/O signal duty ratios

InactiveUS6933755B2Duty ratioPulse automatic controlLogic circuits coupling/interface using field-effect transistorsDriver circuitEngineering

Output driving circuit including at least one or more than one level shifter for receiving an input signal to be provided to an outside of an integrated circuit and shifting a voltage level of the input signal to a voltage level required at the outside of the integrated circuit while maintaining a duty ratio of the input signal constant, and an output driving unit for forwarding the input signal to the outside of the integrated circuit under the control of an output enable signal, thereby permitting application to the integrated circuit operative at a high speed, readily.

Owner:LG ELECTRONICS INC

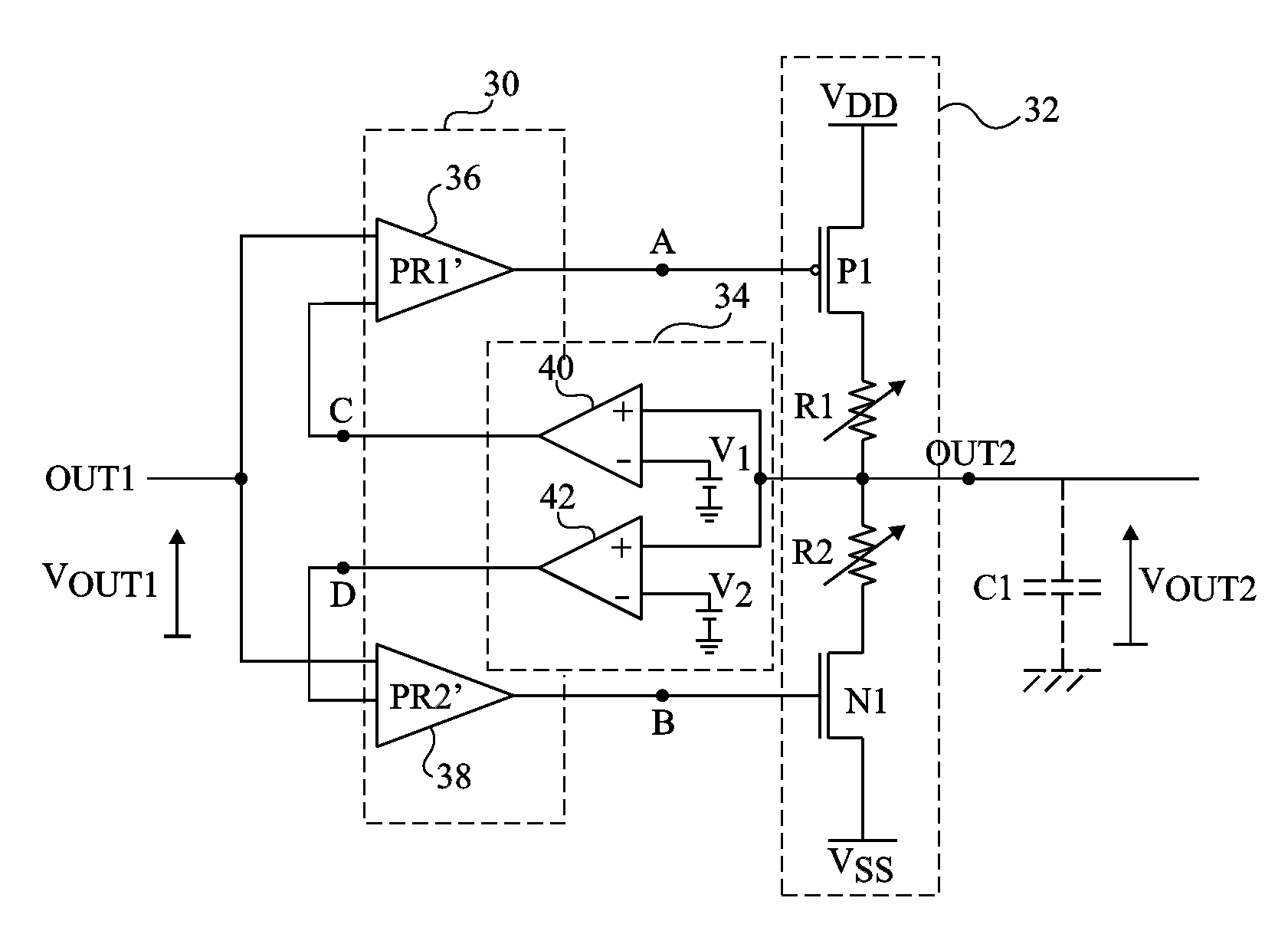

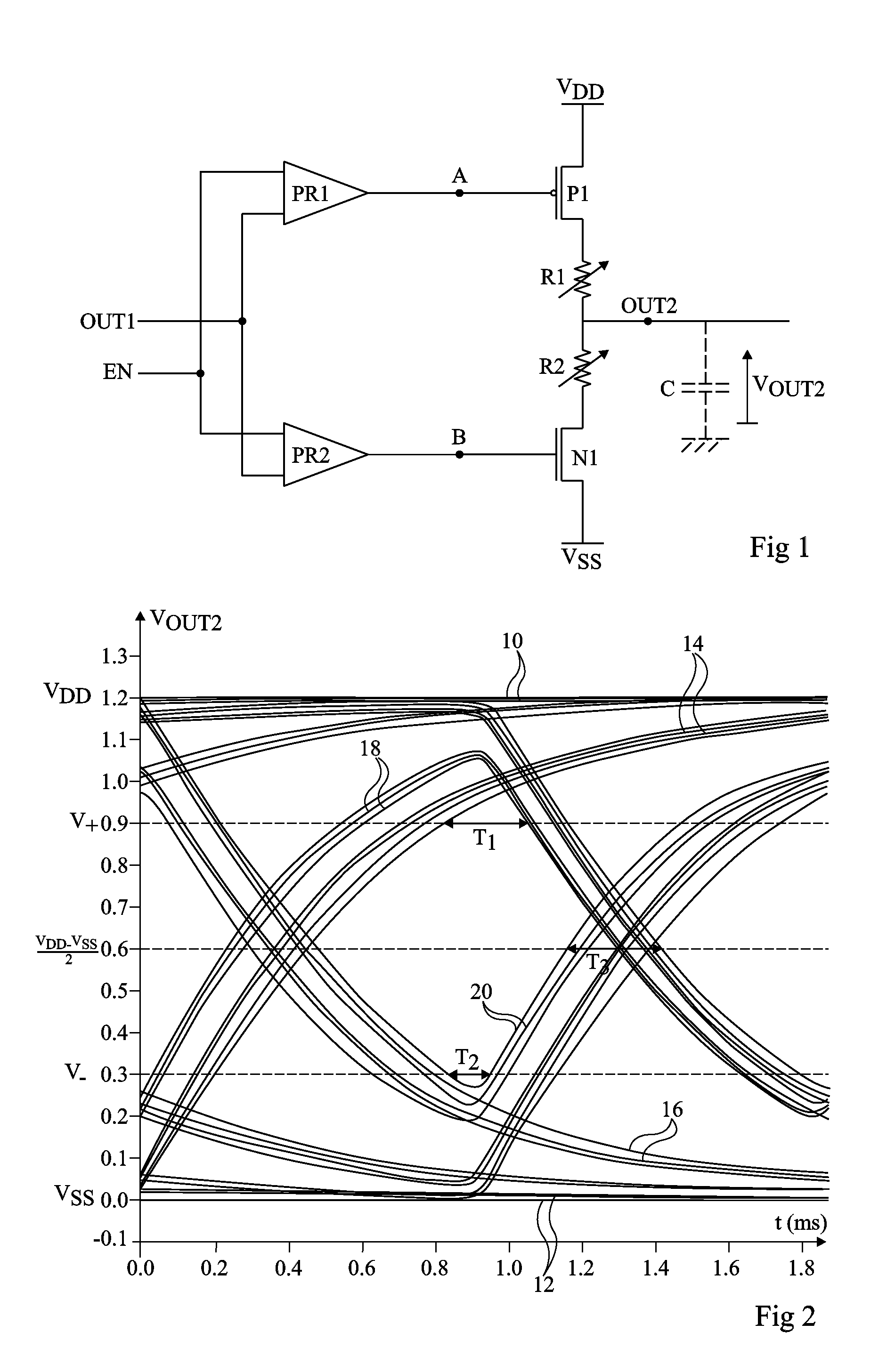

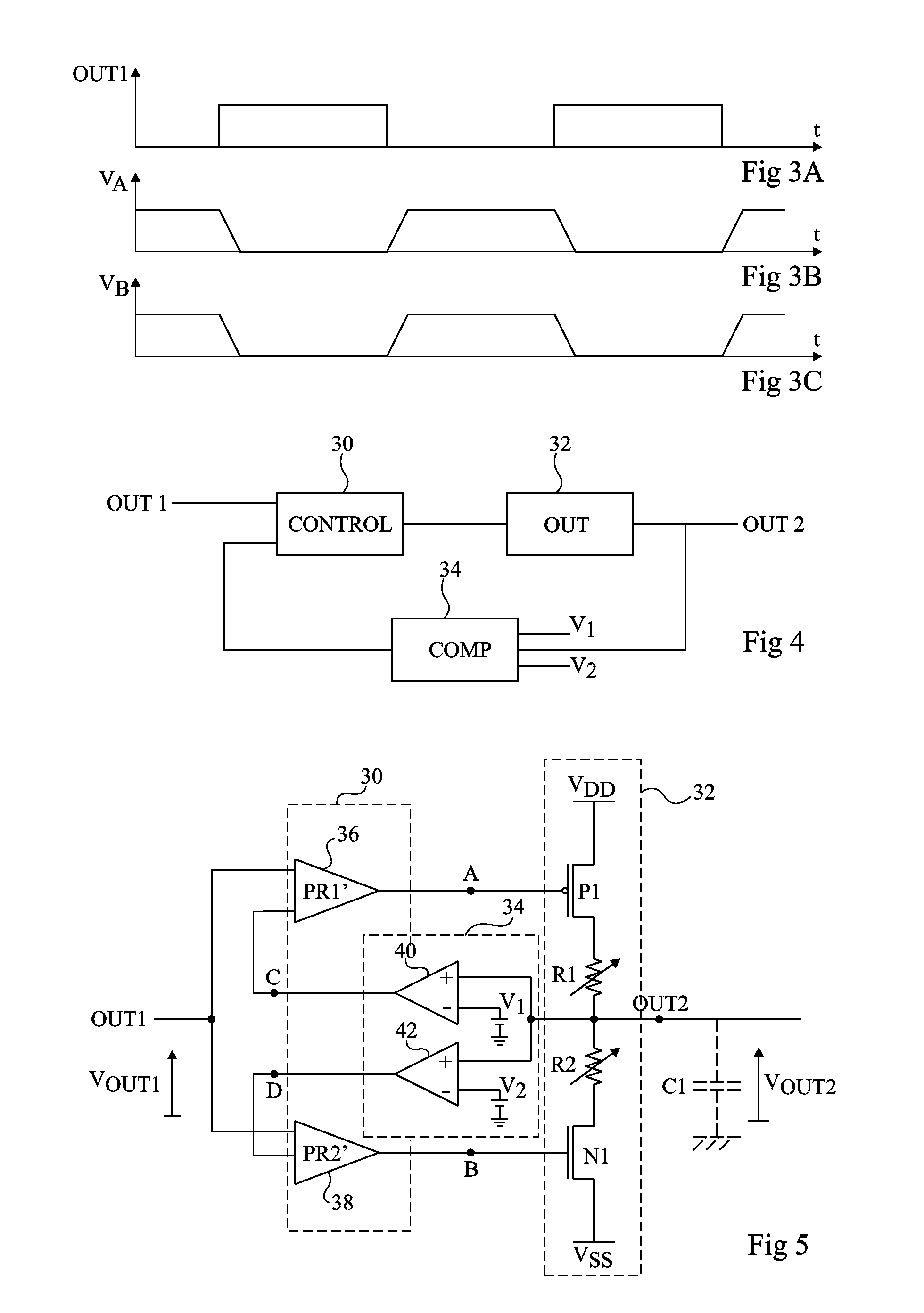

Buffer Circuit for a Capacitive Load of High Value

ActiveUS20110260756A1Power reduction in field effect transistorsMultiple input and output pulse circuitsEngineeringThreshold voltage

A buffer circuit including an input terminal capable of receiving an input signal and an output terminal capable of being connected to a capacitive load, including an output circuit a series connection, between two terminals of application of a power supply voltage, of a first MOS transistor, a first and a second resistor of adjustable values, and a second MOS transistor, and means for controlling said first and second transistors receiving the input signal The buffer circuit further includes means for comparing the voltage on the output terminal of the circuit with at least one threshold voltage, the comparison means being connected to said control means.

Owner:STMICROELECTRONICS SRL

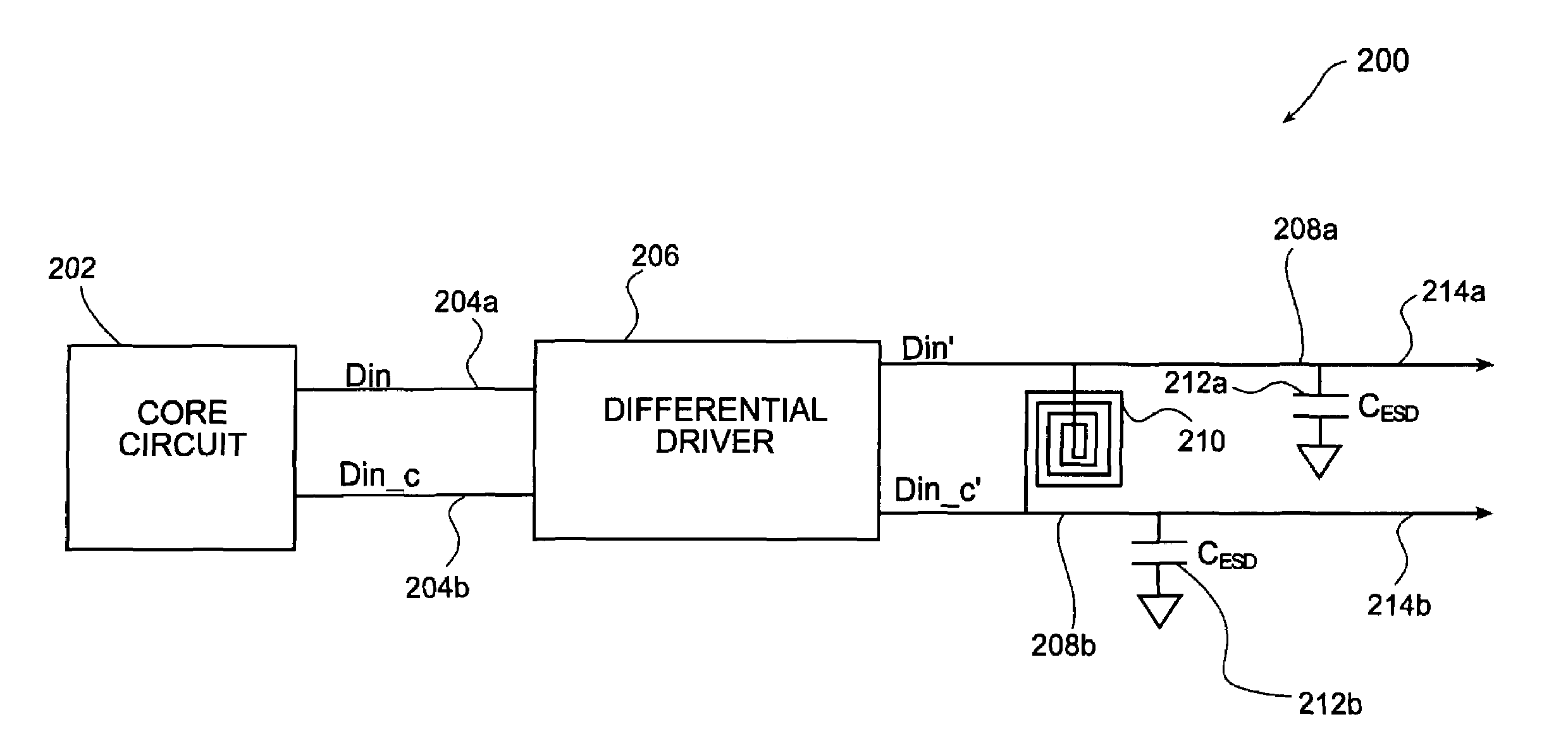

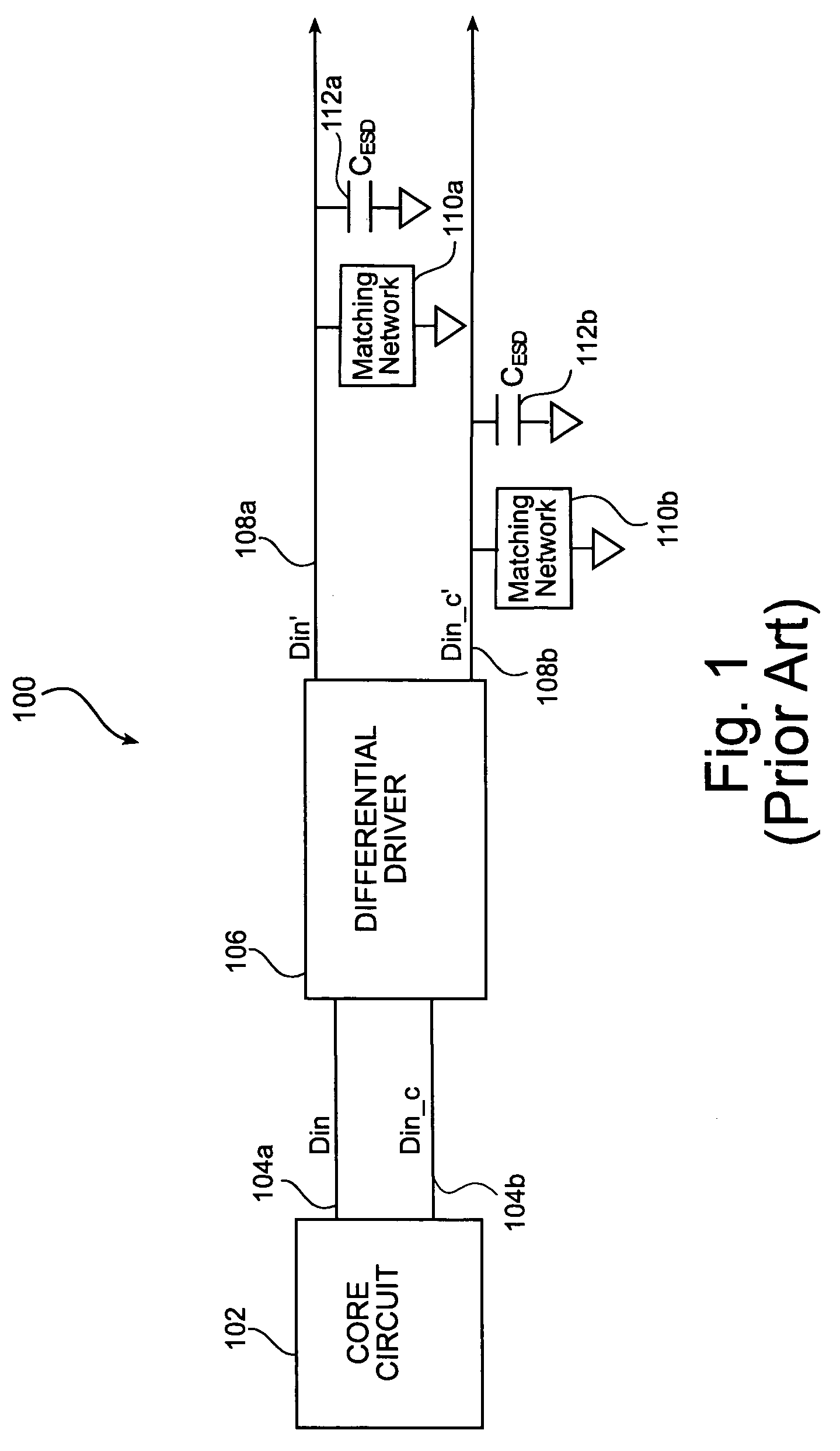

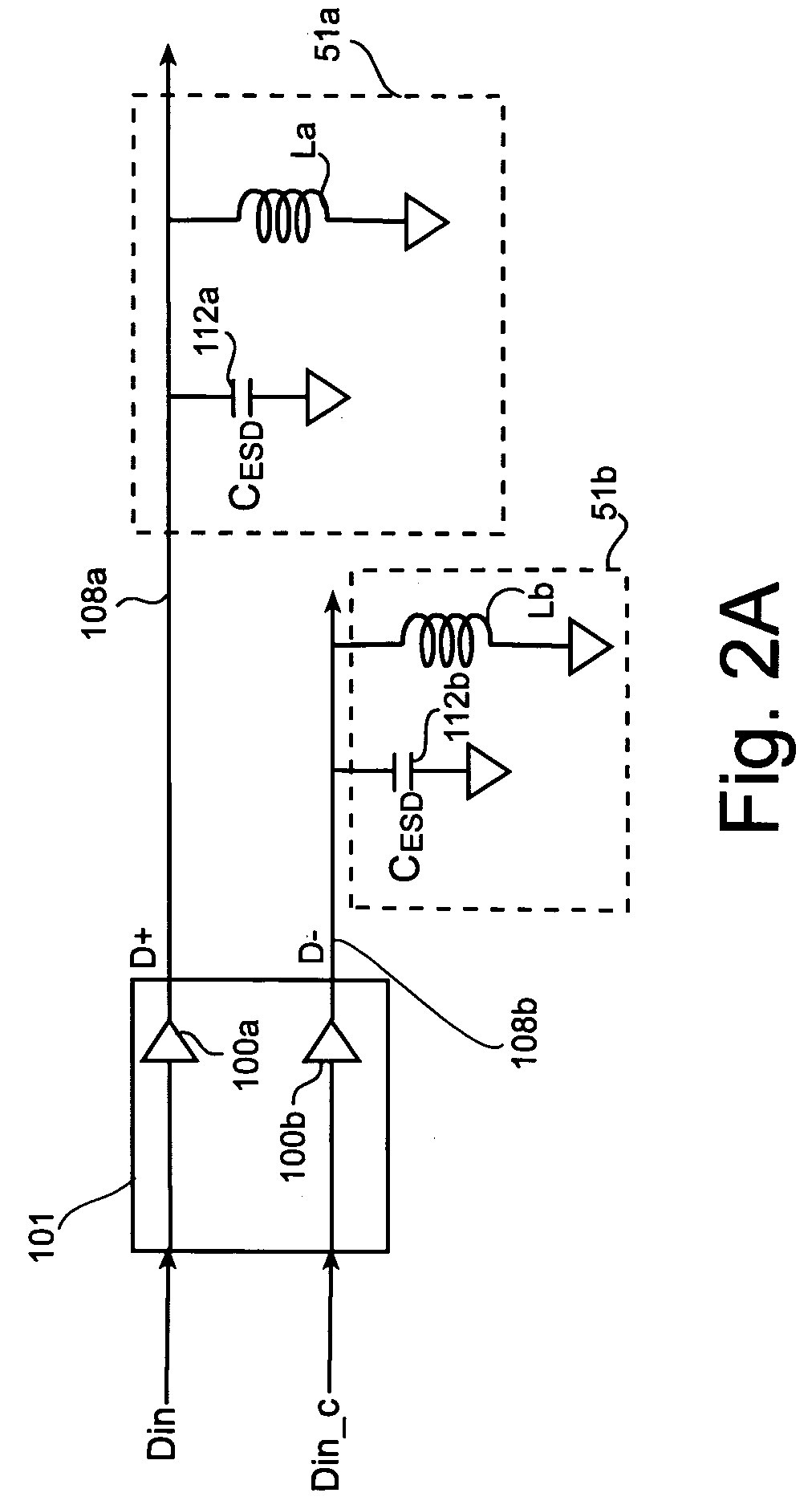

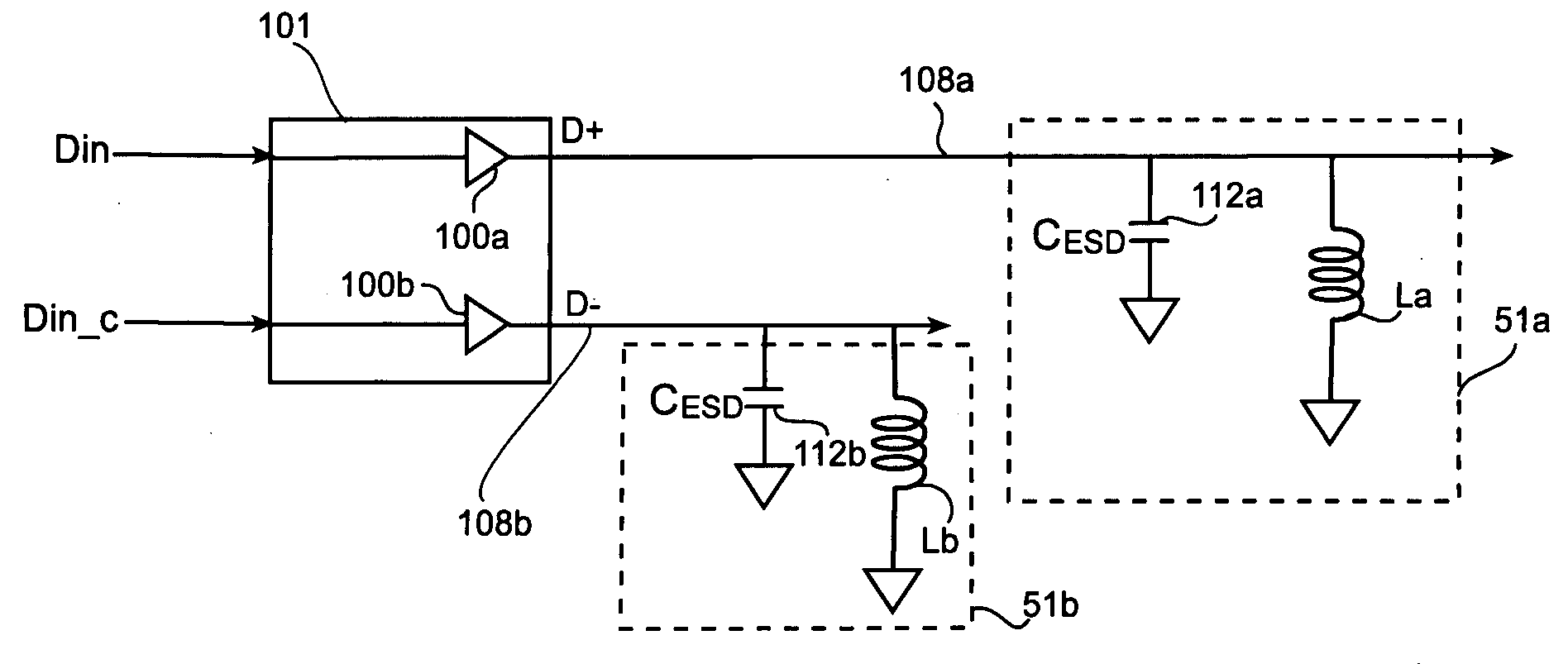

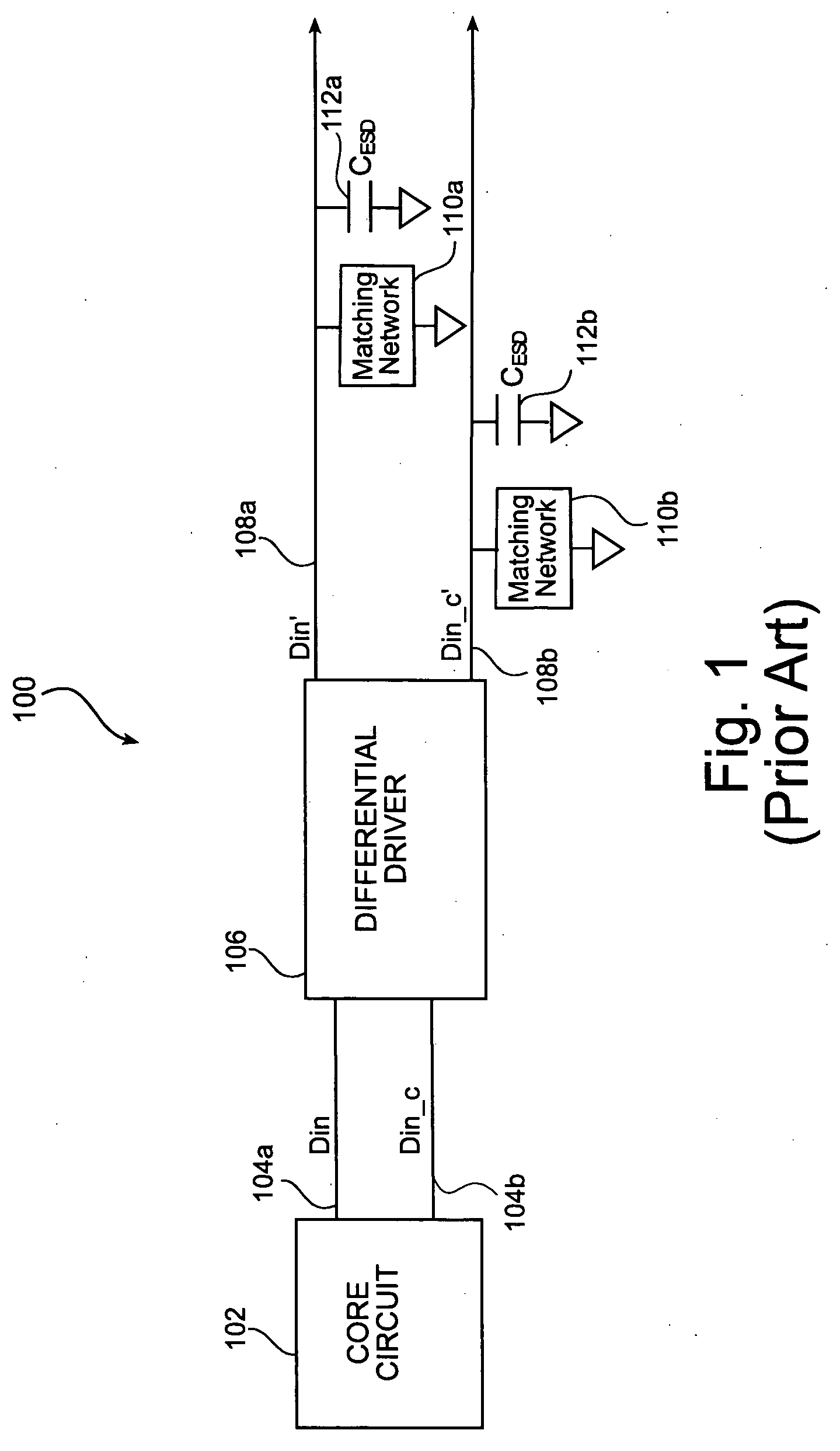

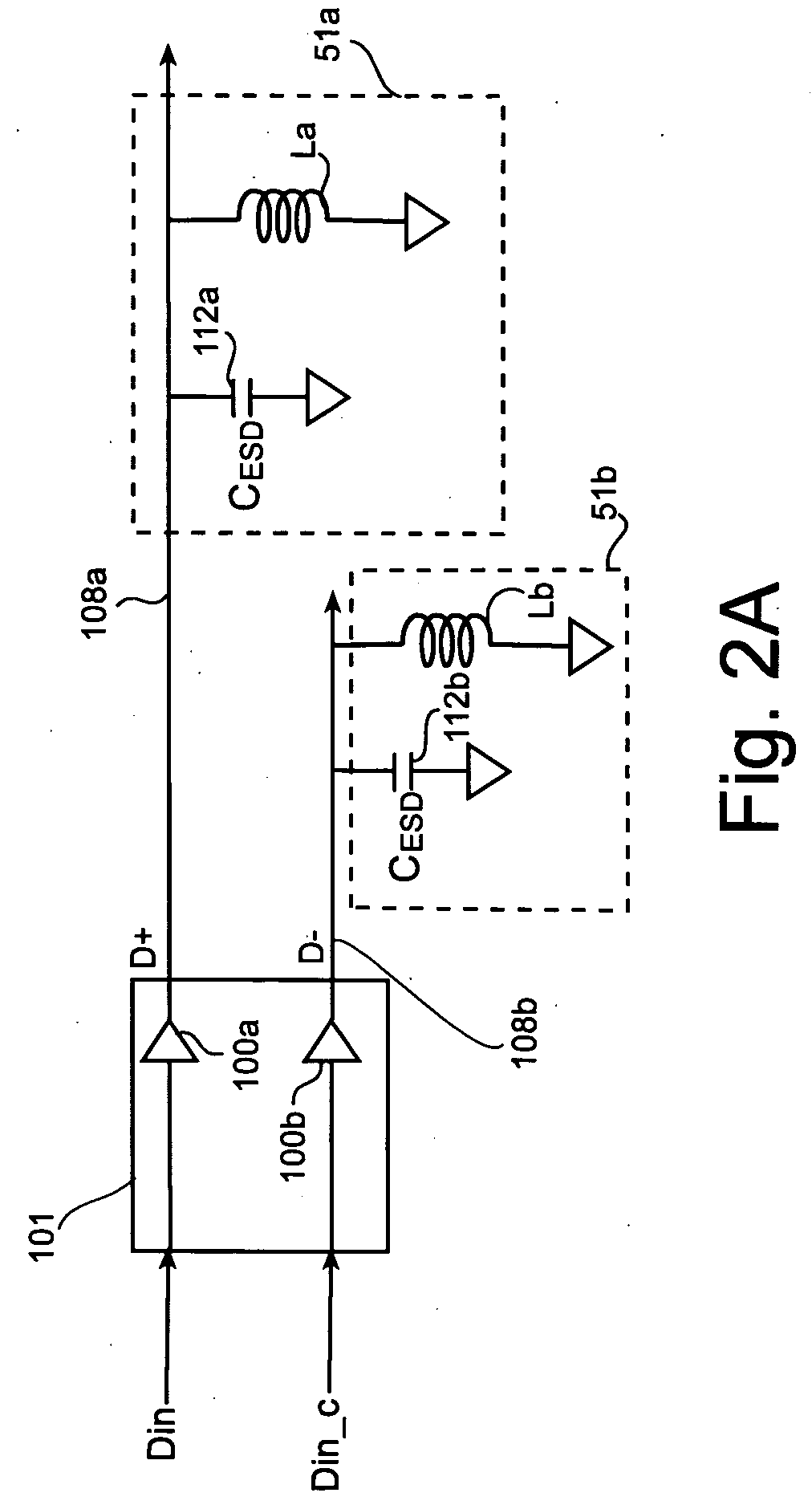

Methods and systems for rise-time improvements in differential signal outputs

InactiveUS7224180B2Reduce load effectSwitching accelaration modificationsMultiple-port networksCapacitanceDifferential signaling

A method for maintaining signal integrity of a differential output signal generated from a differential driver is disclosed. The method includes receiving the differential output signal from the differential driver. Once received, the method includes tuning the differential output signal by exposing the differential output signal to an inductance. The inductance is configured to reduce signal mismatch between complementary signals of the differential output signal. The signal mismatch is a result of having each of the complementary signals exposed to different capacitive loading. A device and system is also provided, which include integrating an inductor between the output leads of a differential driver. The inductor is sized for the particular frequency of operation, and the inductor provides an inductance that assists in eliminating mismatch between the complementary signals of the differential output. A reduction and / or elimination of the mismatch will assist in improving the rise-time of the differential signals.

Owner:SEIKO EPSON CORP

Level conversion circuit

InactiveUS20080001628A1Reduce the differenceDifferenceDelay compensationLogic circuit coupling/interface arrangementsElectricityPower inverter

A level conversion circuit includes an input buffer receiving an external signal, cascade-connected inverter circuits arranged in rear of the input buffer, and a switching circuit supplying an internal power supply potential to a power supply terminal of the inverter circuit while an input signal input to the inverter circuit changes from low level to high level, and supplying an external power supply potential to the power supply terminal while the input signal changes from the high level to the low level. The difference between a time necessary for the input signal to exceed a threshold of one of the inverter circuits when the input signal changes from the low level to the high level and time necessary for the input signal to exceed the threshold of the inverter circuit when the input signal changes from the high level to the low level can be thereby reduced.

Owner:ELPIDA MEMORY INC

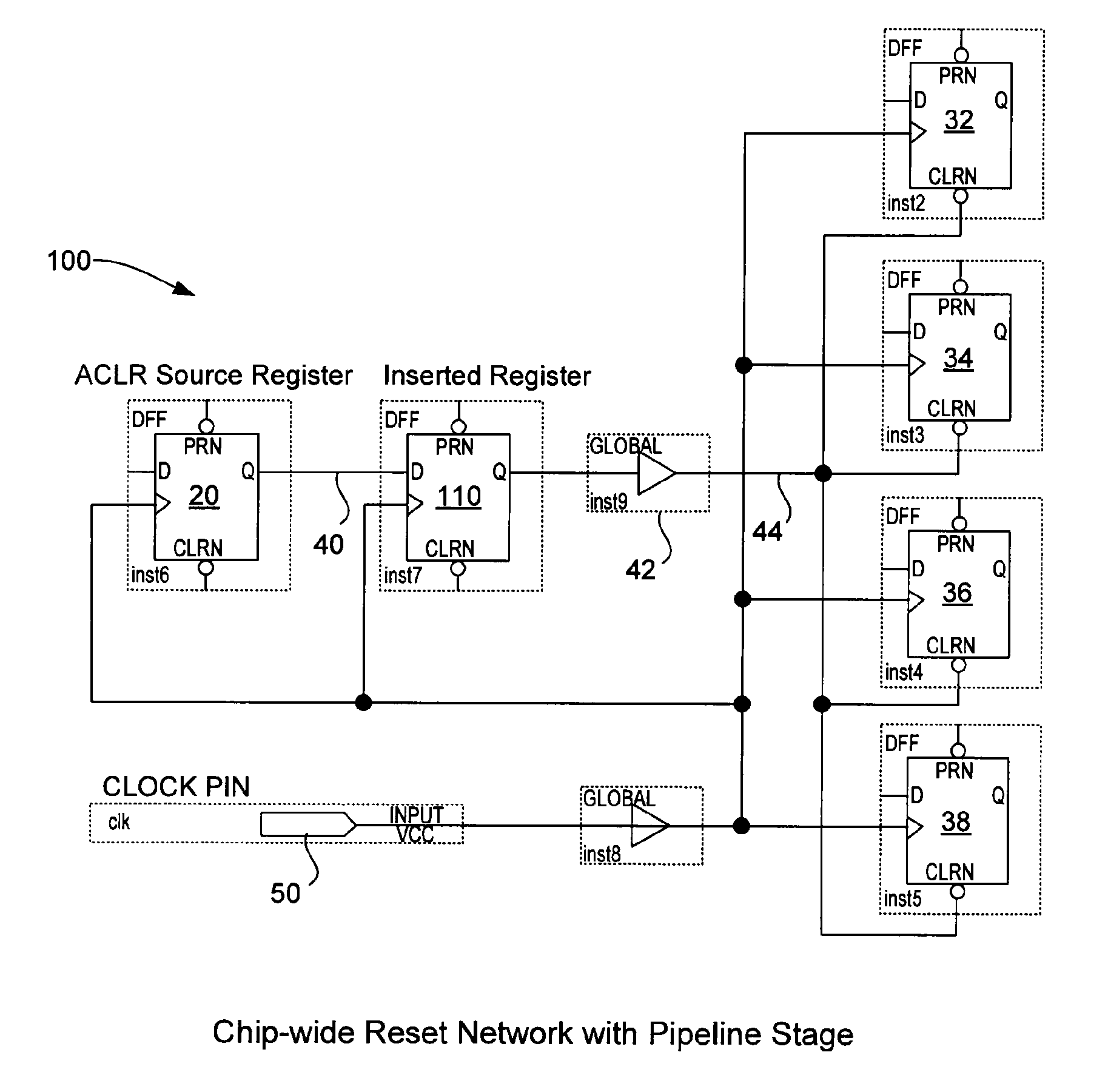

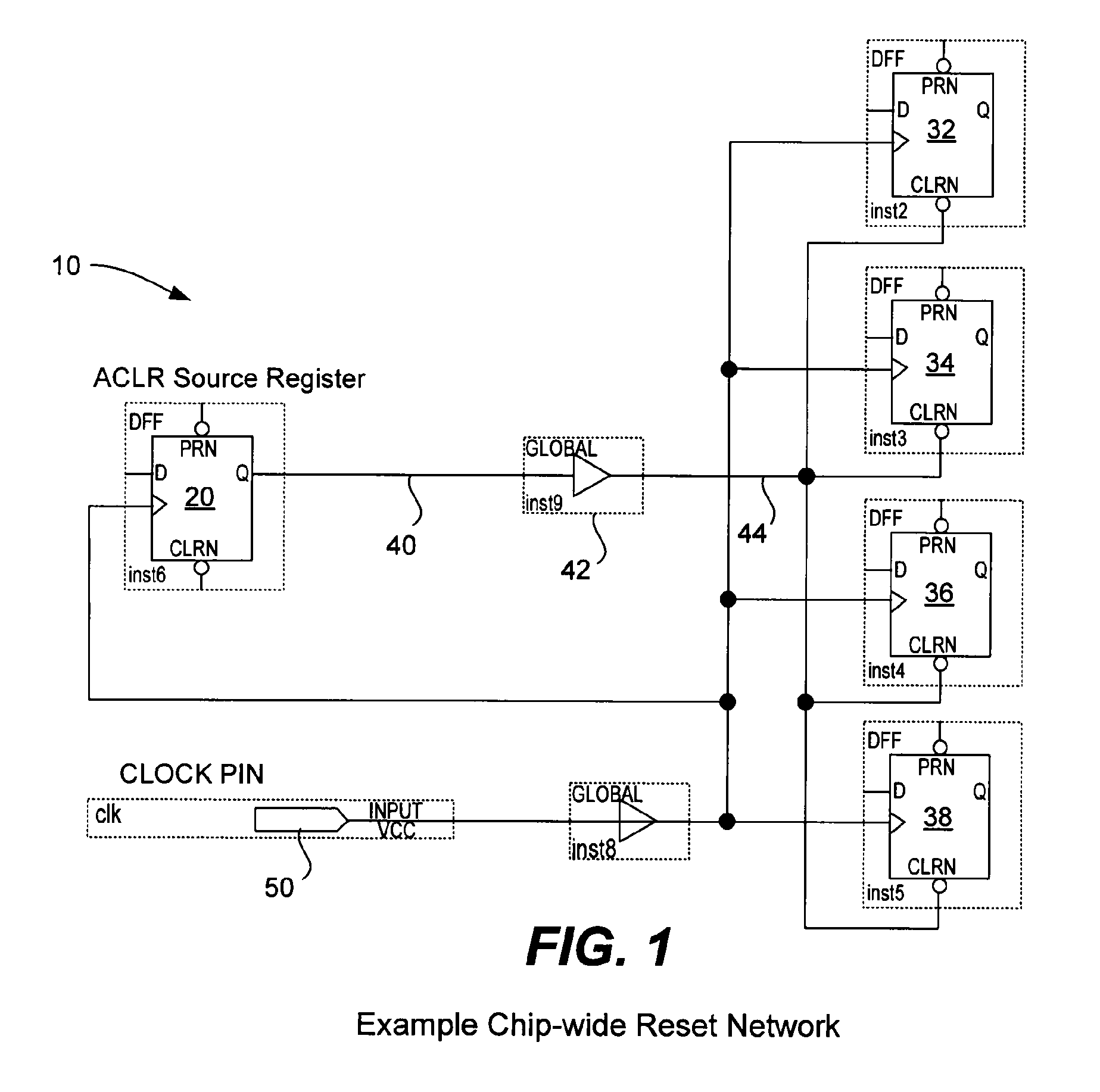

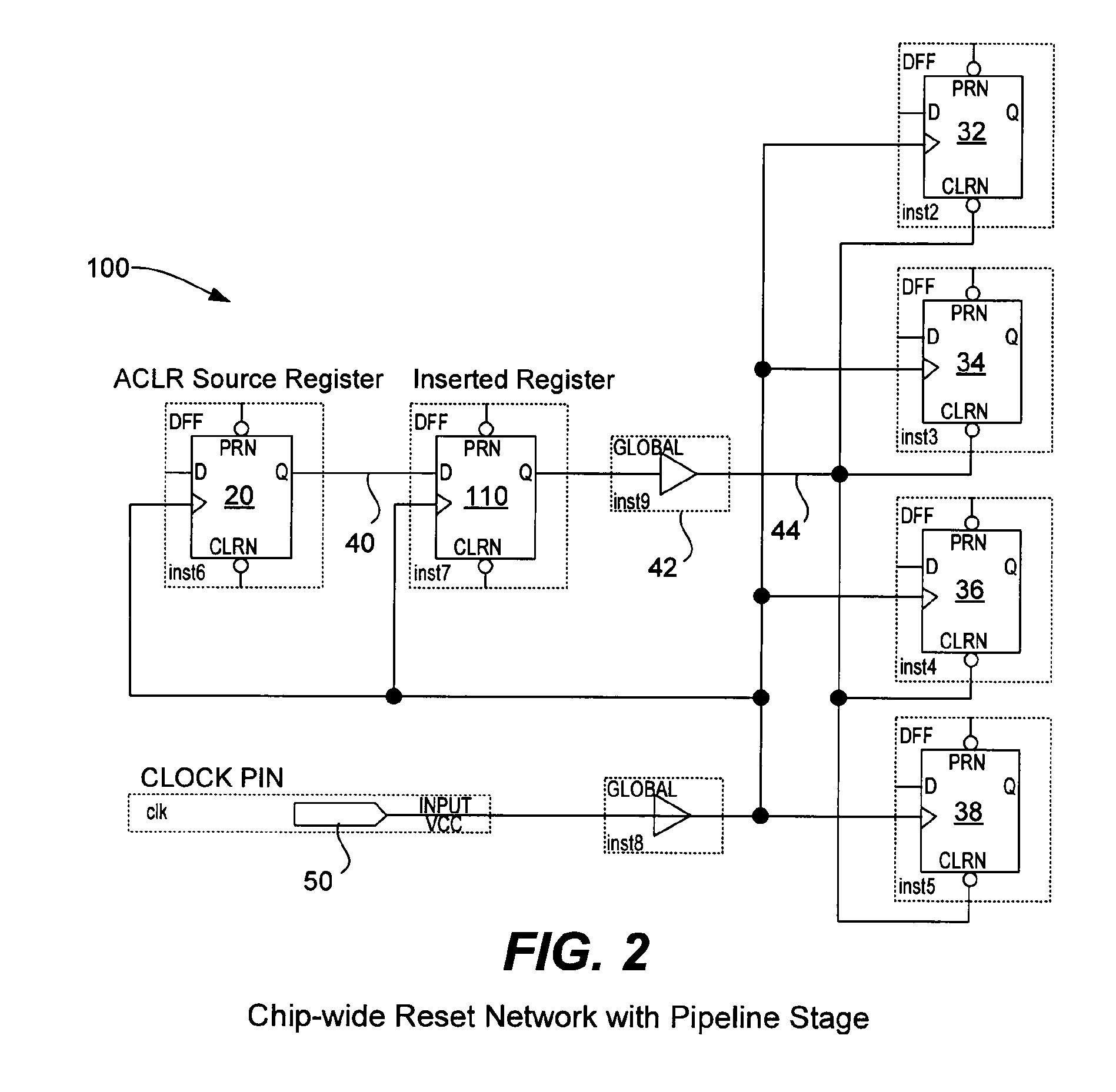

Automatic asynchronous signal pipelining

InactiveUS7676768B1Reduce distribution delayFast internetDelay compensationCAD circuit designTiming marginProcessor register

An electronic design automation (EDA) tool alters a user's netlist to provide timing success for distribution of asynchronous signals. Distribution networks are used with the addition of pipeline registers before and / or after the distribution buffer. Or, a tree of pipeline registers is inserted between the asynchronous source and the destination registers. Or, any number of distribution networks are stitched together and pipeline stages may be inserted before and / or after each distribution buffer. Or, beneficial skew is utilized by introducing a delay component that skews a clock signal. The skewed clock signal drives a pipeline register that is inserted before a distribution buffer in order to improve timing margin. Any of various compilation techniques may be used within the EDA tool to solve the problem of distributing high-speed, high-fanout asynchronous signals. The technique has utility for high-performance FPGAs and structured ASIC families, as well as for low-cost FPGAs and other types of logic devices.

Owner:ALTERA CORP

Enhanced delay matching buffer circuit

ActiveUS20070194815A1Enhanced delay matchingElectric pulse generatorDelay compensationControl signalVoltage source

A buffer circuit includes an input stage including at least one MOS device having a first threshold voltage associated therewith, the input stage being adapted to receive an input signal referenced to a first voltage supply. The buffer circuit further includes an output stage including at least one MOS transistor having the first threshold voltage associated therewith, an input of the output stage being connected to an output of the input stage, the output stage being operative to generate an output signal which is indicative of a logic state of the input signal. The buffer circuit includes a delay control circuit adapted for connection between at least one of the first voltage supply and a voltage return of the buffer circuit, and at least one of the input stage and the output stage. The delay control circuit includes at least one MOS device having a second threshold voltage associated therewith. The MOS device in the delay control circuit being adapted to receive, as a control signal, a second voltage supply, a delay of the buffer circuit being at least partially controlled as a function of a process parameter, the second voltage supply and / or a temperature of the MOS device in the delay control circuit.

Owner:AVAGO TECH INT SALES PTE LTD

Semiconductor integrated circuit device

InactiveUS20050007183A1Logic circuits coupling/interface using field-effect transistorsDelay compensationControl signalEngineering

Owner:RENESAS ELECTRONICS CORP

Methods and systems for rise-time improvements in differential signal outputs

InactiveUS20060103418A1Reduce load effectSwitching accelaration modificationsSemiconductor/solid-state device detailsCapacitanceDifferential signaling

A method for maintaining signal integrity of a differential output signal generated from a differential driver is disclosed. The method includes receiving the differential output signal from the differential driver. Once received, the method includes tuning the differential output signal by exposing the differential output signal to an inductance. The inductance is configured to reduce signal mismatch between complementary signals of the differential output signal. The signal mismatch is a result of having each of the complementary signals exposed to different capacitive loading. A device and system is also provided, which include integrating an inductor between the output leads of a differential driver. The inductor is sized for the particular frequency of operation, and the inductor provides an inductance that assists in eliminating mismatch between the complementary signals of the differential output. A reduction and / or elimination of the mismatch will assist in improving the rise-time of the differential signals.

Owner:SEIKO EPSON CORP

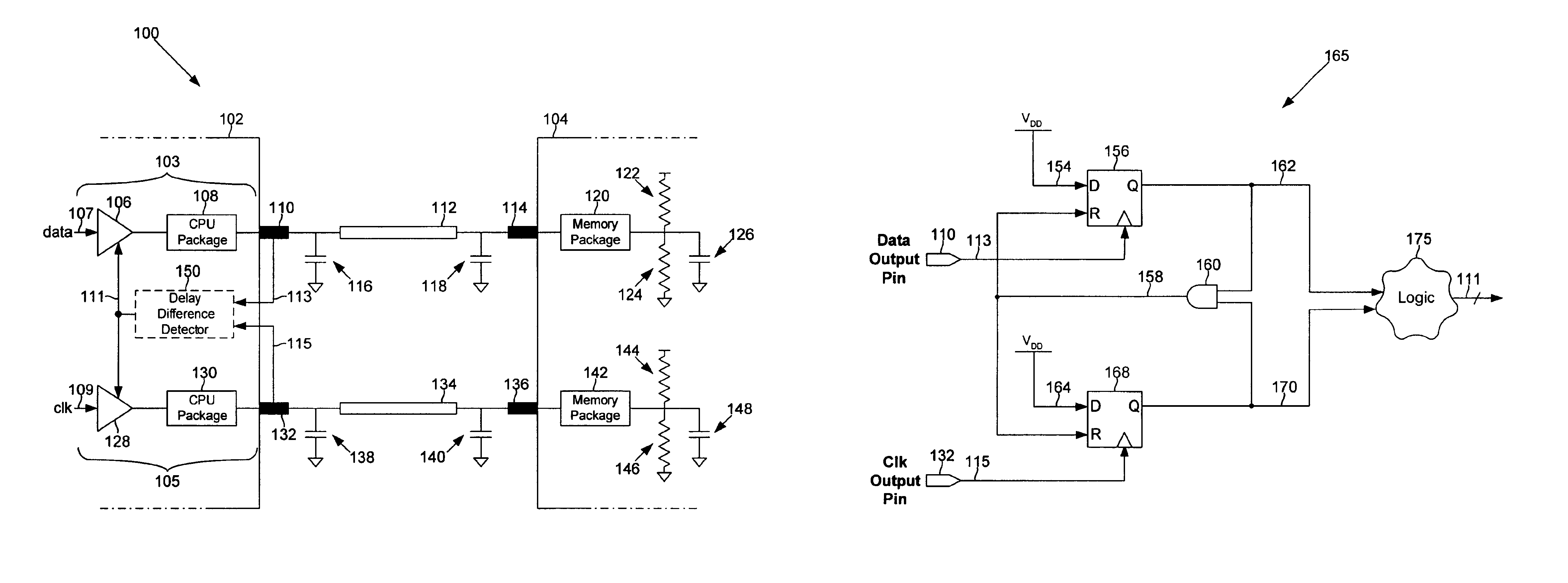

Self-correcting I/O interface driver scheme for memory interface

A self-correcting I / O interface driver scheme uses a delay difference detector to detect a difference in delays between an I / O data path and an I / O clock path. The delay difference detector inputs signals from a data output pin connected to the I / O data path and a clock output pin connected to the I / O clock path. Upon determining a delay difference between the signals from the data and clock output pins, the delay difference detector generates signals to one or more drivers in the I / O data path and the I / O clock path. These signals from the delay difference detector are used to effectively adjust delays of the one or more drivers in order to effectively reduce the delay difference between the I / O data path and the I / O clock path.

Owner:ORACLE INT CORP

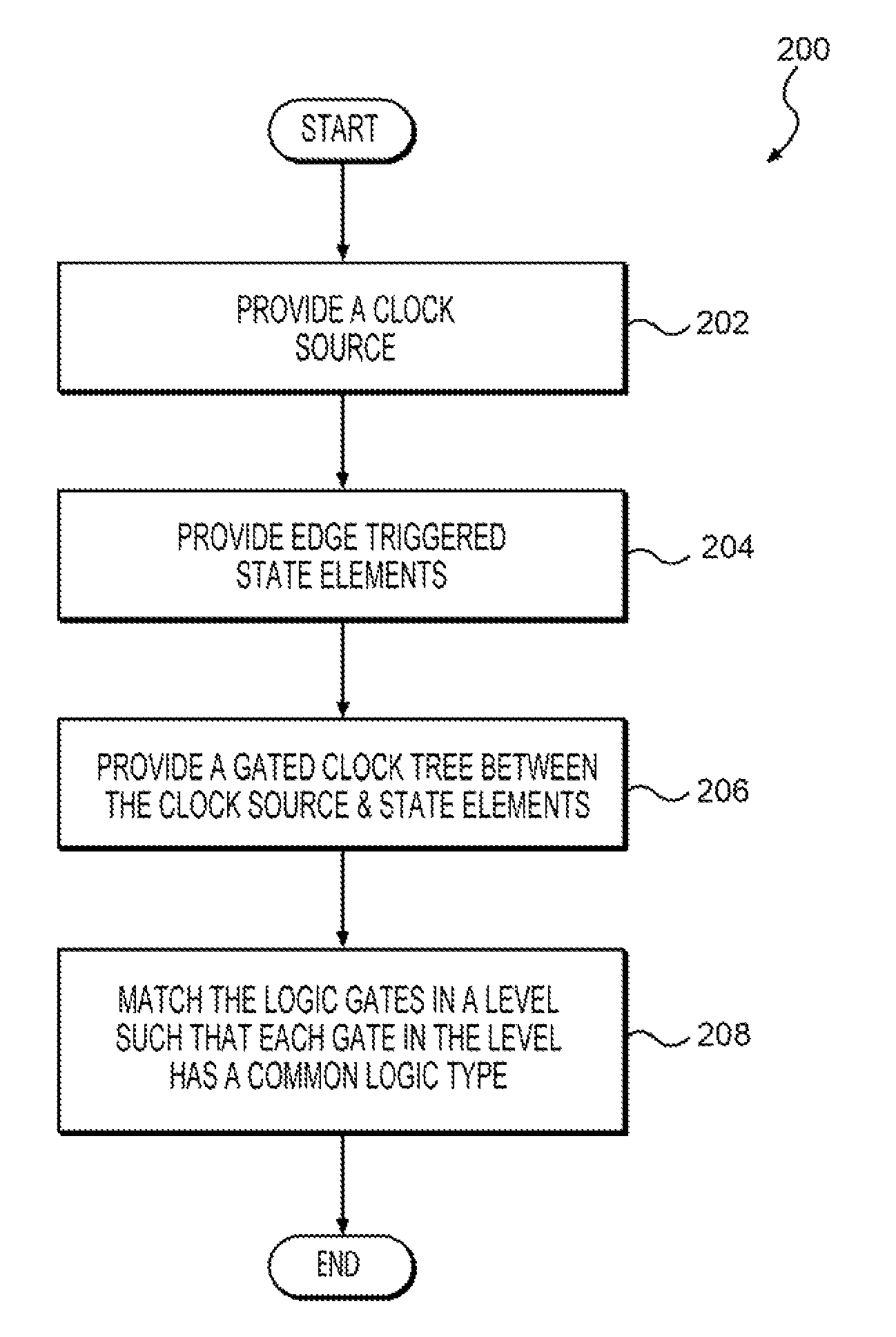

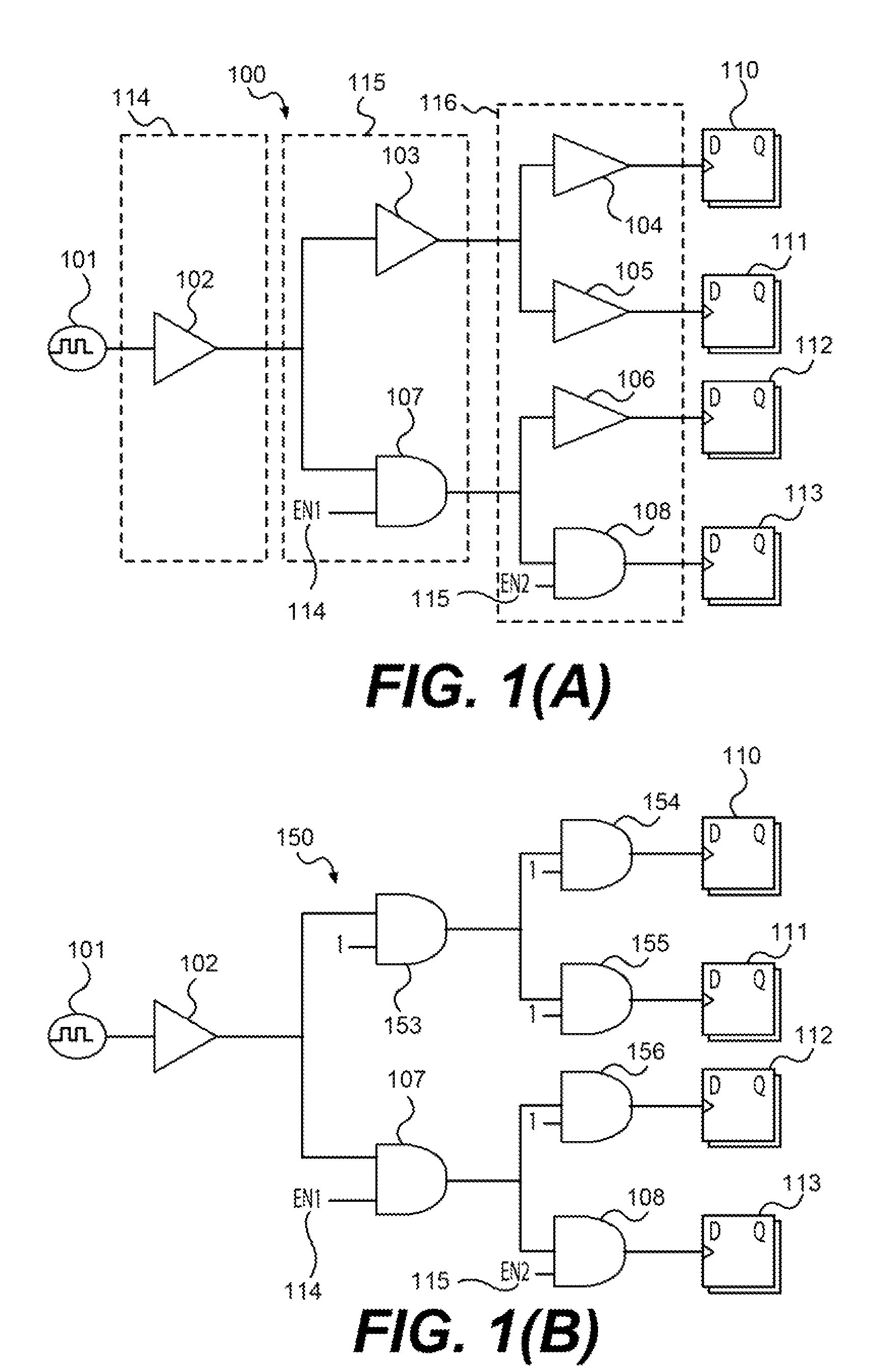

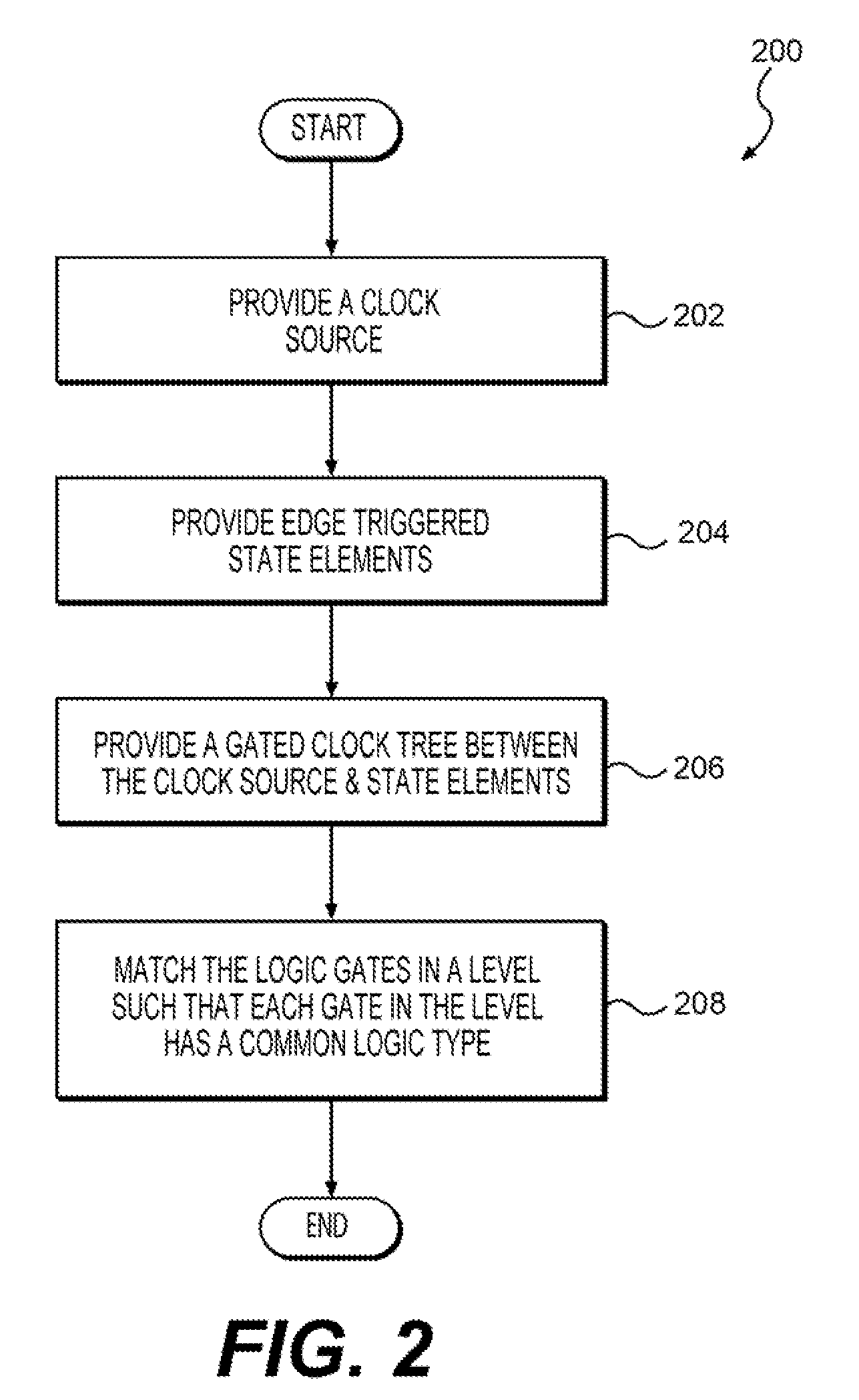

Methods and systems for reducing clock skew in a gated clock tree

Systems and methods for synthesizing a gated clock tree with reduced clock skew are provided. A gated clock tree circuit with reduced clock skew may include a clock source and edge-triggered state elements. A gated clock tree disposed between the clock source and state elements may include a level in which each logic gate has a common logic type. Logic gates in the gated clock tree may also be configured as logic-gate buffers. The logic gates may also be configured as NAND-gated equivalents. The clock signal distributed through the gated clock tree may drive both positive-edge-triggered and negative-edge-triggered state elements.

Owner:SYNOPSYS INC

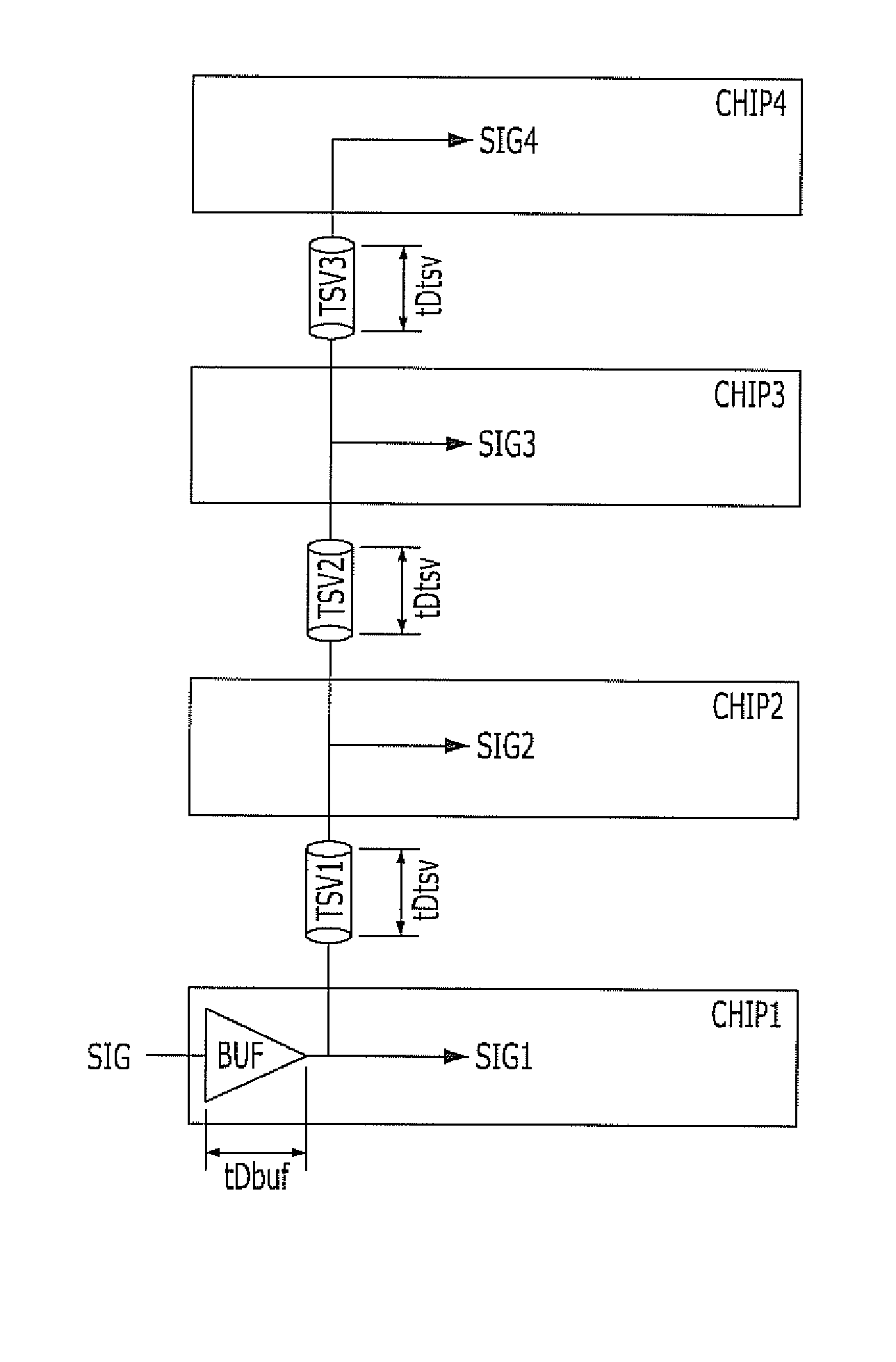

Semiconductor integrated circuit and signal transmission method thereof

ActiveUS20130021079A1Minimize biasSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipDelayed time

A semiconductor integrated circuit includes a plurality of semiconductor chips stacked in a multi-layer structure; a correction circuit in each semiconductor chip configured to reflect a delay time corresponding to the position of the chip in the stack into an input signal to output to each semiconductor chip; and a plurality of through-chip vias formed vertically through each of the semiconductor chips and configured to transmit the input signal to the semiconductor chip.

Owner:SK HYNIX INC

Comparator for determining process variations

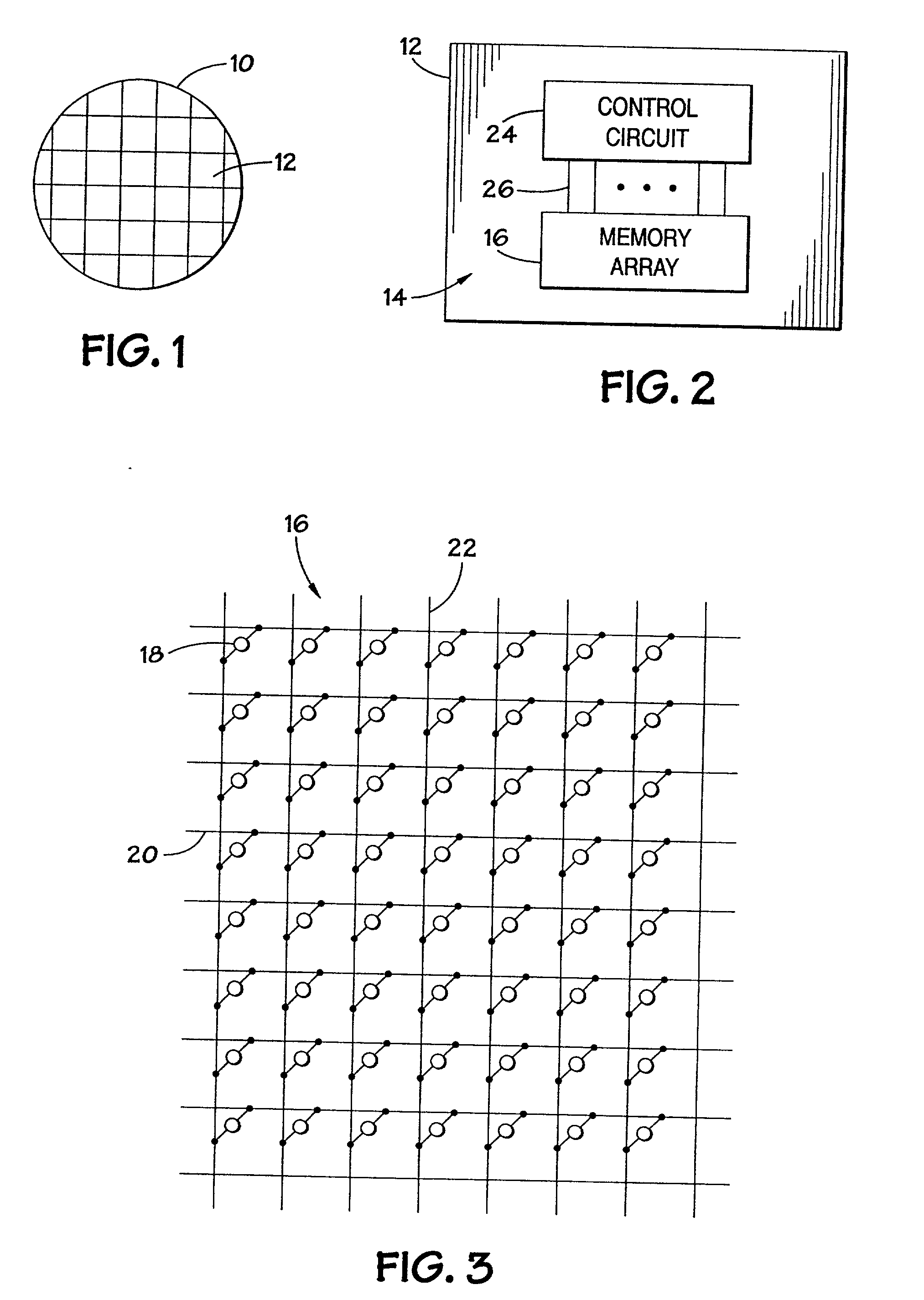

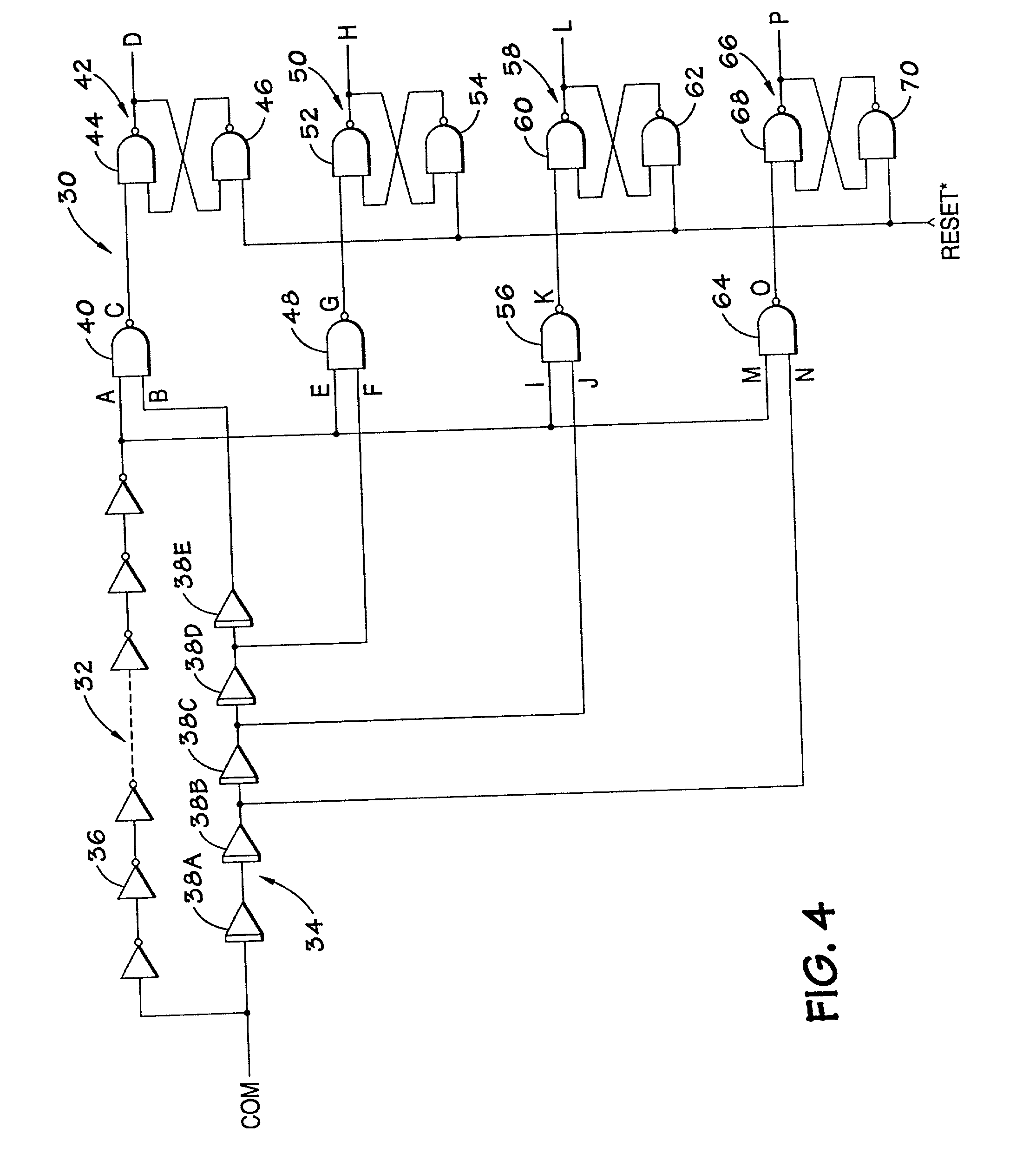

InactiveUS20020021158A1Multiple input and output pulse circuitsDelay line applicationsPropagation delayFirst pathway

A comparison circuit may be fabricated along with a primary circuit on a semiconductor substrate. The propagation delay of a comparison signal across a first path of circuit elements is compared to propagation delays of the comparison signal across a second path of delay elements. As a semiconductor fabrication process varies, the relative propagation delays across the first and second paths will vary in a manner correlative to the process variations. By monitoring the relative propagation delays, the fabrication process may be controlled to ensure that the process does not vary to an undesirable extent. Also, various programmable delay elements may be fabricated into the primary circuit, and these programmable delay elements may be activated and / or deactivated in response to the relative propagation delays of the comparison circuit.

Owner:MICRON TECH INC

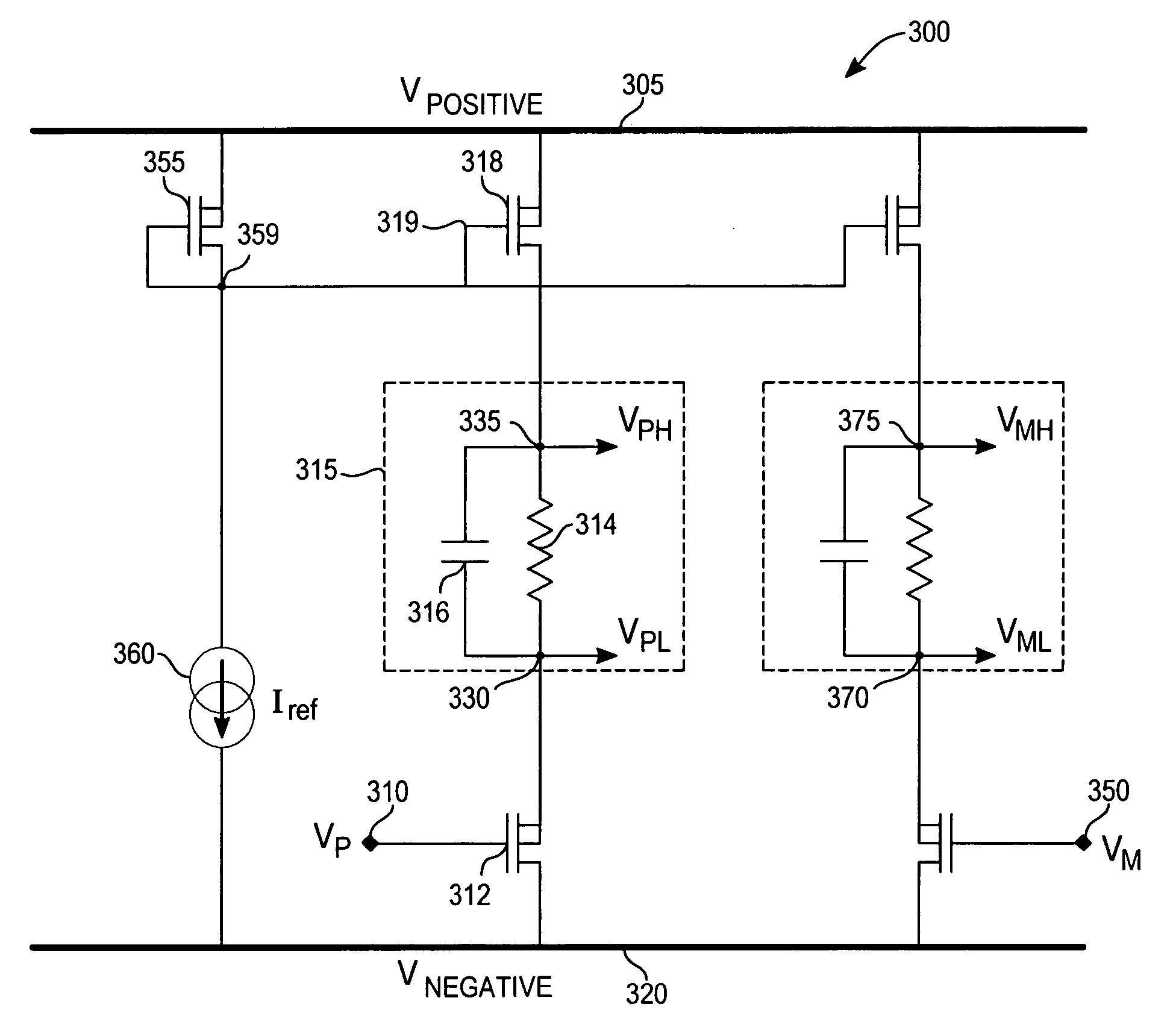

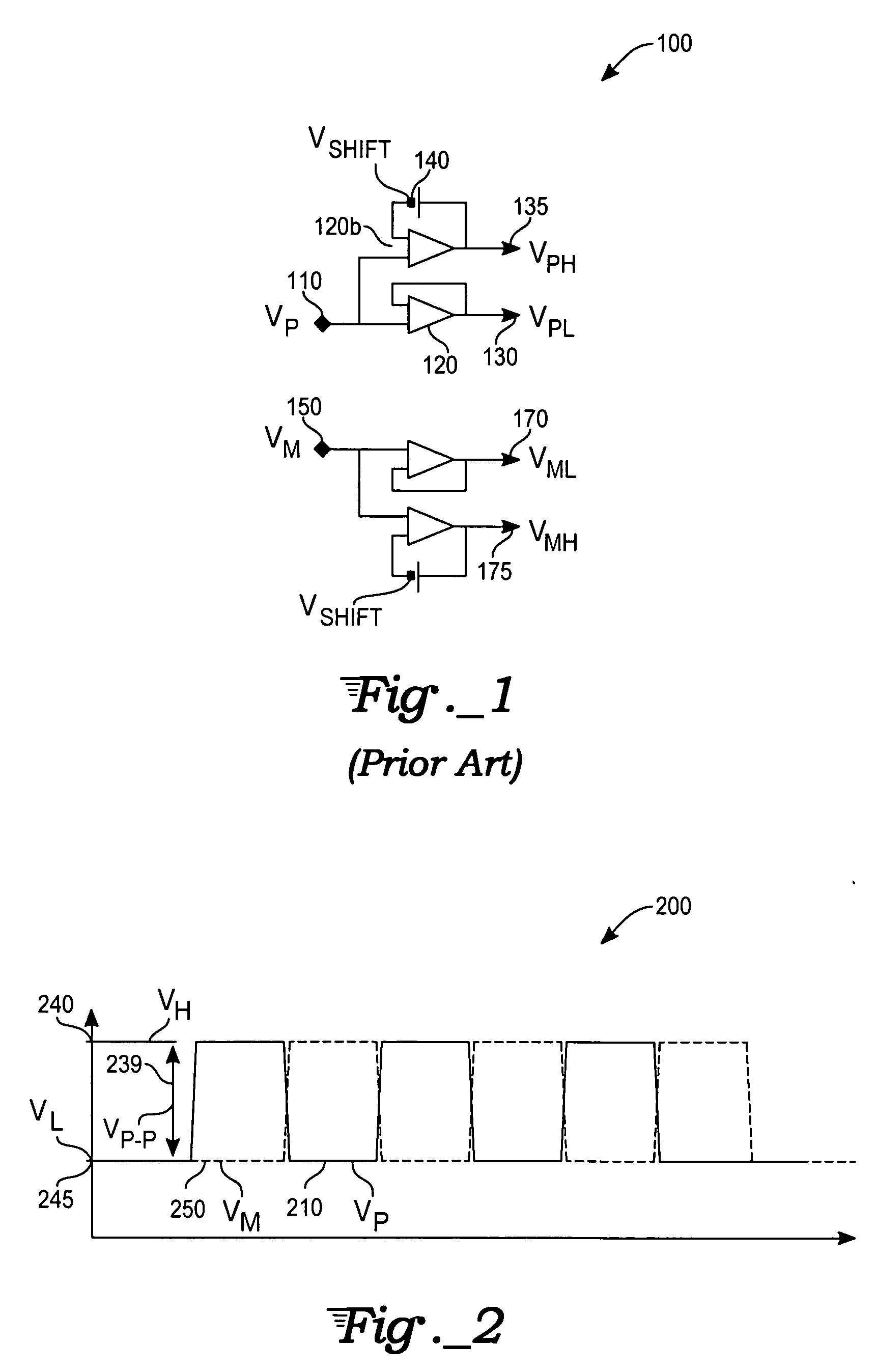

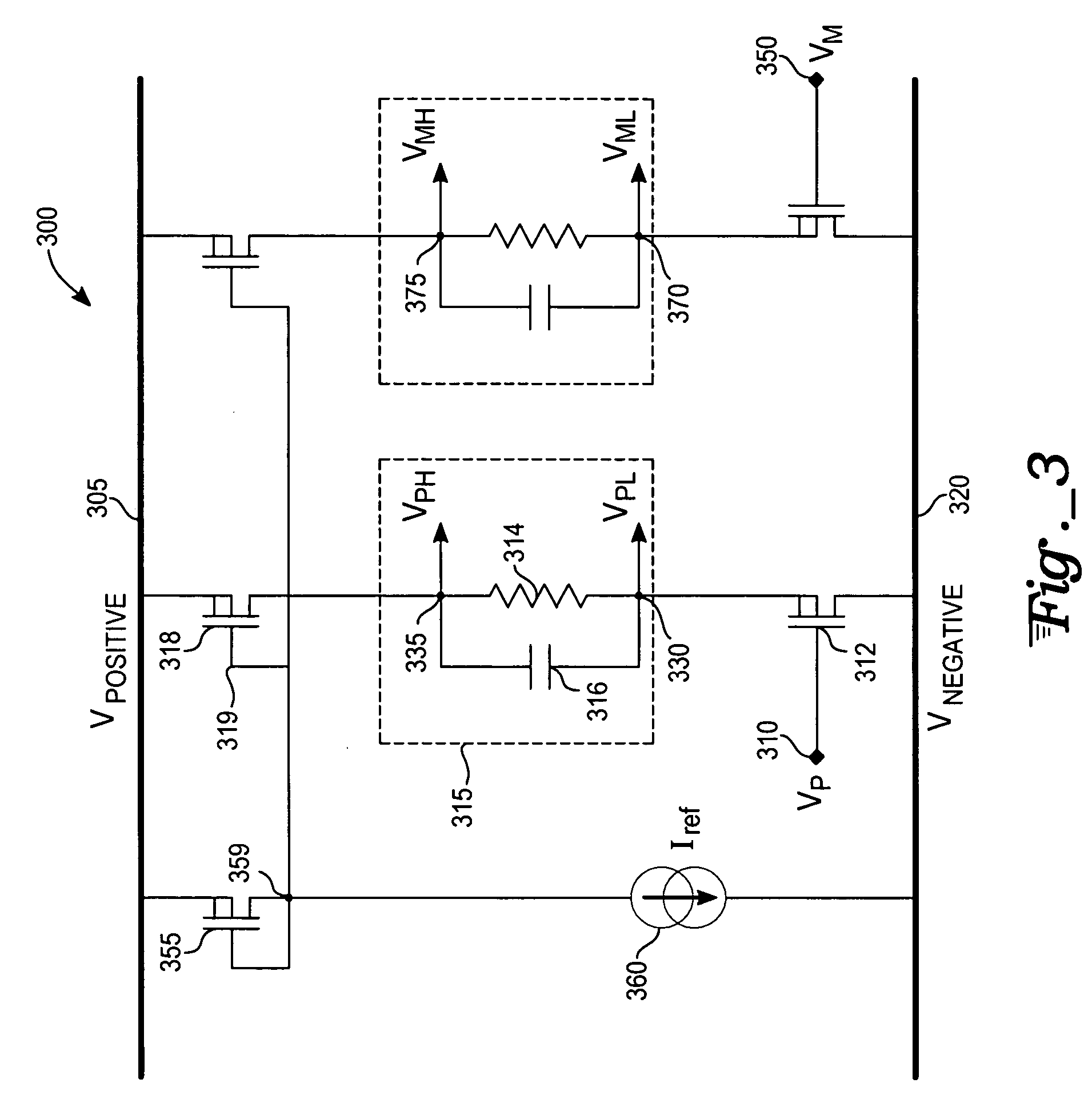

Detector of differential threshold voltage

A differential threshold voltage level detection circuit receives a differential voltage pair as an input, applying each component of the differential pair to an individual voltage shifting circuit. Each voltage shifting circuit is configured with a regulated current producing a shifted and a non-shifted version in-phase. For a shifted set of output differential voltages, the shift magnitude is proportional to the current entering a shifting circuit and is configured to be less than a peak-to-peak magnitude of the differential voltage to be detected. A current mirror within the detector contains a current reference configured to produce a current to be passed through a voltage generator. The current magnitude is sufficient to generate a regulated voltage output to the two current regulating devices that supply the voltage shifting circuits. An overlap detector receiving both differential voltage pairs produces a signal indicating an input is at a detection threshold.

Owner:ATMEL CORP

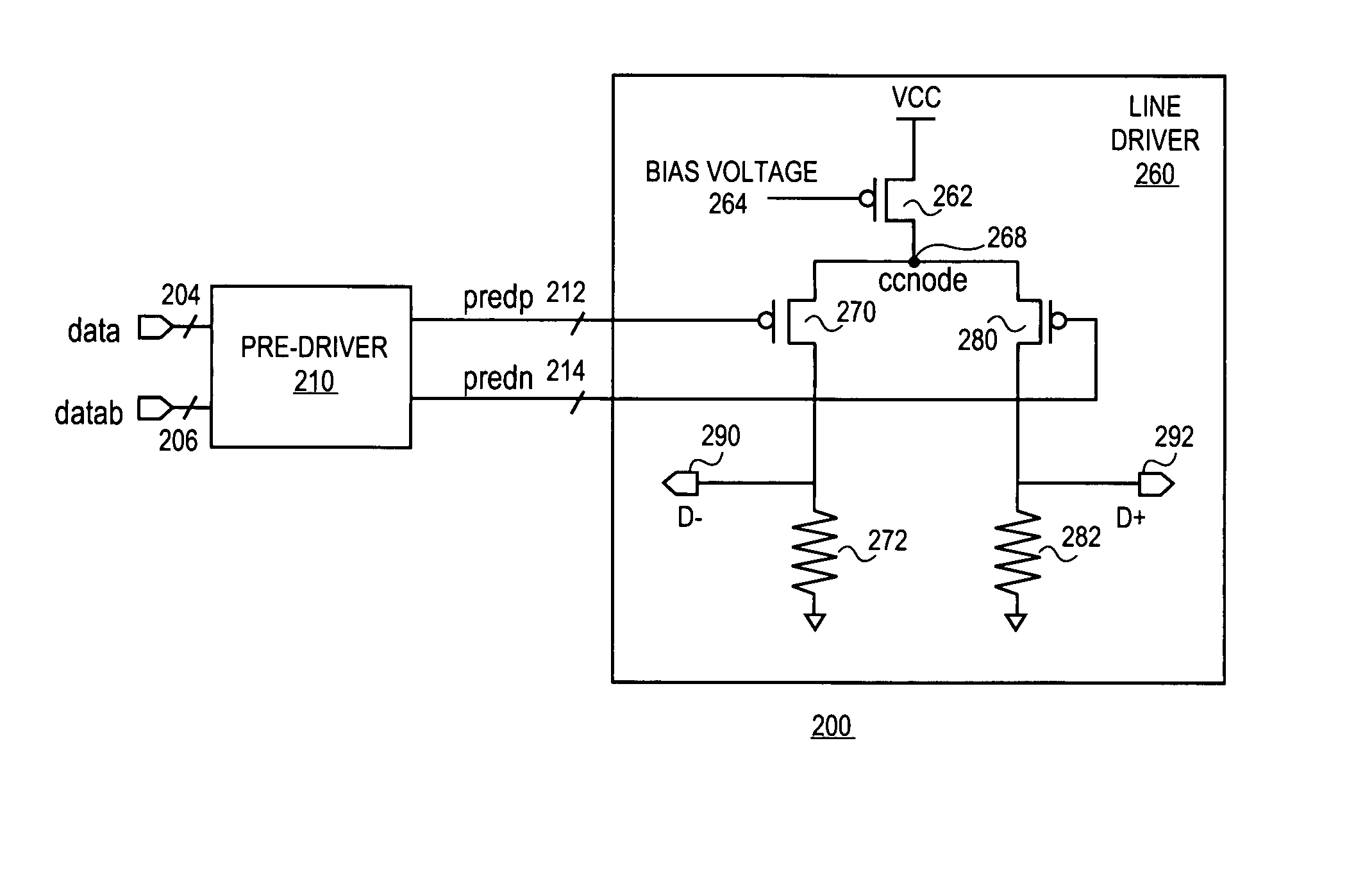

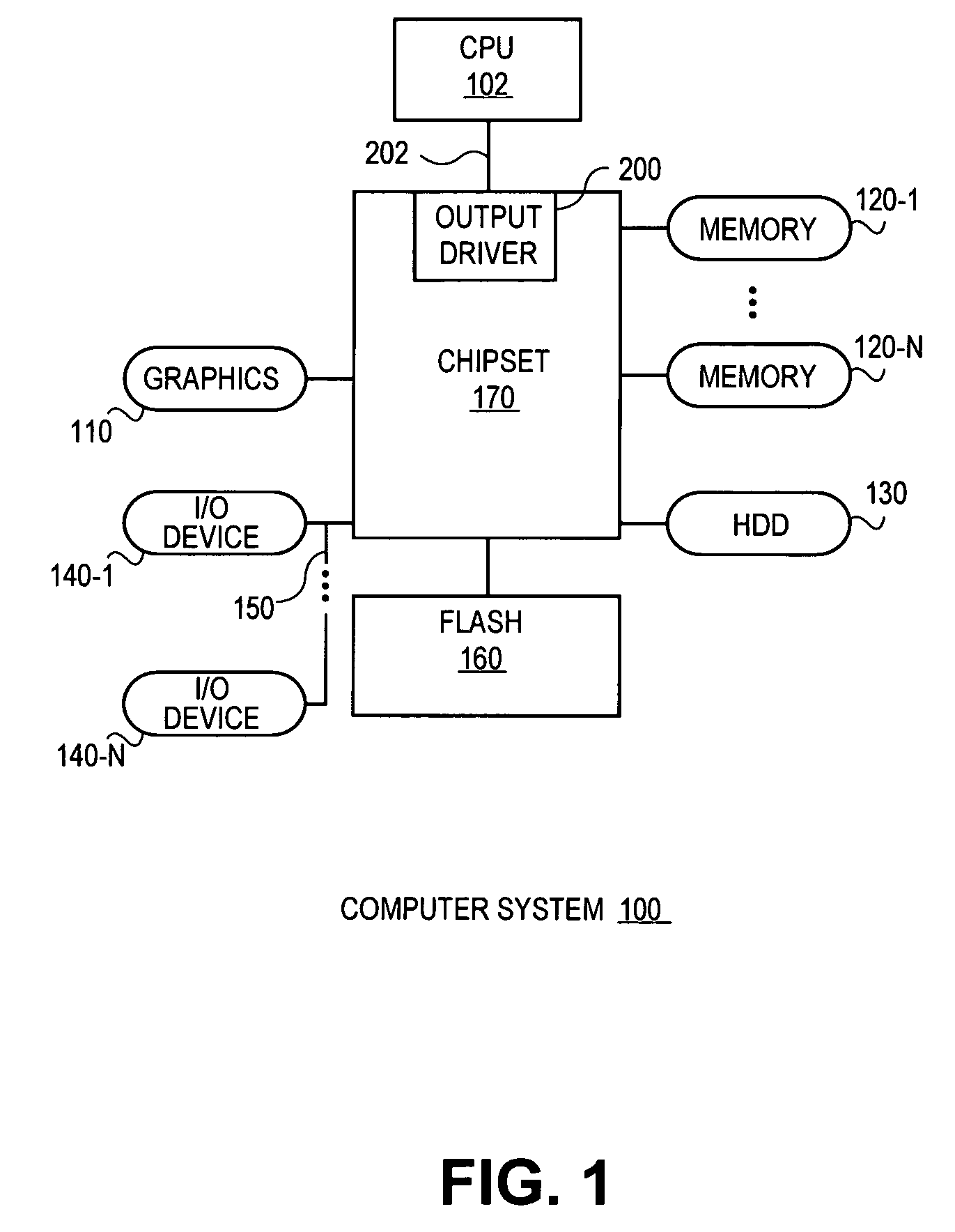

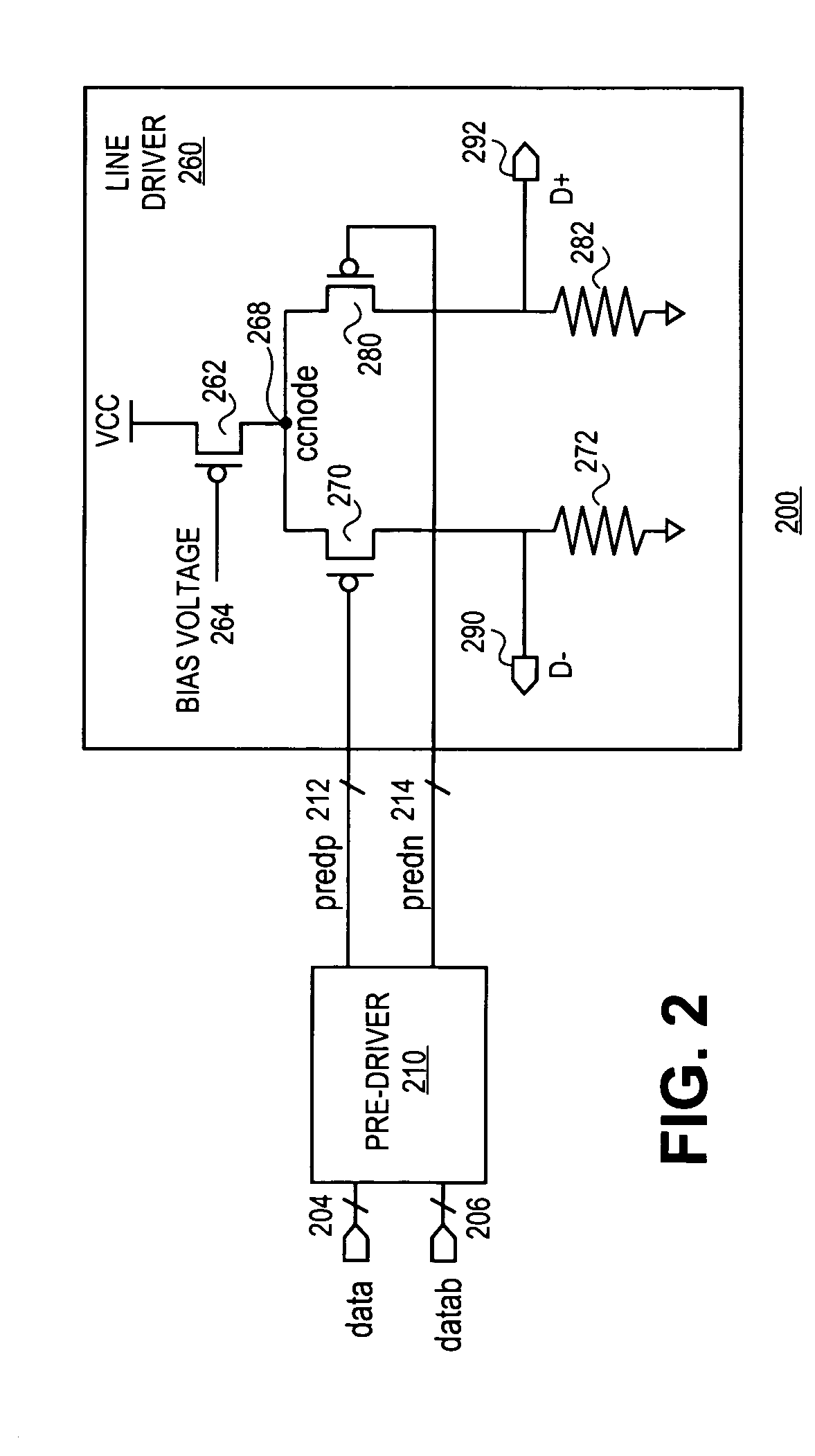

Apparatus and method for a low jitter predriver for differential output drivers

InactiveUS20050212561A1Logic circuits characterised by logic functionLogic circuits coupling/interface using field-effect transistorsDevice typeEngineering

A method and apparatus for a low jitter predriver for differential output drivers. In one embodiment, the predriver comprises a pull-up circuit having at least one pull-up device of a first device type and a pull-down circuit having at least one pull-down device of the first device type In one embodiment, the pull-up circuit and the pull-down circuit to charge an output node and a complement output node in opposite directions to generate a differential predriver signal pair. Accordingly, using the pull-up and pull-down circuits, the predriver circuit generates differential output signals. In one embodiment, the pull-up device and the pull-down device comprise N-channel metal oxide semiconductor (NMOS) devices. Other embodiments are described and claimed.

Owner:INTEL CORP

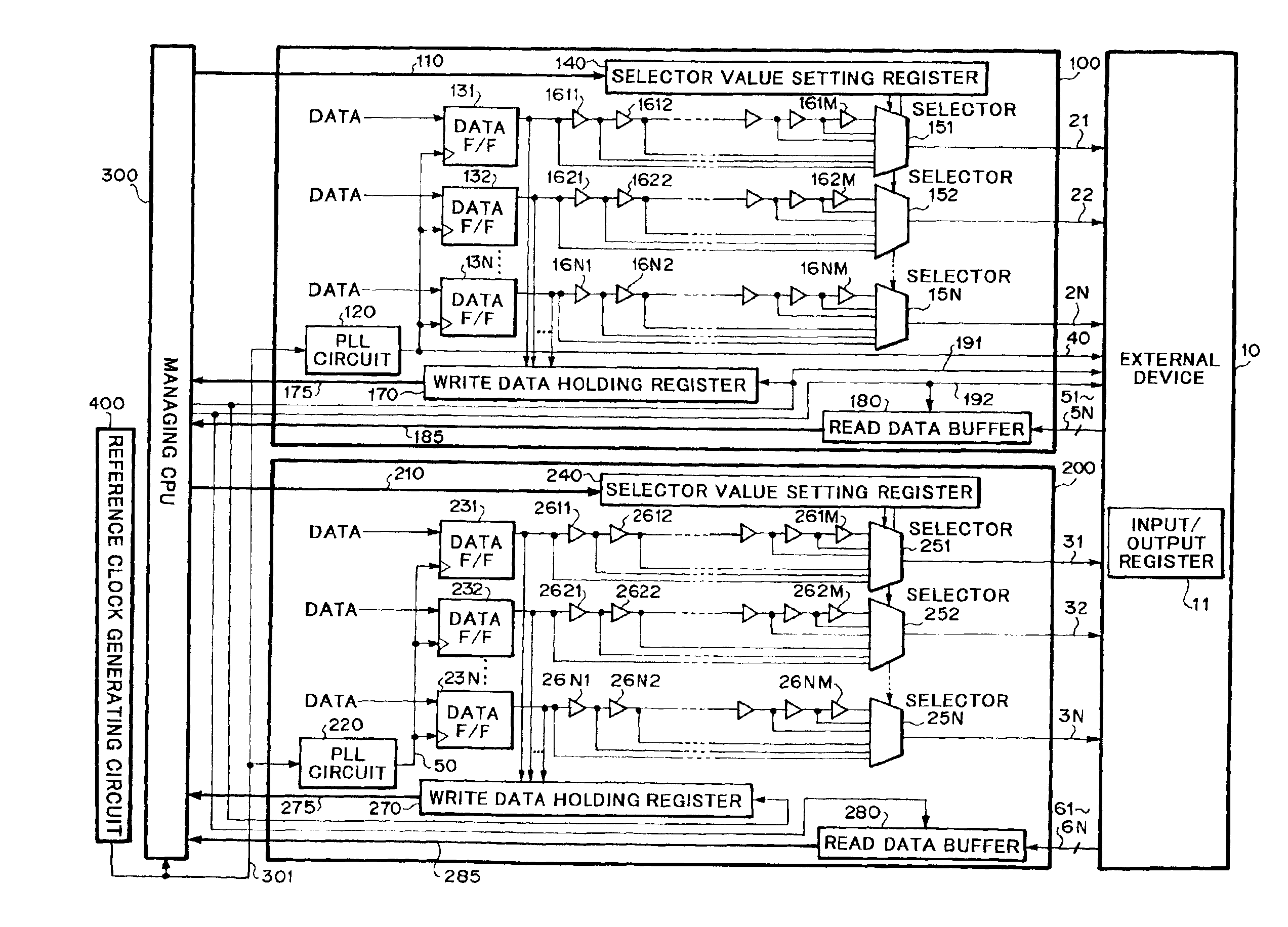

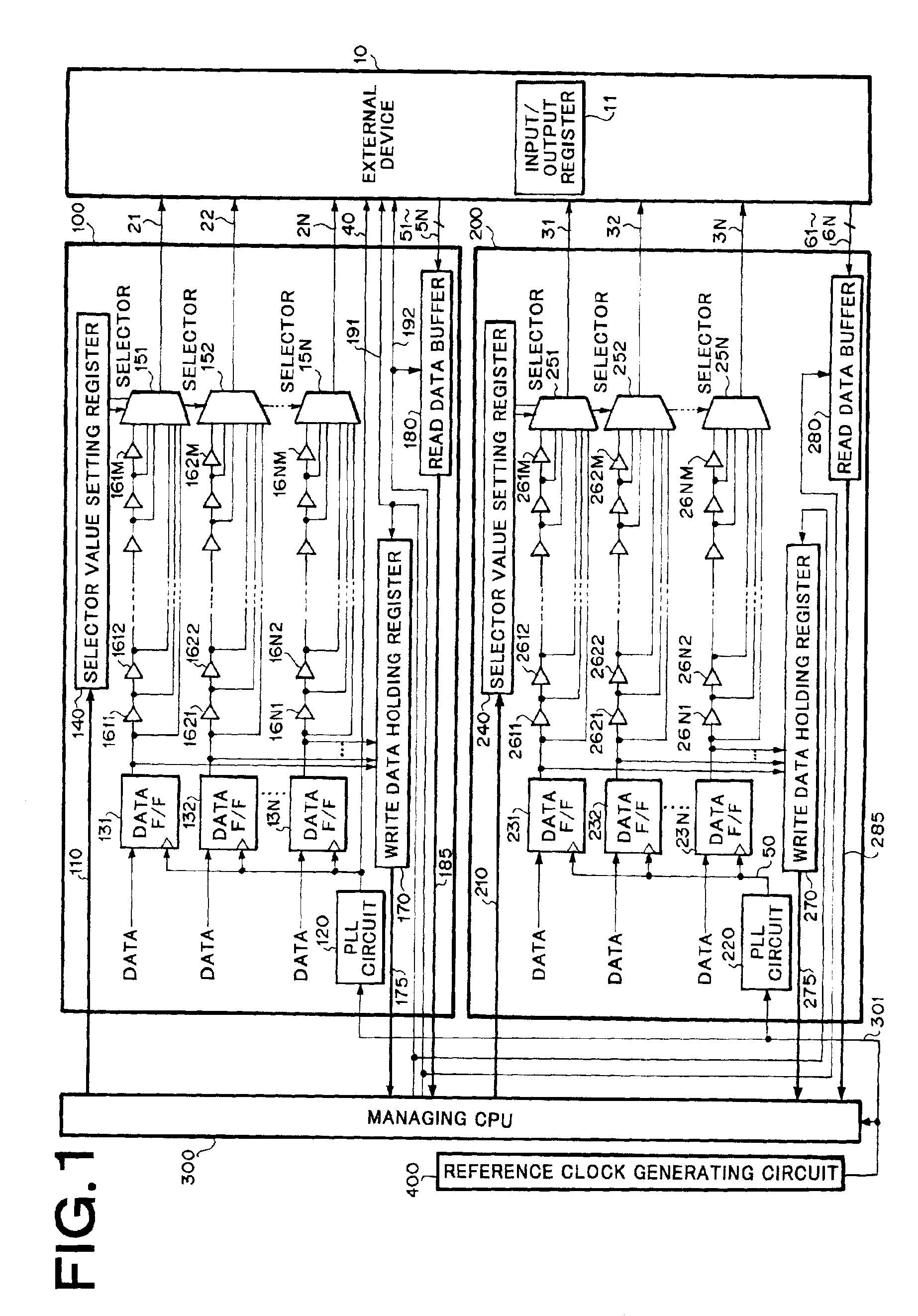

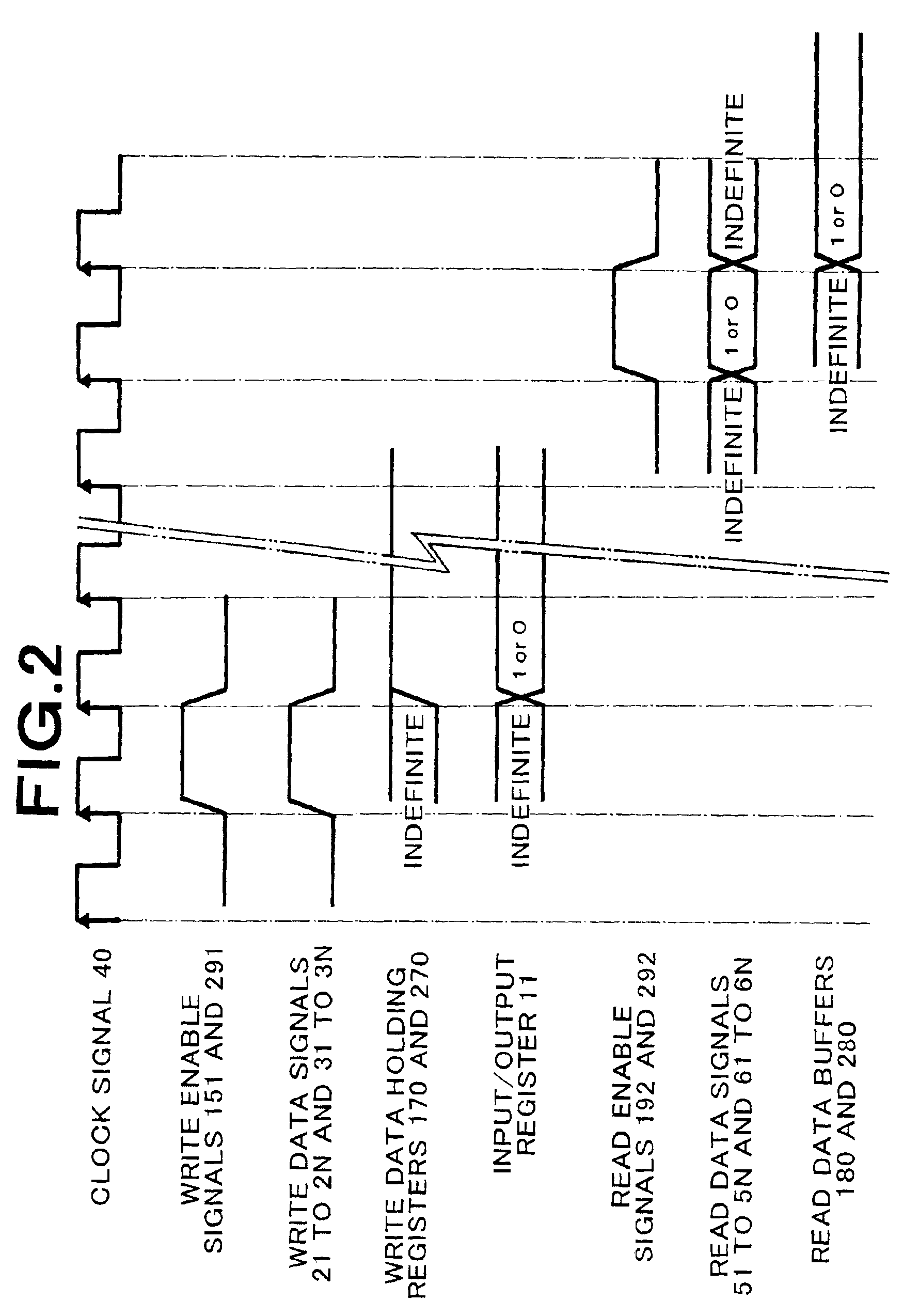

Skew adjusting circuit and semiconductor integrated circuit

InactiveUS6944801B2Error detection/correctionRecord information storageProcessor registerData storing

An output signal of a flip flop at an output stage is supplied to delay gates connected in series thereto. A selector selects the output signal of the flip flop at the output stage or an output signal of one of the delay gates and supplies the selected signal to an external device. A signal to be selected by the selector depends on the value of data stored in a selector value setting register. When a skew adjustment is performed, the output signal of the flip flop at the output stage is held in a write data holding register. The signal supplied to the external device is held in a read data buffer through an input / output register of the external device. Until the value of the signal stored in the write data holding register matches the value of the signal held in the read data buffer, the value of the data stored in the selector value setting register is varied.

Owner:NEC CORP

Popular searches

Pulse conversion Transmitter/receiver shaping networks Transmission line coupling arrangements Computing operations for integral formation Computing operations for integration/differentiation Current/voltage measurement Differential amplifiers Pulse manipulation Synchronising arrangement Dc-amplifiers with dc-coupled stages