Area compact type BCH paralleling decoding circuit supporting pre searching

A decoding circuit and pre-search technology, applied in the direction of cyclic code, error correction/detection using linear code, error correction/detection using block code, etc. Product reliability and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] Below in conjunction with the preferred embodiment shown in accompanying drawing, be described in further detail:

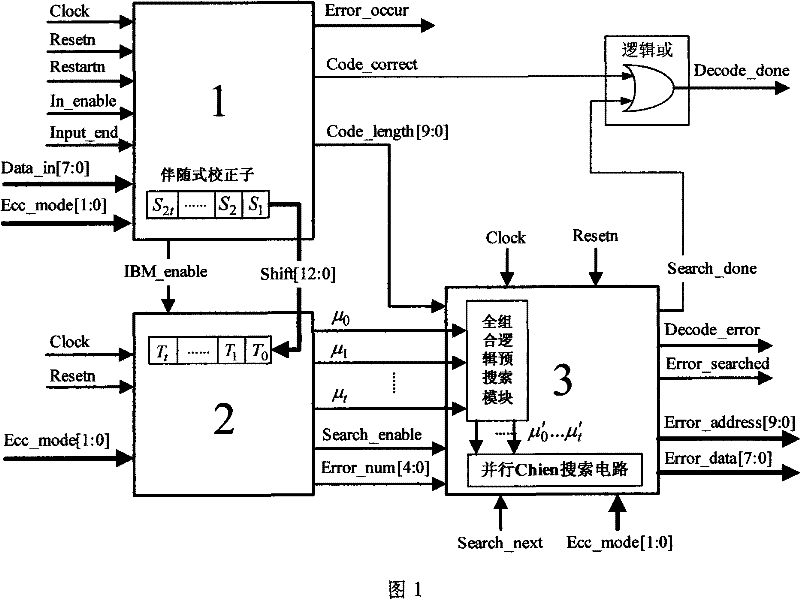

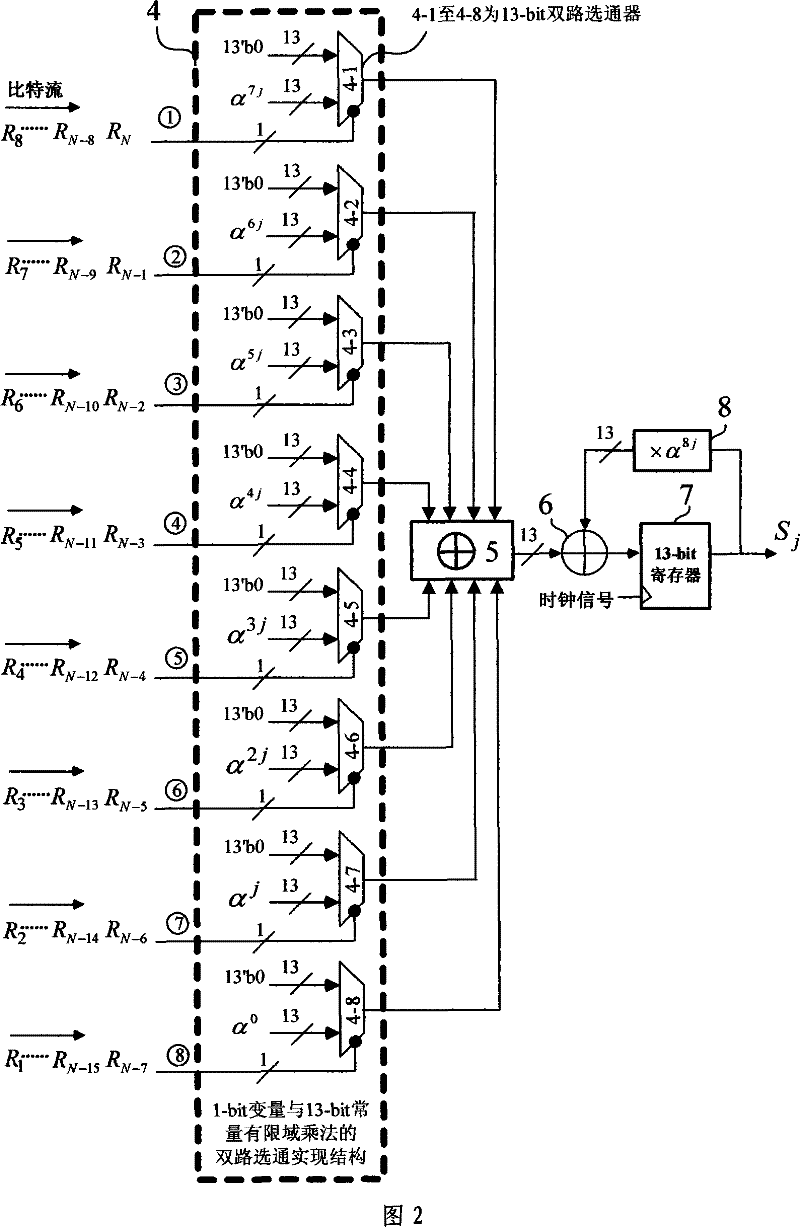

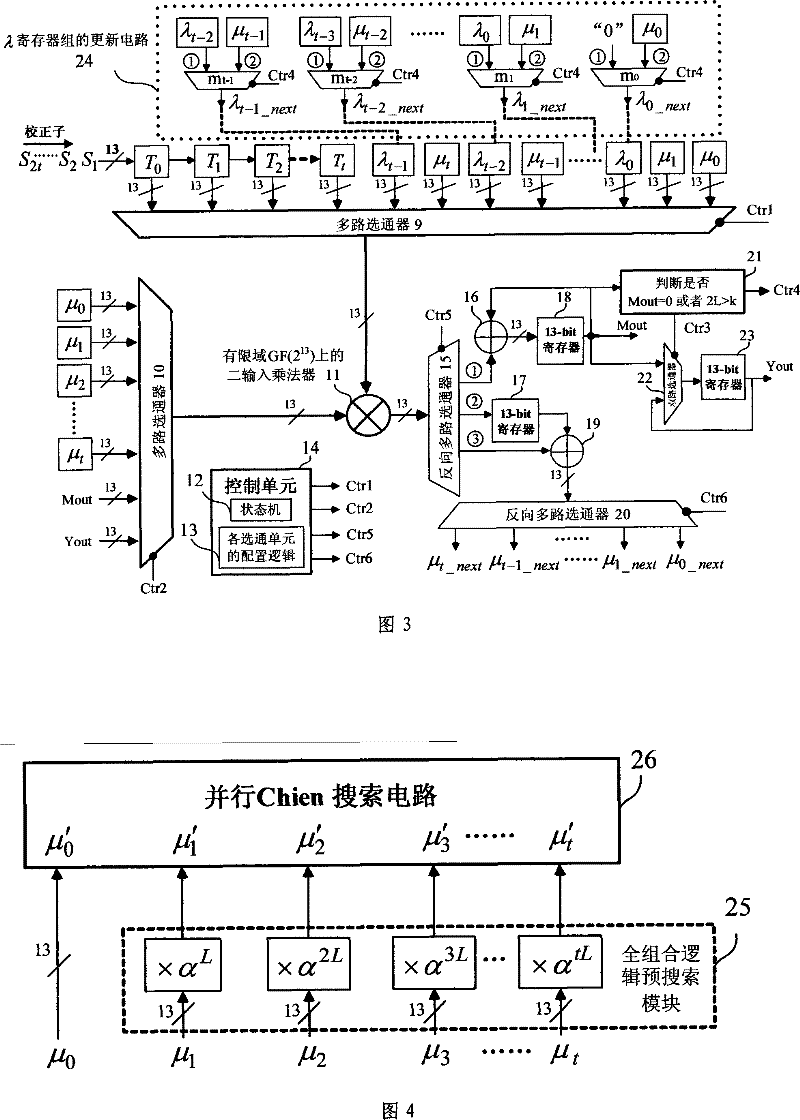

[0044] A compact BCH parallel decoding circuit supporting pre-search, such as Figure 1 to Figure 5 As shown, working in the finite field GF(2 13 ), including an adjoint polynomial syndrome operation circuit 1, an error position polynomial iterative circuit 2 and an error address search circuit 3; Passers 4-1 to 4-8 complete the finite field constant coefficient multiplication of the input; the iterative circuit 2 realizes two sets of multiplexers 9 and 10 of the circuit by means of a round of IBM iterative operations, and multiplexes a finite Domain GF(2 13 ) on the two input multipliers 11, when realizing the IBM iterative algorithm, run a round of iterative multi-beat operation; in the wrong address search circuit 3, a full combinatorial logic pre-search module 25 is set; the BCH parallel decoding circuit It is an 8-bit parallel decoding circuit.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More