Temperature-insensitive clock buffer and H-shaped clock tree circuit

A clock buffer, sensitive technology, used in the field of circuits, can solve the problem of consumption, multi-routing resources, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

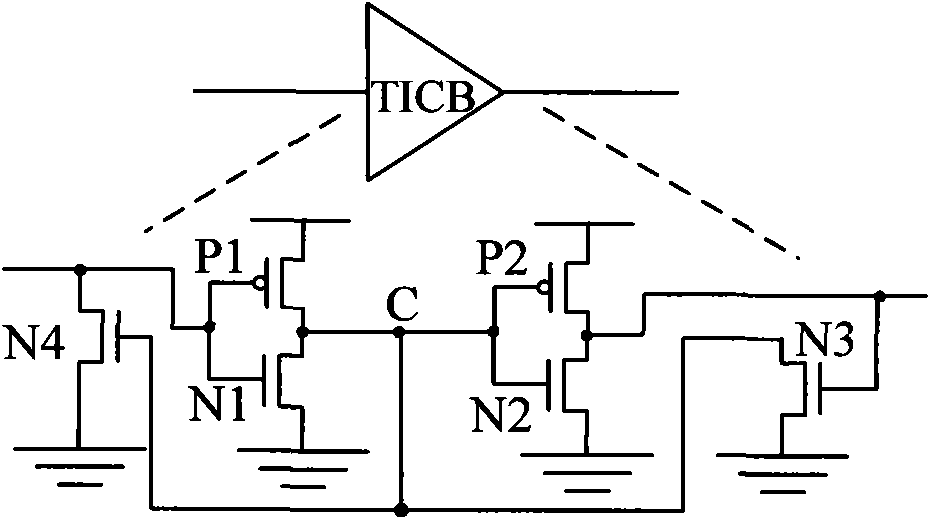

[0068] Embodiment 1. A temperature insensitive clock buffer (TICB), such as figure 1 shown, including:

[0069] The first and second inverters, the first NMOS transistor N4, and the second NMOS transistor N3;

[0070] The output end of the first inverter is connected to the input end of the second inverter; the input end of the first inverter is used as the input end of TICB, and the output end of the second inverter is used as the input end of TICB output terminal;

[0071] The drain of the first NMOS transistor N4 is connected to the input terminal of the first inverter, the gate is connected to the output terminal of the first inverter, and the source is connected to a low level;

[0072] The drain of the second NMOS transistor N3 is connected to the input terminal of the second inverter, the gate is connected to the output terminal of the second inverter, and the source is connected to a low level.

[0073] In this embodiment, the first inverter specifically includes: ...

Embodiment 2

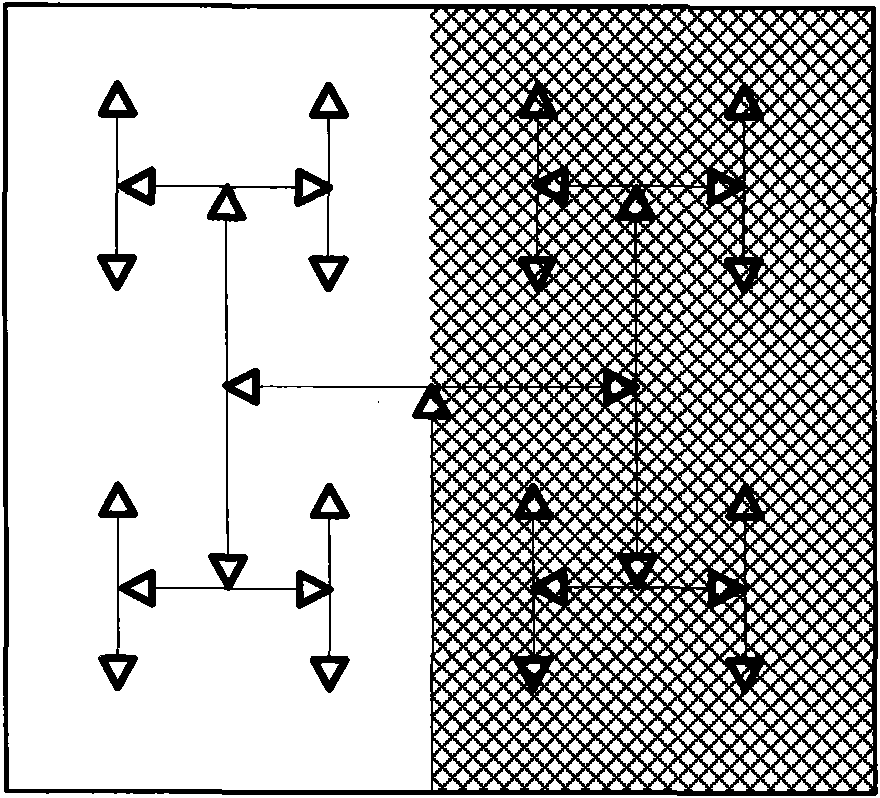

[0096] Embodiment 2, an H-shaped clock tree circuit, comprising:

[0097] Multiple TICBs in Embodiment 1; one of the TICBs is used as the root node of the H-shaped clock tree circuit, and the input end of the TICB is used as the input end of the H-shaped clock tree circuit. Starting from the TICB, each TICB The output end is connected to the input ends of the other two TICBs to form an H tree circuit.

[0098] That is, the TICBs at all levels in the clock tree are connected back and forth, and each level of TICBs drives the loads of two TICBs at the next level to achieve a balanced clock structure.

[0099] Due to the special structure of the TICB in the first embodiment, its delay hardly changes with temperature, so the clock skew caused by uneven temperature distribution inside the chip can be reduced.

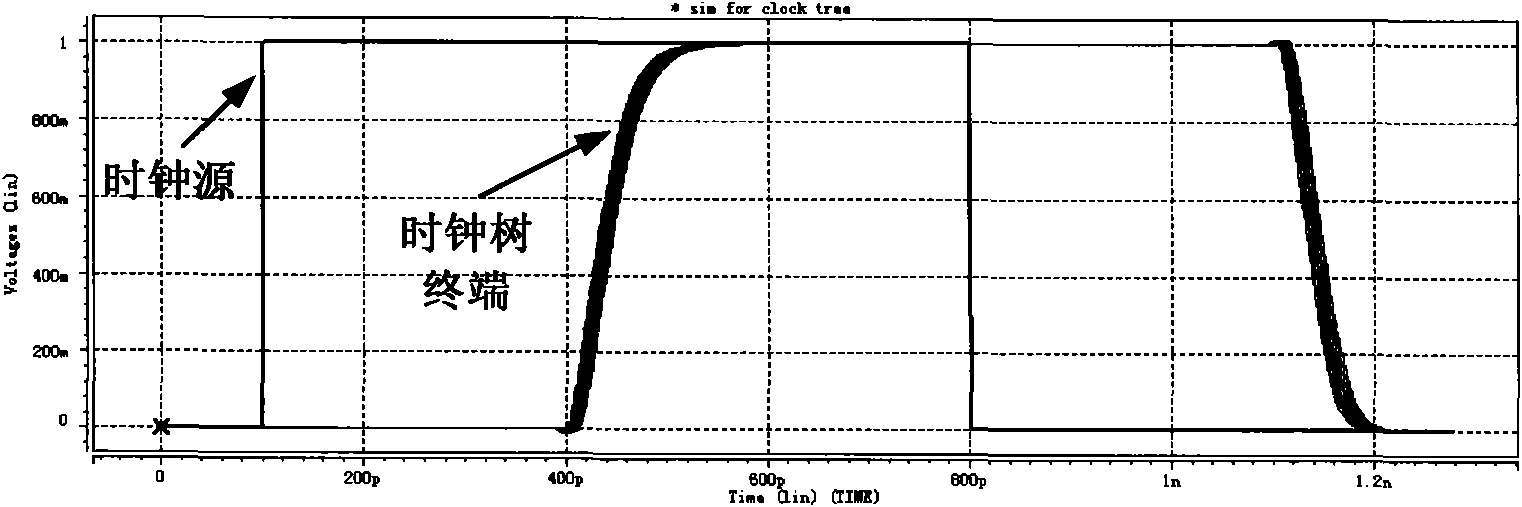

[0100]In order to realize that the signal transmission delay on the clock tree is independent of temperature: when designing the TICB buffer, considering that the typical f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More