Exception handling method and structure tolerant of missing cache and capable of emptying assembly line quickly

An exception handling and pipeline technology, applied in the direction of responding to errors, machine execution devices, etc., to achieve the effects of improving real-time processing capabilities, simple control structure, and eliminating pipeline stalls

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

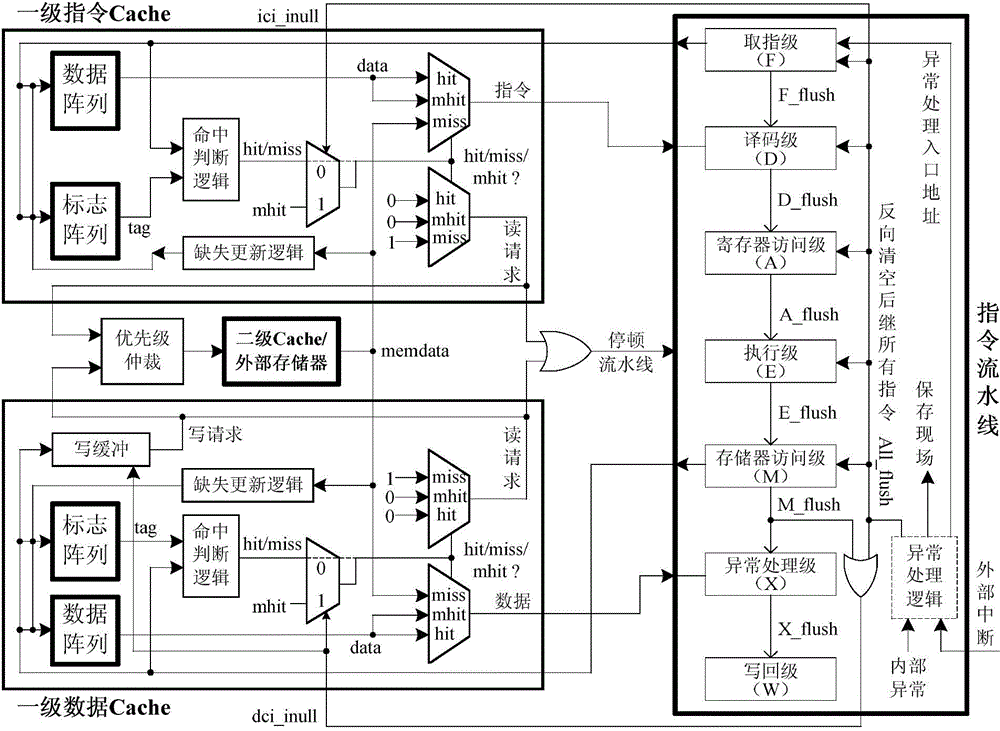

[0028] The present invention mainly includes the following aspects in the exception handling process:

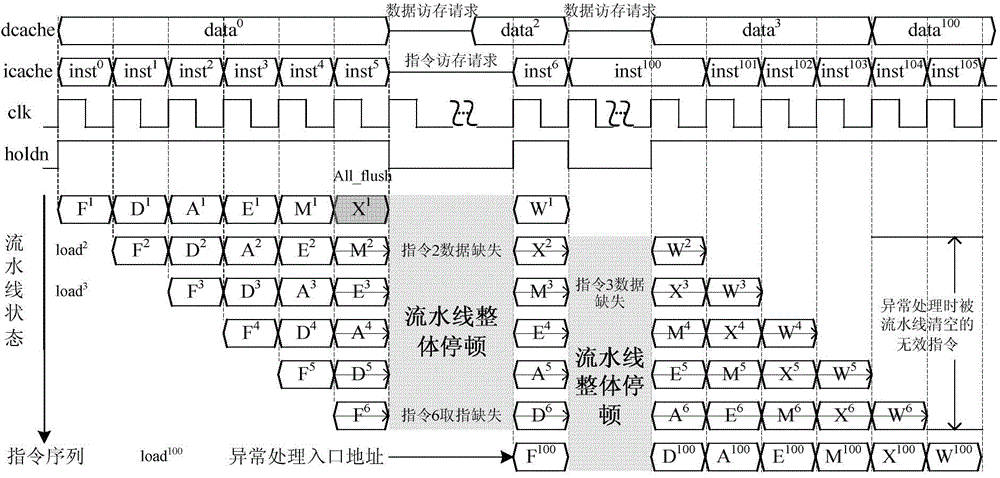

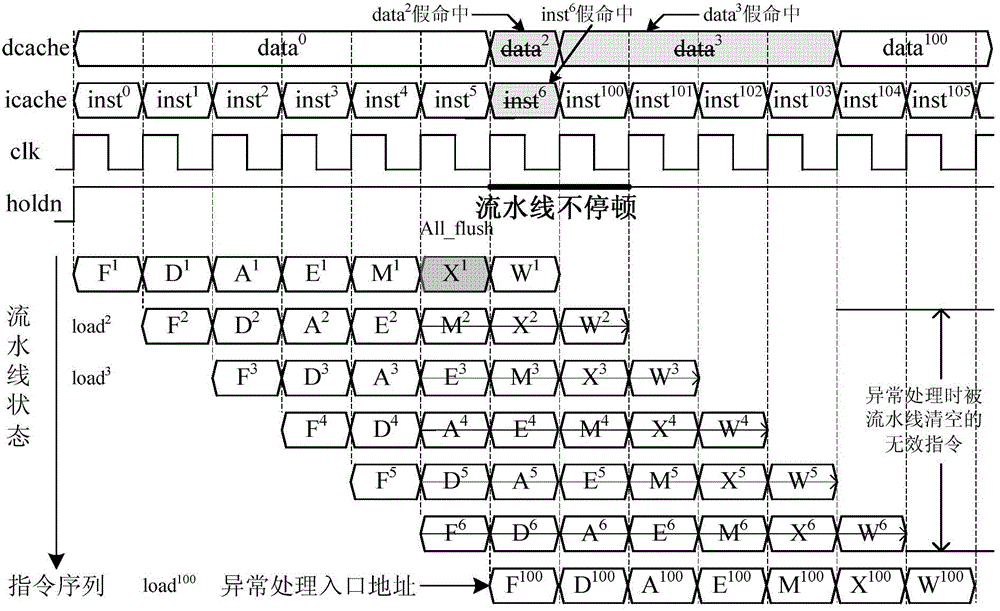

[0029] First, modify the hit judgment logic of the cache. Under normal circumstances, the access results of the cache will only be in two mutually exclusive states, that is, the "hit" state or the "missing" state. We specifically define a "false hit" state for the process of clearing the pipeline during exception handling. It is used to identify the access results of those invalid instructions that are flushed by the pipeline to the cache.

[0030] Second, define the behavior of the cache in the "false hit" state. Since the invalid instructions in the pipeline cannot update any state information of the processor in the end, the instructions obtained by them accessing the cache will not be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More