System on chip and memory access management method thereof

A system-level chip and management method technology, applied in the field of system-level chip and its memory access management, can solve the problems of lack of memory sharing, high power consumption, and increased SOC power consumption, so as to improve software fault tolerance and application flexibility performance, reducing area overhead, and reducing power consumption overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

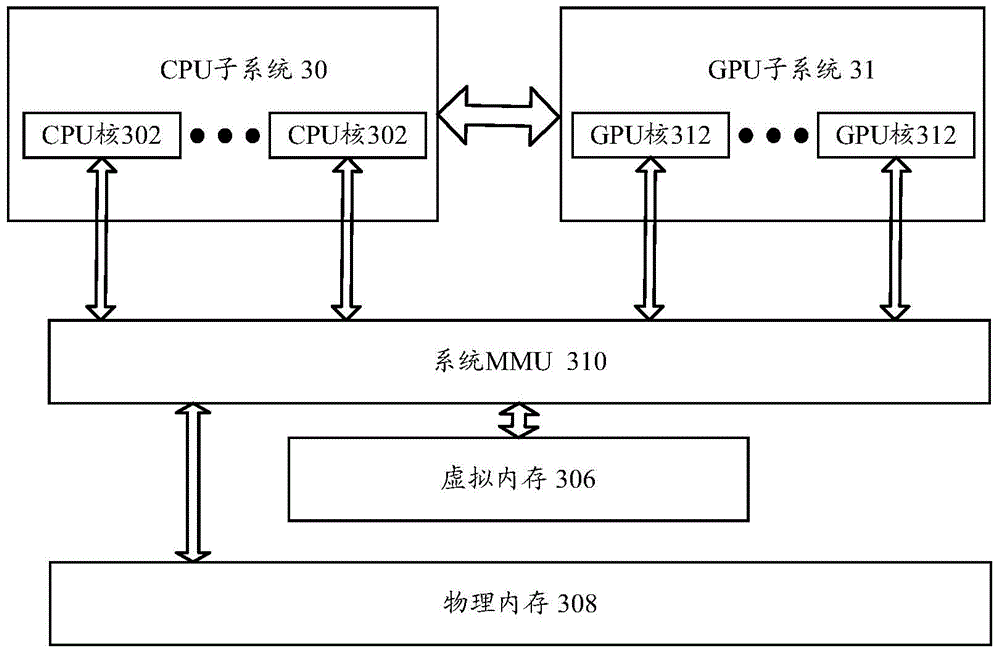

[0030] The specific implementation manners of the system-on-a-chip and the memory access management method provided by the embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

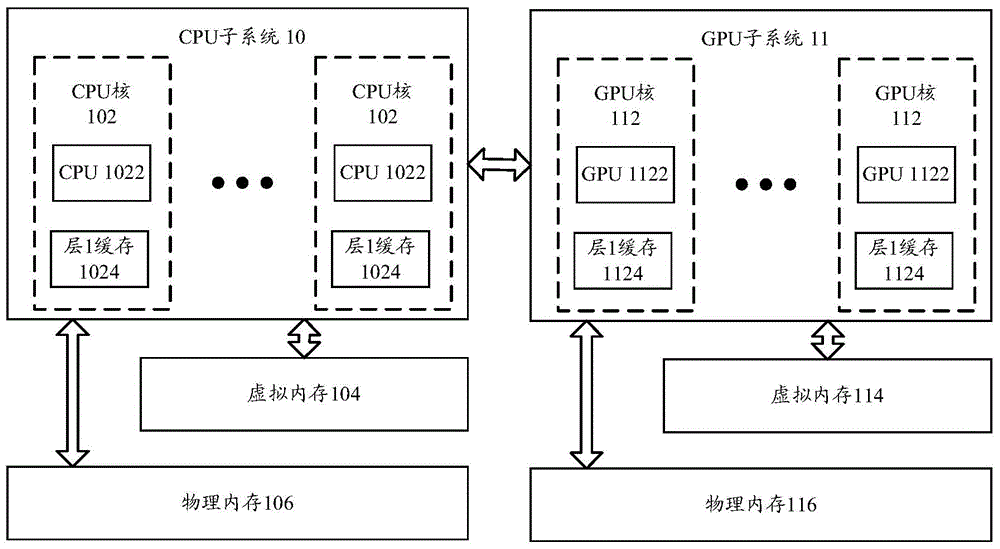

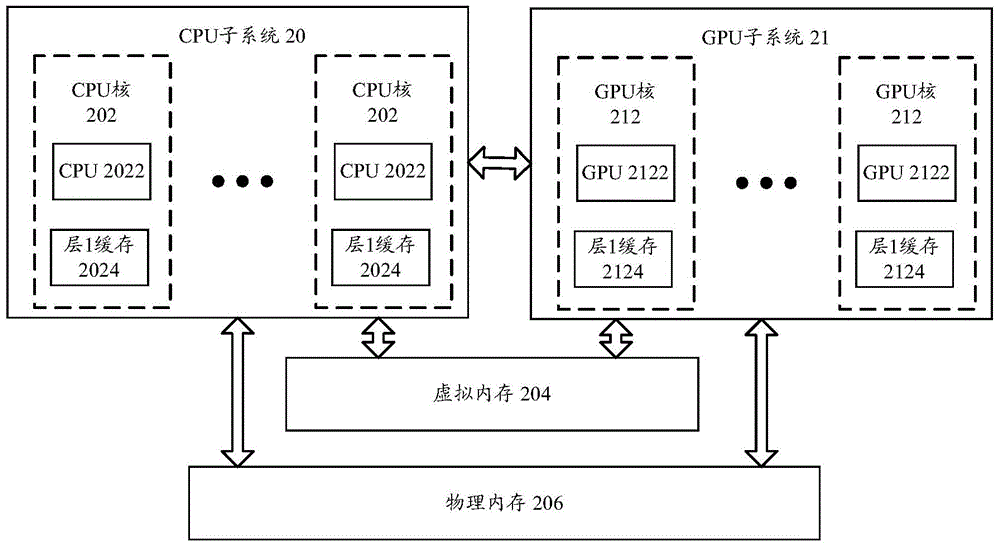

[0031] Due to the relatively large area of the CPU storage subsystem and the GPU storage subsystem, when the SOC provided by the embodiment of the present invention is described below in conjunction with the accompanying drawings, the processor subsystem included in the SOC takes the CPU subsystem and the GPU subsystem as examples. Of course, The SOC provided by the embodiment of the present invention may also include other types of processor subsystems.

[0032] A system-on-a-chip provided by an embodiment of the present invention, such as figure 2 As shown, including: multiple processor subsystems and shared memory shared between multiple processor subsystems, the multiple processor subsystems include such as figure 2 Shown in the CP...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More