Highly reliable network server system on chip and design method thereof

A network-on-chip and design method technology, applied in transmission systems, digital transmission systems, data exchange networks, etc., can solve problems such as exceeding the clock cycle, increase delay, errors, etc., achieve reliable data transmission, reduce area and power consumption overhead Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

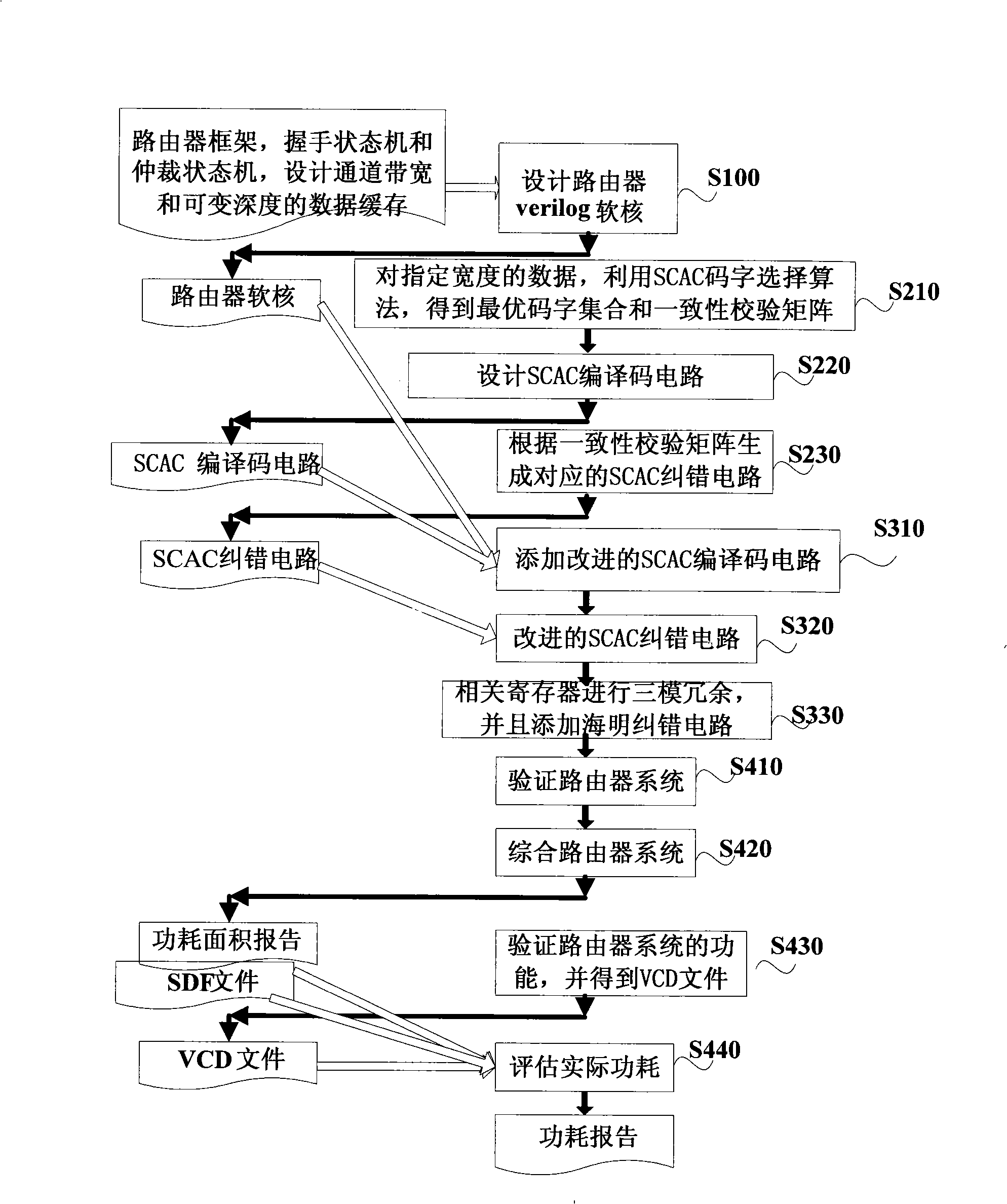

[0087] In order to make the object, technical solution and advantages of the present invention clearer, a highly reliable network-on-chip router system and its design method of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

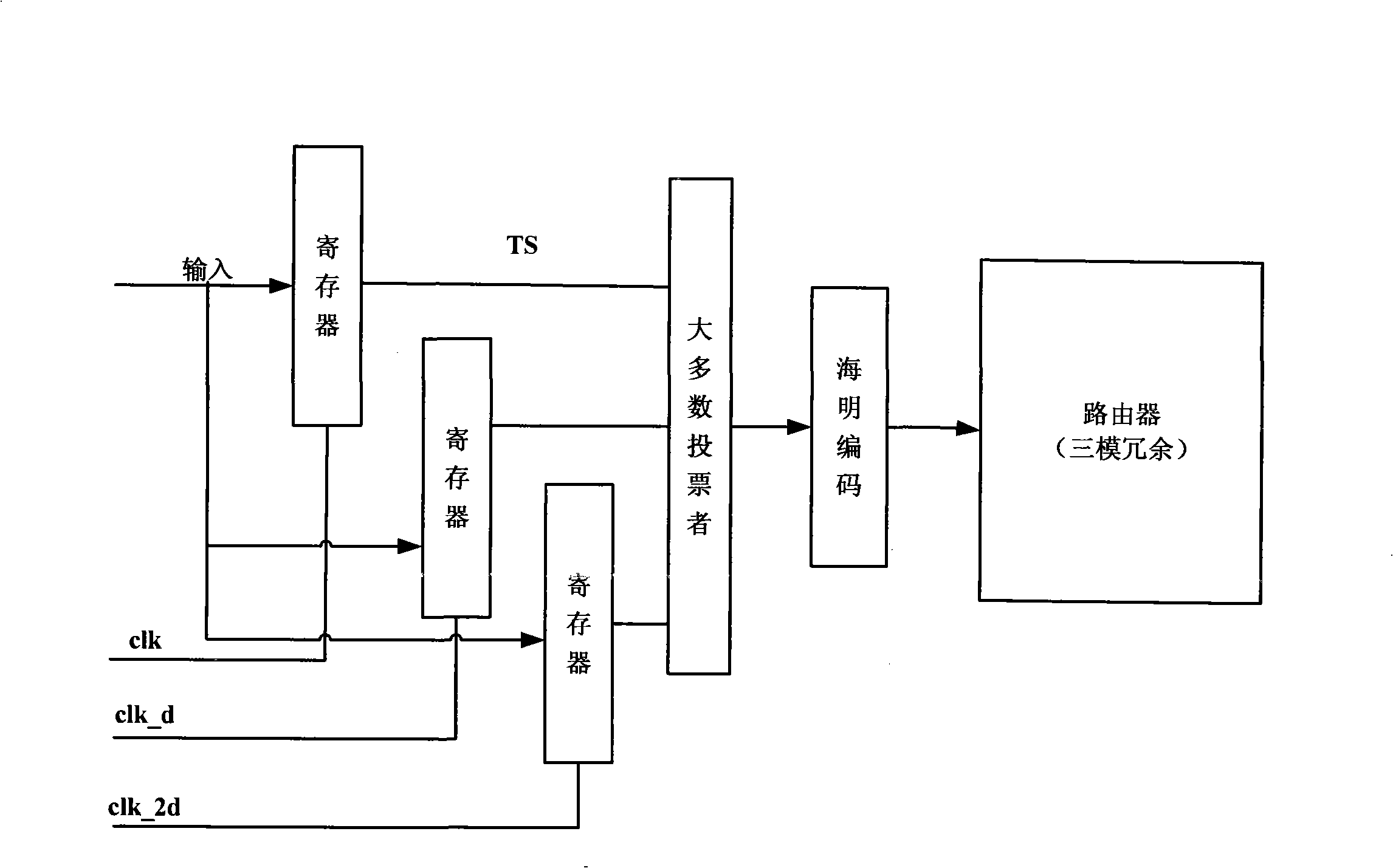

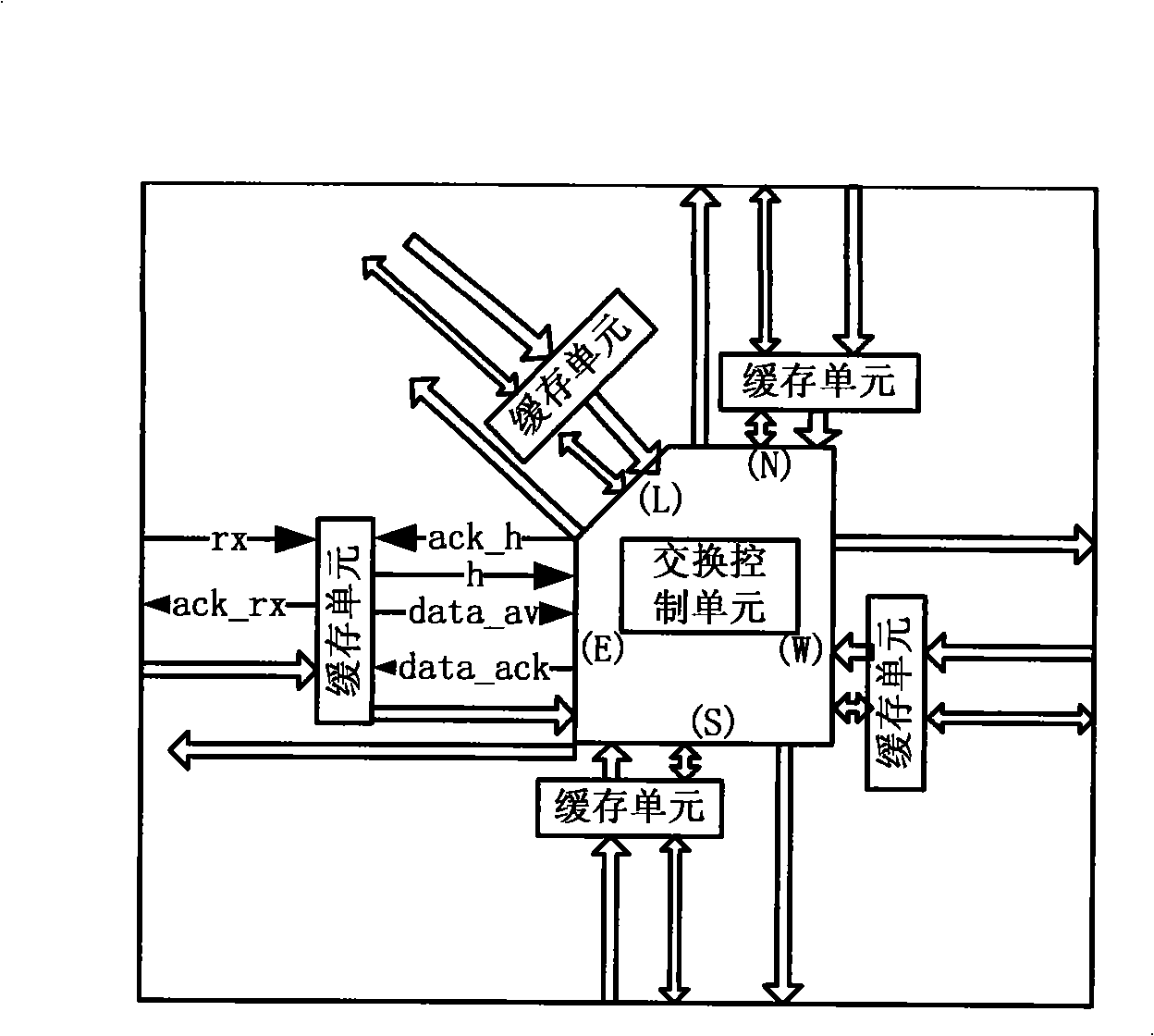

[0088] The present invention is a highly reliable network-on-chip (Network-On-Chip, NOC) router (Router) system based on Selected Crosstalk Avoidance Code (SCAC)-Triple Modular Redundancy (TMR) scheme and Its design method includes the soft core of the network-on-chip router for packet transmission, SCAC encoding circuit, SCAC decoding circuit and SCAC error correction circuit, as well as the fault-tolerant scheme and evaluation unit of the high-reliability router system to ensure that the network-on-chip can transmit data reli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More