Network-on-chip oriented low delay router structure

An on-chip network and router technology, applied in the field of on-chip router structure, can solve the problems of insufficient utilization of storage resources, large delay in forwarding packets, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

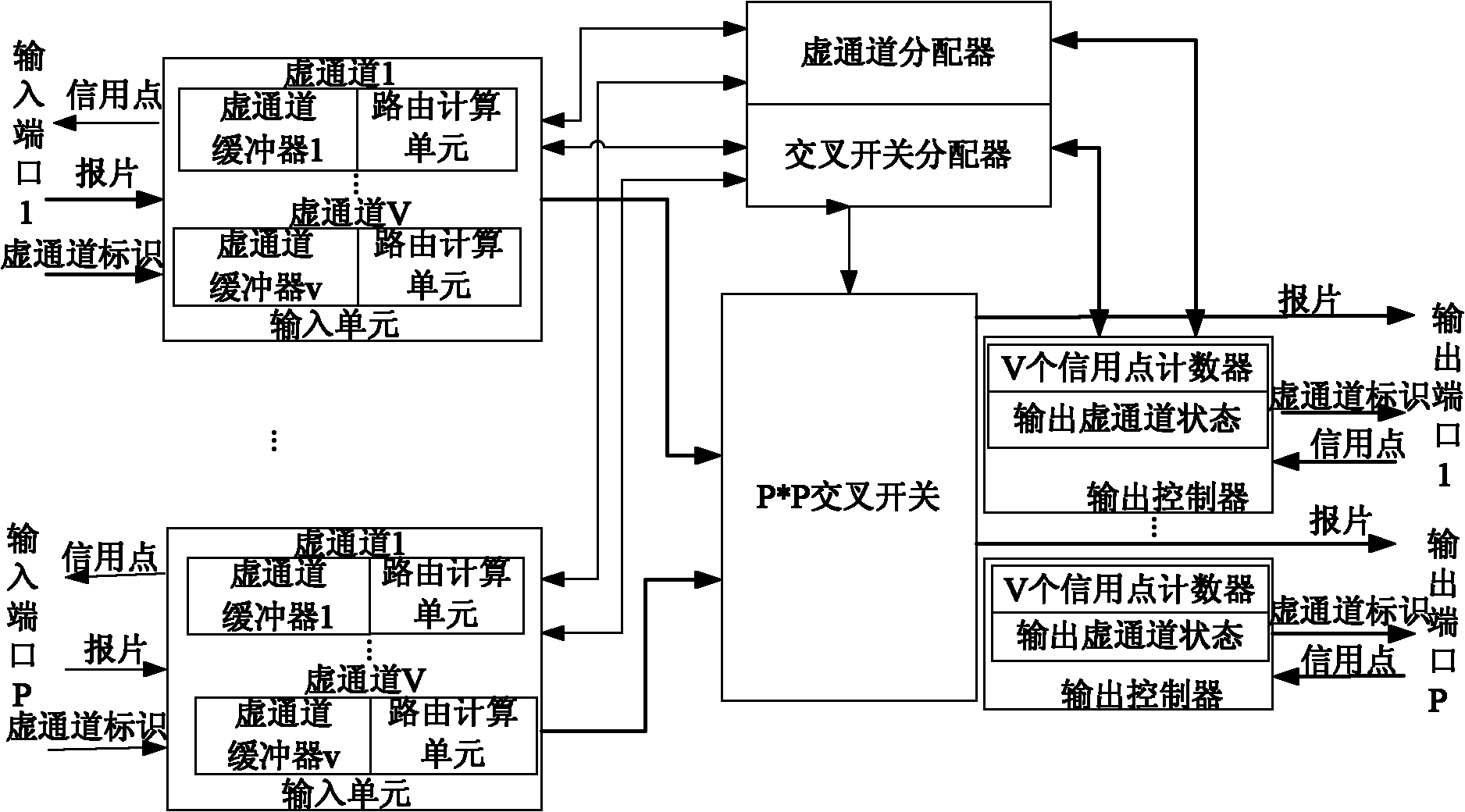

[0039] figure 1 It is a block diagram of the overall structure of a traditional virtual channel router. It consists of P input units, a virtual channel distributor, a crossbar distributor, a crossbar and P output controllers. Each input unit receives fragments and virtual channel identifiers from the upstream router, and returns credits to the upstream router. Each input unit writes the received fragment into the virtual channel specified by the virtual channel identifier. The virtual channel of each input unit sends a request signal for applying for an output virtual channel to the virtual channel allocator, and also sends a request signal for applying for an output port to the crossbar allocator. The input unit also sends the message to the crossbar. The virtual channel allocator receives the request of the virtual channel in the input unit, outputs the status of the output virtual channel in the controller, completes the virtual channel allocation operation, and returns ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More