Testability design method for embedded IP of FPGA

A design method and testing technology, applied in CAD circuit design, special data processing applications, etc., can solve problems such as the reduction of DFT coverage, and achieve the effect of improving DFT test coverage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

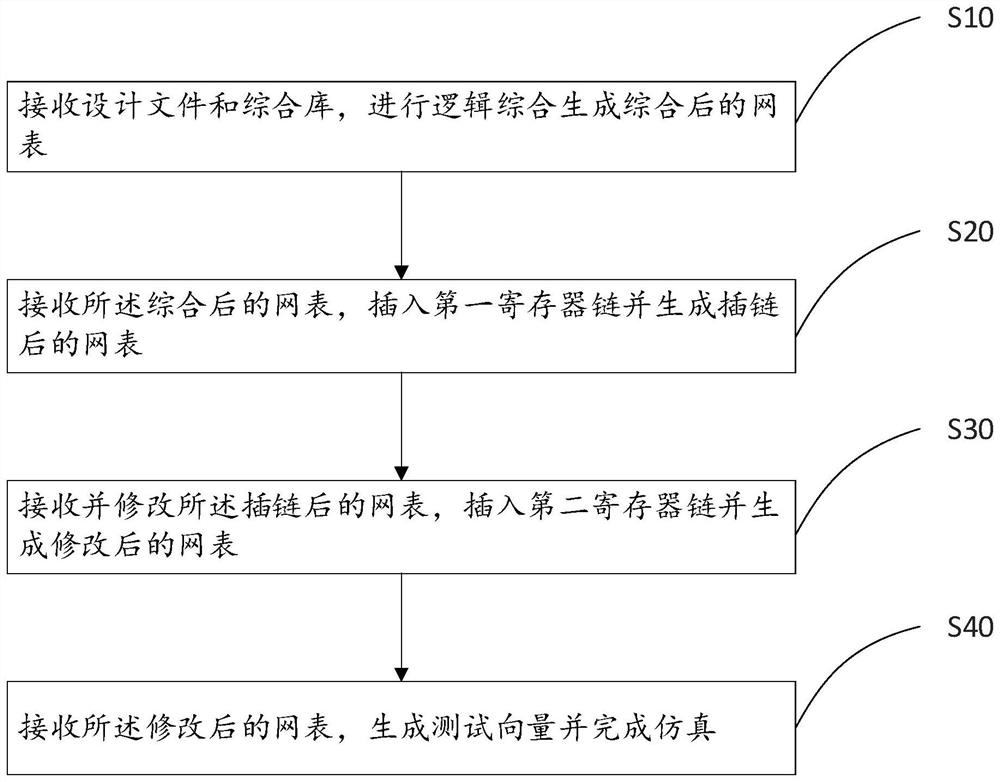

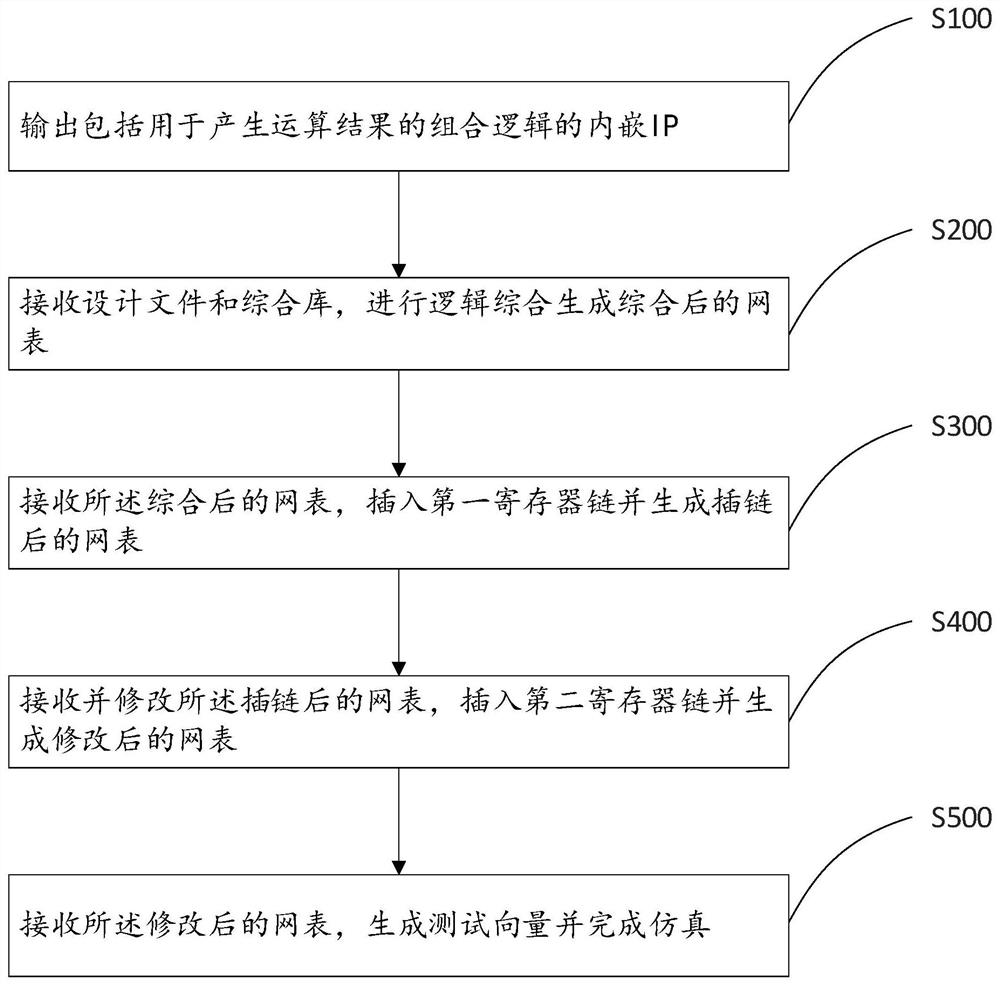

[0020]In order to make this specification, the technical solutions and advantages will be described in conjunction with the specific embodiments and corresponding drawings of the present specification and the corresponding drawings. Obviously, the described embodiments are merely the embodiments of the present specification, not all of the embodiments. Based on the embodiments in this specification, one of ordinary skill in the art does not have all other embodiments obtained without creative labor, all of which are protected by this specification. It should be noted that the features in the embodiments and embodiments in the present application may be combined with each other in the case of an unable conflict.

[0021]The description and claims of the invention and the terms "first", "second" and "third", and the like in the above drawings are for distinguishing different objects rather than to describe a particular order. Moreover, the terms "include" and any variation, intending to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More