Digital logic chip and method capable of testing design

A technology of digital logic and test design, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of not being able to observe N signals, not being able to directly observe, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

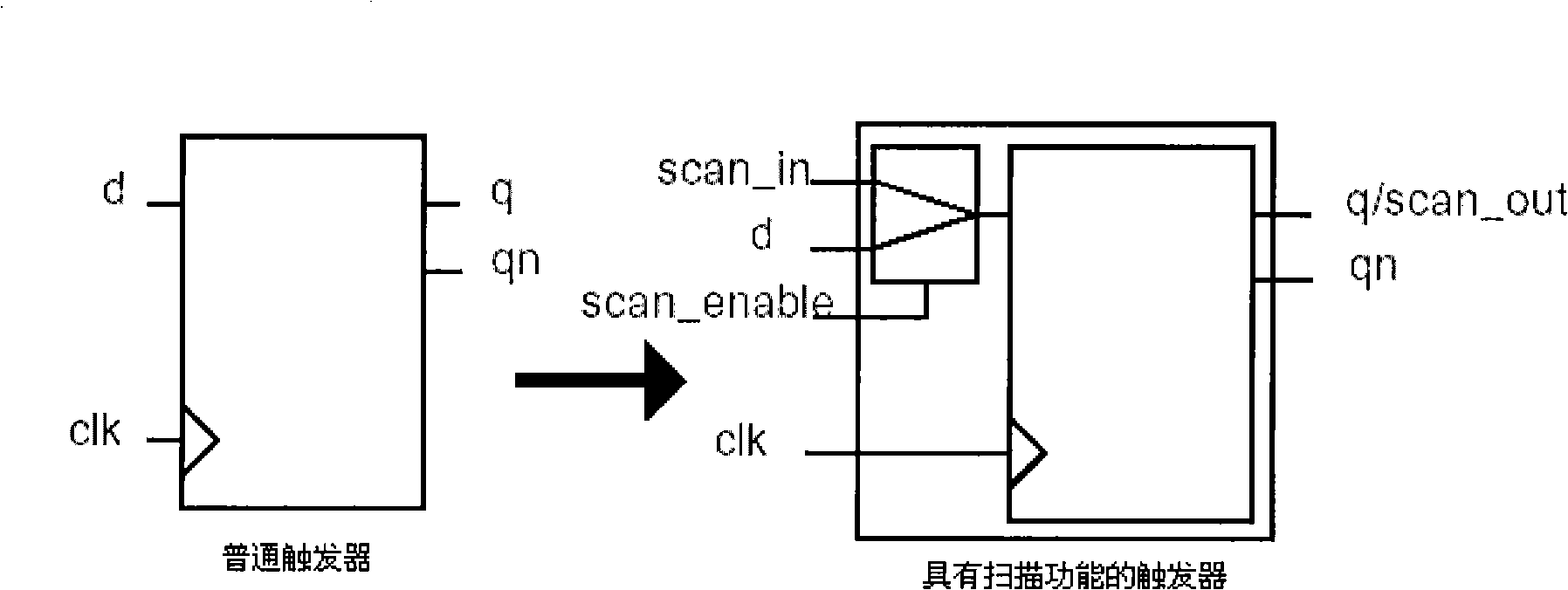

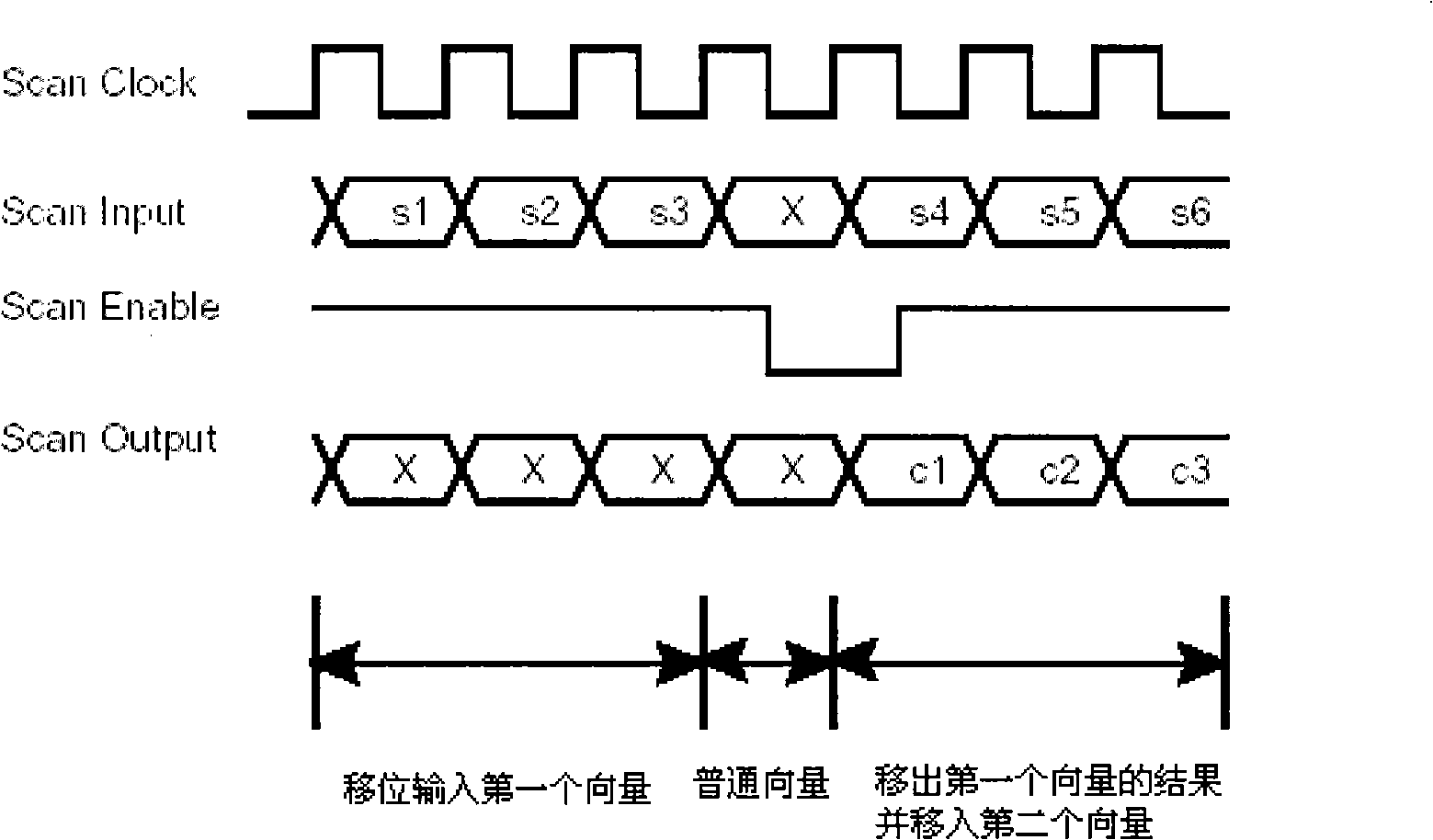

Method used

Image

Examples

Embodiment Construction

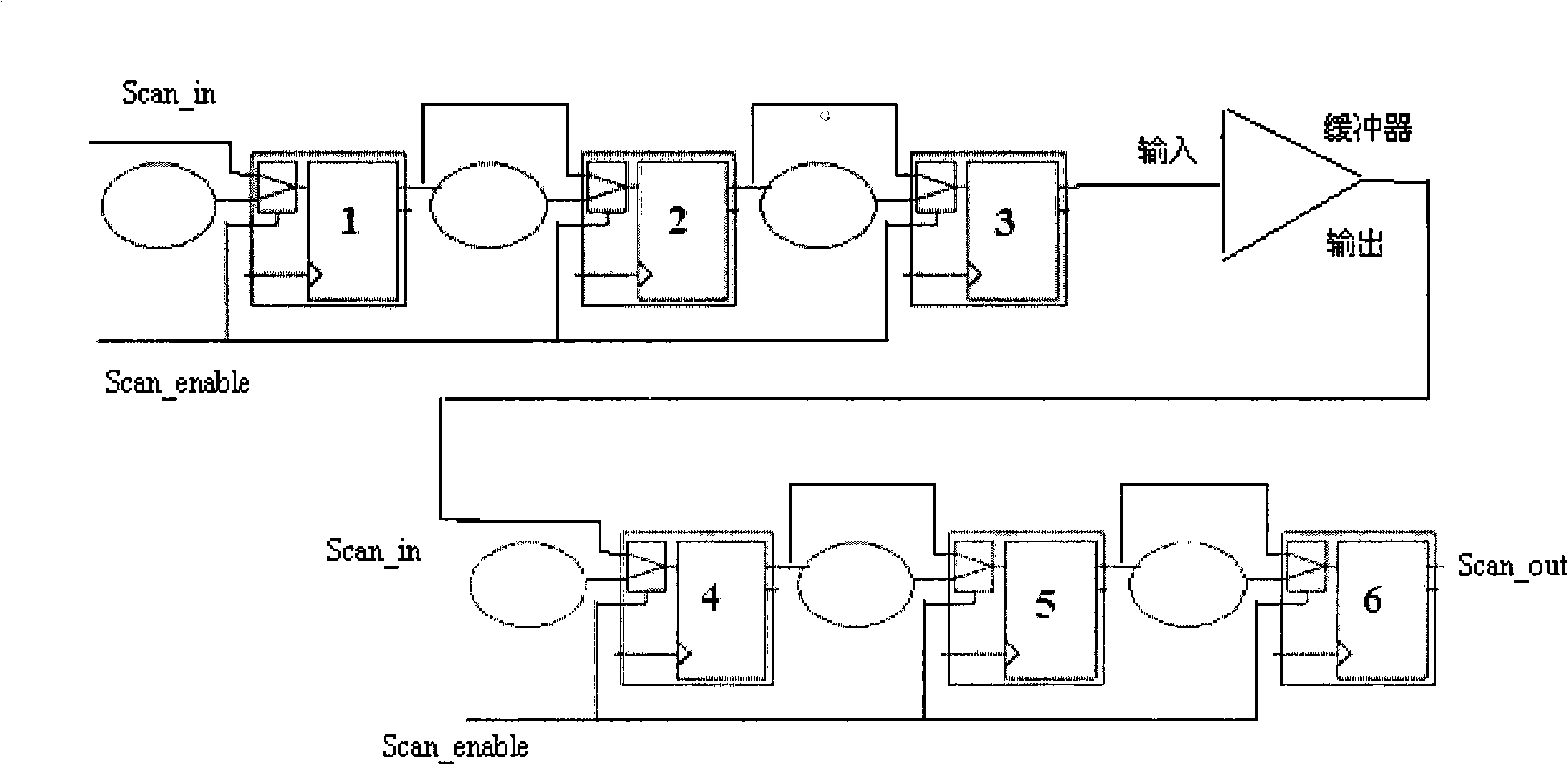

[0033] Hereinafter, the digital logic chip and its testable design method of the present invention will be described in detail with reference to the accompanying drawings.

[0034] Such as Figure 5 Shown, be the method flow chart of digital logic chip testable design of the present invention, this method comprises the following steps:

[0035] Corresponding logic devices are arranged between each scan flip-flop and the observation pin in the digital logic chip;

[0036] Observing the signals of each scan flip-flop in time division through the observation pin;

[0037] After the signal passes through the above-mentioned logic device, it is judged whether the observation result is consistent with the predetermined observation result; if it is consistent, it is considered that the digital logic chip is normal; if it is inconsistent, it is considered that the digital logic chip is abnormal.

[0038] Such as Figure 6 As shown in , it is a schematic diagram of using a pin pin f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More