Embedded test method of phase-locked loop circuits

A test method and phase-locked loop technology, applied in the direction of electronic circuit testing, measuring electricity, measuring devices, etc., can solve problems such as occupying test resources, shorten test time, reduce test difficulty and test cost, improve fault detection rate and The effect of fault isolation rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

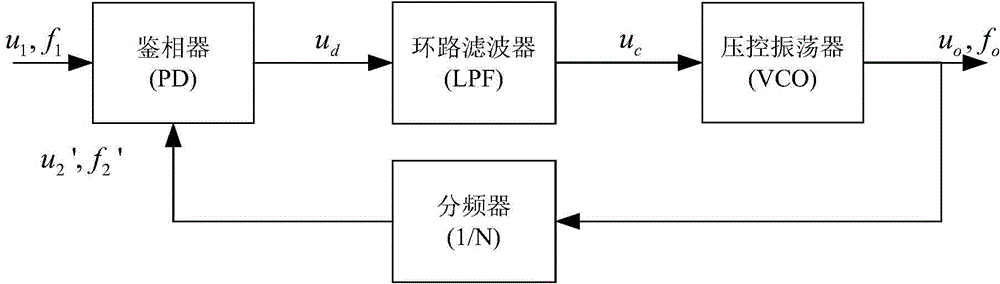

[0023] Step 1: Carry out testability design for the phase-locked loop circuit, and first determine the fault set.

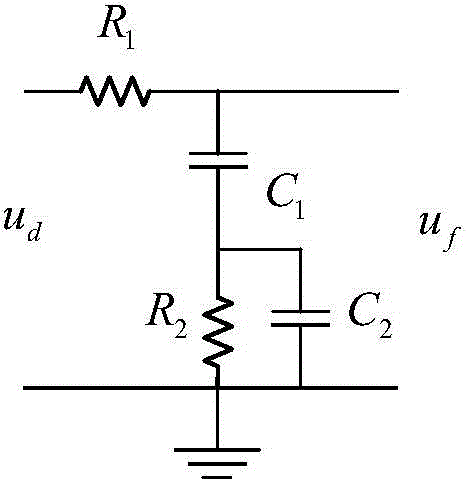

[0024] The common faults of the phase-locked loop circuit include abnormal power supply, damage to the phase detector, open circuit, short circuit and parameter failure of the resistance and capacitance elements in the filter, open circuit, short circuit and failure of the resistance and capacitance elements of the peripheral control circuit of the voltage-controlled oscillator (VCO). Parameter failure, abnormal operation of the VCO itself, and damage to the frequency divider. The failure of the above-mentioned phase-locked loop will cause some performance changes of the phase-locked loop,

[0025] When performing fault verification, it is necessary to simulate the fault phenomenon. To this end, the fault set of the phase-locked loop circuit is designed, and the measurable points of each part of the phase-locked loop are obtained by analyzing the phase-locked lo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More