Secure testability design structure of encryption chip

A technology for encrypting chips and designing structures, which is applied in the field of testable design structures, can solve problems such as large attacks, and achieve the effect of low area overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

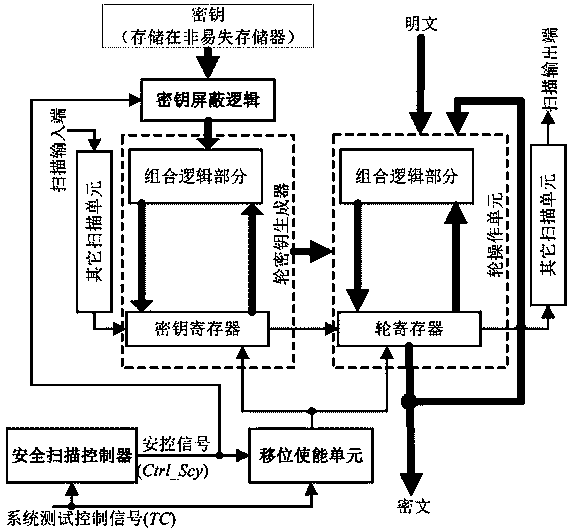

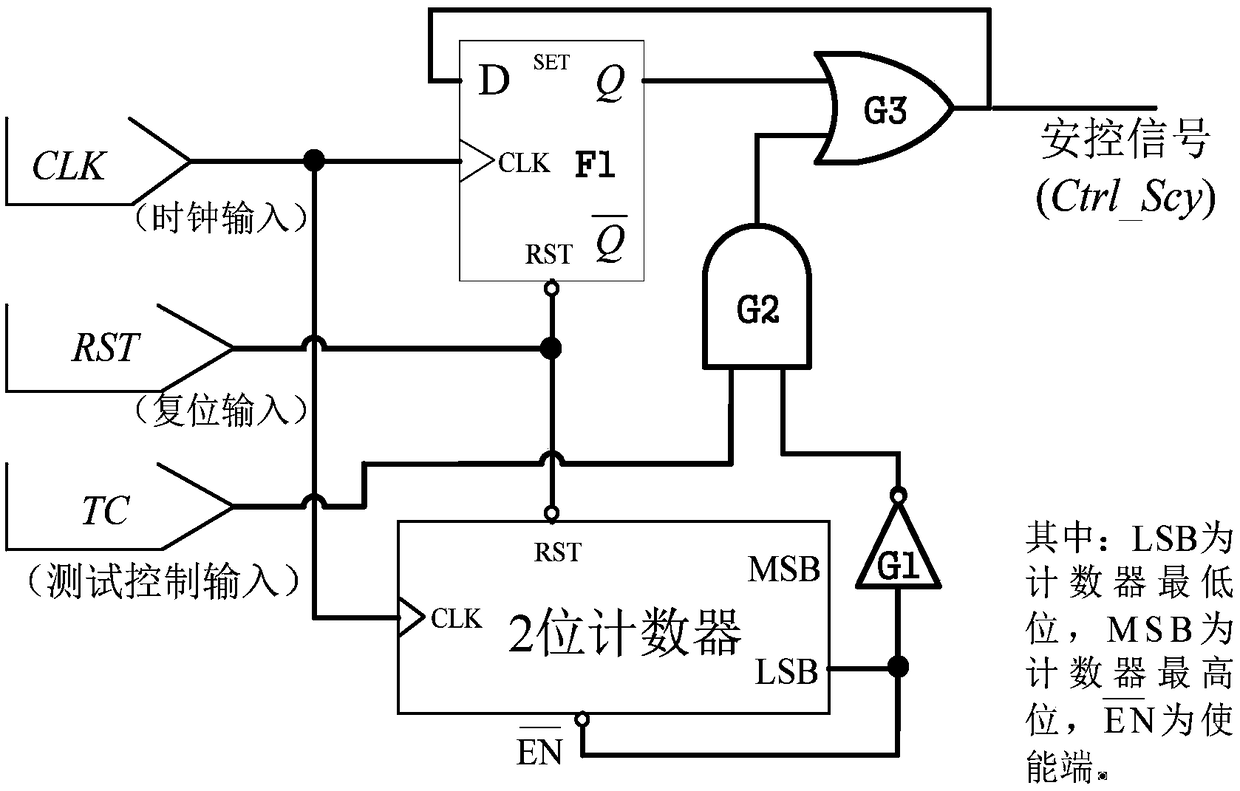

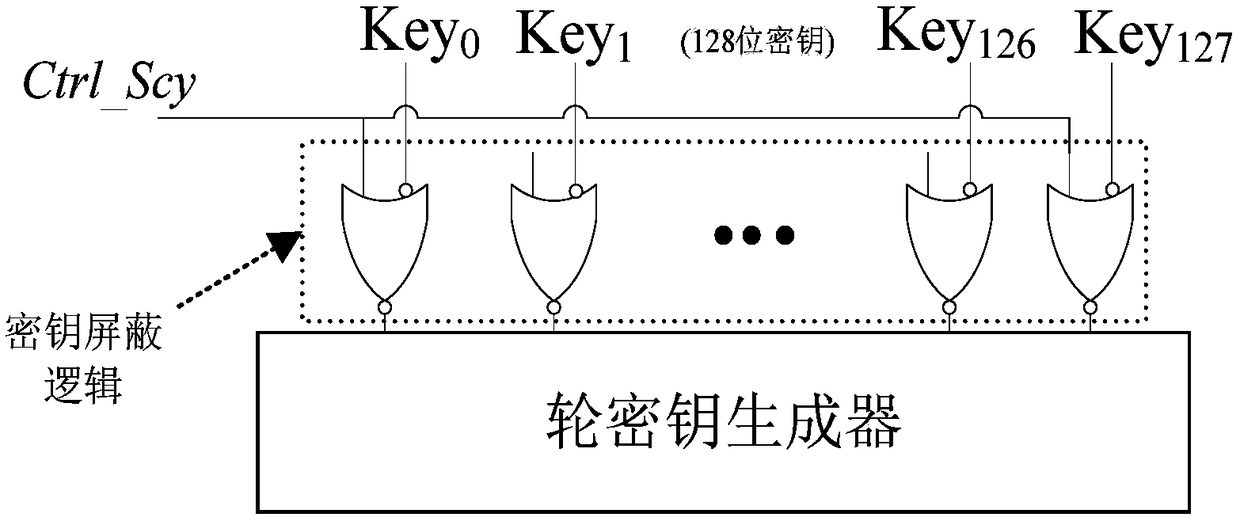

[0017] The core components of the AES encryption chip include a round operation unit and a round key generator. In the conventional scanning design, the chip key register, the wheel register in the wheel operation unit and other flip-flops are first transformed into scanning units, and then these scanning units are sequentially connected into a scanning chain. The scan chain can be used to shift in test stimuli, capture test responses, and shift out test responses under the action of test control signals. Such as figure 1 As shown, the security scanning structure of the present invention adds key...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More