Patents

Literature

665results about How to "Improve data processing capabilities" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

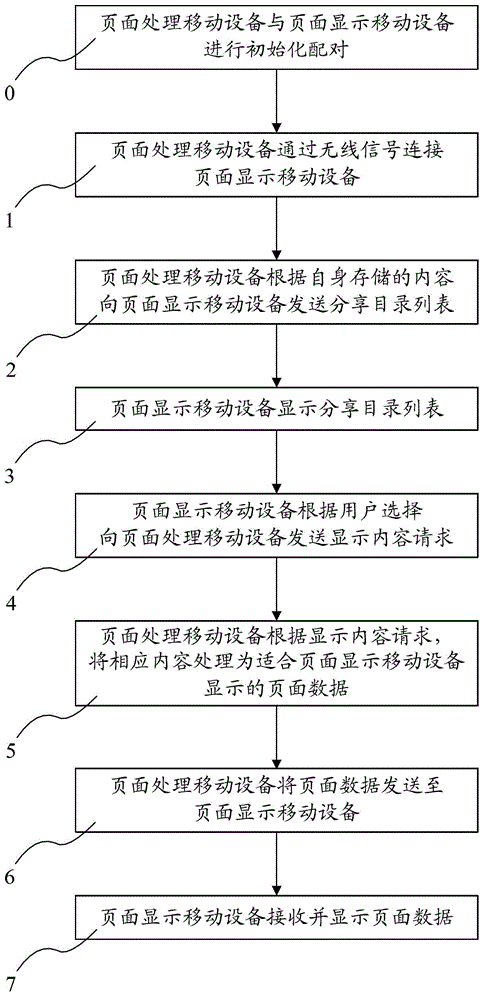

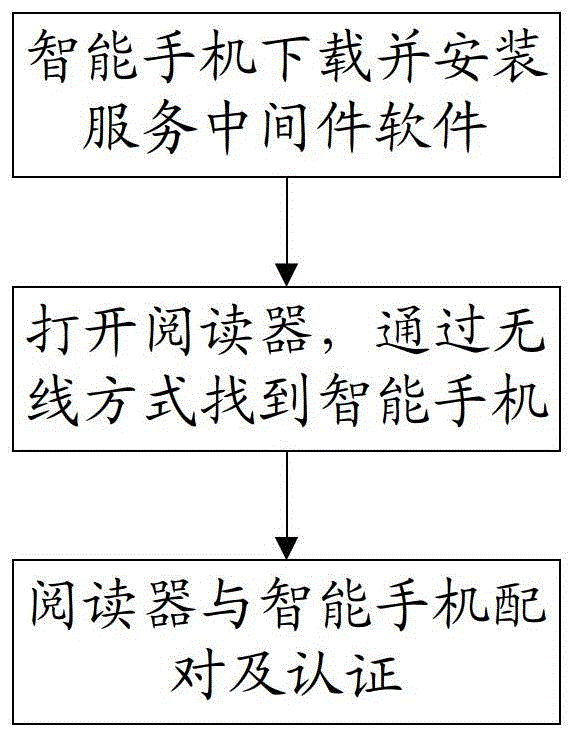

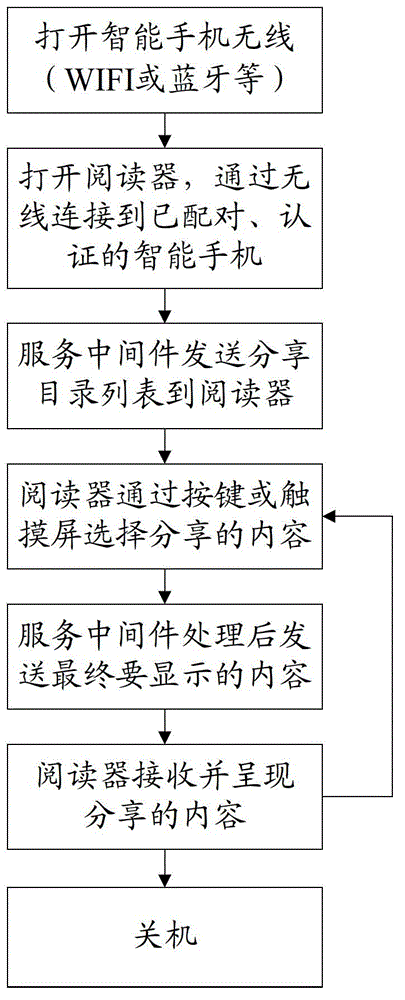

Method for achieving control of wirelessly shared and displayed pages between electronic devices

InactiveCN102750086AReduce hardware costsImprove reading experienceTransmissionInput/output processes for data processingComputer hardwareCombined use

The invention relates to a method for achieving control of wirelessly shared and displayed pages between electronic devices. In the method, a page processing electronic device is connected with a page displaying electronic device through a wireless signal, the page displaying electronic device sends a display content request to the page processing electronic device. The page processing electronic device processes corresponding contents into page data suitable for being displayed by the page displaying electronic device according to the display content request and sends the page data to the page displaying electronic device in a wireless mode to be displayed. By utilizing the method, the page processing electronic device with strong data processing capability and the page displaying electronic device with good displaying effect are combined for use, the pages are generated by utilizing the page processing electronic device and shared to the page displaying electronic device to be displayed, thereby saving the hardware cost of the page displaying electronic device and providing best reading experience for users. In addition, the method for achieving the control of the wirelessly shared and displayed pages between the electronic devices is simple in achieving mode and wide in application range.

Owner:SHANGHAI BIBANG INFORMATION TECH

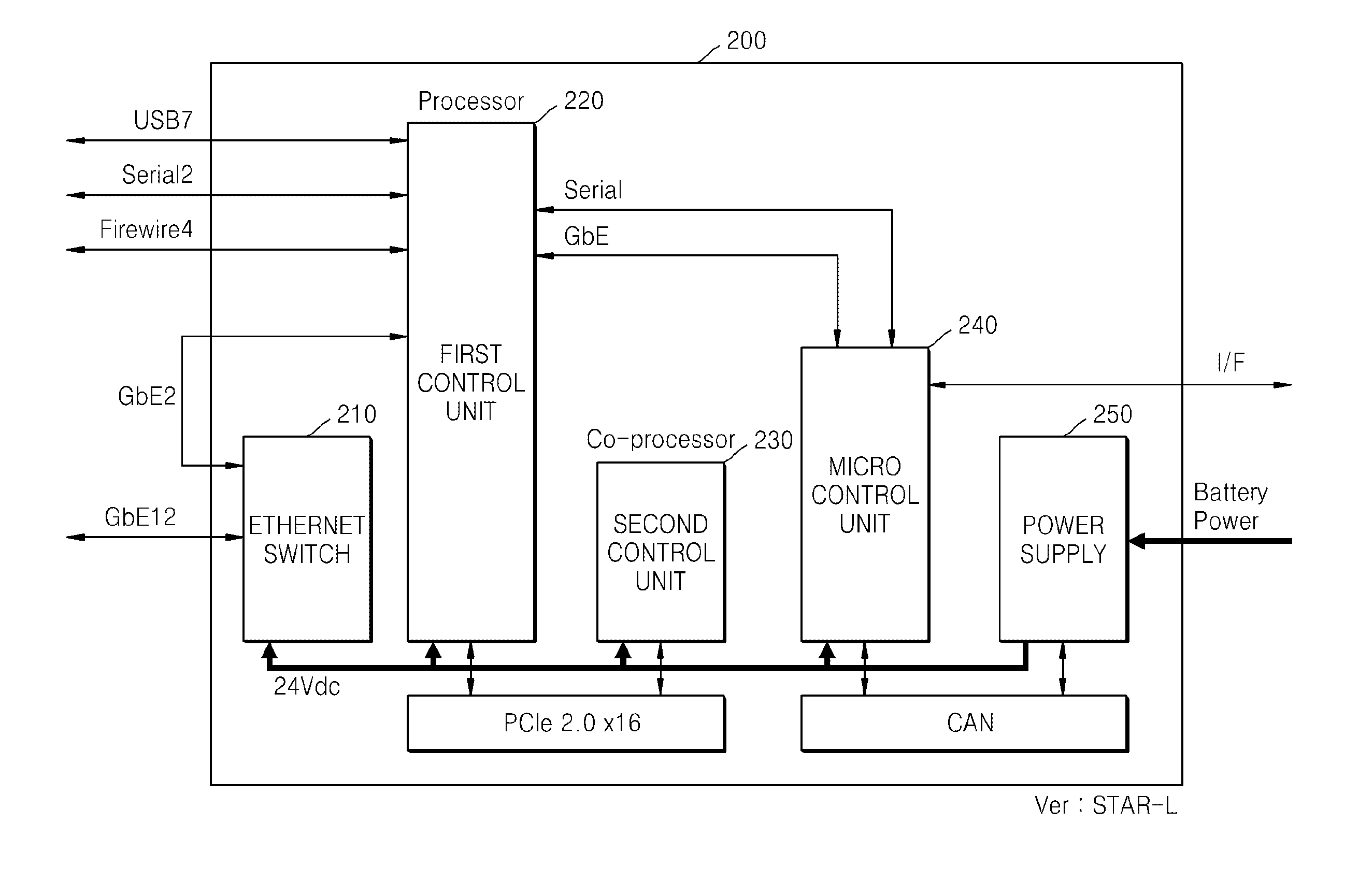

Mini integrated control device

ActiveUS20160008985A1Convenient and accurateReduce resolutionProgramme-controlled manipulatorComputer controlComputer moduleElectric power

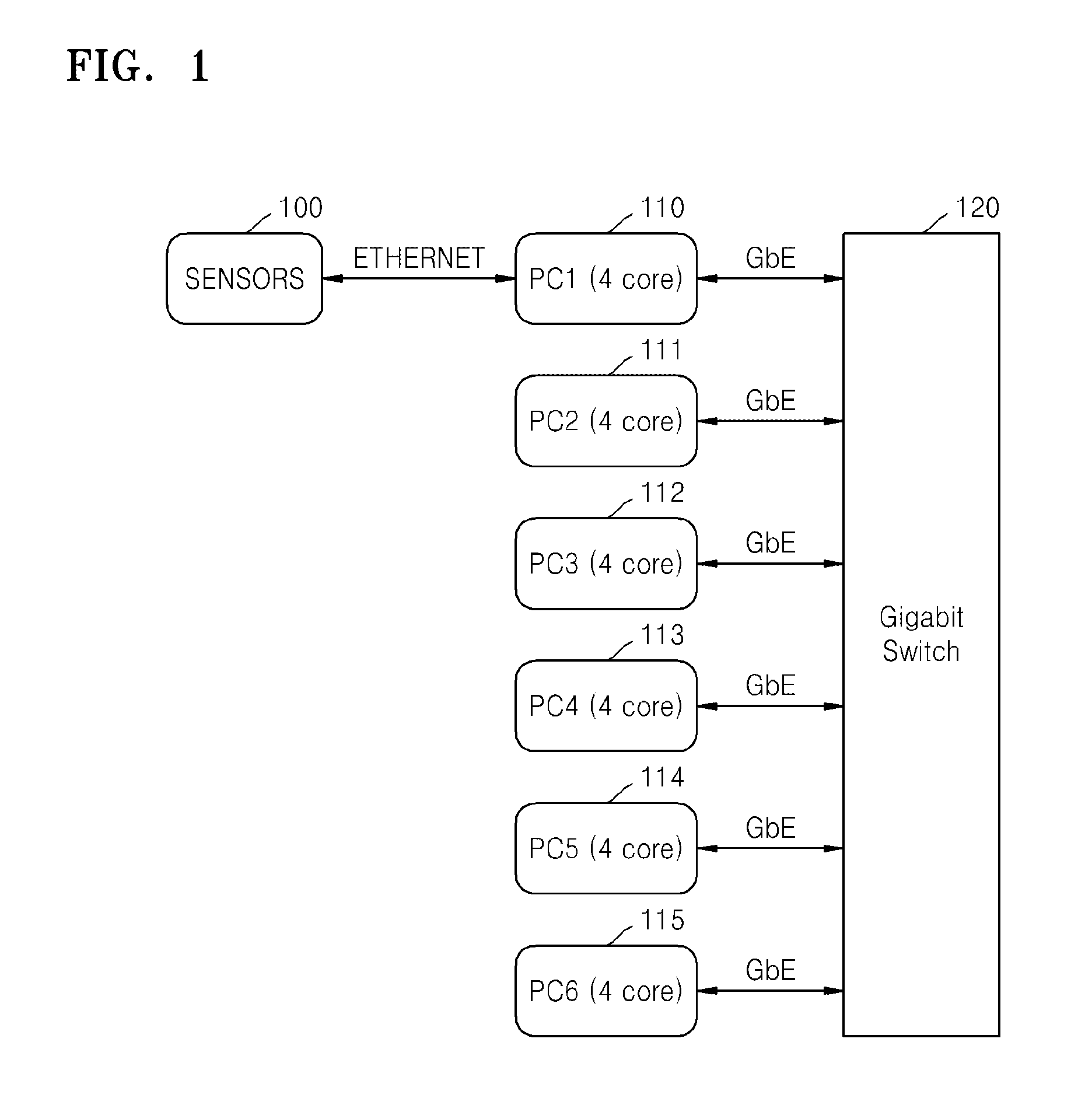

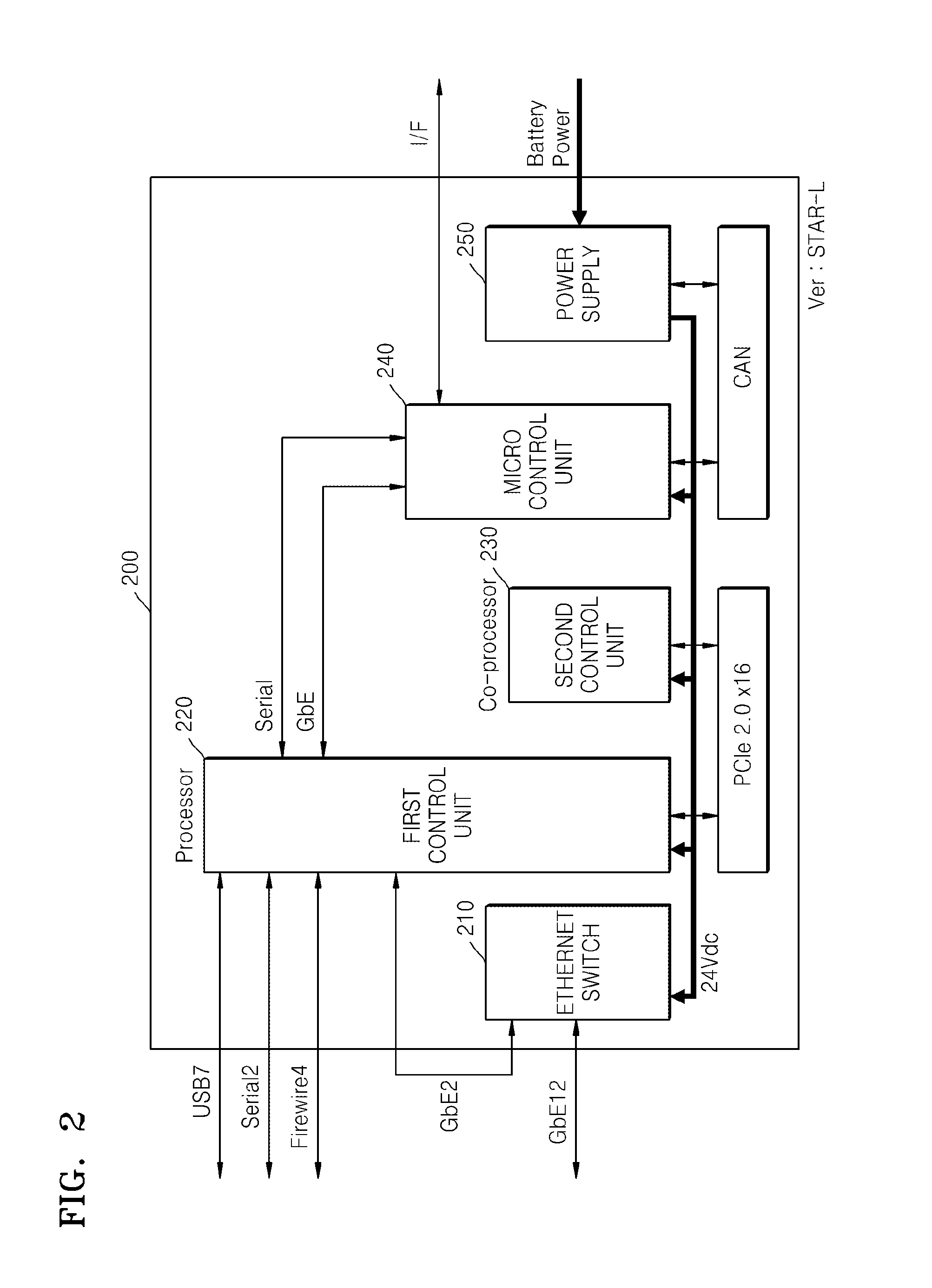

Provided is a mini integrated control device including a first control unit for receiving large-scale sensor data generated while an autonomous driving robot is operated and performing large-scale calculations in parallel, a second control unit for performing the large-scale calculations in parallel together with the first control unit, a micro control unit for monitoring a state of power of the robot, monitoring obstacles located near the robot, controlling a motor of the robot, controlling a relay module of the robot, and communicating with the first control unit, and a power supply for controlling supply of power.

Owner:HANWHA AEROSPACE CO LTD

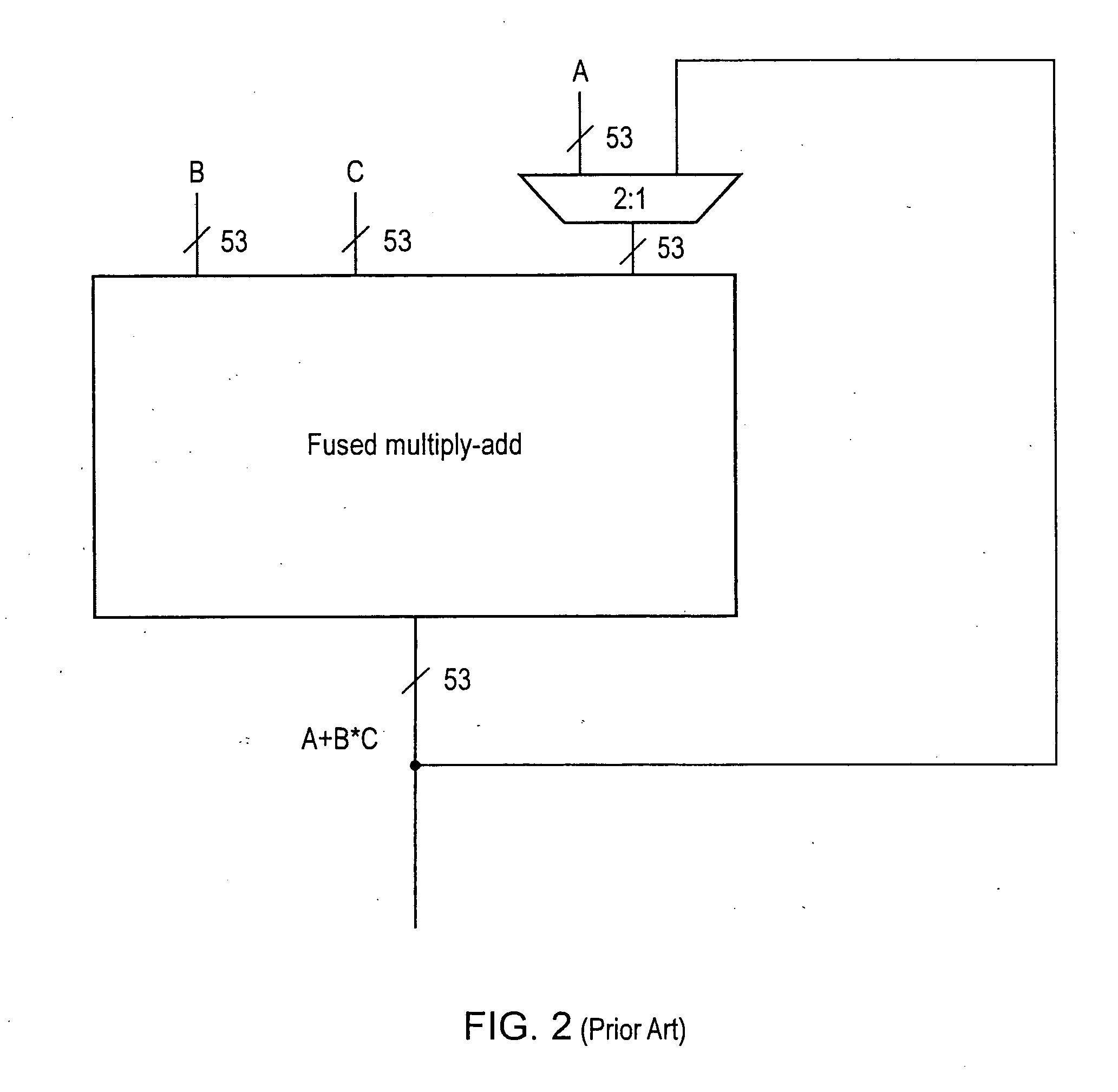

Apparatus and method for performing fused multiply add floating point operation

ActiveUS20110072066A1Precise cuttingImprove final accuracyComputation using denominational number representationComputer architectureFloating-point unit

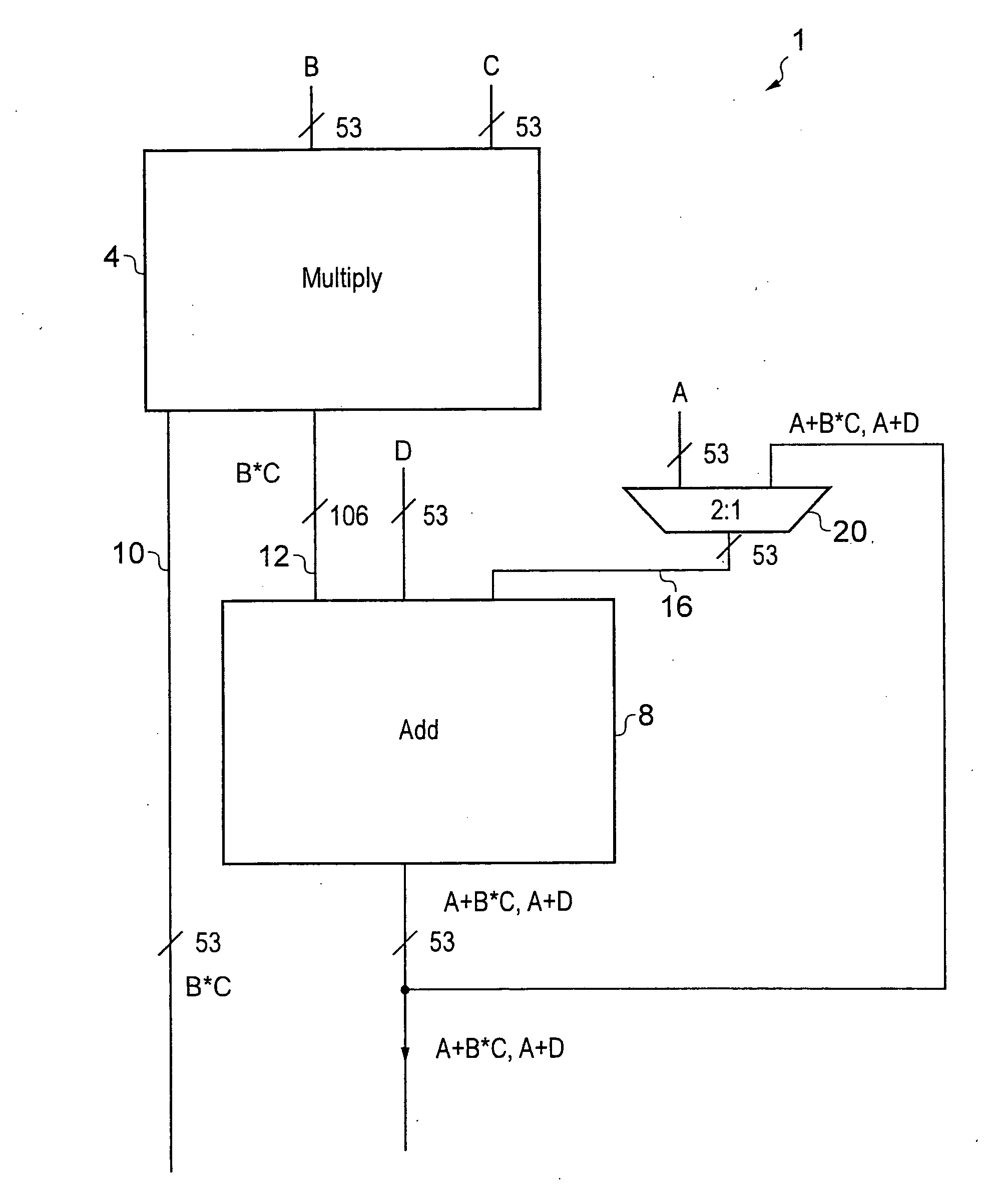

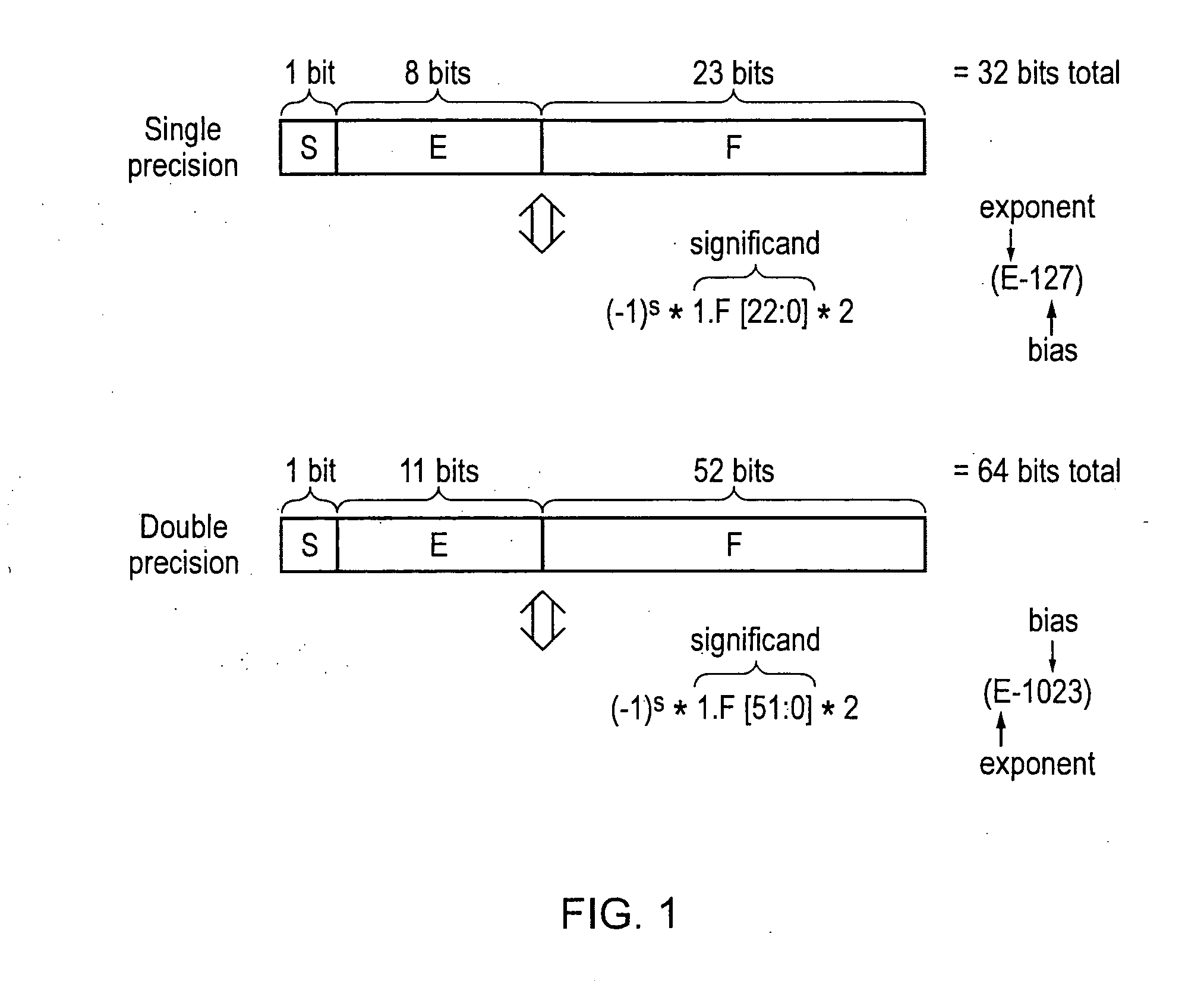

A fused multiply add floating point unit 1 includes multiplying circuitry 4 and adding circuitry 8. The multiply circuitry 4 multiplies operands B and C having N-bit significands to generate an unrounded product B*C. The unrounded product B*C has an M-bit significand, where M>N. The adding circuitry 8 receives an operand A that is input at a later processing cycle than a processing cycle at which the multiplying circuitry 4 receives operands B and C. The adding circuitry 8 commences processing of the operand A after the unrounded product B*C is generated by the multiplying circuitry 4. The adding circuitry 8 adds the operand A to the unrounded product B*C and outputs a rounded result A+B*C.

Owner:ARM LTD

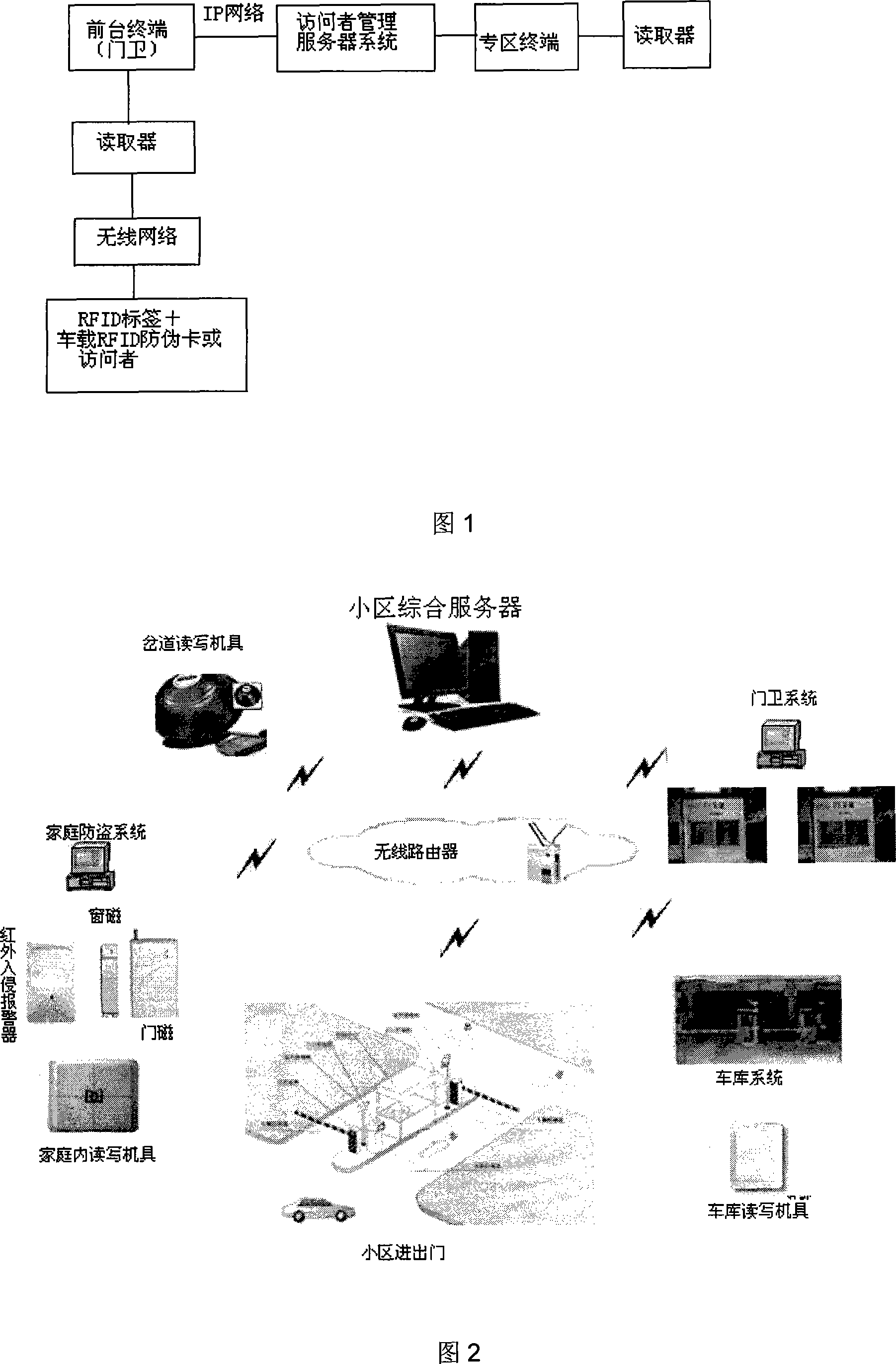

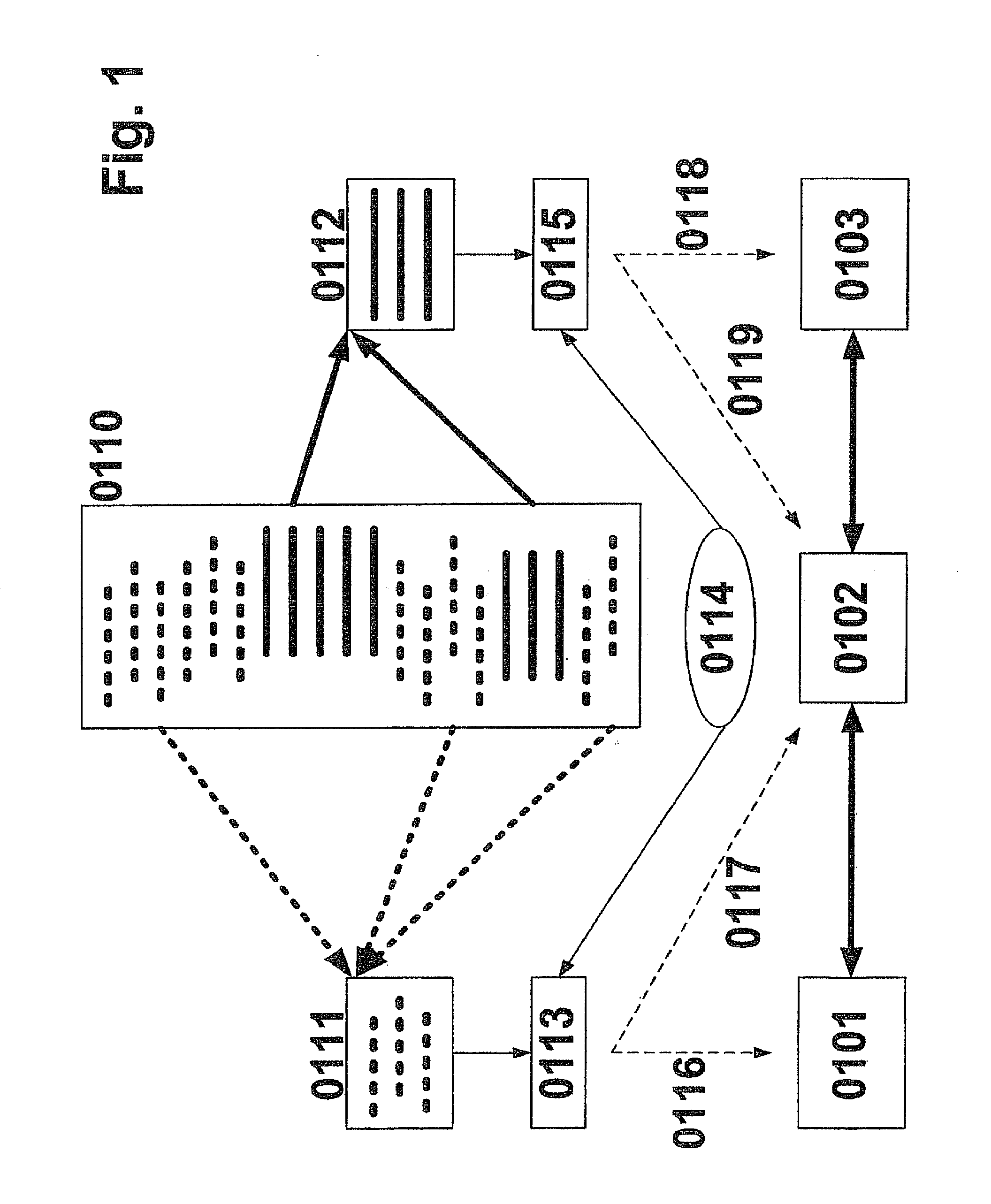

Personal identification and article anti-theft intelligent information management system and method

InactiveCN101246610AImprove performanceQuick identificationCo-operative working arrangementsIndividual entry/exit registersAudio electronicsRecognition system

The present invention provides an identification and product anti-theft intelligent information management system and method, the whole system is composed of number plate electronic tag, a ''subdistrict residence'' electronic tag, a wireless LAN emitter, a desk computer, a computer sound, a door magnet or infrared intrusion system, a fixed electronic tag reader-writer, special camera, an image recognition system, an electronic tag managememt system and a comprehensive service platform, the system automatically identifies exotic personnel entering in the district, and omnibearing monitoring operation rail; pepole having illegimate identity is alarmed when intruding in the district, the vehicle, non-motorized vehicle entering in the district are automatically identified; the public property belonging to the district is automatically monitored, so as to achieve the anti-theft aim. The invention can improve the comprehensive management level, avoiding waste of social resource caused by thefts and burglaries, and also reducing stolen source of the secondary market.

Owner:高喆

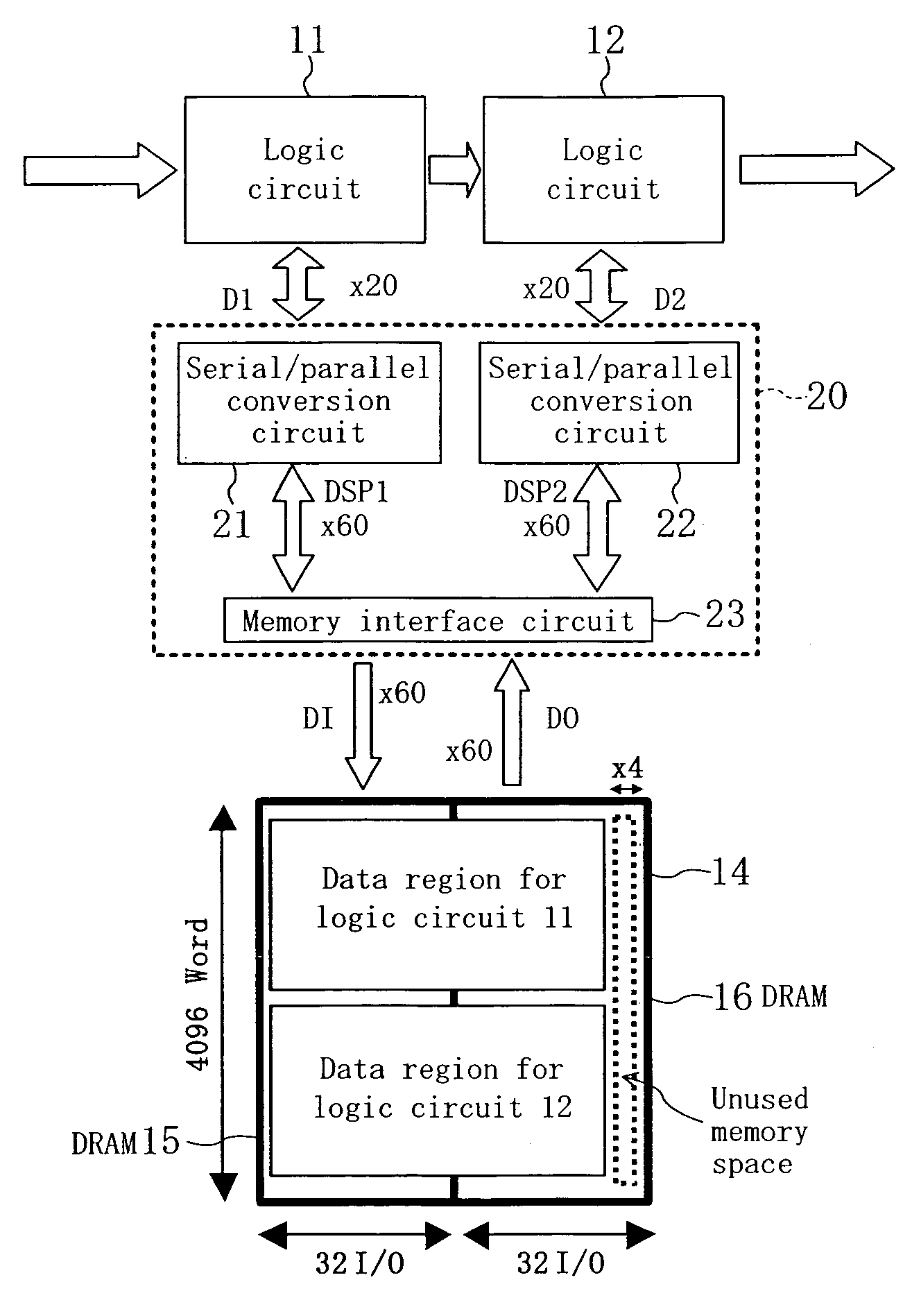

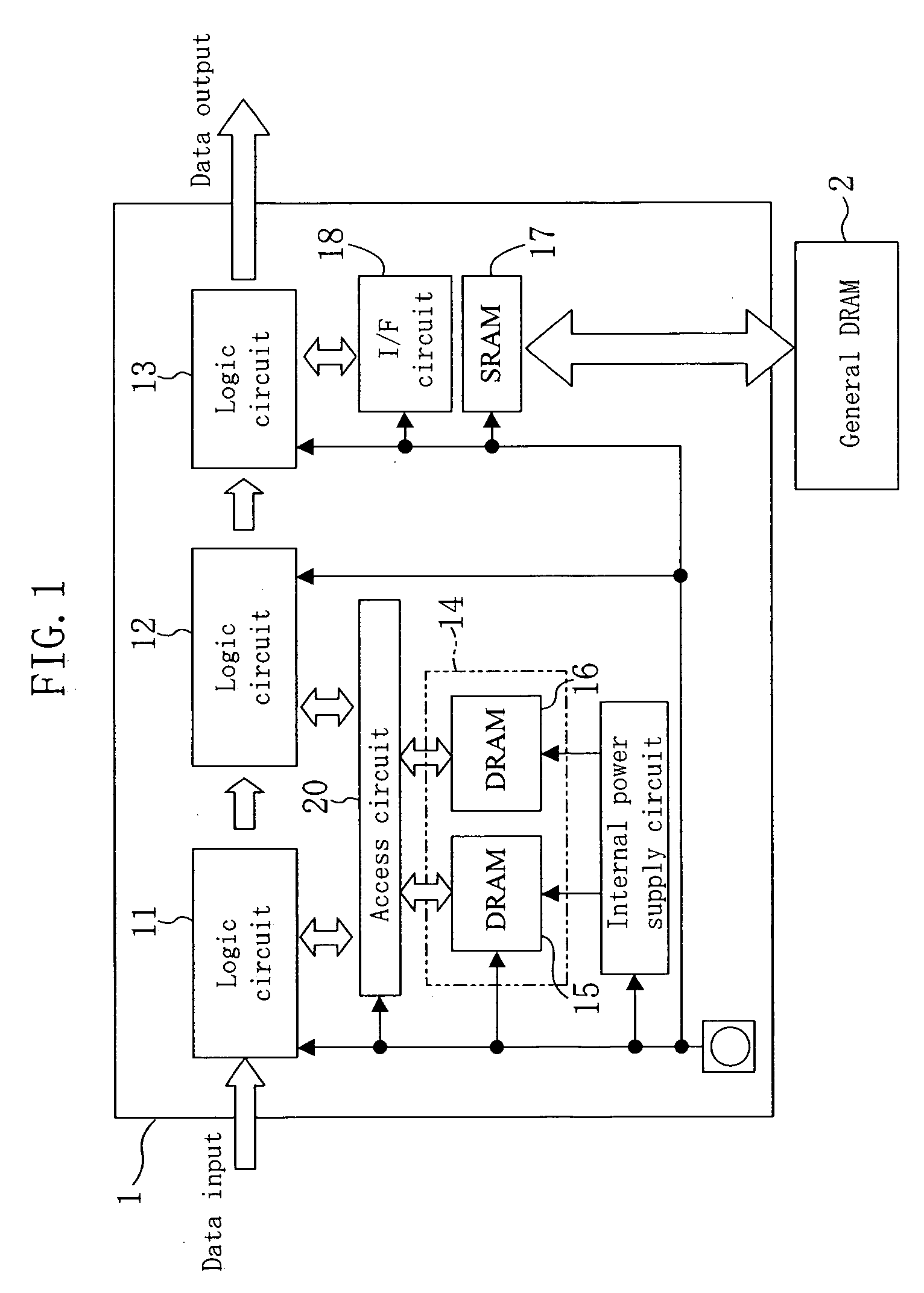

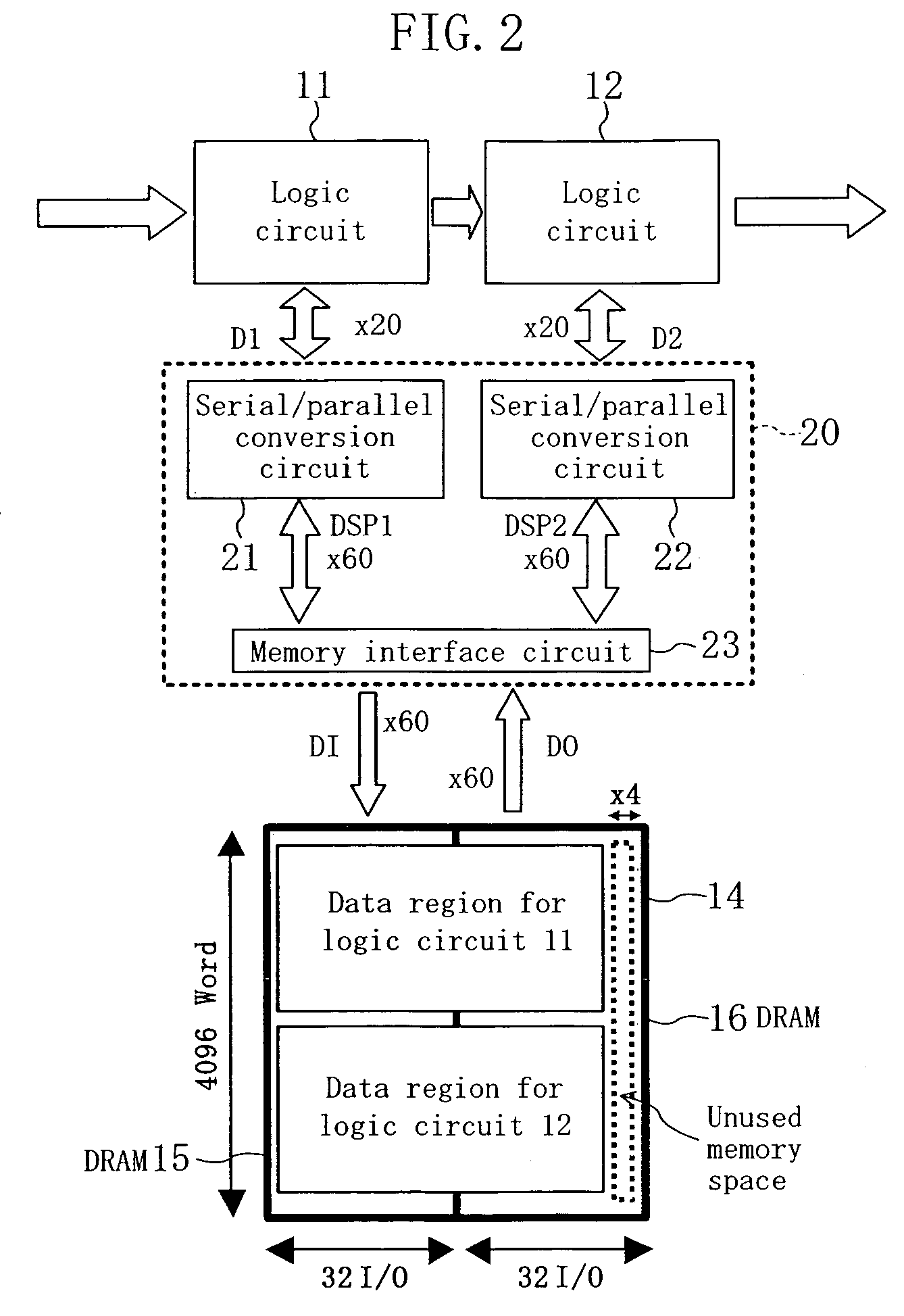

Semiconductor integrated circuit device having a common DRAM block accessed by a plurality of logic circuits

ActiveUS6990043B2Lower capability requirementsReduce areaMemory adressing/allocation/relocationDigital storageHemt circuitsComputer science

A plurality of logic circuits access a DRAM block by way of an access circuit. The operation clock for the DRAM block is set at a higher frequency than the system clock for the logic circuits. Outputs of a first bit width from the logic circuits are subjected to serial / parallel conversion into data of a second bit width and the data is written into the DRAM block.

Owner:CETUS TECH INC

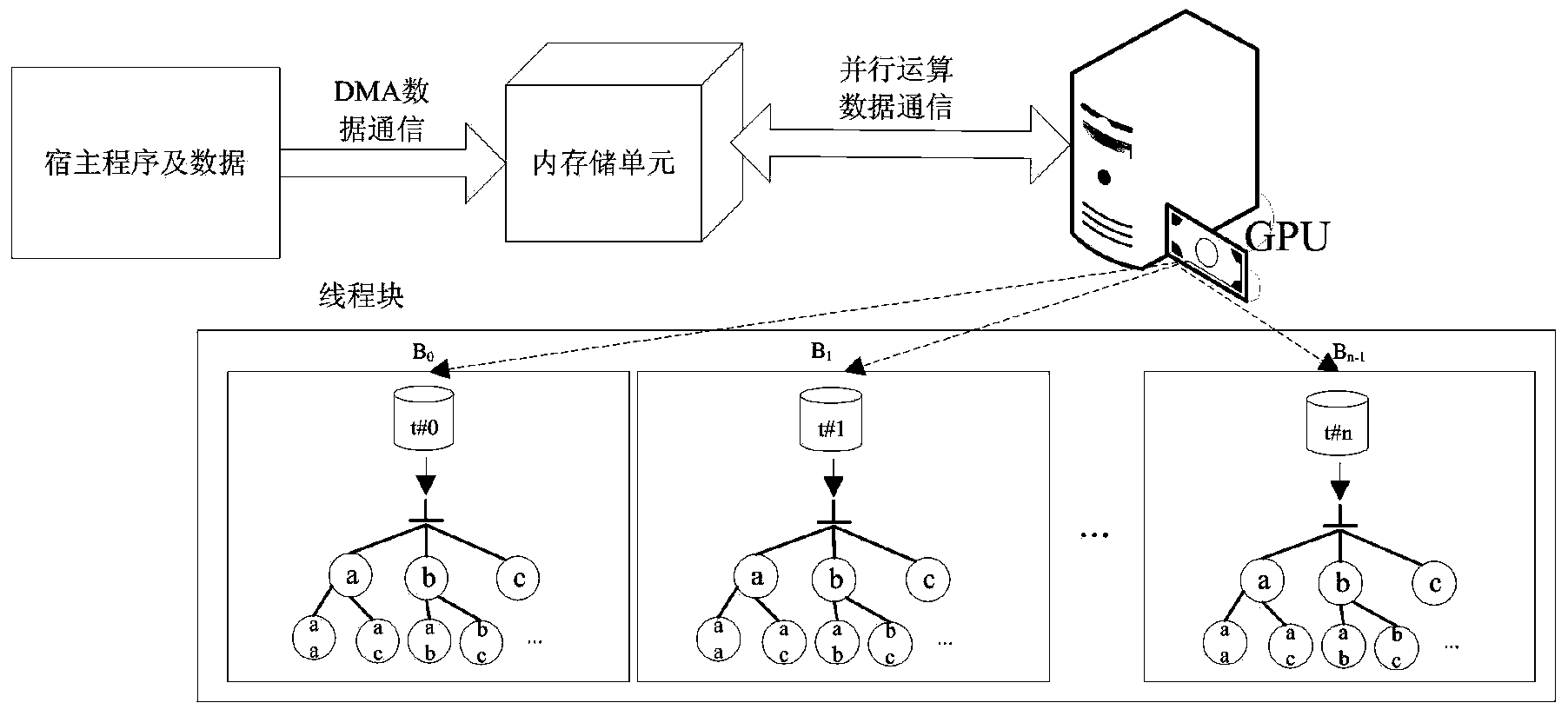

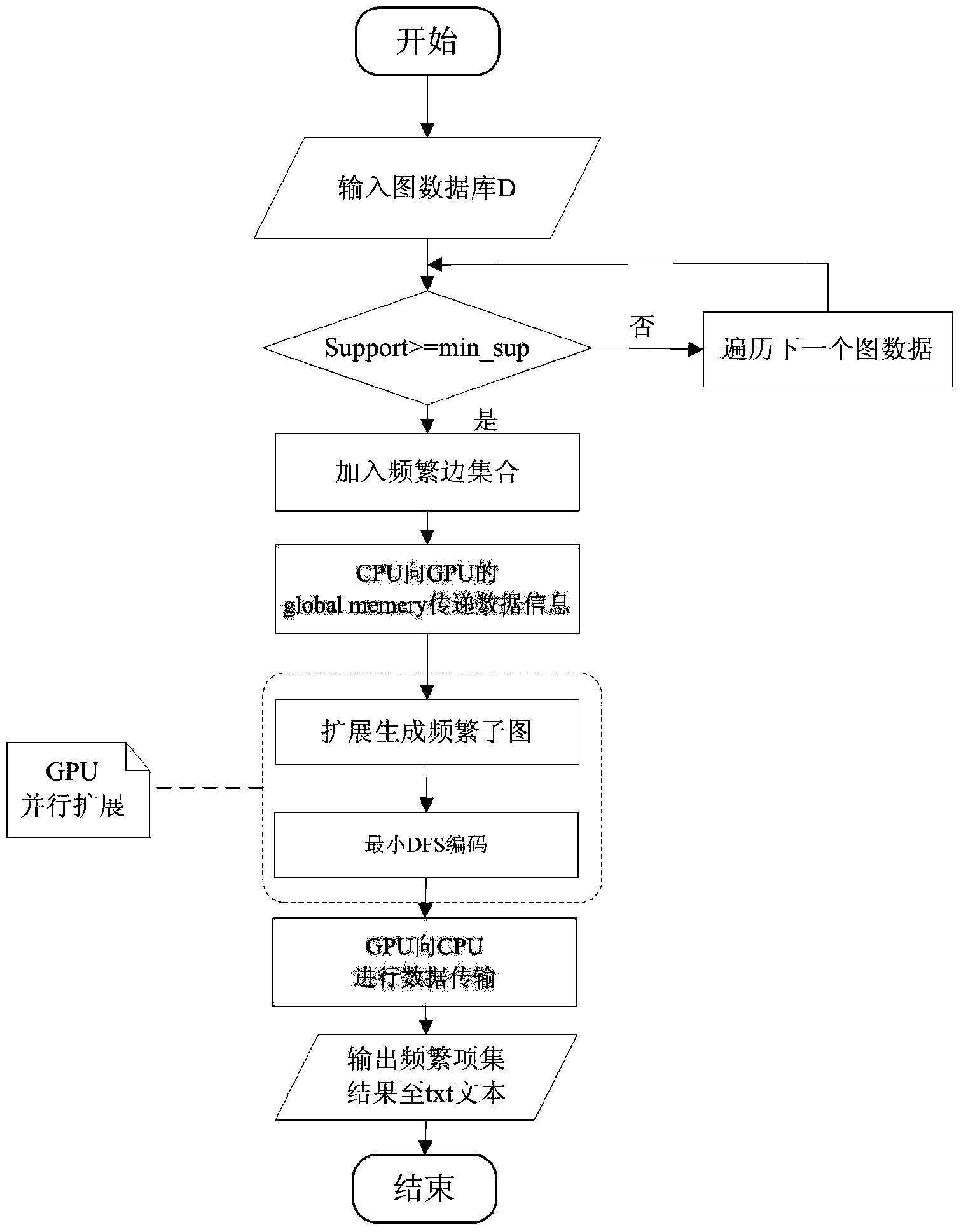

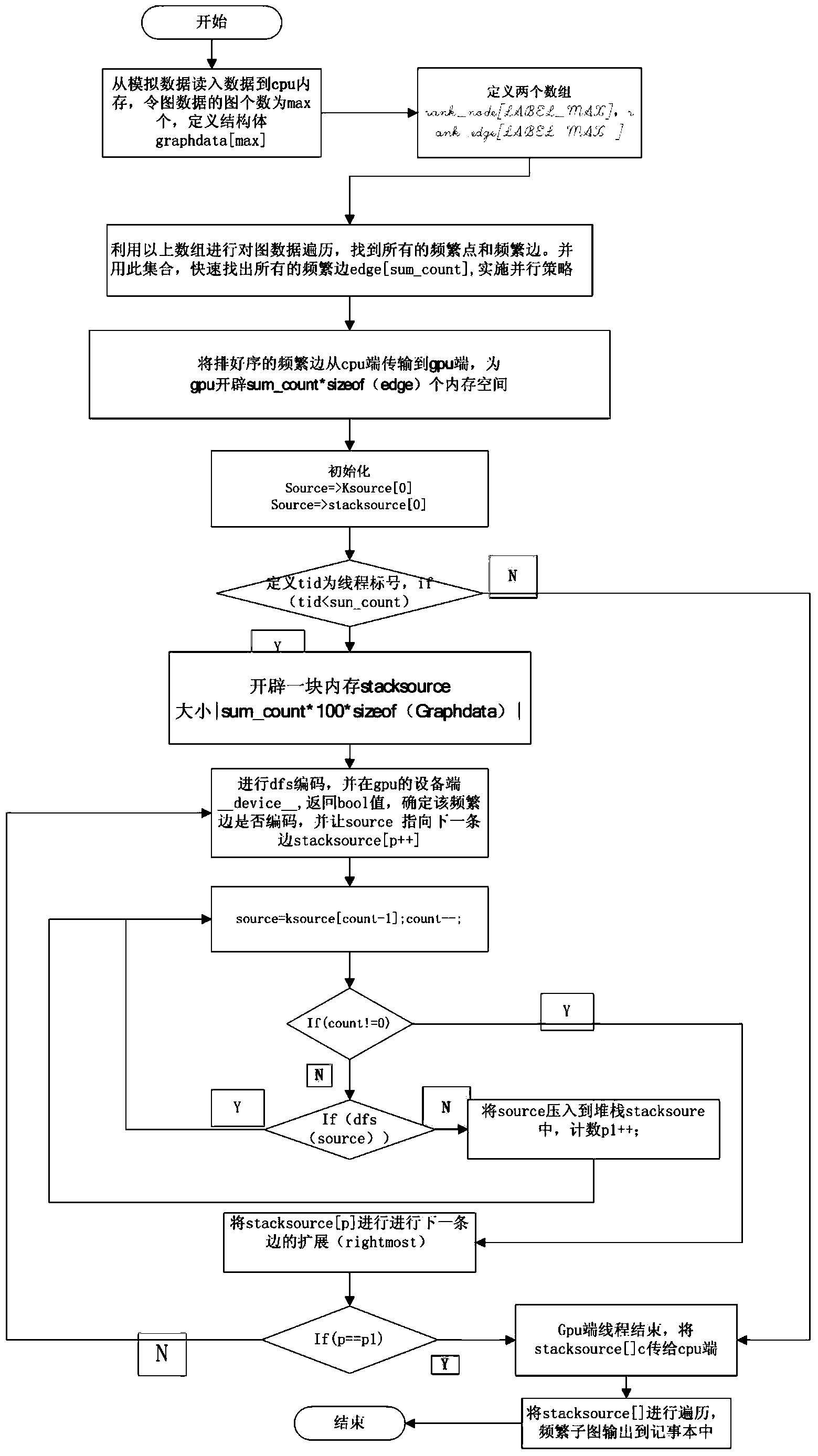

Frequent subgraph excavating method based on graphic processor parallel computing

ActiveCN103559016ACollaborative Computing RealizationImprove data processing capabilitiesResource allocationConcurrent instruction executionGraphicsData set

The invention discloses a frequent subgraph excavating method based on graphic processor parallel computing. The method includes marking out a plurality of thread blocks through a graphic processing unit (GPU), evenly distributing frequent sides to different threads to conduct parallel processing, obtaining different extension subgraphs through right most, returning the graph excavating data set obtained by each thread to each thread block, finally utilizing the GPU to conduct data communication with a memory and returning a result to a central processing unit (CPU) to process the result. The graph excavating method is feasible and effective, graph excavating performance is optimized under intensive large data environment, graph excavating efficiency is improved, data information is provided for scientific research analysis, market research and the like fast and reliably, and a parallel excavating method on a compute unified device architecture (CUDA) is achieved.

Owner:JIANGXI UNIV OF SCI & TECH

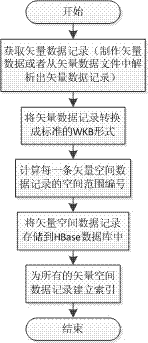

Vector space big data storage method based on HBase

InactiveCN103116610AImprove scalabilityEasy to handleSpecial data processing applicationsData fieldData store

The invention relates to the field of big data storage of computers and discloses a vector space big data storage method based on the HBase. The vector space big data storage method based on the HBase includes the following steps: 1) a vector data record is collected; 2) spacial scale numbers of the vector data record are computed; 3) an ID of the vector data record is taken as a row key, a data field and an attribute field except for the ID of the vector data record are taken as a row, and a data record is created; 4) the spacial scale numbers of the vector data record is taken as the row key, IDs of all vector space data in the spacial scale numbers are taken as the row, and an index is created. The vector space big data storage method based on the HBase has the advantages of being capable of supporting distributed storage and management of vector space data of a super-large scale and supporting quick query of a geographic position range. Compared with the existing vector space data storage method, the vector space big data storage method based on the HBase has a high visit concurrent amount and supports expansion of a data scale.

Owner:ZHEJIANG UNIV

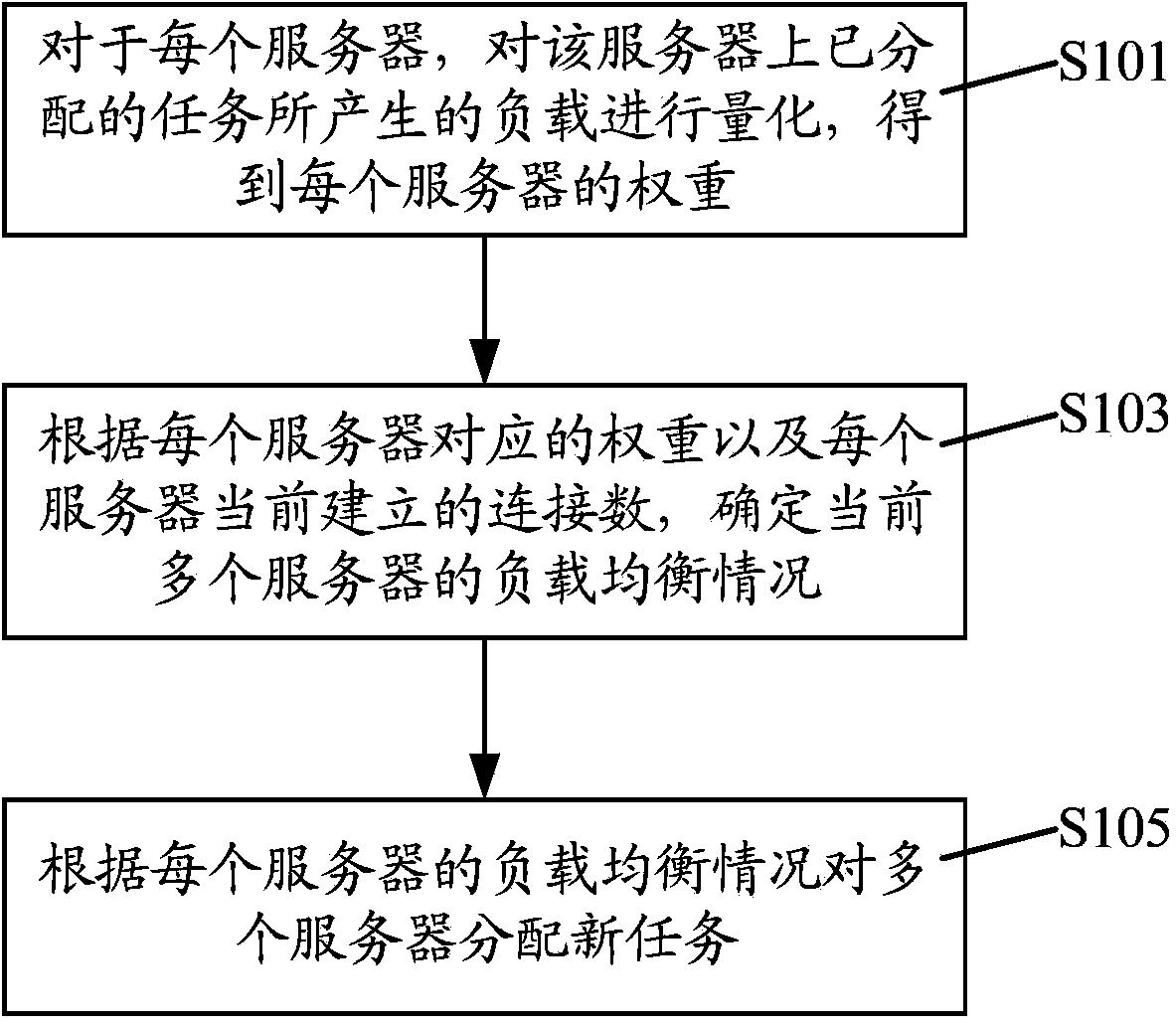

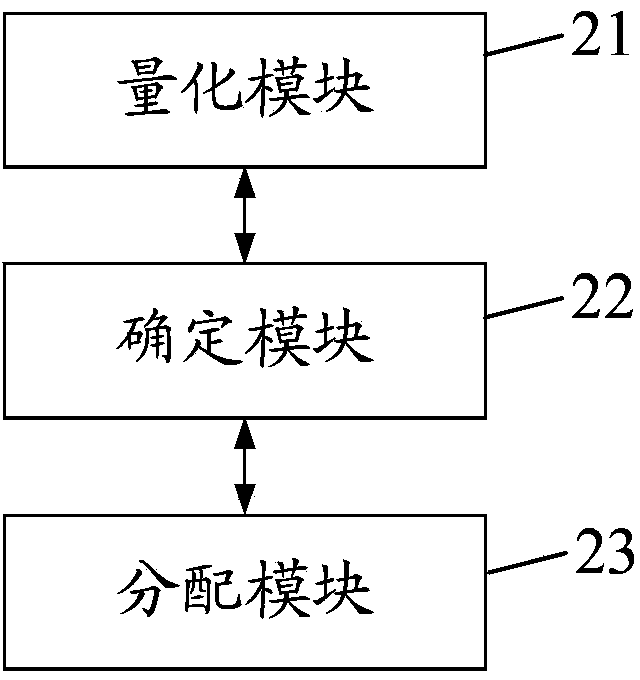

Method and device for allocating tasks to multiple servers

The invention discloses a method and a device for allocating tasks to multiple servers. The method comprises steps as follows: quantizing a load produced by a task allocated to each server, and obtaining a weight of each server; determining load balancing conditions of the multiple current servers according to the corresponding weight of each server and current connections established by each server; and allocating new tasks to the multiple servers according to the load balancing conditions of each server. According to the method, the load balancing conditions of the multiple current servers are determined according to the corresponding weight of each server and the current connections established by each server, so that the tasks can be reasonably allocated according to the load condition of each server, the data processing capacity is enhanced, the server resources are reasonably used, and the flexibility and the usability of the servers are improved.

Owner:DAWNING INFORMATION IND BEIJING

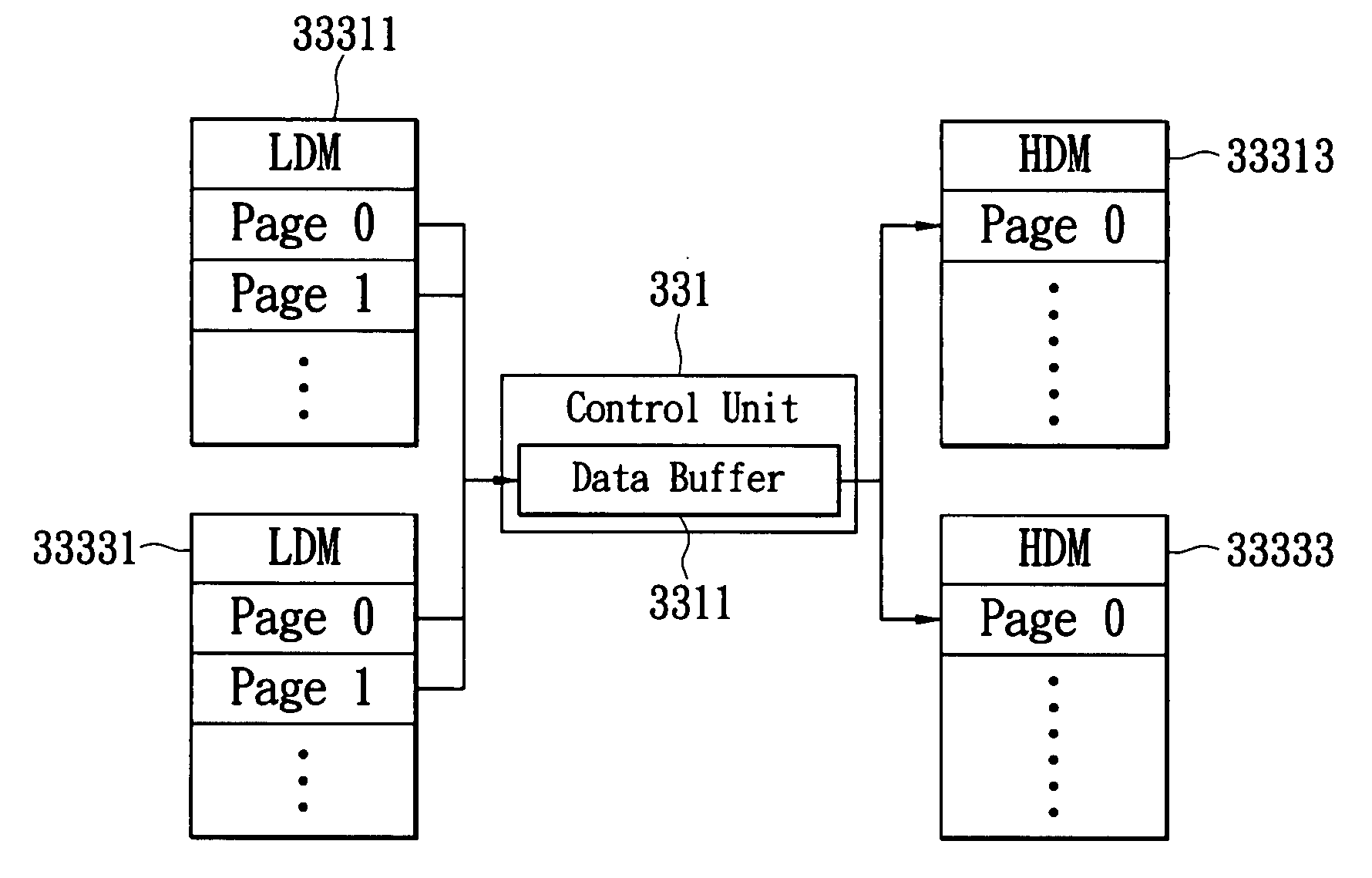

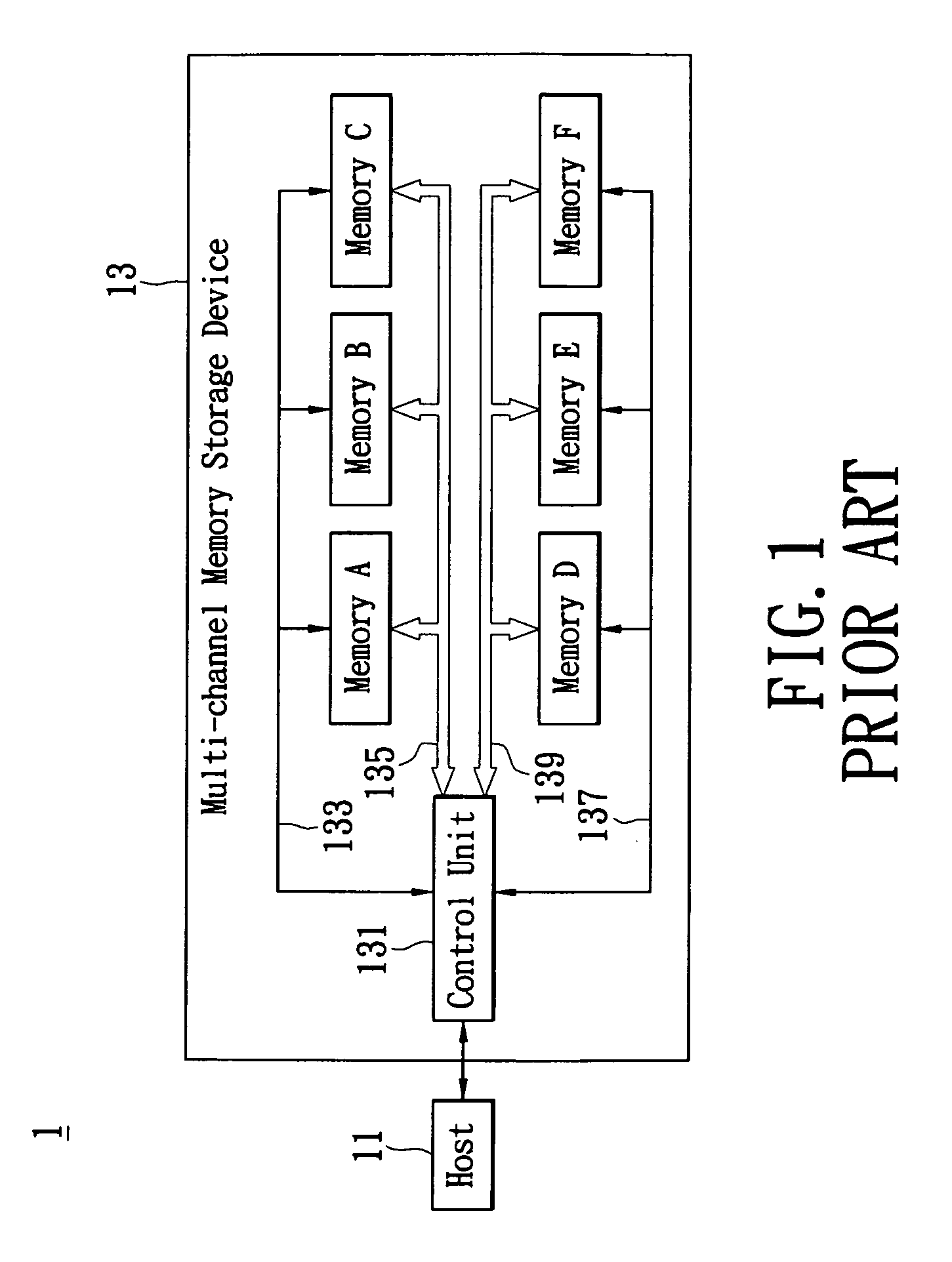

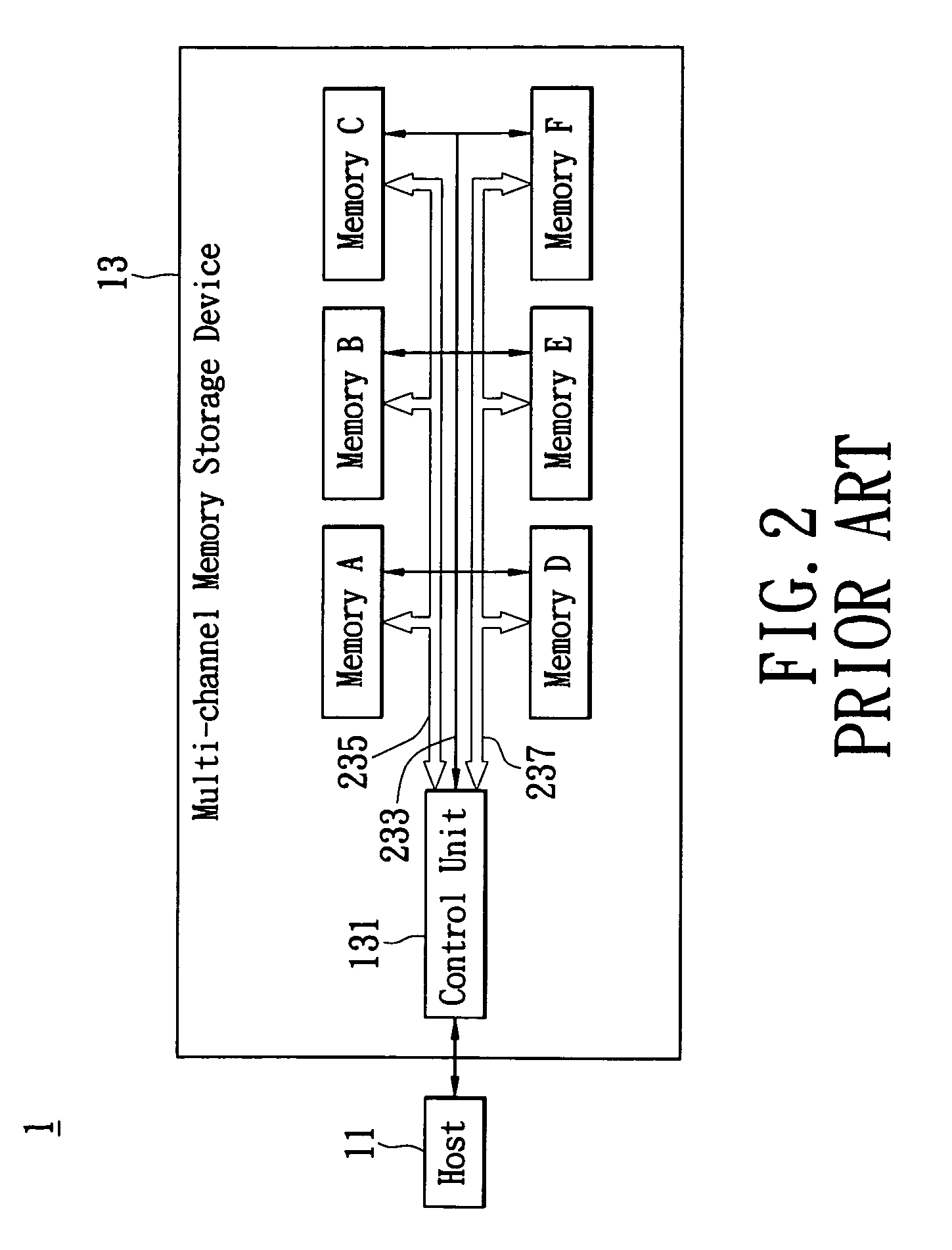

Multi-channel hybrid density memory storage device and control method thereof

ActiveUS20090307418A1Improve access speedImprove data processing capabilitiesMemory architecture accessing/allocationError detection/correctionComputer hardwareHigh density

The present invention discloses a control method of a multi-channel hybrid density memory storage device for access a user data. The storage device includes a plurality of low density memories (LDM) and high density memories (HDM). The steps of the method comprises: first, determining where the user data transmitted; then, using one of two error correction circuits which have different error correction capability to encode or decode the user data.

Owner:ADATA

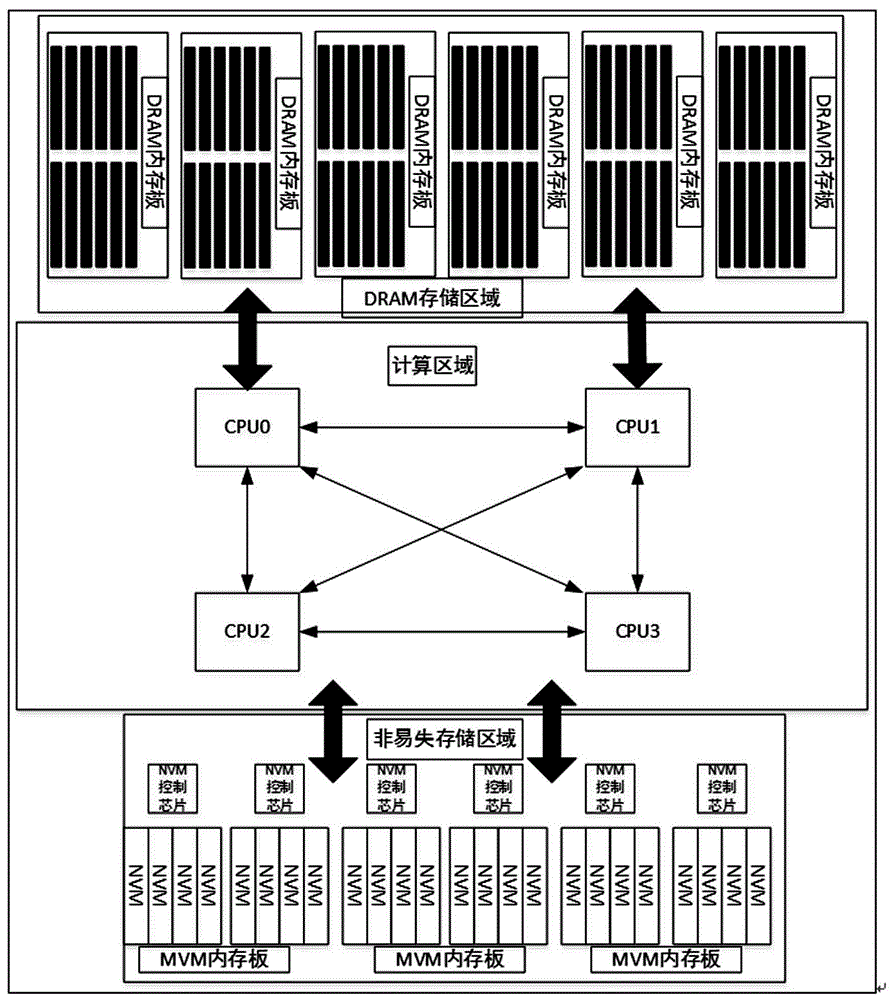

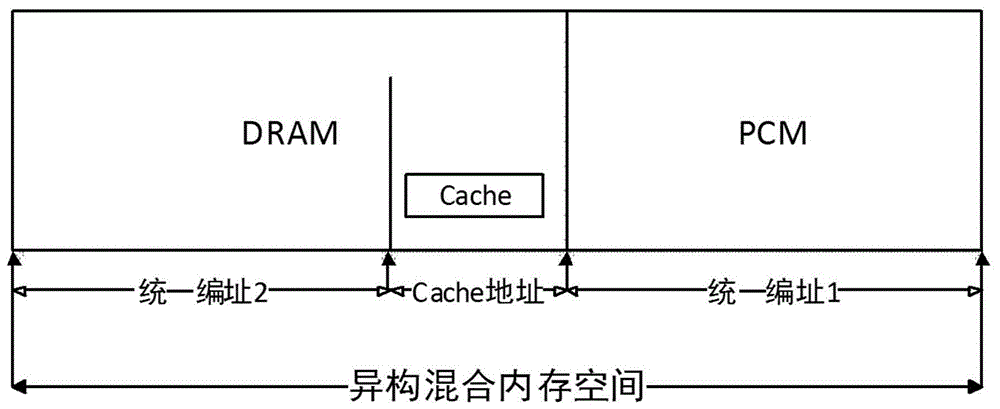

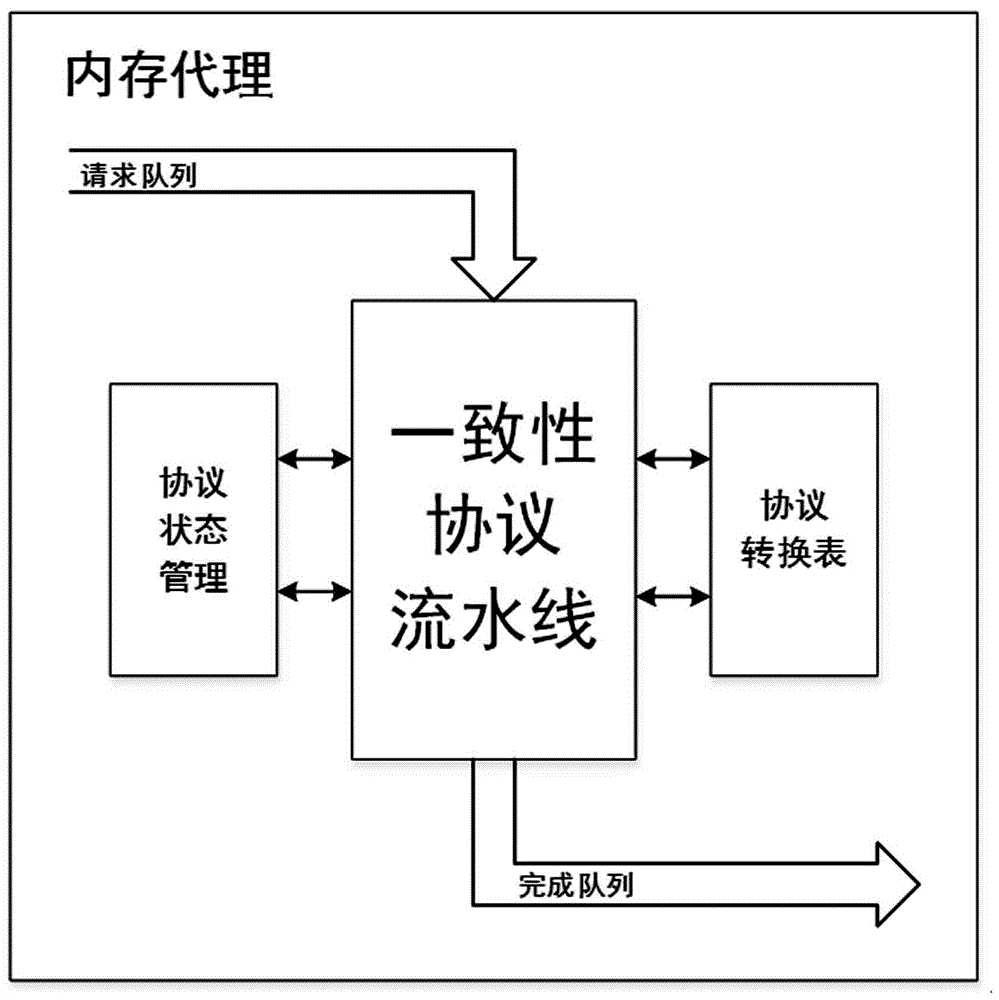

System and method for extending nonvolatile memory based on consistency buses

InactiveCN106843772AImprove access performanceSolve technical bottlenecksInput/output to record carriersMemory systemsDram memoryParallel computing

The invention discloses a system and method for extending a nonvolatile memory based on consistent buses. The system structurally comprises a plurality of nodes mutually connected through cache consistency high-speed mutually-connected buses, wherein each node is configured with a hybrid memory consisting of a processor, a DRAM memory and a NVM memory, a NVM memory controller is configured between the processor and the NVM memory, a DRAM memory controller is configured between the processor and the DRAM memory, the processor is mutually connected with the NVM memory and the DRAM memory through the cache consistency high-speed mutually-connected buses, and the DRAM memory and the NVM memory are addressed in a unified mode to achieve overall cache consistency of a heterogeneous hybrid memory system. The method is achieved based on the system. Compared with the prior art, existing technical bottlenecks of the DRAM memory are solved by adopting the system and method for extending the nonvolatile memory based on the consistent buses, the NVM memory access performance is improved, data processing capability of the whole system is improved, and the system and method is high in practicability, wide in application range and easy to popularize.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

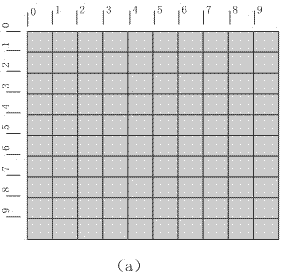

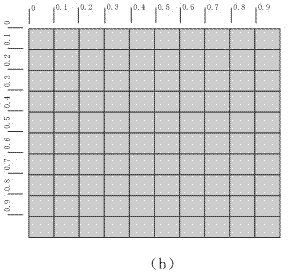

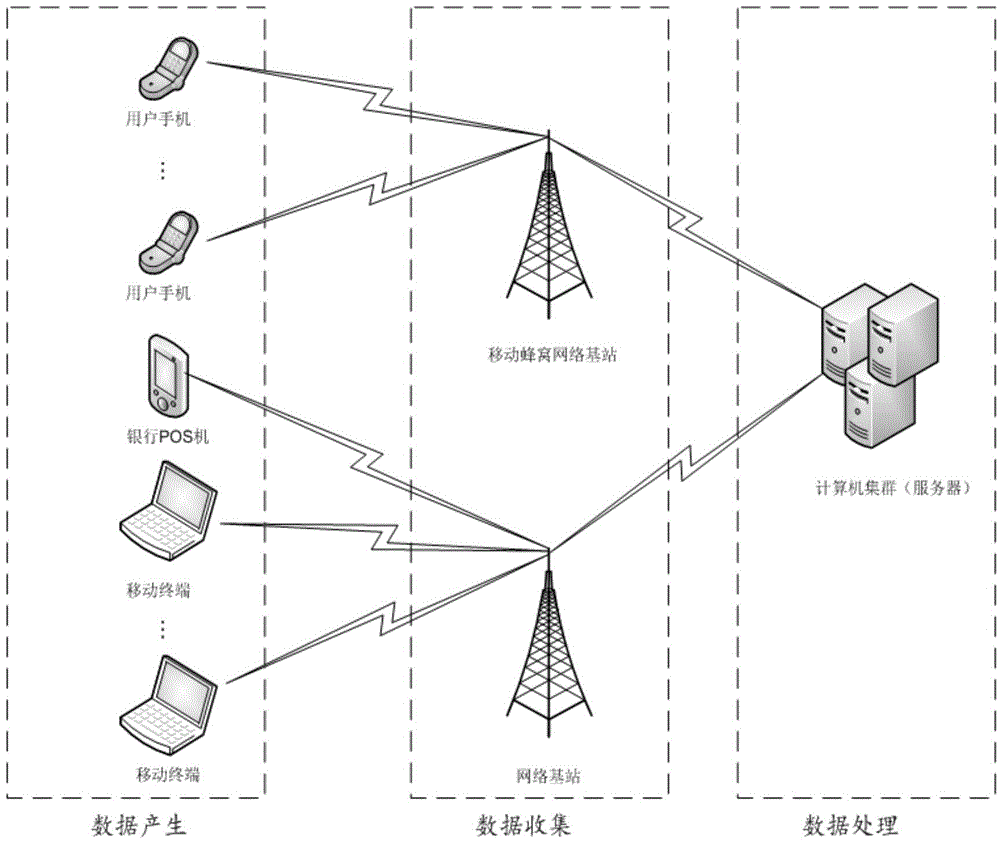

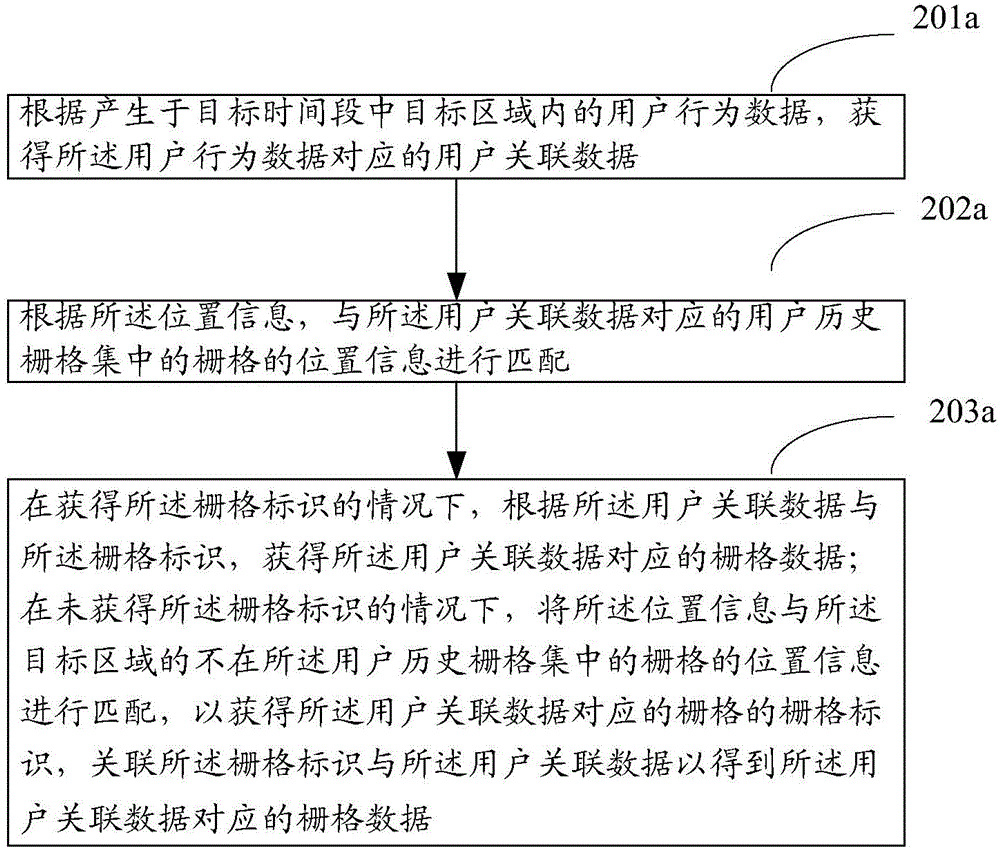

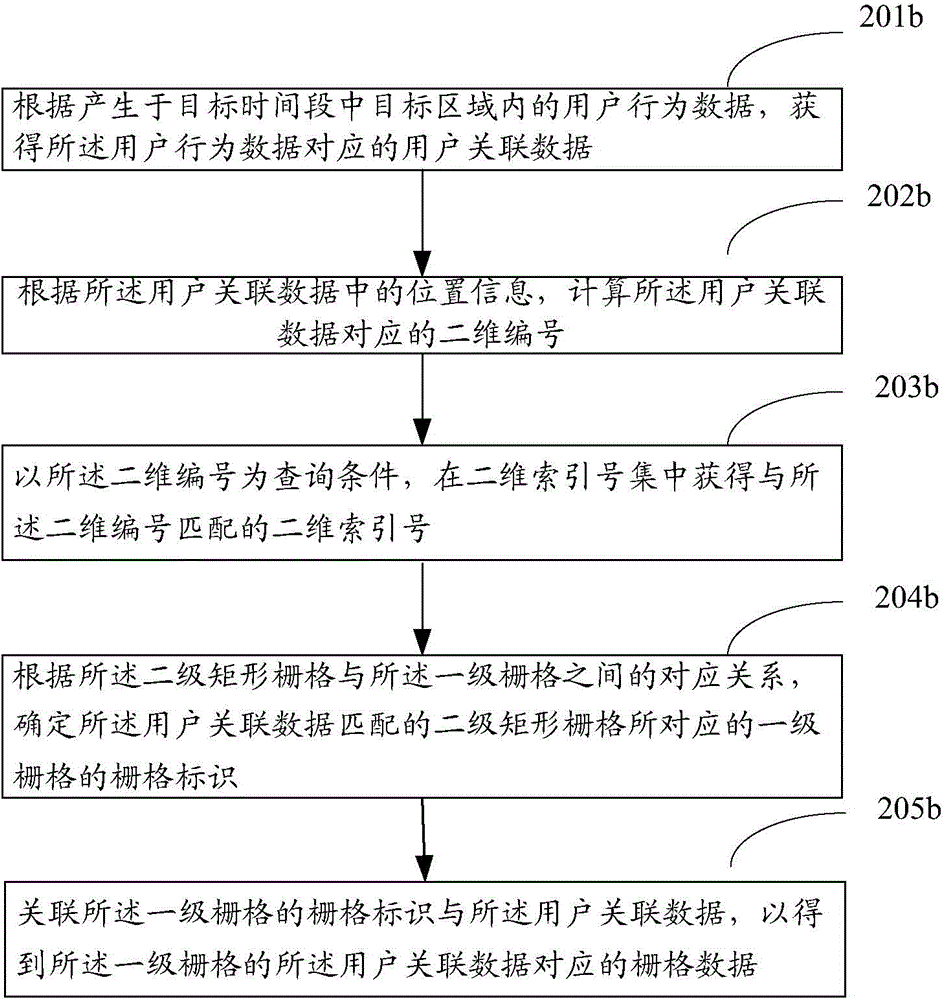

Method and device for data rasterization and method and device for user behavior analysis

ActiveCN104598557AImprove data processing efficiencyReduce occupancySpecial data processing applicationsBehavioral analyticsBehavior rule

The embodiment of the invention discloses a method and a device for data rasterization and a method and a device for user behavior analysis. The method for the data rasterization comprises the following steps of acquiring corresponding user associated data according to user behavior data produced in a target time period and located in a target area; computing a two-dimension number corresponding to the user associated data according to position information in the user associated data; acquiring a corresponding two-dimension index number from a two-dimension index number set by taking the two-dimension number as a query condition; associating a raster mark with the user associated data so as to obtain corresponding raster data. The efficiency of the data rasterization is increased, and user behavior rule or preference analysis based on mass of diversified real-time raster data is realized.

Owner:TIANJIN BAOGU INFORMATION TECH CO LTD

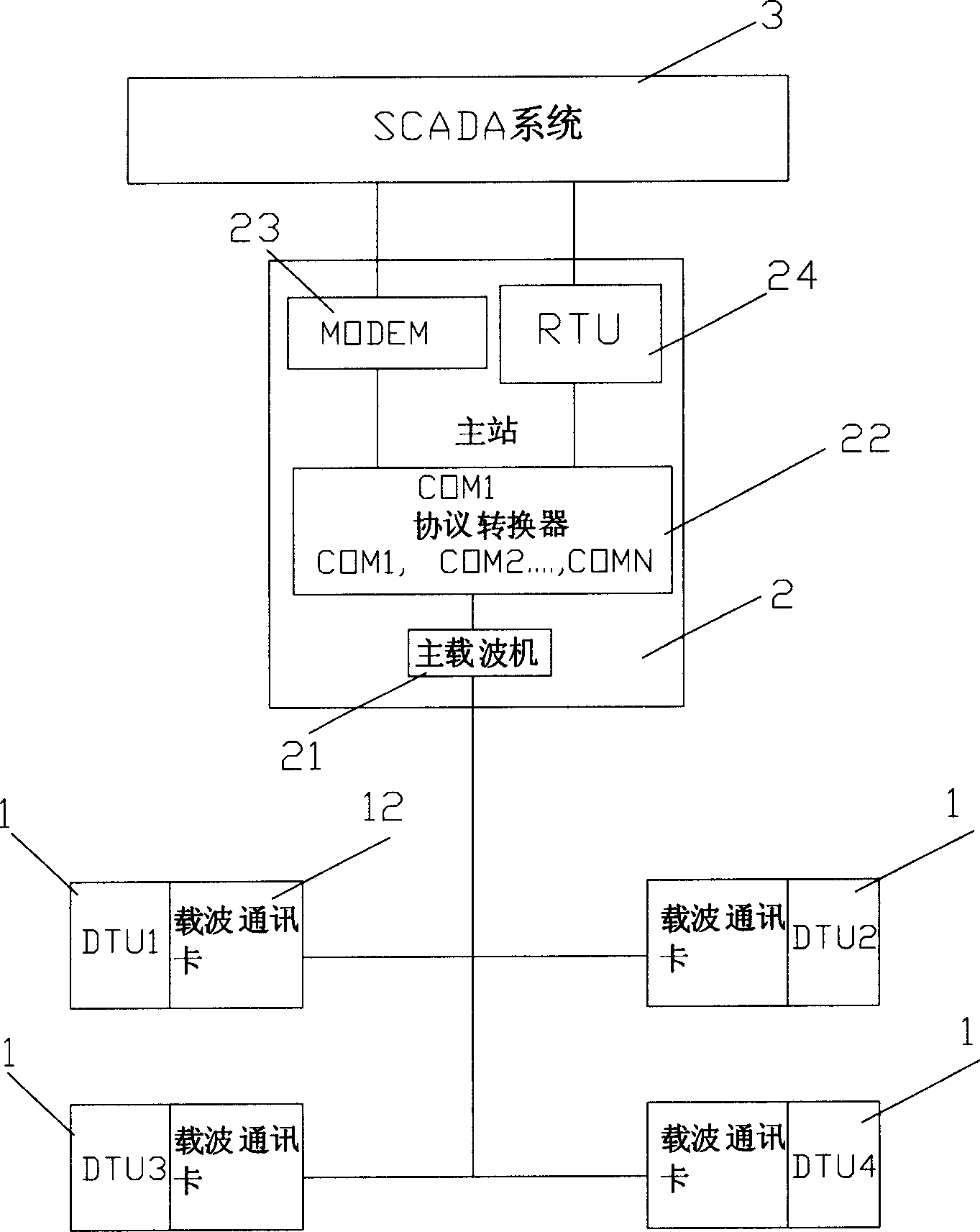

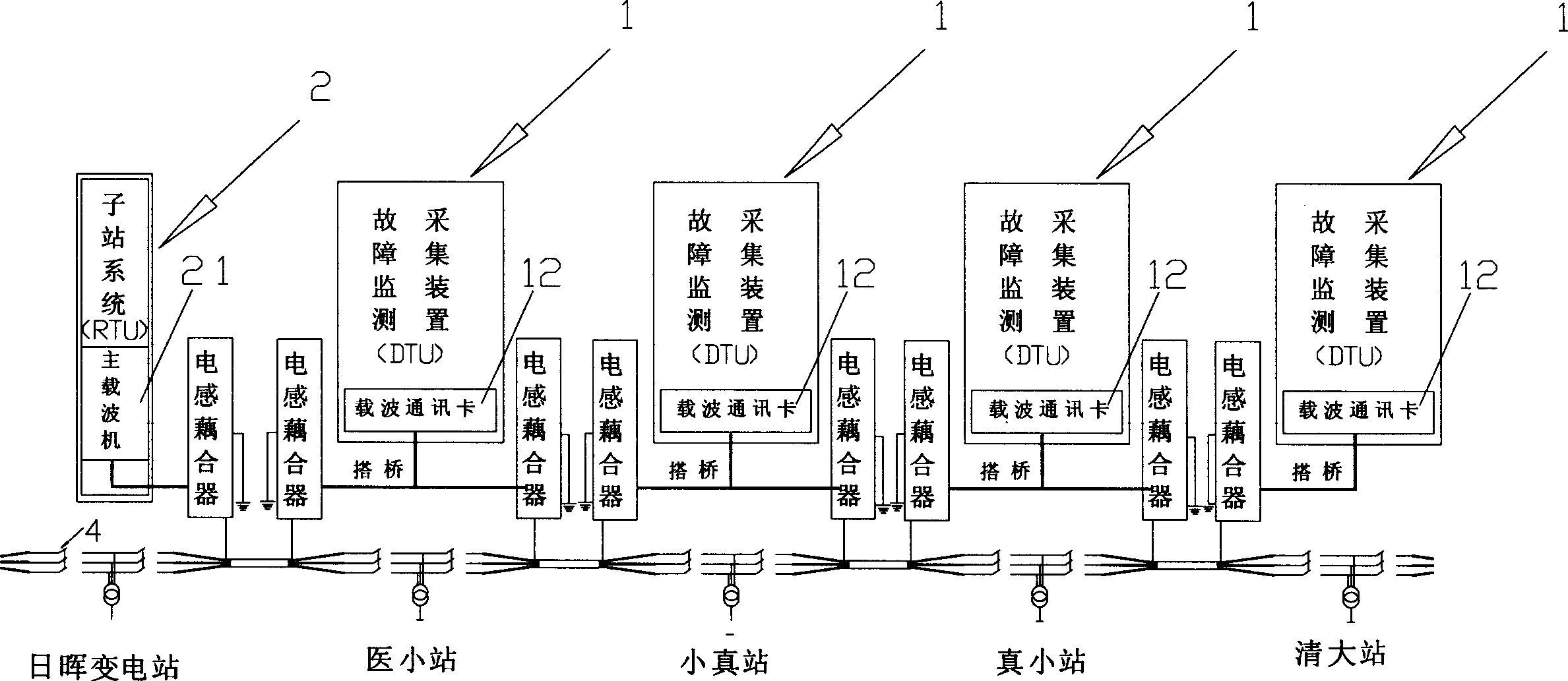

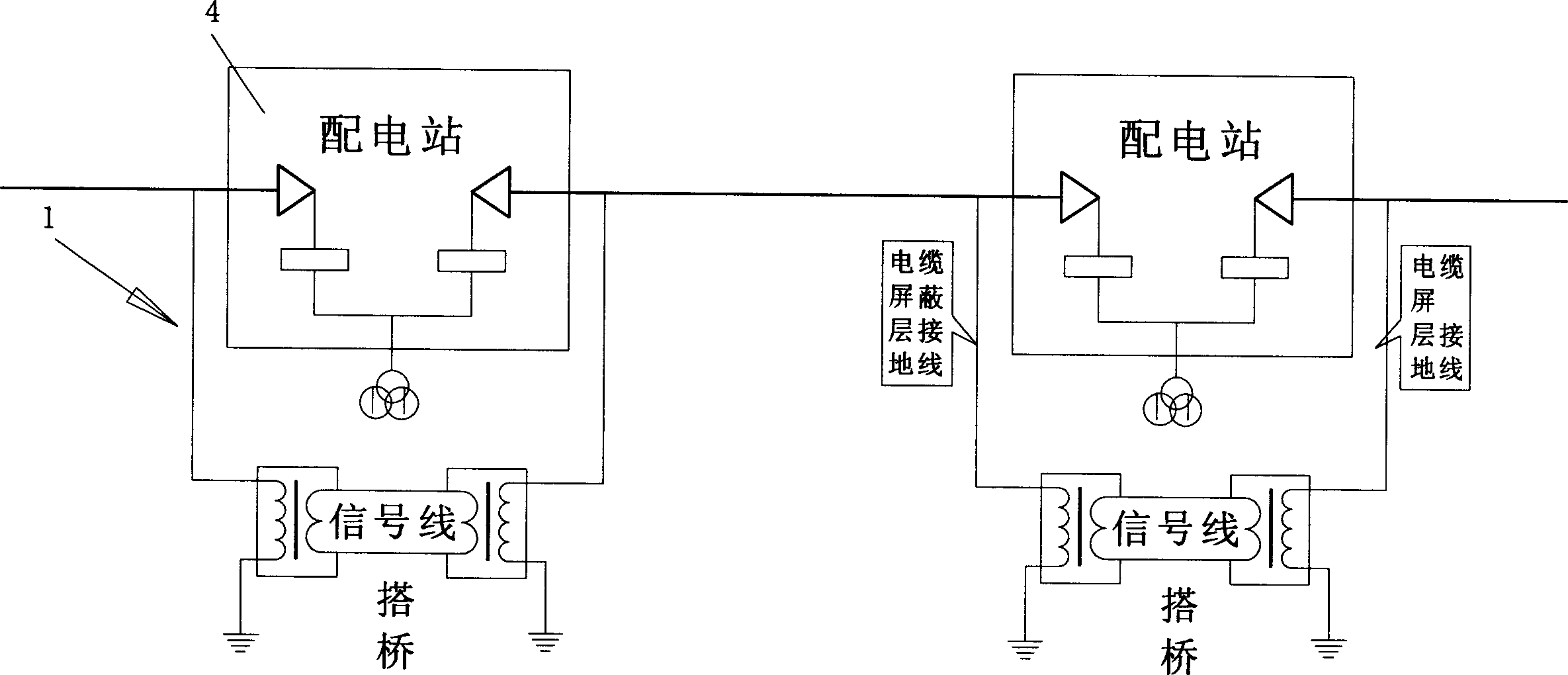

Distribution line fault monitoring system

ActiveCN1707277AImprove reliabilityImprove data processing capabilitiesElectrical testingInformation technology support systemProtocol converterMonitoring site

The fault monitoring system for power distributing system includes monitoring sites and one main station connected via power cables to the monitoring sites. In each of the monitoring sites, there are DTU with built-in carrier communication card and inductor coupler. The carrier communication card modulates data the DTU acquires and couples the modulated signal via the coupler to the power cable shielding layer. In the main station, there are main carrier machine, protocol converter and conductive coupler. Through coupling the modulated signals to the carrier machine in the main station, demodulation and corresponding protocol conversion, the RTU in the main station transmit the signal to peripheral SCADA system for fault analysis directly or via modem. After the fault section is determined, fault isolation and restoring power transmission may be completed. The present invention can raise the reliability of the power supply system.

Owner:SHANGHAI ELECTRIC POWER COMM +1

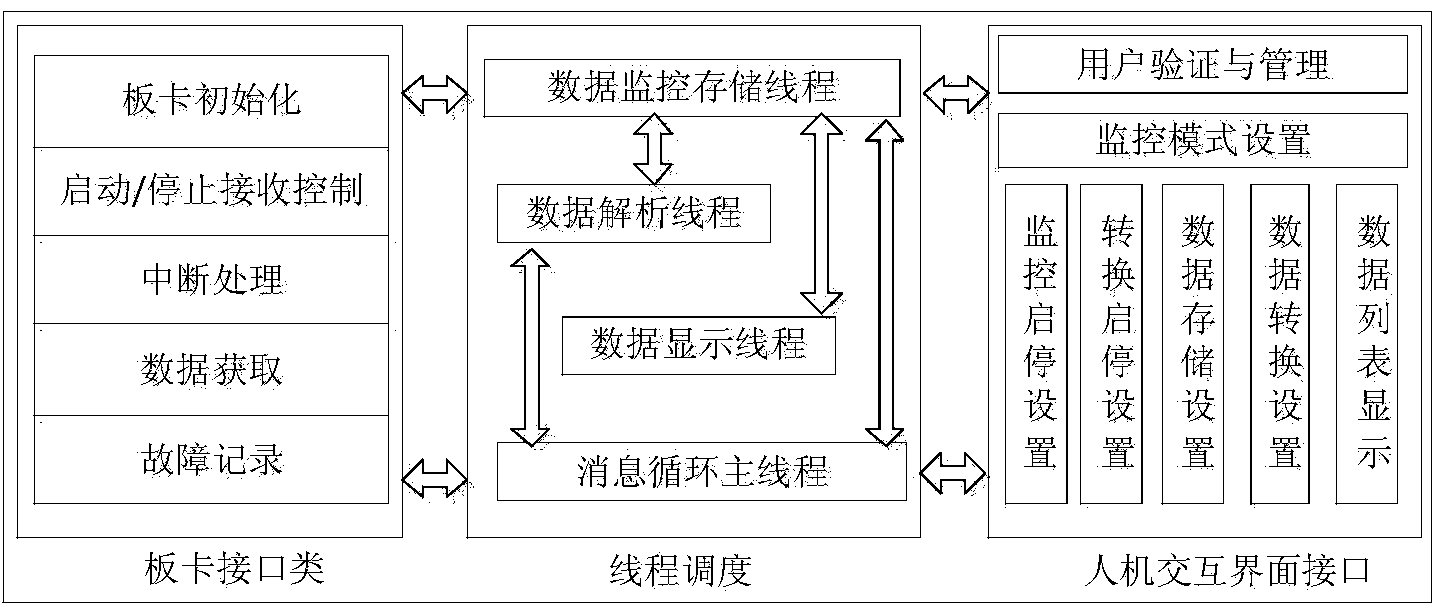

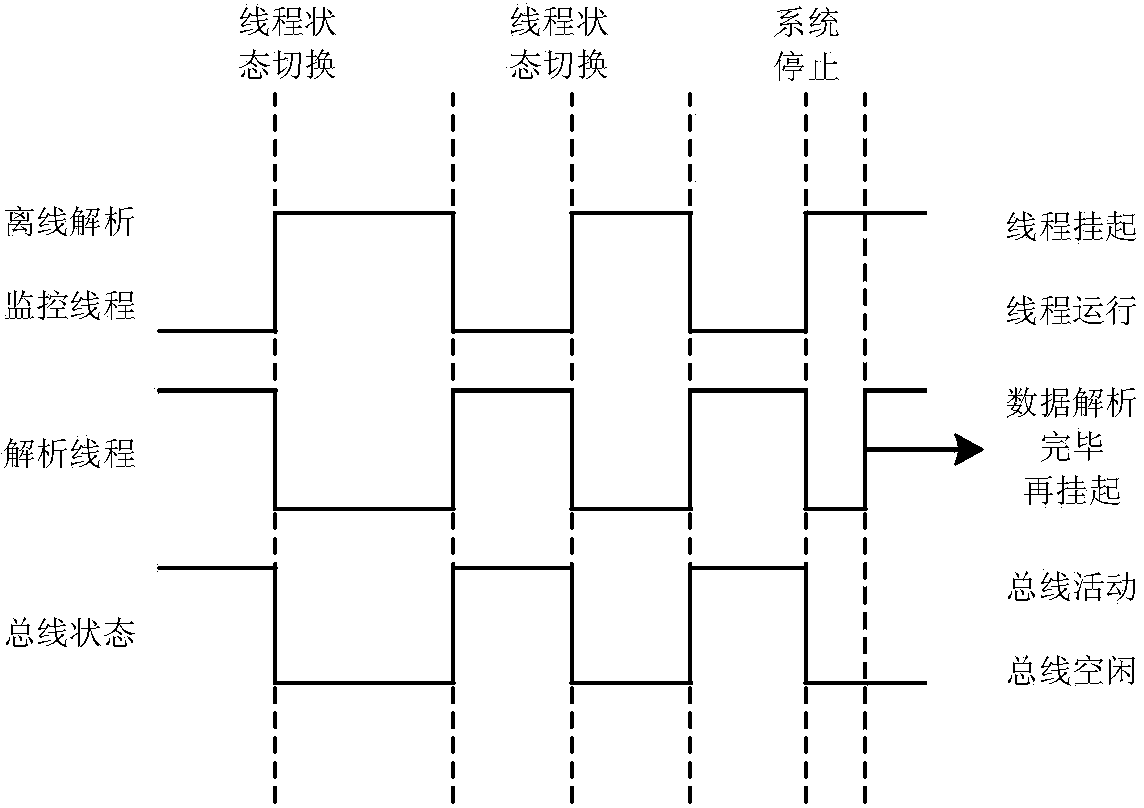

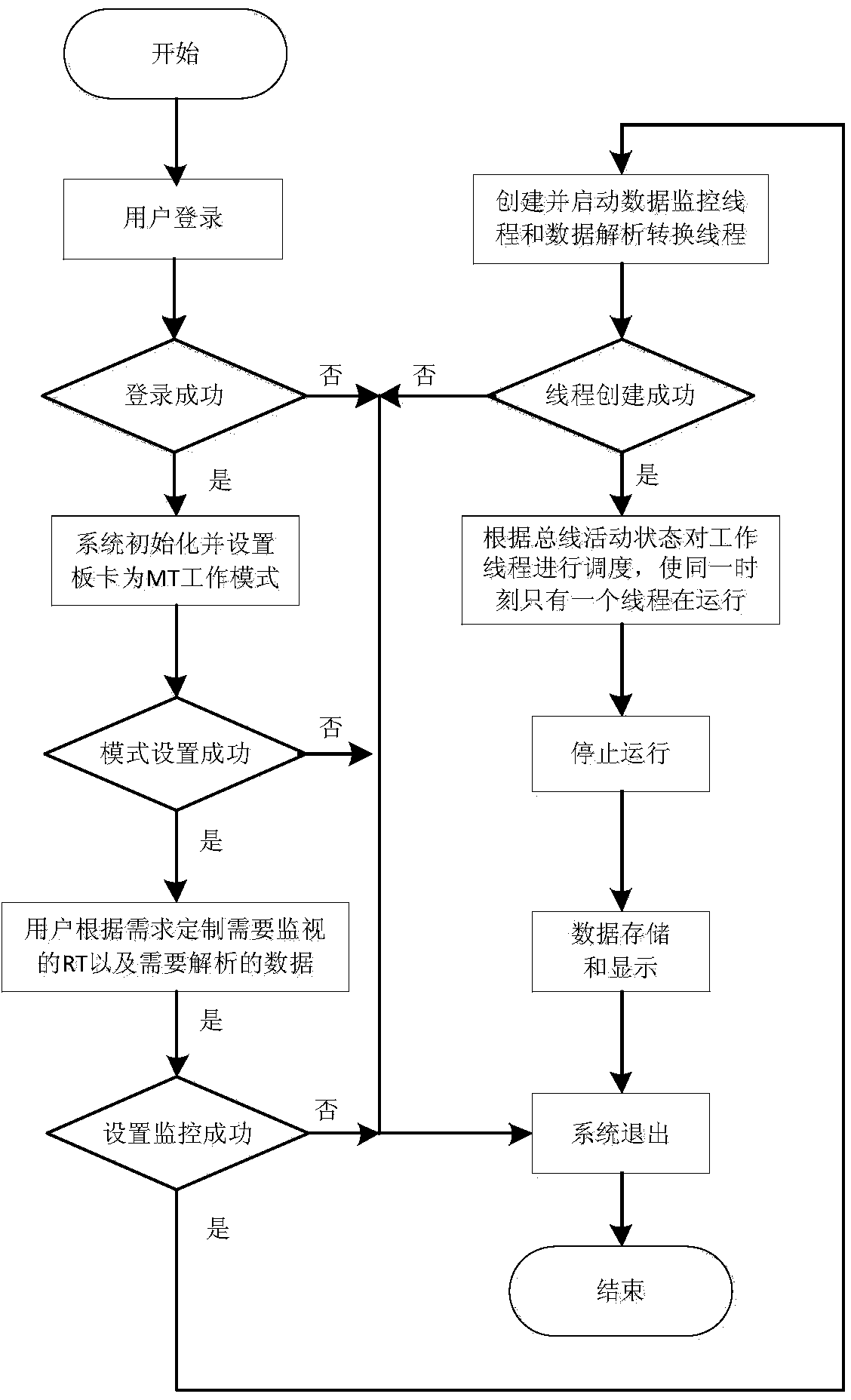

MIL-STD-1553B bus monitoring and data analysis system

ActiveCN103645947AGuaranteed resource exclusivityImprove data processing capabilitiesProgram initiation/switchingSpecial data processing applicationsData conversionMonitoring data

The invention discloses a 1553B bus monitoring and data analysis system. The 1553B bus monitoring and data analysis system comprises a board card interface module, a thread scheduling module and a man-machine interaction interface module. The board card interface module comprises a board card initialization module, a starting / stopping receiving control module, an interrupt processing module, a data acquisition module and a failure recording module. The thread scheduling module is provided with a data monitoring storage thread, a data analysis thread, a data display thread and a message loop main thread. The man-machine interaction interface module is provided with a user authentication and management module, a monitoring mode setting module, a monitoring starting and stopping setting module, a data conversion setting module, a conversion starting and stopping setting module, a data memory module and a data list display module. According to the 1553B bus monitoring and data analysis system, a thread dynamic scheduling algorithm is adopted, comprehensive monitoring of bus data and real-time storage, display and analysis conversion of MT monitoring data can be achieved, and display of bus monitoring information stored in a specific format and conversion processing of stored data can also be achieved.

Owner:BEIHANG UNIV

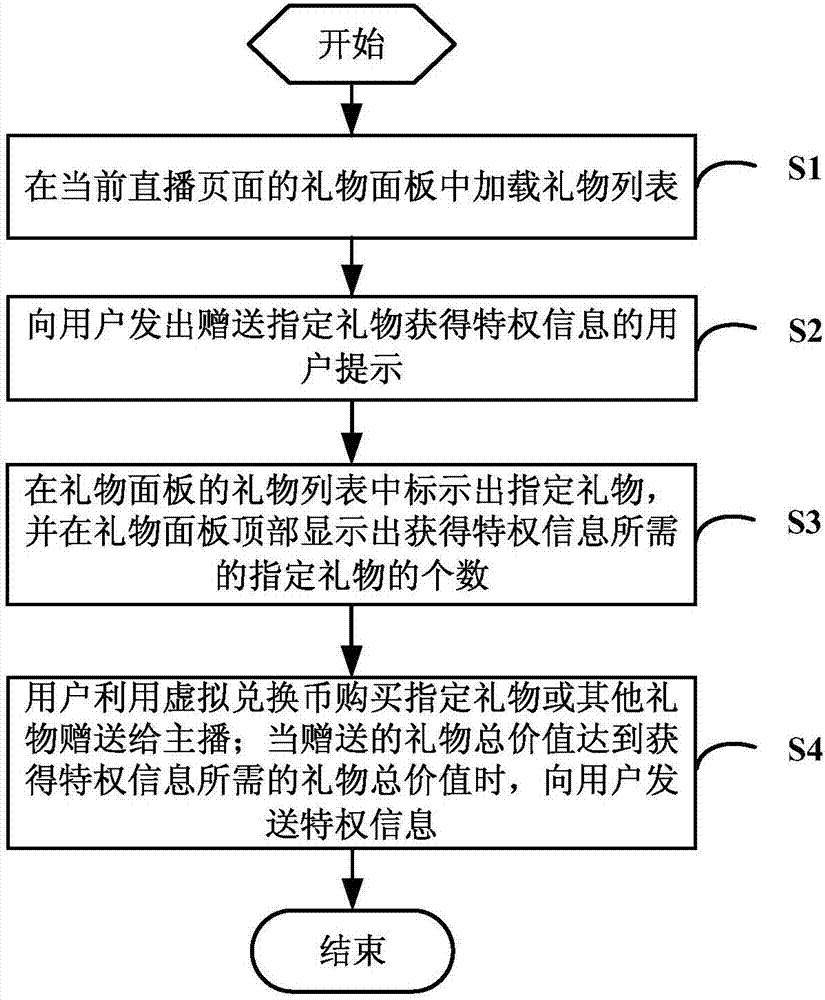

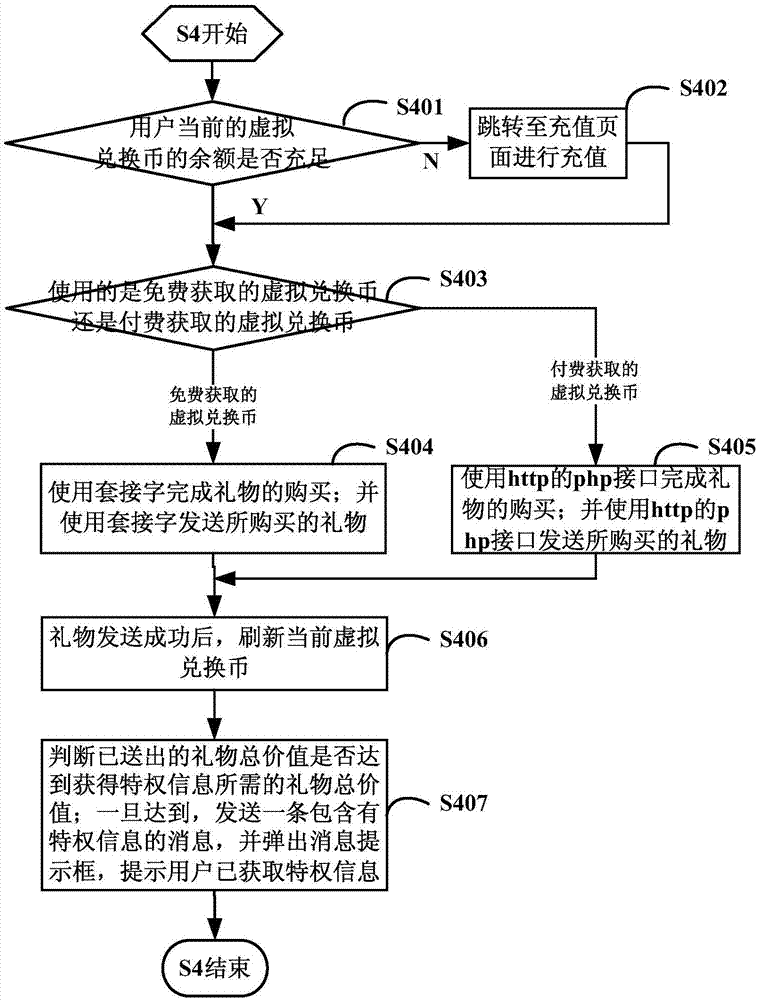

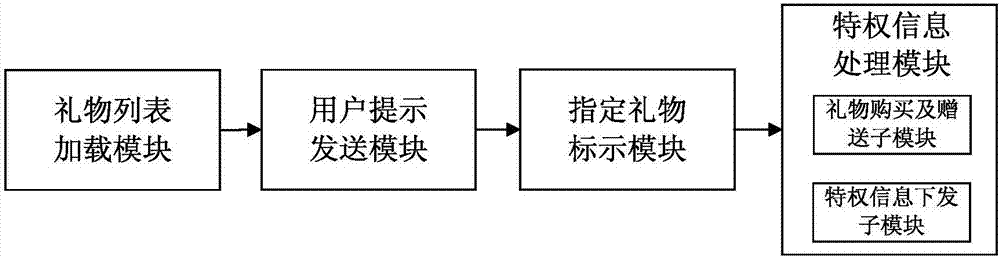

Implementation method and system for obtaining privilege information in live streaming

ActiveCN106911968AIncrease willingness to payMeet interaction needsTransmissionSelective content distributionThe InternetComputer science

The invention discloses an implementation method and system for obtaining privilege information in live streaming and belongs to the Internet video live streaming technical field. The implementation method includes the following steps that: a gift list is loaded in the gift panel of a current live streaming page; a user prompt indicating that a user can obtain privilege information through giving specified gifts is sent to the user; and the specified gifts are marked in the gift list of the gift panel, and the number of the specified gifts required by obtaining the privilege information is displayed at the top of the gift panel; and the user uses virtual conversion currencies to purchase the specified gifts or other gifts so as to give the gifts to an anchor, when the total value of the given specified gifts or other gifts reaches the total value of the gifts required by obtaining the privilege information, the privilege information is sent to the user. With the implementation method and system of the invention adopted, a concrete realization scheme is provided for narrowing the distance between the anchor and the user, and interaction demands of the paying user can be satisfied, and the willingness of the user to pay is improved.

Owner:WUHAN DOUYU NETWORK TECH CO LTD

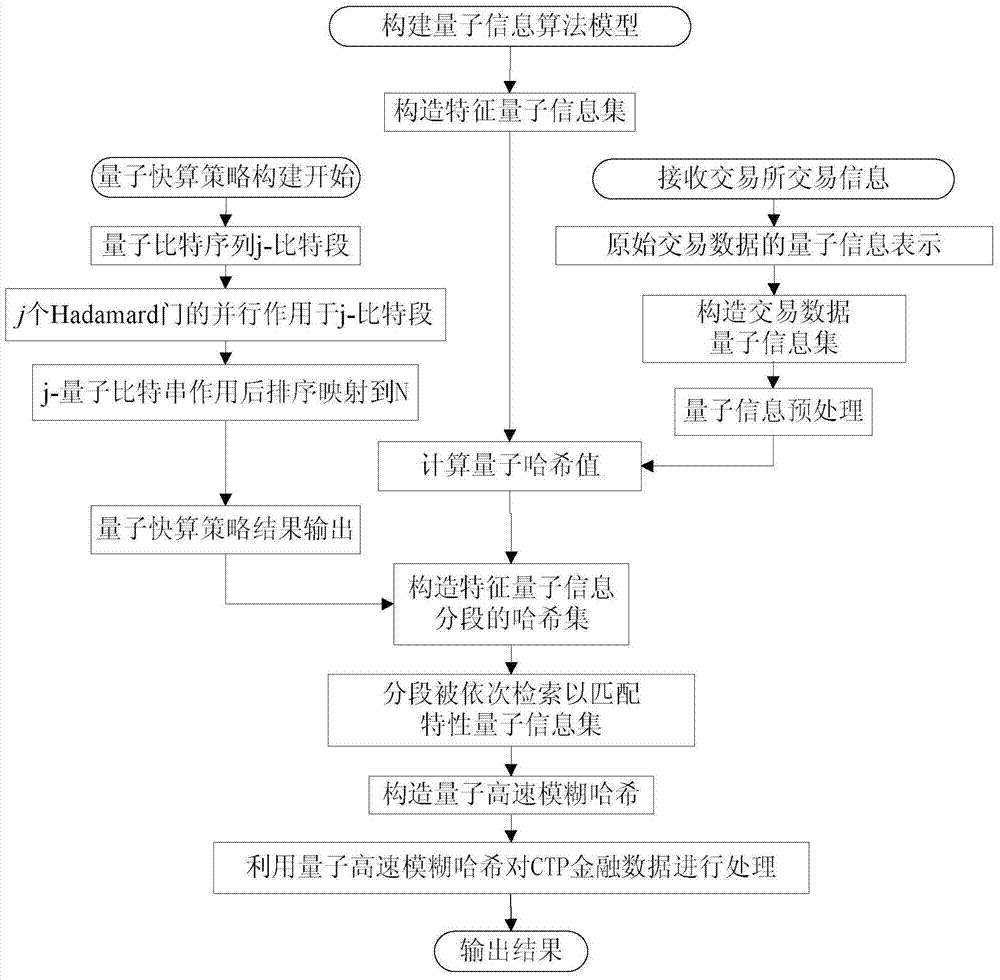

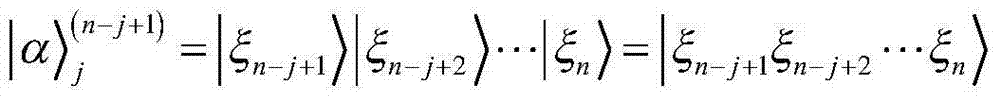

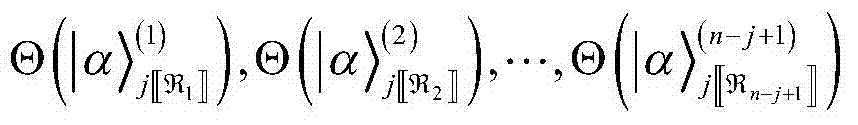

Quantum information feature extraction method based on CTP financial data

ActiveCN104504601AImplement featuresReduce computational complexityFinanceComputation complexityFeature extraction

The invention discloses a quantum information feature extraction method based on CTP financial data. Data issued by an exchange is processed by means of a quantum information algorithm model, a superposed-state quantum information presentation mode is firstly adopted to effectively describe the diversity of transaction data, description and processing by means of a quantum algorithm are facilitated on the basis, the data processing capacity of a quantum information algorithm model established on the basis of a quantum quick-calculation strategy and a quantum high-speed fuzzy hash method is improved remarkably, the calculation complex of the model is reduced remarkably, response delay is effectively reduced, the calculation complex of the algorithm is reduced, the response delay is reduced, and feature extraction and feature classification of the CTP financial data are achieved on the basis of the quantum information algorithm model.

Owner:上海卡方信息科技有限公司

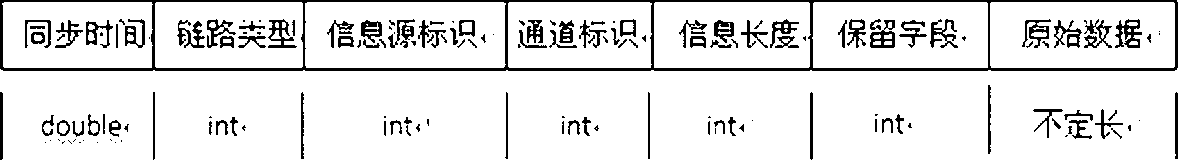

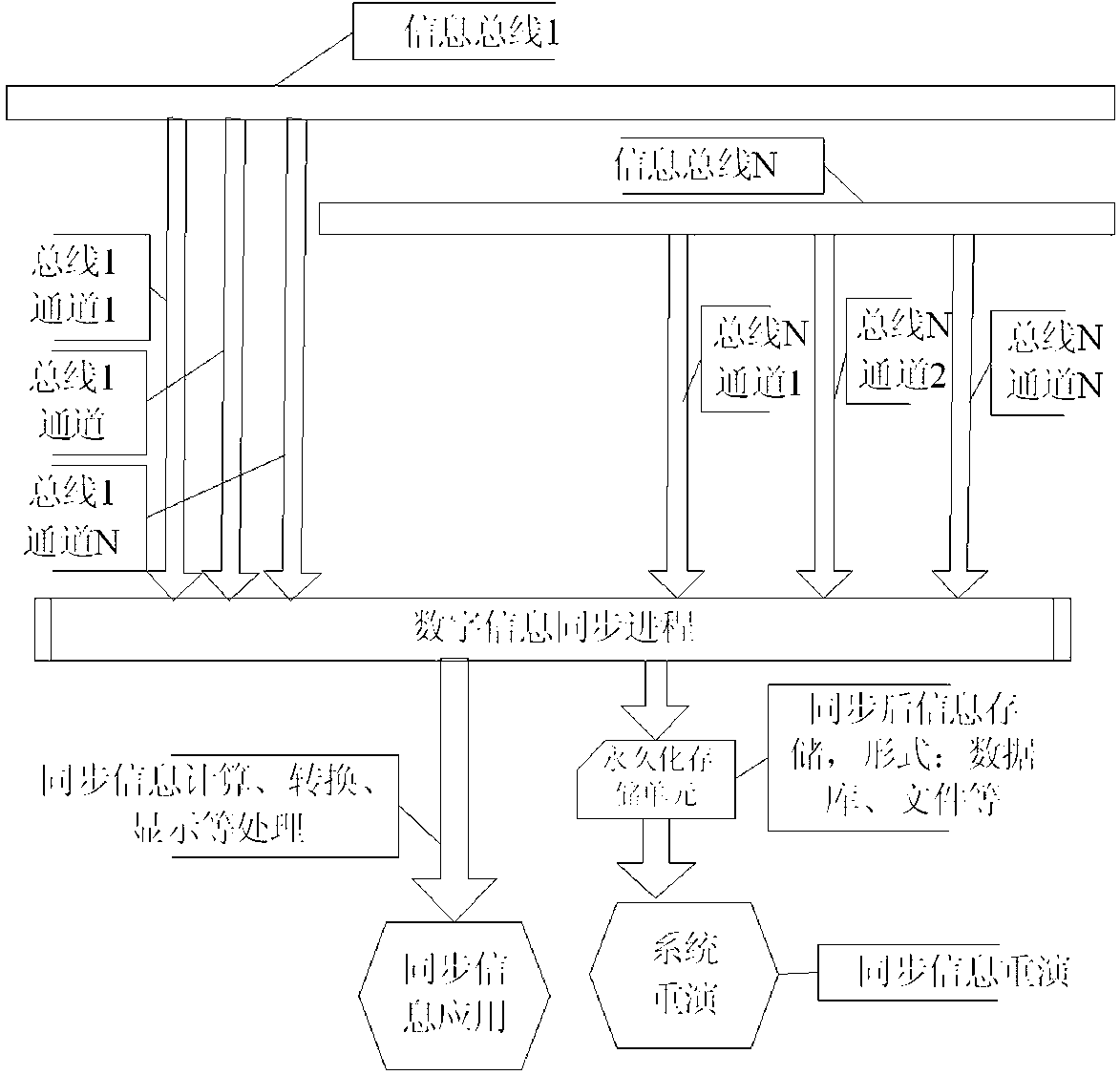

Information system synchronous data processing method utilizing secondary buffer technology

ActiveCN103023809AGood synchronization adaptabilityExport Designs UnrestrictedError preventionData switching networksData synchronizationData format

An information system synchronous data processing method utilizing secondary buffer technology. The method includes the steps of firstly, using uniform data format to package data in information channels, and processing frame header packaging information to realize mapping of synchronous data with corresponding information channels of the synchronous data; secondly, using multithread data synchronization method, which realizes data synchronization of high-speed multi-channel information, of a secondary buffer processing mechanism; and using and processing data after information data synchronization. The method has the advantages that the method is fine in data synchronization adaptability, better in synchronization performance, more reliable and stable, high in data synchronization precision, fine in data synchronization independence, high in reducibility, and transparent to users.

Owner:NO 709 RES INST OF CHINA SHIPBUILDING IND CORP

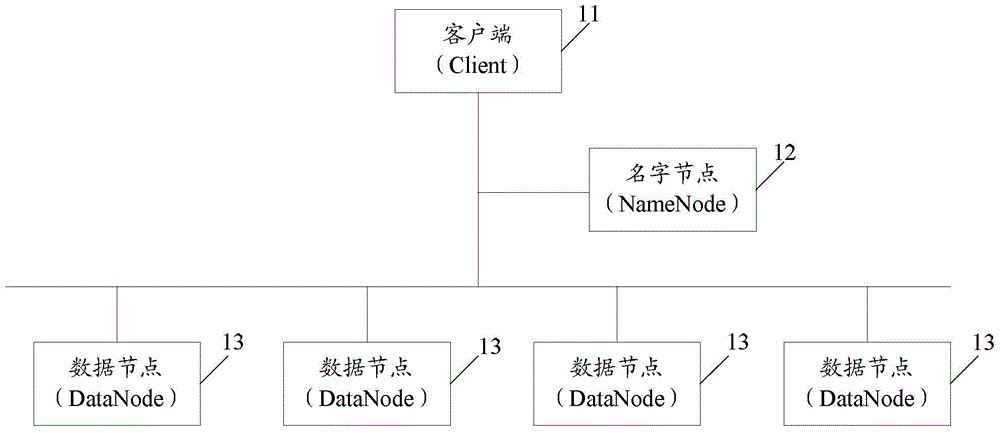

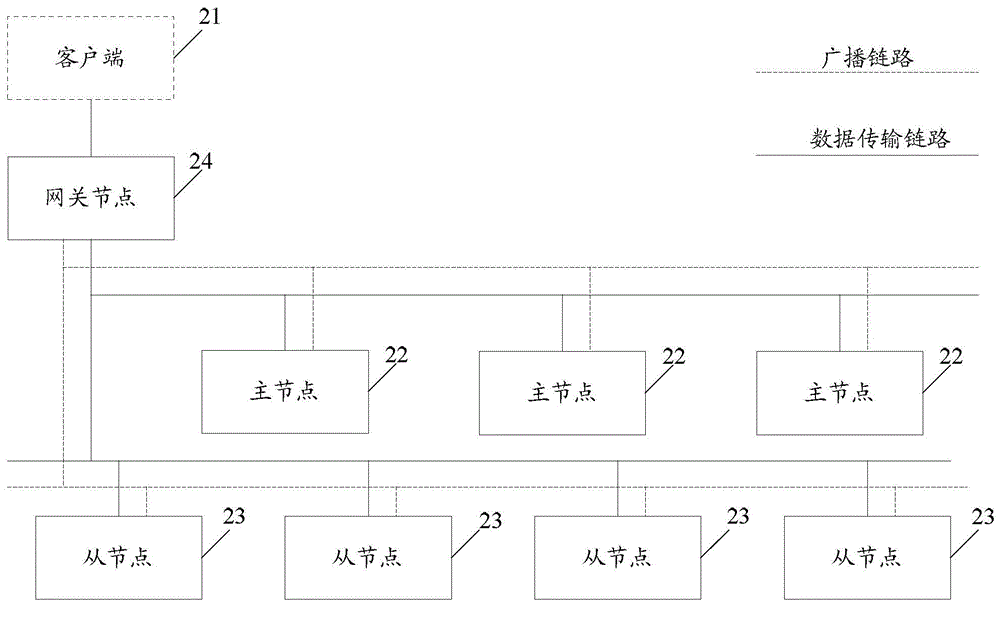

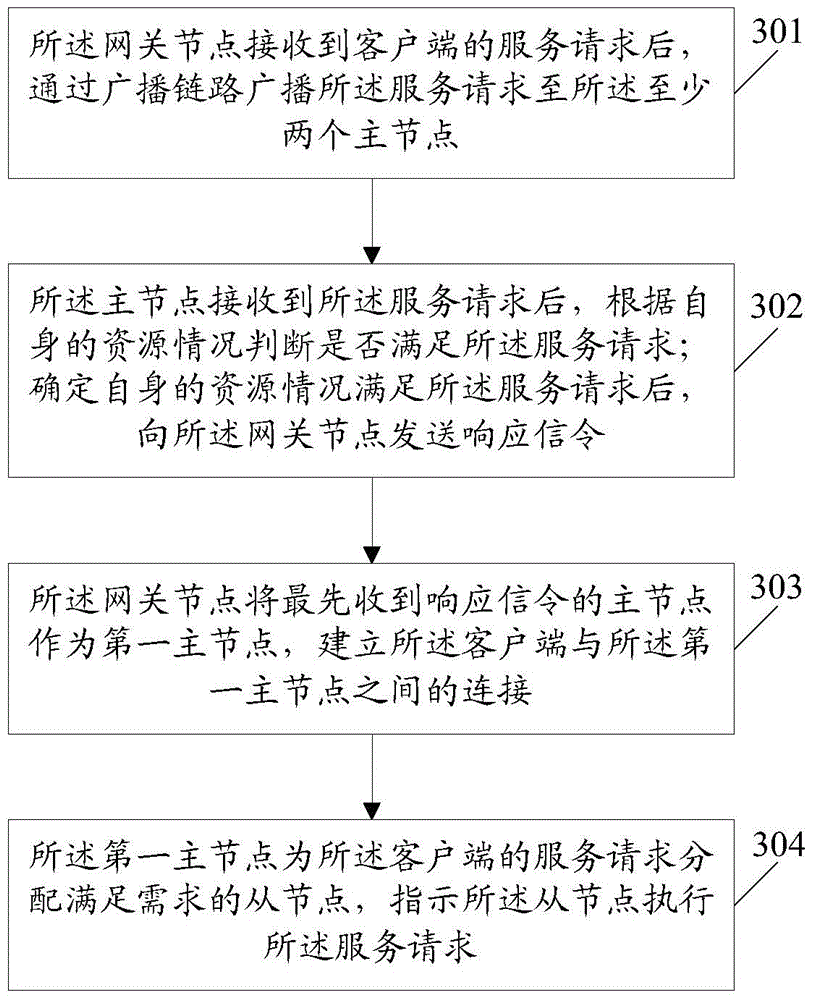

Hadoop cluster system and data processing method

ActiveCN105824810AImprove securityImprove data processing capabilitiesTransmissionSpecial data processing applicationsClient-sideCluster systems

The embodiment of the present invention discloses a Hadoop cluster system and a data processing method; the system includes: a gateway node, at least two master nodes and at least two slave nodes; the gateway node is configured to receive a service request from a client , broadcasting the service request to the at least two master nodes through a broadcast link, and using the master node that received the response signaling first as the first master node; and also used to establish the relationship between the client and the first A connection between master nodes; the master node is configured to judge whether the service request is satisfied according to its own resource conditions after receiving the service request broadcast by the gateway node; determine that its own resource conditions satisfy the service request After the request, send a response signaling to the gateway node; it is also used to allocate a slave node that meets the requirements for the service request of the client after establishing a connection with the client through the gateway node, and instruct the slave node to execute The service request.

Owner:HANDAN BRANCH OF CHINA MOBILE GRP HEBEI COMPANYLIMITED

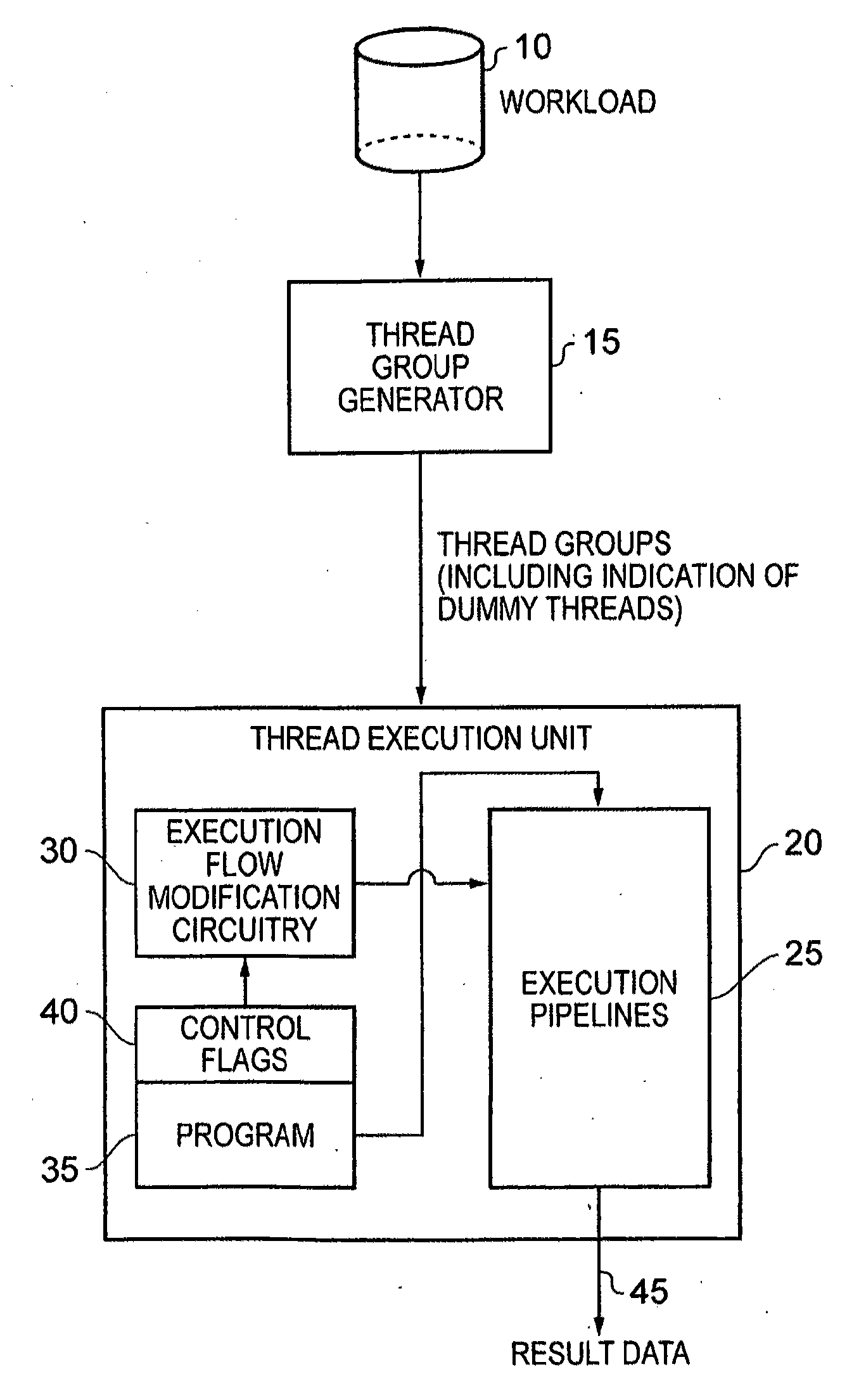

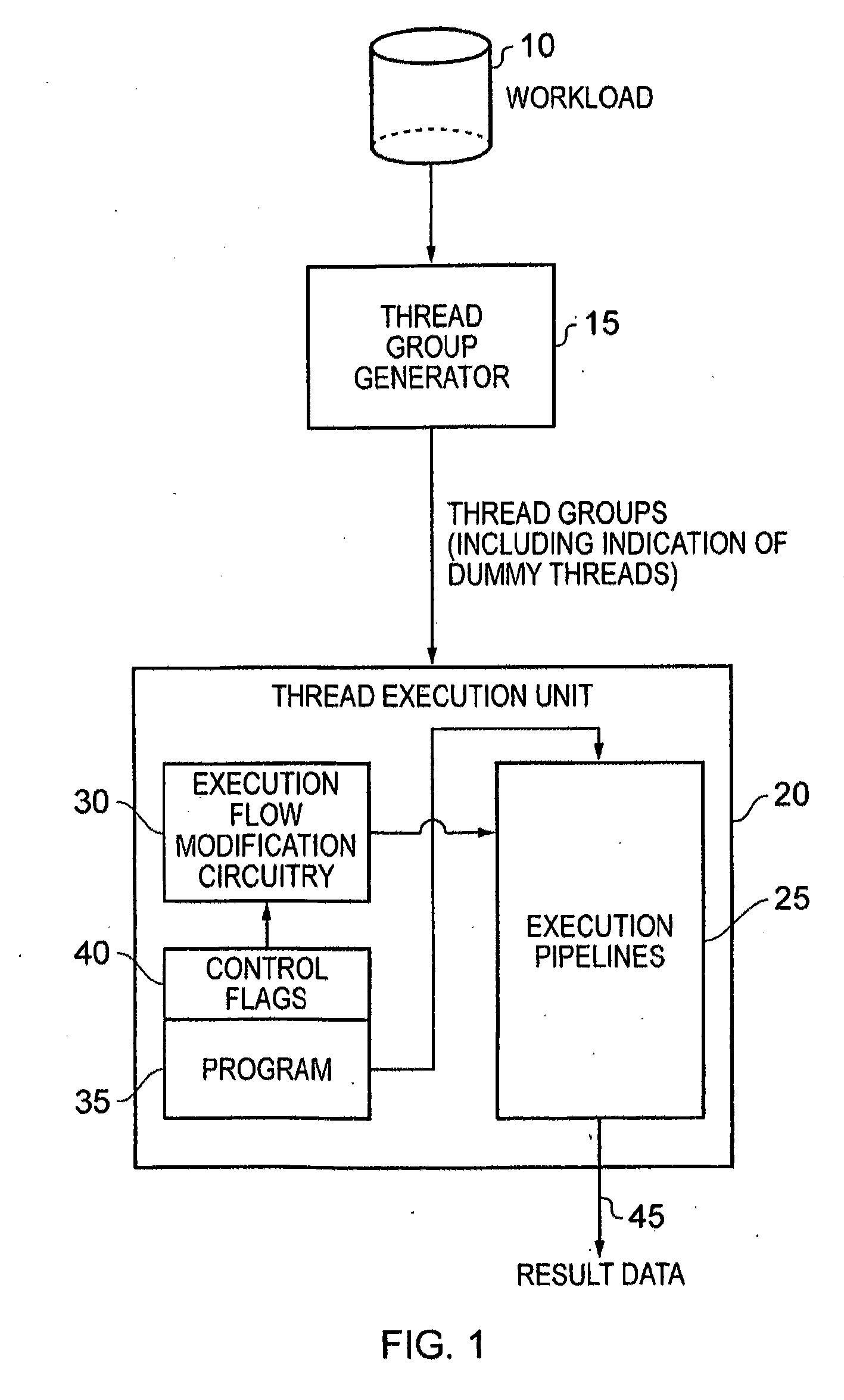

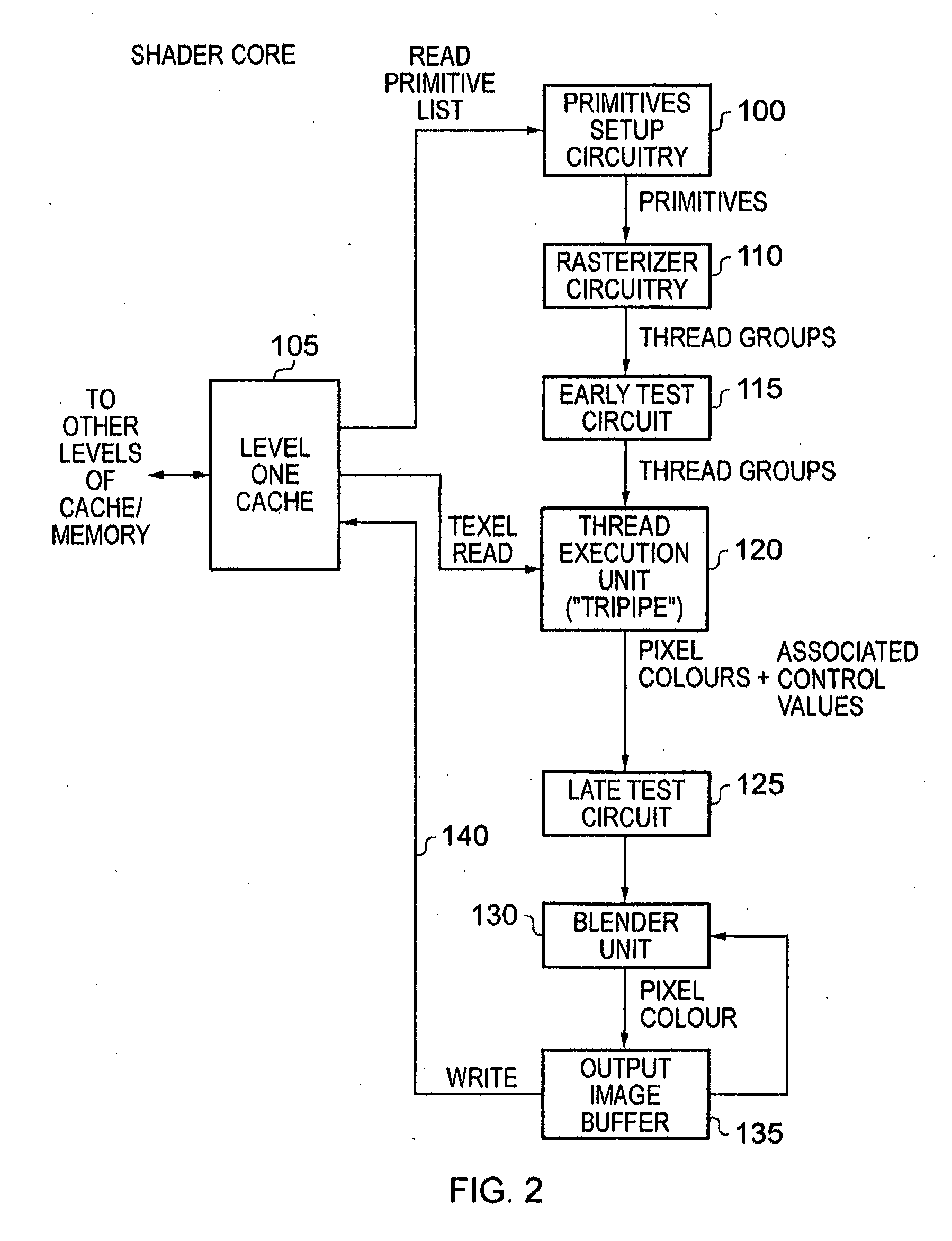

Data processing apparatus and method for processing a received workload in order to generate result data

ActiveUS20120304194A1Reduce calculationResourceEnergy efficient ICTMultiprogramming arrangementsGraphicsProgram instruction

A data processing apparatus and method are provided for processing a received workload in order to generate result data. A thread group generator generates from the received workload a plurality of thread groups to be executed to process the received workload. Each thread group consists of a plurality of threads, and at least one thread group has an inter-thread dependency existing between the plurality of threads. Each thread may be either an active thread whose output is required to form the result data, or a dummy thread required to resolve the inter-thread dependency for one of the active threads but whose output is not required to form the result data. The thread group generator identifies for each thread group any dummy thread within that thread group. A thread execution unit then executes each thread within a thread group received from the thread group generator by executing a predetermined program comprising a plurality of program instructions. Execution flow modification circuitry is responsive to the received thread group having at least one dummy thread, to cause the thread execution unit to selectively omit at least part of the execution of at least one of the plurality of instructions when executing each dummy thread, in dependence on control information associated with the predetermined program. In one particular embodiment the received workload is a graphics rendering workload and the thread execution unit performs graphics rendering operations in order to generate as the result data pixel values and associated control values. Such an approach can yield significant improvements in performance, as well as reducing power consumption.

Owner:ARM LTD

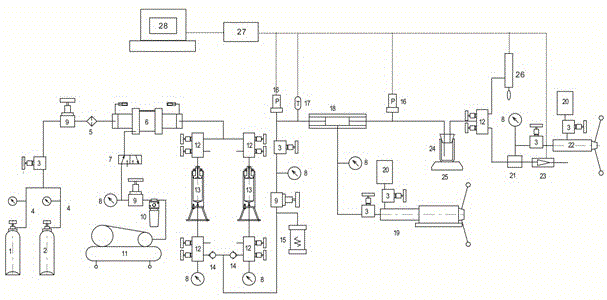

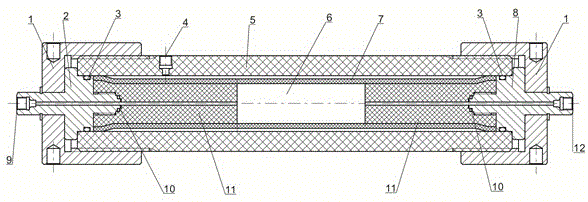

Instrument for measuring relative permeability of low permeability reservoir using nuclear magnetic resonance

ActiveCN105606517AReduce penetrationRelative Permeability of Low Permeability ReservoirsPermeability/surface area analysisData displayPermeability measurements

The invention discloses an instrument for measuring the relative permeability of a low permeability reservoir using nuclear magnetic resonance. The instrument comprises hardware and software, wherein the hardware comprises a non-magnetic rock sample clamp, a pressure-bearing container, a gas drying device, an electronic balance and a gas flow measurement device; and the software comprises a communication acquisition module, a data arrangement module, a data display module, a data recording module, an experiment process control module and a data exporting module. The instrument can be used for a measurement experiment of the relative permeability of gas and water of a non-conventional reservoir and can accurately provide experimental parameters to achieve the aim of dynamically monitoring the fluid distribution and the flowing rule.

Owner:CHINA UNIV OF GEOSCIENCES (BEIJING)

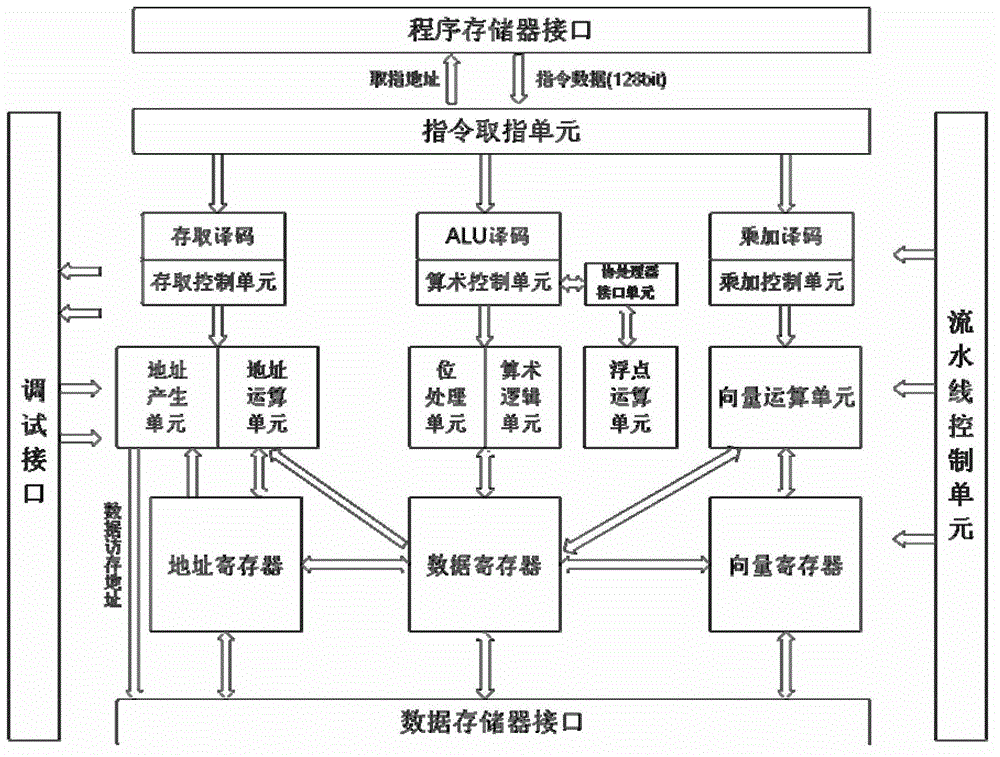

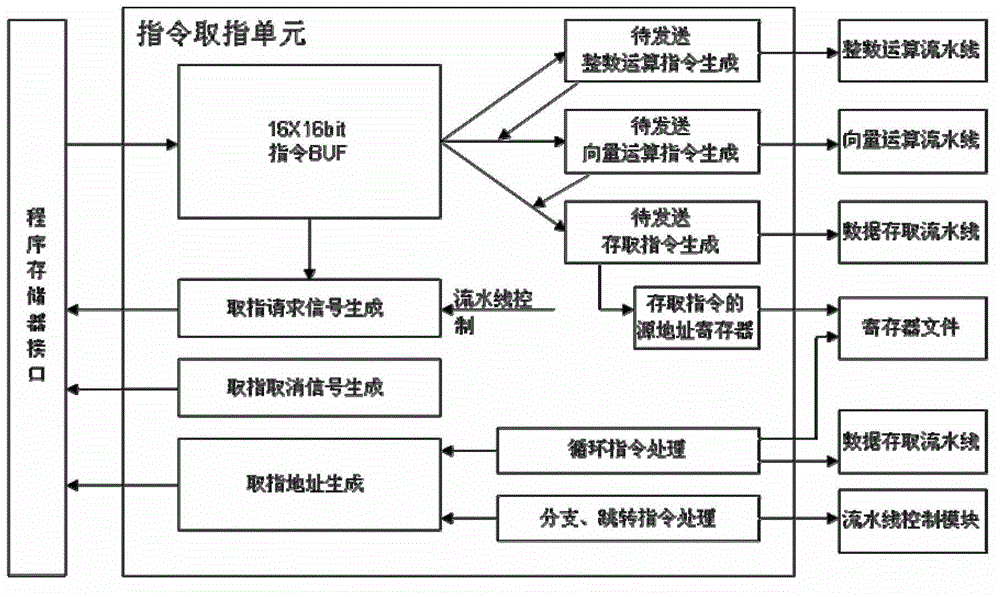

32-Bit triple-emission digital signal processor supporting SIMD

ActiveCN102750133ASupport operationReduce power consumptionConcurrent instruction executionMemory interfaceData access

The invention discloses a 32-bit triple-emission digital signal processor supporting SIMD (Single Instruction Multiple Data), comprising three flow lines in parallel emission: a data access flow line, an integer arithmetic flow line and a vector arithmetic flow line, wherein each flow line is provided with an independent decoding and execution unit and supports SIMD operation. The 32-bit triple-emission digital signal processor supporting SIMD is mainly composed of a program memory interface unit, a data memory interface unit, an instruction fetch unit, a flow line control unit, a system bus, a data access flow line unit, an integer arithmetic flow line unit, a vector arithmetic flow line unit, a data register, an address register, a vector register, a coprocessor interface unit and a floating point arithmetic unit, all of which are connected together through a circuit. The 32-bit triple-emission digital signal processor supporting SIMD supports parallel execution of three flow lines so that the parallel processing capability of a DSP (Digital Signal Processor) is improved; besides, the 32-bit triple-emission digital signal processor supports parallel execution four groups of 16-bit multiplying and adding operations in a single cycle, and supports simultaneous execution of the operation of five groups of data and the access operation of one group of data; therefore, the data processing capability of the DSP is enhanced.

Owner:58TH RES INST OF CETC

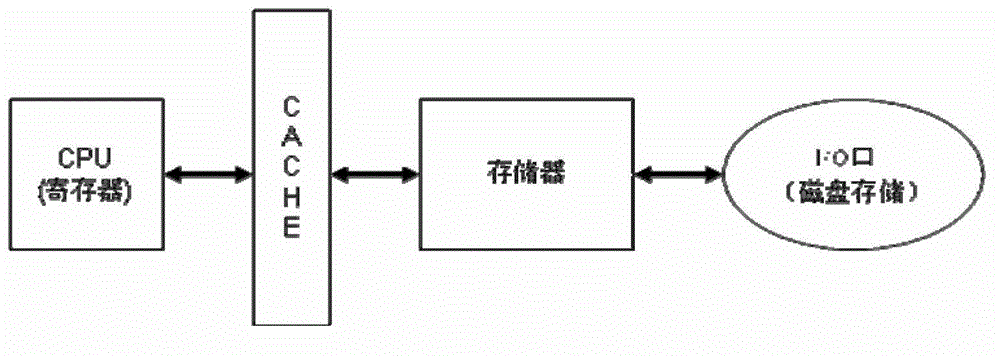

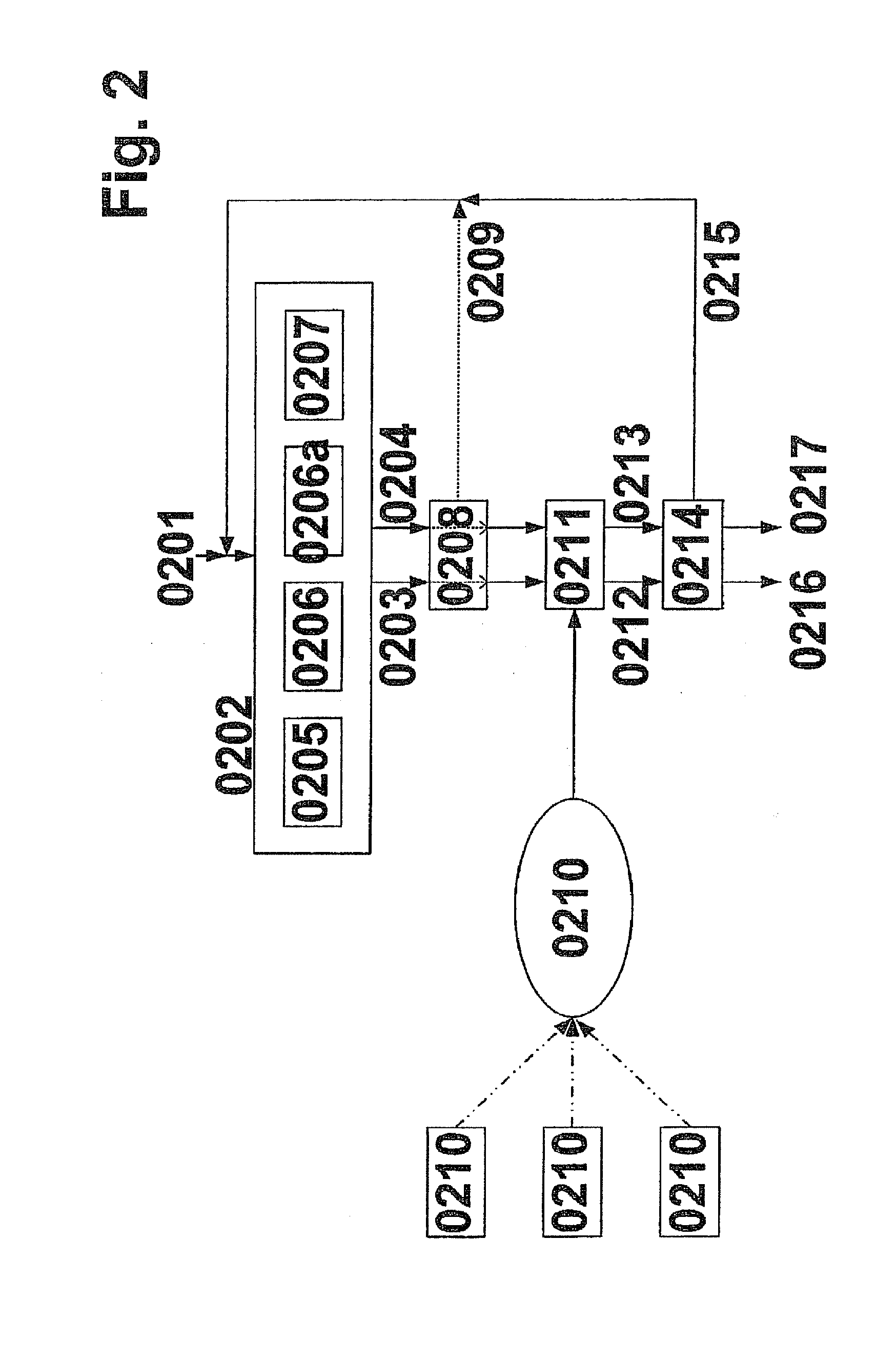

Method for increasing the data processing capability of a computer system

ActiveUS20070288769A1Improve data processing capabilitiesOptimize data processingEnergy efficient ICTDigital data processing detailsComputerized systemParallel computing

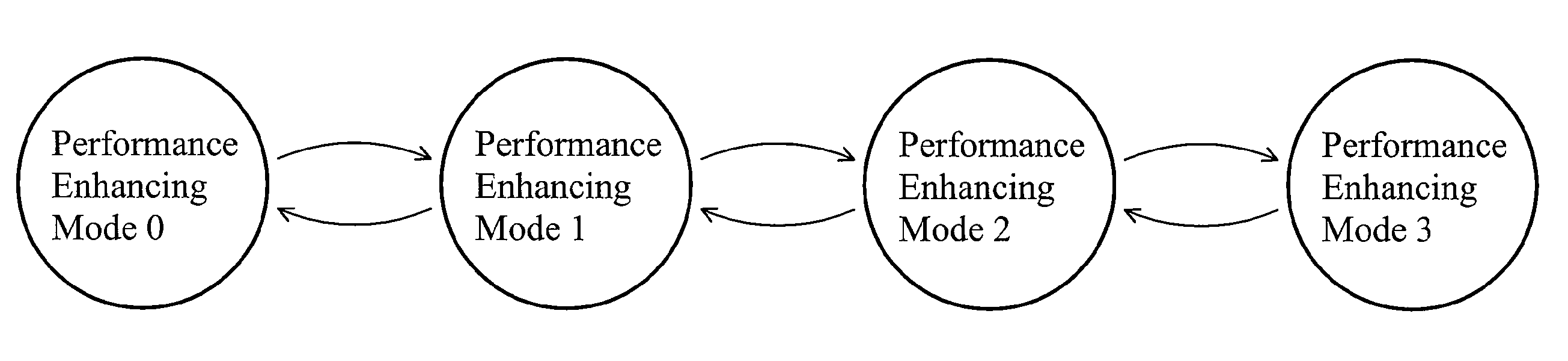

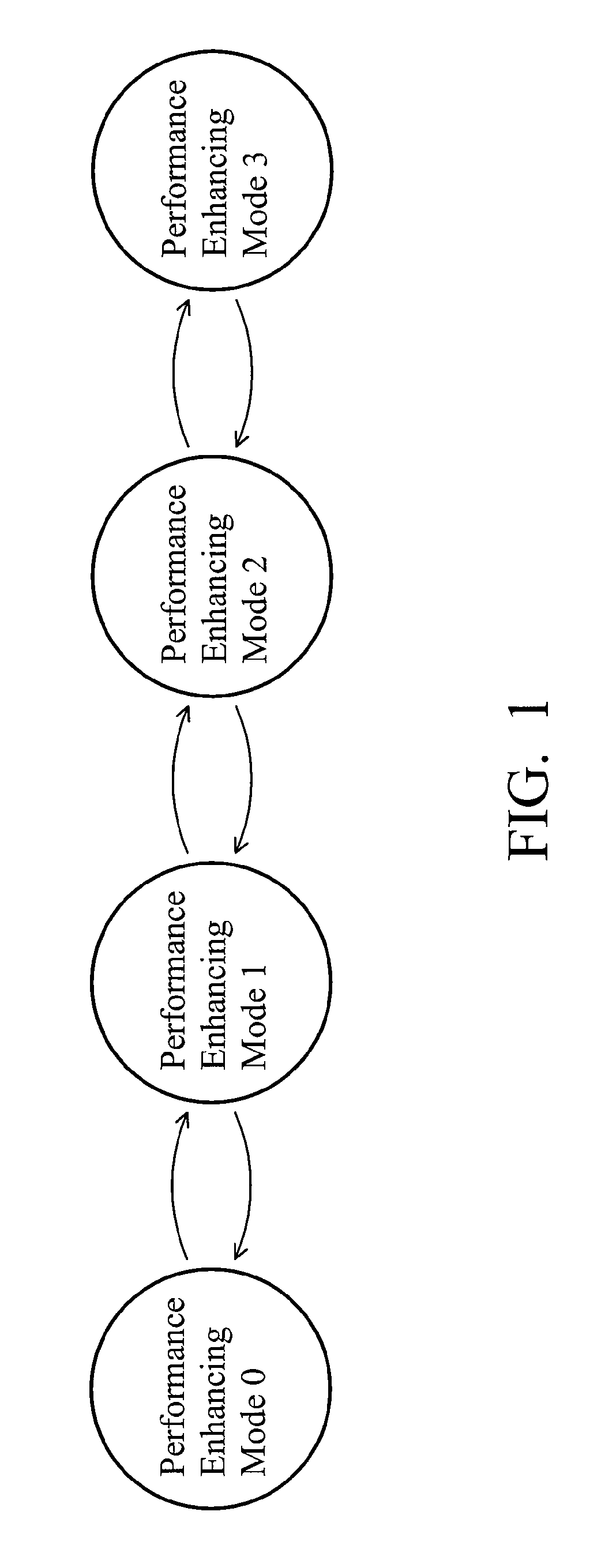

A method for dynamically increasing the data processing capability of a computer system is provided. The computer system comprises a processor, a memory and a chipset. The data processing capability of the computer system is classified into a predetermined number of performance enhancing modes. At least one performance enhancing mode transition condition is checked to determine whether to automatically raise the performance enhancing mode of the computer system. The processor is suspended from using the processor bus during the transition of the performance enhancing mode of the computer system. The performance enhancing mode of the computer system is raised by increasing a first working frequency of the processor, a second working frequency of the processor bus and a third working frequency of the memory. The data processing rate of the computer system is further increased when the performance enhancing mode of the computer system is further raised.

Owner:VIA TECH INC

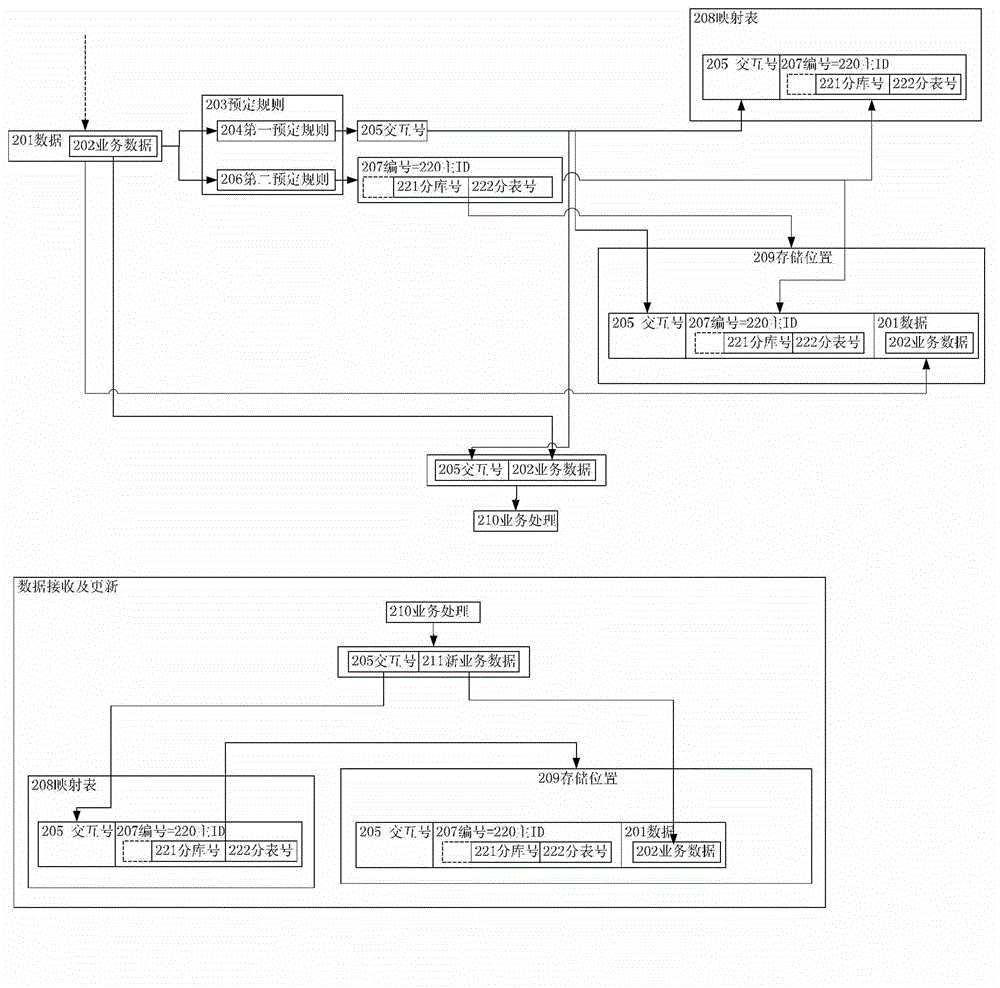

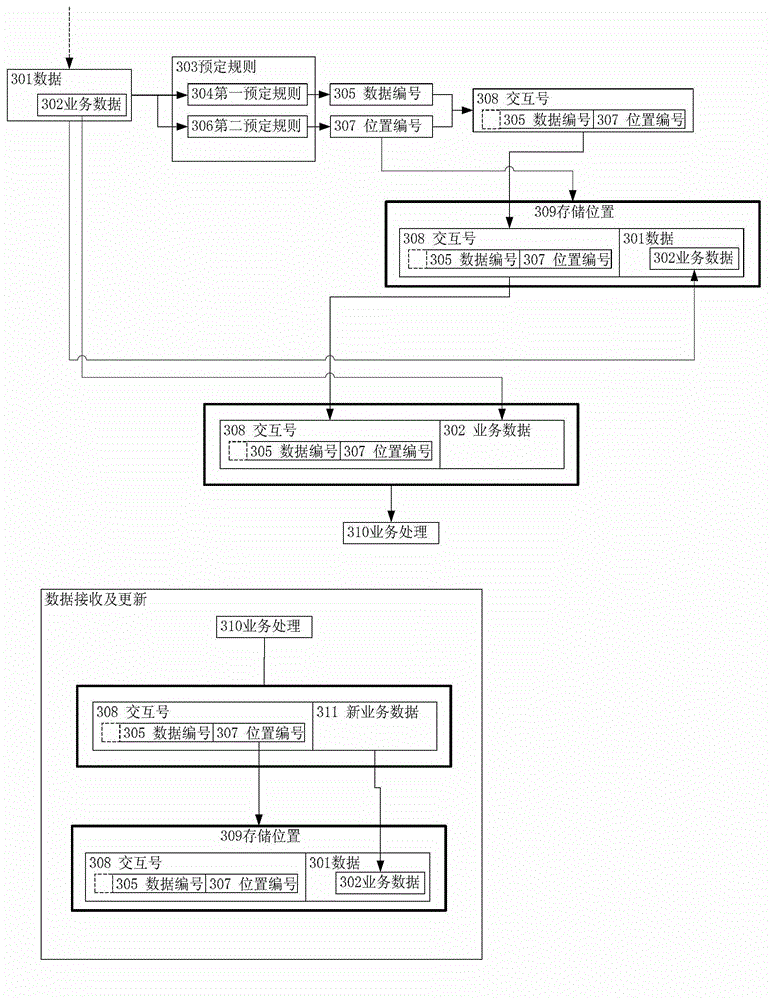

Data processing method

ActiveCN103942209AReduce overheadAvoid scanningDatabase distribution/replicationSpecial data processing applicationsDatabaseSerial code

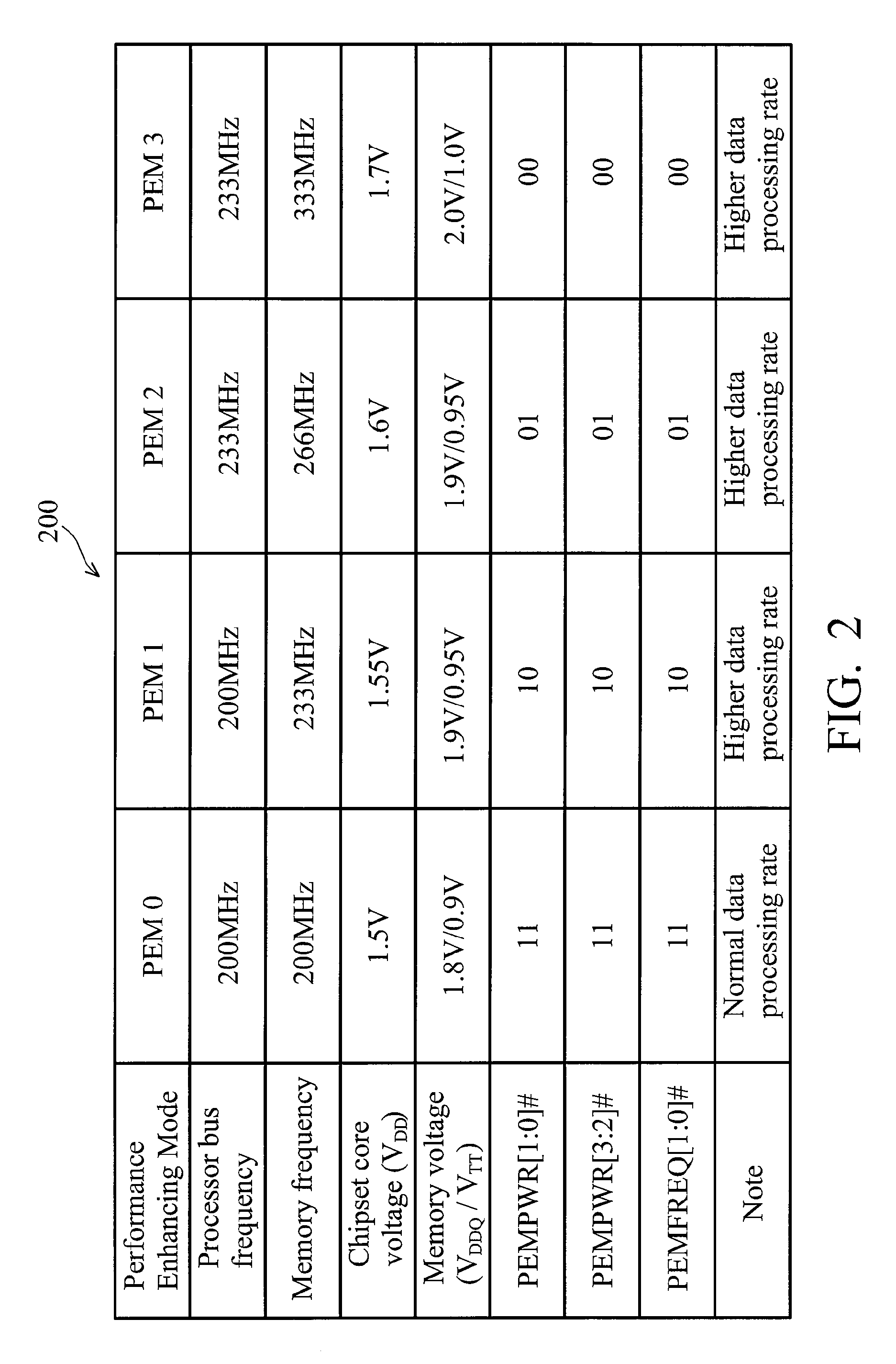

The invention provides a data processing method. The method includes the steps that one of one or more items of data including service data is obtained, wherein the one or more items of data wait for service processing; according to a preset rule, an interaction number and a serial number corresponding to the interaction number are generated for one item of data; a mapping table is established for generating a mapping relation between the interaction number and the serial number; one item of data, the interaction number and the serial number are stored at storage positions in a sub-library and a sub-table in a main database, wherein the sub-library and the sub-table correspond to the one item of data and are indicated by the serial number; the service data of the one item of data and the interaction number are sent to perform service processing. According to the method, a storage seeking mode of a distributed system is improved, the library and table where the data are located can be accurately positioned, all libraries and all tables in the database are prevented from being scanned, the overhead for the database is reduced, and the capacity for processing the data through the system is improved.

Owner:ADVANCED NEW TECH CO LTD

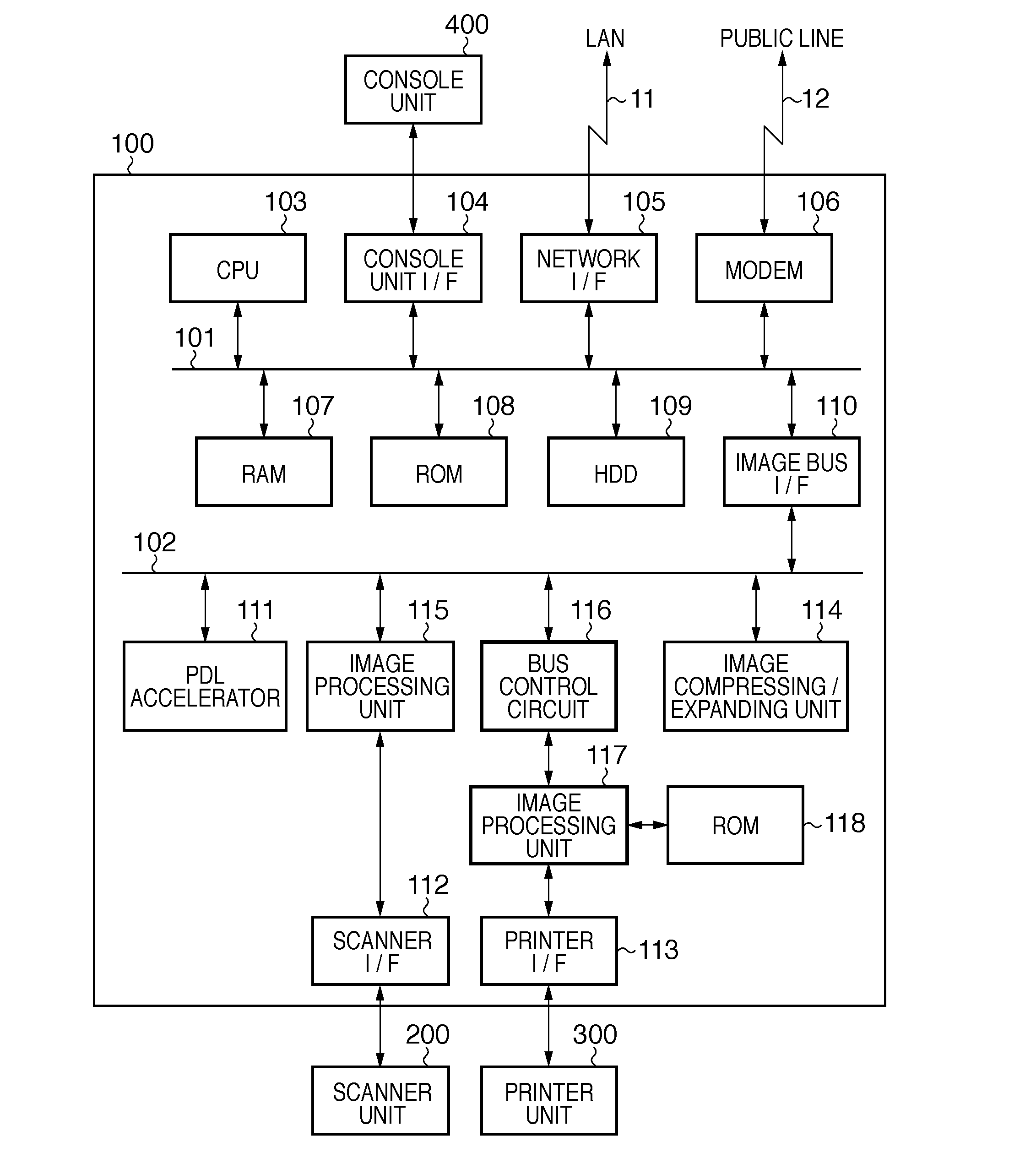

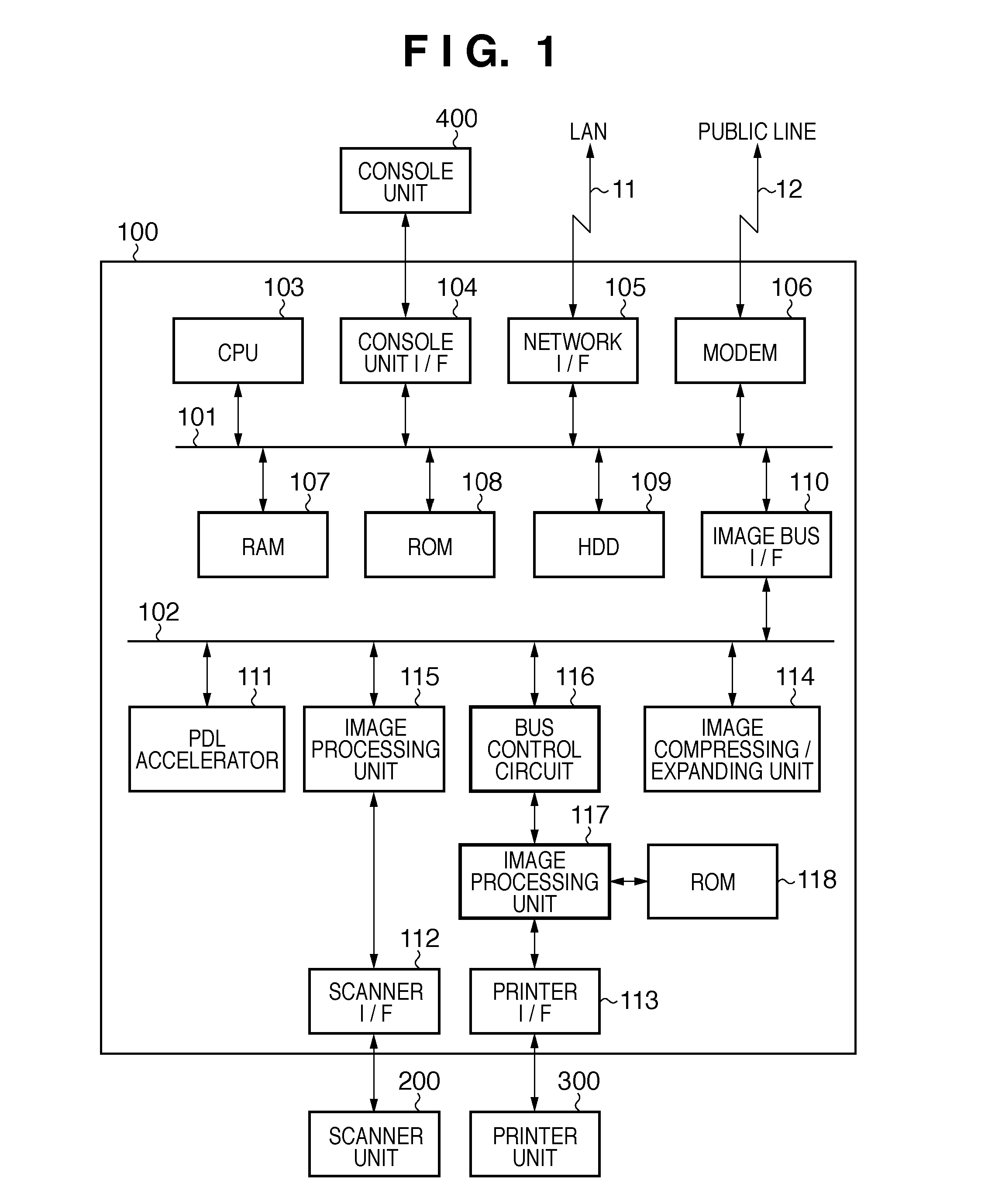

Data processing apparatus and method for controlling the apparatus

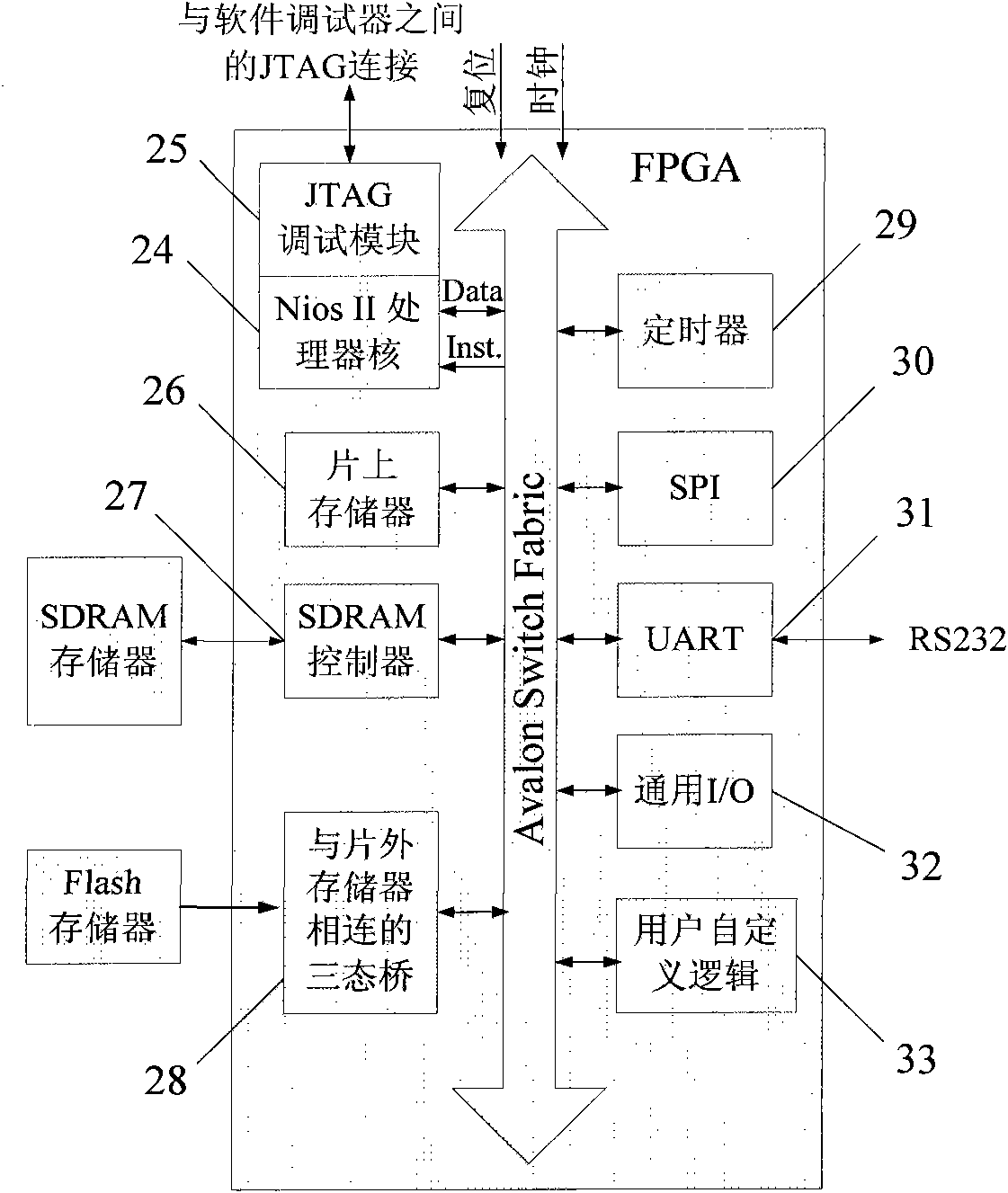

InactiveUS20110109931A1Reduce loadImprove data processing capabilitiesDigital computer detailsLogic circuits using elementary logic circuit componentsProcessor registerEmbedded system

The present invention provides a data processing apparatus having a programmable logic and a method for controlling the apparatus. If it is determined that the reconfiguration of the programmable logic is necessary, register setting data for reconfiguring the programmable logic is supplied to the programmable logic. The programmable logic reads out circuit information from a memory storing the circuit information in accordance with the register setting data and reconfigures a function of the programmable logic. A CPU transfers the register setting data to the programmable logic and then transfers data to be processed by the programmable logic whose function has been reconfigured, to the programmable logic.

Owner:CANON KK

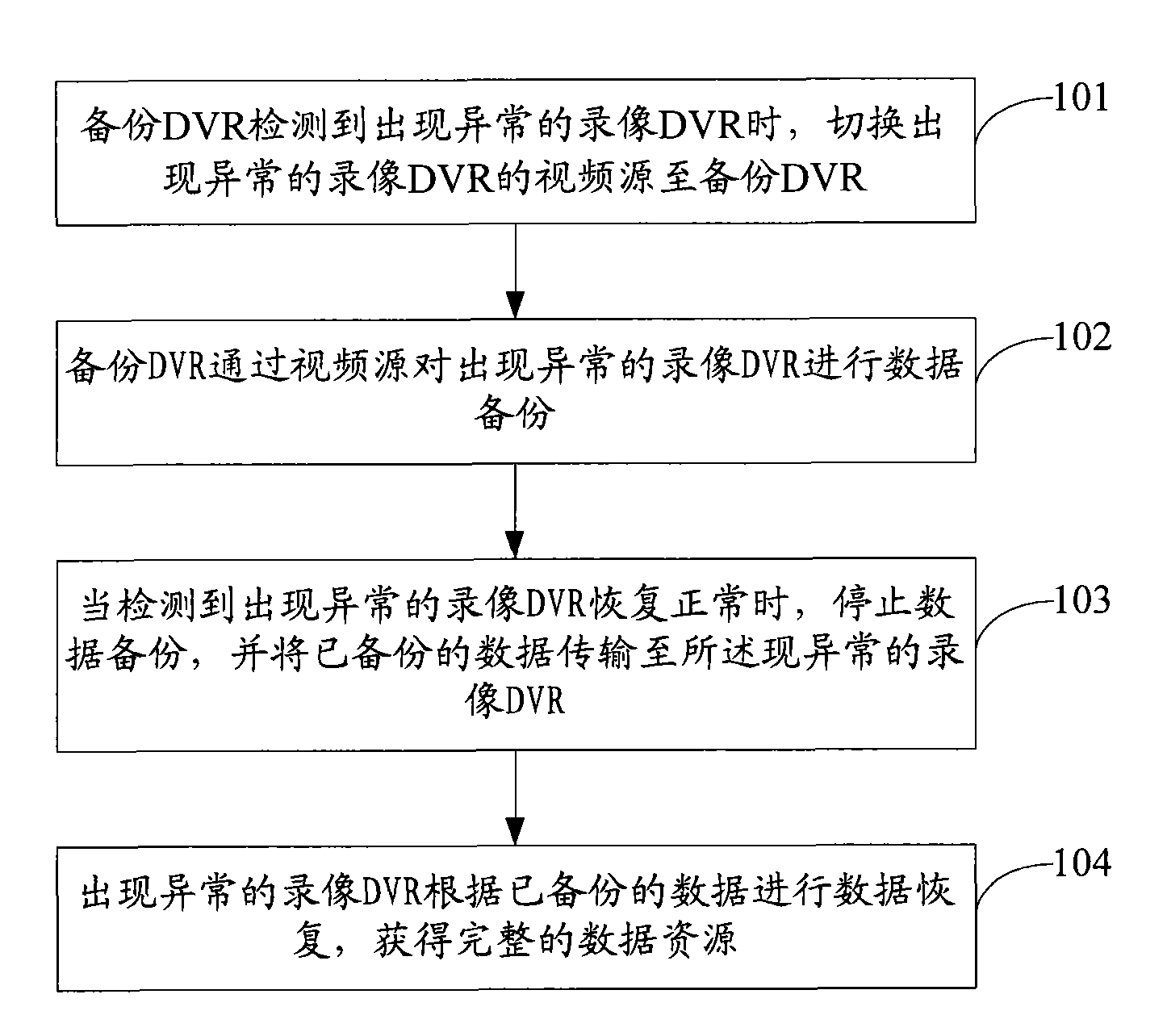

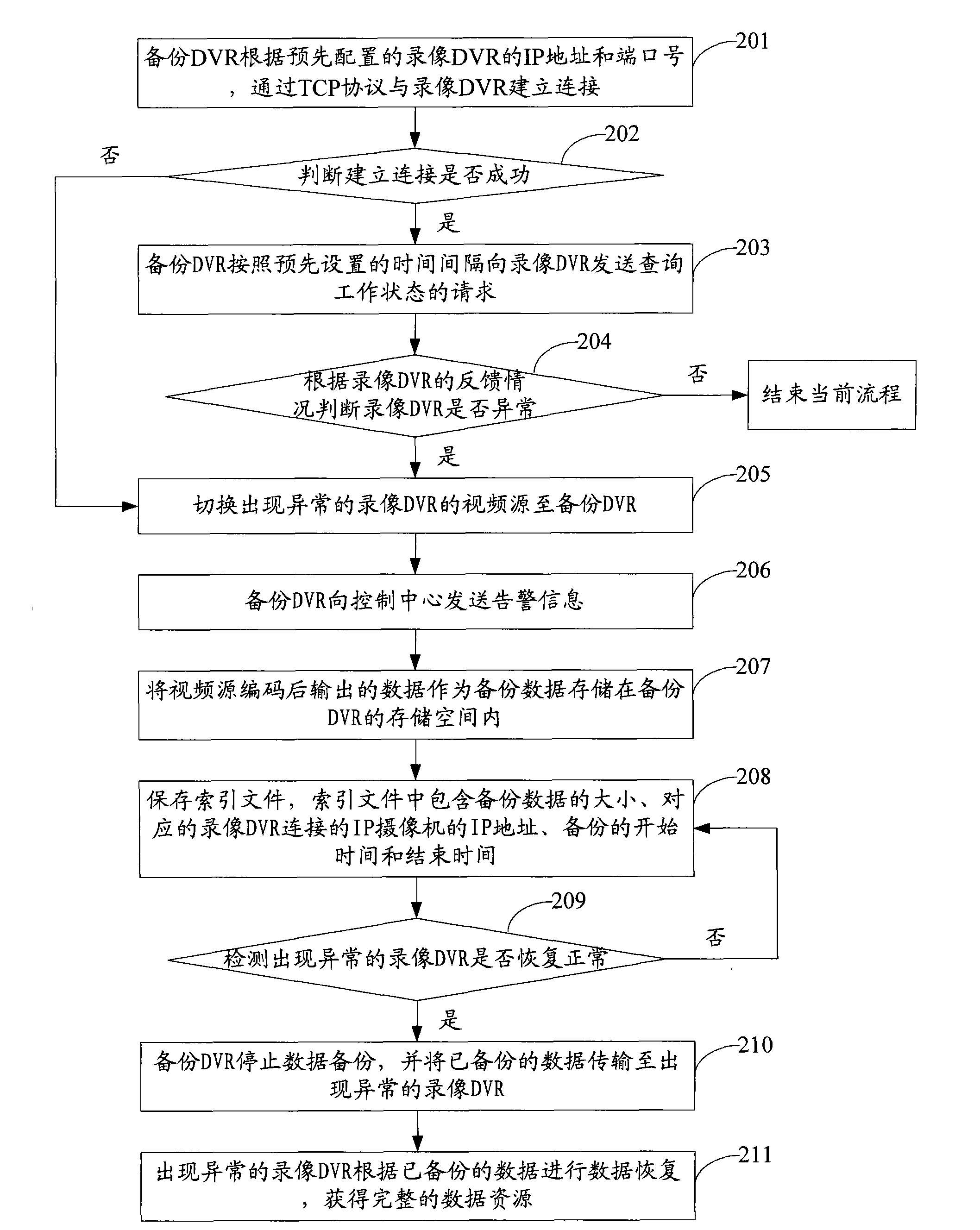

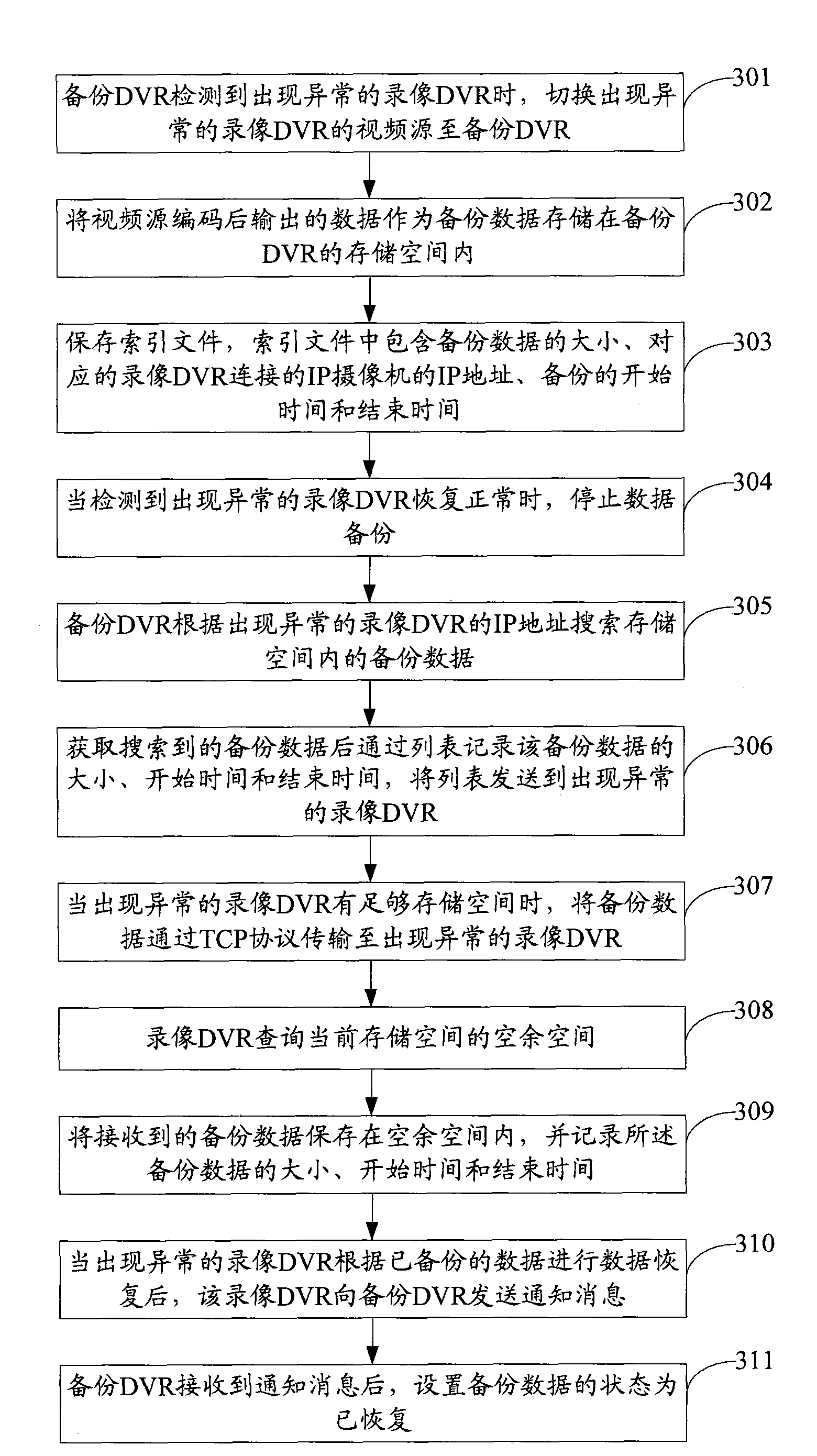

DVR (Digital Video Recorder) as well as data backup and recovery method and system thereof

ActiveCN101873462AReduce complexityImprove data processing performanceTelevision system detailsColor television detailsData transmissionDigital video

The embodiment of the invention discloses a DVR (Digital Video Recorder) as well as data backup and recovery method and system thereof, which are applied to a monitoring system comprising a backup DVR and a plurality of video DVRs, wherein the backup DVR is connected with the video DVRs. The method comprises the following steps of: when the backup DVR detects abnormal video DVRs, switching the videos of the abnormal video DVRs to the backup DVR; carrying out data backup on the abnormal video DVRs through a video source by the backup DVR; when the detected abnormal video DVRs return to normal, stopping the data backup and transmitting the backed up data to the abnormal video DVRs; and carrying out data recovery by the abnormal video DVRs according to the backed up data to obtain a complete data source. By applying the invention, the recovery of complete data can be automatically carried out according to the backup data transmitted by the backup DVR, thereby the operation complexity is reduced.

Owner:HANGZHOU HIKVISION DIGITAL TECH

Method for processing data

InactiveUS20140297948A1Efficient executionImprove data processing capabilitiesInput/output to record carriersDigital computer detailsManagement unitParallel computing

A method for operating a system on a chip comprising a conventional processor unit (CISC, RISC, VLIW, DSP) and an array processor having a multidimensional arrangement of arithmetic units. Operation information for the array processor are stored in a memory shared between the conventional processor and the array processor. At runtime the conventional processor points the array processor to the memory area comprising the operation information. A management unit inside the array processor is autonomously loading the operation information into the array processor

Owner:PACT XPP SCHWEIZ AG

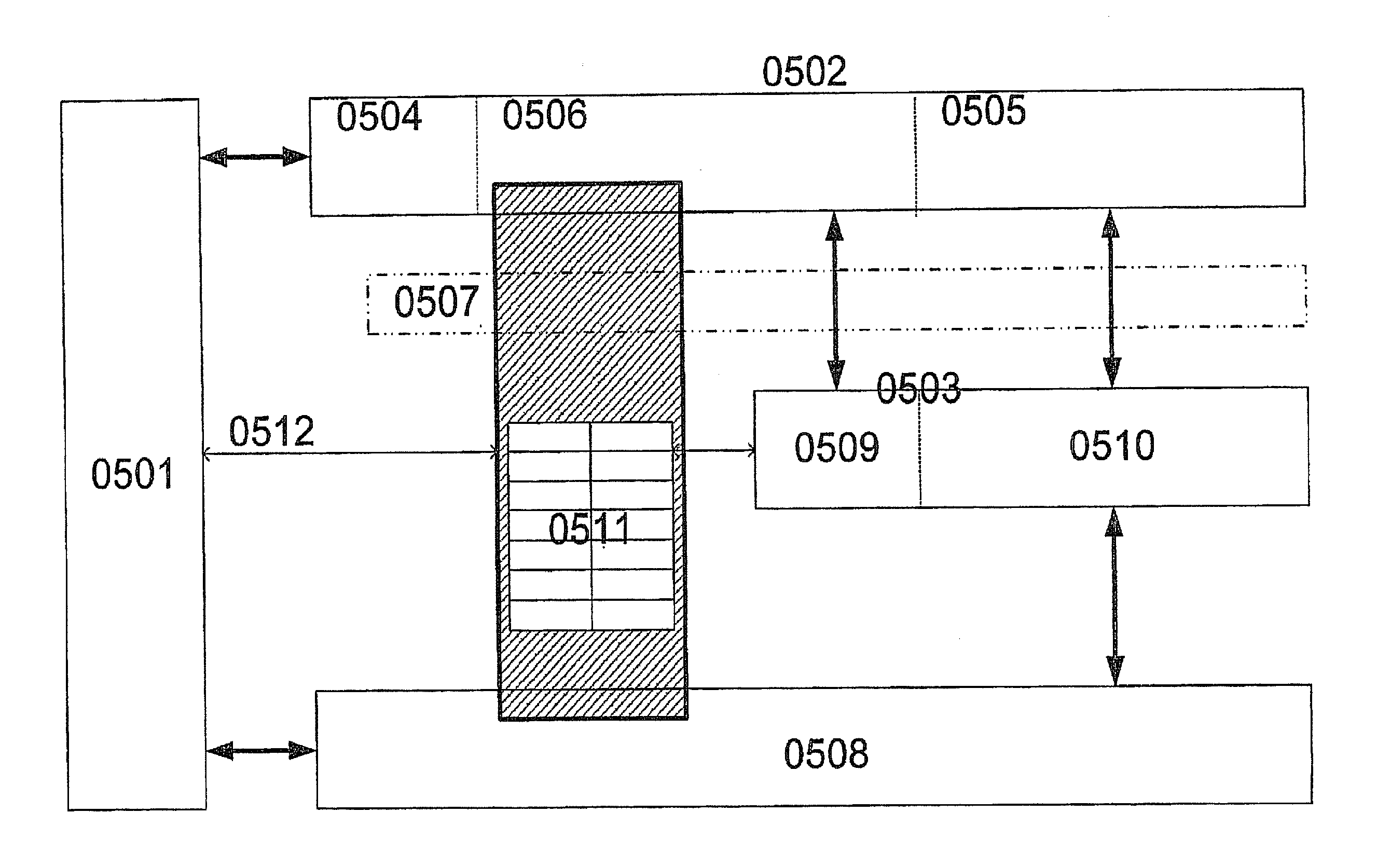

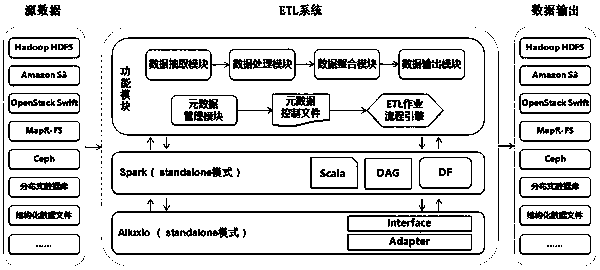

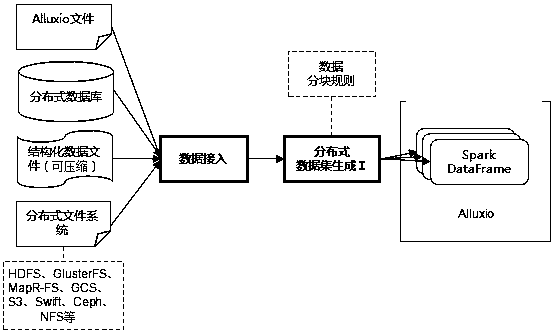

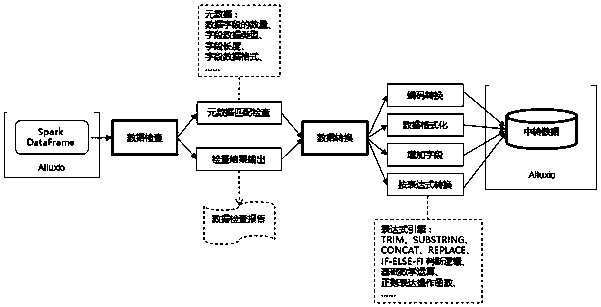

ETL system and method completely based on distributed type memory computation

InactiveCN108304538AEasy maintenanceNo programming requiredSpecial data processing applicationsDistributed memoryMetadata management

Provided is an ETL system completely based on distributed type memory computation. The system comprises five functional modules, namely the data extracting module, the data processing module, the dataintegrating module, the data outputting module and the metadata managing module, and one ETL operation procedure engine. The metadata managing module outputs a metadata control file to be used by theETL operation procedure engine. The ETL operation procedure engine reads the metadata control file, computes the number of the layer where each node is located, and conducts layering on all the operation nodes according to the layer numbers. The ETL operation procedure engine sequentially operates ETL operations of all the layers according to the executing route from the lower layer to the higherlayer and finally completes the execution of all the ETL operations in an ETL operation procedure diagram. By means of the system, based on the Spark and Alluxio technology, the elasticity of the system frame is improved, data management is simplified, and the data processing performance is improved.

Owner:广东奡风科技股份有限公司

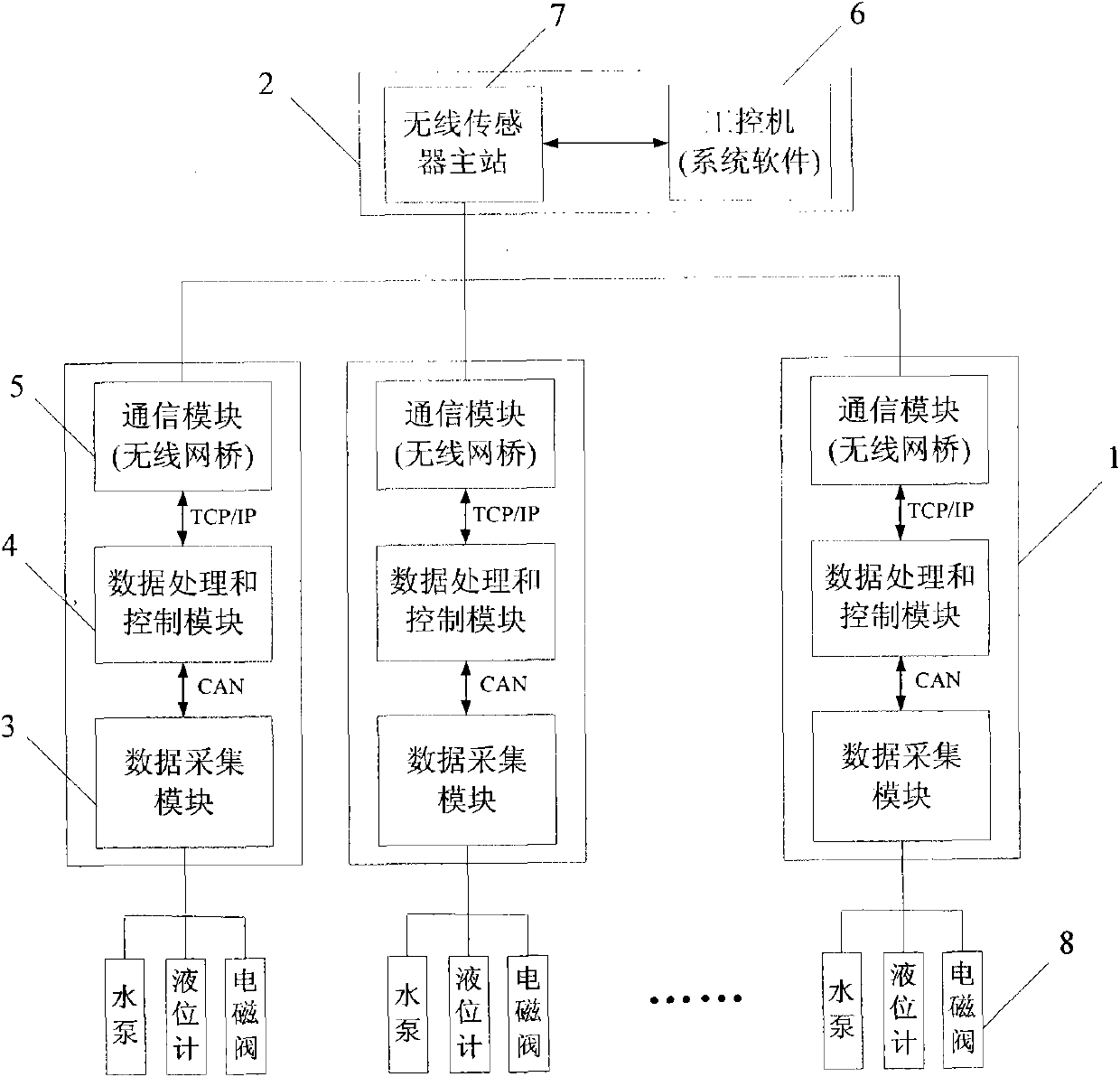

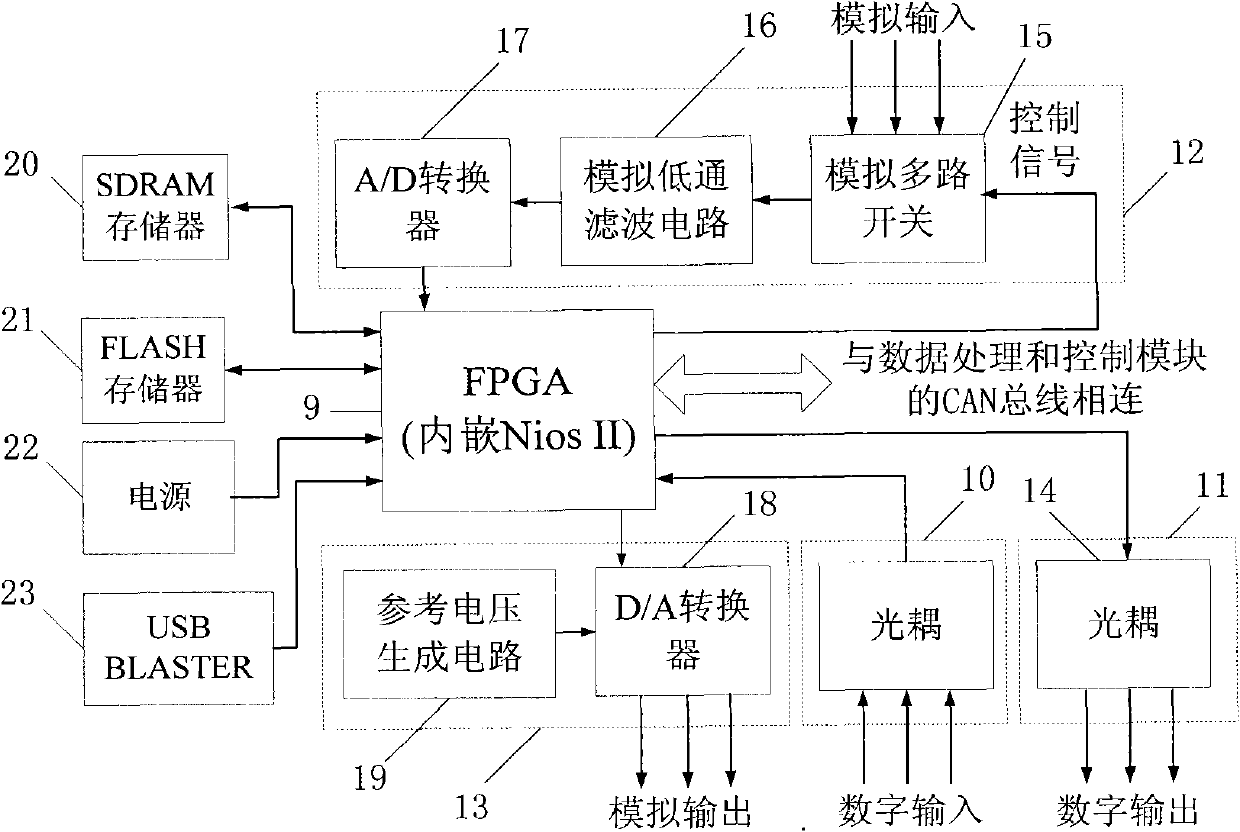

Water treatment project monitoring system based on wireless sensor network

InactiveCN101995865AReduce failureImprove data processing capabilitiesNetwork topologiesTotal factory controlLine sensorData acquisition module

The application relates to a water treatment project monitoring system based on a wireless sensor network. As present sewage treatment equipment has limited processing ability to use PLC data and a slow running speed, further improvement in system performance is restricted. The system comprises a central control system (2), which is connected with a group of wireless sensor network nodes (1) and comprises an industrial personal computer (6). The industrial personal computer (6) is connected with a wireless sensor master station (7). The wireless sensor network node comprises a data collecting module (3) which is connected with a data processing and controlling module (4). The data processing and controlling module is connected with a communication module (5). The system is used for monitoring the system of the sewage treatment equipment.

Owner:哈尔滨云水工大环保科技股份有限公司

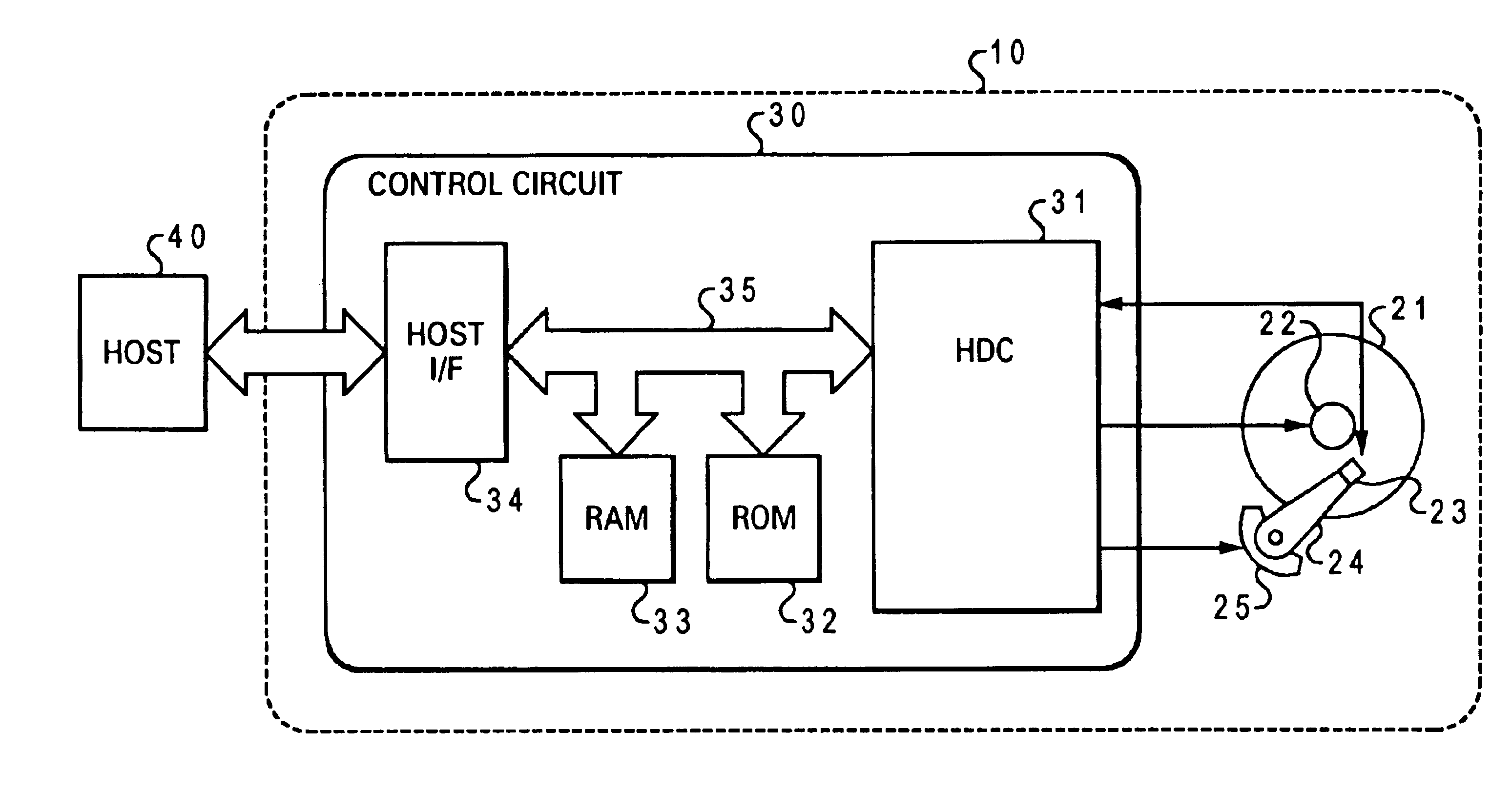

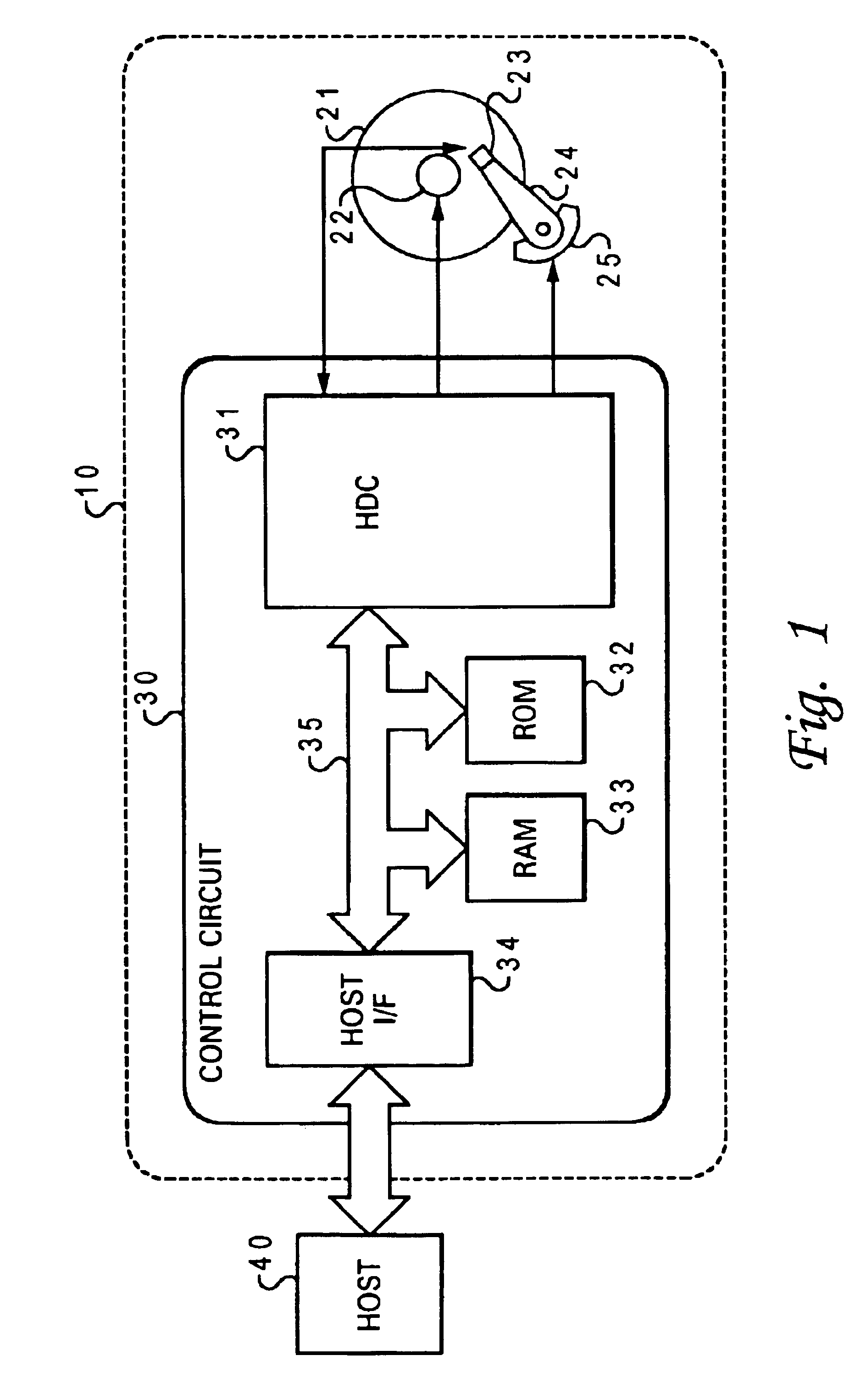

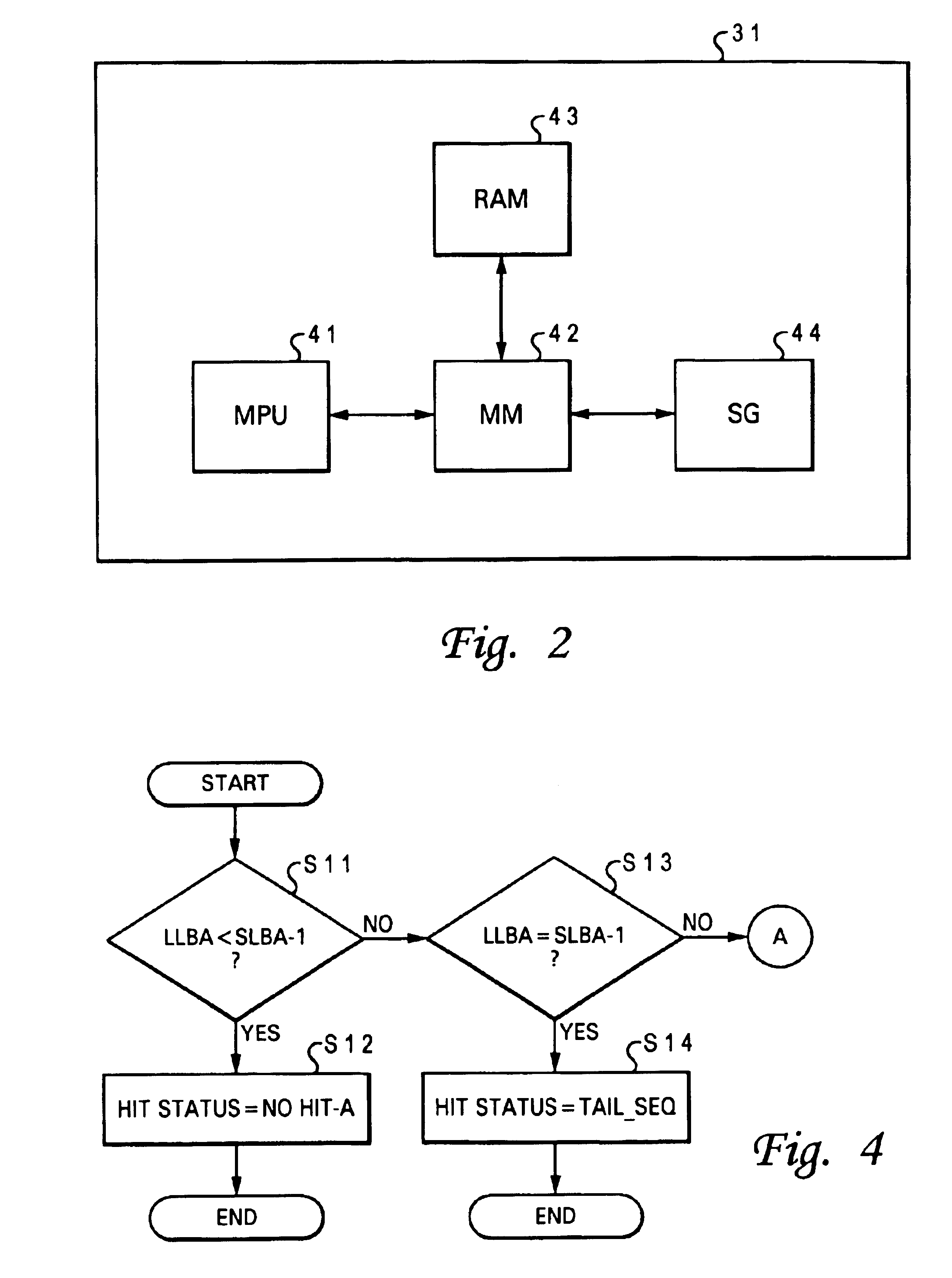

System and method of implementing a buffer memory and hard disk drive write controller

InactiveUS6842801B2Lower latencyNot enough space to solveInput/output to record carriersDigital recording/reproducingHard disc driveLogic circuitry

A method and system for writing data which includes the steps of: receiving a write command, storing associated data in a buffer memory, determining whether or not enough free space exists in the buffer memory to store a subsequent unit of write data, and sending a “command complete” signal to the external device, if it is determined that there exists enough free space to store a subsequent unit of write data. The disk drive unit includes: a random access recording medium, a command memory, a buffer memory, and a logic circuit for determining whether or not enough free space exists in the buffer memory to store a subsequent unit of write data, with a predetermined reference value representing the amount of free space occupied by a typical unit of write data.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

Data processing method and equipment

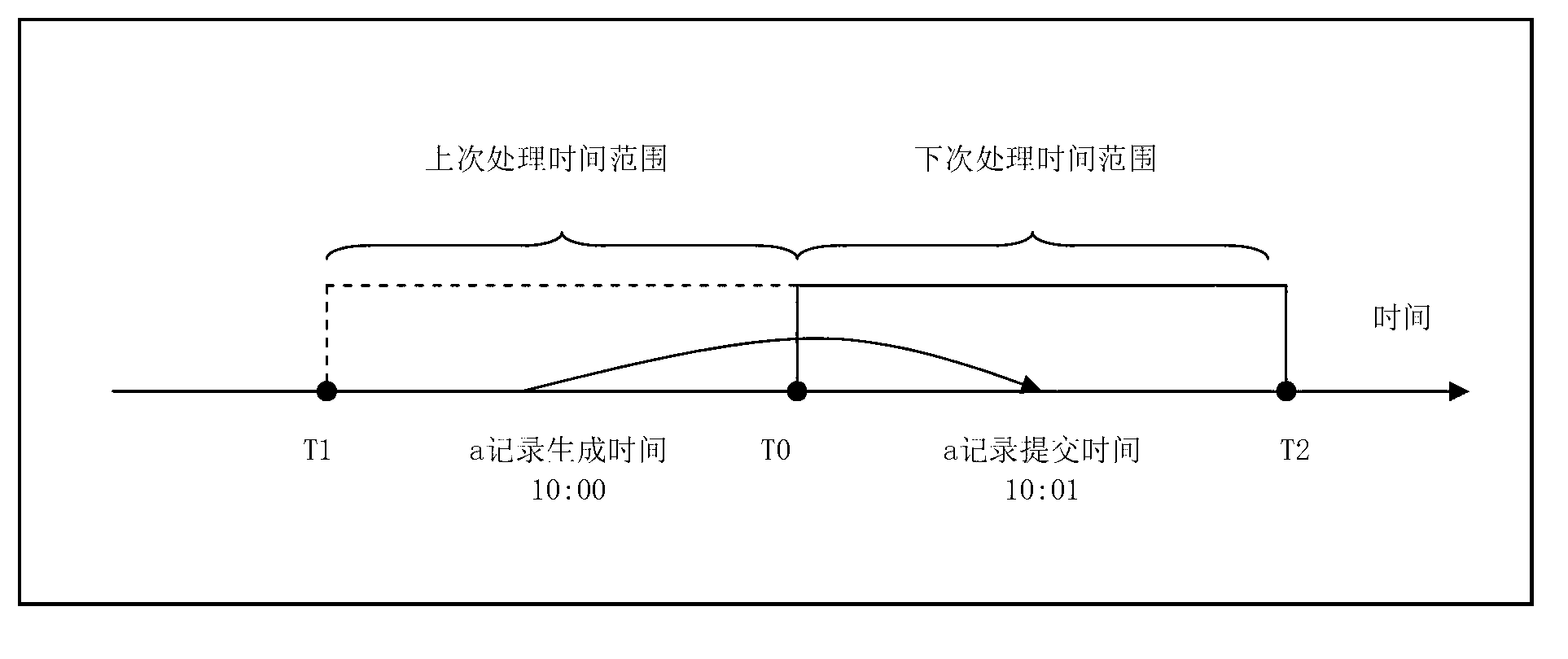

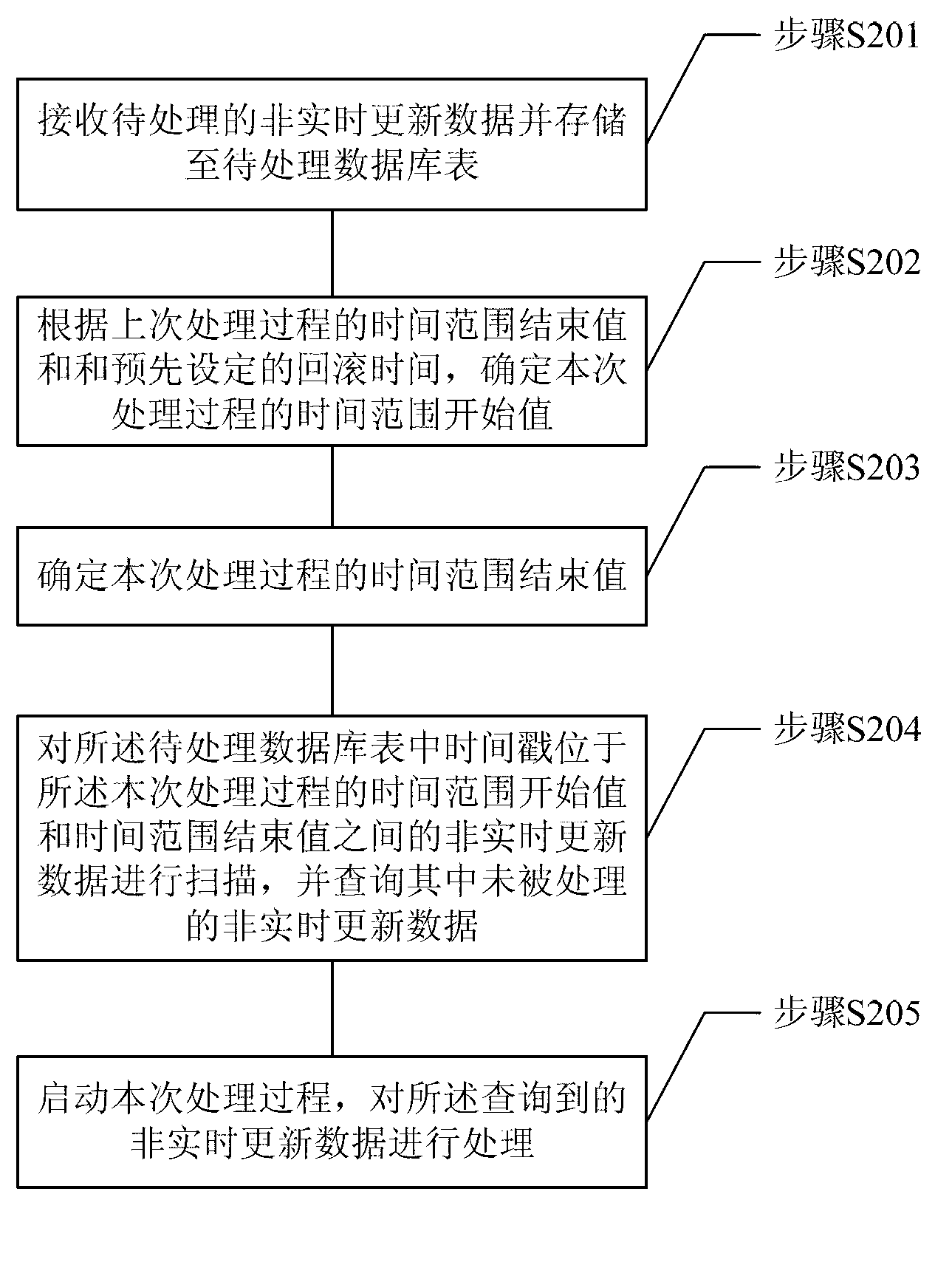

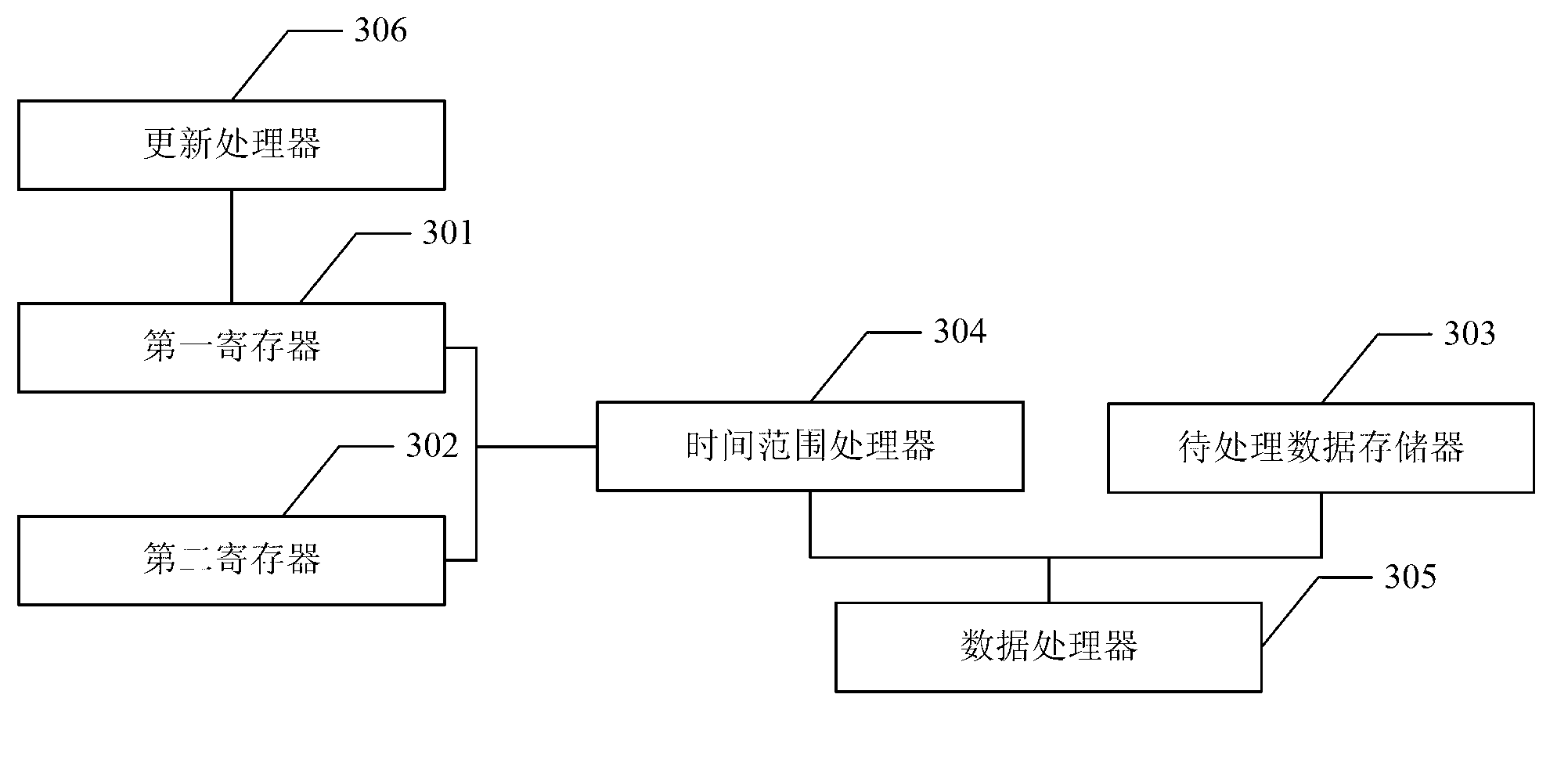

InactiveCN103020304AAvoid the situation of being left outImprove securitySpecial data processing applicationsTime rangeNon real time

The invention provides a data processing method and equipment. The method comprises the following steps: receiving non-real time update data to be processed and storing the data in a processing database table; determining a time range beginning value of a this-time processing process according to a time range finishing value of a last-time processing process and a predetermined rollback time; determining a time range finishing value of the this-time processing process; scanning the non-real time update data of which the time stamps in the processing database table are between the time range beginning value and the time range finishing value of the this-time processing process, and inquiring the non-real time update data not processed therein; and starting the this-time processing process to process the inquired non-real time update data. The method and the equipment solve the problem of leakage processing of data records in the time range clinical point of two processing processes, and can achieve a better data processing effect and improve the system reliability.

Owner:INDUSTRIAL AND COMMERCIAL BANK OF CHINA

Digital television set-top box, device and method for managing window layout

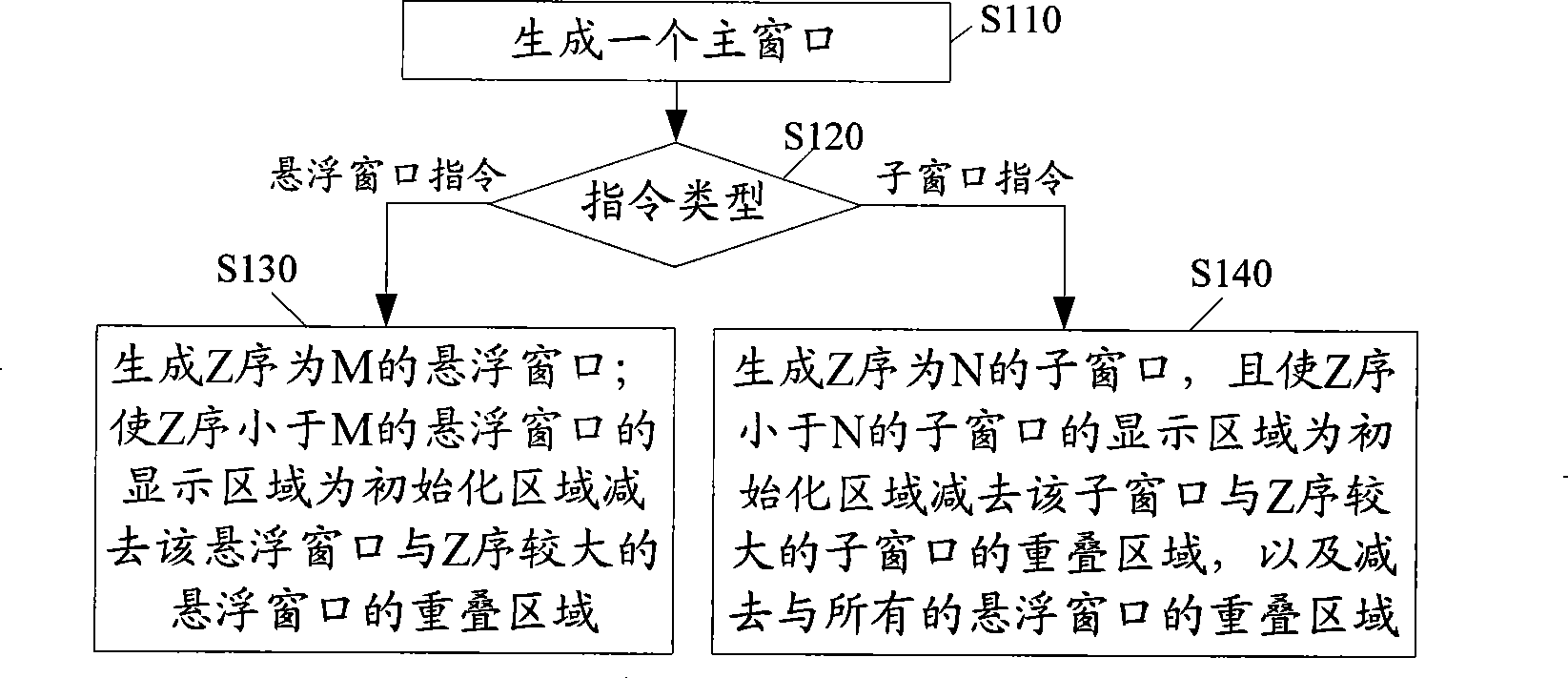

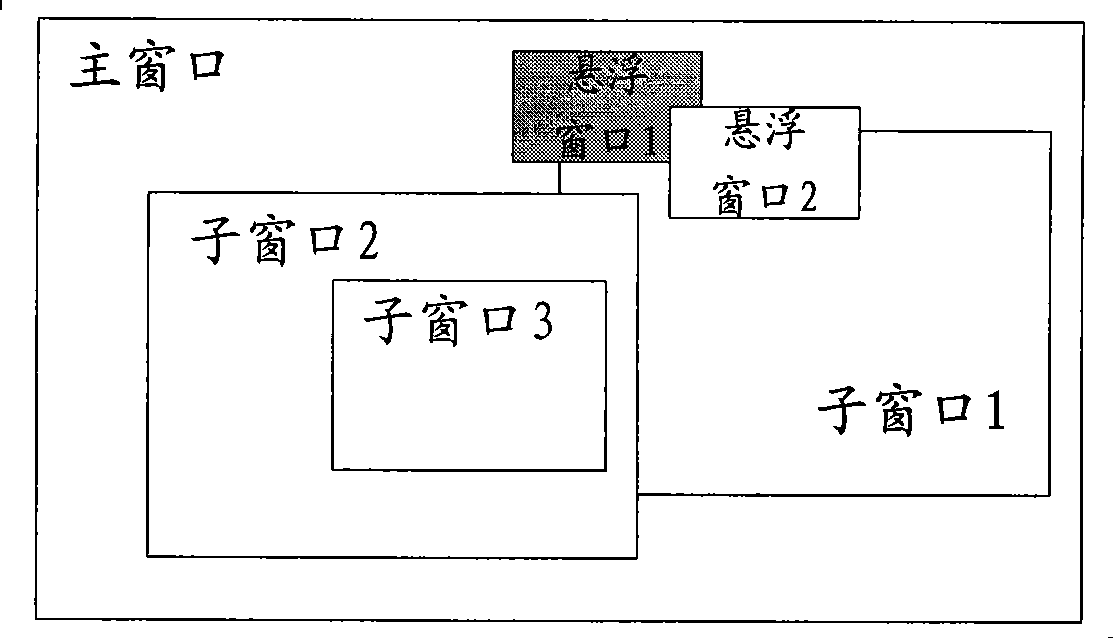

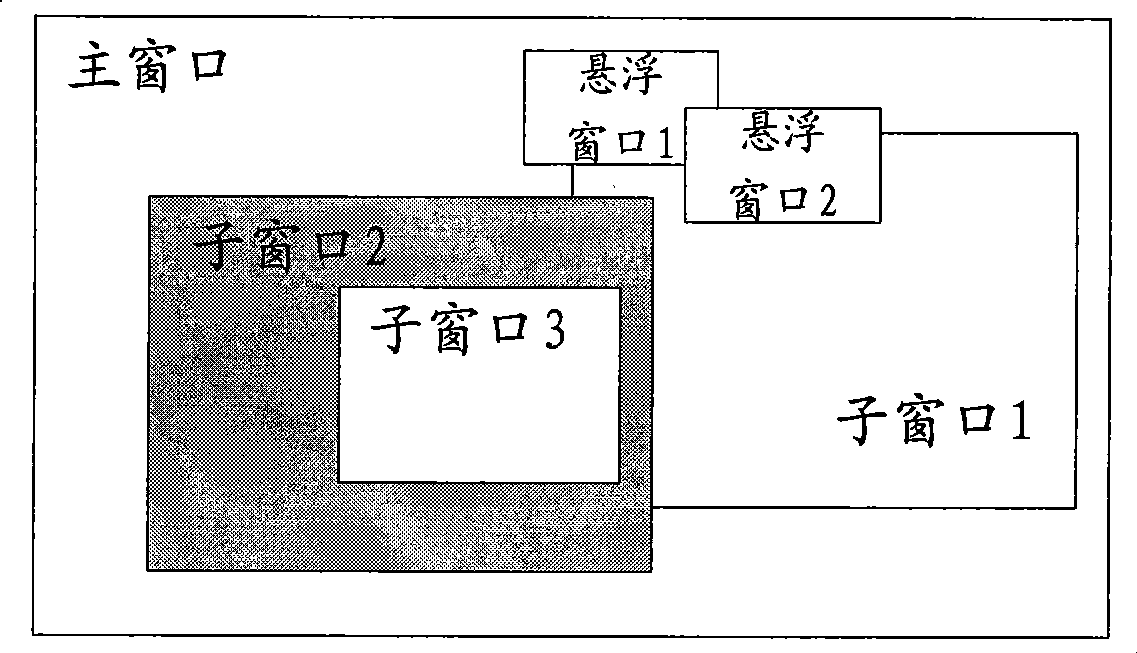

InactiveCN101465995AShow generalization and simplificationMeet the needs of displaying global informationTelevision system detailsColor television detailsComputer scienceDigital television

The invention discloses a management method of window layout. The method comprises: a main window is generated; according to a command, a child window or a floating window are generated and managed in the main window: when the command is for generating the floating window, the floating window which cuts the main window is controlled and generated; according to the sequence M of generating the floating window, the Z sequence is defined as M, and an initialized area minus a cutting area of other floating windows leaves a display area of the floating window with the Z sequence less than M. when the command is for generating the child window, the child window which cuts the main window is controlled and generated; according to the sequence N of generating the child window, the Z sequence is defined as N, and the initialized area minus the cutting areas of other floating windows and all floating windows leaves the display area of the child window with the Z sequence less than N. The invention further discloses a management equipment of the window layout and a digital television set-top box. The requirement for displaying the whole information of the digital television set-top box is satisfied.

Owner:SHENZHEN SKYWORTH DIGITAL TECH CO LTD