DFT (Design for Testability) method for double-edge trigger

A technology of double-edge triggering and design method, applied in the fields of instruments, computing, special data processing applications, etc., can solve the problems of inability to test vector verification, unable to apply double-edge triggers, unable to handle double-edge triggers, etc., to achieve data processing. The effect of capacity improvement and power consumption reduction by half

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

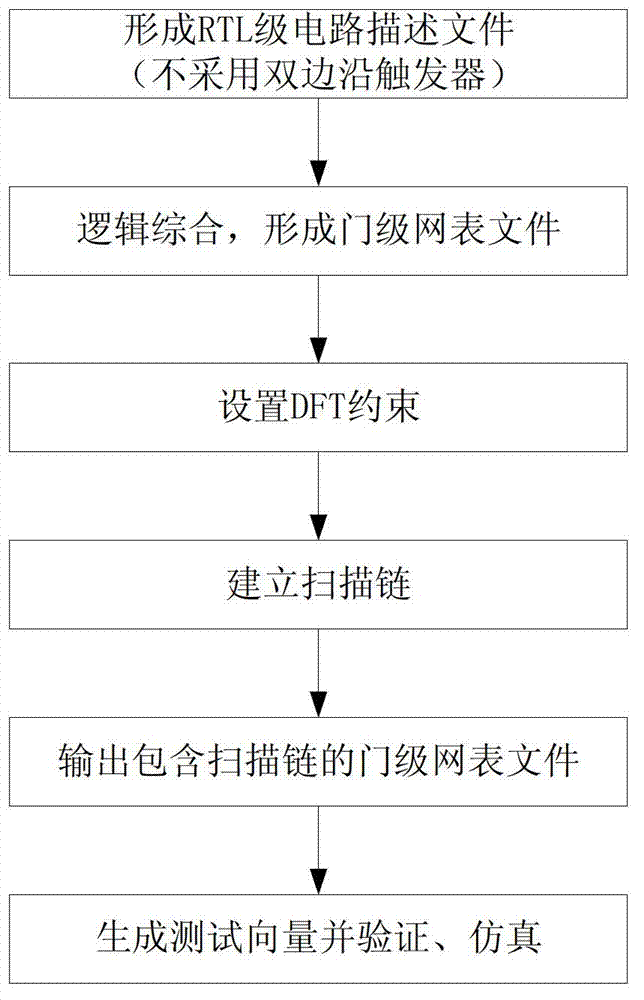

[0047] See Figure 7 , The testability design method used in the double-edge flip-flop in this application also adopts internal scanning design, including the following steps:

[0048] The first step is to design the input to form an RTL-level circuit description file. At this time, double-edge flip-flops are not used. When a flip-flop is needed, all single-edge flip-flops are used. Common design input tool software includes Verilog, VHDL, etc. The suffixes of the RTL-level circuit description files formed by them are .v and .vhd respectively.

[0049] In fact, both of the hardware description languages Verilog and VDHL can be used to describe double-edge flip-flops, but since the subsequent logic synthesis tools do not support double-edge flip-flops, it is not necessary to use dual-edge flip-flops when designing inputs.

[0050] The second step is to logically synthesize the RTL-level circuit description file to form a gate-level netlist file.

[0051] The common logic synthesis t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More