A method and a system for designing the testability of a high-speed serial IO interface based on DLL clock recovery

A technology of clock recovery and high-speed serial, which is applied in the field of testability design of high-speed serial IO interface, can solve the problems of huge number of bits, long test time, and failure to obtain parameter information, etc., achieve low hardware cost, reduce test cost, The effect of shortening test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The testability design method and system based on the DLL clock recovery high-speed serial IO interface provided by the present invention will be described in detail below in conjunction with the accompanying drawings, but this does not constitute a limitation to the present invention.

[0023] The present invention is based on the high-speed serial IO interface testing method of DLL clock recovery, and its implementation step comprises:

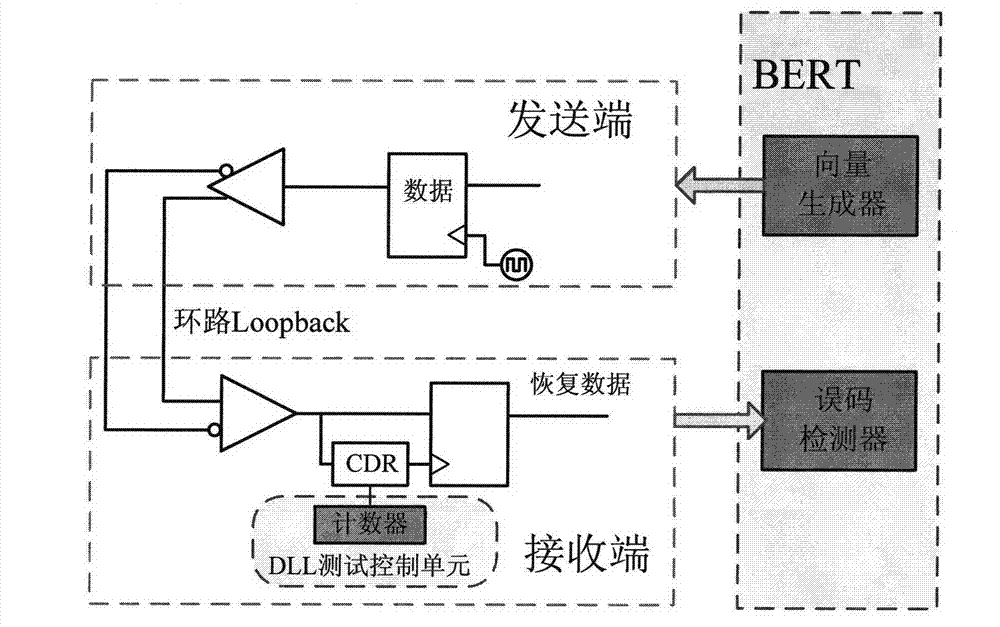

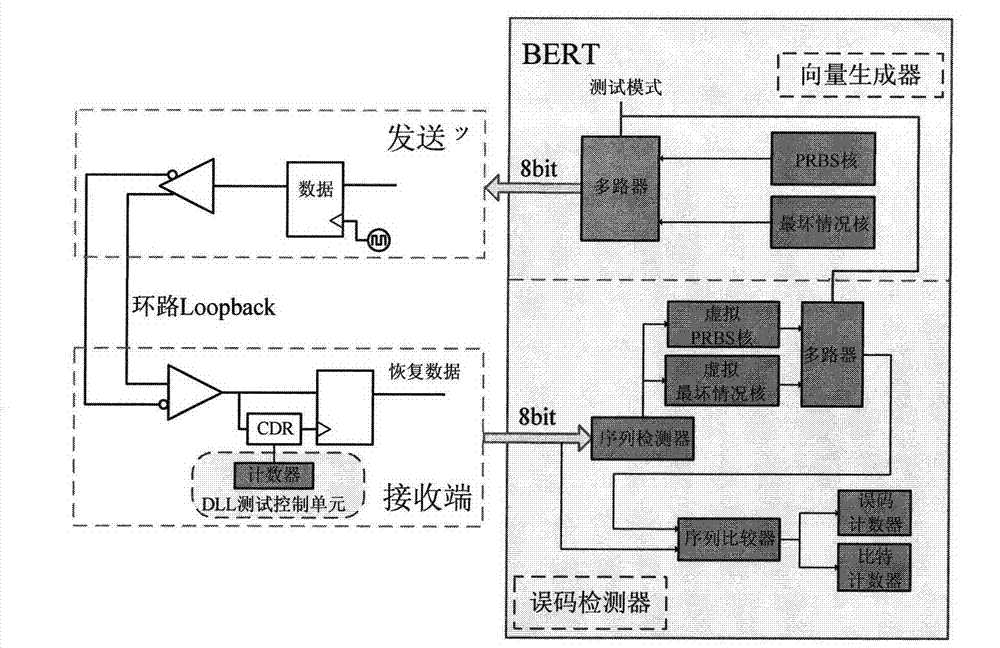

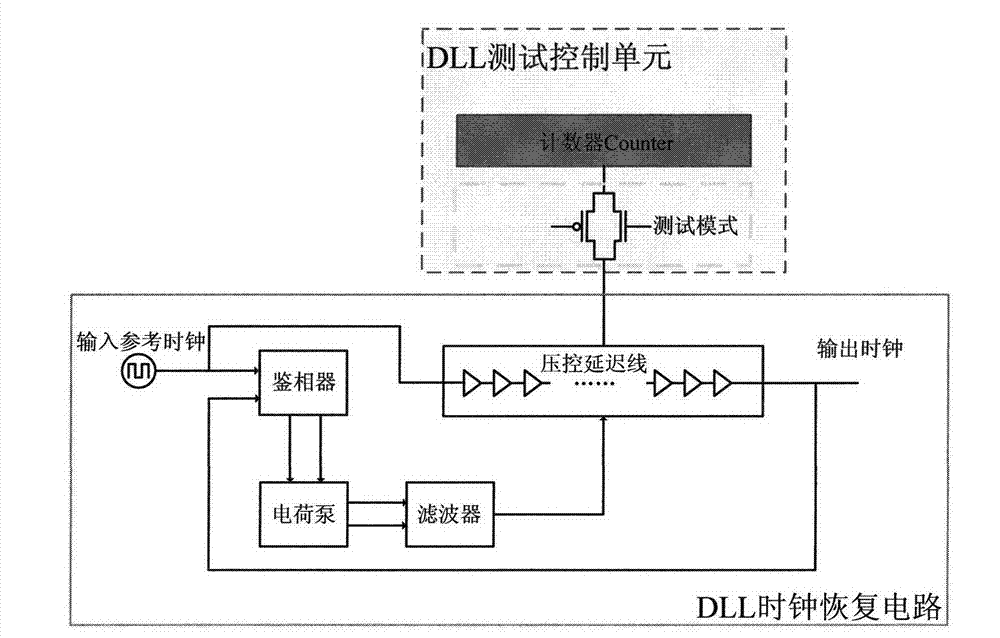

[0024] Phase 1: Build the BIST circuit

[0025] Step1: After the high-speed serial IO circuit design is completed, insert the BIST circuit for testing. BIST circuit of the present invention comprises two parts: BERT and DLL test control unit, as figure 1 shown. BERT is designed as figure 2 As shown, it includes a vector generator and a bit error detector. The vector generator is composed of a PRBS kernel (Pseudo Random Binary Sequence) and a worst-case test kernel to generate test data. The bit error detector is used for bit erro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More