System and method for testing system fault on integrated circuit board

A system-on-chip and integrated circuit technology, which is applied in the direction of electronic circuit testing, measuring electronics, and measuring devices, etc., can solve problems such as the difficulty in effectively controlling and improving the fault coverage index of the integrated circuit system-on-chip chip fault test, and achieve test The search mechanism is simple, the test overhead is reasonable, and the fault coverage rate is improved

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

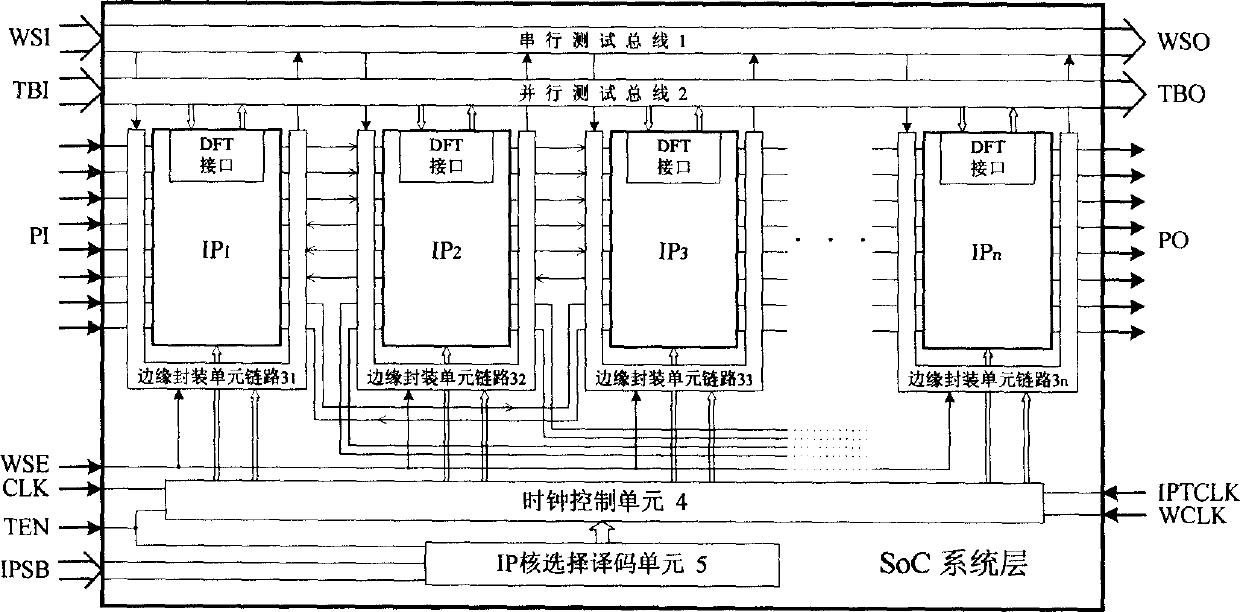

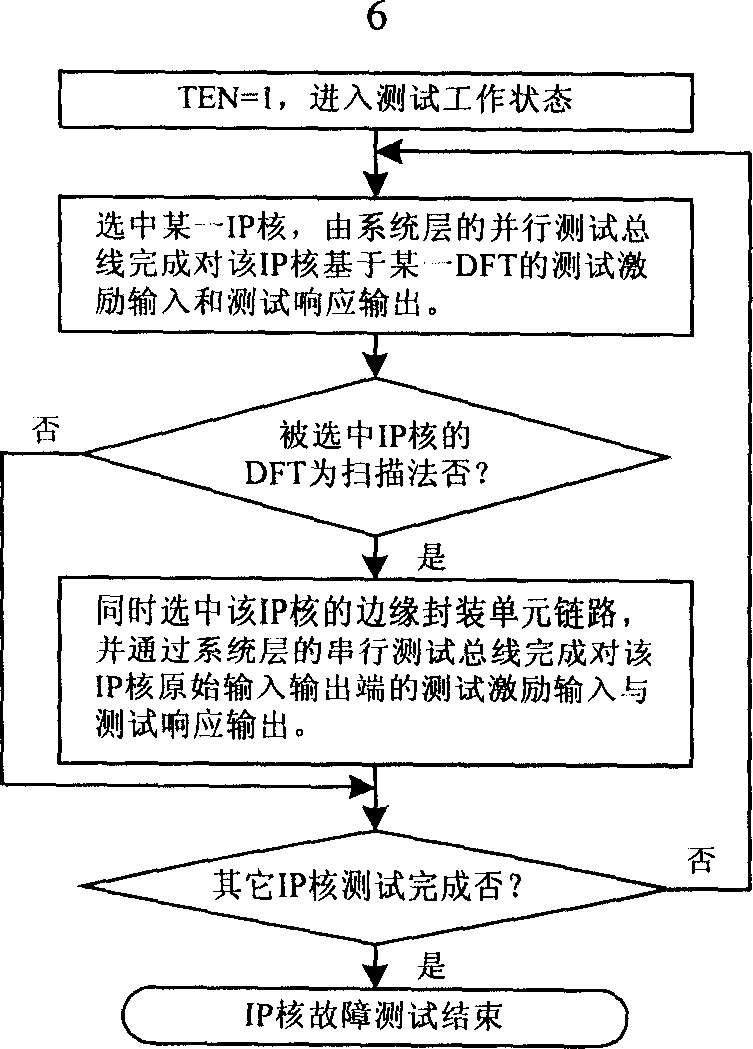

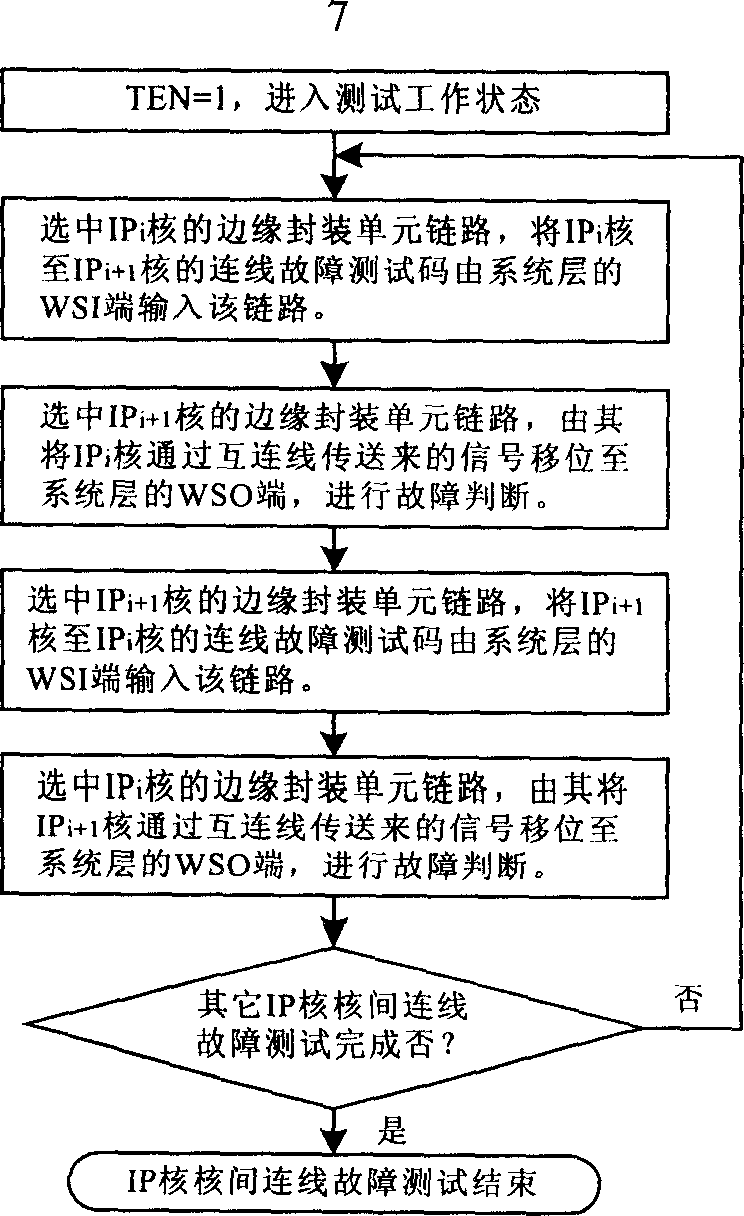

[0031] A preferred embodiment of the present invention is: referring to Fig. 1, Fig. 2 and Fig. 3, it includes a circuit added to improve the testability of the integrated circuit system on chip and a test seeking mechanism based on the operation of the circuit. Its circuit is composed of IP core serial test bus 1, parallel test bus 2, IP (Intellectual Property) core edge packaging unit link 3, clock control unit 4 and IP core selection decoding unit 5; its test search mechanism is composed of IP core It consists of an independent test search mechanism 6 and an IP core inter-core connection fault test search mechanism 7.

[0032] This circuit structure is: referring to Fig. 1, the serial test bus 1 has the input and output pins WSI, WSO of the external scan link, and the edge packaging unit link 3 connected to each IP core by the chip output; the parallel test bus 2 has a group The test bus signal input pin TBI and a group of test bus signal output pins TBO are connected to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More