Patents

Literature

67 results about "Circuit sizing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

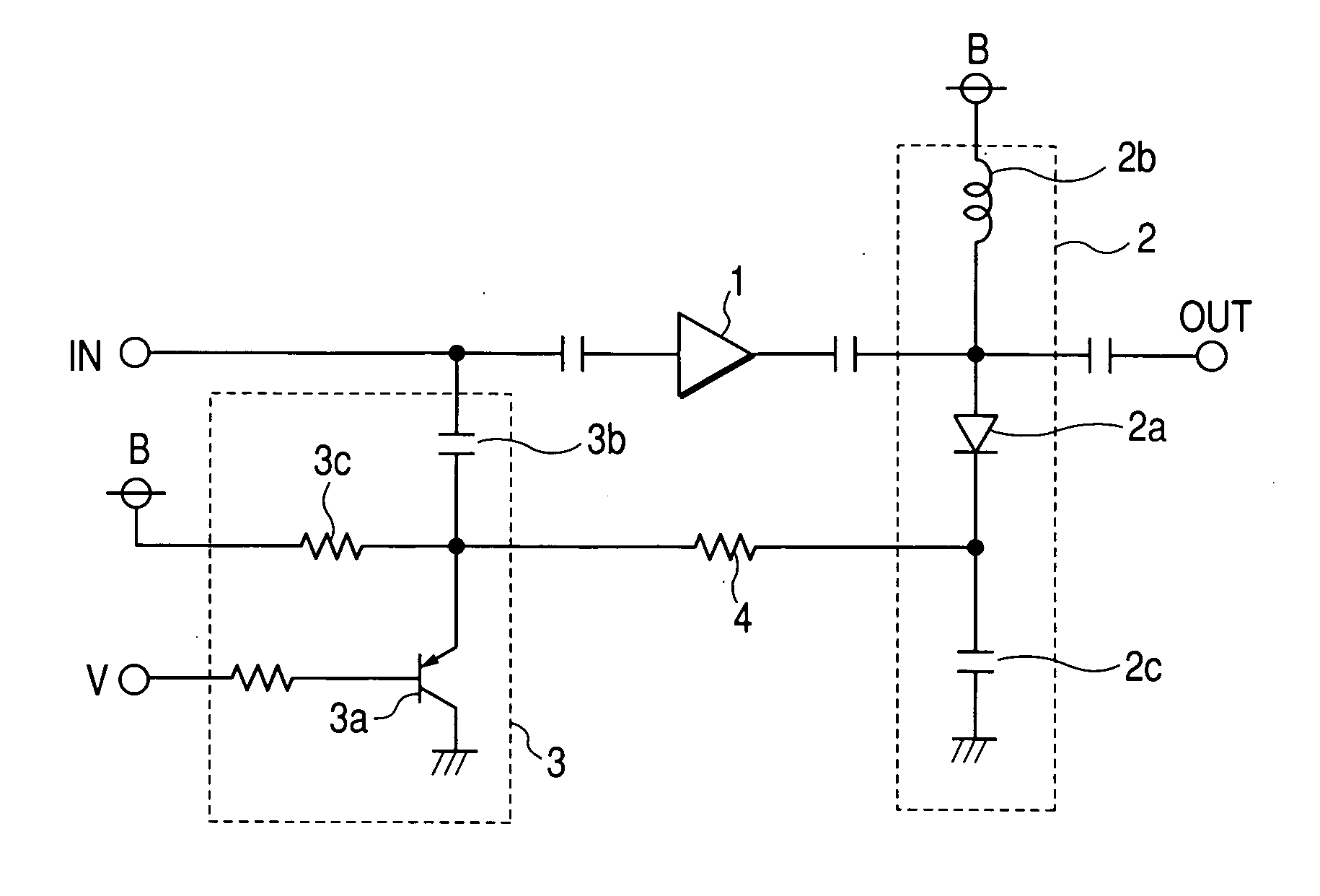

Semiconductor integrated circuit device and receiving device

InactiveUS20080030336A1Small sizeImprove performanceMemory record carrier reading problemsAmplitude-modulated carrier systemsCircuit sizingTransceiver

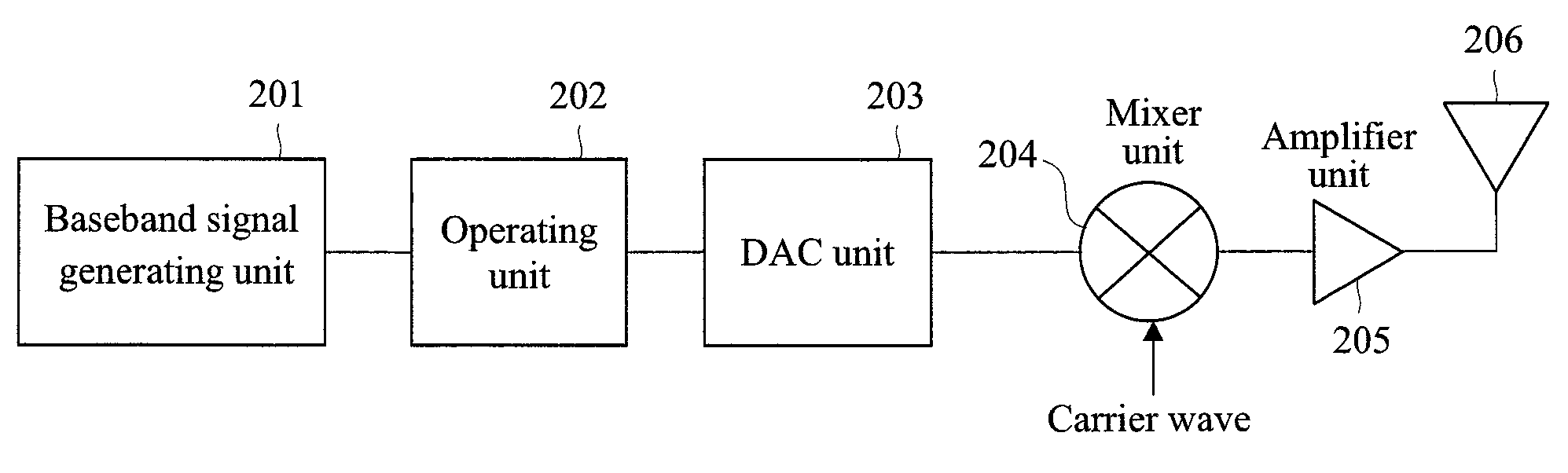

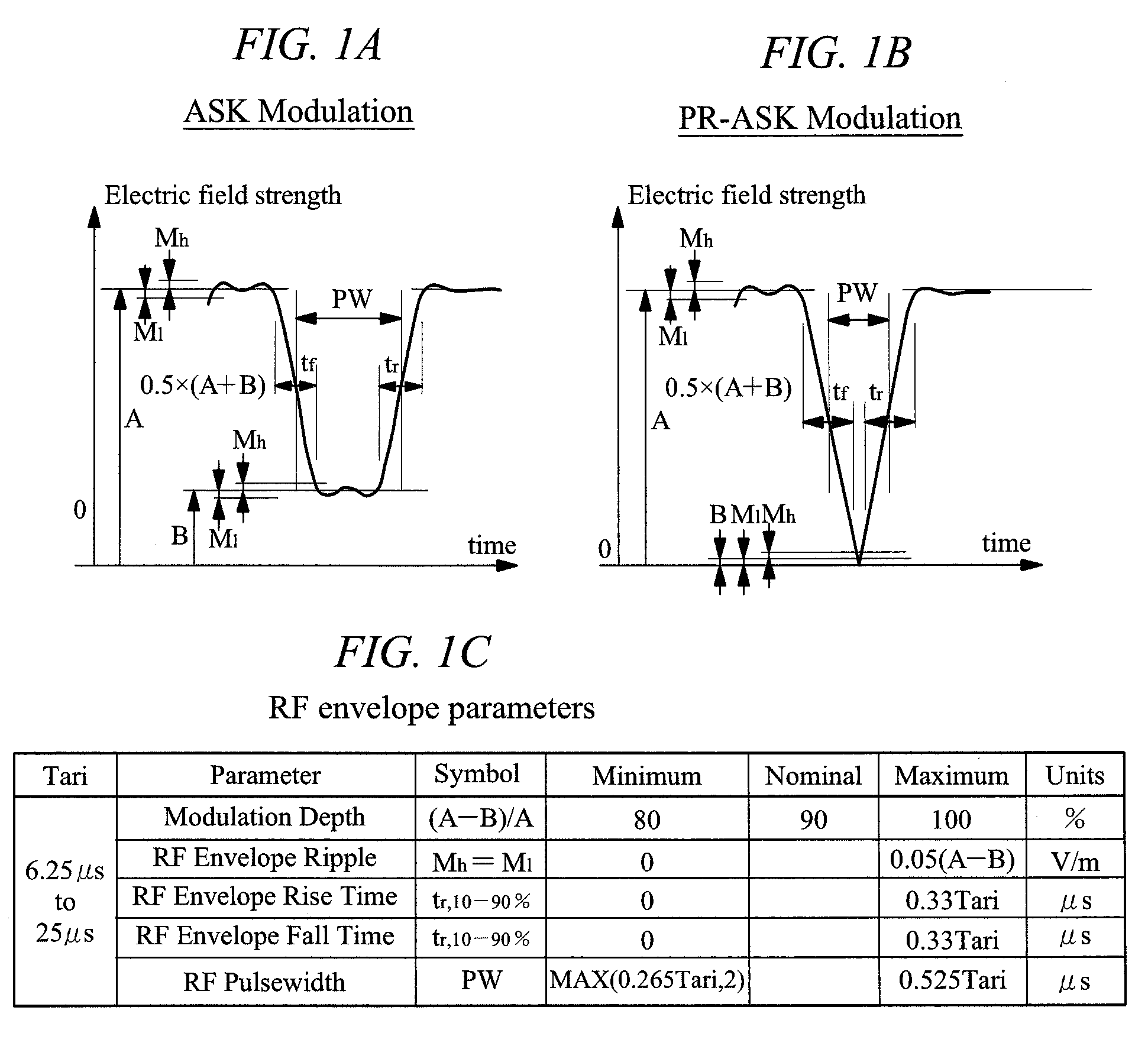

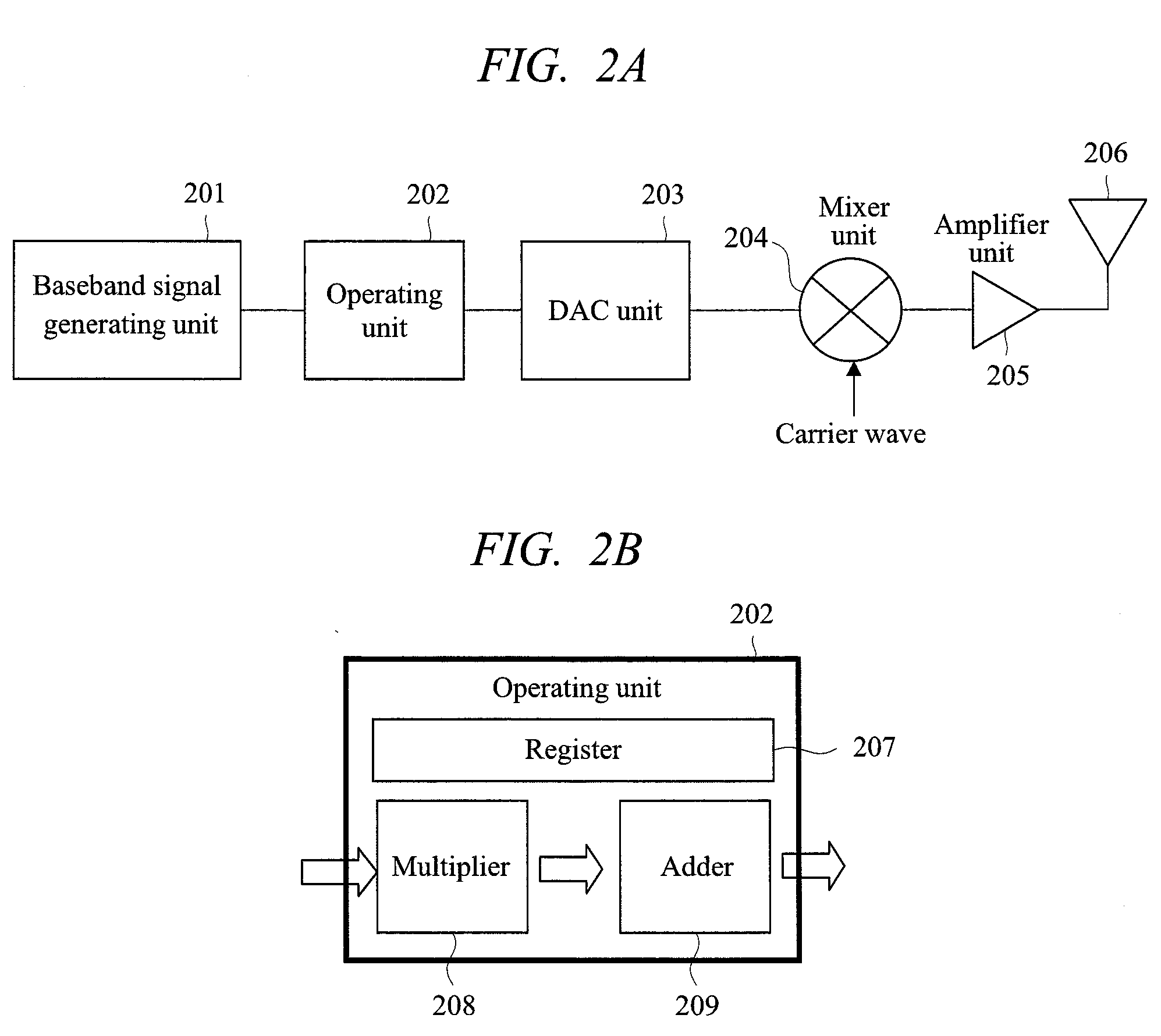

A technique that can reduce a size of a circuit in a radio receiver device such as a reader-writer device of RFID is provided. In a semiconductor integrated circuit device (IC) used for a transceiver such as a reader-writer in a UHF band electronic tag system, an operating unit including a multiplier, an adder, and a register is disposed between a baseband signal generating unit and a DAC unit. By this structure, an ASK modulation depth and a DC bias of an ASK modulation signal can be adjusted with a simple configuration.

Owner:RENESAS TECH CORP

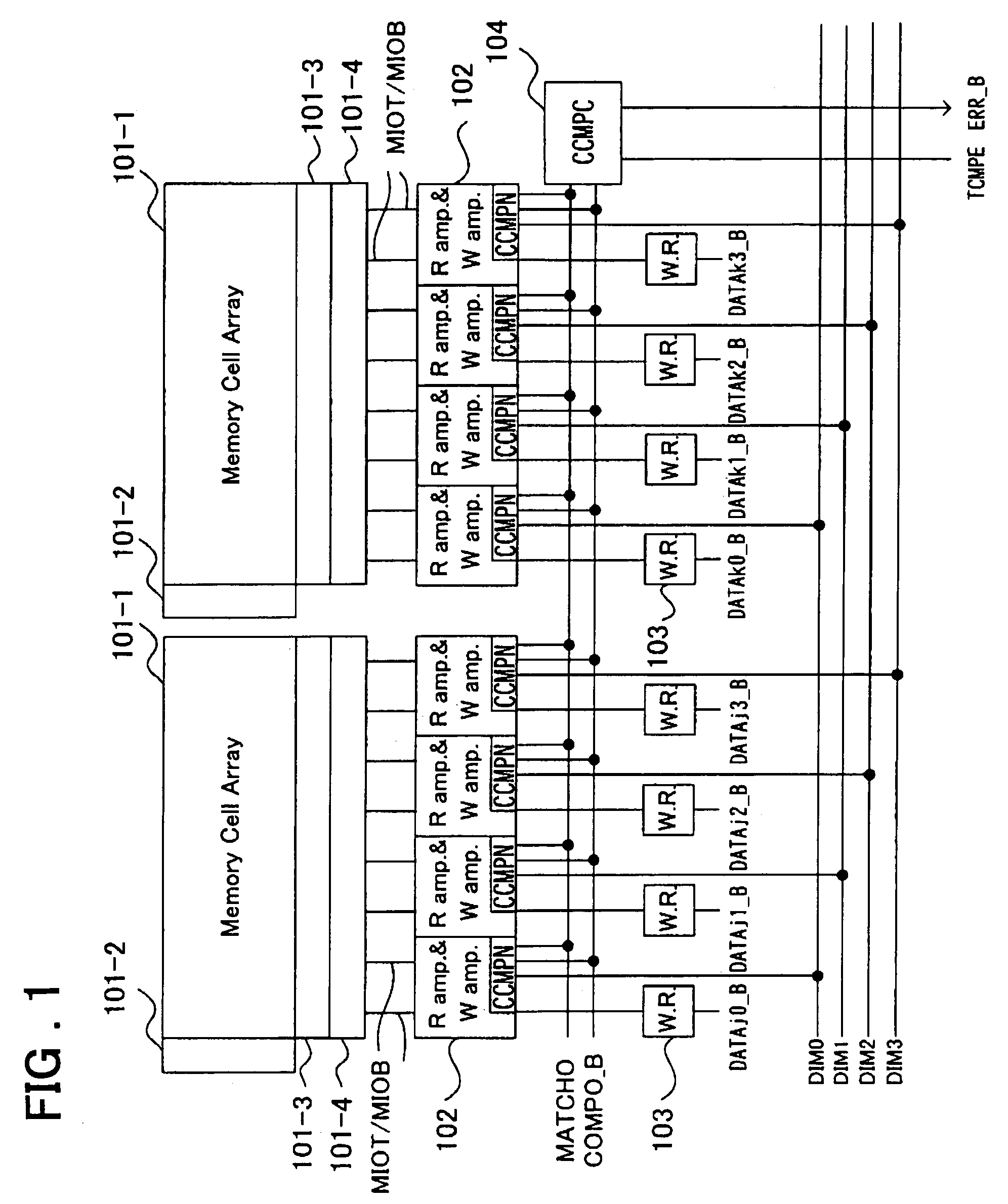

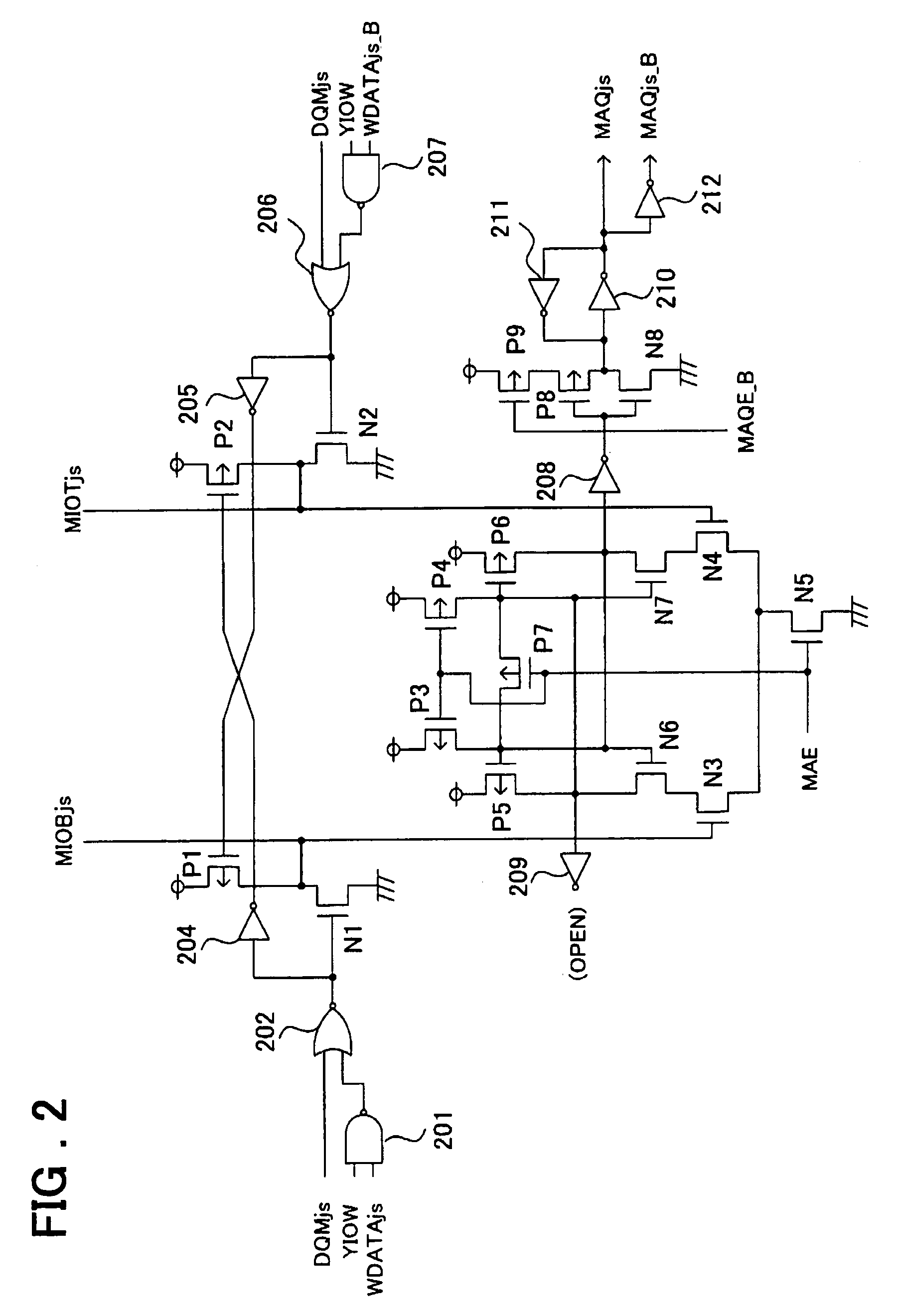

Semiconductor storage device

InactiveUS7240253B2Avoid simple structuresImprove testabilityElectronic circuit testingDigital storageCircuit sizingControl signal

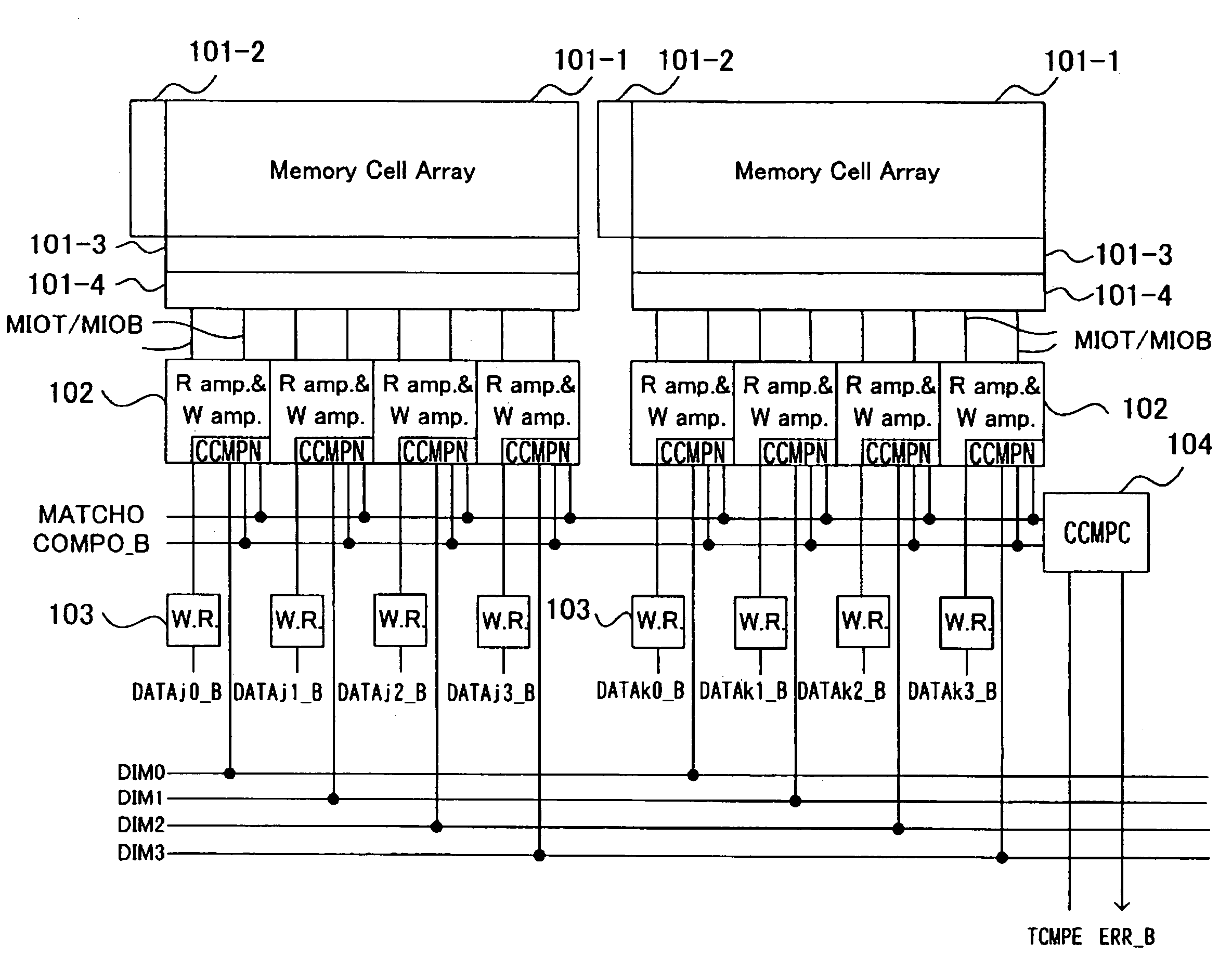

A testing device for a semiconductor storage device suppresses the increase in the circuit size, provides for facilitated accommodation to a test with frequent changes in the test pattern, and improves testability of the semiconductor storage device. A plurality of holding circuits are provided holding write data for memory cells of a memory cell array. (Original) The write data from the holding circuits are written in the memory cells of the selected address. A plurality of comparators are supplied with data read out from the memory cells and with data held by the holding circuits as expectation data to compare the readout data and the expectation data. The non-inverted or inverted value of the write data held by the holding circuits is output as the write data to the memory cells and as expectation data to the comparators depending on the value of the inversion control signal.

Owner:LONGITUDE LICENSING LTD

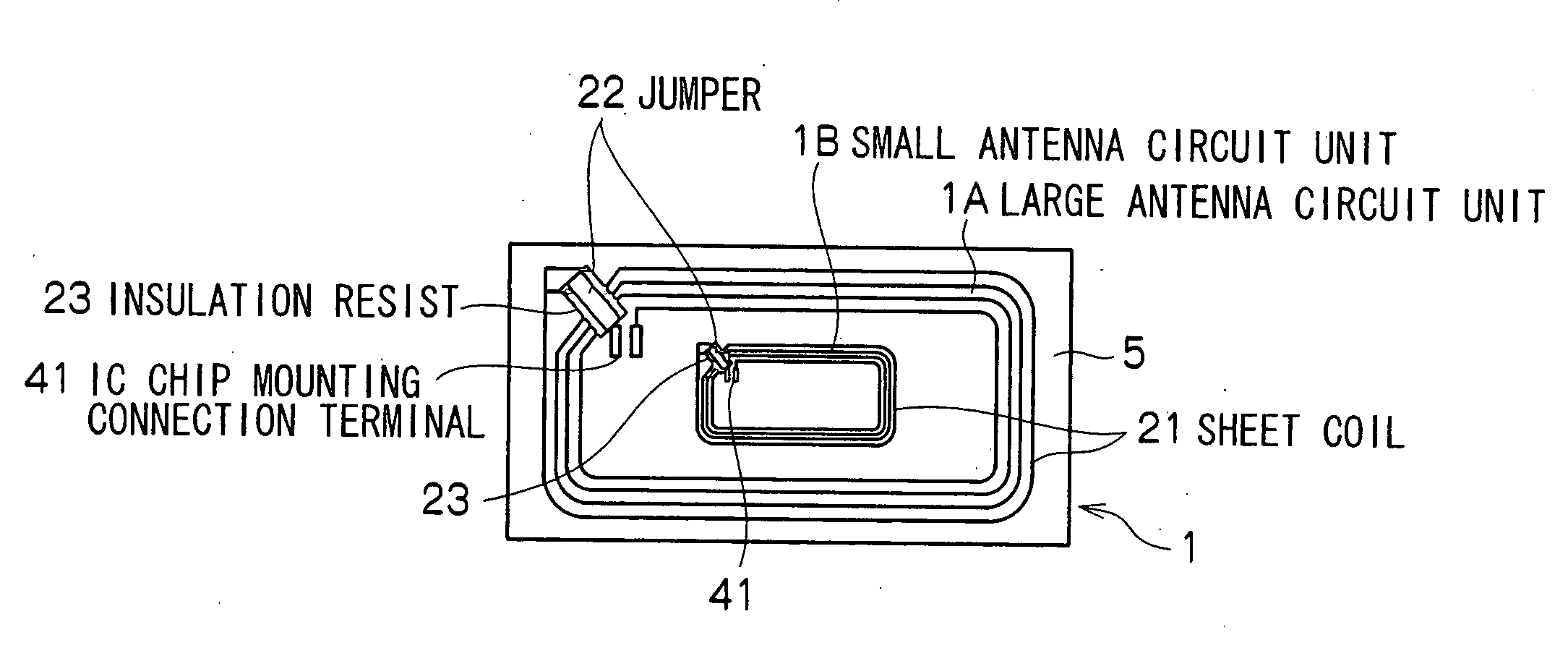

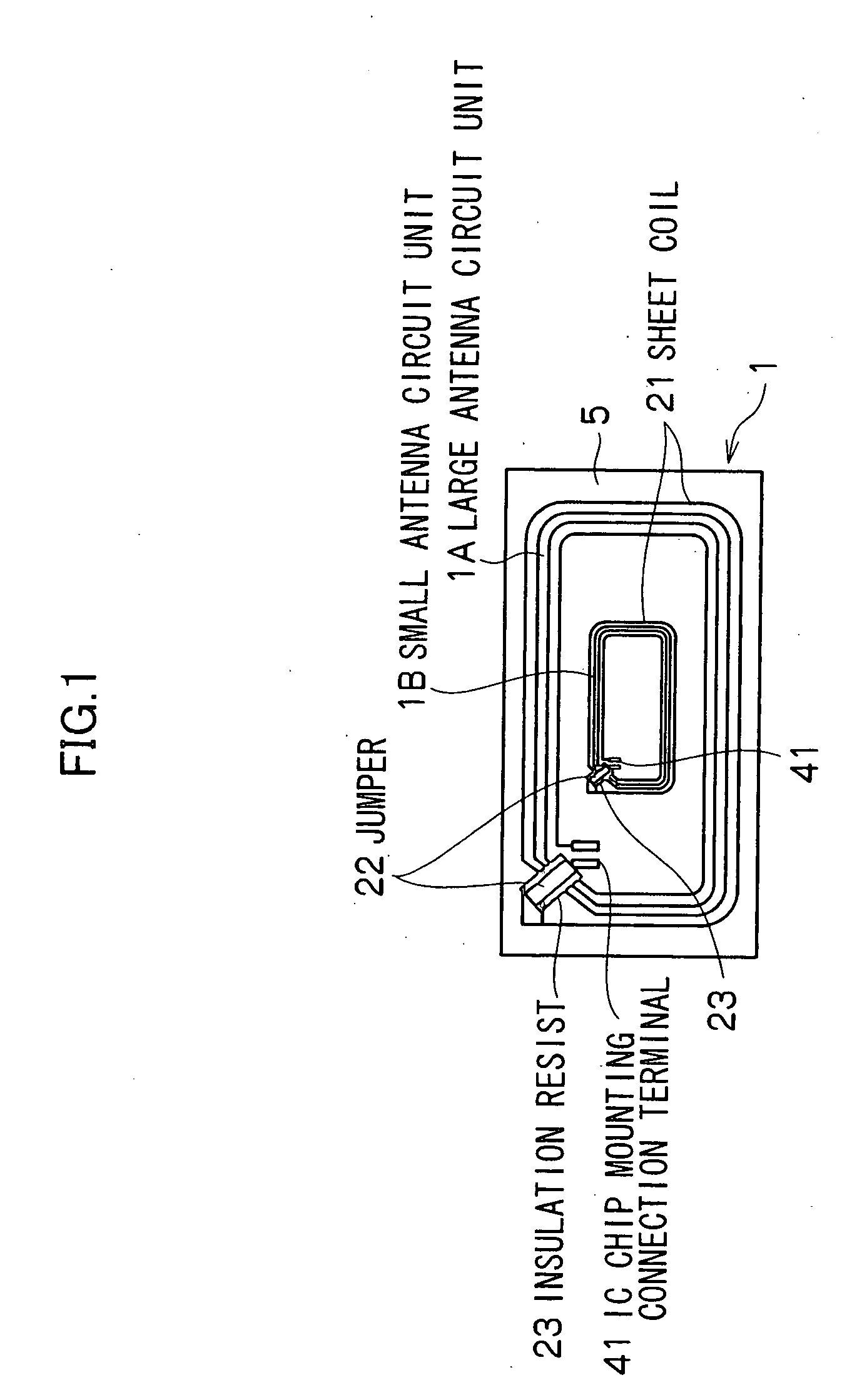

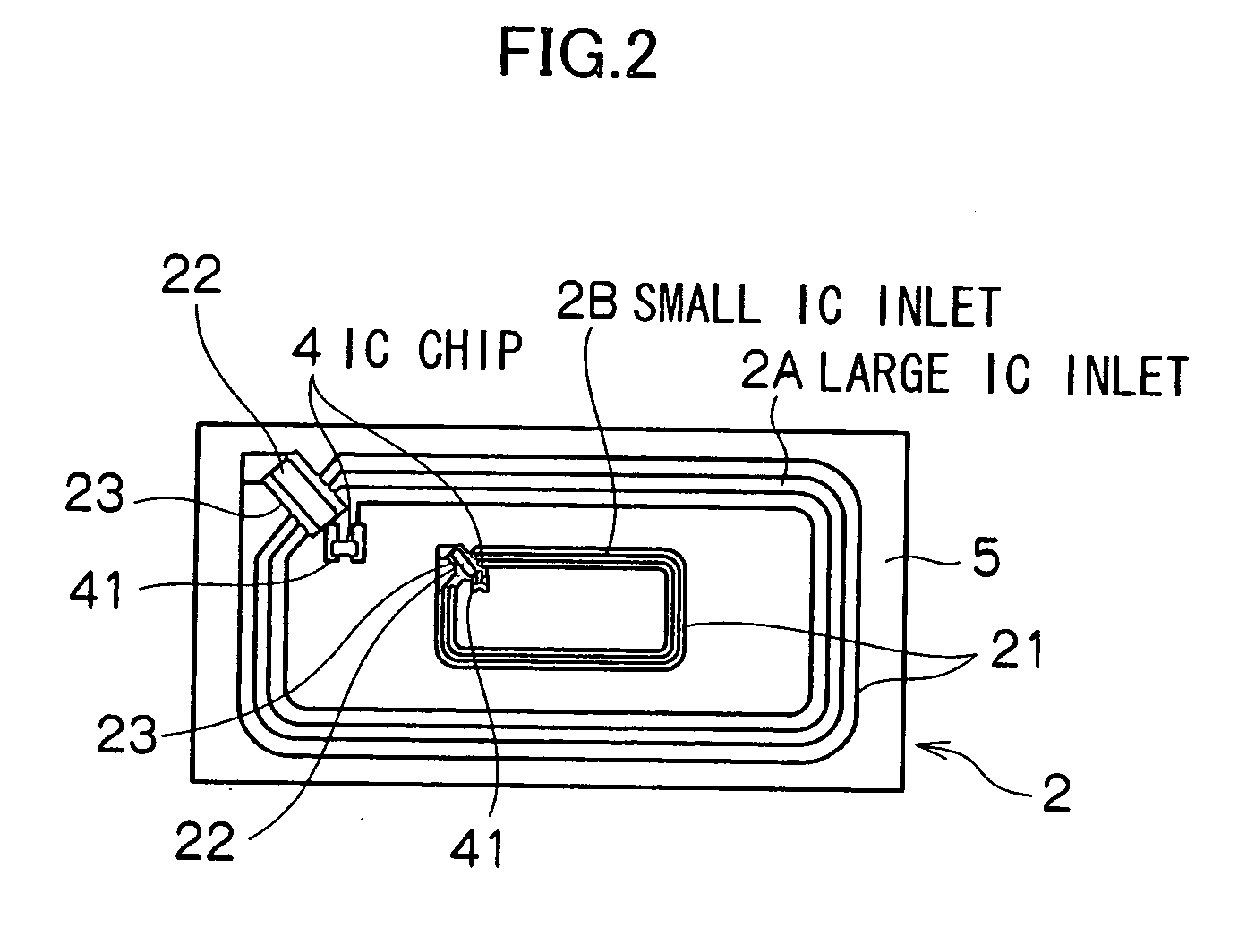

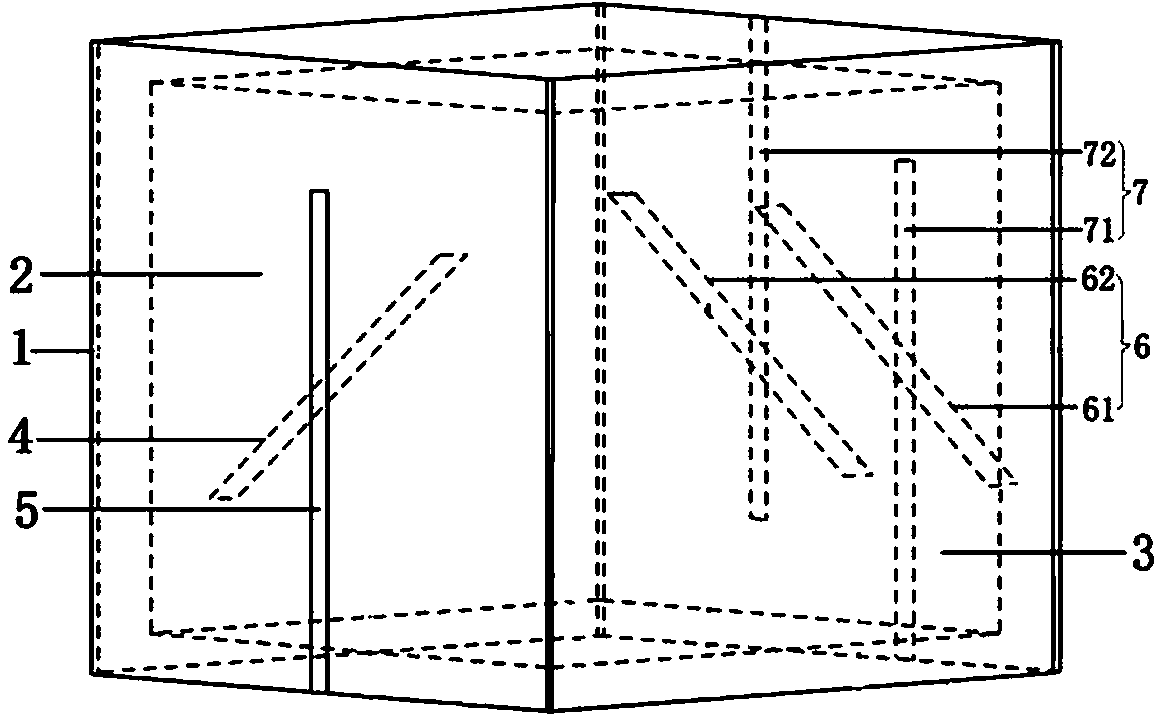

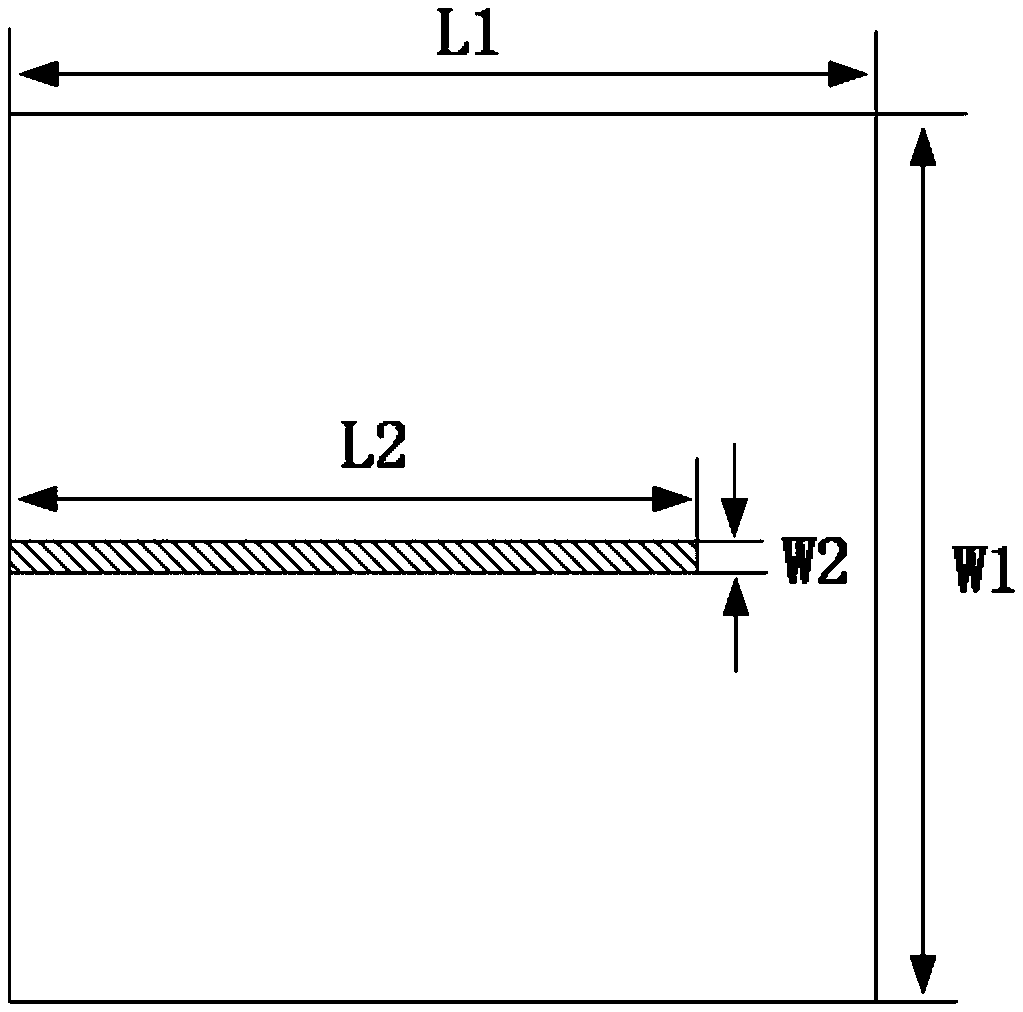

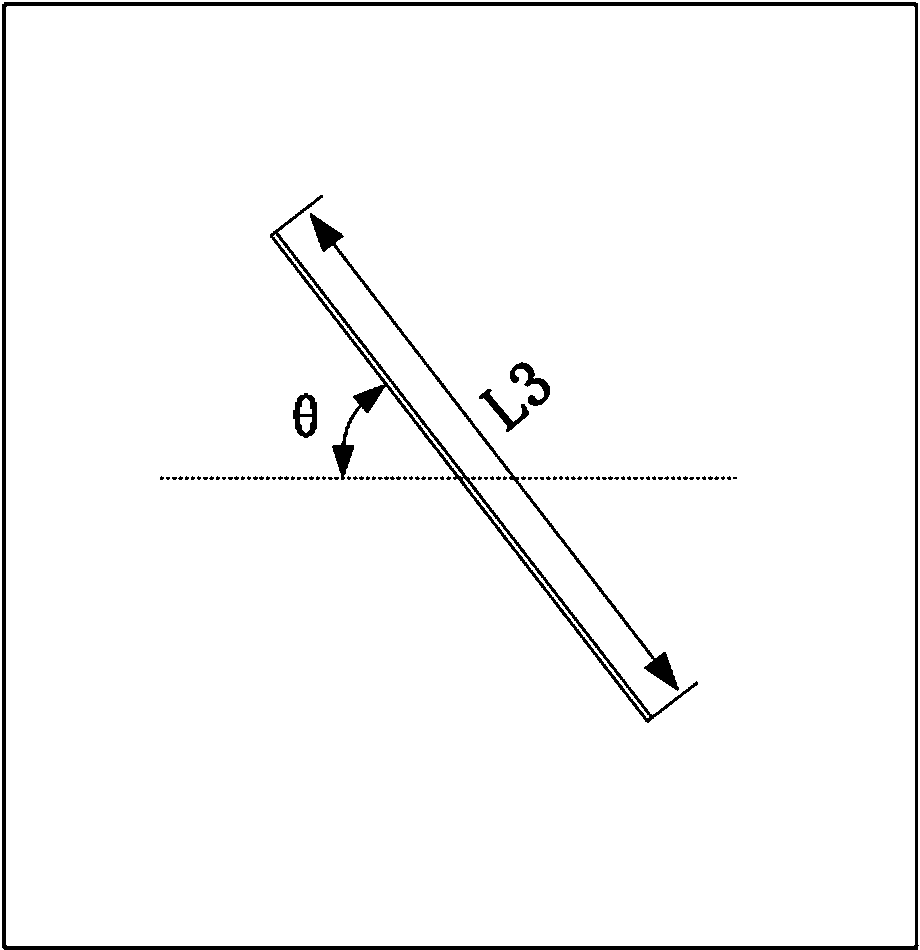

Antenna circuit, IC inlet, multi tag, and method for producing multi tag

InactiveUS20070159339A1Efficient productionAntenna supports/mountingsRecord carriers used with machinesCircuit sizingEngineering

An antenna circuit includes a plurality of antenna circuit units on a circuit substrate. The plurality of antenna circuit units includes: a large antenna circuit unit whose circuit size is large; and a small antenna circuit unit whose circuit size is smaller than the size of the large antenna circuit unit, the small antenna circuit unit provided inside the large antenna circuit unit and provided detachable from the large antenna circuit unit.

Owner:LINTEC CORP

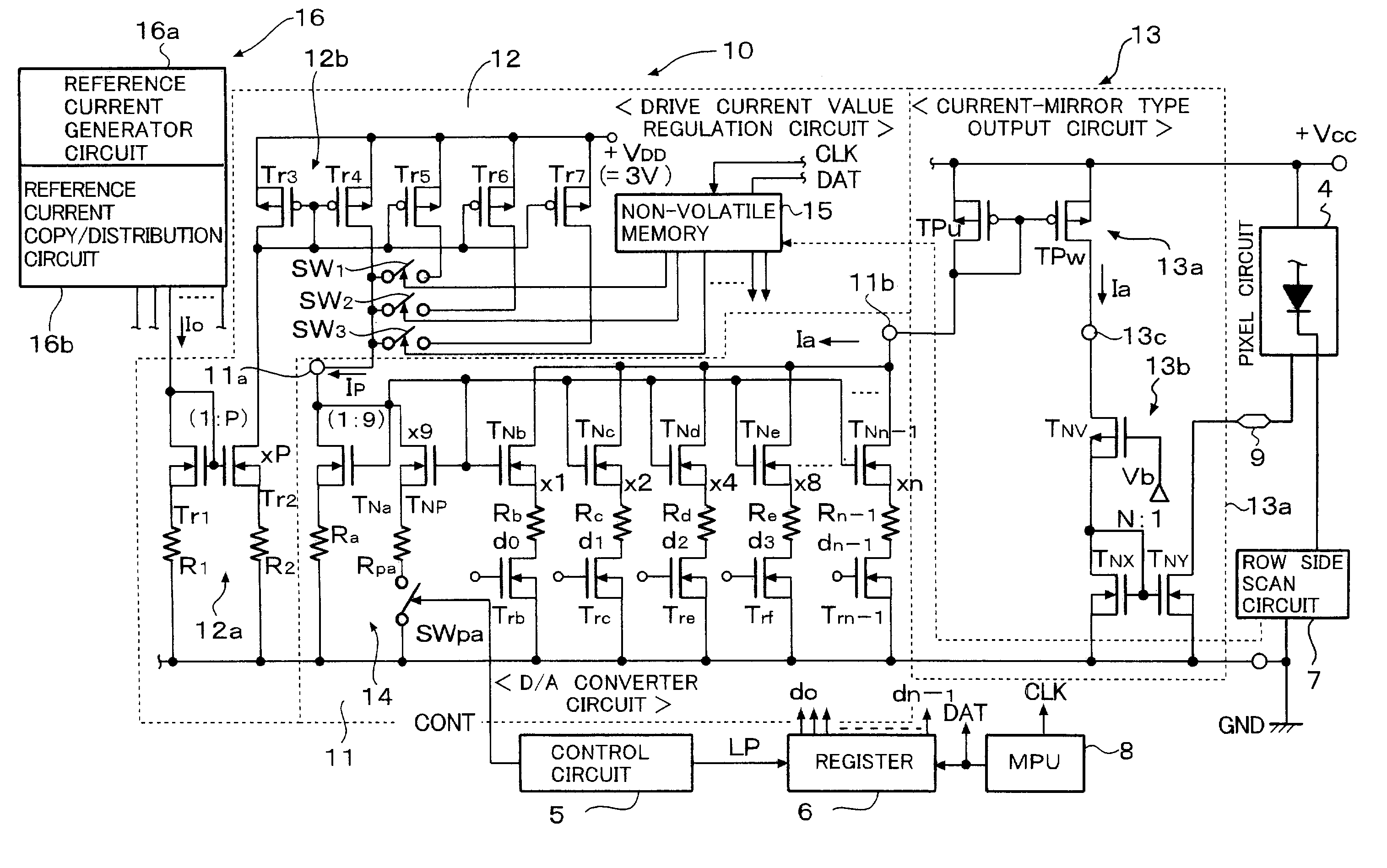

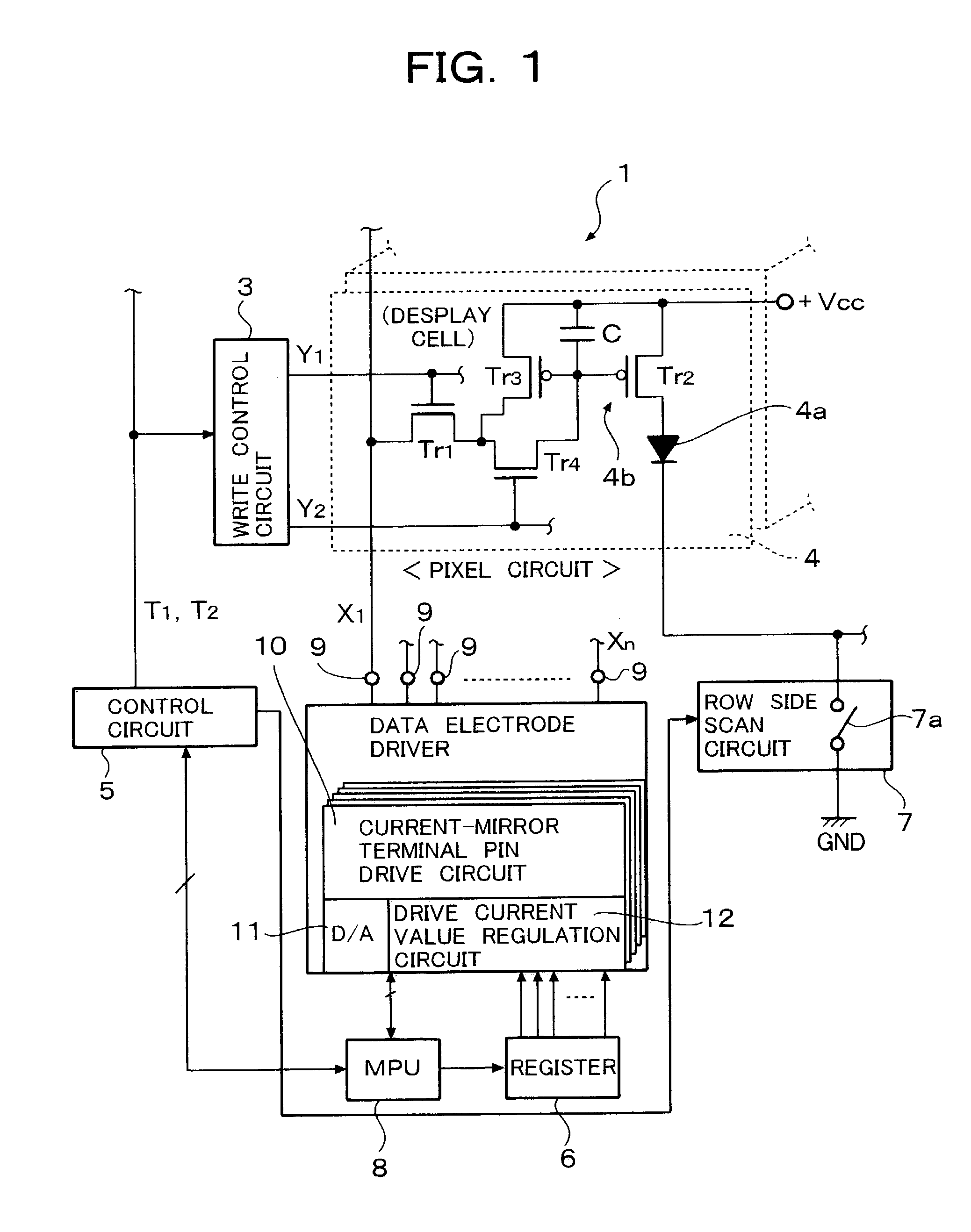

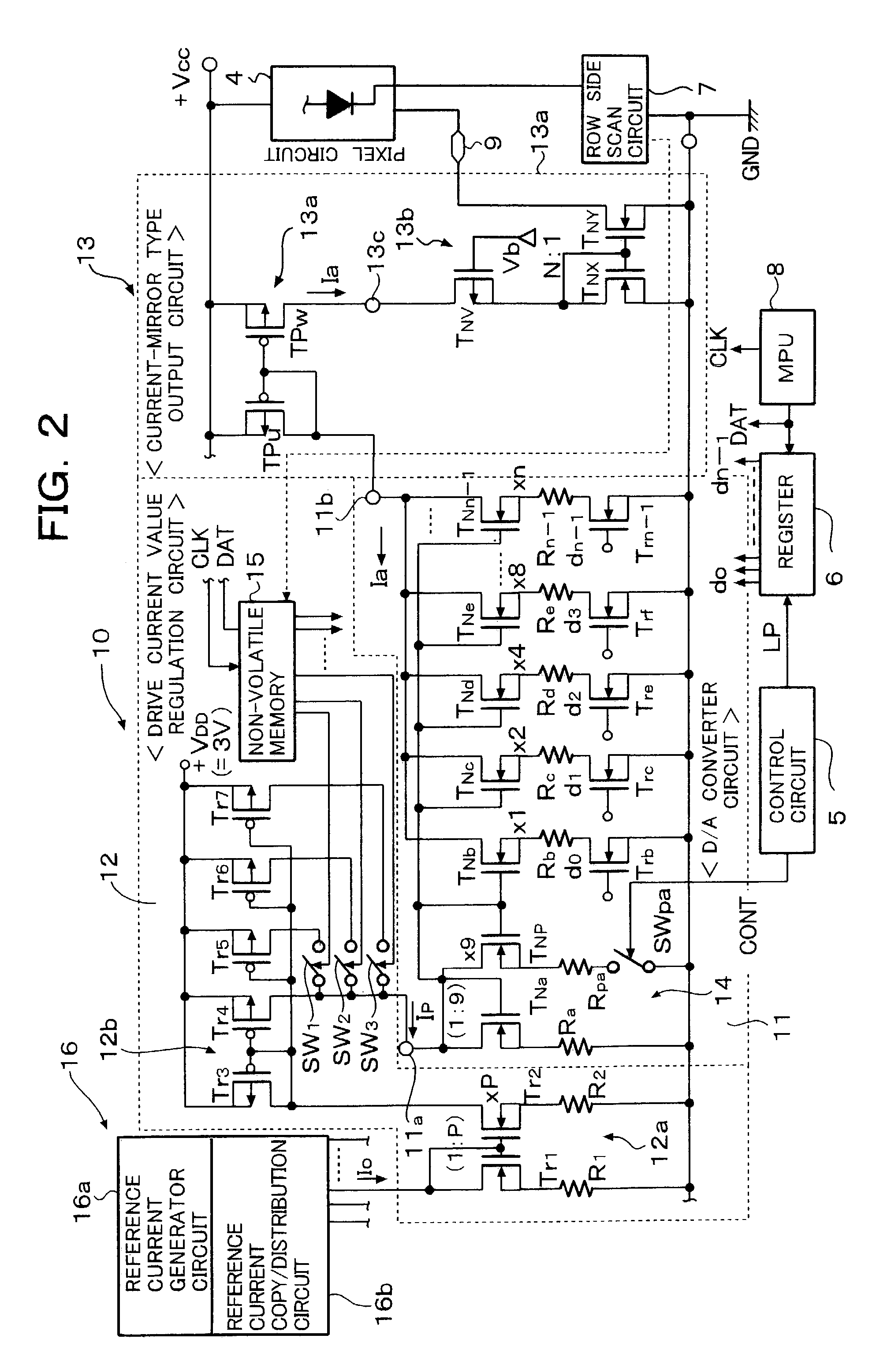

Drive circuit of active matrix type organic EL panel and organic EL display device using the same drive circuit

ActiveUS7109953B2Reduce brightness unevennessSuitableCathode-ray tube indicatorsInput/output processes for data processingActive matrixControl line

A drive current value is regulated by a current value regulator circuit of a current drive circuit provided externally of each pixel circuit, so that control lines for a program control provided in order to unify operating threshold values of drive transistors becomes unnecessary. Therefore, the number of transistors of each pixel circuit can be reduced and the circuit size of each pixel circuit can be reduced thereby.

Owner:ROHM CO LTD

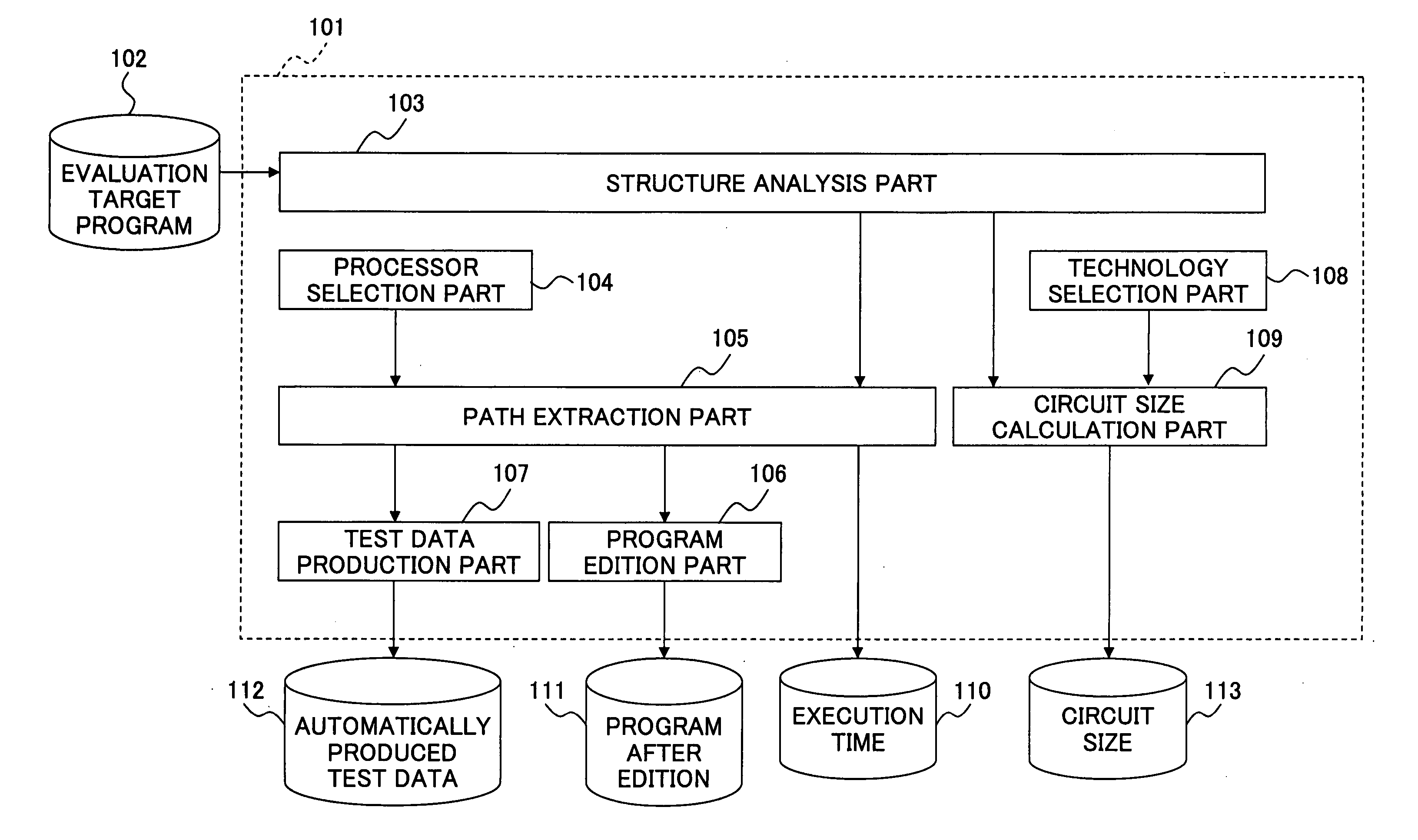

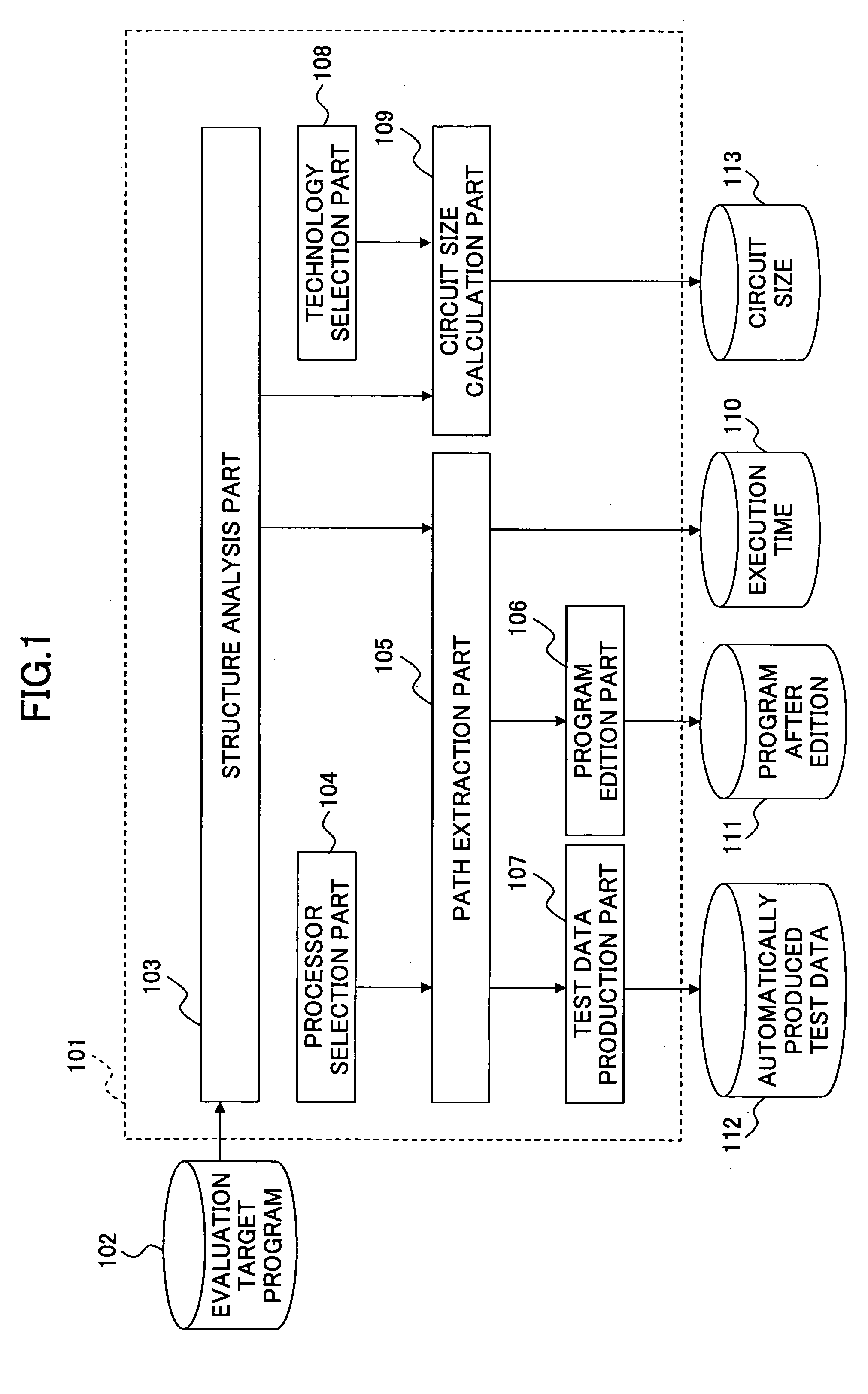

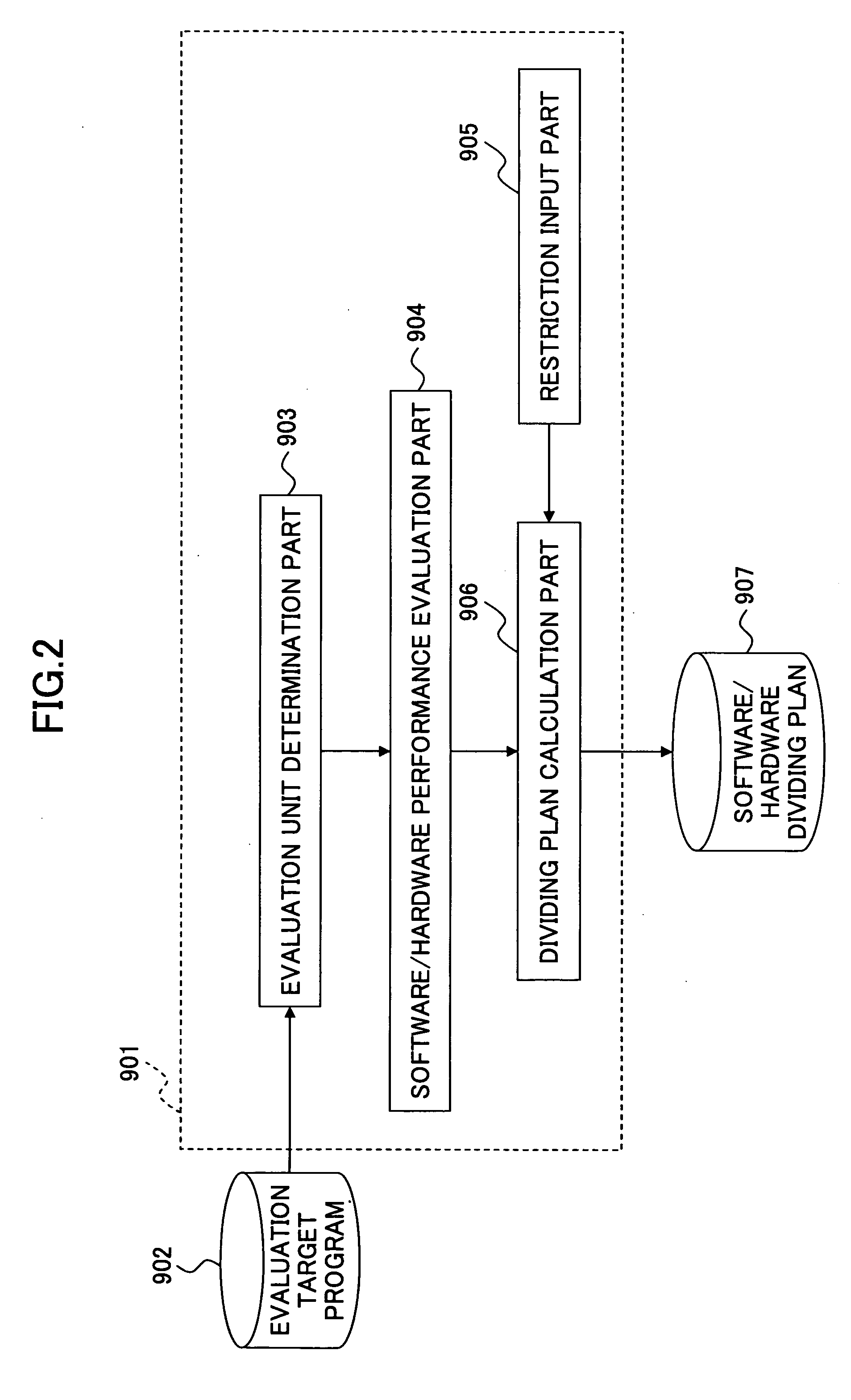

Data processing device designing method, data processing device designing apparatus, program and computer readable information recording medium

InactiveUS20050187750A1Easy to calculateMaximum required execution timeHardware monitoringCAD circuit designParallel computingDesign methods

A method includes steps of calculating, for each predetermined operation included in a program, an execution time required when the operation is executed by a predetermined processor, or calculating, for each predetermined operation included in the program, a circuit size required when the operation is realized in a form of hardware according to a predetermined technology; and calculating, for the entirety of the predetermined program or operations corresponding to a part the entirety of the predetermined program, a total execution time required when the entirety of the predetermined program is executed by the predetermined processor, as a result of applying in sequence the required execution time, or calculating, for the entirety of the predetermined program or operations corresponding to a part the entirety of the predetermined program, a total circuit size required when the entirety of the predetermined program or programs corresponding to a part of the entirety of the predetermined program, as a result of applying in sequence the required circuit size.

Owner:FUJITSU LTD

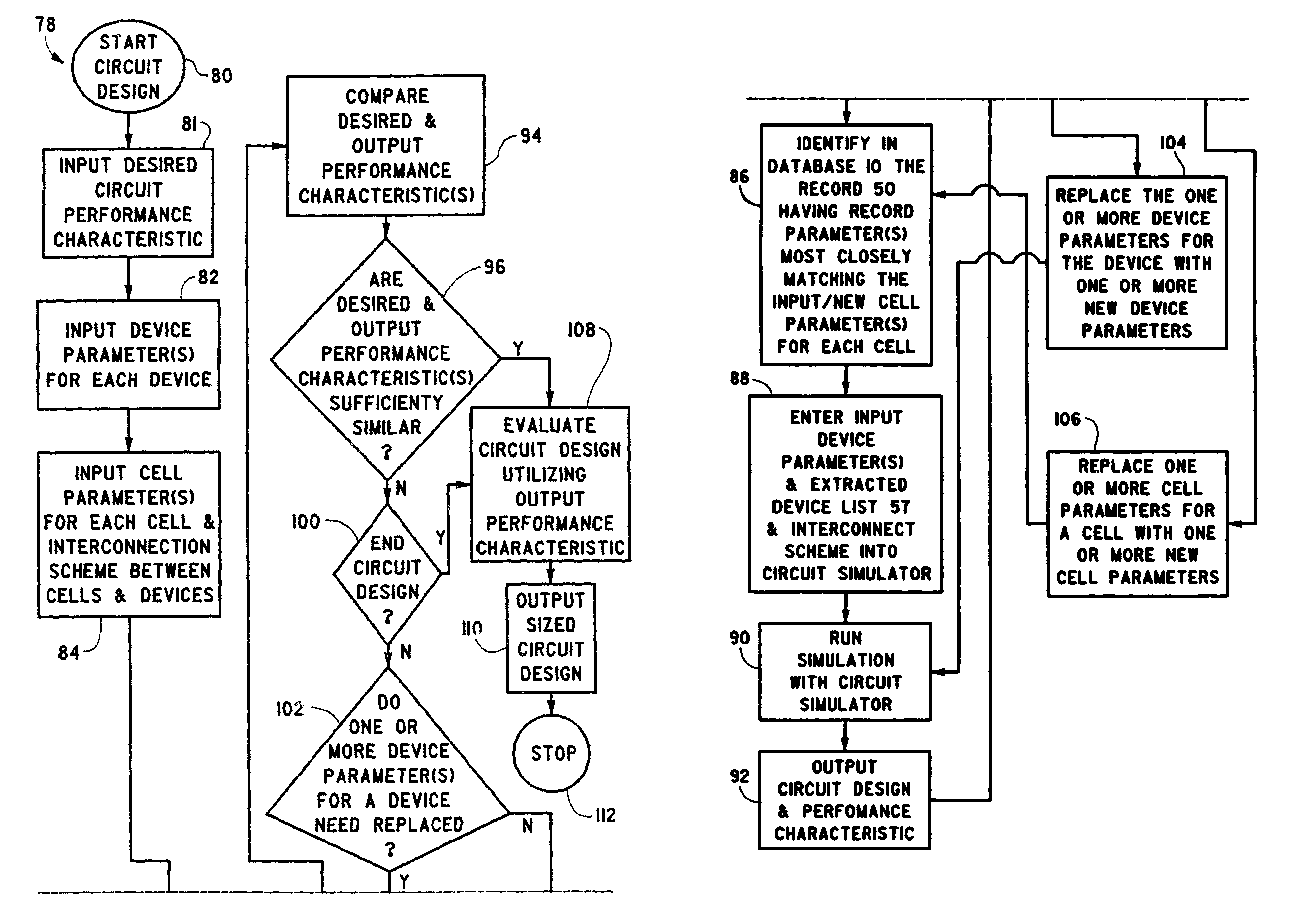

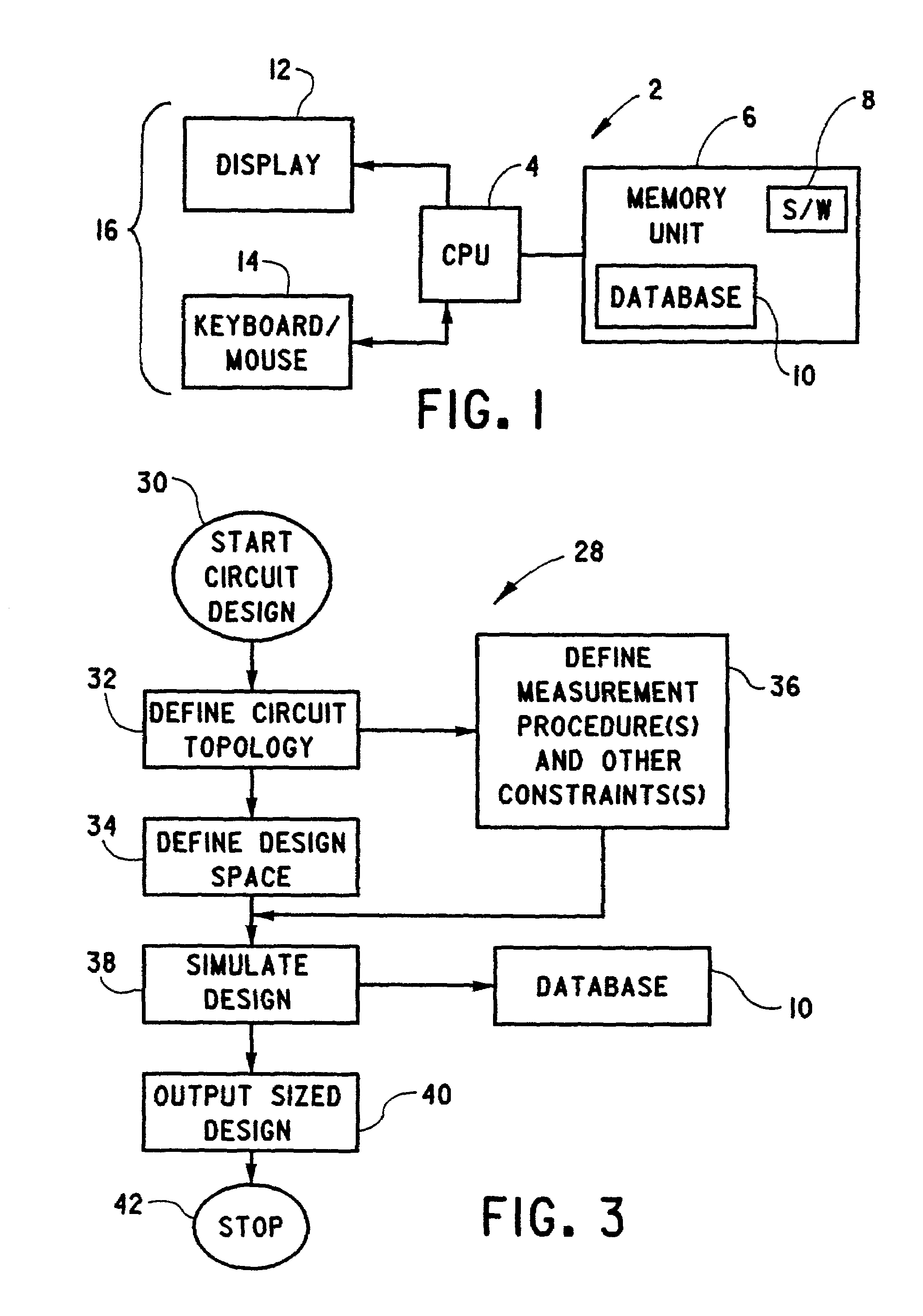

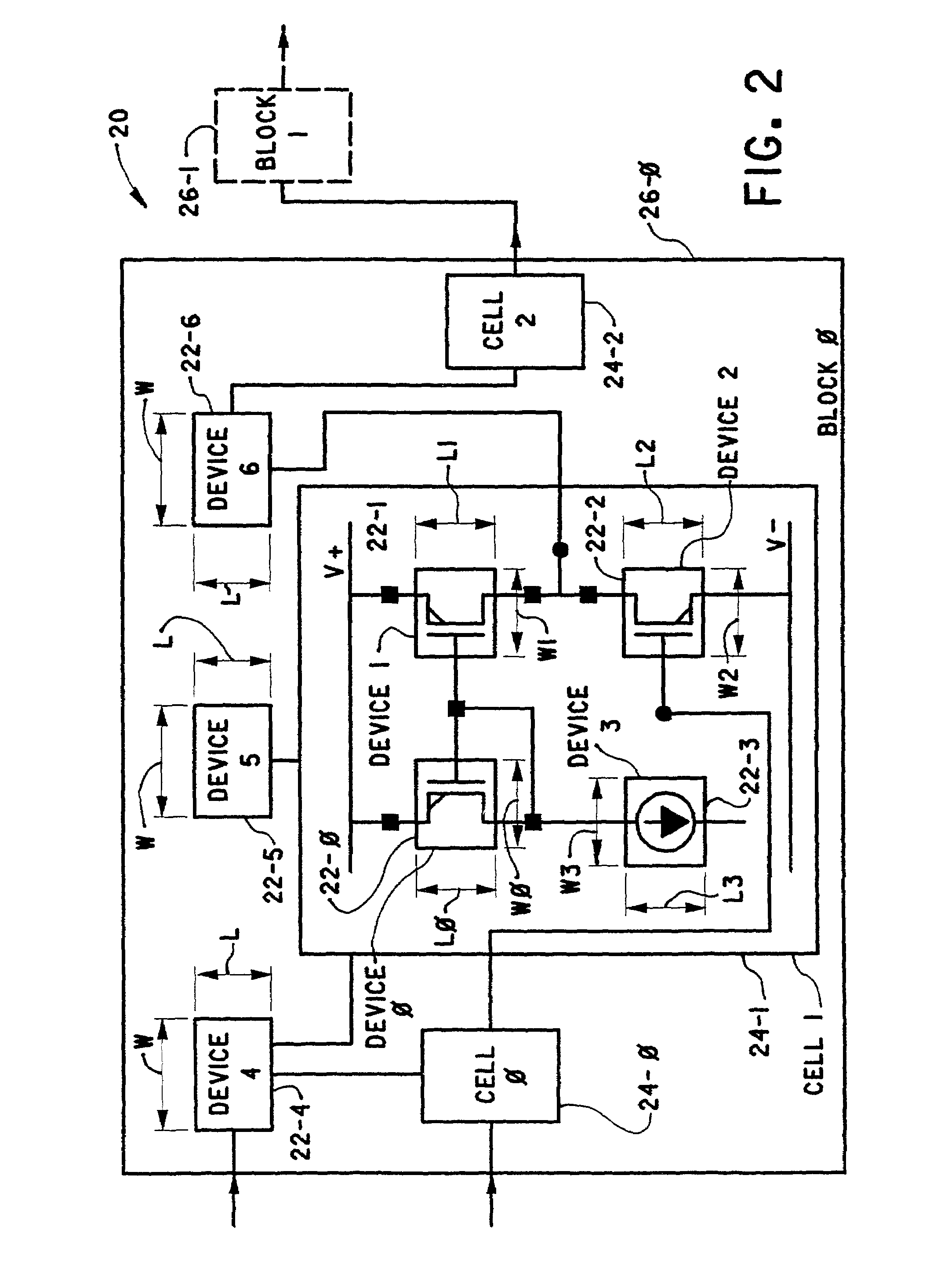

Method for automatically sizing and biasing circuits by means of a database

InactiveUS7058916B2Detecting faulty computer hardwareComputer programmed simultaneously with data introductionData miningCell parameter

In a method of automatically sizing and biasing a circuit, a database is provided including a plurality of records related to cells that can be utilized to form an integrated circuit. A cell parameter of a cell for a circuit is selected and compared to cell parameters residing in the records stored in the database. One record in the database is selected based upon this comparison and a performance characteristic of the circuit is determined from this record.

Owner:CADENCE DESIGN SYST INC

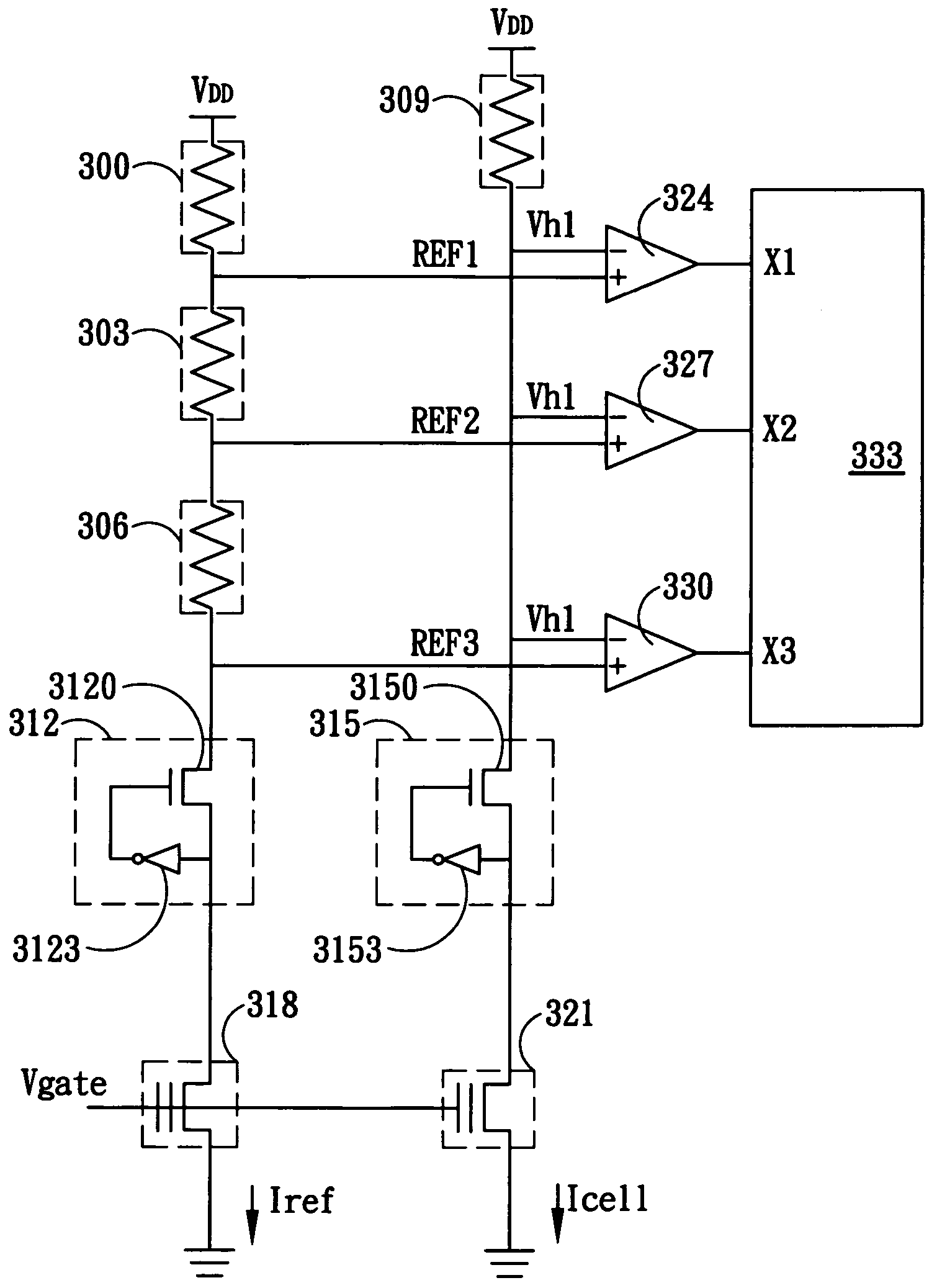

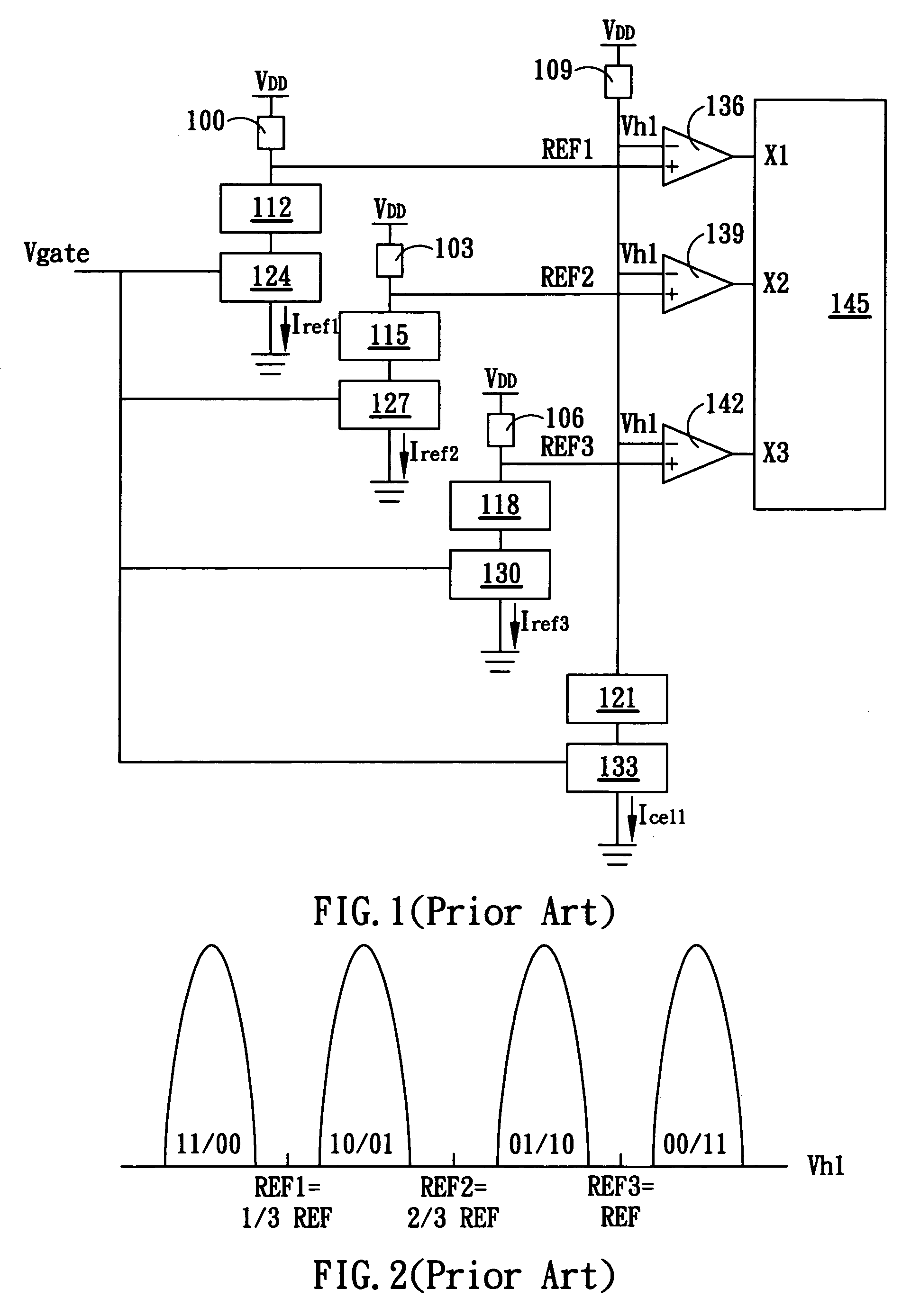

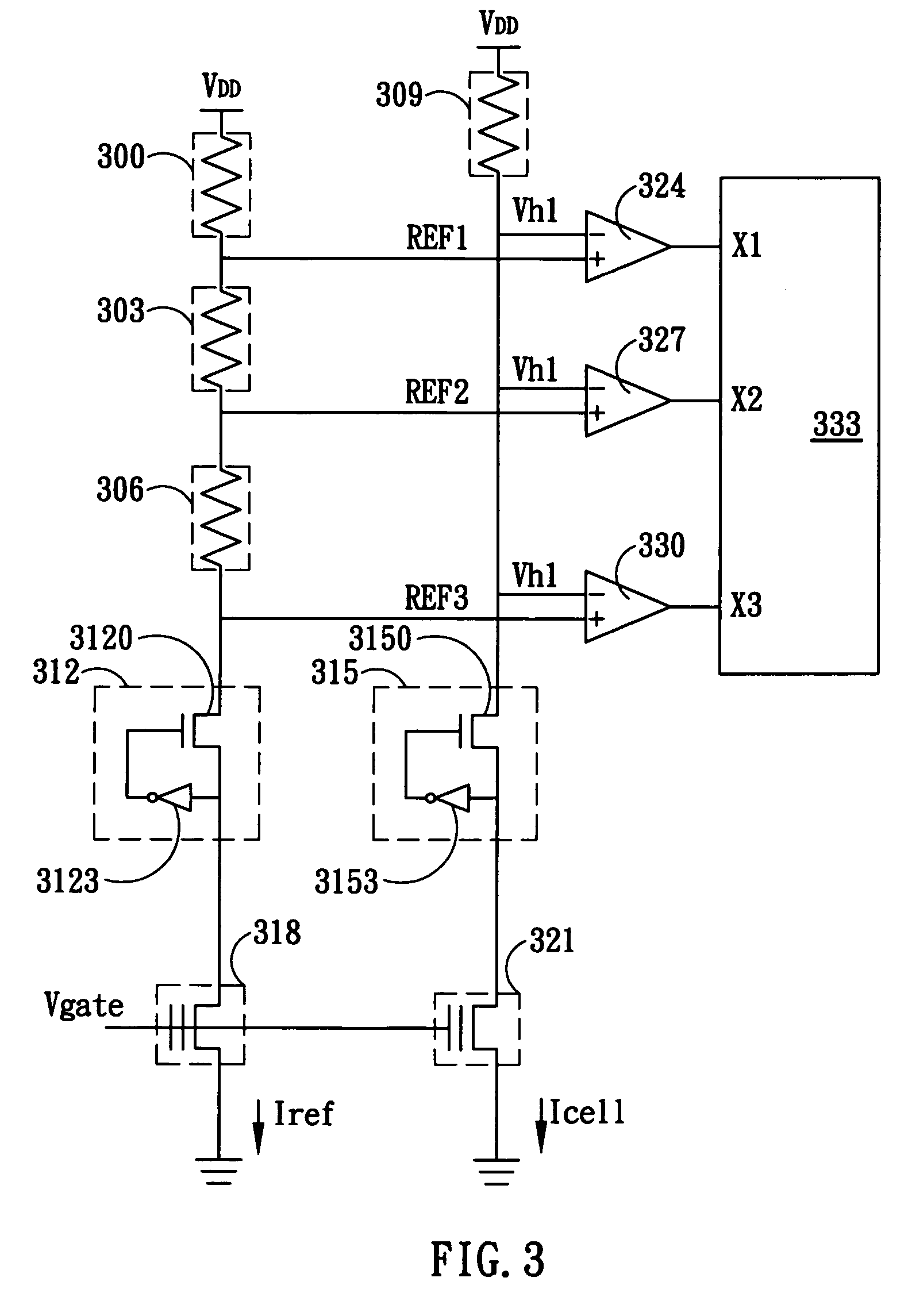

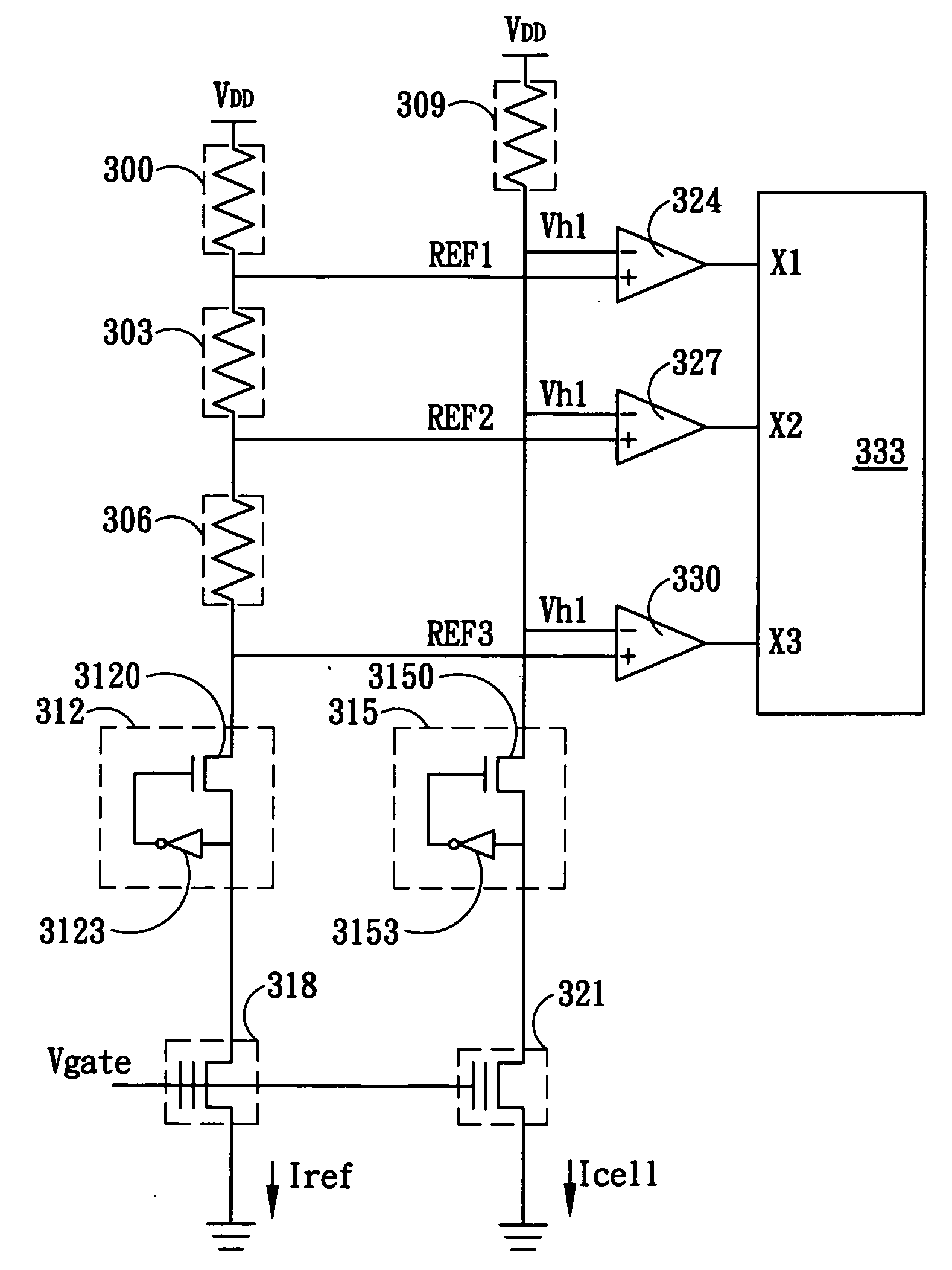

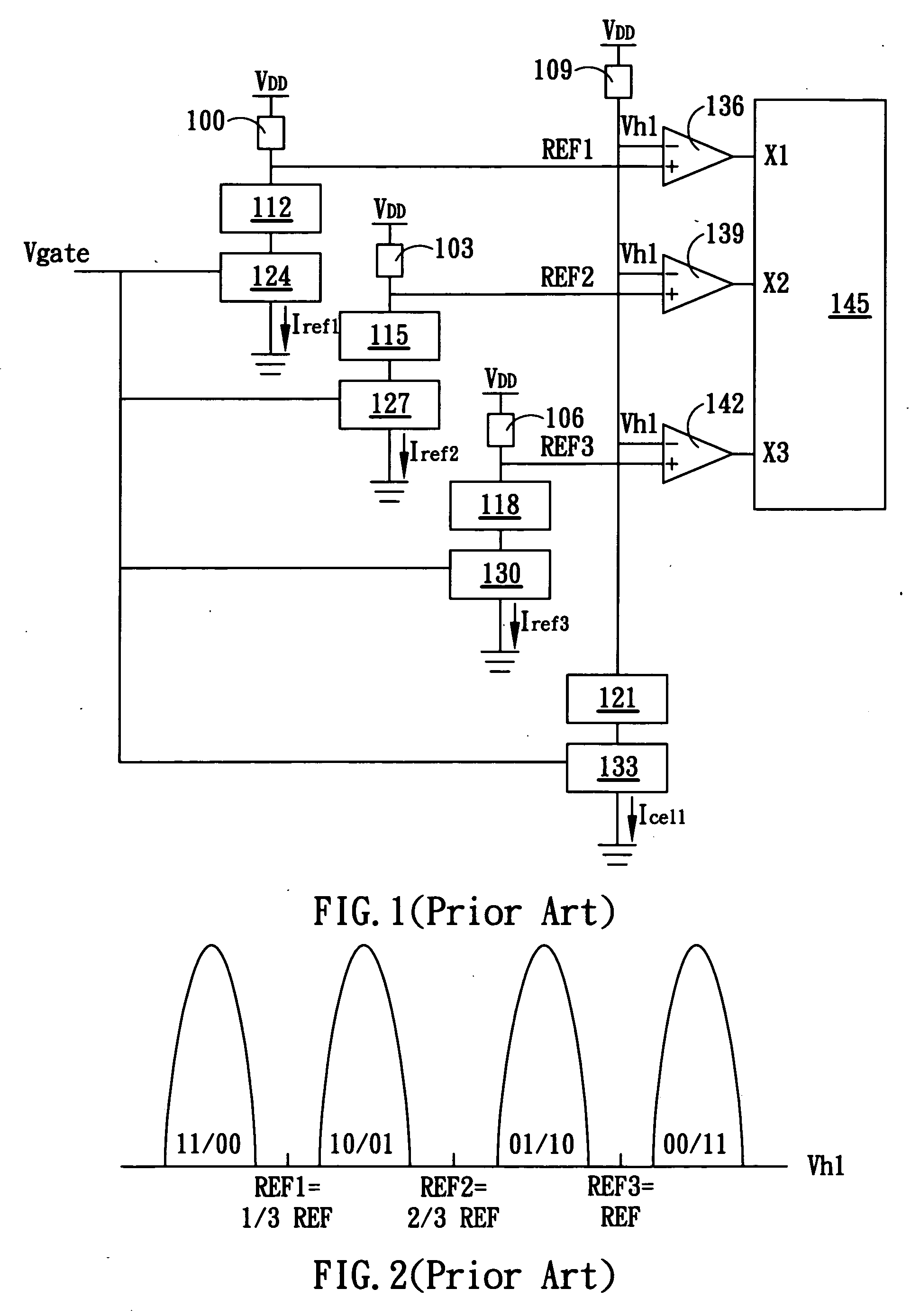

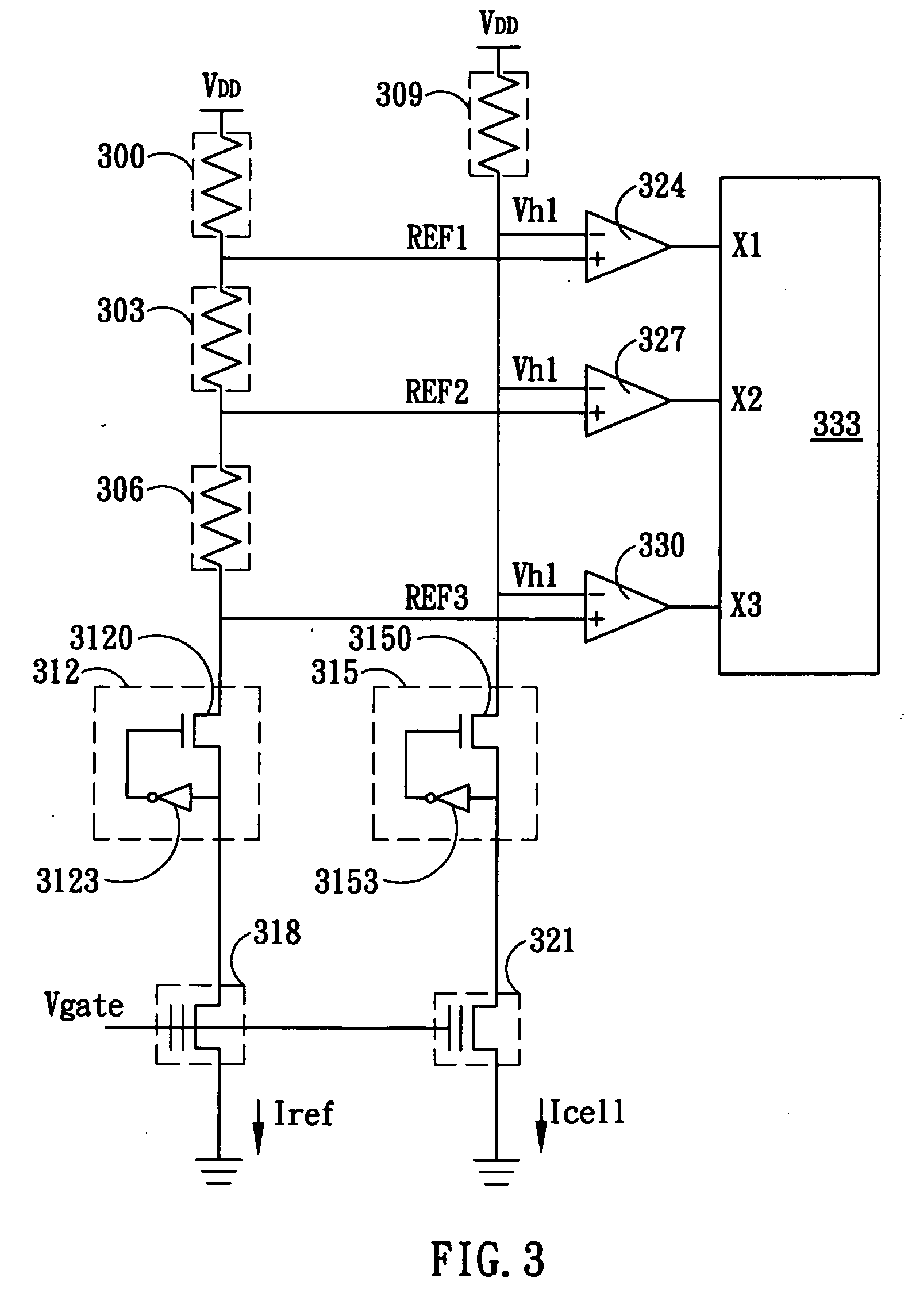

Sensing circuit for multi-level flash memory

InactiveUS7369441B2Less testing timeEfficient mass productionRead-only memoriesDigital storageCircuit sizingVoltage generator

A sensing circuit for multi-level flash memory is disclosed. The advantages of the sensing circuit are reducing the circuit size, reducing the testing time for tuning reference voltage and maintaining a constant difference between two approximate reference voltages. The sensing circuit comprises a reference voltage generator which includes a number of serial connected resistive devices and provides several reference voltages by voltage division; a data saving circuit outputs a data voltage; a comparing circuit compares the data voltage with the several reference voltages to output a comparing signal; a decoder receives and then decodes the comparing signal to output the data.

Owner:WINBOND ELECTRONICS CORP

Sensing circuit for multi-level flash memory

InactiveUS20070025146A1Reduce circuit sizeShorten test timeRead-only memoriesDigital storageVoltage generatorCircuit sizing

A sensing circuit for multi-level flash memory is disclosed. The advantages of the sensing circuit are reducing the circuit size, reducing the testing time for tuning reference voltage and maintaining a constant difference between two approximate reference voltages. The sensing circuit comprises a reference voltage generator which includes a number of serial connected resistive devices and provides several reference voltages by voltage division; a data saving circuit outputs a data voltage; a comparing circuit compares the data voltage with the several reference voltages to output a comparing signal; a decoder receives and then decodes the comparing signal to output the data.

Owner:WINBOND ELECTRONICS CORP

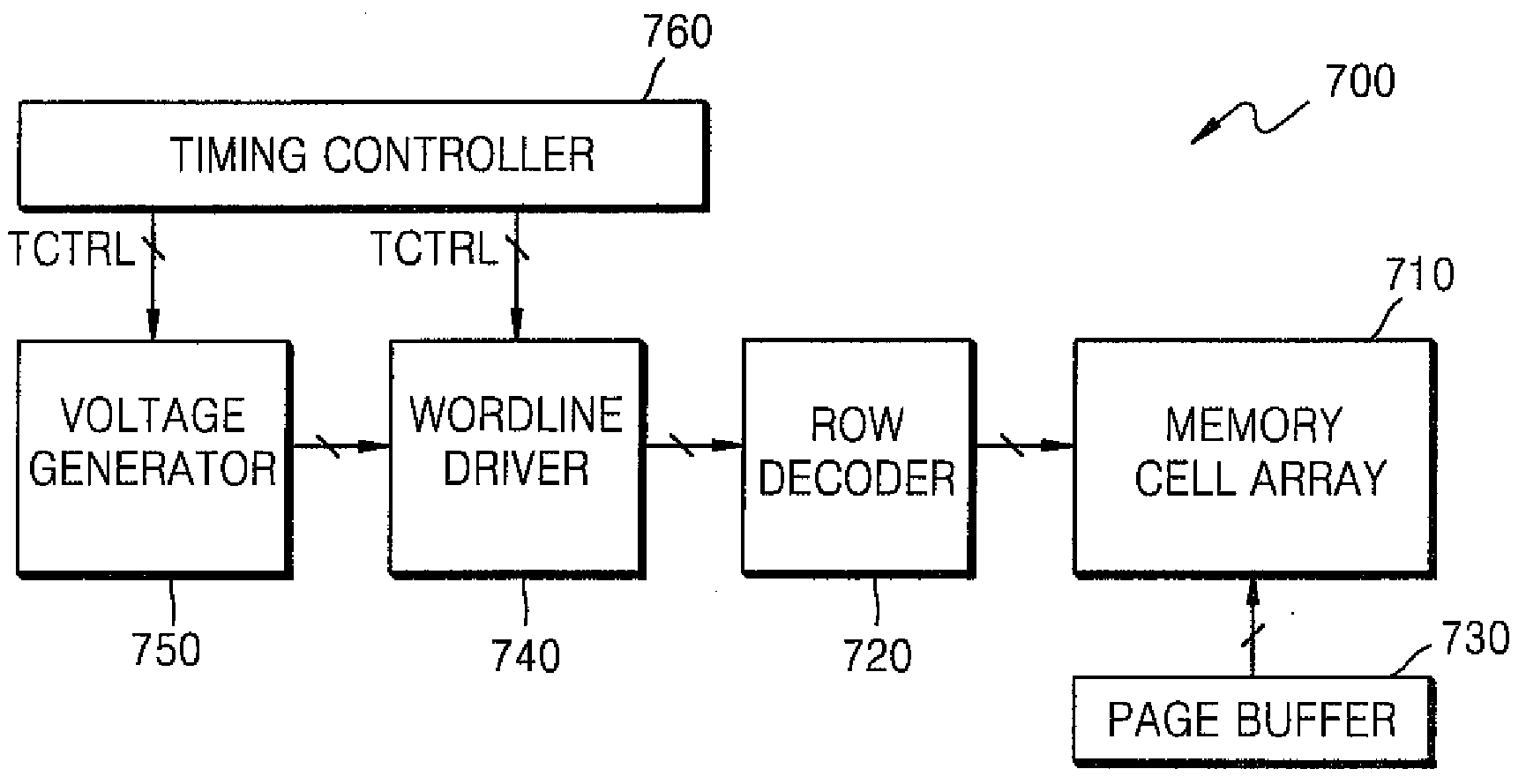

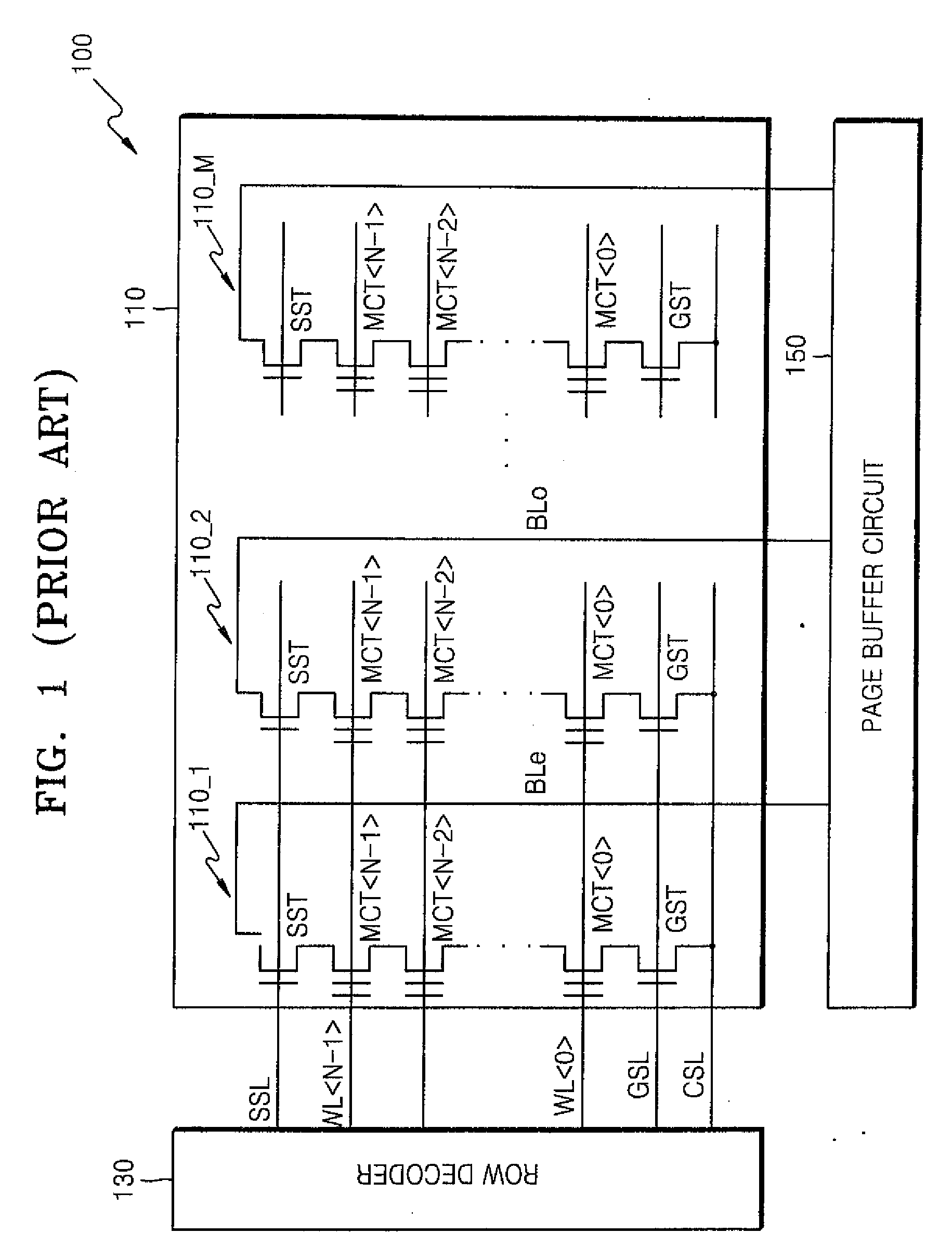

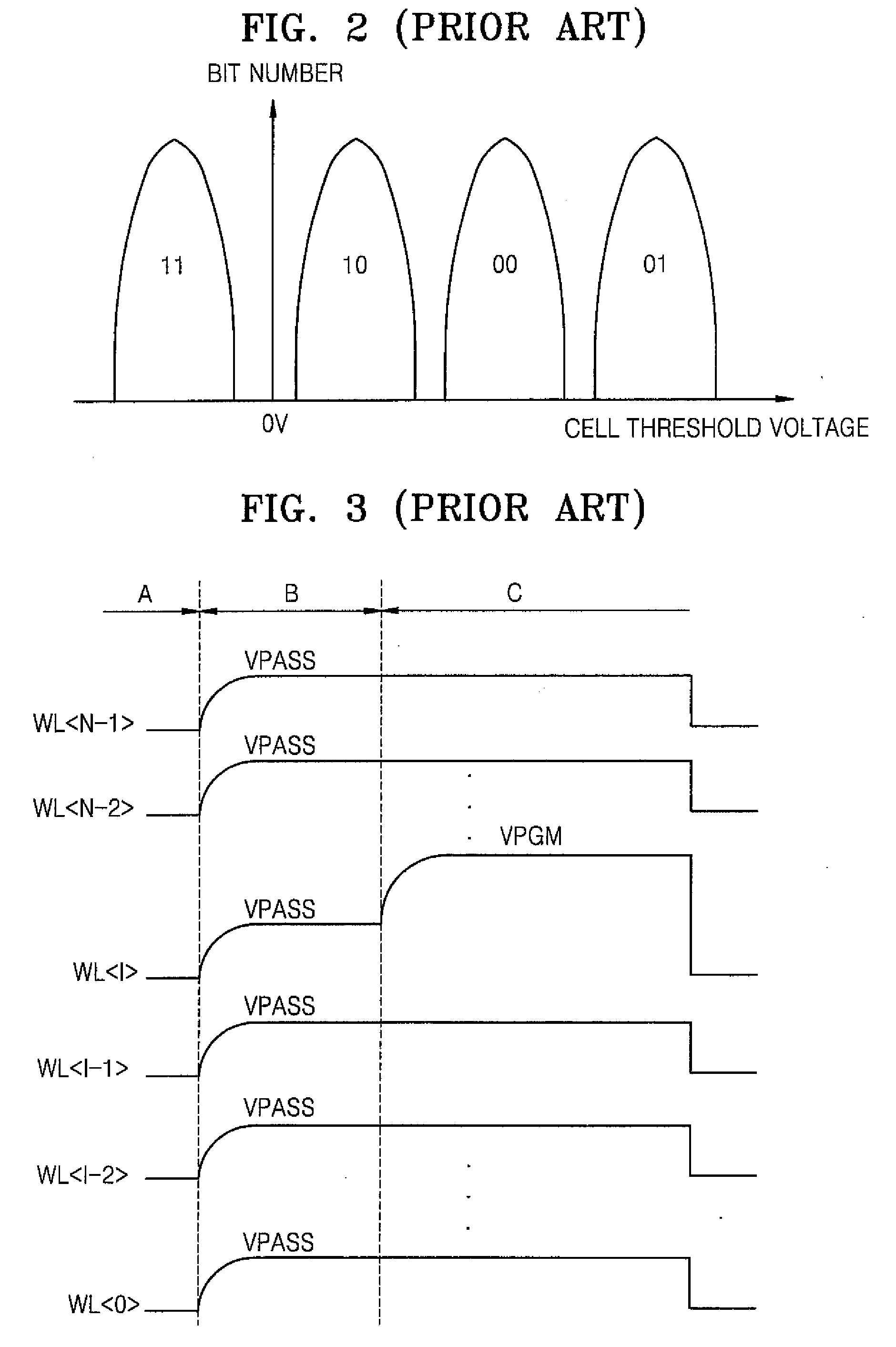

Method of programming a nonvolatile memory device using hybrid local boosting

A method of programming a nonvolatile memory device using hybrid local boosting which includes a plurality of cell strings each having a plurality of electrically erasable and programmable memory cells connected in series and a plurality of wordlines respectively connected to control gates of the plurality of memory cells. The address of a selected cell that is to be programmed is received. A determination is made as to whether a selected wordline connected to the selected cell is located above or under a reference wordline based on the received address. The selected cell is programmed using local boosting when the selected wordline corresponds to the reference wordline or is located above the reference wordline. The selected cell is programmed using self-boosting when the selected wordline is located under the reference wordline. The programming method reduces circuit size of a nonvolatile memory device employing the programming method and efficiently prevents program disturbance due to charge sharing.

Owner:SAMSUNG ELECTRONICS CO LTD

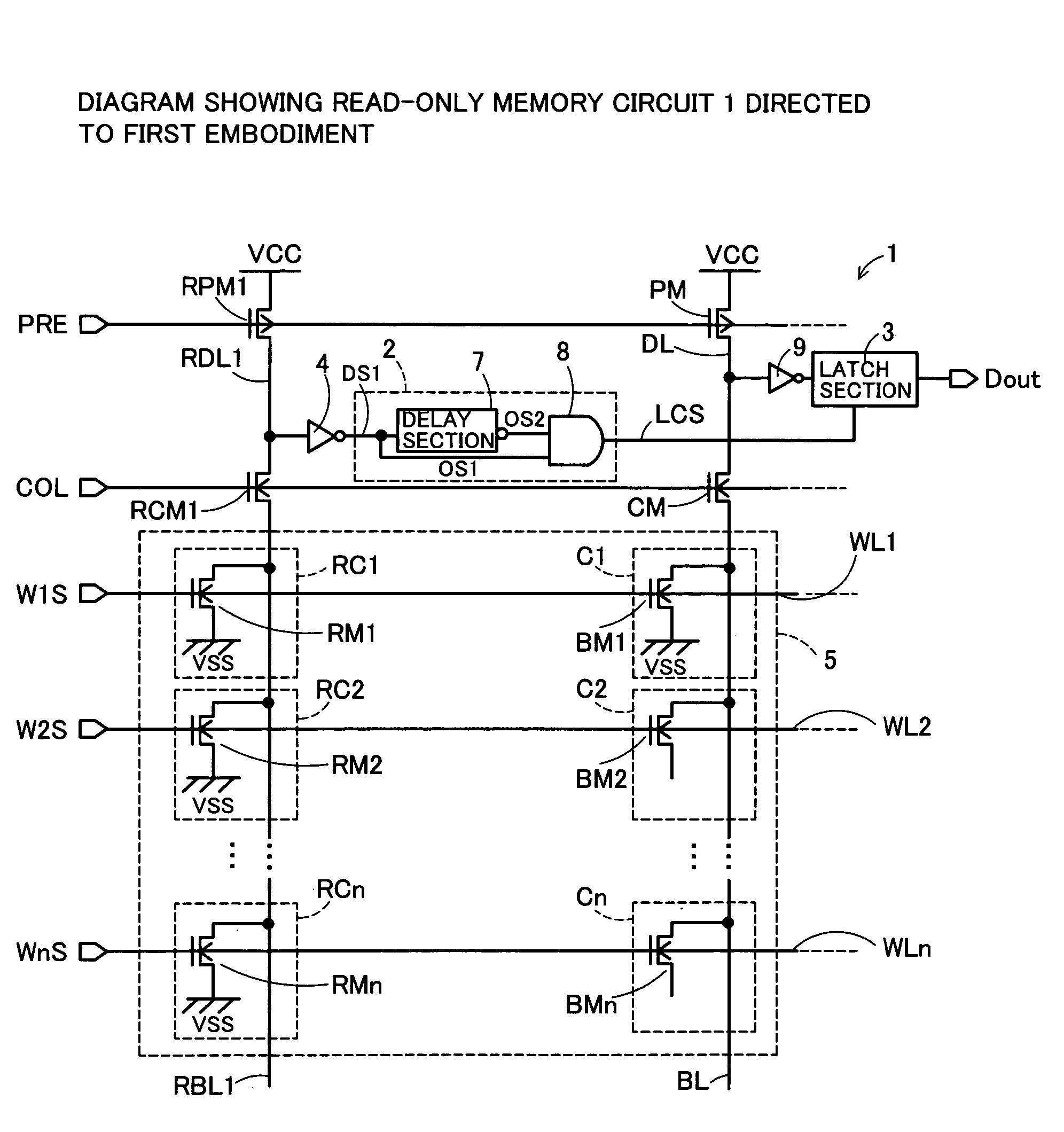

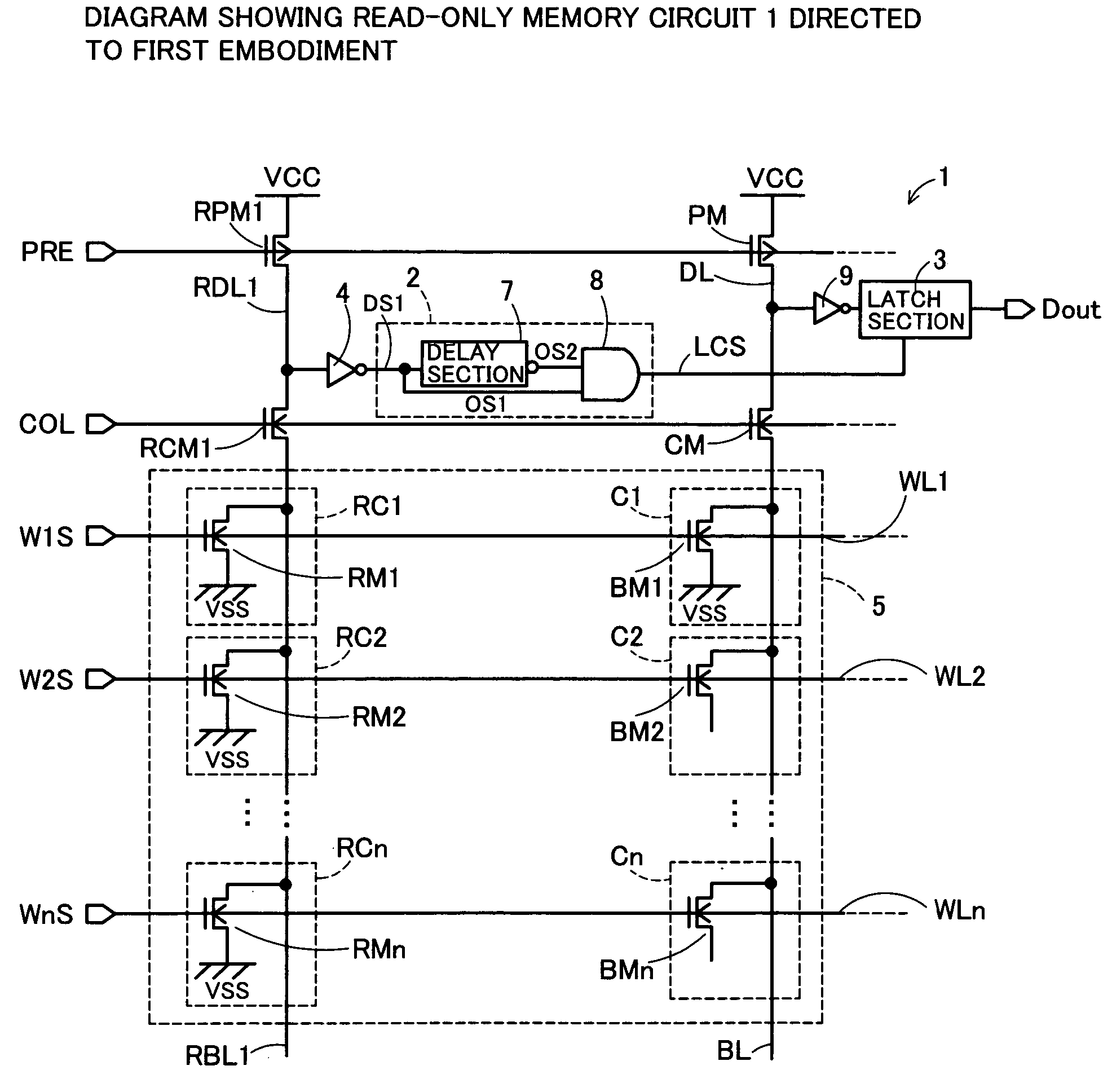

Semiconductor memory device and control method for semiconductor memory device

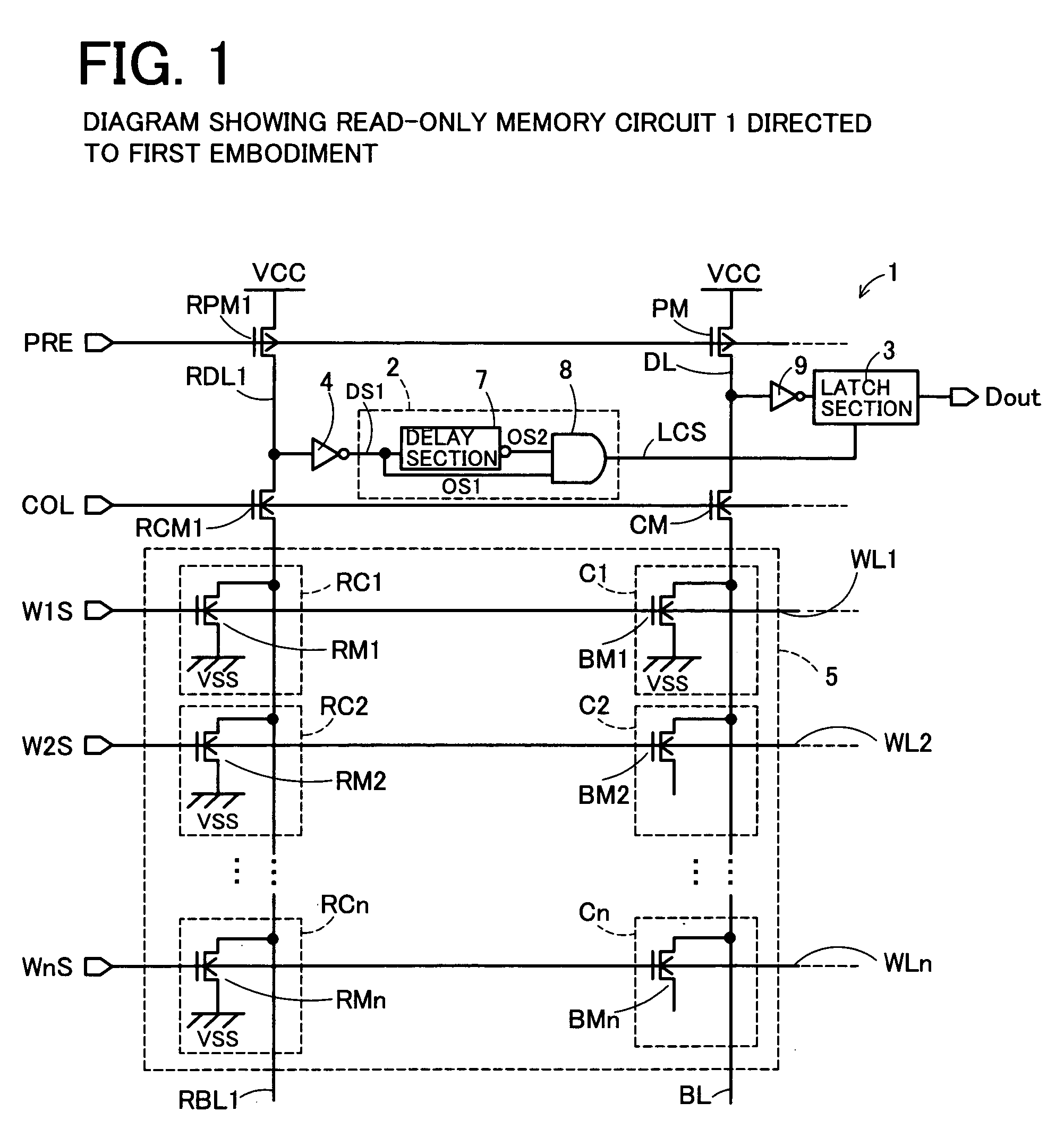

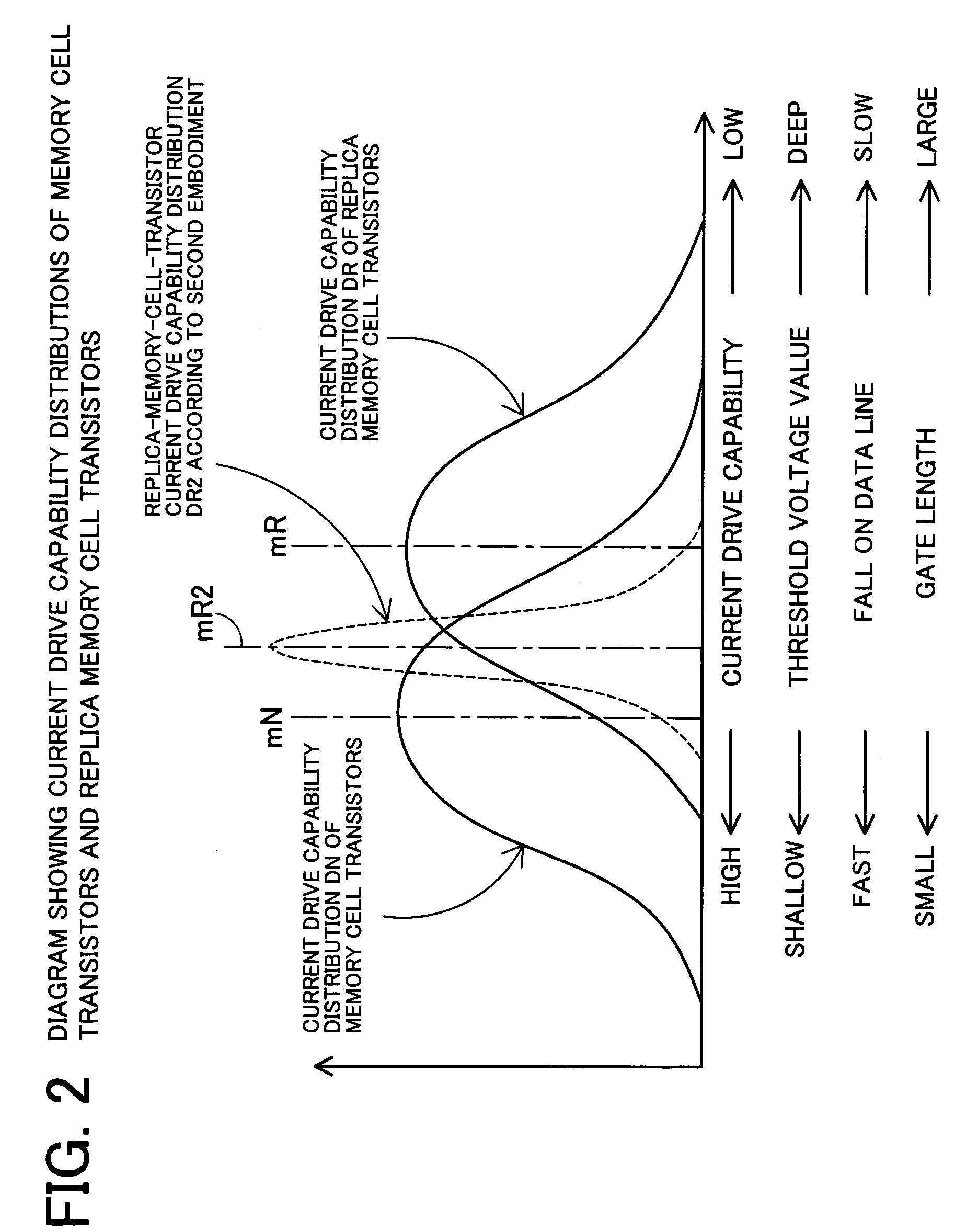

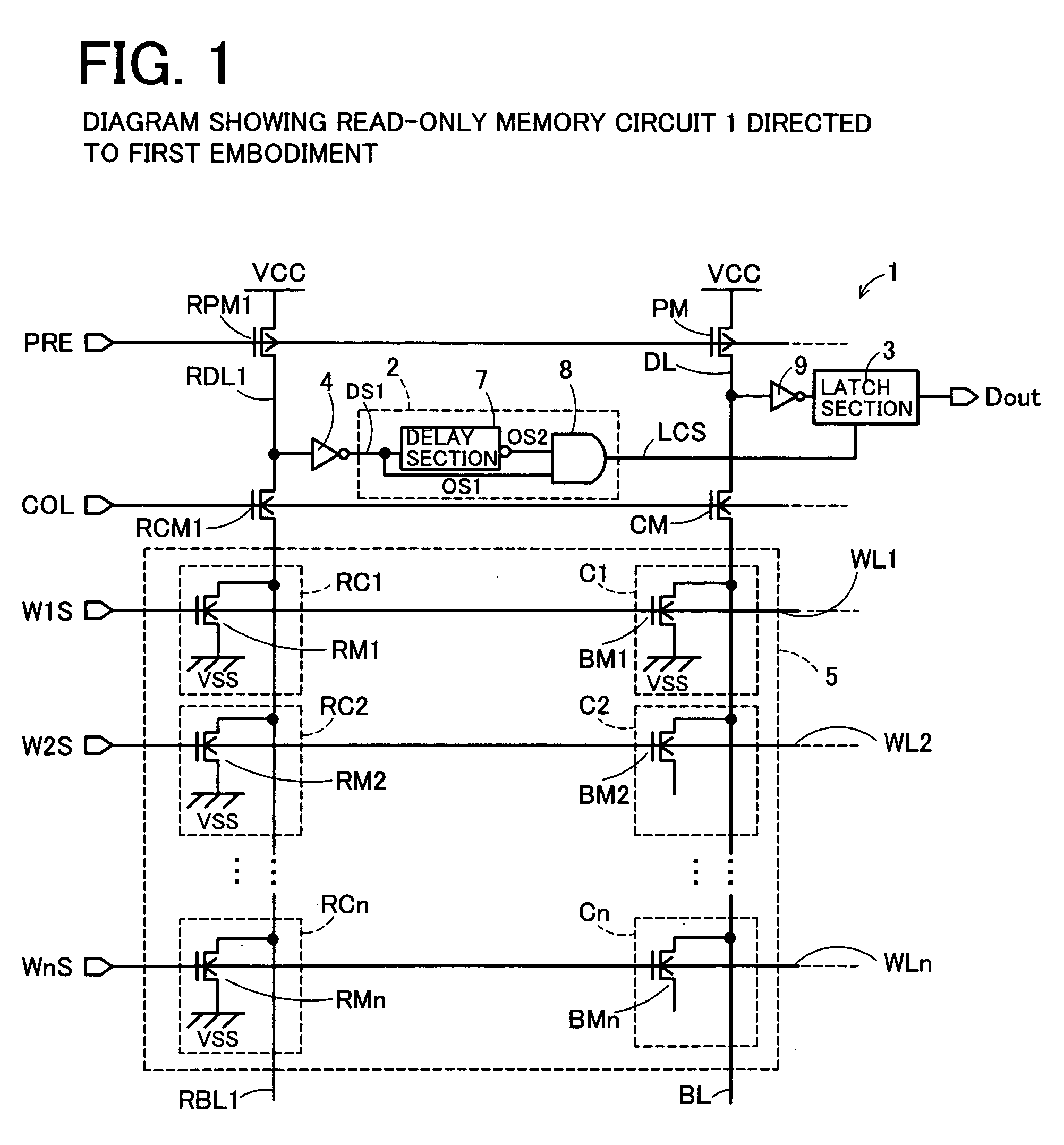

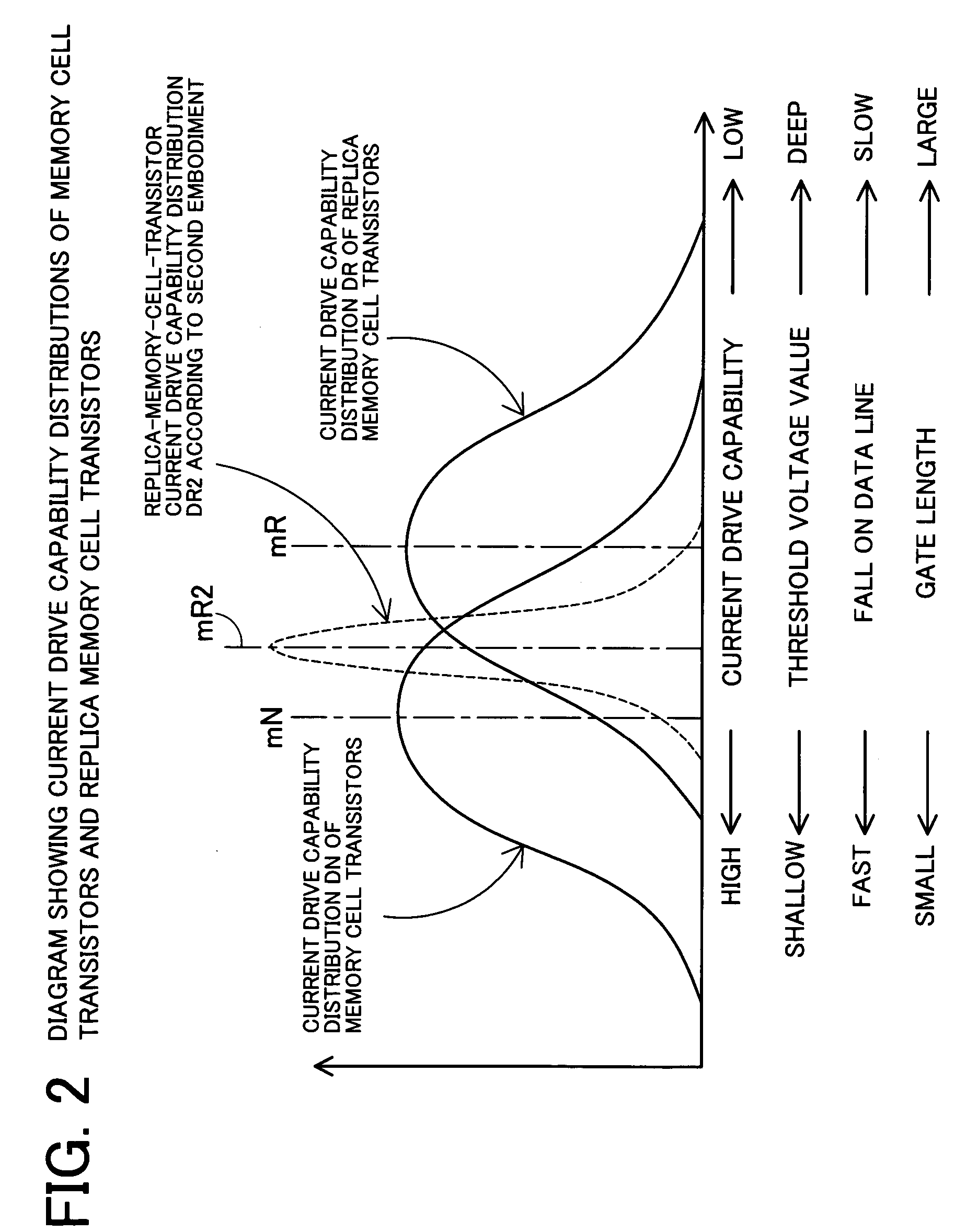

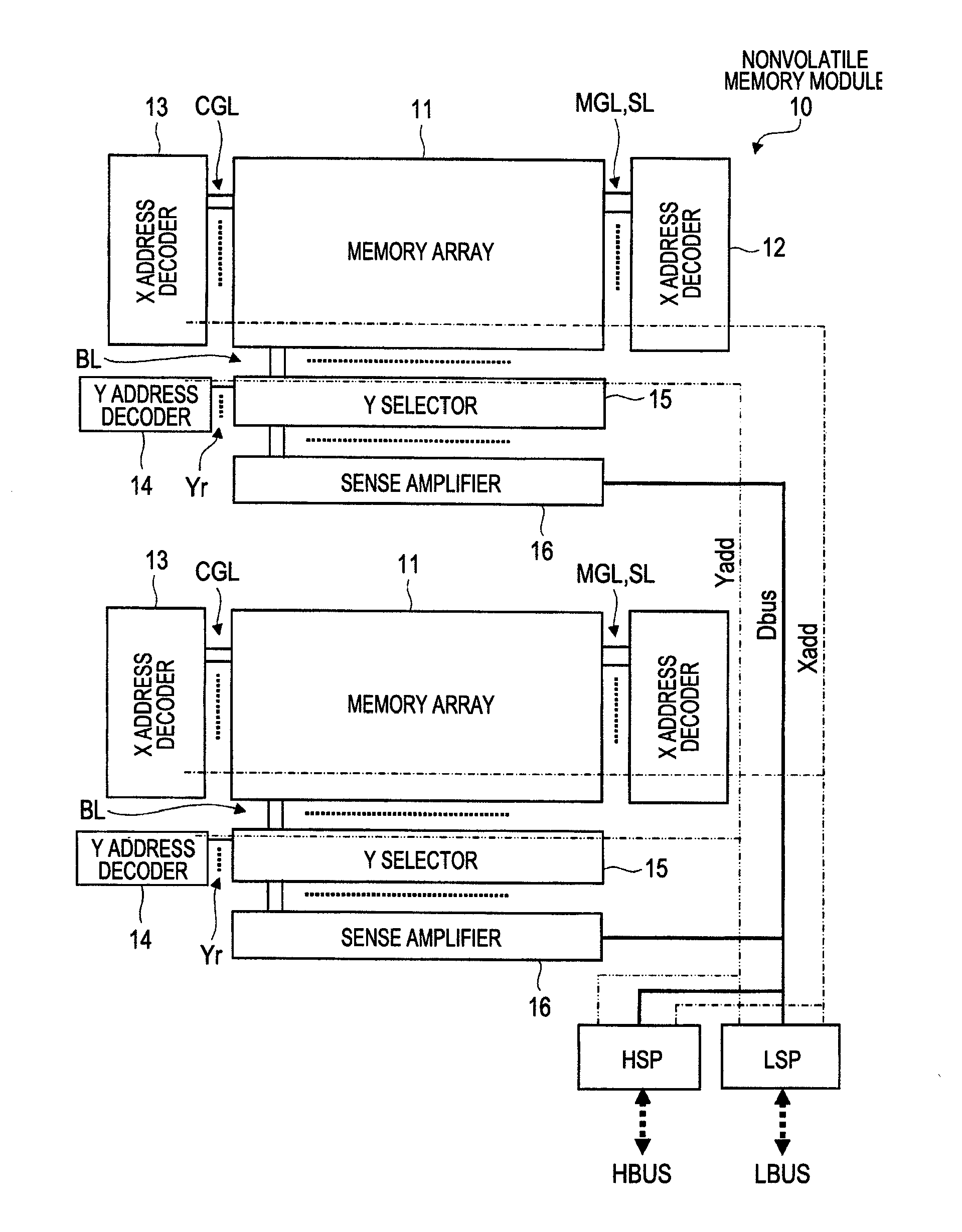

InactiveUS7149102B2Reduce incidenceReduced drive capability requirementsRead-only memoriesDigital storageStart timeControl signal

Provided is a semiconductor memory device using a single-bit line method that determines read operation timing in accordance with operation of a replica bit line. Further provided is a control method for the semiconductor memory device. Even when a transistor property fluctuation has occurred, the semiconductor memory device and the control method are capable of preventing, for example, increases in access time and circuit size and concurrently capable of reducing the occurrence probability of data readout error. The gate lengths of replica memory cell transistors are set as being values greater than the gate length of memory cell transistors. Thereby, a distribution center of a current drive capability distribution of the replica memory cell transistors is set lower than a distribution center of a current drive capability distribution of the memory cell transistors. Consequently, an occurrence probability of a delay in a voltage-fall start time on a regular data line can be reduced to be lower in comparison to a transmission timing of a latch control signal.

Owner:SOCIONEXT INC

Multi-layer power distribution network of high-frequency printed boards based on accessory resistive films

InactiveCN104319448ASmall sizeReduce weightPrinted circuit detailsWaveguidesEngineeringLine structure

The invention provides a multi-layer power distribution network of high-frequency printed boards based on accessory resistive films. The multi-layer power distribution network of the copper-clad plates based on the accessory resistive films is formed by overlaying multiple layers of copper-clad plates, each layer of the multi-layer power distribution network is arranged to be of a strip line structure, lower-layer media of the strip line structures are core plates, and upper-layer media of the strip line structures are prepregs; stepped open grooves are formed in the multi-layer power distribution network to lead out signal lines so that the multi-layer power distribution network can be connected with other circuits conveniently; by utilizing a printed board multi-layer mixed pressing technology, the power distribution network and the other circuits are integrated through mixed pressing. By the adoption of the scheme, a lining plate and a shielding cavity are not needed, and the circuits are small in size and low in weight; isolating resistors are directly buried in the multiple layers of printed boards, punching is not needed, the isolating resistors are connected with a surface-layer resistor, different layers of the power distribution network are not affected mutually, and a power distribution network with more layers can be manufactured.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

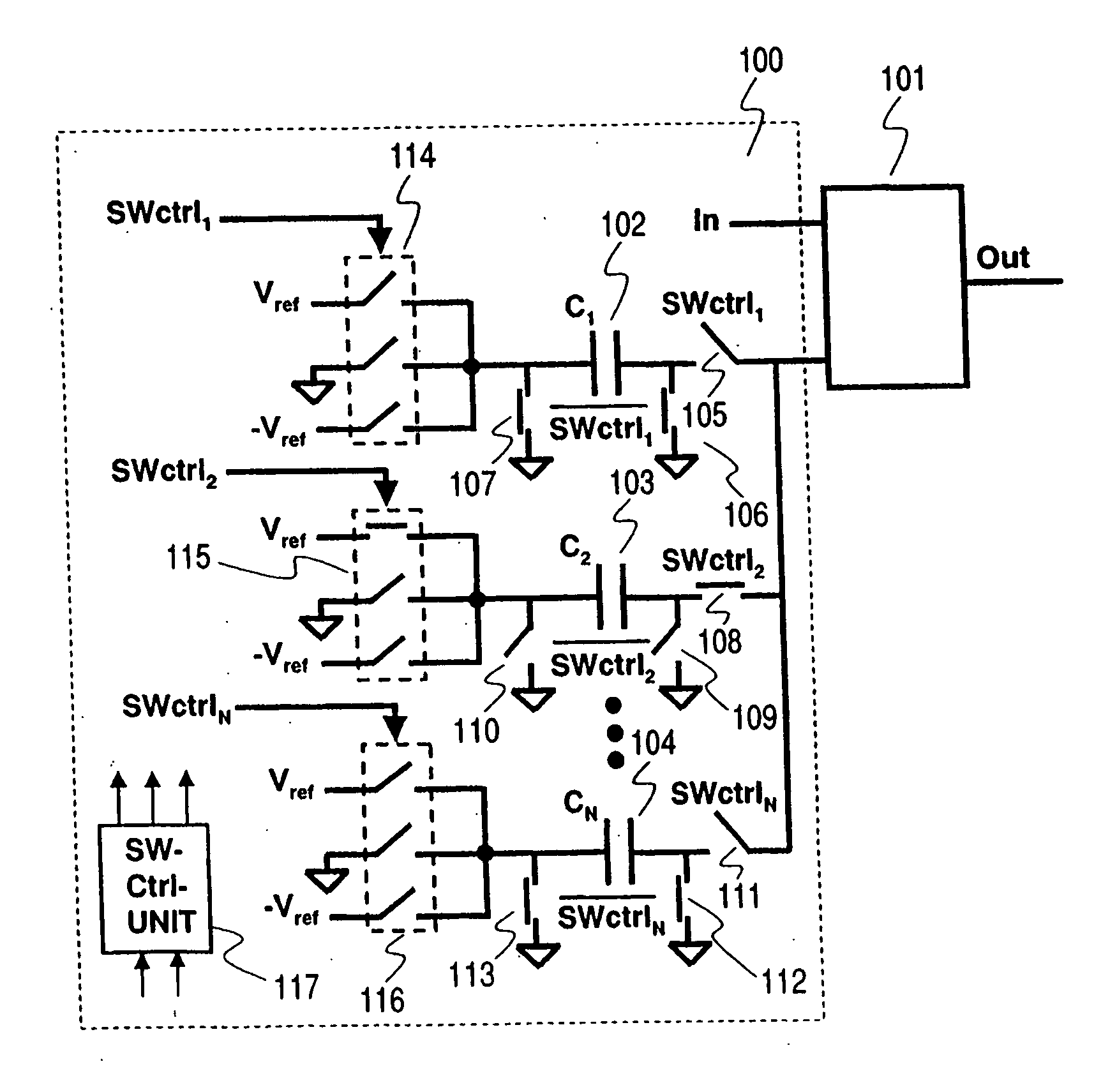

Analog-to-digital converter, method of controlling the same, and wireless transceiver circuit

InactiveUS20090015455A1Reduce the impactSmall capacitanceElectric signal transmission systemsAnalogue-digital convertersCapacitanceCircuit sizing

In an analog-to-digital converter, when a capacitive element with a small capacitance is used in order to reduce power consumption, the characteristics of the analog-to-digital converter deteriorate due to the variation in the specific accuracy. Further, the method of reducing the variation with the specific accuracy causes an increase in the size of the circuit and power consumption. An analog-to-digital converter includes an analog core unit having at least one capacitive element. The capacitive element includes a capacitive bank having plural capacitive element units having substantially the same capacitance value, and the capacitive bank is configured to select one capacitive element unit from the plural capacitive element units with substantially equal probability.

Owner:HITACHI LTD

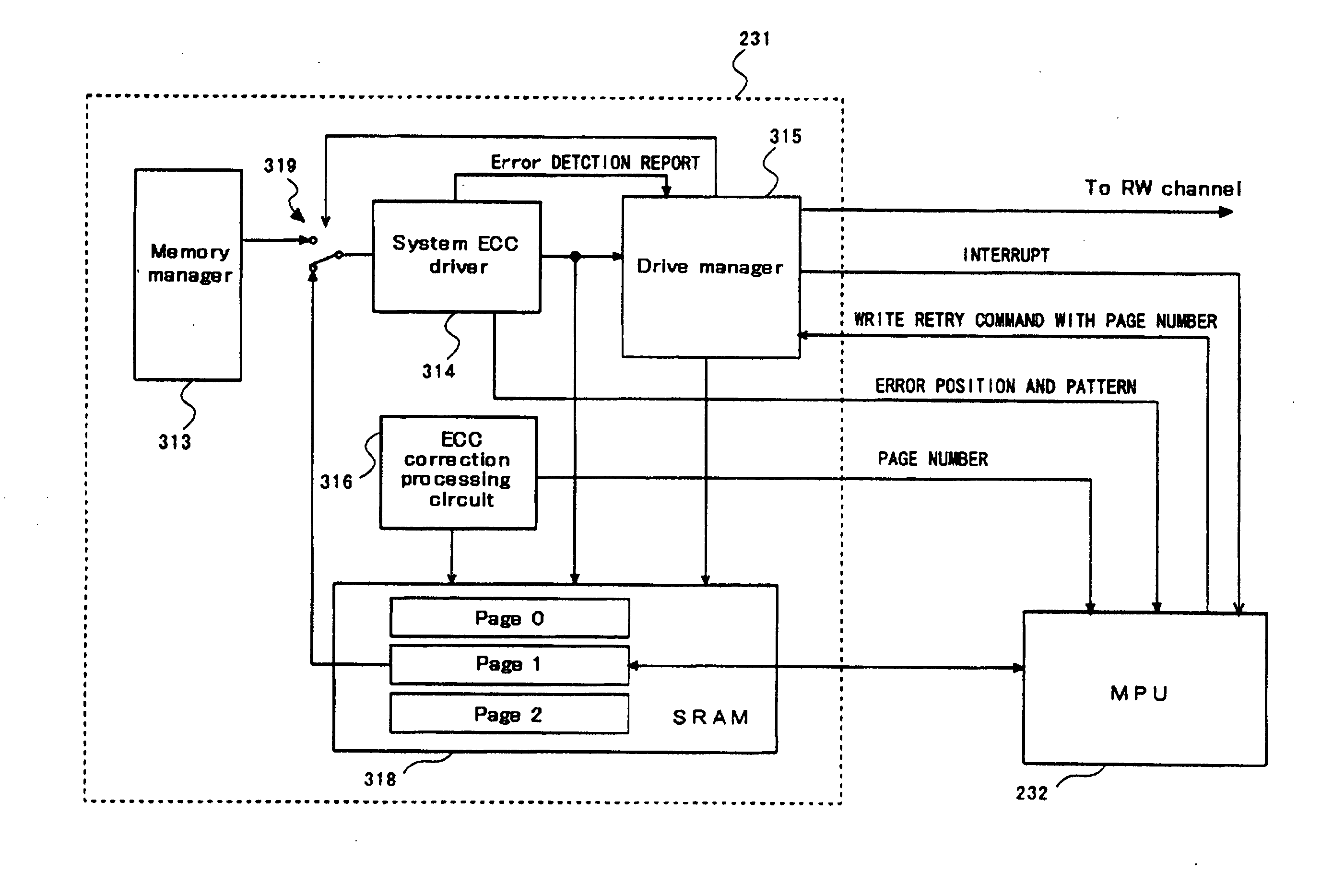

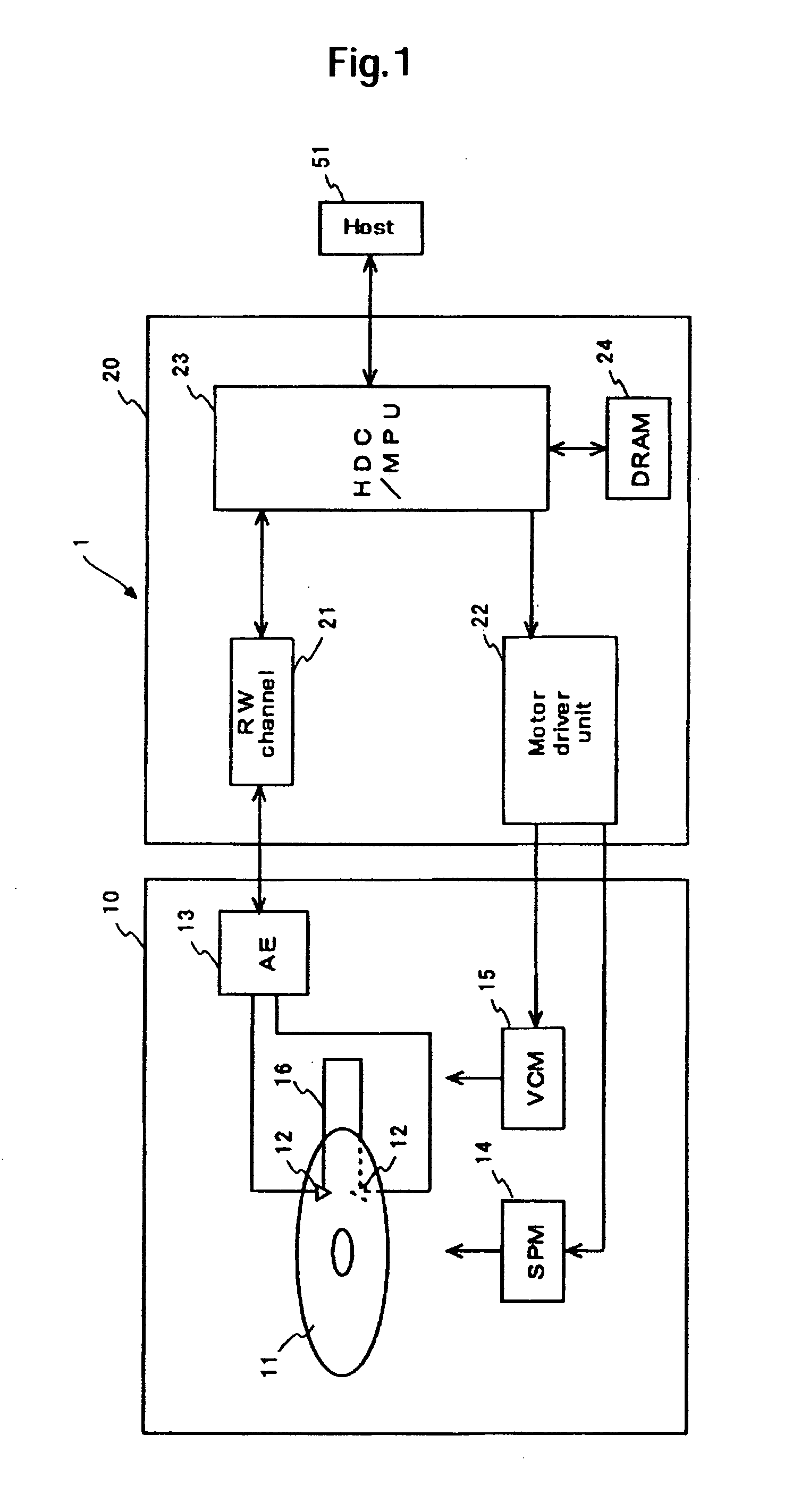

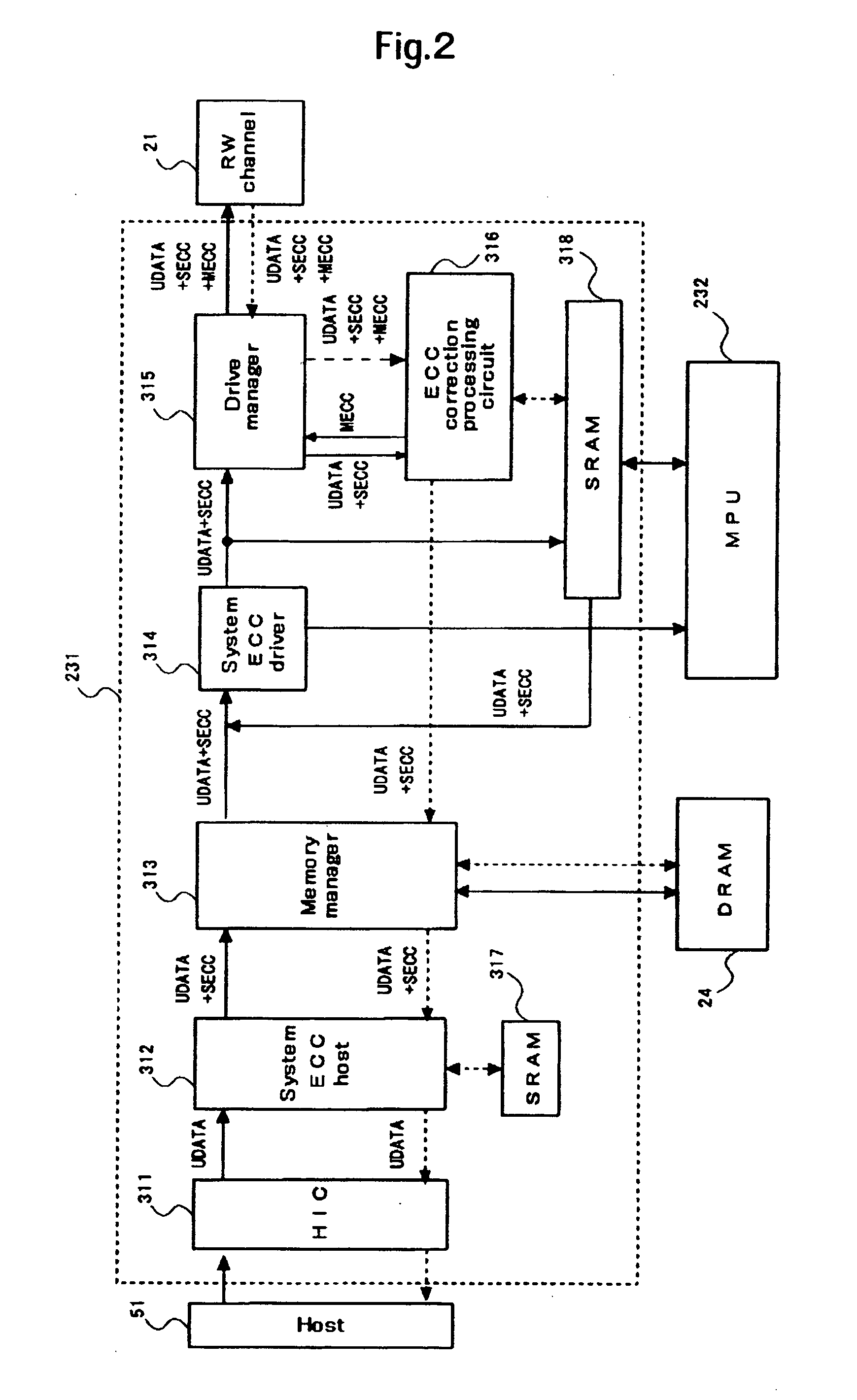

Data storage device and error correction method

InactiveUS20080016429A1High data reliabilityReduce circuit sizeError detection/correctionRecord information storageCircuit sizingHard disc drive

Embodiments in accordance with the present invention increase the reliability of a data storage device, and to reduce the circuit size. According to one embodiment of the present invention, a hard disk drive (HDD) executes not only error correction processing of data to be written to a magnetic disk, but also error correction processing of data stored in the DRAM. In the HDD according to this embodiment, one SRAM is shared by both kinds of error correction processing. As a result of executing the error correction processing of the data stored in the DRAM, the reliability of the HDD is improved. In addition, by using the same SRAM for the two kinds of error correction processing that differ from each other, it is possible to suppress the increase in circuit size.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

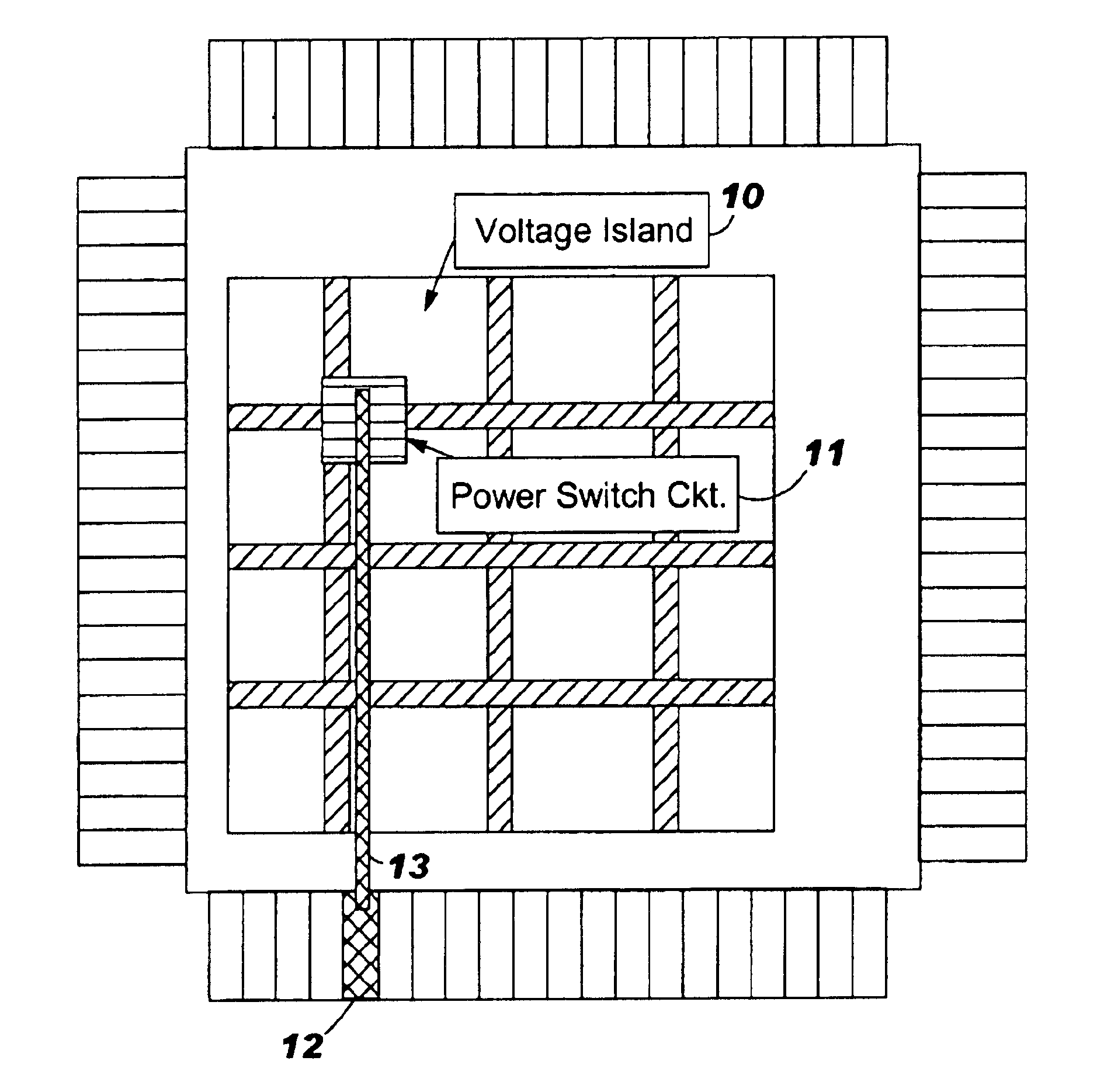

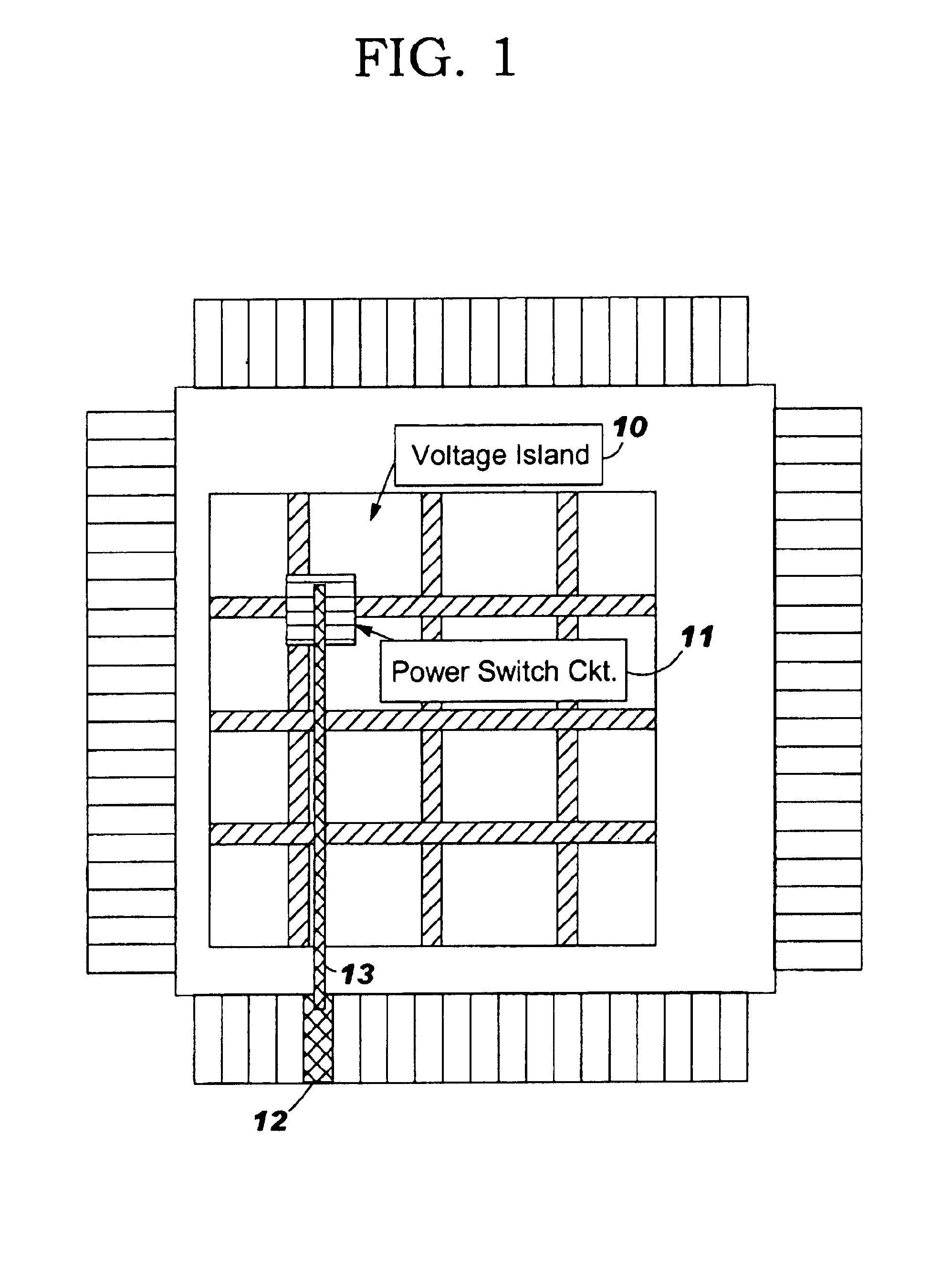

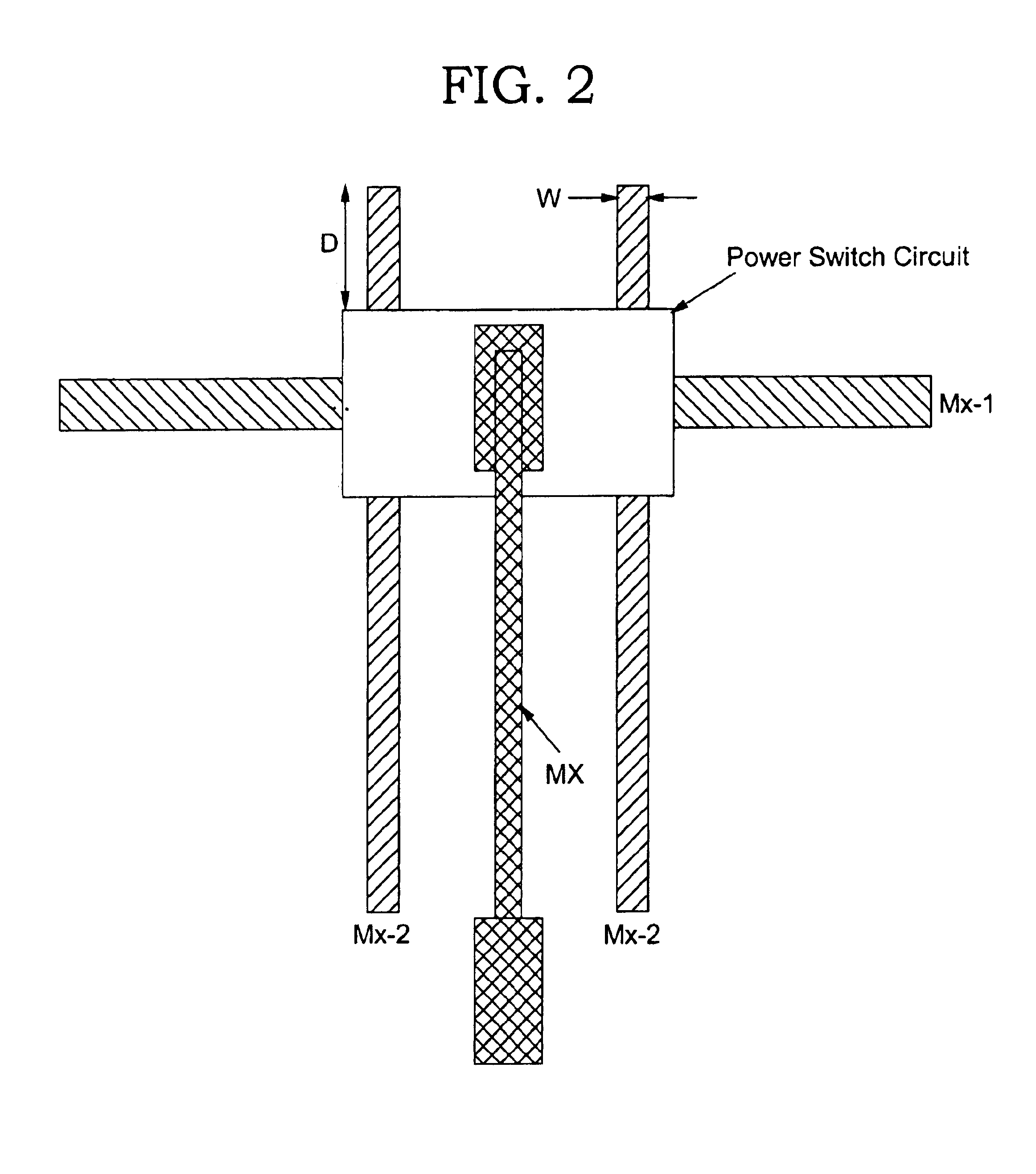

Power switch circuit sizing technique

InactiveUS6924661B2Semiconductor/solid-state device detailsSolid-state devicesCircuit sizingPower switching

An integrated circuit structure has at least one voltage island and a pattern of power switches within the voltage island. The pattern determines the number of (and evenly spaces) the power switches according to the size of the serviceable area to which each of the power switches can provide power. The size of the power switches are matched to the current and voltage that will be provided by the power buses. The size of the serviceable area to which each of the power switches can provide power is dependent upon the size of the power switches.

Owner:GLOBALFOUNDRIES US INC

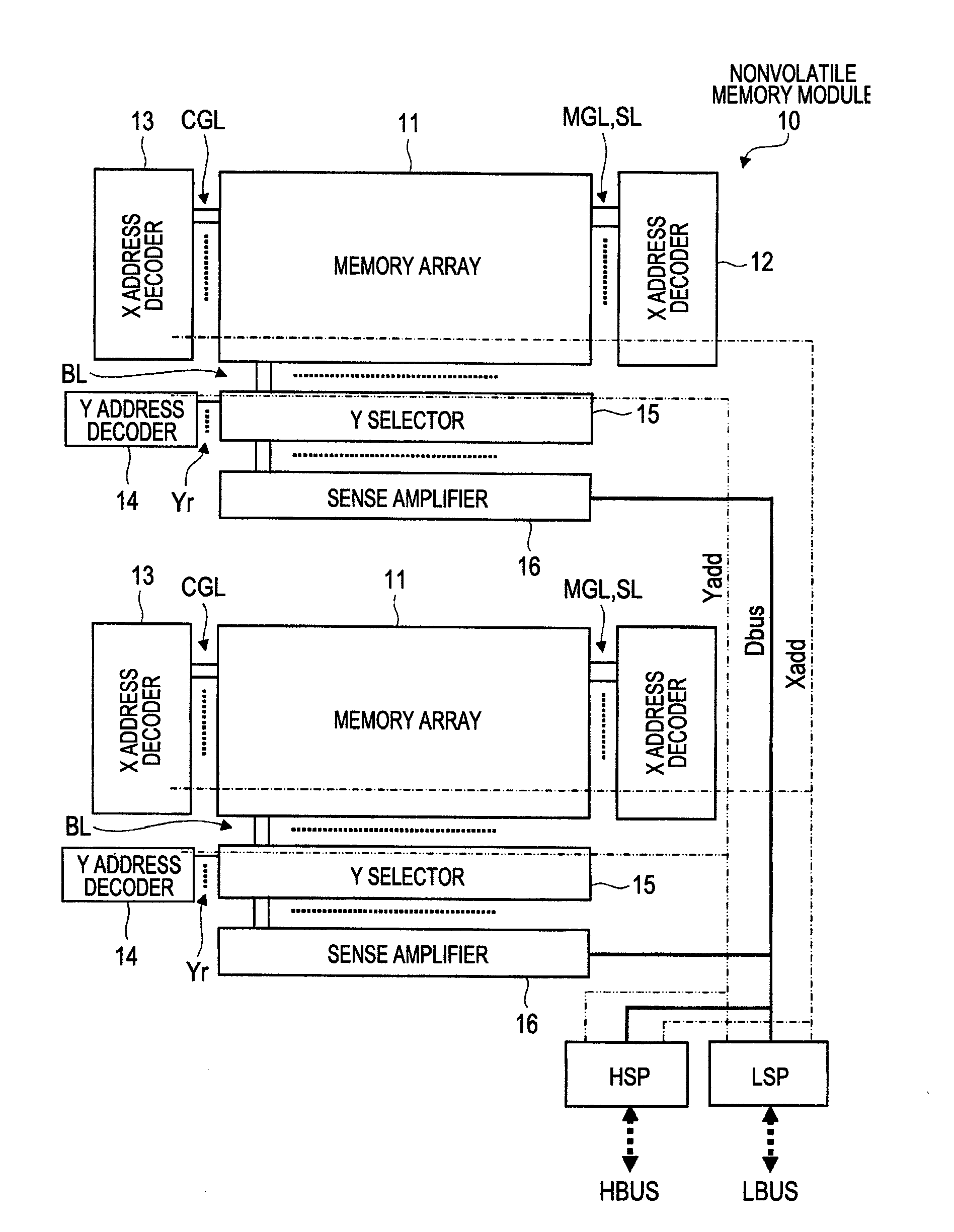

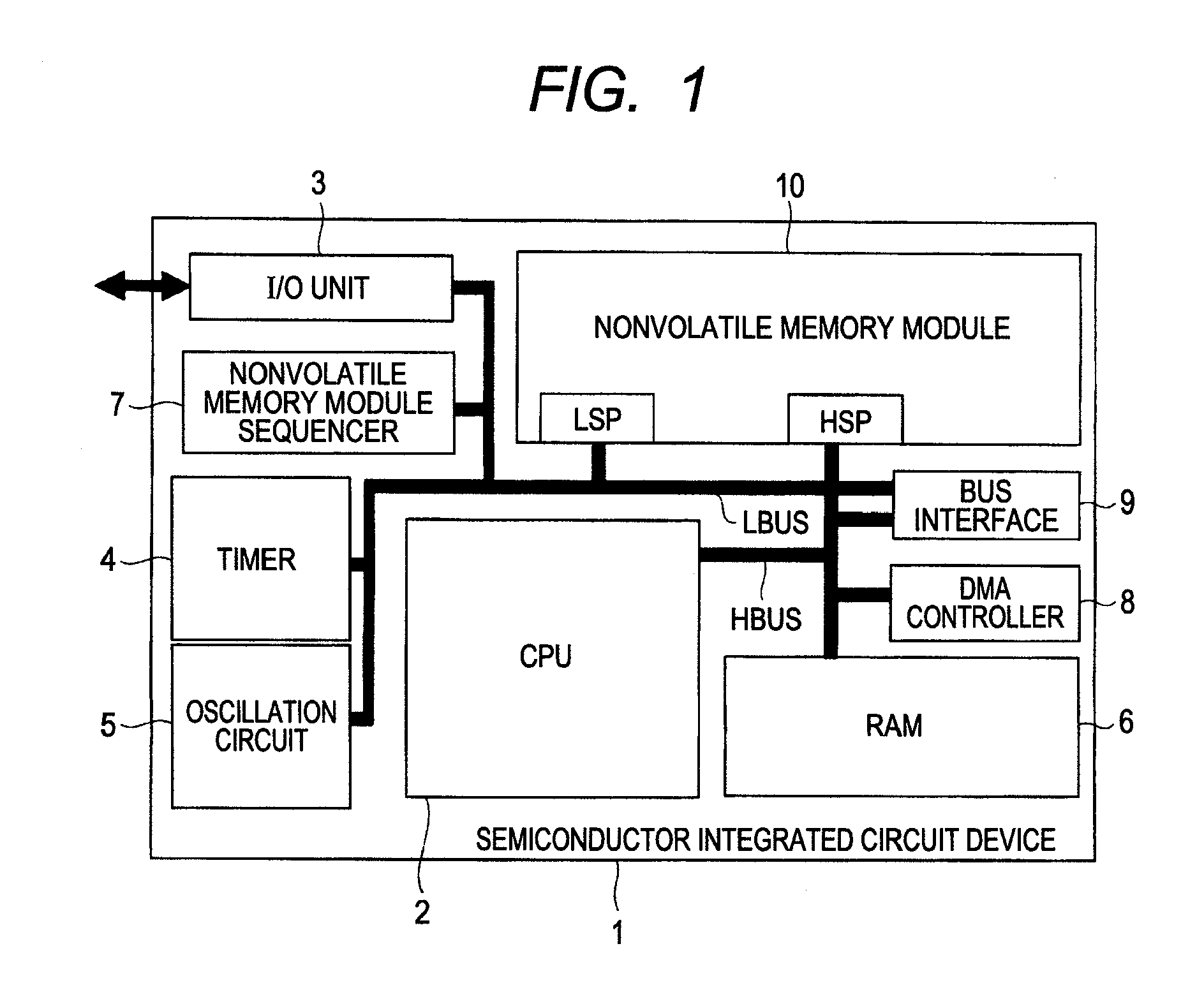

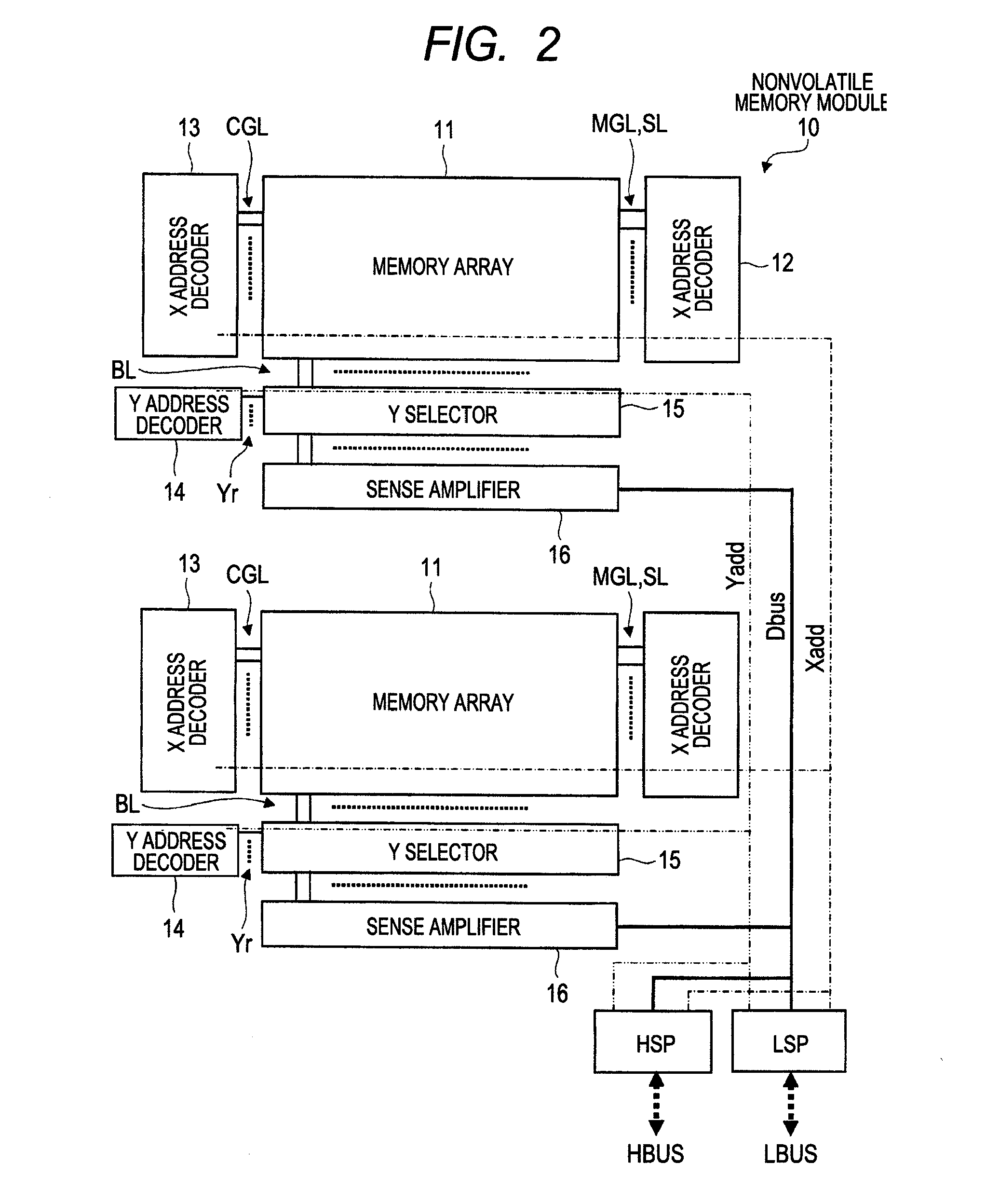

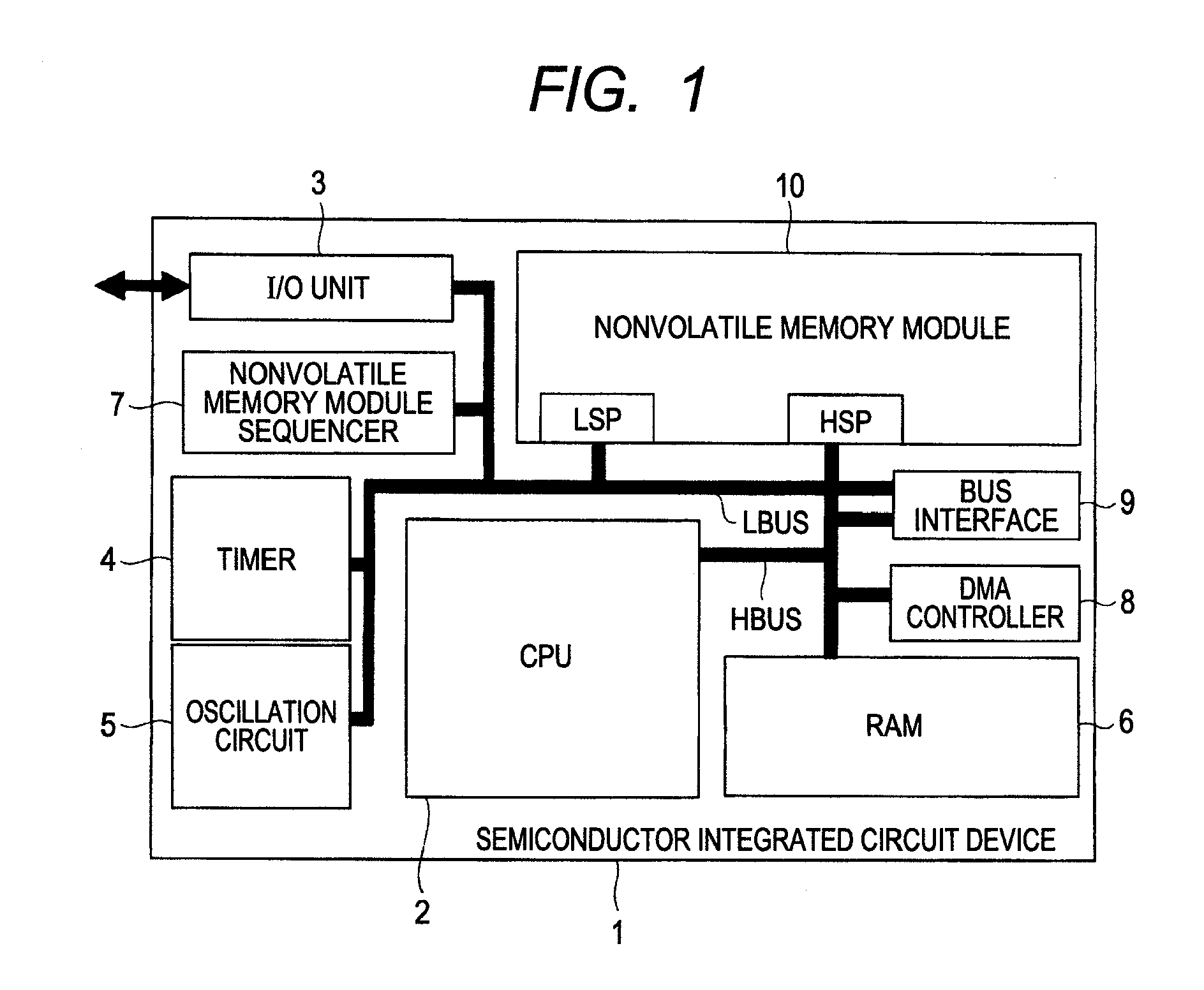

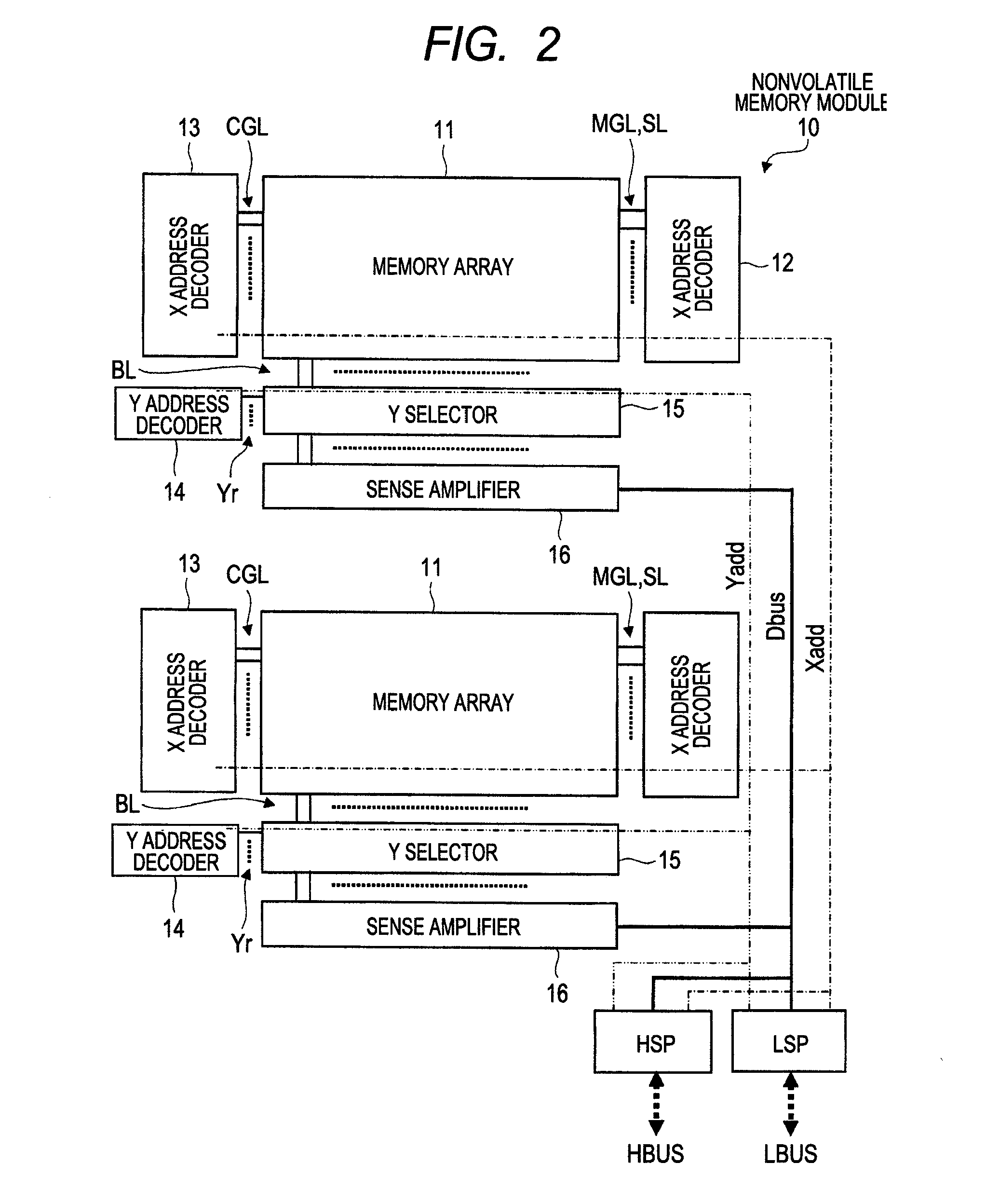

Semiconductor integrated circuit device

This invention is to reduce the number of memory gate drivers, while lessening the number of times of disturb occurrence in a memory array configuration that implements writing in small byte units. A memory array comprises a plurality of sub-arrays, MG transfers, SL drivers, and CG drivers. Each sub-array includes a plurality of memory gate lines, control gate lines, source lines, and bit lines. Memory cells are arranged in positions of intersections of these lines. The control gate lines, CG drivers, source lines, and SL drivers are common to the sub-arrays, whereas the memory gate lines and MG buffer circuits are provided for each sub-array. Thereby, the units in which data is written are decreased and adverse effects of disturb are reduced without increasing the circuit size of the memory array.

Owner:RENESAS ELECTRONICS CORP

Semiconductor memory device and control method for semiconductor memory device

InactiveUS20060007756A1Extended access timeOccurrence probabilityRead-only memoriesDigital storageStart timeControl signal

Provided is a semiconductor memory device using a single-bit line method that determines read operation timing in accordance with operation of a replica bit line. Further provided is a control method for the semiconductor memory device. Even when a transistor property fluctuation has occurred, the semiconductor memory device and the control method are capable of preventing, for example, increases in access time and circuit size and concurrently capable of reducing the occurrence probability of data readout error. The gate lengths of replica memory cell transistors are set as being values greater than the gate length of memory cell transistors. Thereby, a distribution center of a current drive capability distribution of the replica memory cell transistors is set lower than a distribution center of a current drive capability distribution of the memory cell transistors. Consequently, an occurrence probability of a delay in a voltage-fall start time on a regular data line can be reduced to be lower in comparison to a transmission timing of a latch control signal.

Owner:SOCIONEXT INC

Semiconductor integrated circuit device

This invention is to reduce the number of memory gate drivers, while lessening the number of times of disturb occurrence in a memory array configuration that implements writing in small byte units. A memory array comprises a plurality of sub-arrays, MG transfers, SL drivers, and CG drivers. Each sub-array includes a plurality of memory gate lines, control gate lines, source lines, and bit lines. Memory cells are arranged in positions of intersections of these lines. The control gate lines, CG drivers, source lines, and SL drivers are common to the sub-arrays, whereas the memory gate lines and MG buffer circuits are provided for each sub-array. Thereby, the units in which data is written are decreased and adverse effects of disturb are reduced without increasing the circuit size of the memory array.

Owner:RENESAS ELECTRONICS CORP

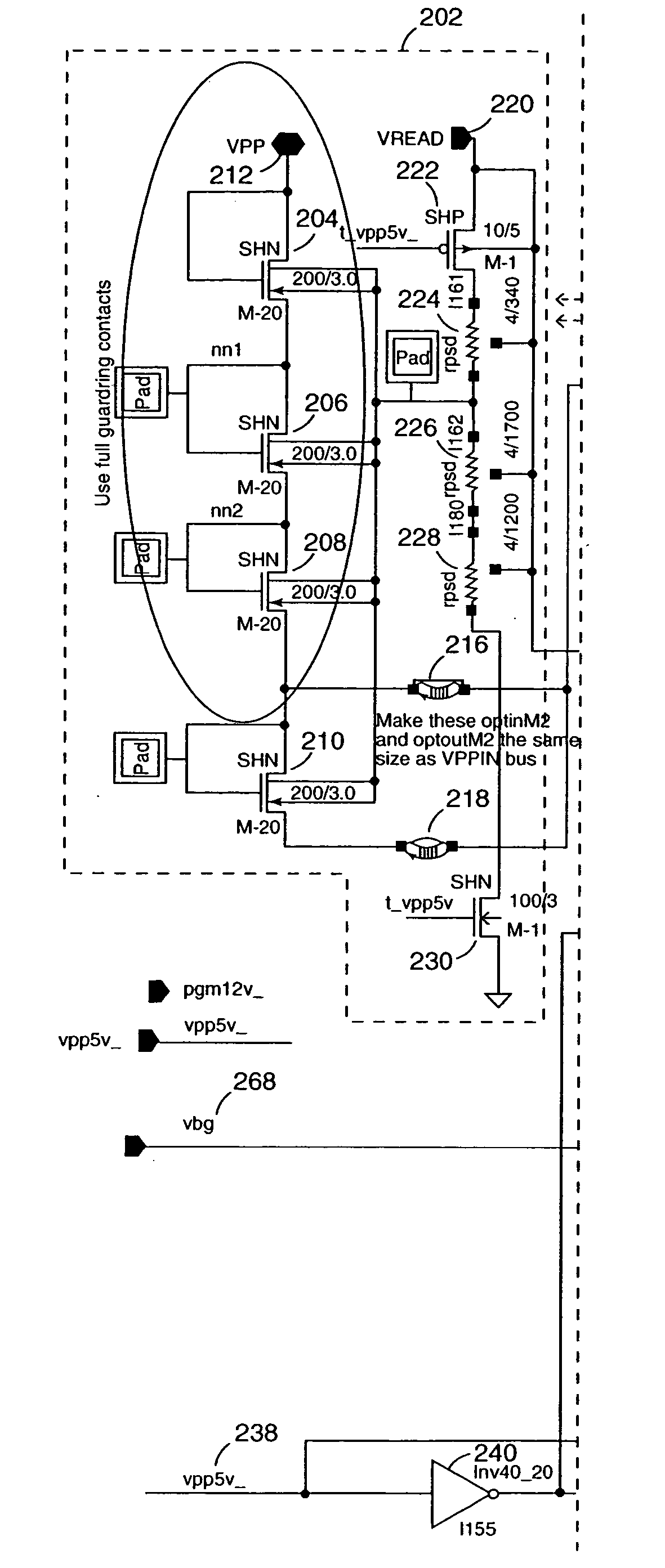

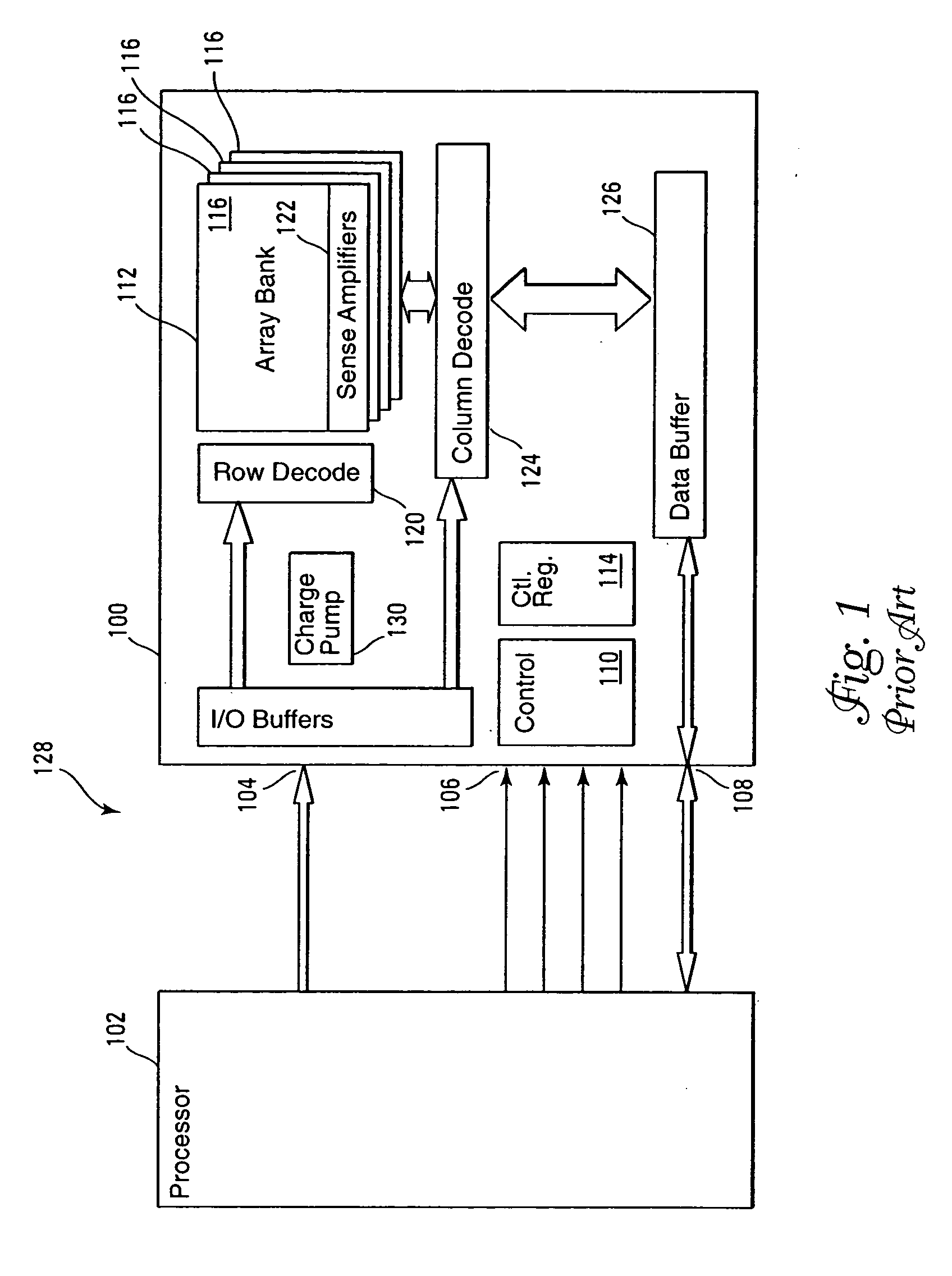

High voltage regulator for low voltage integrated circuit processes

Owner:MICRON TECH INC

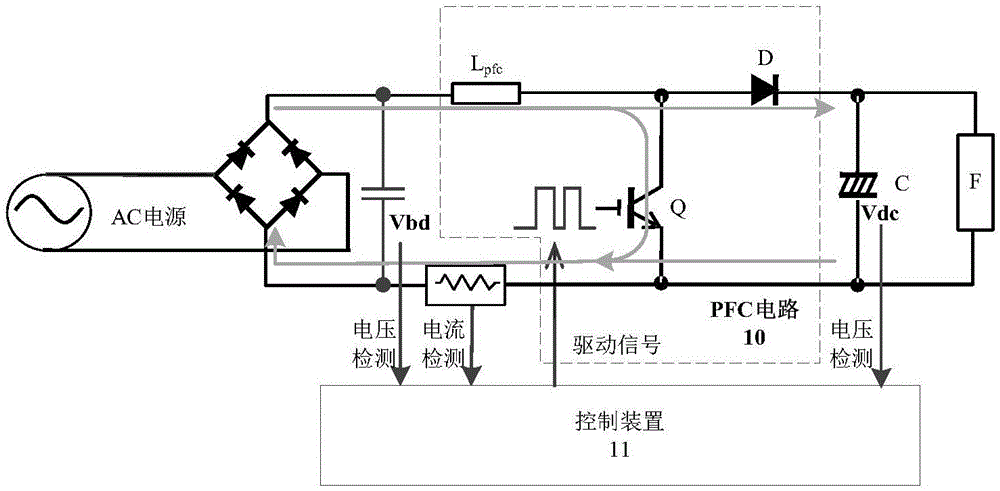

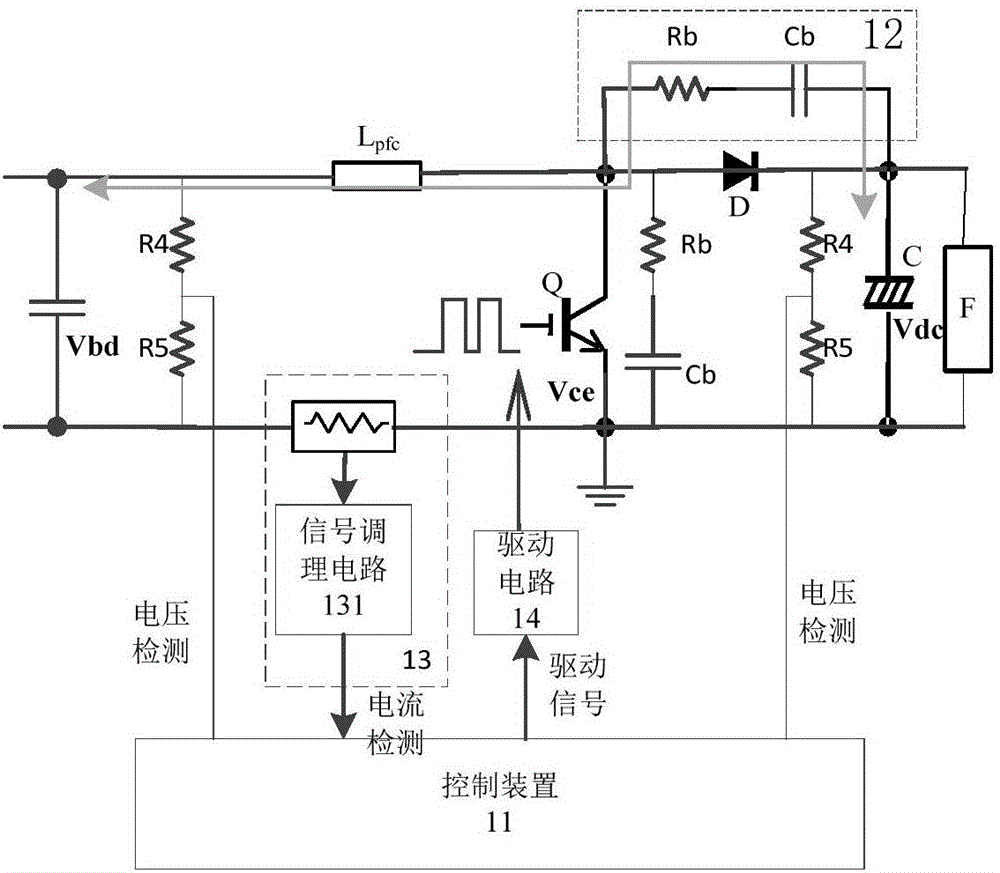

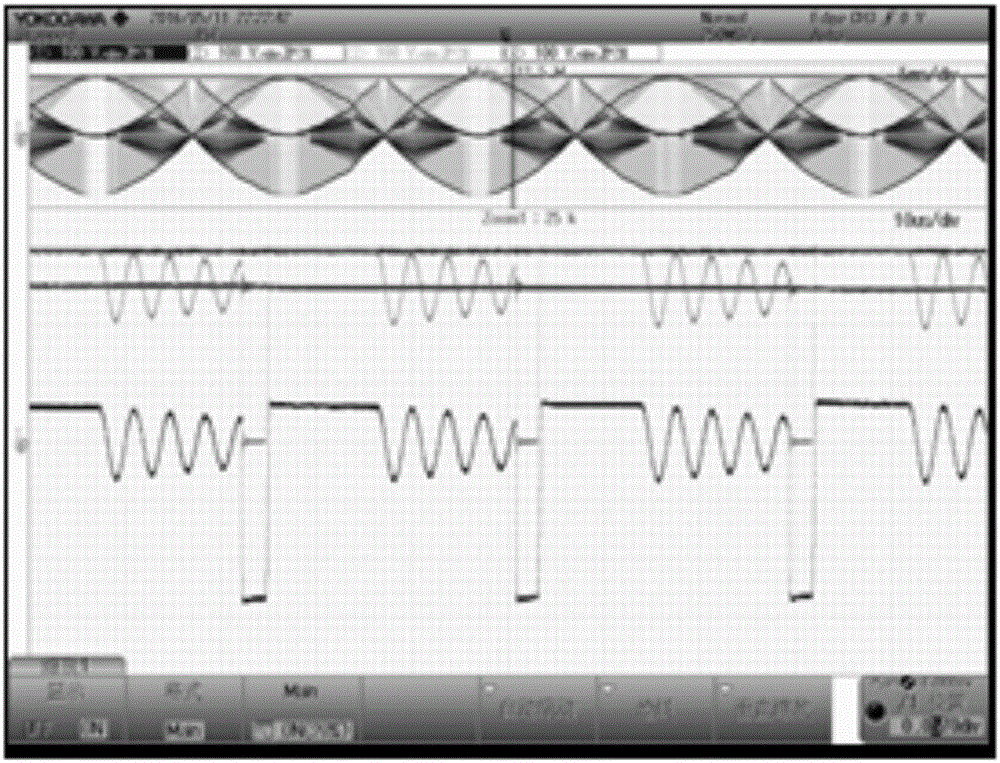

Household appliance and PFC circuit thereof

InactiveCN106208661ASmall sizeMeet EMC requirementsEfficient power electronics conversionPower conversion systemsCircuit sizingHome appliance

The invention relates to the field of household appliances, and discloses a household appliance and a PFC circuit thereof. The PFC circuit comprises a noise generating device for generating high-frequency noise and an absorbing buffering circuit connected with the noise generating device in parallel and used for inhibiting generated high-frequency noise. In this way, the high-frequency PFC circuit can be adopted in the household appliance, the EMC requirements can be met, and the size of the circuit is reduced.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD +1

Novel anti-SEU (Single Event Upset) reinforcement storage cell based on crossly-coupled miller capacitors

InactiveCN103886894APrevent inversionIncrease feedback delay timeDigital storageCapacitanceCritical load

The invention discloses a novel anti-SEU (Single Event Upset) reinforcement storage cell based on crossly-coupled miller capacitors. The novel anti-SEU reinforcement storage cell comprises a storage cell. The novel anti-SEU reinforcement storage cell is characterized in that the storage cell is a DICE (Dual Interlocked storage Cell); a miller capacitor is arranged between each two nodes in four nodes of the DICE. The novel anti-SEU reinforcement storage cell has the beneficial effects that the crossly-coupled miller capacitors are connected among the nodes of the DICE so as to obtain relatively great capacitance by using small capacitance. On the aspect of a circuit size, the area of the device can not be obviously increased by the miller capacitors so as to meet the requirement that the size of an integrated size is smaller and smaller. The crossly-coupled miller capacitors are additionally arranged so that the critical load of overturning the nodes is increased, the change of voltage of each node, caused by collection loads with the same quantity, is reduced, the feedback delaying time between two phase inverters of the DICE is increased, the multi-point anti-SEU reinforcement capability of the DICE is improved, and a possible inversion phenomenon caused by that the two nodes are simultaneously influenced by radiation effects is avoided.

Owner:HOHAI UNIV CHANGZHOU

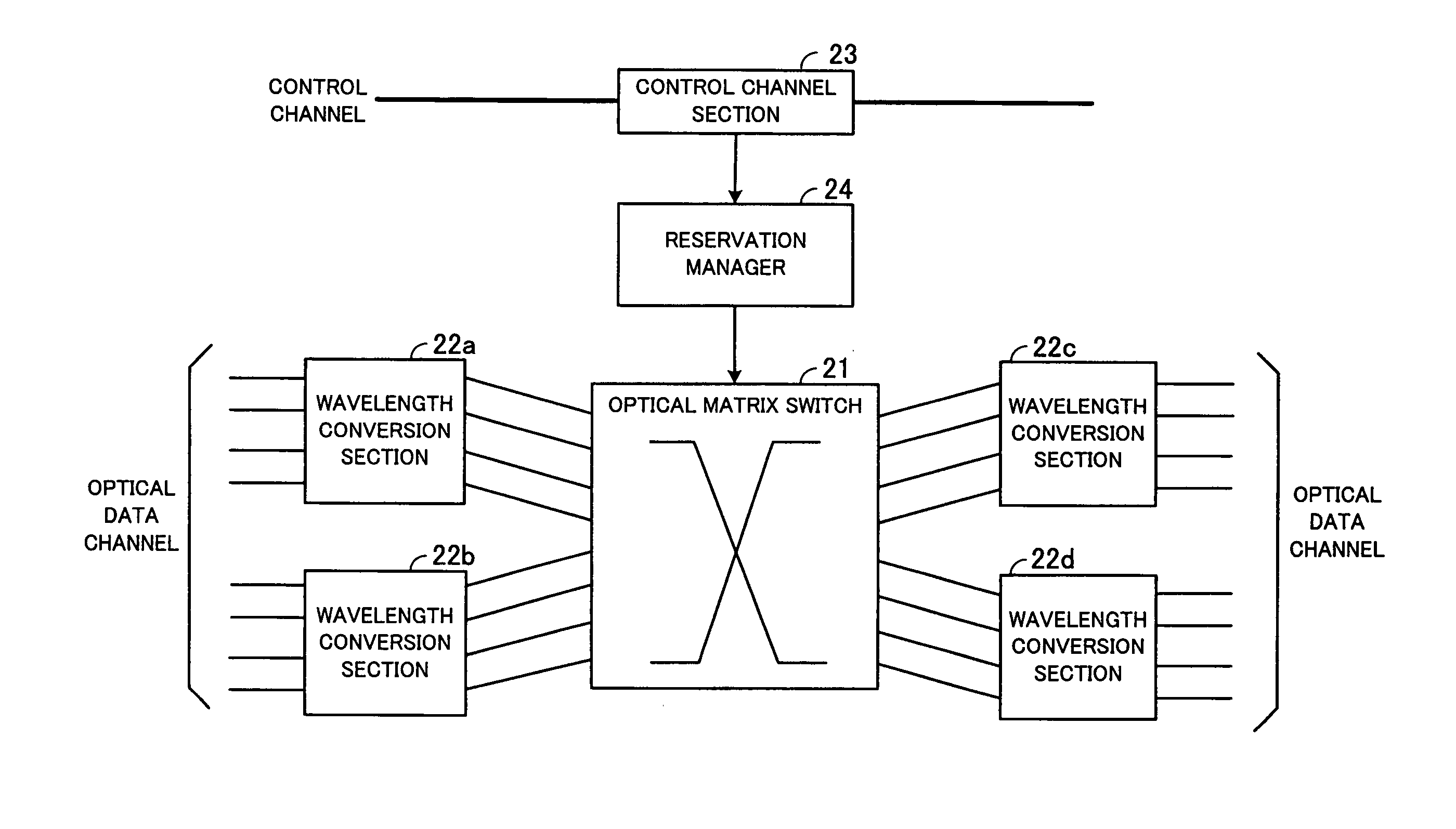

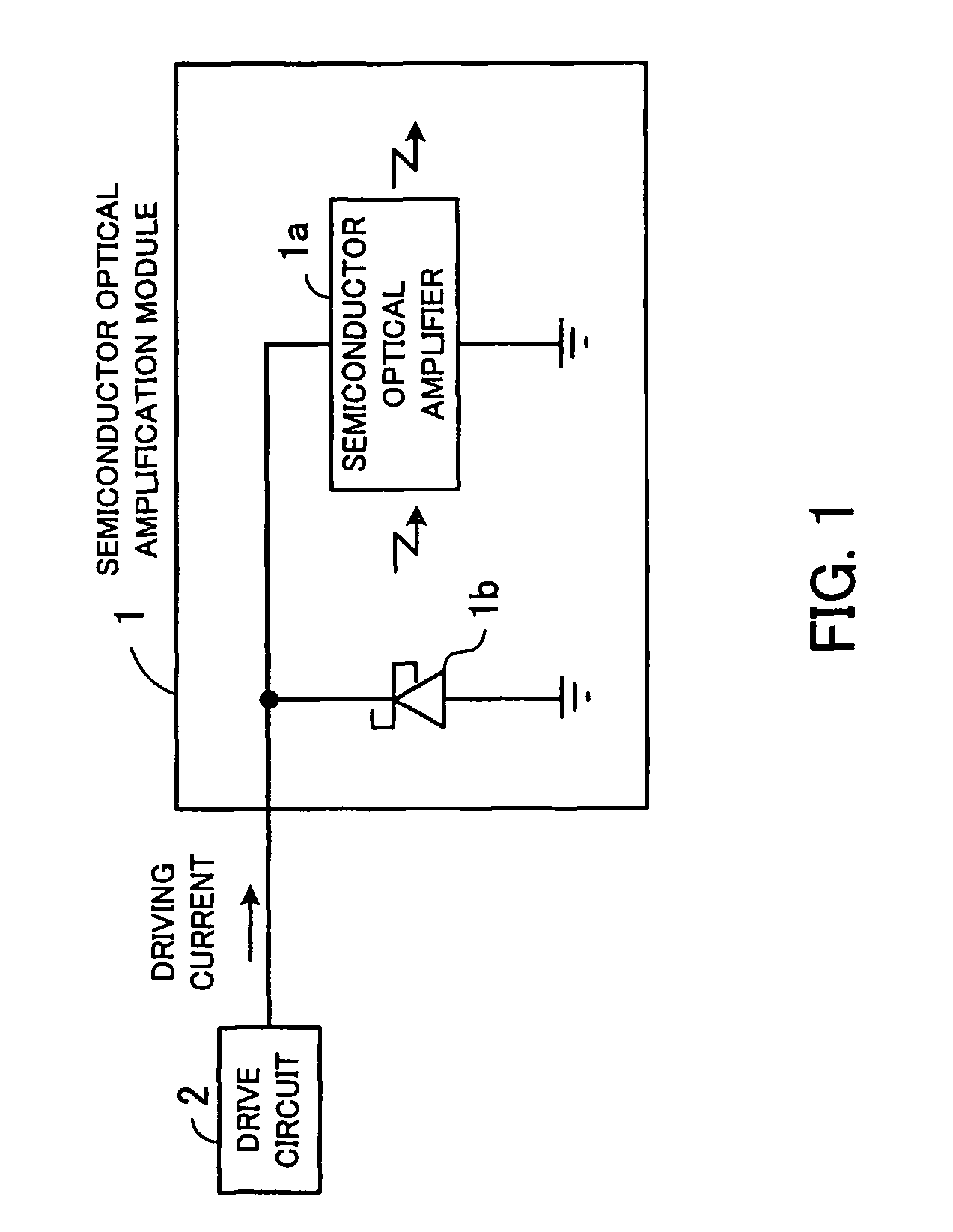

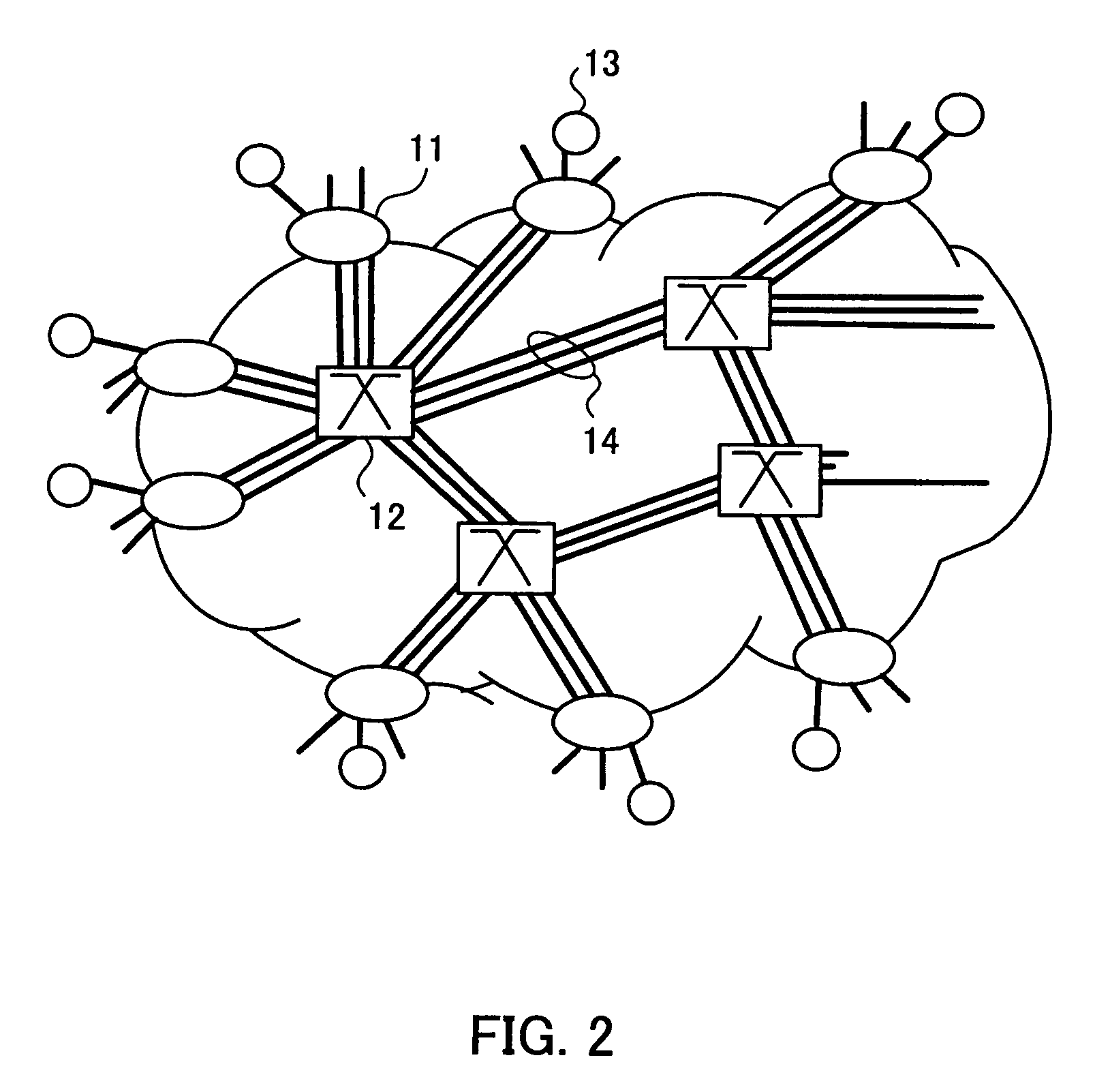

Semiconductor optical amplification module, optical matrix switching device, and drive circuit

ActiveUS8274733B2Suppress consumptionSuppress operationLaser detailsDigital dataDriver circuitCircuit sizing

A semiconductor optical amplification module that can suppress ringing without increasing power consumption or circuit size or inhibiting high-speed operation. A semiconductor optical amplifier outputs an optical signal inputted according to driving current outputted from a drive circuit. A diode is connected in parallel with the semiconductor optical amplifier. As a result, it becomes possible to suppress ringing without connecting a large resistor to the drive circuit.

Owner:FUJITSU LTD

Cavity-based filtering balun

Provided in the invention is a cavity-based filtering balun which comprises a cavity resonator. An input terminal PCB board and an output terminal PCB board are arranged at the two opposite sides of the cavity resonator; an input terminal slot line is arranged at one side, approaching the side of the cavity resonator, of the input terminal PCB board; and an input terminal microstrip line is arranged at the other side. A first slot hole that corresponds to the input terminal slot line completely is arranged at the position corresponding to the input terminal slot line on the side wall of the input terminal PCB board at the cavity resonator; an output terminal slot line is arranged at one side, approaching the side of the cavity resonator, of the output terminal PCB board and an output microstrip line is arranged at the other end; and a second slot hole corresponding to the output terminal slot line completely is arranged at the position corresponding to the output terminal slot line, onthe side wall of the output terminal PCB board at the cavity resonator. According to the invention, the filtering balun body is a cavity resonator, so that the quality factor is improved and the insertion losses are reduced. With the two resonance modes in the cavity resonator, the bipolar transmission band requirement is realized in the single cavity structure; and the circuit dimension is reduced.

Owner:广州瀚信通信科技股份有限公司

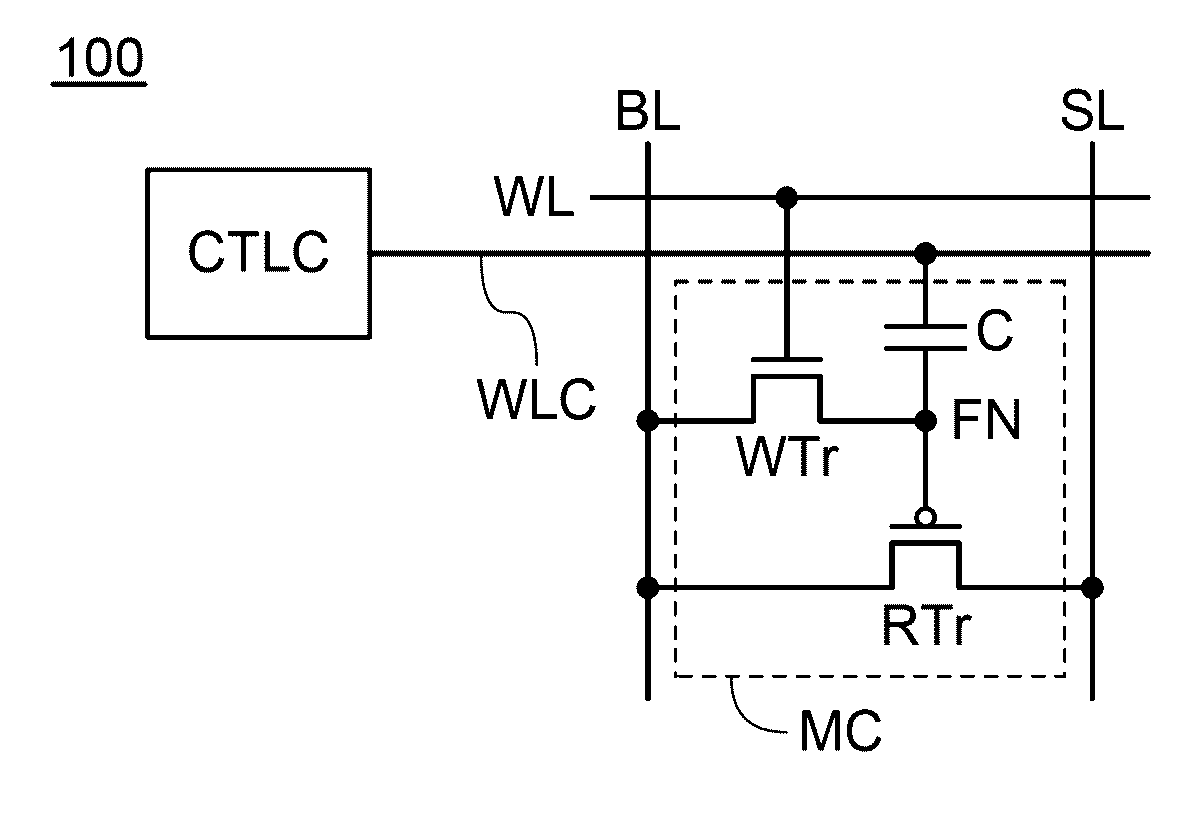

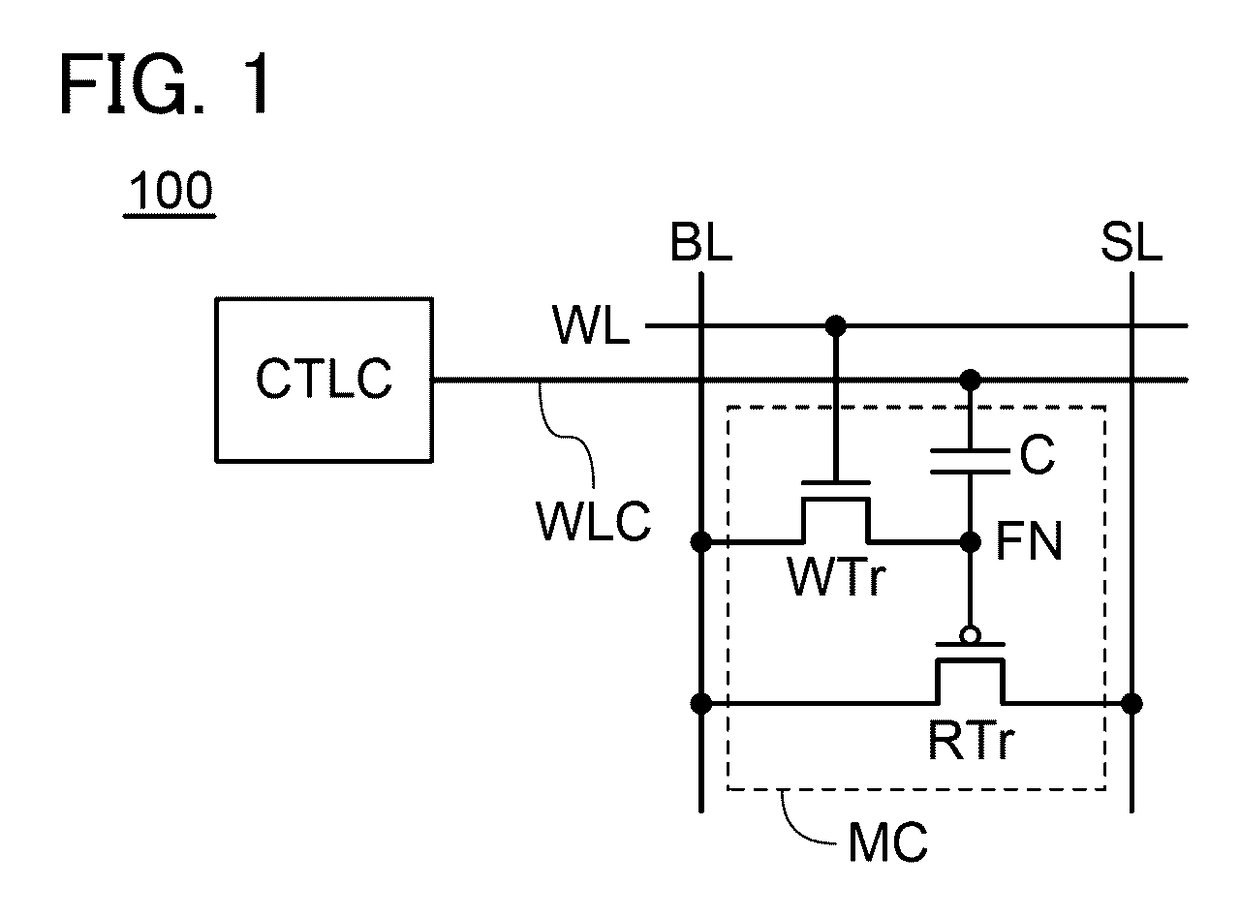

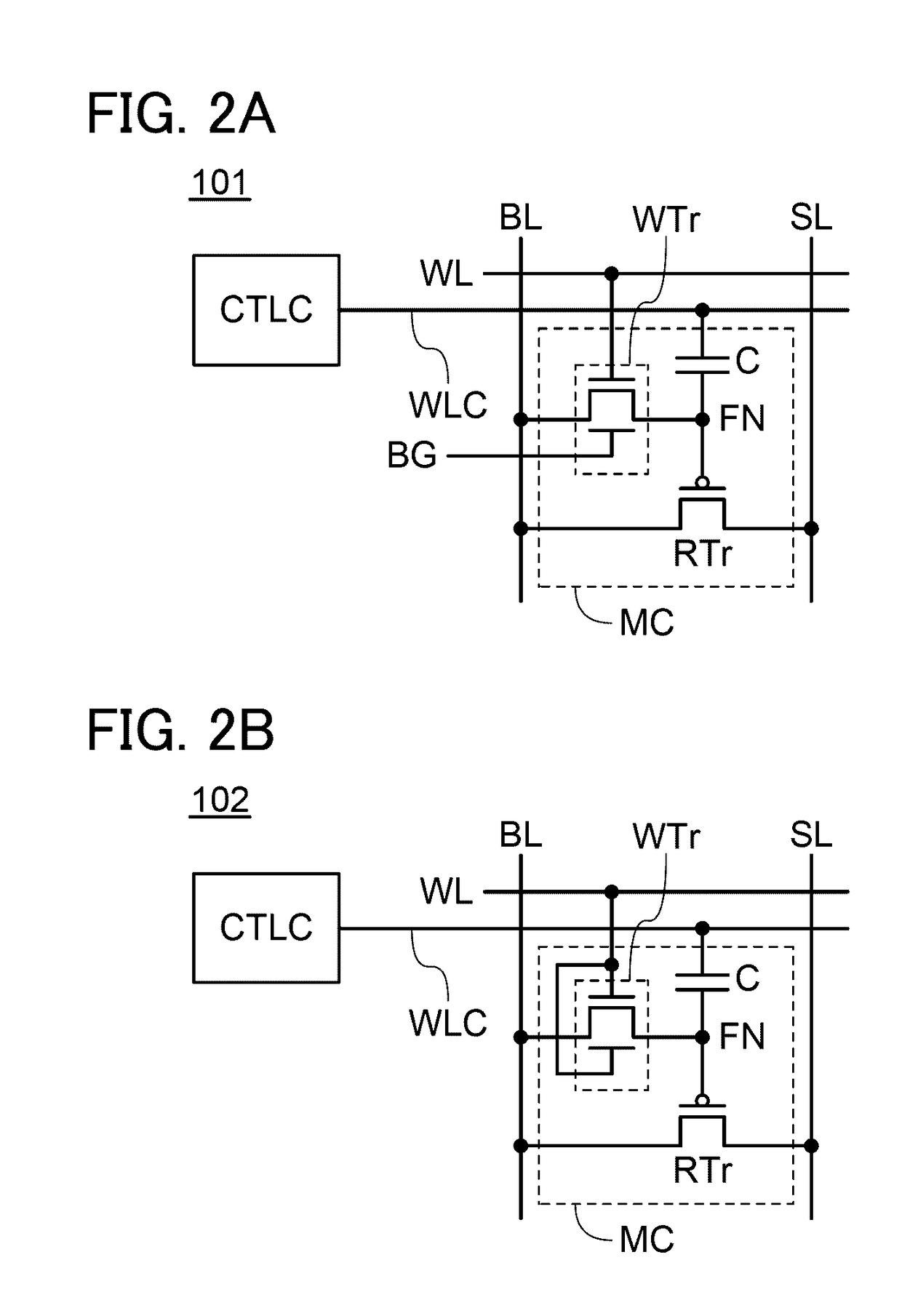

Semiconductor device, memory device, electronic device, or method for driving the semiconductor device

InactiveUS20170125420A1Large data storage capacityReduce circuit sizeTransistorSemiconductor/solid-state device testing/measurementCircuit sizingEngineering

A semiconductor device with an improved arithmetic processing speed and a decreased circuit size, and its driving method are provided. In the semiconductor device, a first terminal of a first transistor and a gate of a second transistor are electrically connected to a first terminal of a capacitor, and a control circuit is electrically connected to a second terminal of the capacitor. The control circuit supplies a first potential to the second terminal of the capacitor, in other words, adds a value corresponding to the first potential to the value of first data previously retained in the gate of the second transistor in order to obtain second data. In the second transistor, the second data, specifically, a third potential commensurate with the potential of the gate will be output from a second terminal when a second potential is supplied to a first terminal.

Owner:SEMICON ENERGY LAB CO LTD

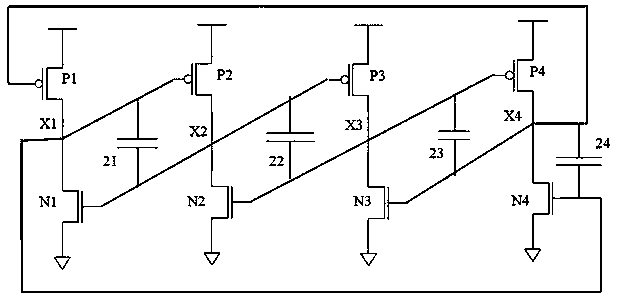

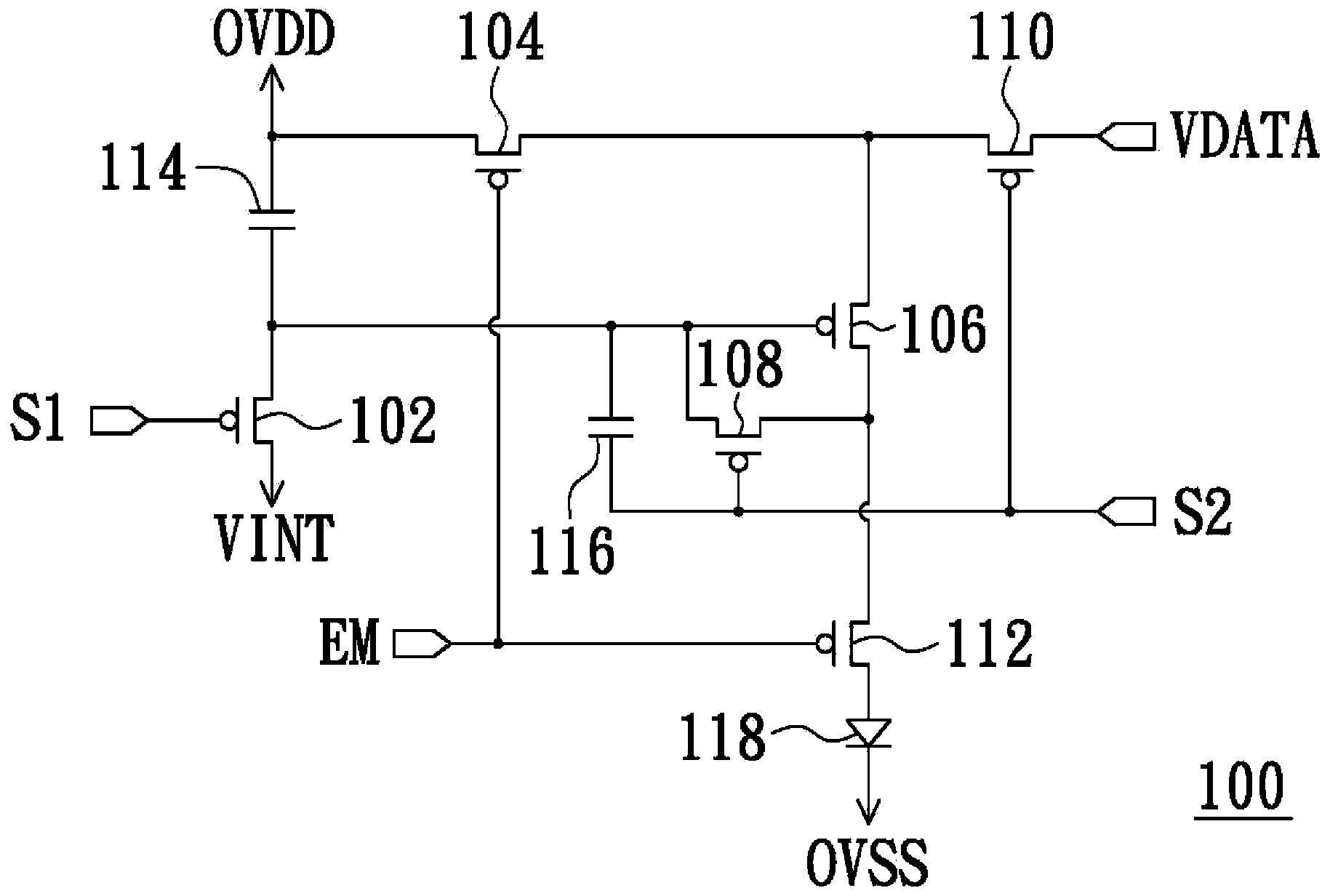

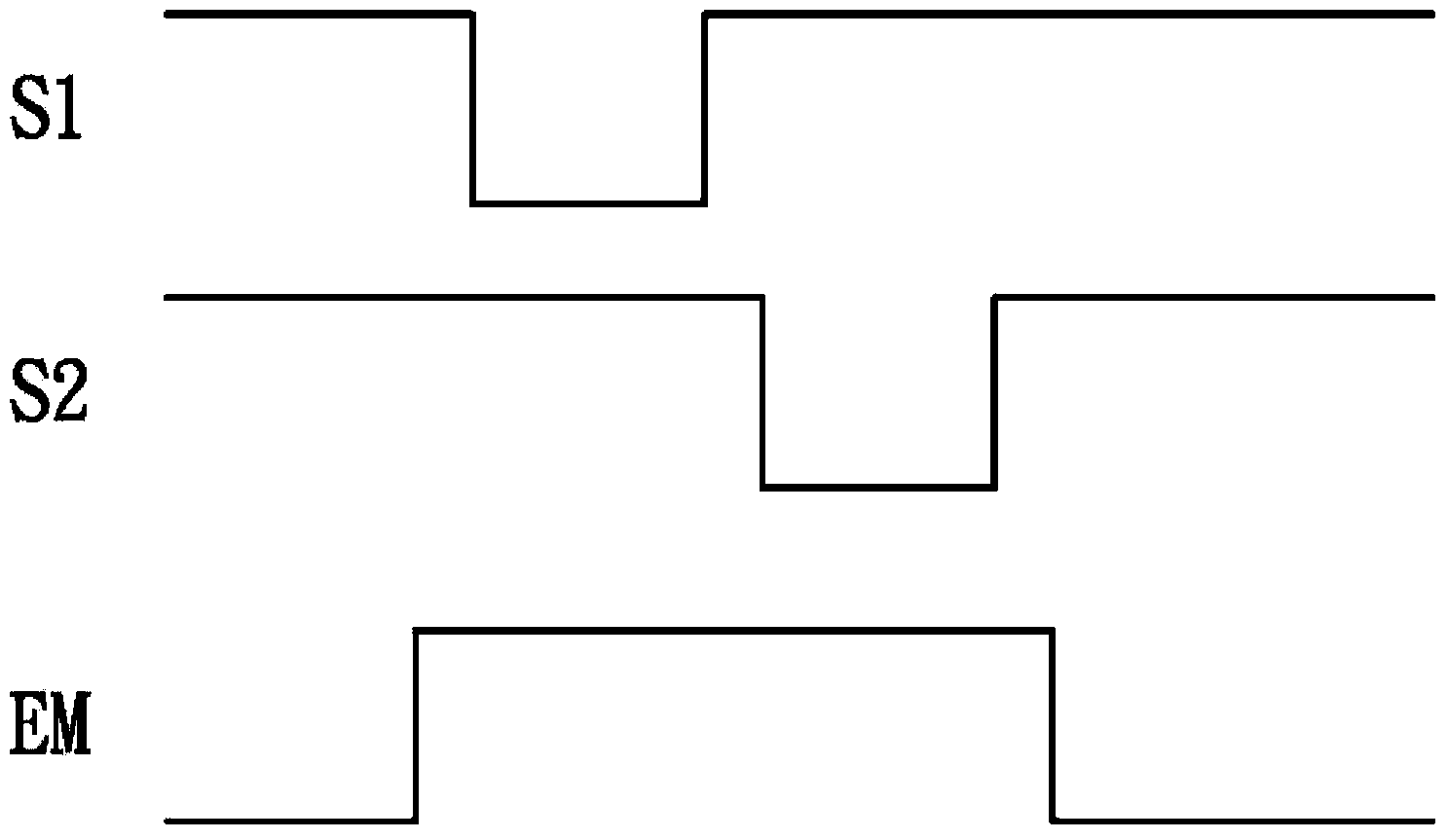

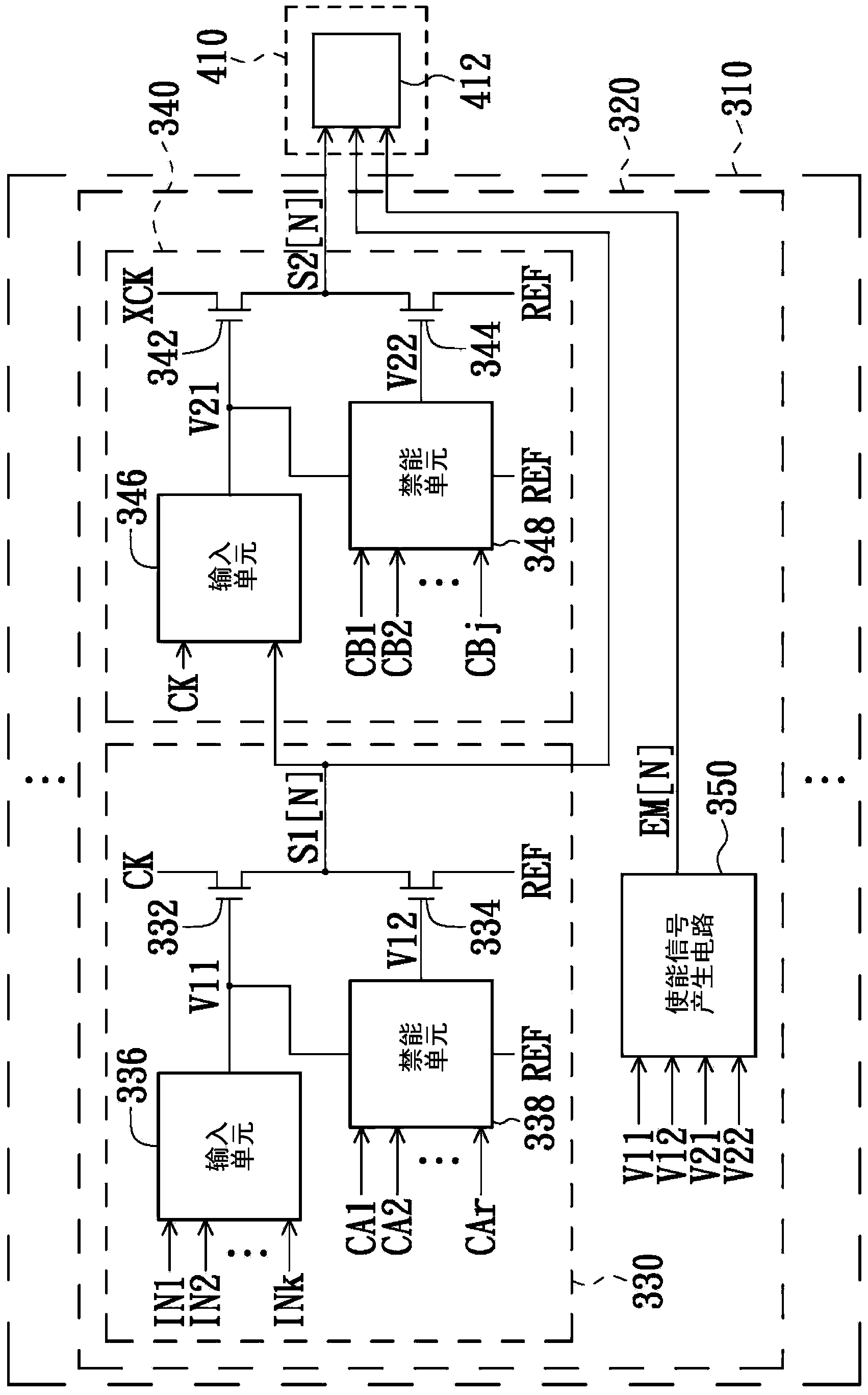

Shift register circuit

ActiveCN103456269ASimple designSmall sizeStatic indicating devicesDigital storageShift registerHemt circuits

The invention provides a shift register circuit, which is suitable for driving an organic LED display panel. The shift register circuit comprises a plurality of circuit levels in series connection. Each circuit level comprises two shift registers and an enable signal for generating circuit. The shift register comprises two transistors, an input unit and a forbidden energy unit. The enable signal generates circuit, so that an enable signal can be generated based on the signal of the control end of the four transistors in the two shift registers. The shift register circuit is advantageous in that the circuit design of each circuit level is relatively simple; circuit size is relatively small; cost is relatively low.

Owner:AU OPTRONICS CORP

High voltage regulator for low voltage integrated circuit processes

InactiveUS20050002237A1Reducing external voltageRead-only memoriesDigital storageCircuit sizingLow voltage

An improved voltage reduction circuit and method is described that incorporates an independently controllable back bias voltage for increased gate / bulk fields in isolation well voltage reduction transistors that couple to and reduce external voltages that are too high for the integrated circuit process technology limits. The improved voltage reduction circuit and method allows for a higher overall available voltage and current flow for regulation by the circuit. Additionally, the improved voltage reduction circuit and method reduces voltage reduction circuit size by allowing for efficient implementation in a single isolation well. Furthermore, the improved voltage reduction circuit and method includes a back bias voltage control circuit that turns on and regulates the back bias voltage and avoids the problem of reverse bias conditions.

Owner:MICRON TECH INC

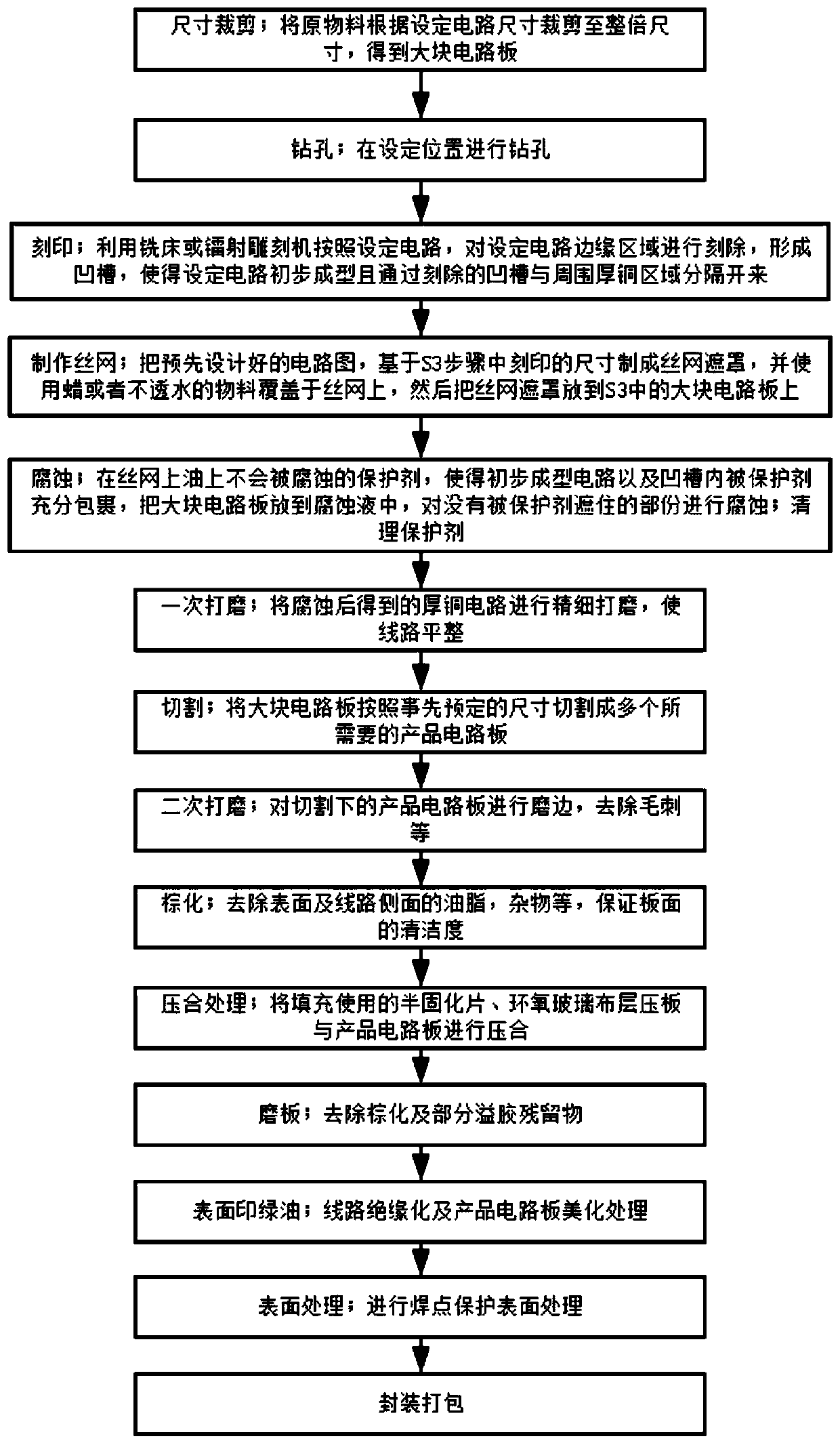

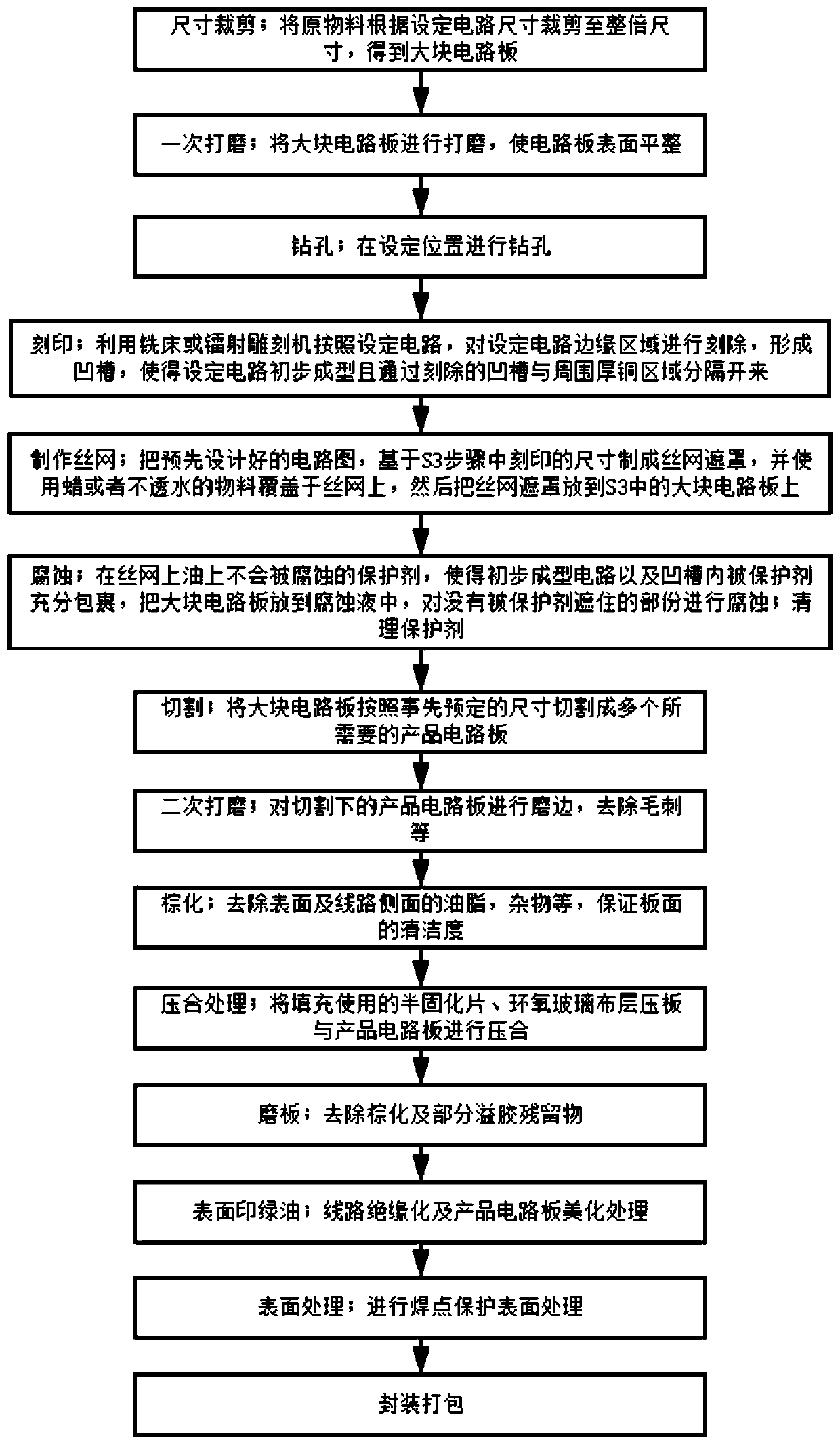

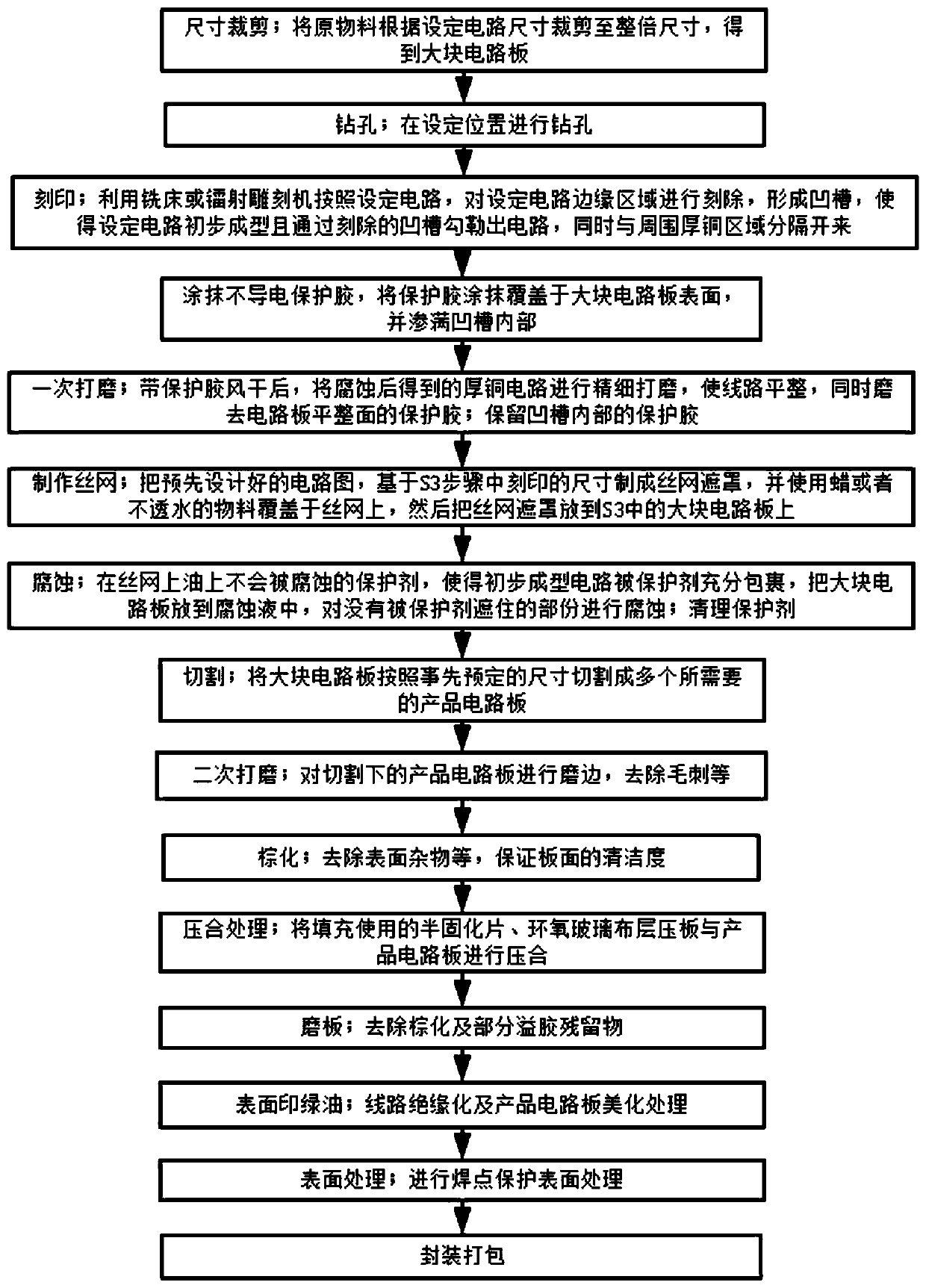

Manufacturing method of thick copper printed circuit board

ActiveCN111479401AFully protectedEasy to handleConductive pattern polishing/cleaningNon-metallic protective coating applicationCircuit sizingLaser engraving

The invention discloses a manufacturing method of a thick copper printed circuit board, and relates to the field of circuit board manufacturing. For improving manufacturing quality, the method specifically comprises the following steps: size cutting; cutting the raw material into a full size according to a set circuit size to obtain a large circuit board; performing drilling; drilling at a set position; engraving and printing; a milling machine or a laser engraving machine is used for engraving the edge area of the set circuit according to the set circuit to form a groove, so that the set circuit is preliminarily formed and separated from the surrounding thick copper area through the engraved groove; manufacturing a silk screen; and, making a pre-designed circuit diagram into the silk screen mask based on the size engraved in the step S3. Based on the thick copper material, the groove is engraved in the engraving step, and then the protective agent treatment is carried out, so that theside edge of the circuit board circuit can be fully protected, and the situation that the thick copper side edge of the designed circuit is corroded due to long etching time, and the performance andquality of the product are affected is effectively avoided.

Owner:JINGDEZHEN HONGYI ELECTRONICS TECH CO LTD

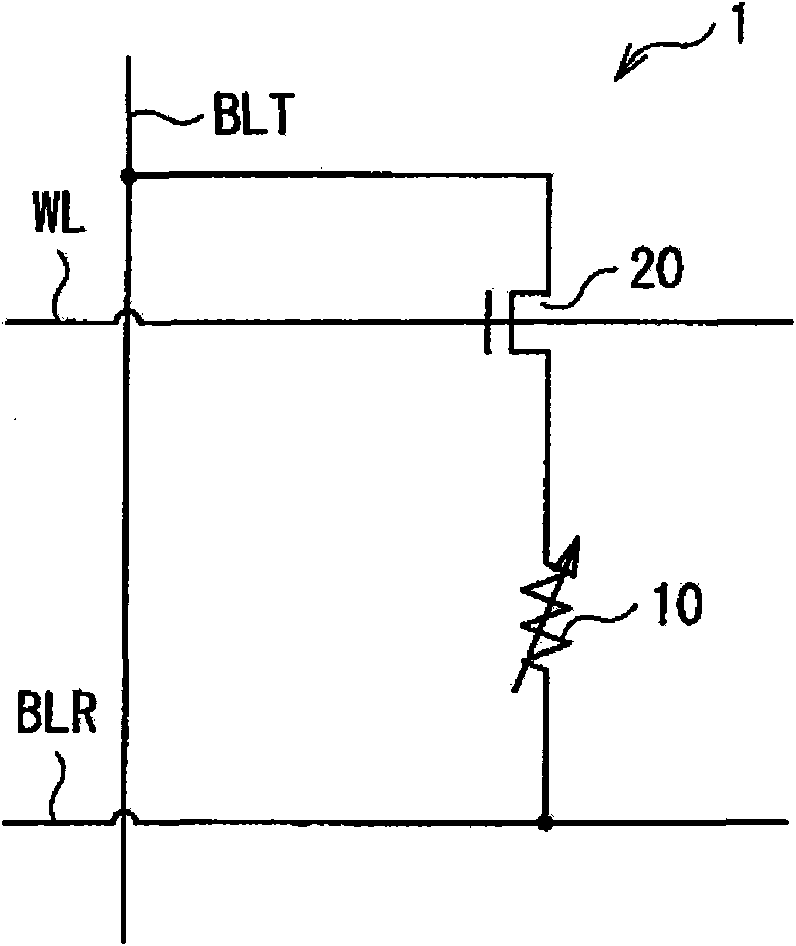

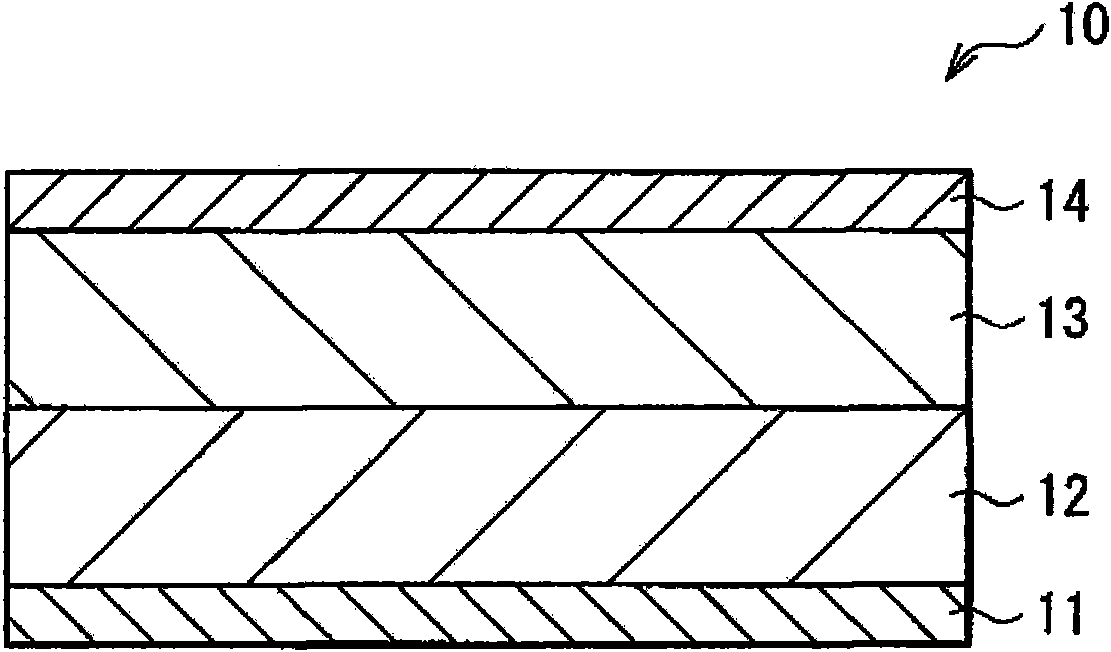

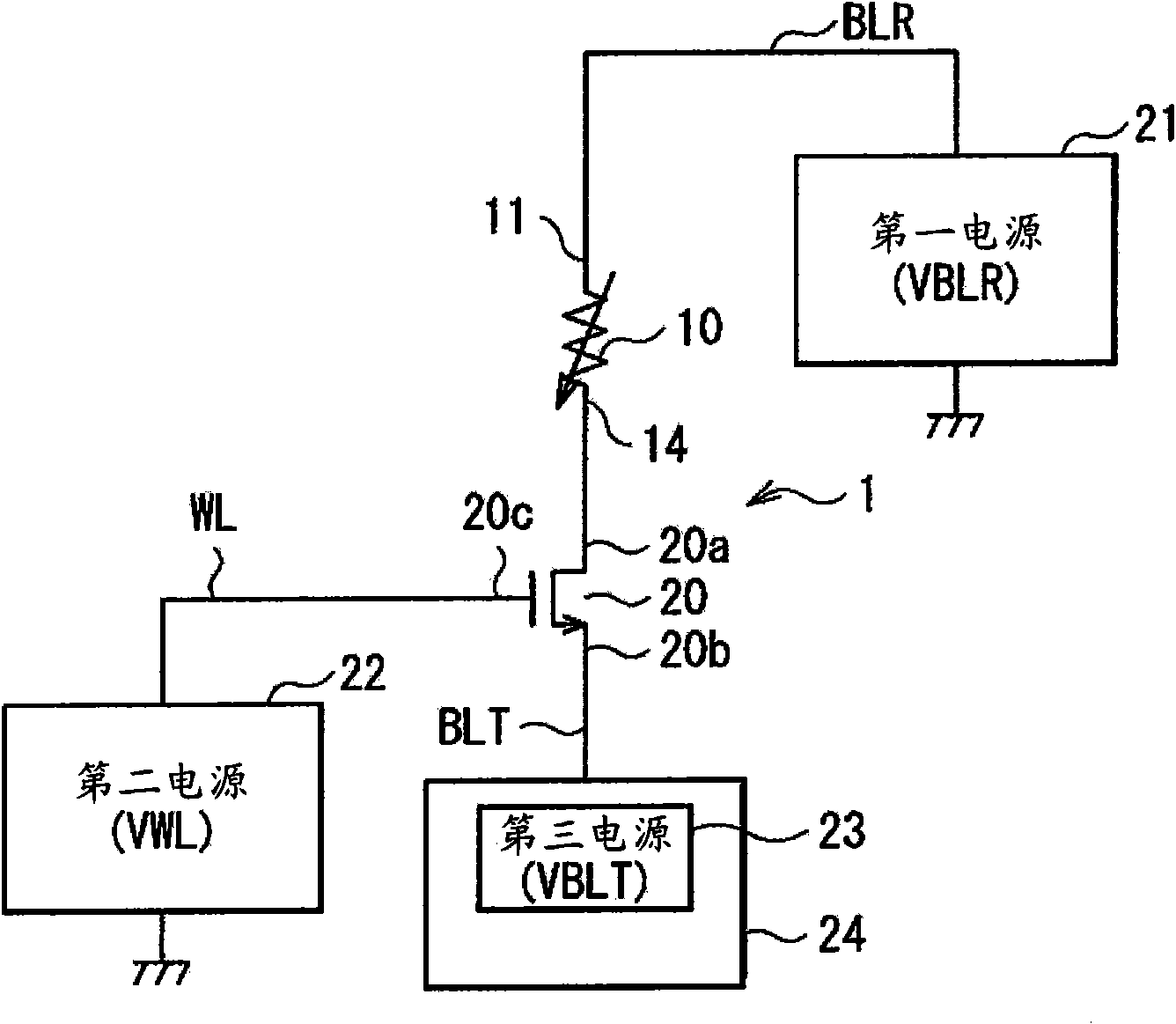

Storage device and information rerecording method

Provided is a storage device wherein a voltage requiring control is reduced and a peripheral circuit scale is reduced. A first pulse voltage (VBLR) is supplied to an electrode (11) of a variable resistance element (10) from a first power supply (21) through a bit line (BLR), a second pulse voltage (VWL) for cell selection is supplied to a control terminal (20c) of a transistor (20) from a second power supply (22) through a word line (WL), and a third pulse voltage (VBLT) is supplied to a second input / output terminal (20b) of the transistor (20) from a third power supply (23) through the bit line (BLT). At the time of rewriting information, a cell voltage and a cell current can be varied (reduced or increased) by adjusting the voltage value (VBLT) of the third power supply (23) by the adjusting circuit (24).

Owner:SONY CORP

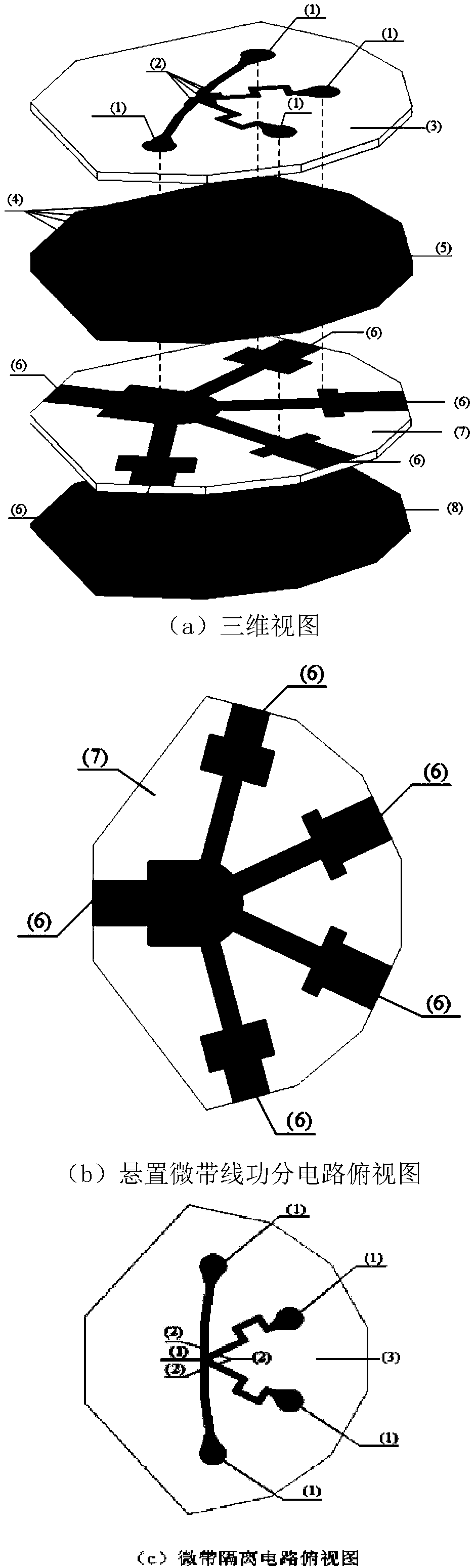

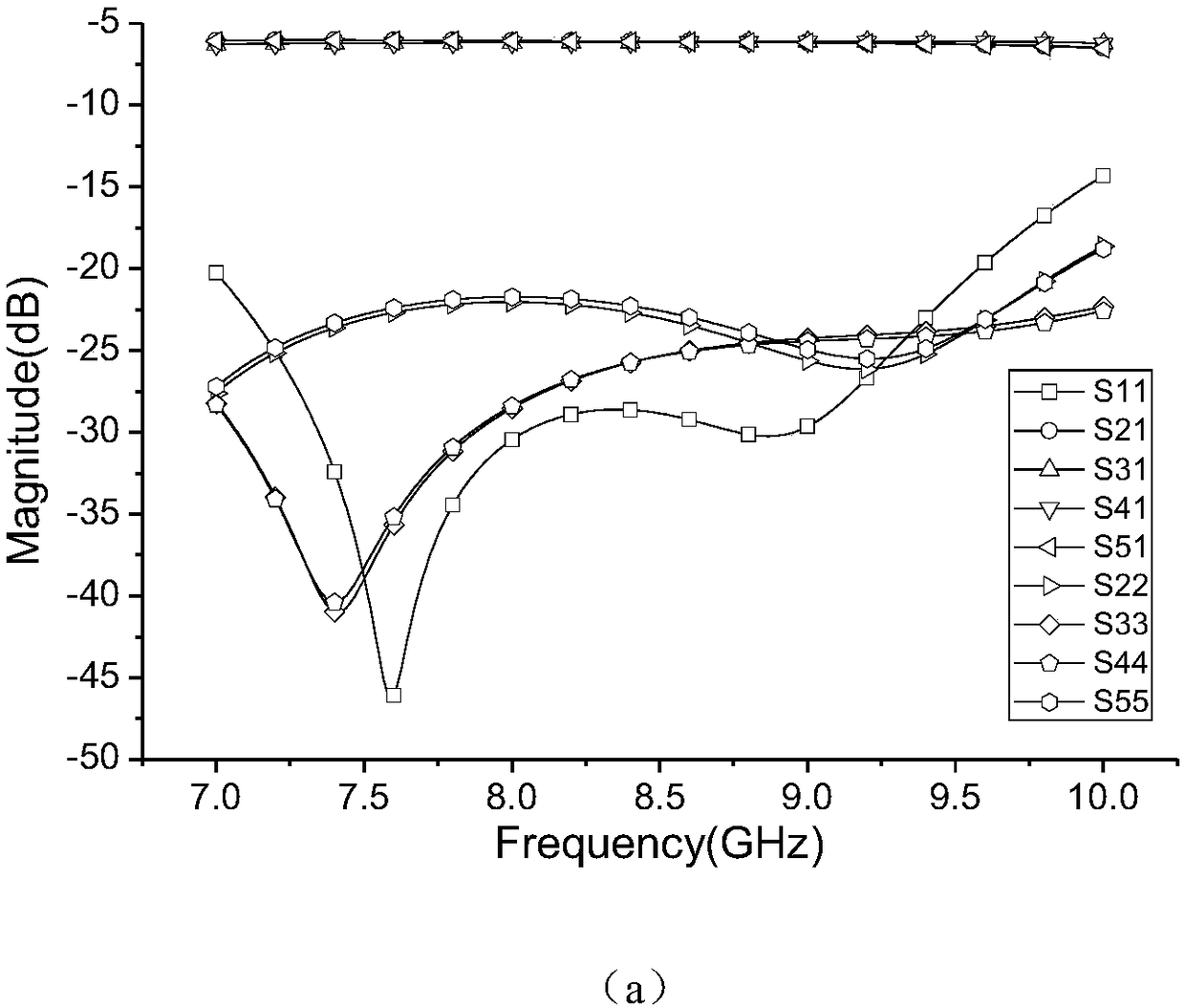

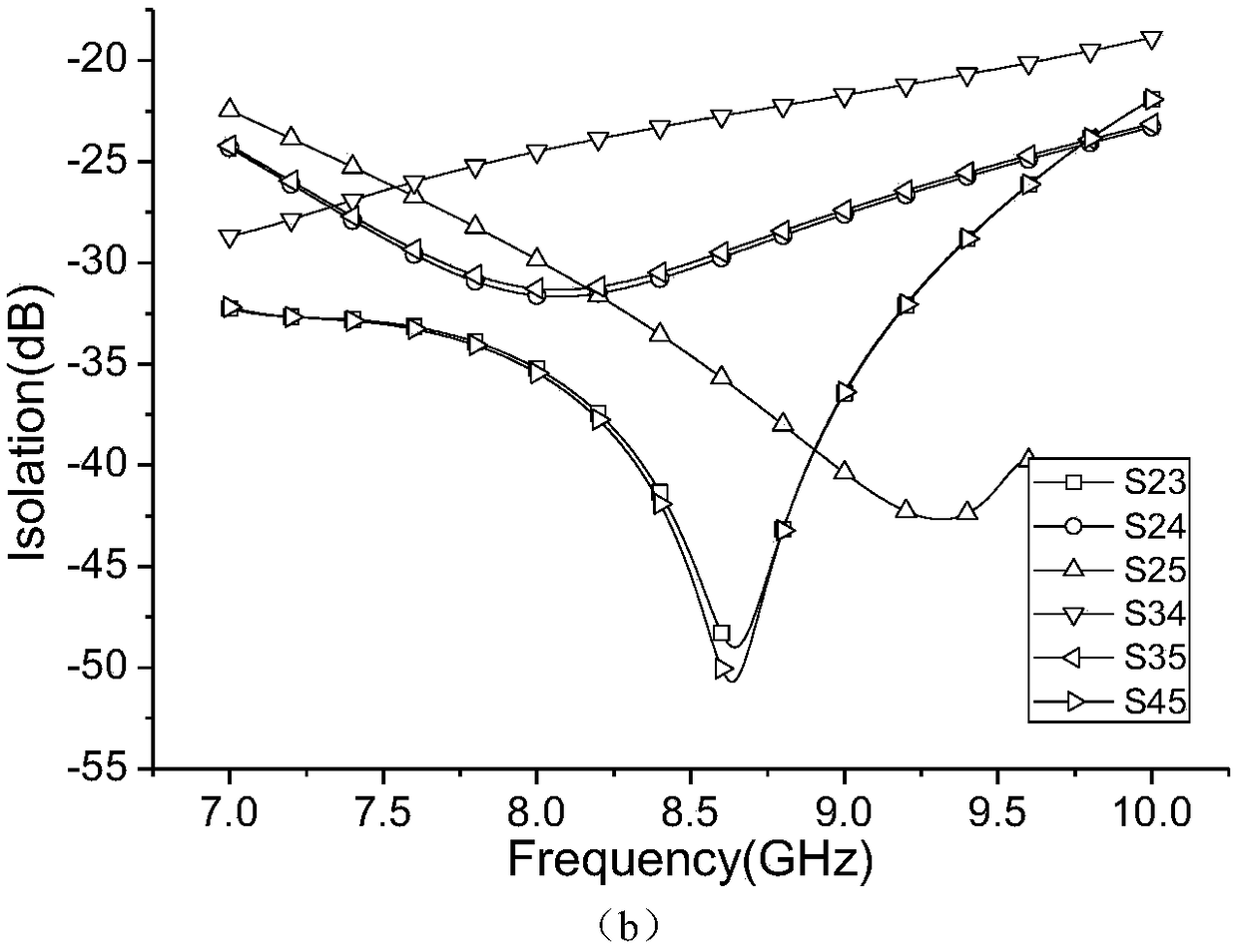

Compact suspended microstrip high-isolation multi-power combiner

The invention relates to a compact suspended microstrip high-isolation multi-power combiner. The compact suspended microstrip high-isolation multi-power combiner is composed of a suspended microstrippower dividing / combining circuit, a microstrip or suspended microstrip isolation circuit and connection coaxial cables; the suspended microstrip power dividing / combining circuit is composed of input ports, an output port, a dielectric substrate, metal microstrips, an upper grounding metal plate and a lower grounding metal plate; the isolation circuit adopts star connection, and an isolation resistor is installed on the isolation circuit; the suspended microstrip power dividing circuit achieves power allocation and input / output impedance matching; and the isolation circuit achieves good outputVSWR and isolation among the ports. The compact suspended microstrip high-isolation multi-power combiner has the advantages of being low in insertion loss, good in input / output echo, high in power capacity and isolation, wide in bandwidth, small in circuit size and the like, can be applied into various high-power microwave and millimeter wave systems and has the wide application prospect in systems of communication, radar, measurement and control and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

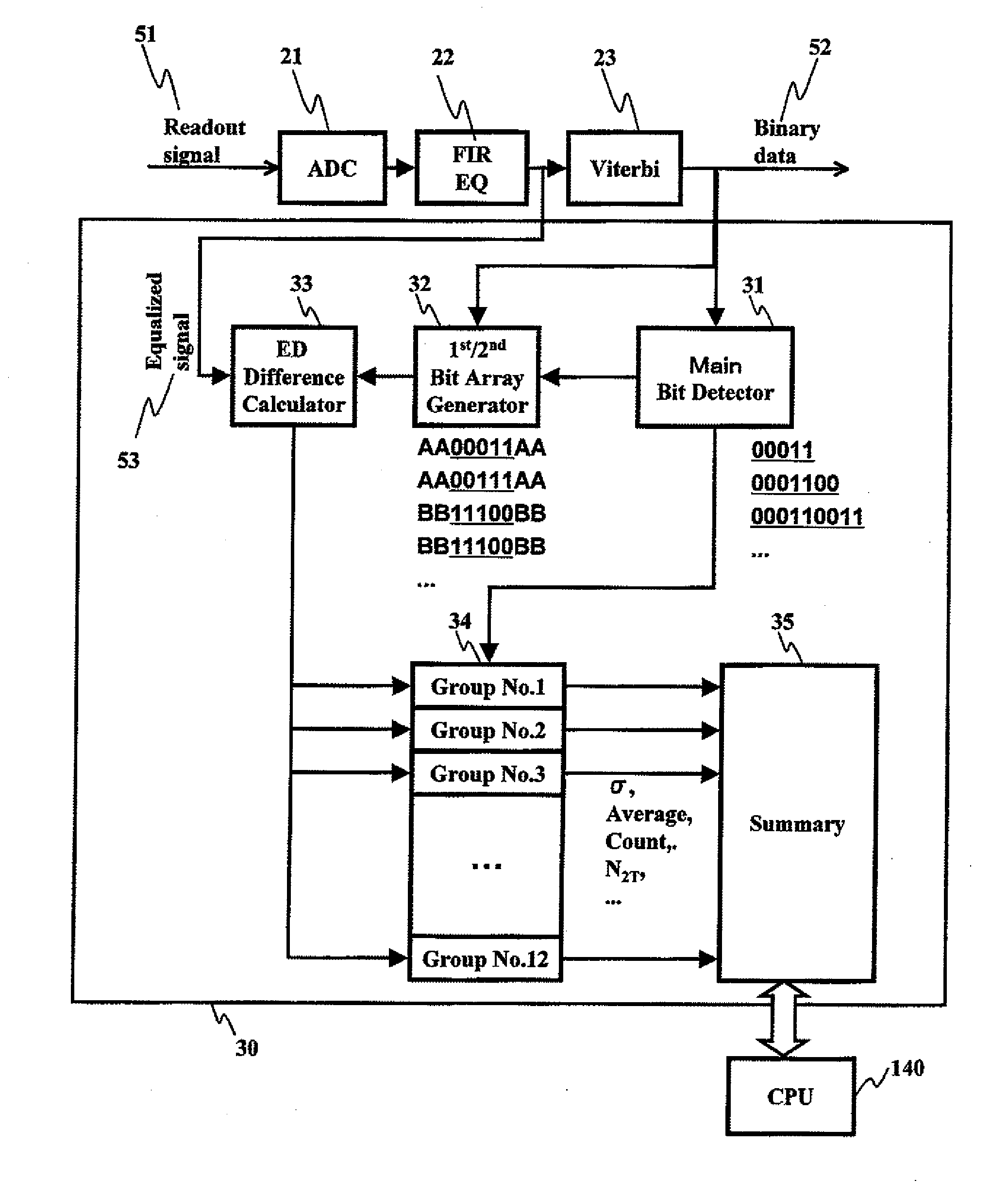

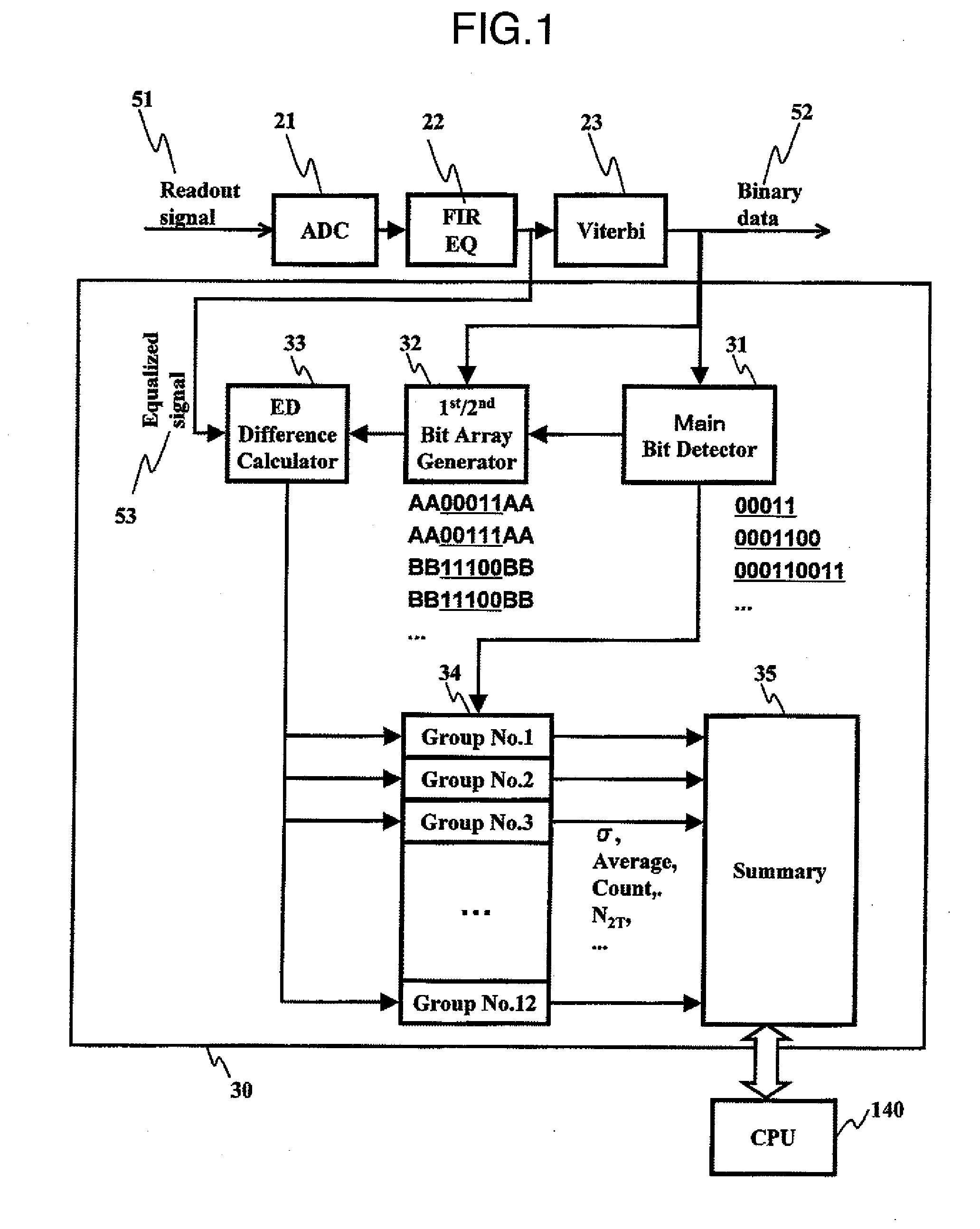

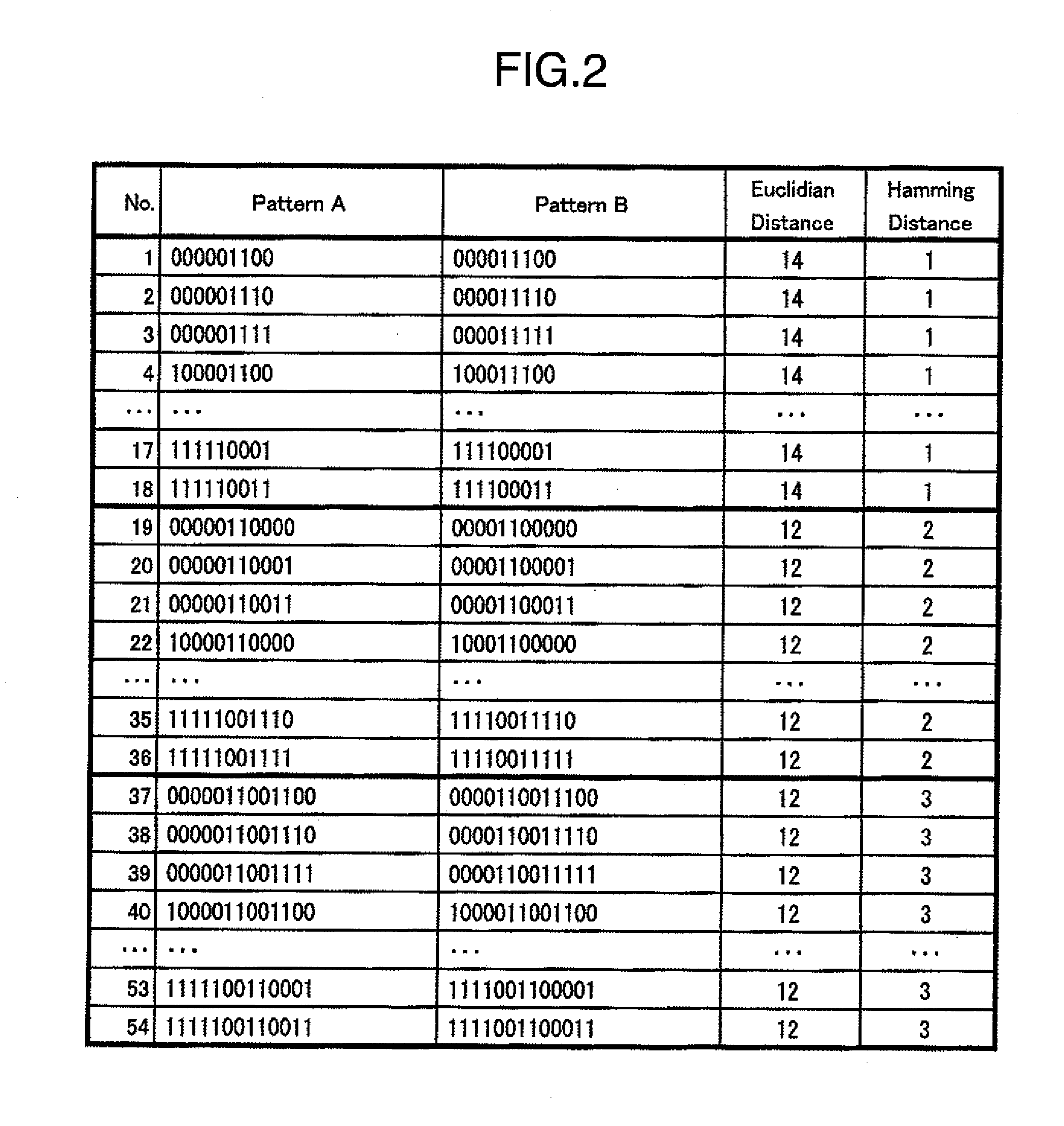

Method of evaluating reproduce signal and optical disc drive

InactiveUS20100195462A1Simple processConvenient lengthCombination recordingTelevision system detailsCircuit sizingTarget signal

Owner:KONINKLJIJKE PHILIPS NV

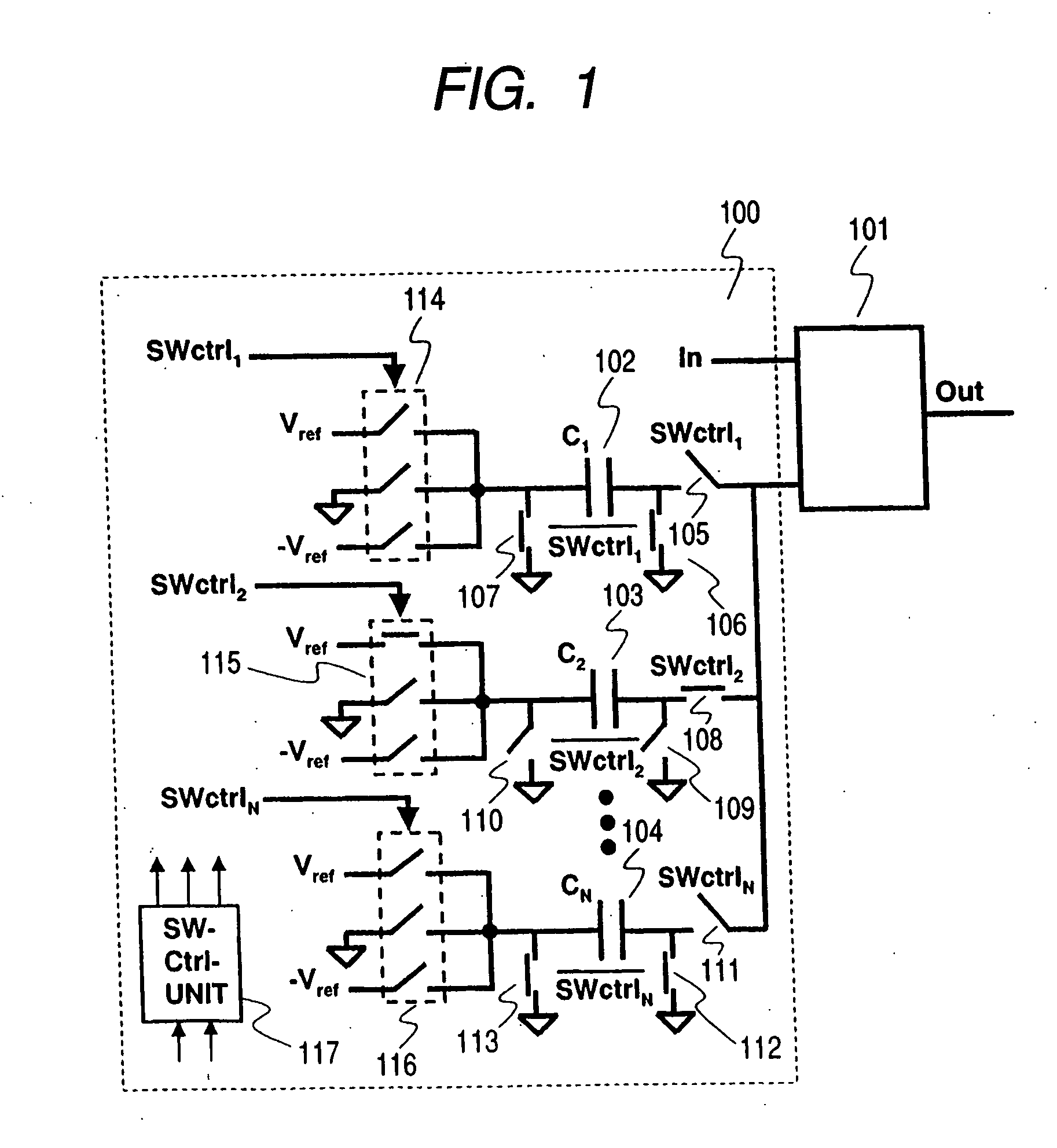

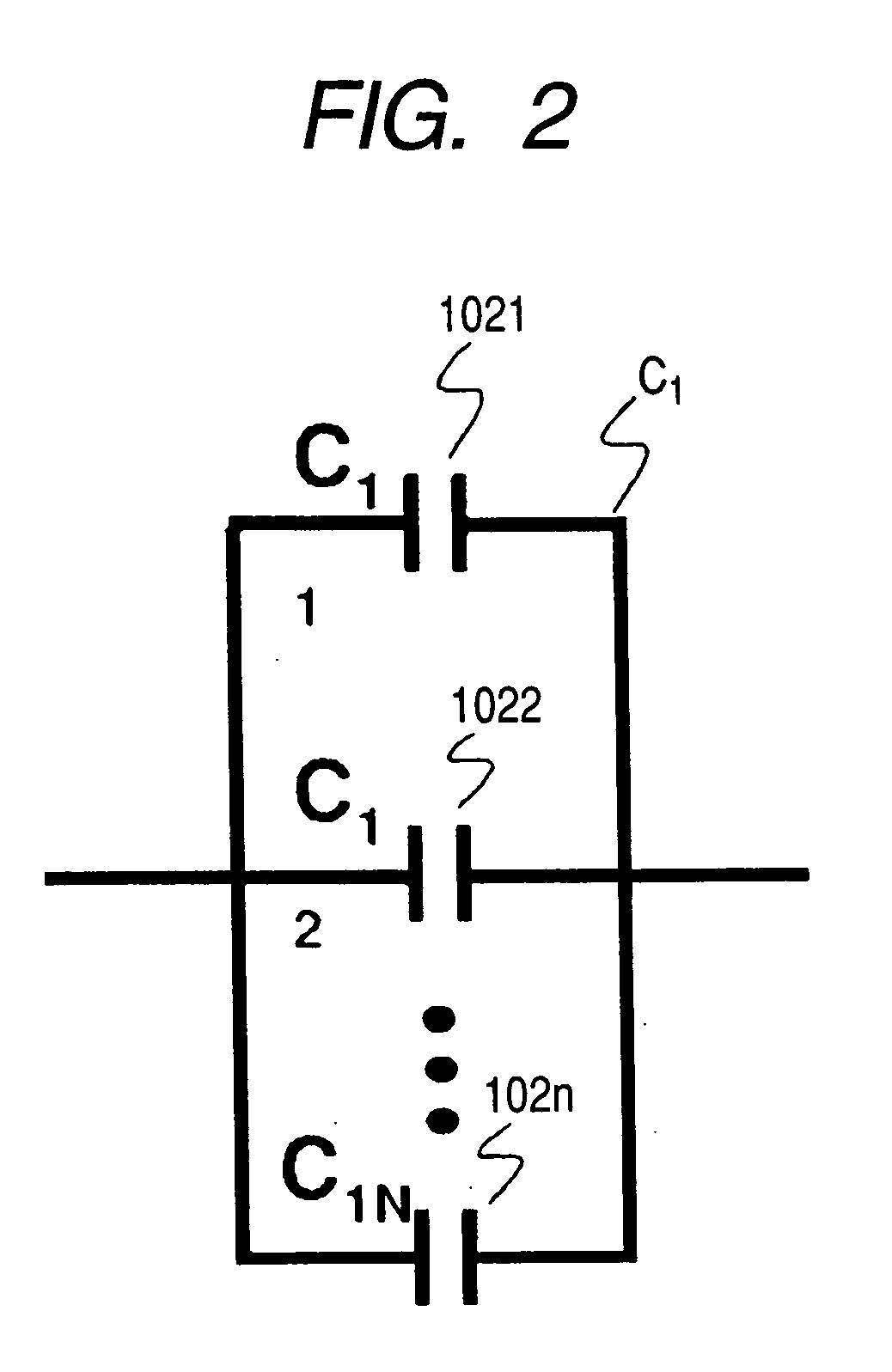

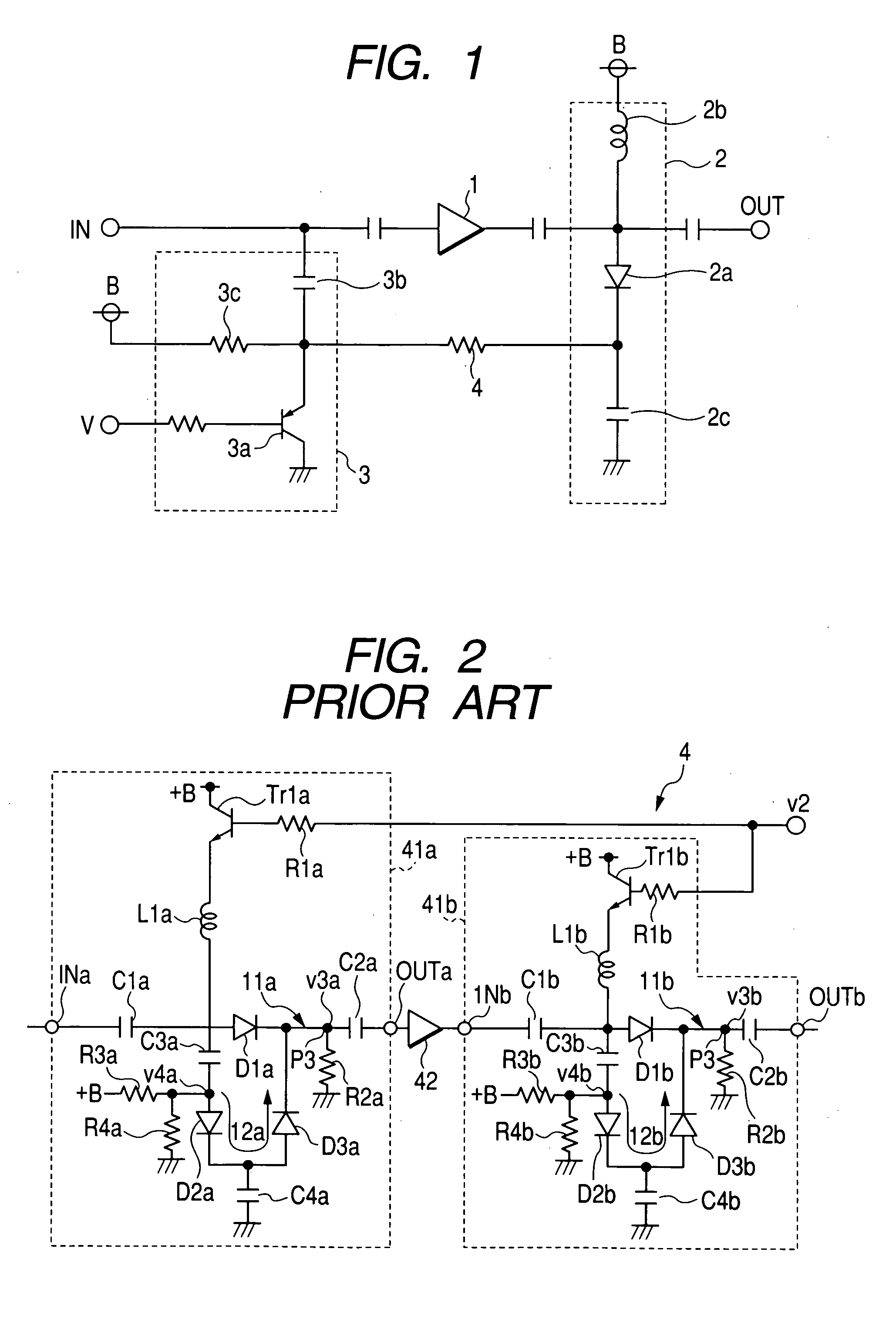

Variable attenuation circuit having large attenuation amount with small circuit size

InactiveUS20060028291A1Large attenuation amountSmall distortionMultiple-port networksPulse automatic controlUltrasound attenuationCircuit sizing

A variable attenuation circuit includes an attenuation circuit which has a first semiconductor variable impedance element, and an attenuation control circuit of which the impedance is changed by a control voltage to be applied from the outside and which has a second semiconductor variable impedance element for controlling the impedance of the first semiconductor variable impedance element. The attenuation circuit and the attenuation control circuit are connected in cascade. Therefore, signals can be attenuated by the attenuation control circuit, in addition to the attenuation circuit.

Owner:ALPS ALPINE CO LTD