Large scale integrated circuit test data and method for testing power consumption cooperate optimization

A large-scale integrated circuit and test data technology, applied in the fields of electronic circuit testing, electrical measurement, measurement devices, etc., can solve problems such as hindering the rapid development of system-on-chip SOC testing technology, compressing test data in a single research direction, etc., to reduce scan testing. Power Consumption, Guaranteed Test Coverage, Ease of Implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

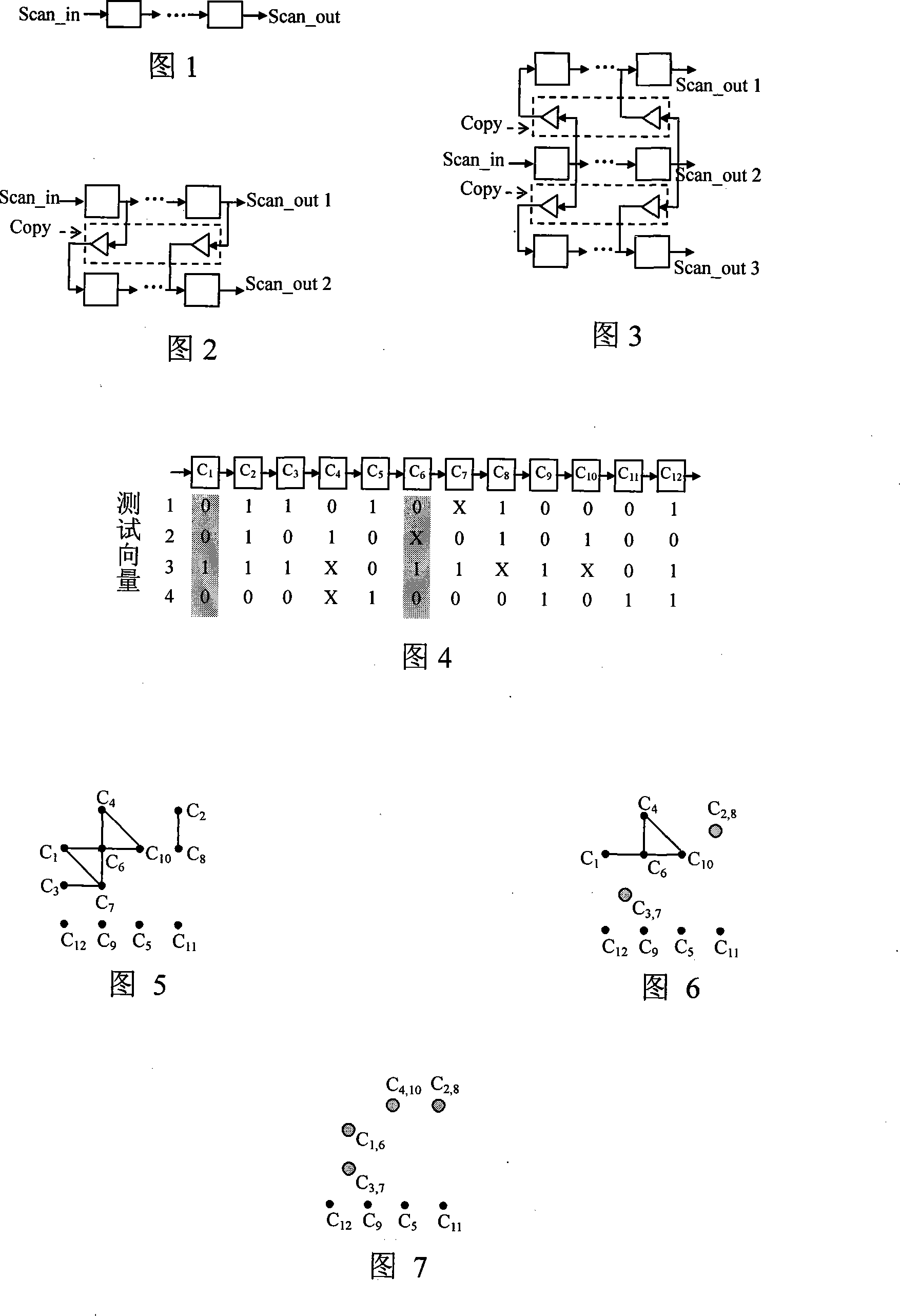

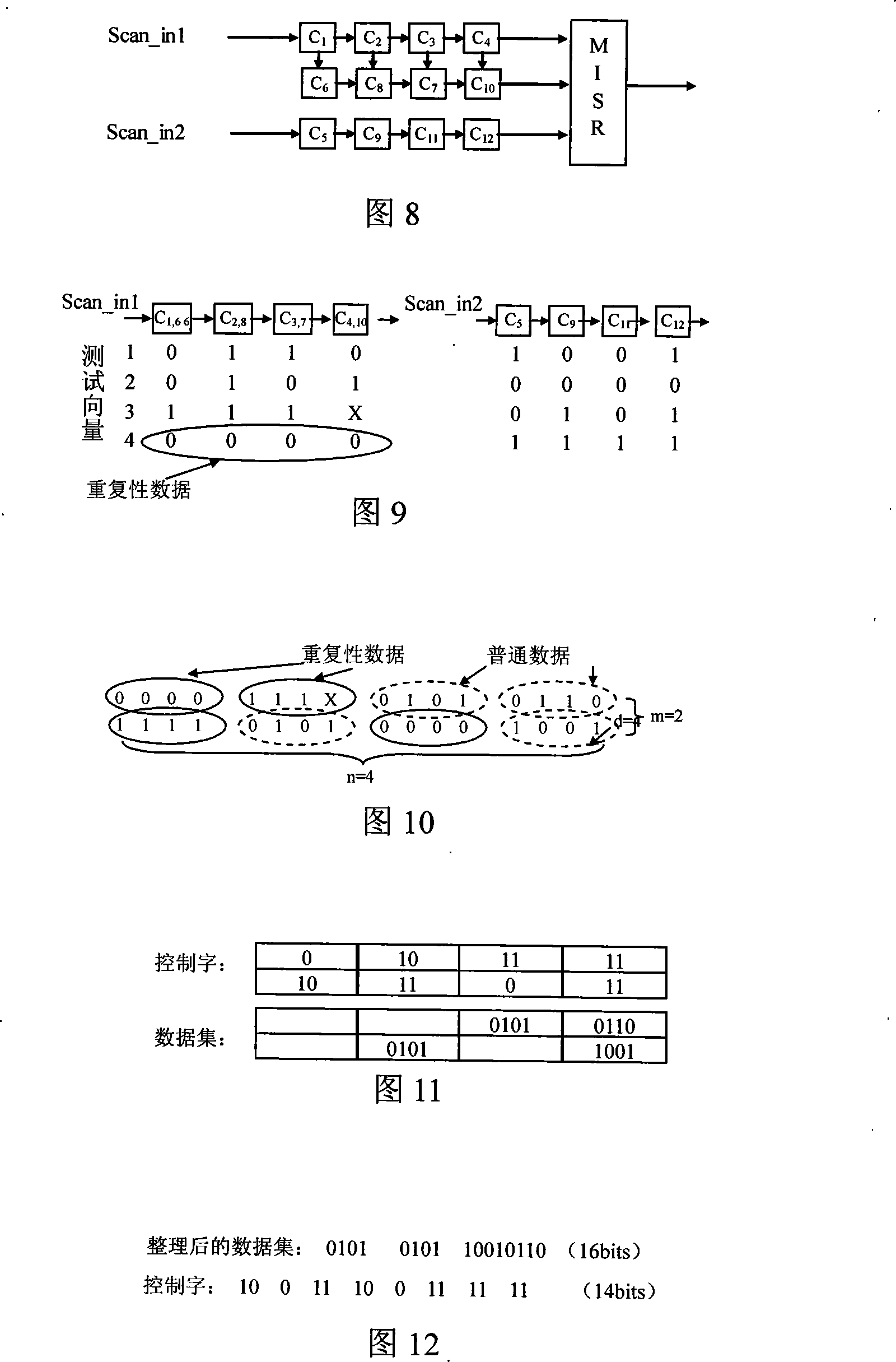

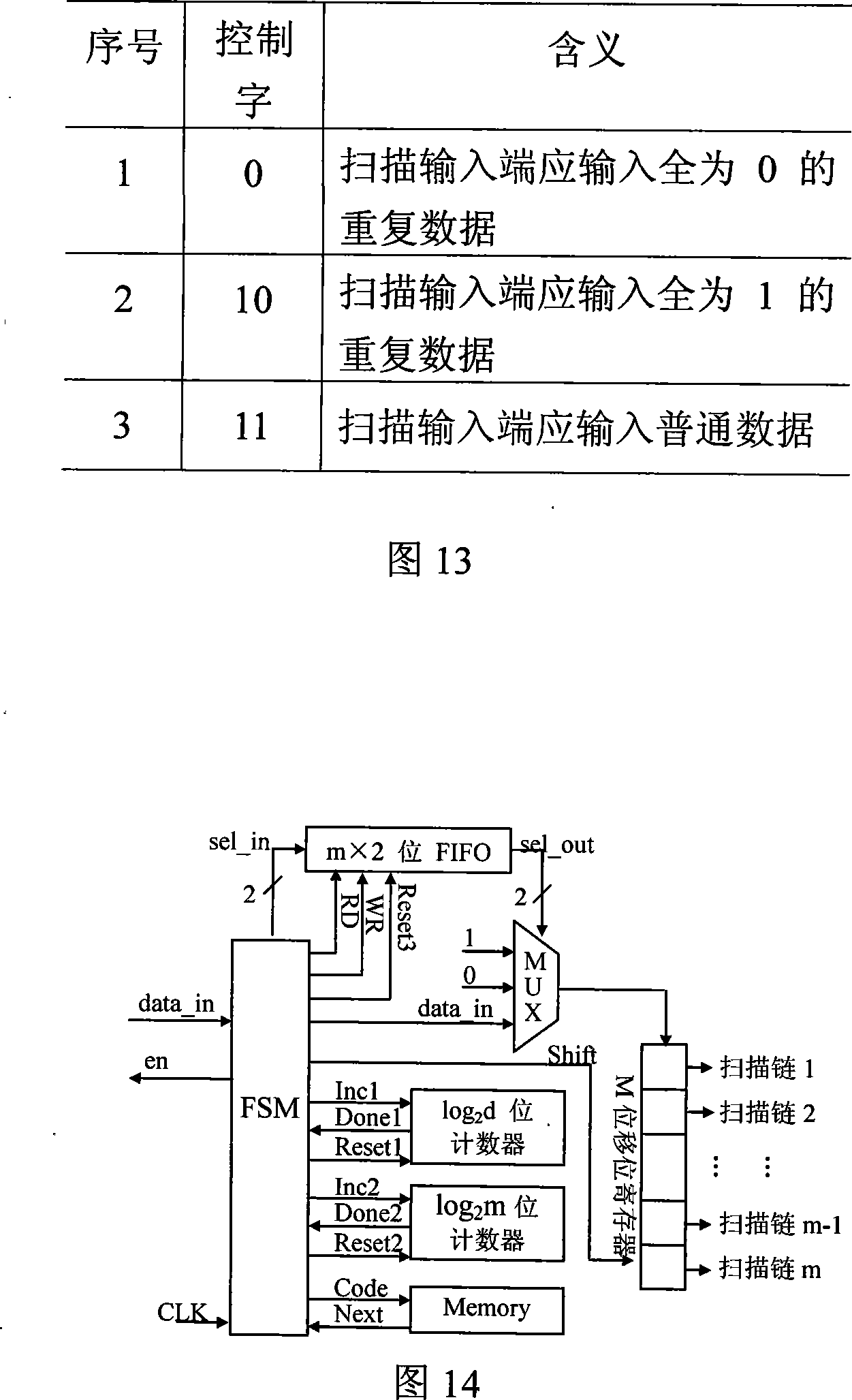

[0018] Specific implementation mode 1: This implementation mode is described in conjunction with FIGS. 1 to 14 . The method steps of this implementation mode are:

[0019] Step 1: Put the test set T D ={t 1 , t 2 ,...tn} is represented as a two-dimensional matrix, each row represents a test vector, a total of n test vectors, each column represents the value assigned to a scan unit in turn, a total of S scan units; calculate the compatibility between the column vectors in the test set , that is, the compatibility between each scanning unit;

[0020] Step 2: Divide the scanning units into K1, K2, and K3 groups by using the clique division method based on the principle of prior merging of isolated points and 2-complete points. The scanning units in each clique are completely compatible. Each group contains only one scanning unit. For the group belonging to the K2 class, each group contains only two scanning units. For the group belonging to the K3 class, each group contains th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More