Low-power deterministic bist and seed compression method based on single and double jumps

A deterministic, low-power technology that is applied in functional testing, measuring electrical variables, and detecting faulty computer hardware. It can solve problems such as failure to achieve fault coverage, increase test power consumption, and high fault coverage. Effects of reduced test power consumption, reduced test power consumption, and reduced test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described below in conjunction with accompanying drawing.

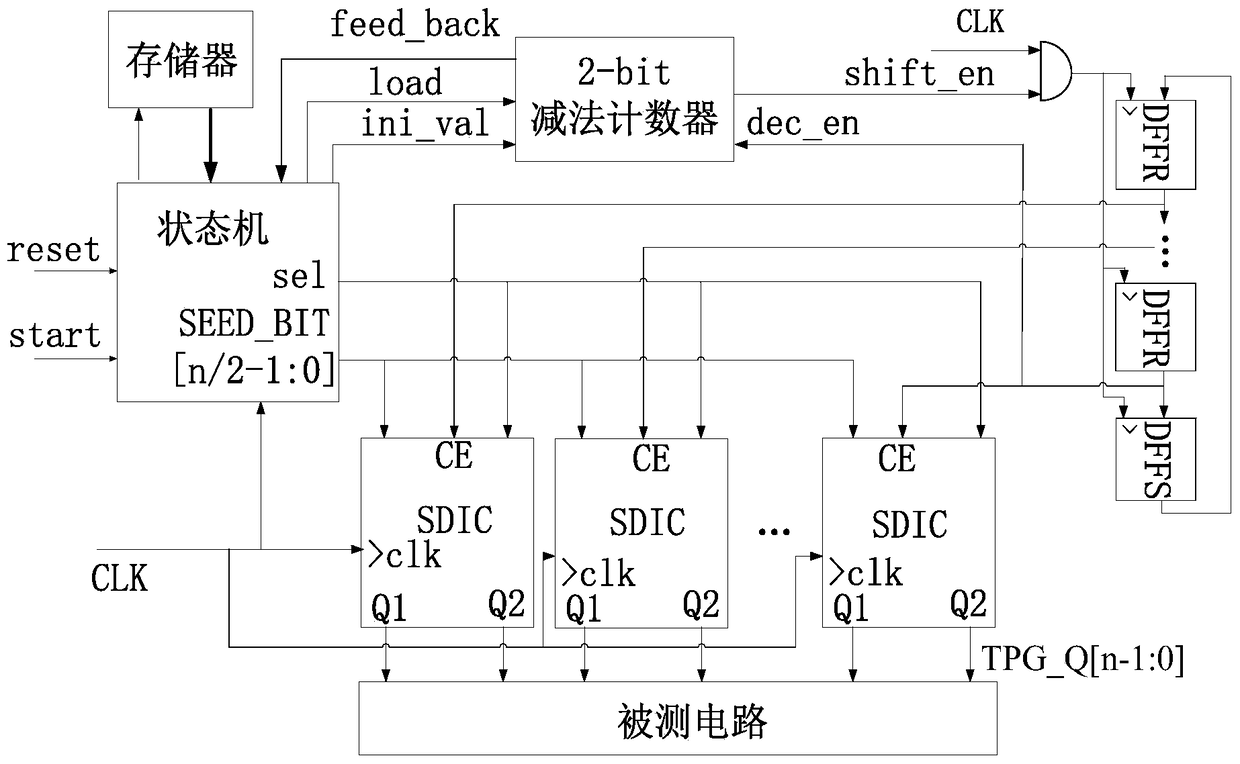

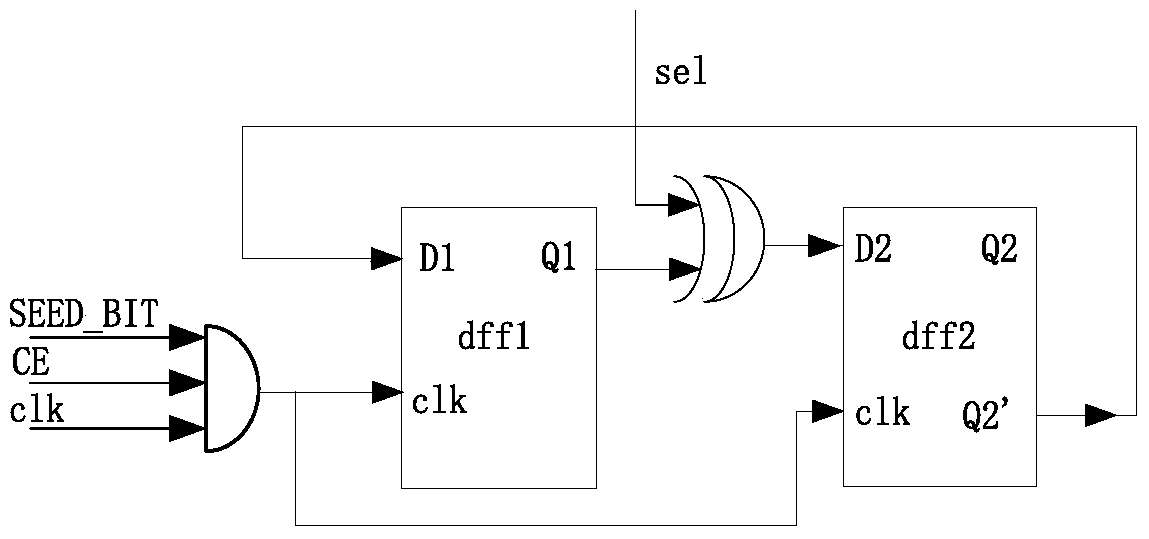

[0031] Such as figure 2 As shown, a low-power deterministic BIST based on single and double transitions, including a state machine, n / 2 single and double transition units SDIC, a length of n / 2+1 bit serial shift register, a subtraction counter, Memory and circuit under test, wherein n is the test width of test vector set; Described state machine is provided with 5 input data ports, is respectively CLK, start, reset, feedback and ROM data output, in addition, state machine is also provided with 5 An output signal port is respectively SEED_BIT[n / 2-1:0], sel, ini_val, load and ROM read control signals; each SDIC unit in the n / 2 single and double transition unit SDIC is provided with 4 input ports are respectively SEED_BIT, CE, sel and clk, in addition, there are also 2 output ports, which are respectively Q1 and Q2; the length is n / 2+1 bit serial shift register, which is com...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More