Low power consumption LFSR reseeding test compression method facing scanning design

A technology of test compression and reseeding, which is applied in the direction of measuring electricity, measuring devices, and measuring electrical variables, etc., can solve the problems of high test power consumption, achieve the effects of reducing test power consumption, reducing the number, and improving test compression efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

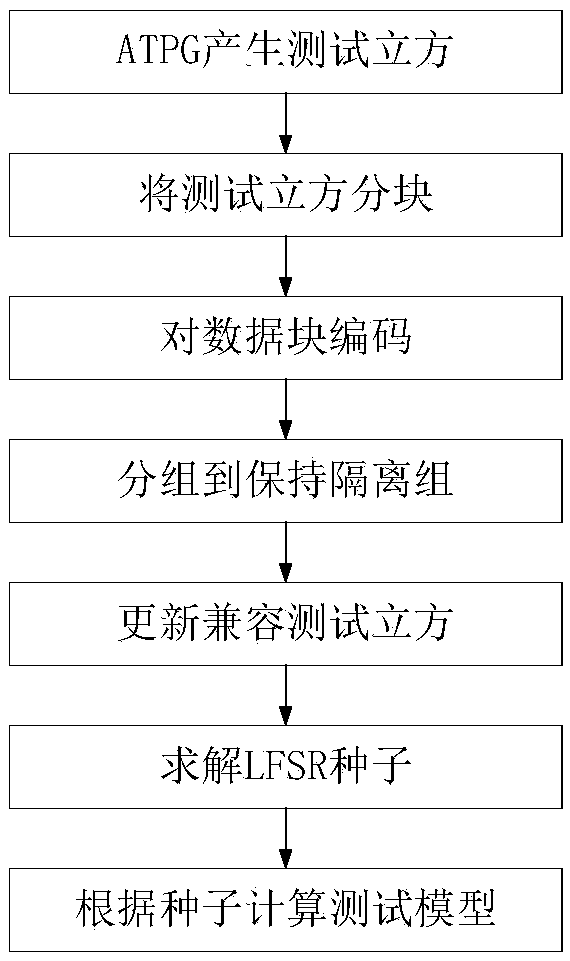

[0038] Below in conjunction with accompanying drawing and specific embodiment the method of the present invention is further described, and concrete steps of the present invention are as follows:

[0039] Step 1: Refer to attached figure 1 , to obtain the test set for the test circuit. First, 10,000 pseudo-random test patterns are used to test the circuit, and then the LFSR reseeding test is performed for those difficult-to-measure faults, and the test set is determined to be generated by the ATPG tool provided by Atalanta.

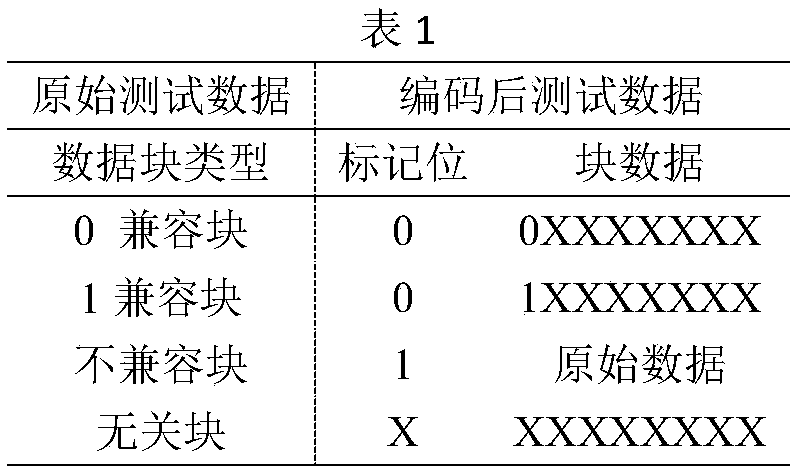

[0040] Step 2: Combine the attached figure 1 and figure 1 (a), block preprocessing is performed on the test cube, and different mark bits are added to the data block according to different data types.

[0041] Step 3: According to the attached figure 1, according to the compatibility of the mark bits, the test cubes are grouped and sorted, and the update mark bits are added to determine whether the corresponding mark bits are loaded into the scan chai...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More