Automatic test system and method of programmable logic device on basis of boundary scan

An automatic test system and boundary scan technology, applied in the field of electronics, can solve problems such as non-compliance with rapid testing, complex supporting software, and high learning costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

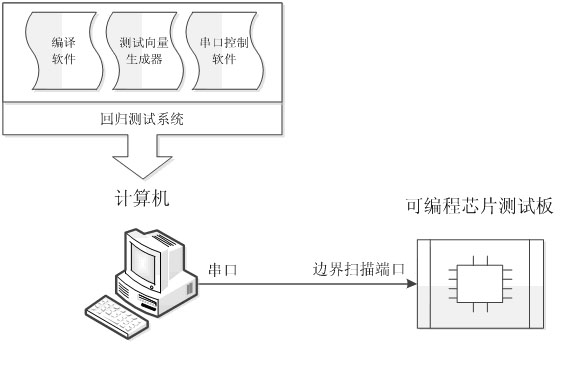

[0045] In order to simulate the test needs of users, we selected a total of 105 examples to be tested, including 51 examples of pure combinational circuits and 56 examples of sequential circuits; from the functional point of view, they include simple adders, multipliers, comparison device, encryption and decryption logic, as well as complex singing, VGA port control, communication and other applications. In addition, an FPGA chip selected by the test board supports JTAG boundary-scan technology, and has matching compiling software to meet the test requirements.

[0046] When testing, you only need to enter a command in the command line environment, and all 105 examples can be synthesized, compiled, downloaded, tested and counted. The whole process does not require manual operation, which greatly facilitates users to carry out repeated tests. It has been verified that most of the examples can pass the test at one time, and the examples that fail the test can be found by checkin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More