Patents

Literature

42 results about "Non-maskable interrupt" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computing, a non-maskable interrupt (NMI) is a hardware interrupt that standard interrupt-masking techniques in the system cannot ignore. An NMI is often used when response time is critical or when an interrupt should never be disabled during normal system operation. Such uses include reporting non-recoverable hardware errors, system debugging and profiling, and handling of special cases like system resets.

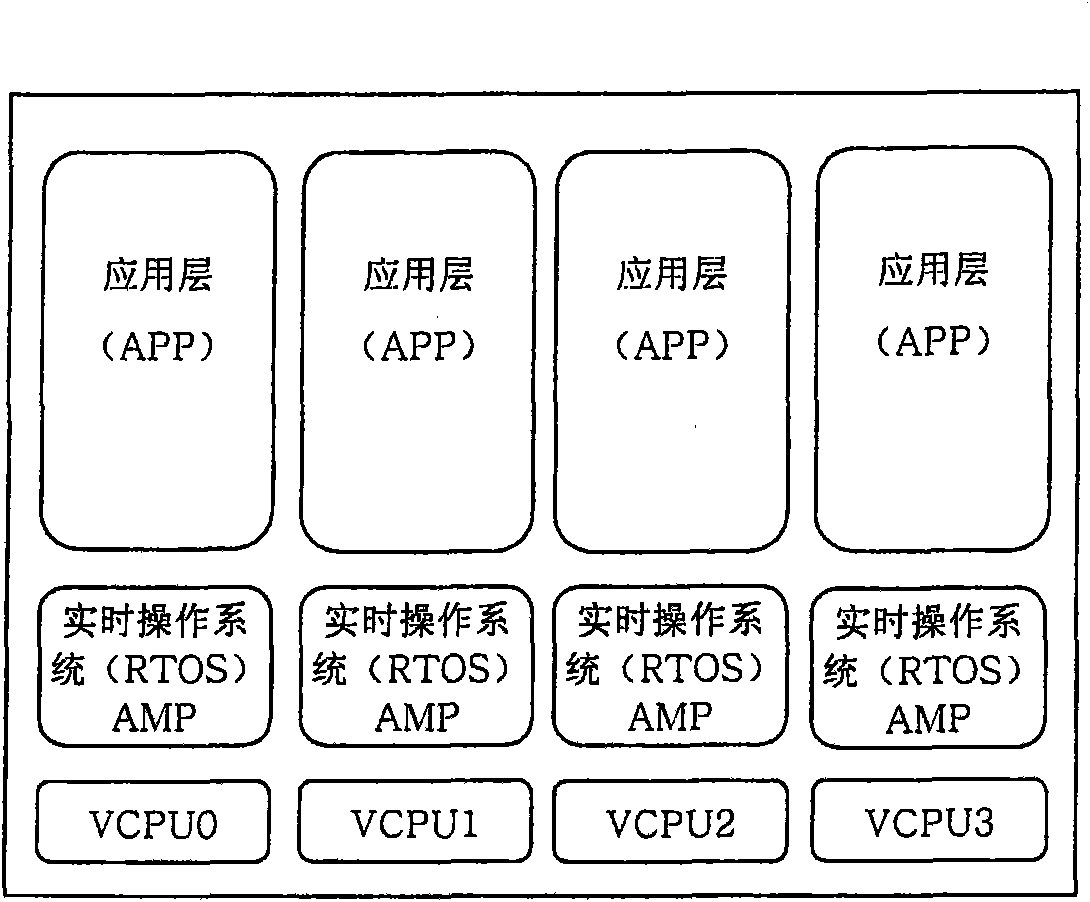

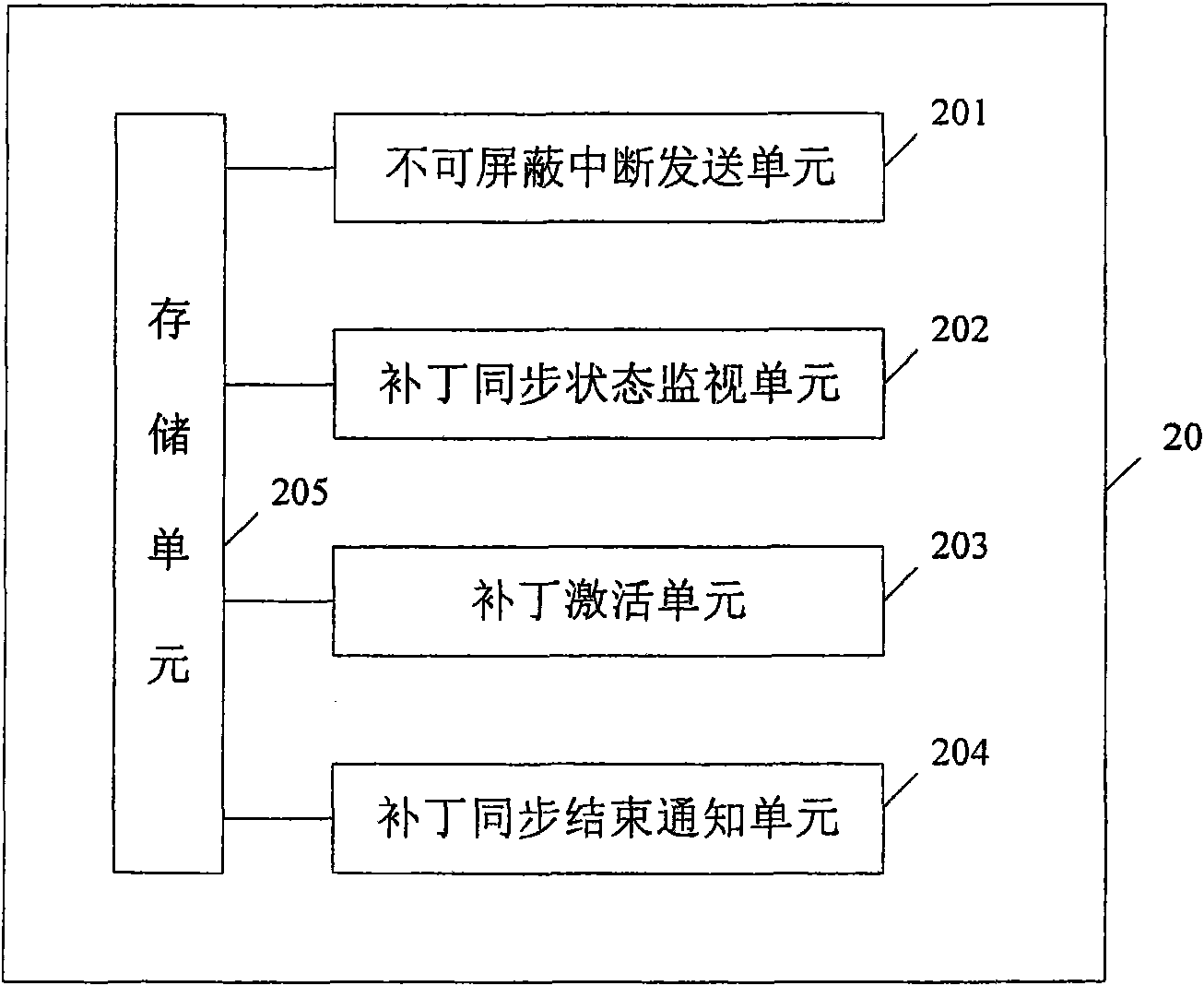

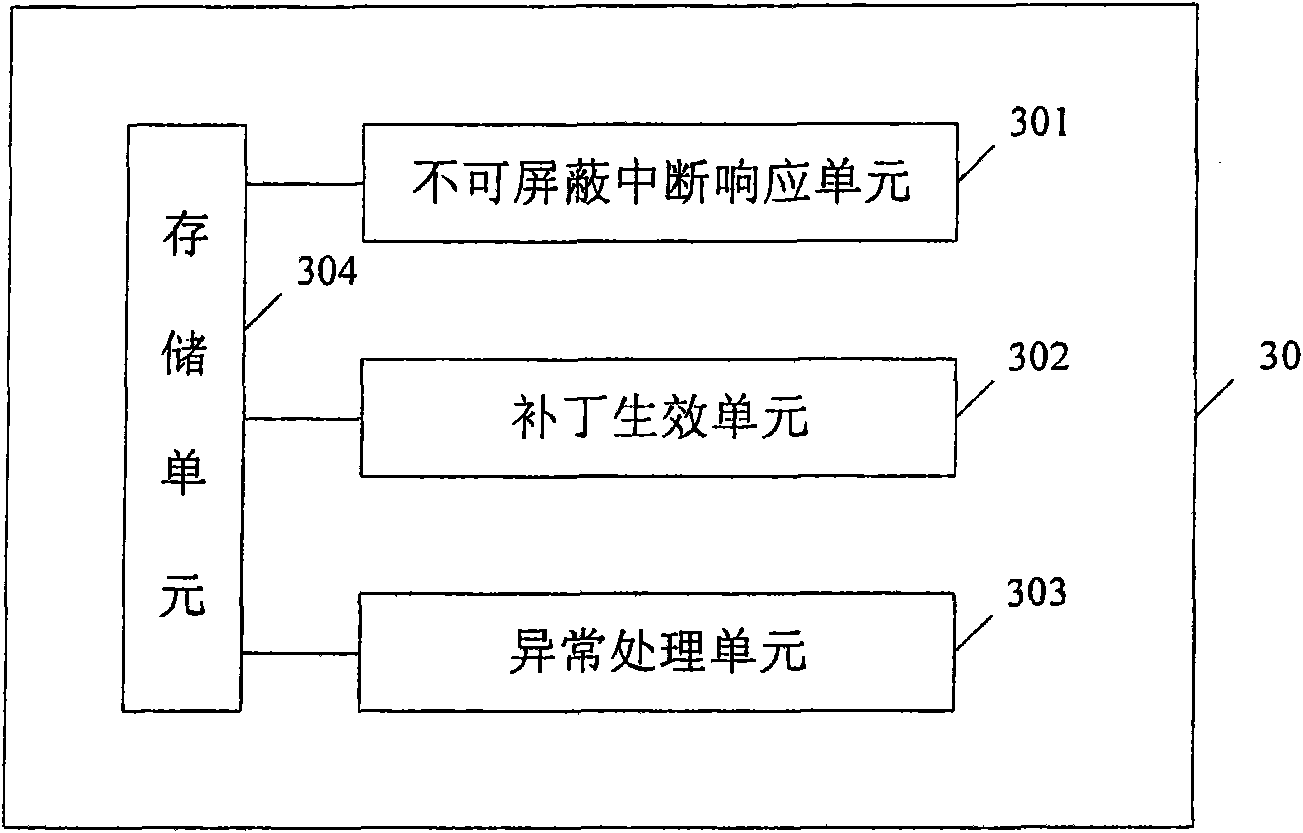

Patching method and patching device under multi-core environment

ActiveCN101561764AReduce overheadImprove reliabilityProgram initiation/switchingProgram loading/initiatingNon-maskable interruptBiological activation

The embodiment of the invention provides a patching method and a patching device under multi-core environment; the patching method comprises the steps of sending internuclear non-maskable interrupt to each target-virtual CPU of a shared code segment target-virtual CPU group so as to cause the target-virtual CPUs to respond to the internuclear non-maskable interrupt and enter a patching synchronization state, monitoring the patching synchronization state of the target-virtual CPUs, changing the first command of the patched primitive function of the target-virtual CPUs into an abnormal command after all target-virtual CPUs enter the patching synchronization state, and outputting an notice on the finishing of the patching synchronization state to all target-virtual CPUs so as to shift the patched primitive function to a new patching function while the patched primitive function is executed to an abnormity handling process triggered by the abnormal command. The method and the device adopt the synchronous mode of internuclear non-maskable interrupt to realize the patching synchronous activation of the target-virtual CPUs of the shared code segment and realize the complete effectiveness of patches during the abnormal handling process.

Owner:HUAWEI TEHCHNOLOGIES CO LTD

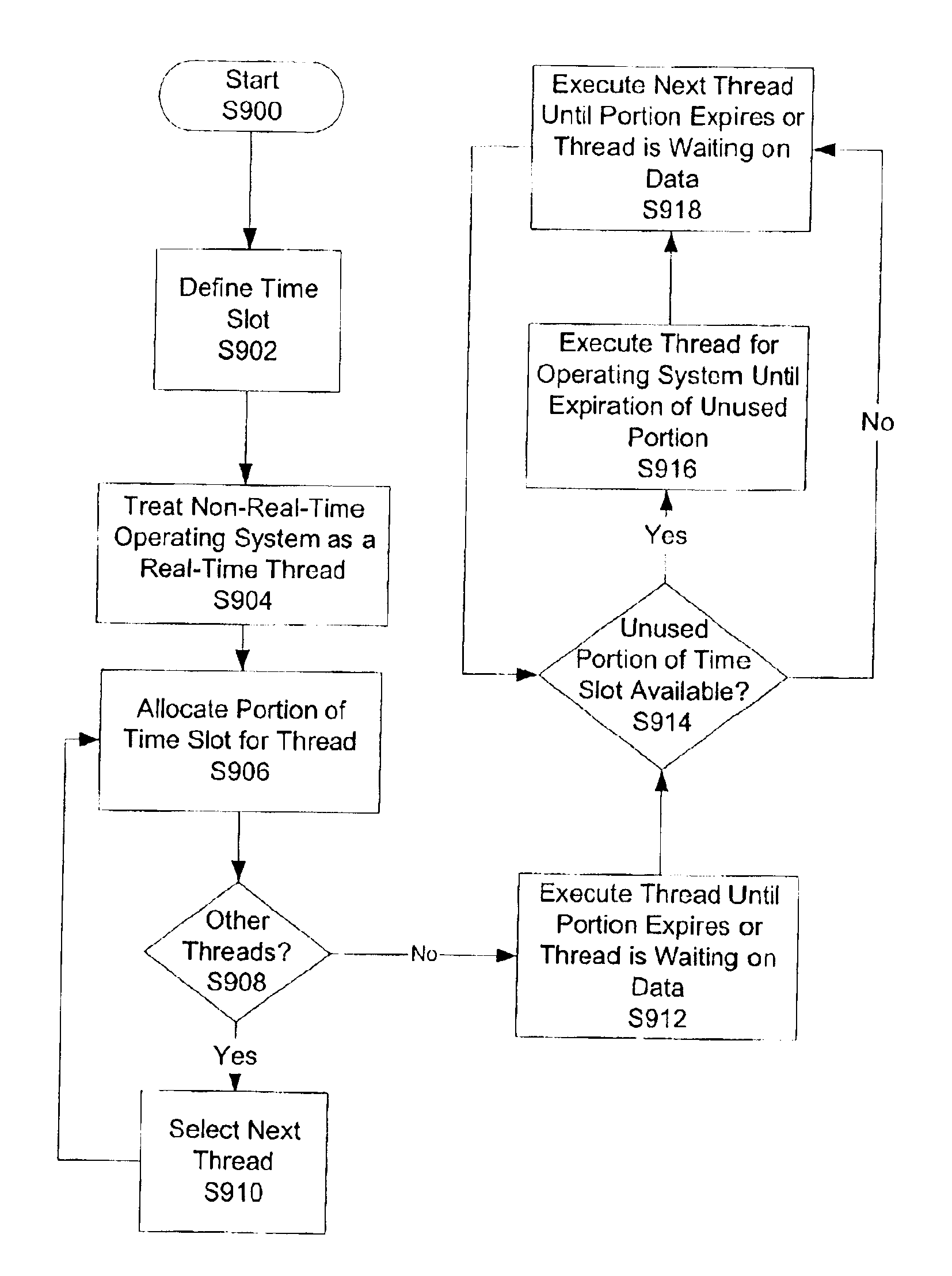

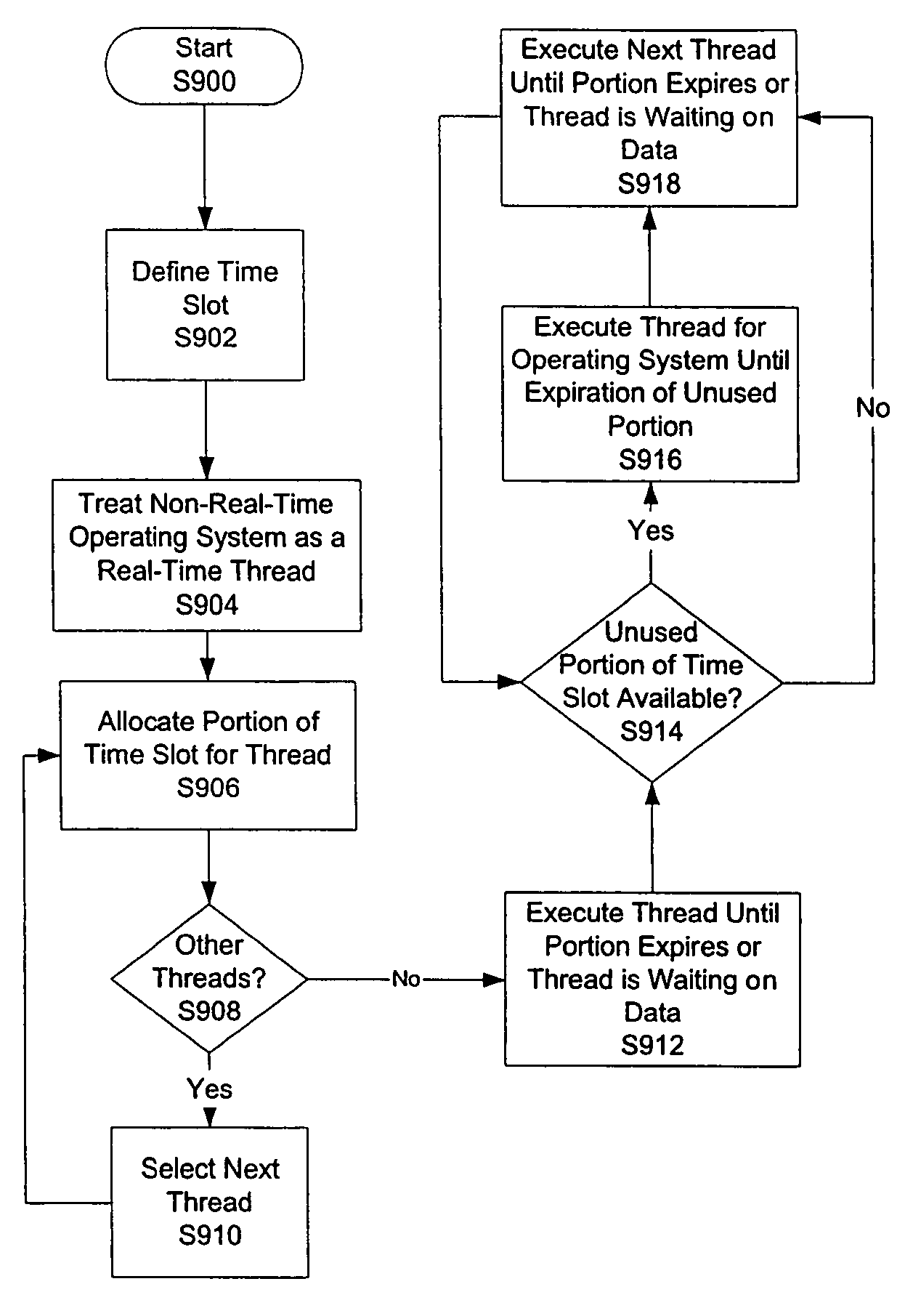

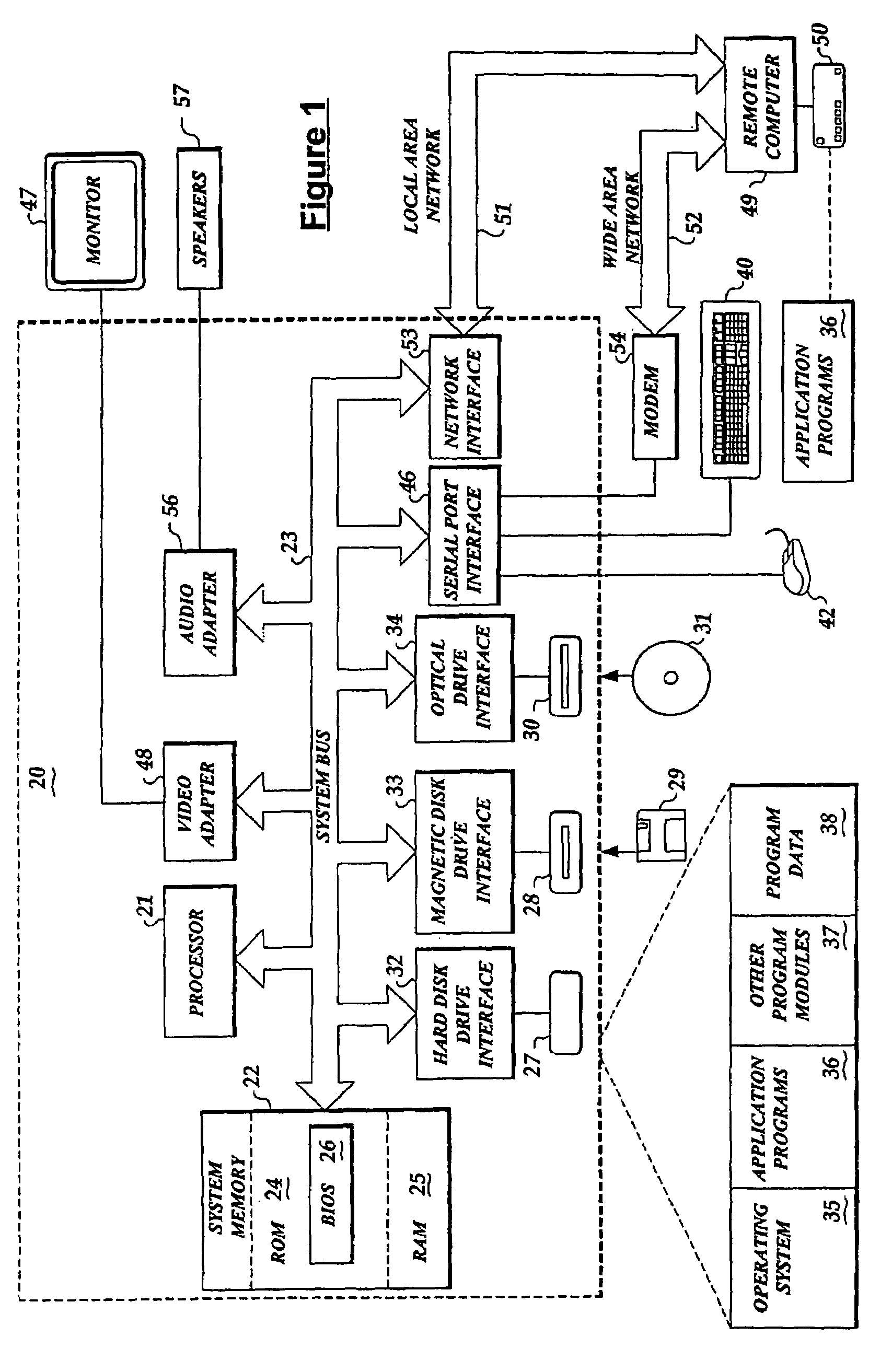

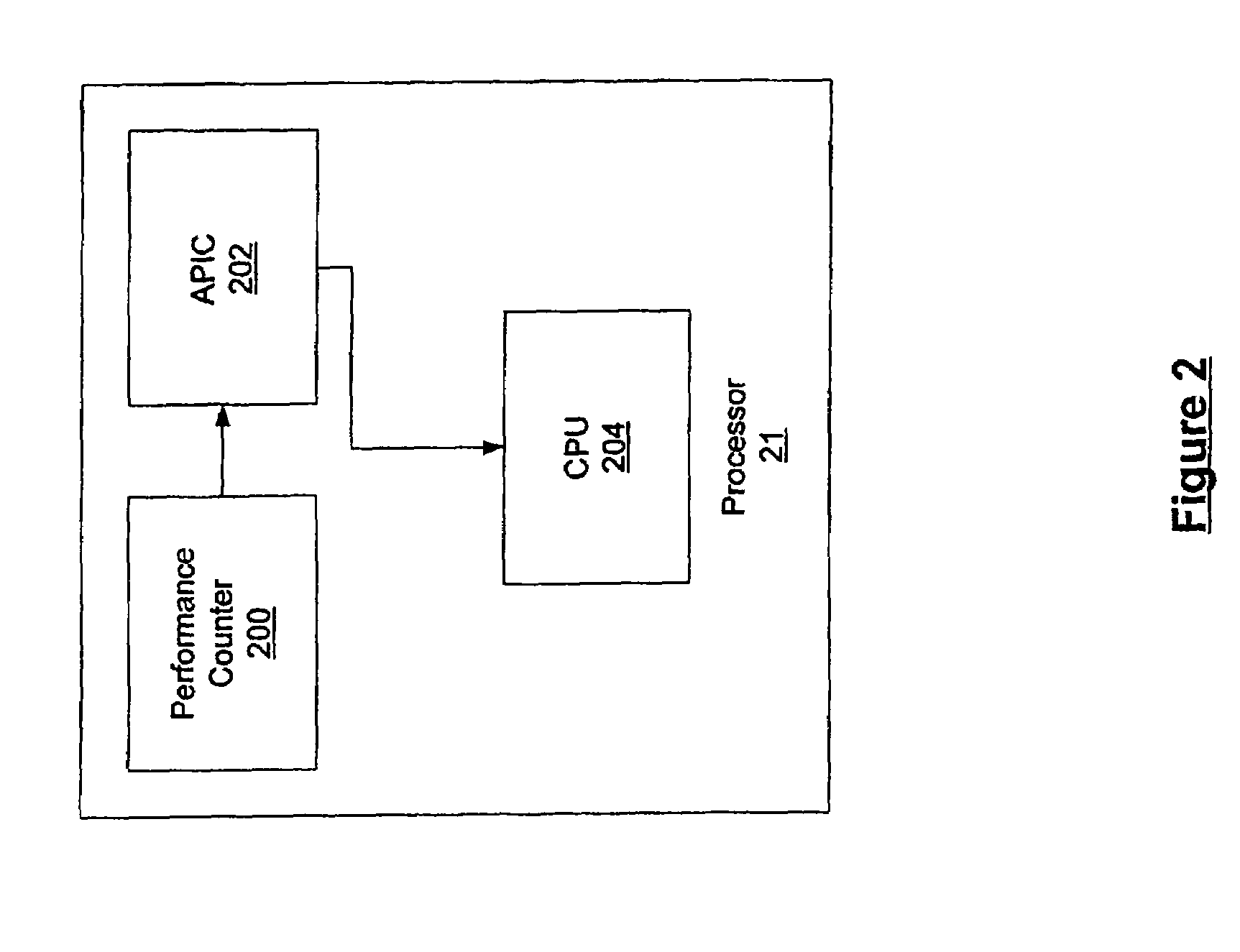

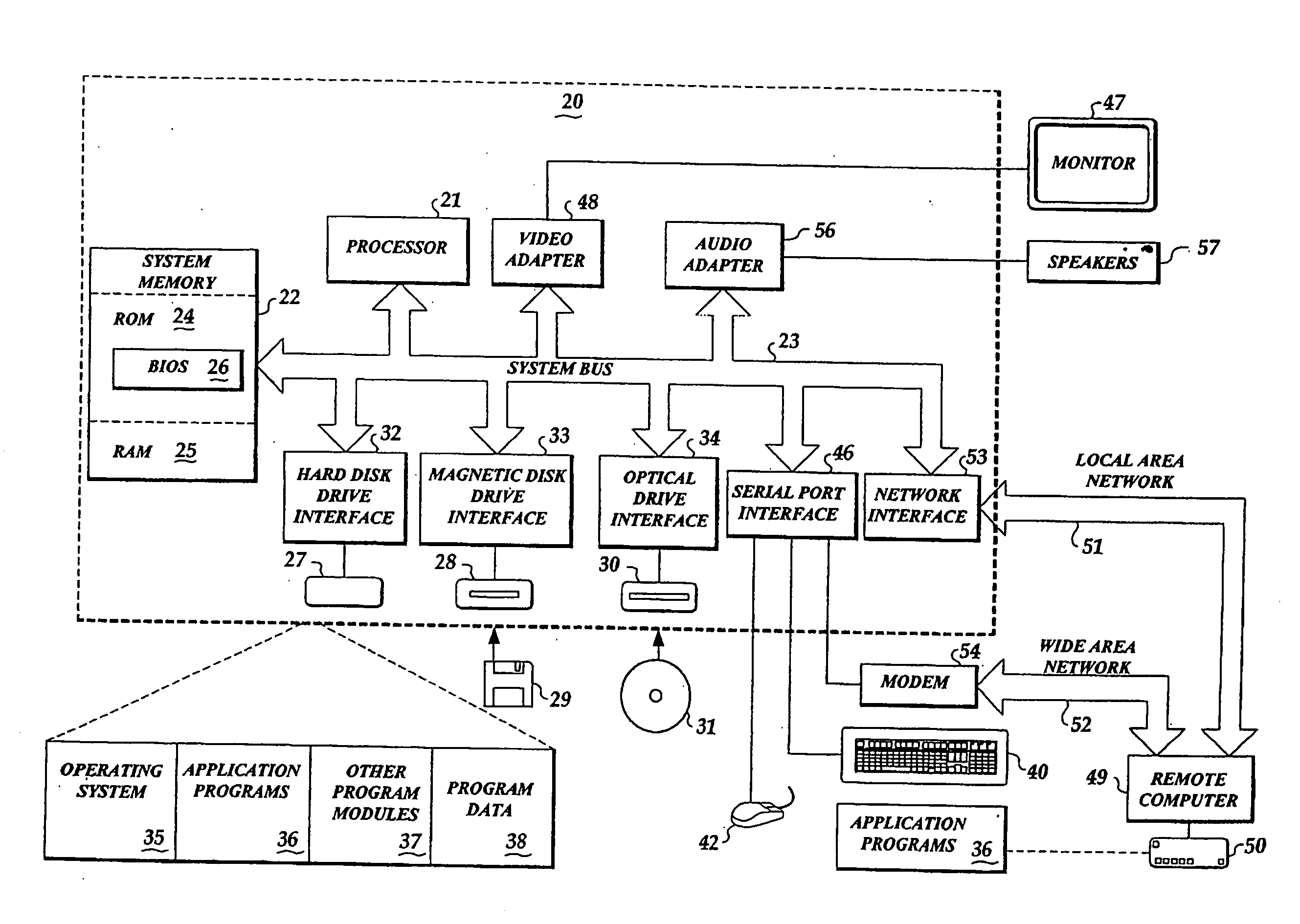

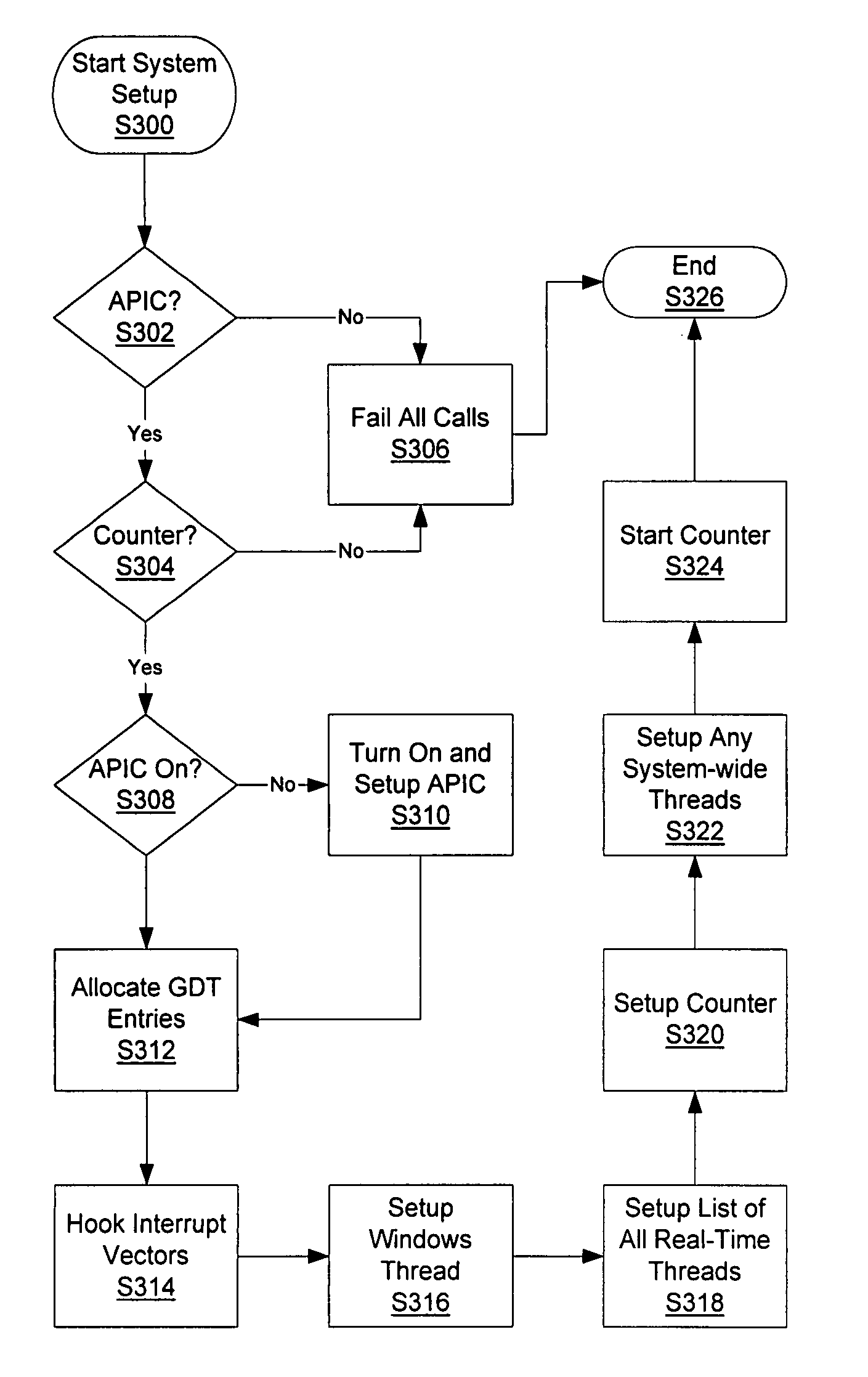

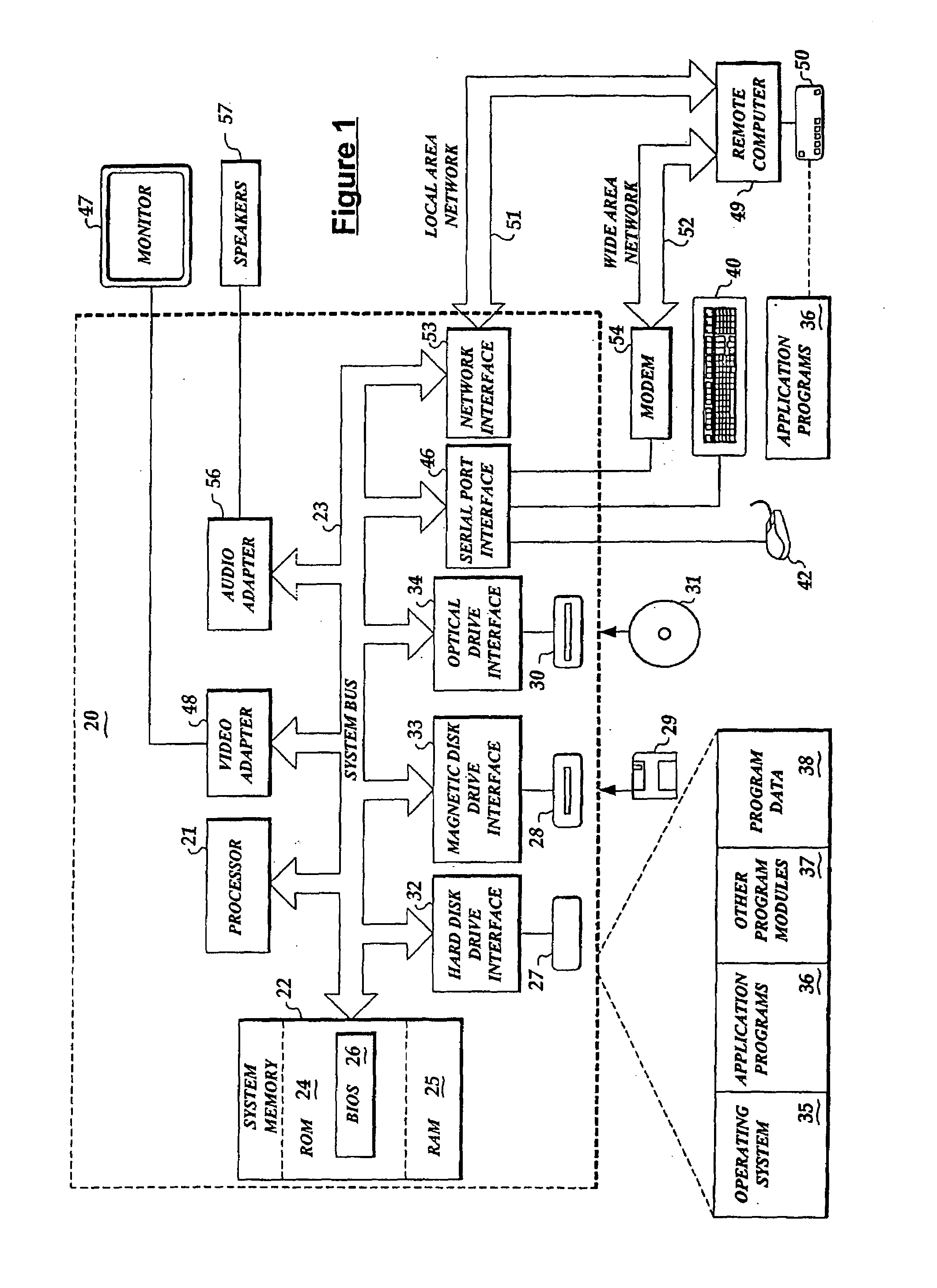

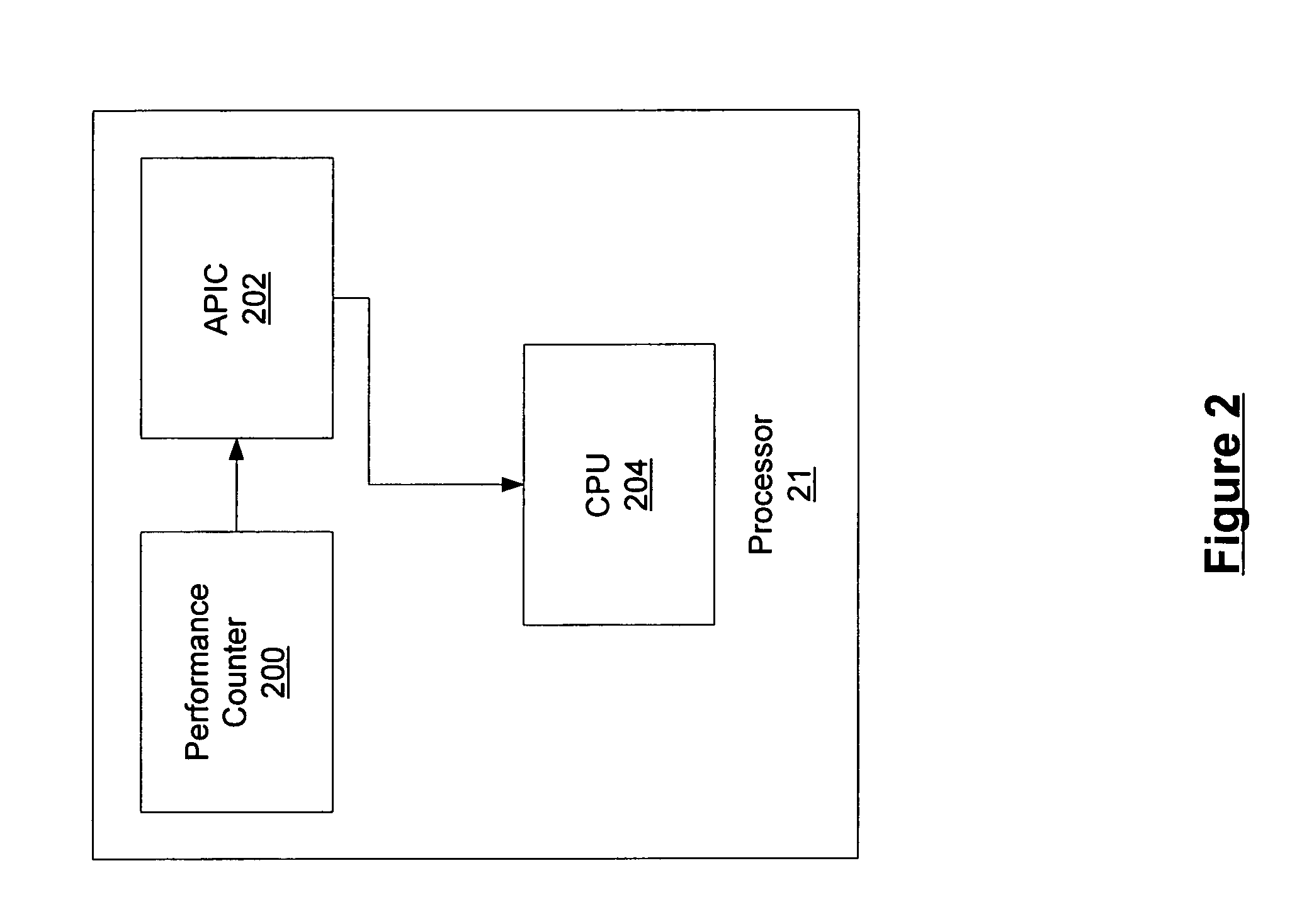

Real-time scheduler

InactiveUS6957432B2Facilitates real-time schedulingSpeed of execution of operatingProgram initiation/switchingResource allocationTime scheduleNon real time

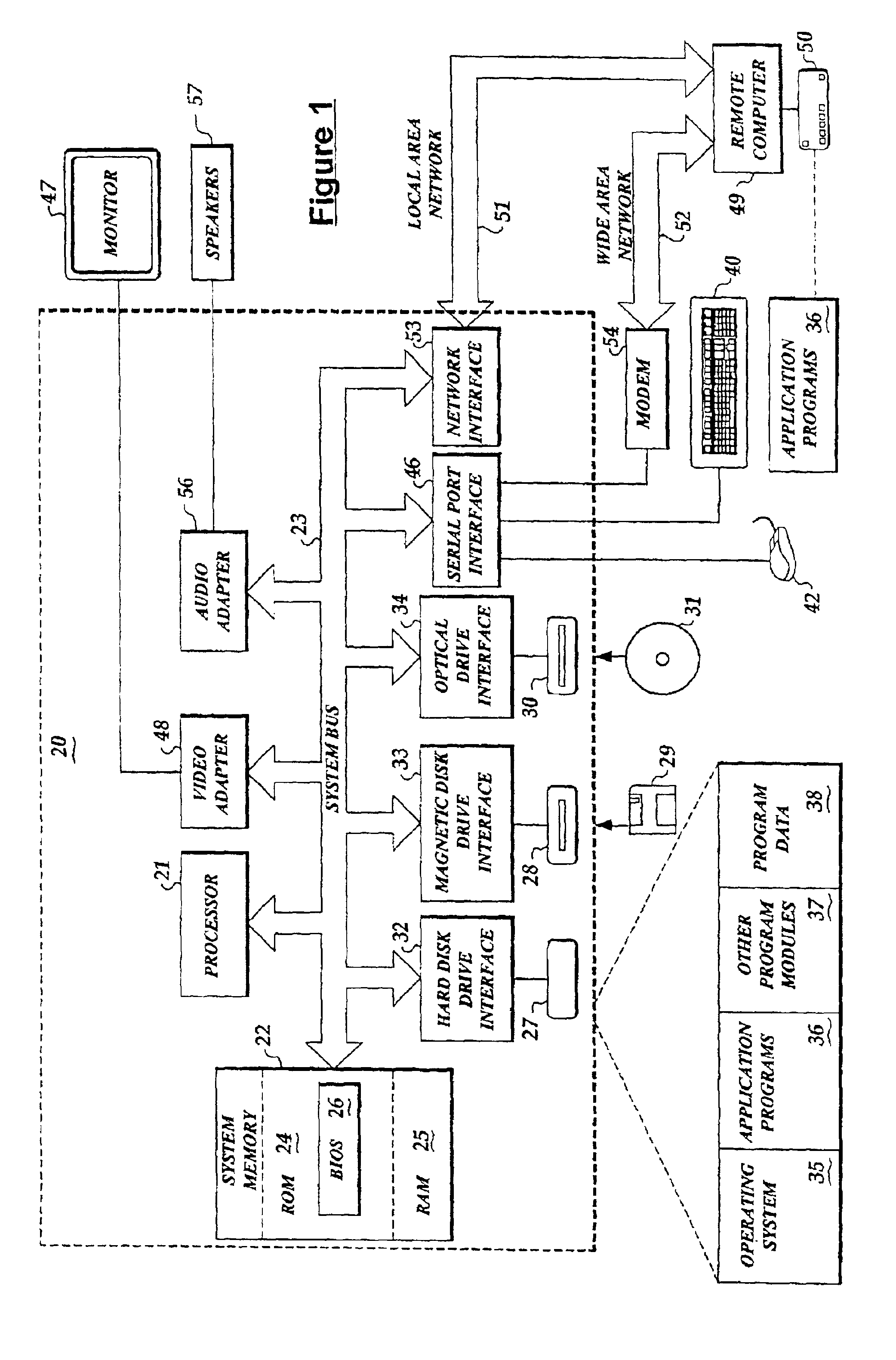

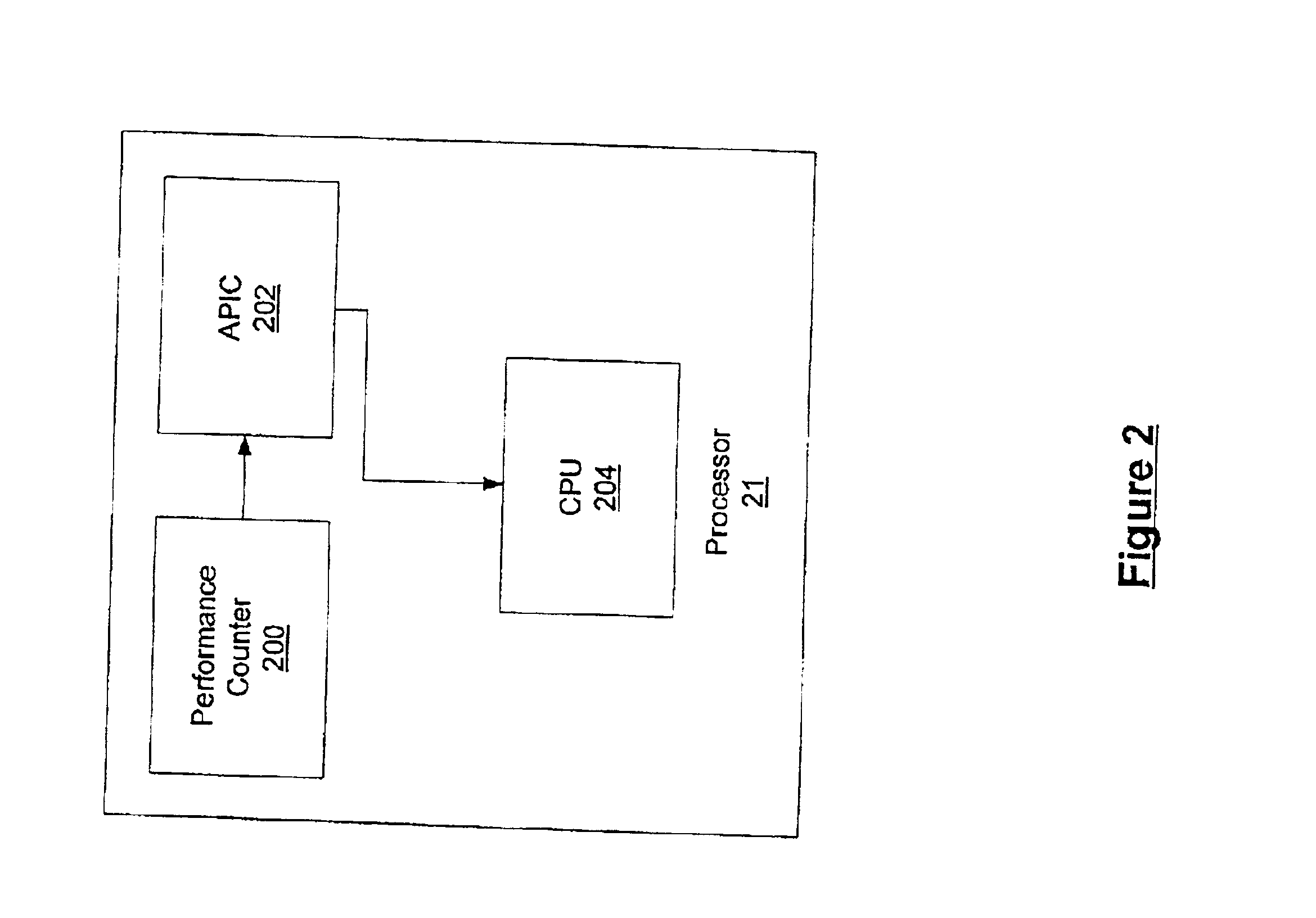

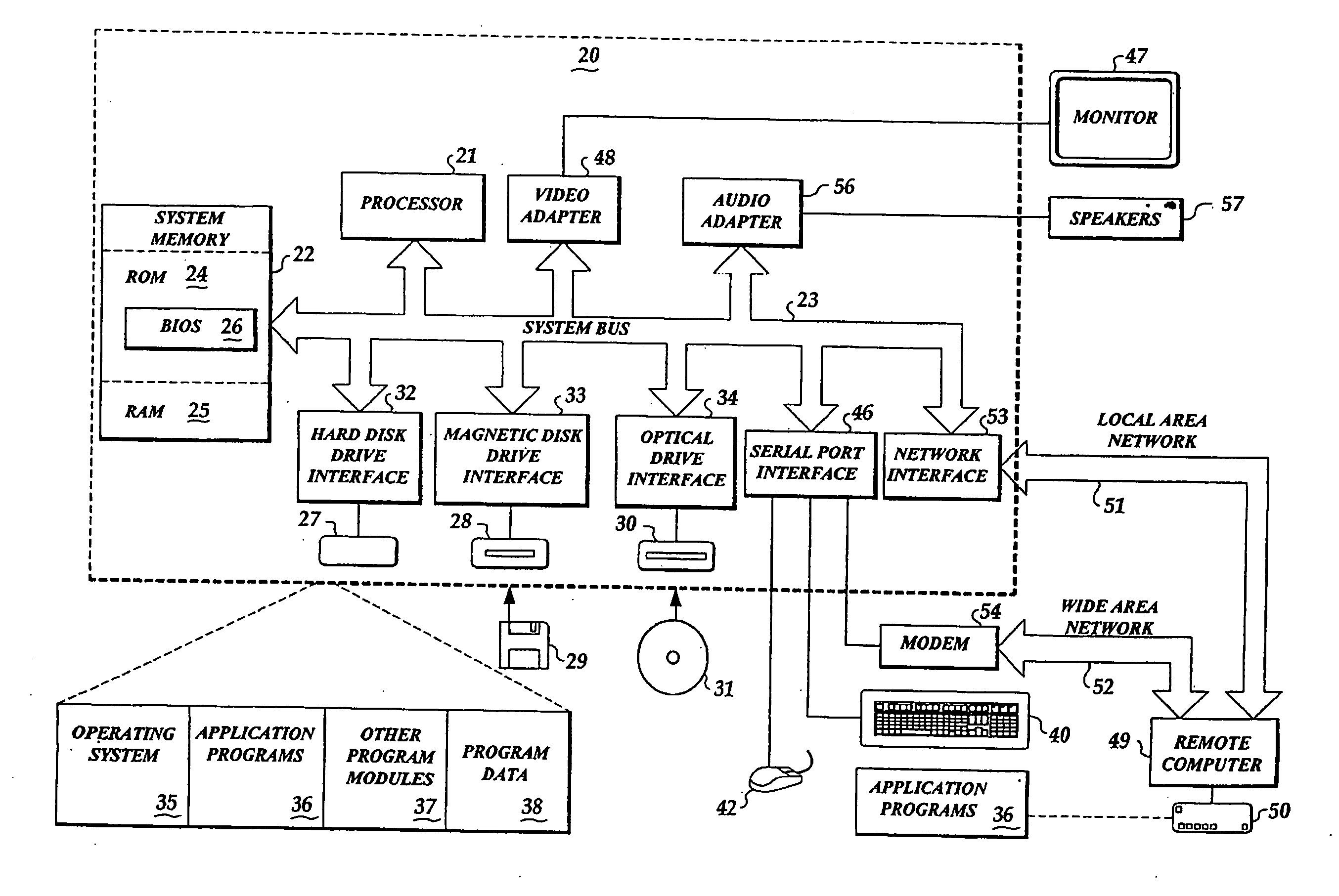

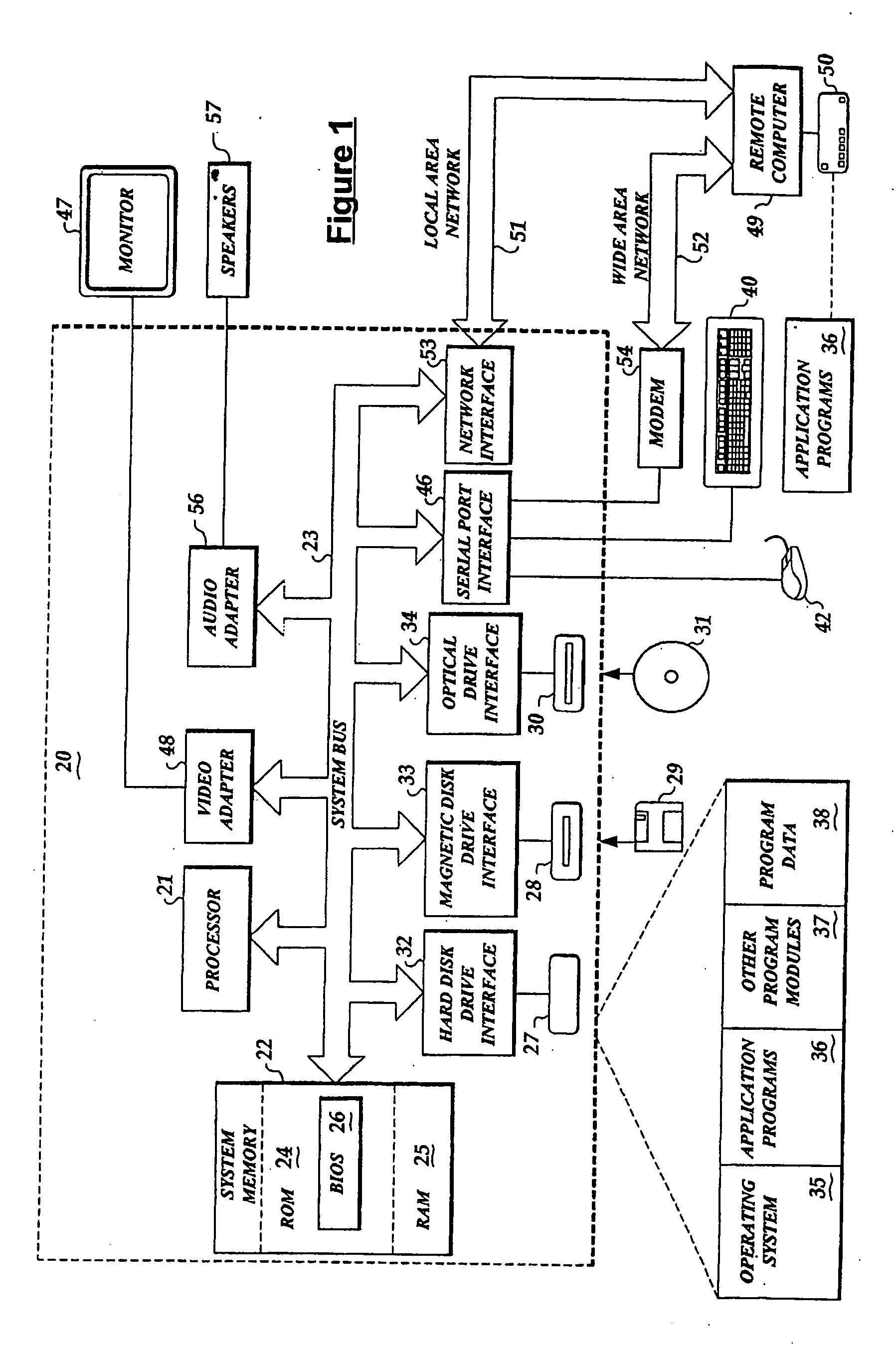

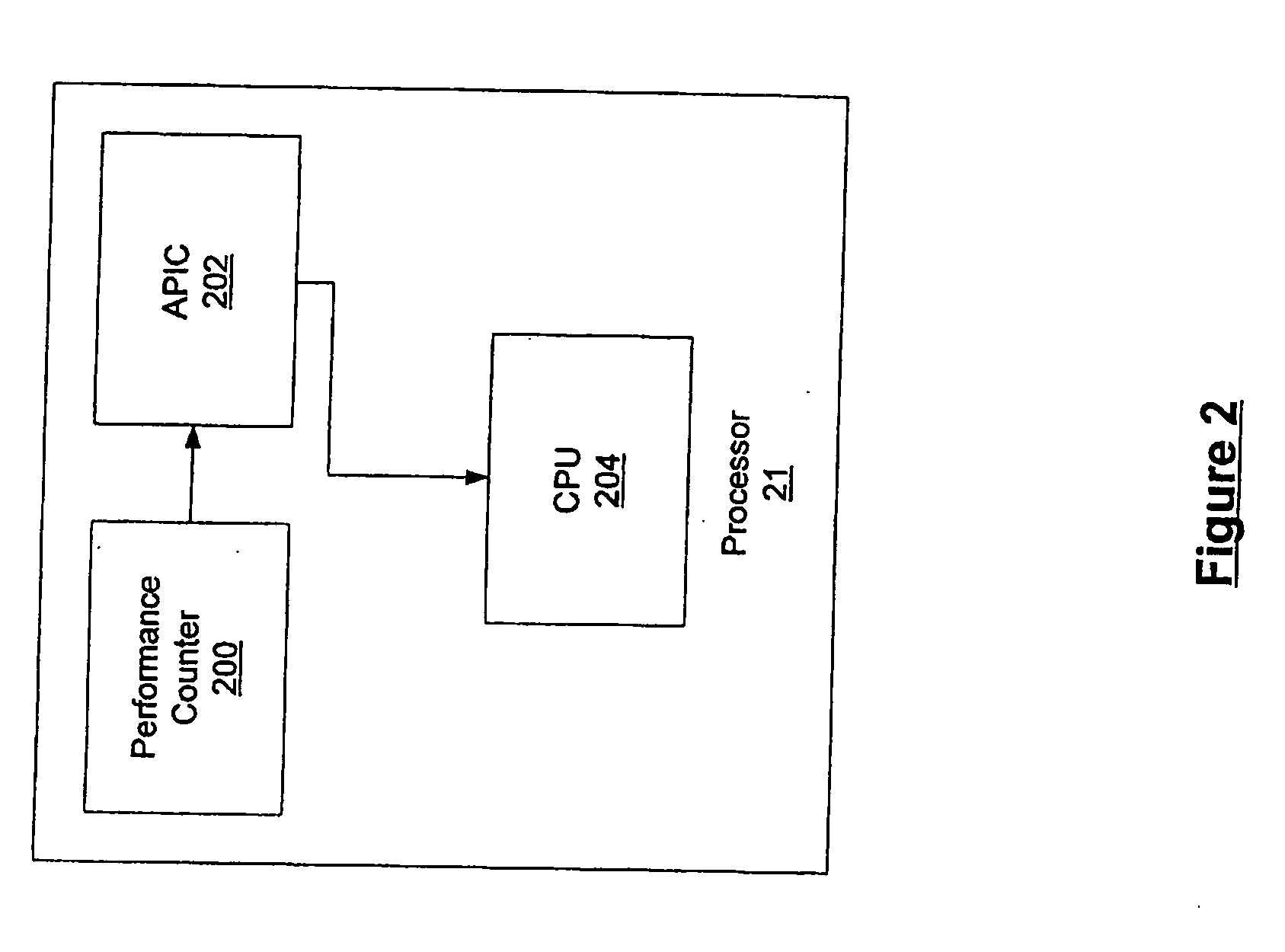

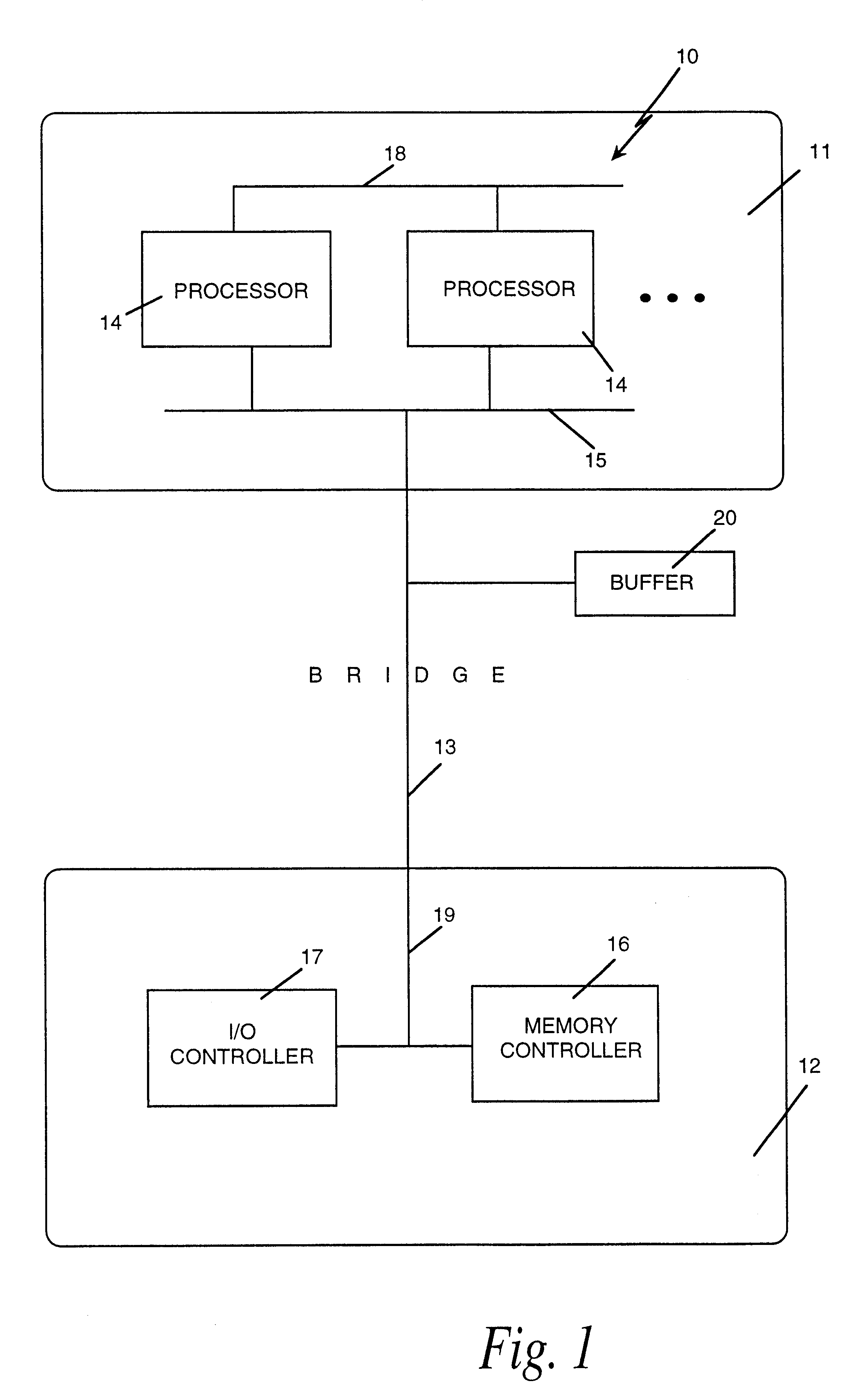

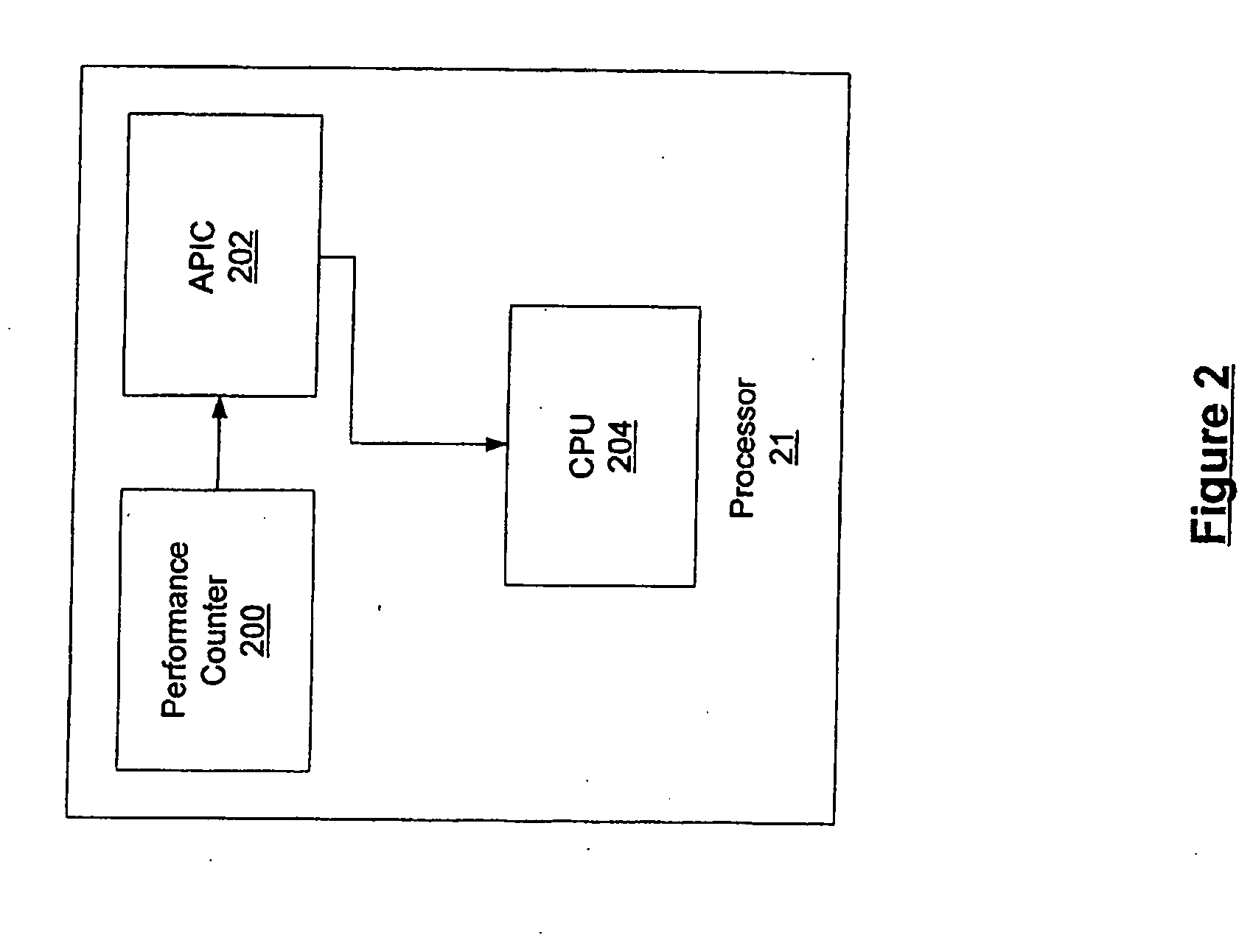

Methods and computer-executable components for real-time scheduling of CPU resources are disclosed. A performance counter determines when to allocate CPU resources to a thread. When it is time to allocate the CPU resources, the performance counter issues a maskable or non-maskable interrupt to an advanced programmable interrupt controller (APIC). The APIC then issues a maskable non-maskable interrupt to the CPU. In response to receiving the non-maskable interrupt, the CPU allocates resources to the thread. In addition, the disclosed methods and computer-executable components also: (a) allow scheduling of CPU resources such that real-time threads are guaranteed respective portions of time slots, (b) enable real-time scheduling on a non-real-time operating system, and (c) provide scheduling of CPU resources on a uni-processor machine such that at least first and second real-time threads dependent on one another are synchronized.

Owner:MICROSOFT TECH LICENSING LLC

Method and system for real time scheduler

InactiveUS20050229179A1Facilitates real-time schedulingSpeed of execution of operatingProgram initiation/switchingResource allocationTime scheduleNon-maskable interrupt

Methods and computer-executable components for real-time scheduling of CPU resources are disclosed. A performance counter determines when to allocate CPU resources to a thread. When it is time to allocate the CPU resources, the performance counter issues a maskable or non-maskable interrupt to an advanced programmable interrupt controller (APIC). The APIC then issues a maskable non-maskable interrupt to the CPU. In response to receiving the non-maskable interrupt, the CPU allocates resources to the thread. In addition, the disclosed methods and computer-executable components also: (a) allow scheduling of CPU resources such that real-time threads are guaranteed respective portions of time slots, (b) enable real-time scheduling on a non-real-time operating system, and (c) provide scheduling of CPU resources on a uni-processor machine such that at least first and second real-time threads dependent on one another are synchronized.

Owner:MICROSOFT TECH LICENSING LLC

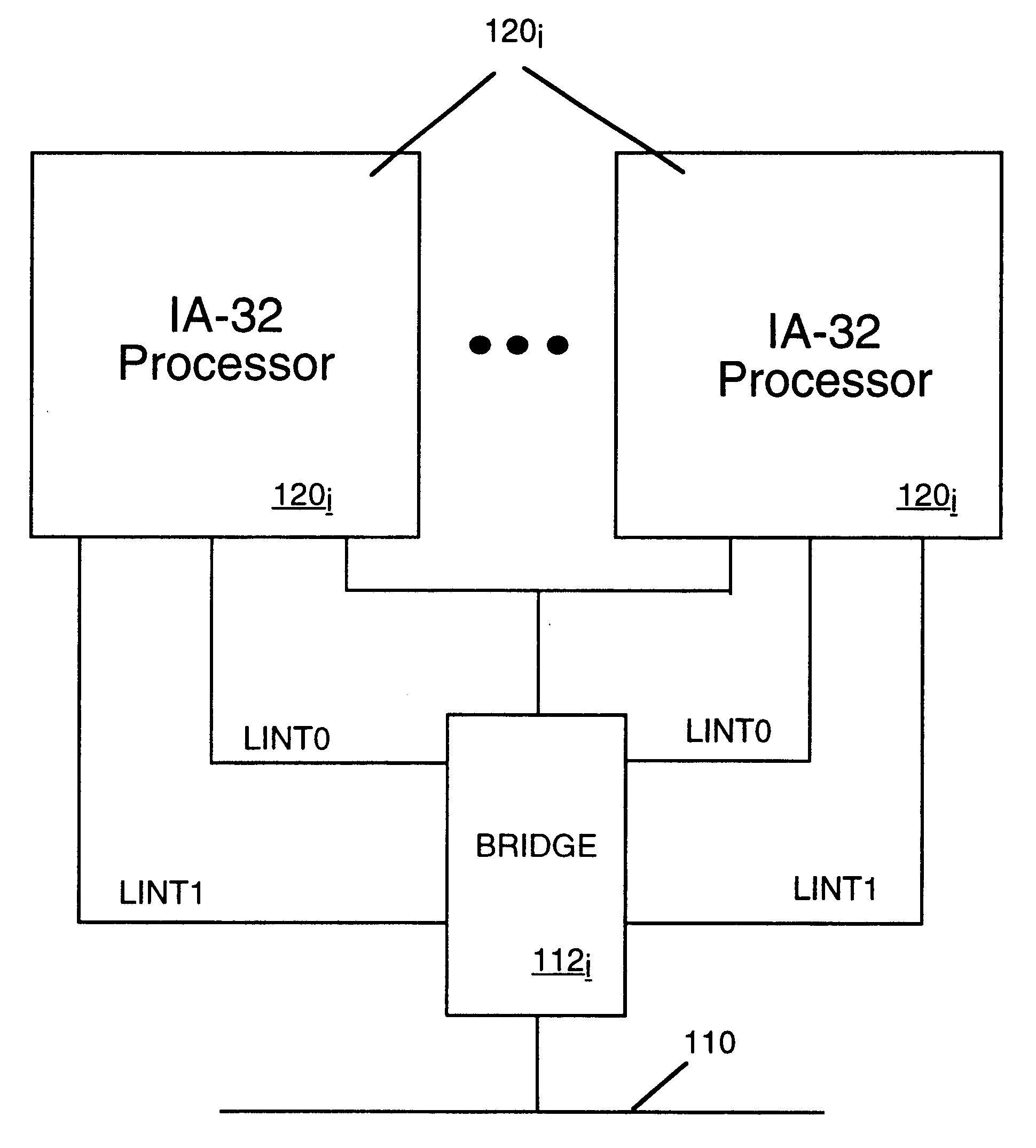

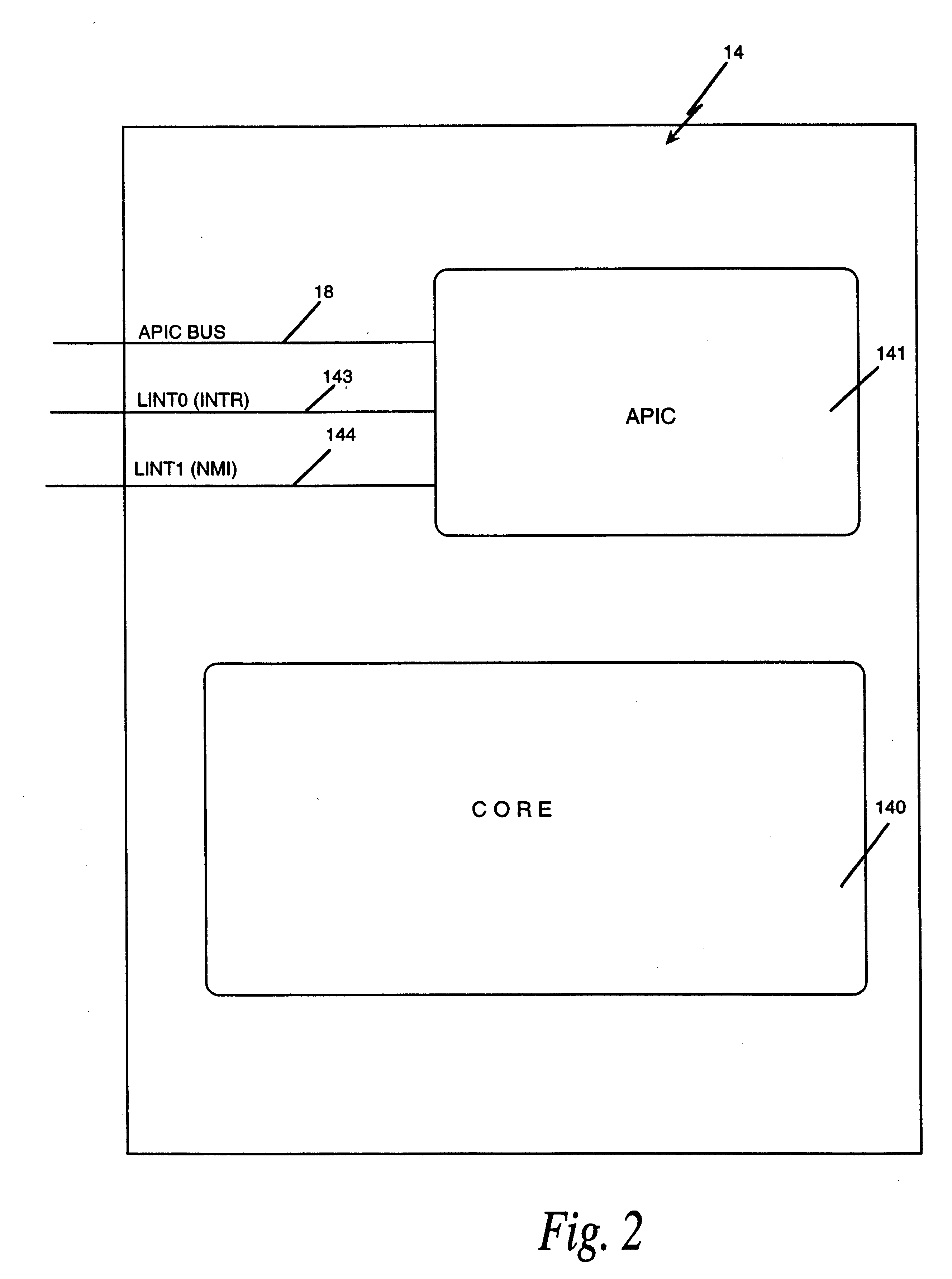

Apparatus and method for converting interrupt transactions to interrupt signals to distribute interrupts to IA-32 processors

An apparatus and method for distributing interrupts to Intel(R) Architecture (IA)-32 processors includes a system bus having a number of nodes. Each node includes a bridge that couples the system bus to a processor bus. The processor bus may include multiple IA-32 processors. The system bus may include any number of nodes. Interrupt transactions appearing on the system bus are converted by the bridge to interrupt signals. The bridge asserts the interrupt signals at one of two pins on a target IA-32 processor. One pin may be programmed to receive non-maskable interrupts and the other pin may be programmed to receive external interrupts. The bridge incorporates a priority and threshold mechanism. The bridge includes a buffer to store pending interrupt signals. The apparatus and method may be used in a mixed IA-32 and IA-64 computer architecture that uses IA-64 components to receive interrupts and uses the bridge to convert the transactions on an IA-64 bus into interrupt signal assertions to an IA-32 processor.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Method and system for realtime scheduler

InactiveUS6990665B2Facilitates real-time schedulingSpeed of execution of operatingProgram initiation/switchingResource allocationTime scheduleNon real time

Methods and computer-executable components for real-time scheduling of CPU resources are disclosed. A performance counter determines when to allocate CPU resources to a thread. When it is time to allocate the CPU resources, the performance counter issues a maskable or non-maskable interrupt to an advanced programmable interrupt controller (APIC). The APIC then issues a maskable non-maskable interrupt to the CPU. In response to receiving the non-maskable interrupt, the CPU allocates resources to the thread. In addition, the disclosed methods and computer-executable components also: (a) allow scheduling of CPU resources such that real-time threads are guaranteed respective portions of time slots, (b) enable real-time scheduling on a non-real-time operating system, and (c) provide scheduling of CPU resources on a uni-processor machine such that at least first and second real-time threads dependent on one another are synchronized.

Owner:MICROSOFT TECH LICENSING LLC

Method and system for real time scheduler

InactiveUS20050229178A1Facilitates real-time schedulingSpeed of execution of operatingProgram initiation/switchingResource allocationTime scheduleNon-maskable interrupt

Methods and computer-executable components for real-time scheduling of CPU resources are disclosed. A performance counter determines when to allocate CPU resources to a thread. When it is time to allocate the CPU resources, the performance counter issues a maskable or non-maskable interrupt to an advanced programmable interrupt controller (APIC). The APIC then issues a maskable non-maskable interrupt to the CPU. In response to receiving the non-maskable interrupt, the CPU allocates resources to the thread. In addition, the disclosed methods and computer-executable components also: (a) allow scheduling of CPU resources such that real-time threads are guaranteed respective portions of time slots, (b) enable real-time scheduling on a non-real-time operating system, and (c) provide scheduling of CPU resources on a uni-processor machine such that at least first and second real-time threads dependent on one another are synchronized.

Owner:MICROSOFT TECH LICENSING LLC

Computing system being able to quickly switch between an internal and an external networks and a method thereof

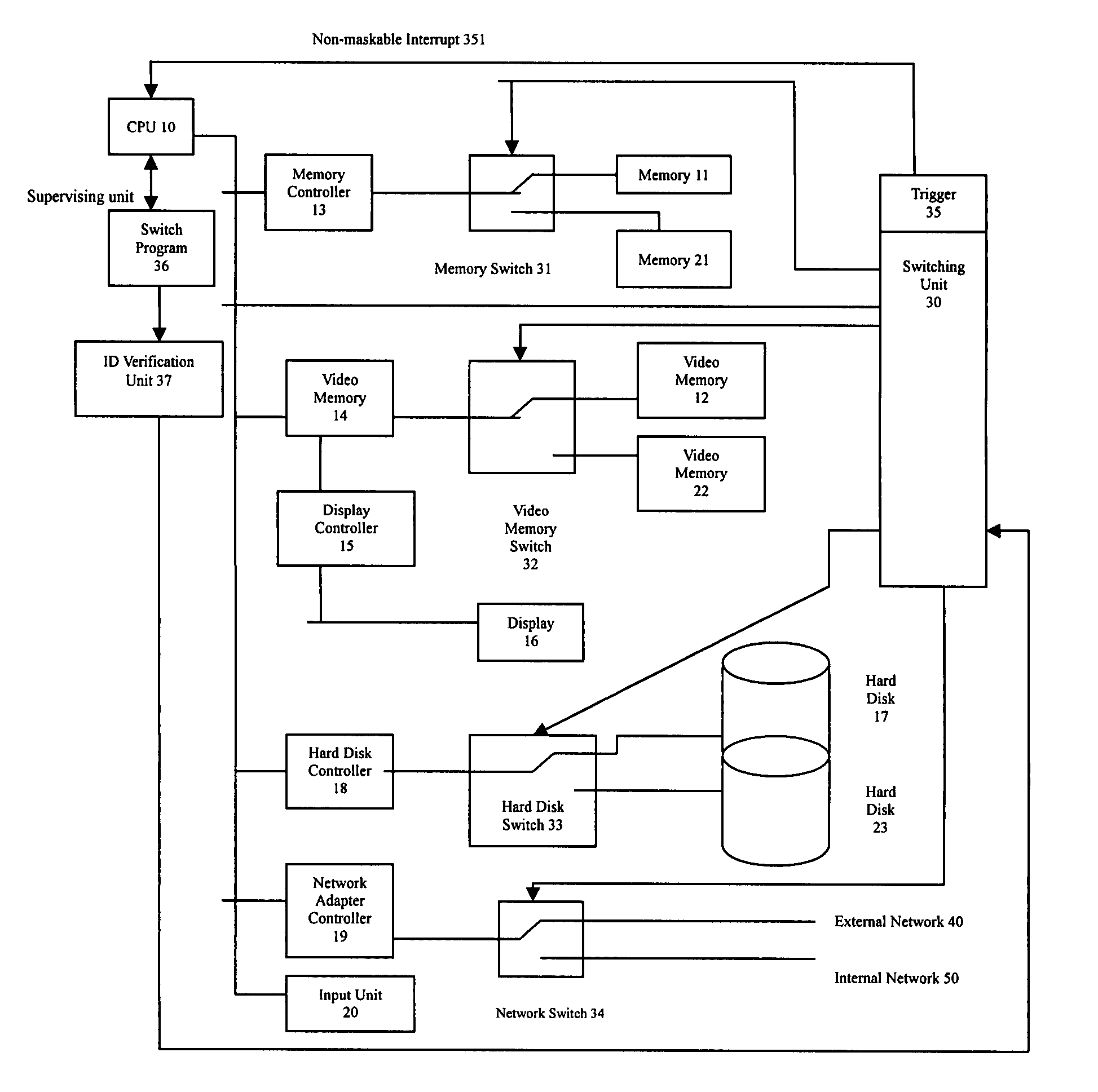

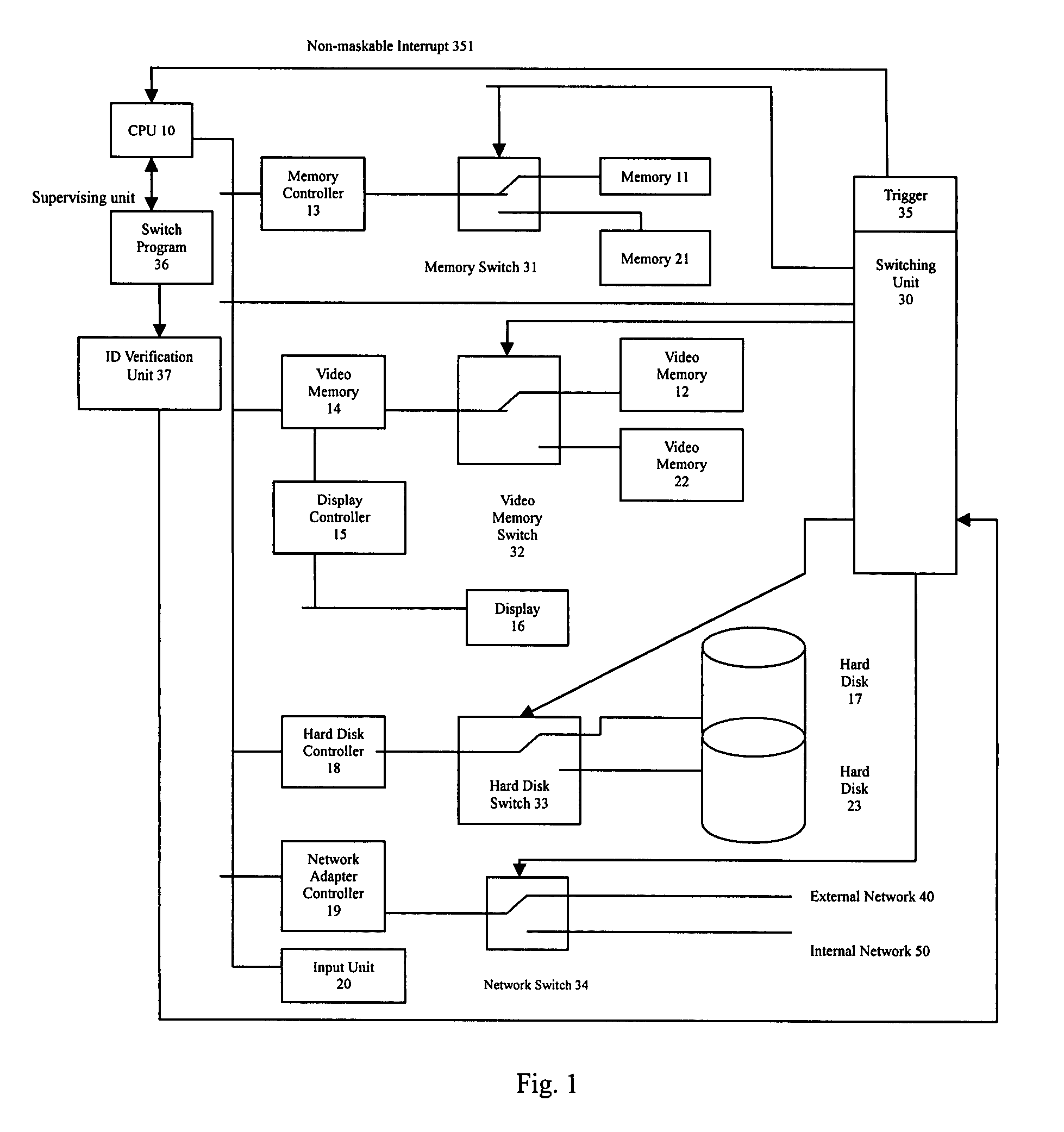

InactiveUS7370193B2Ensure physical separationQuick switchAnalogue secracy/subscription systemsData resettingNon-maskable interruptUser input

The invention discloses a computing system such as a computer, a Personal Digital Assistant, or a mobile phone, being connected both to an internal network and an external network and being able to quickly and safely switch therebetween without being shut down while ensuring a physical separation between the two networks. When a user inputs a request of switching, a switching unit will set a trigger thereof and generate a consequent non-maskable interrupt to CPU. After receives the NMI, the CPU controls the switching unit to run a switch program kept therein to back up a current status of the system. Then the switch program backs up a current status, controls the switching unit to interrupt all serving programs and loads the other status other than the current status to the computing system, and finally control the switching unit to reset the trigger.

Owner:SHAO TONG

Debugging method based on diagnosis of CPU (central processing unit) non-maskable interrupt system problems

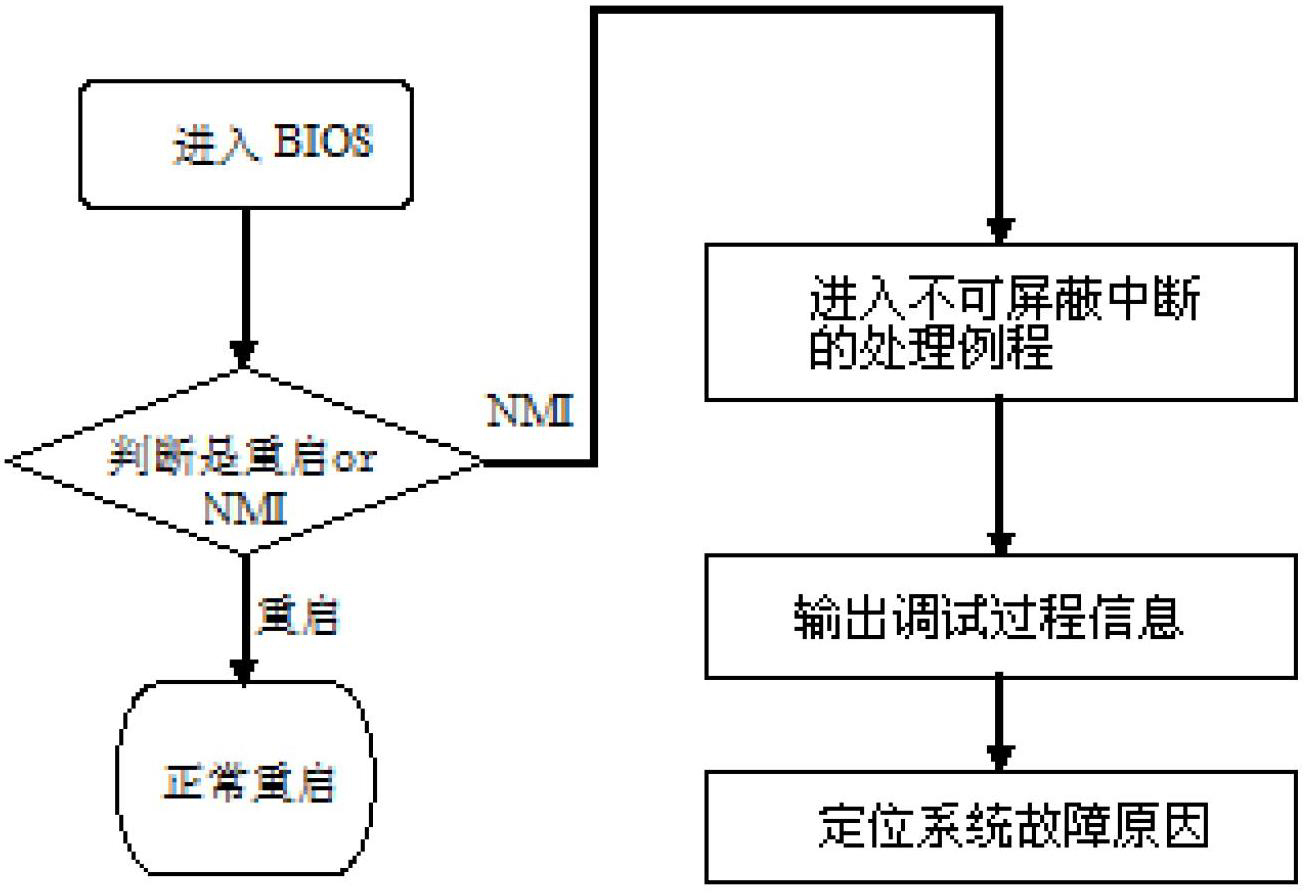

The invention discloses a debugging method based on diagnosis of CPU (central processing unit) non-maskable interrupt system problems, and the debugging method is a debugging method for diagnosis of system problems. The method comprises the following steps: step (1) of entering a basic input-output system; step (2) of judging whether a current state of a computer is restart or non-maskable interrupt; if the current of the computer is restart, carrying out starting by the basic input-output system and loading a kernel start system; if the current state of the computer is the non-maskable interrupt, adding a processing routine for the non-maskable interrupt in the basic input-output system; step (3) of entering processing routine for non-maskable interrupt; step (4) of outputting debugging process information; and step (5) of locating system fault causes. Due to execution of the method, fault clues in a system interrupt process are shown, and users can clear faults conveniently.

Owner:JIANGSU LEMOTE TECH CORP

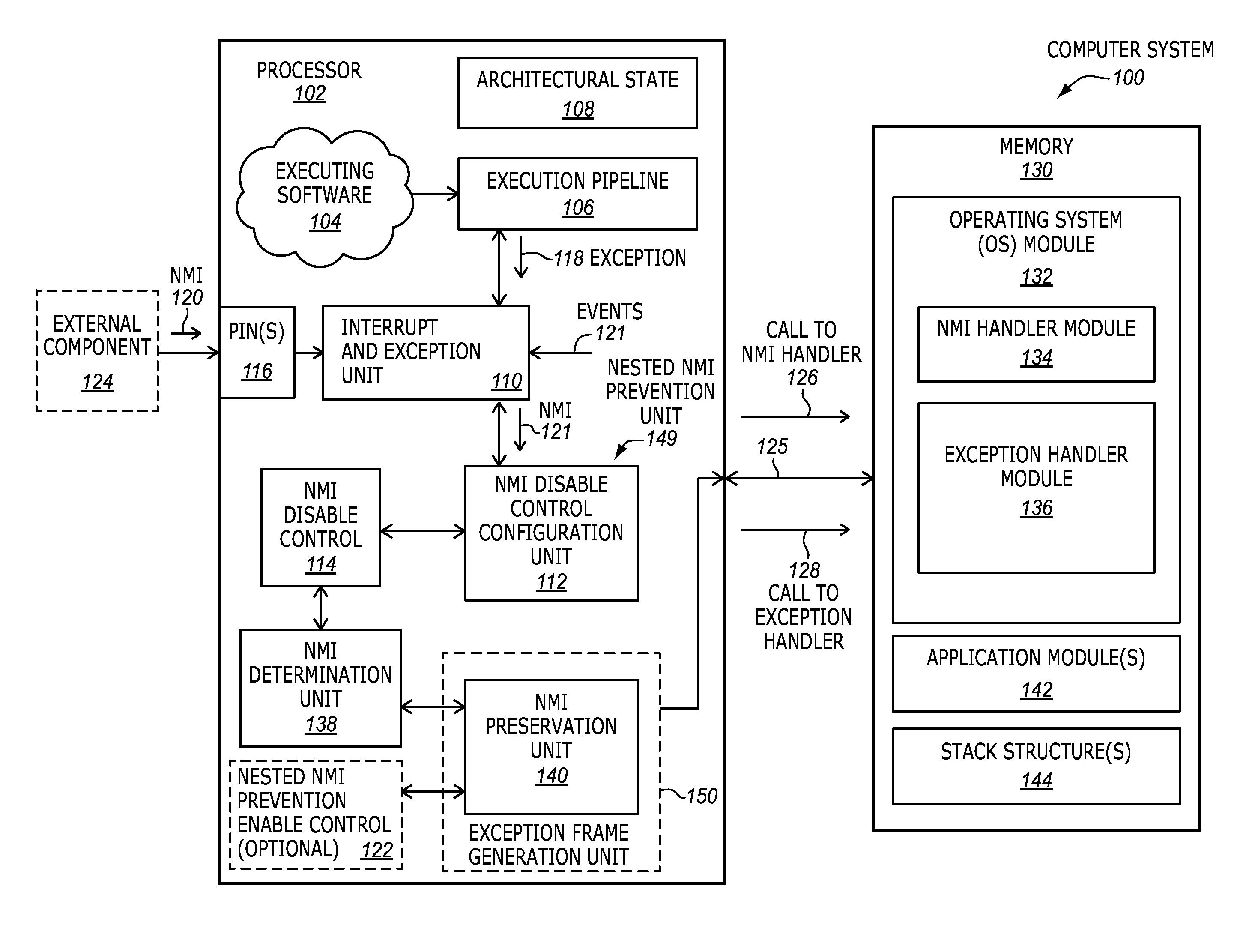

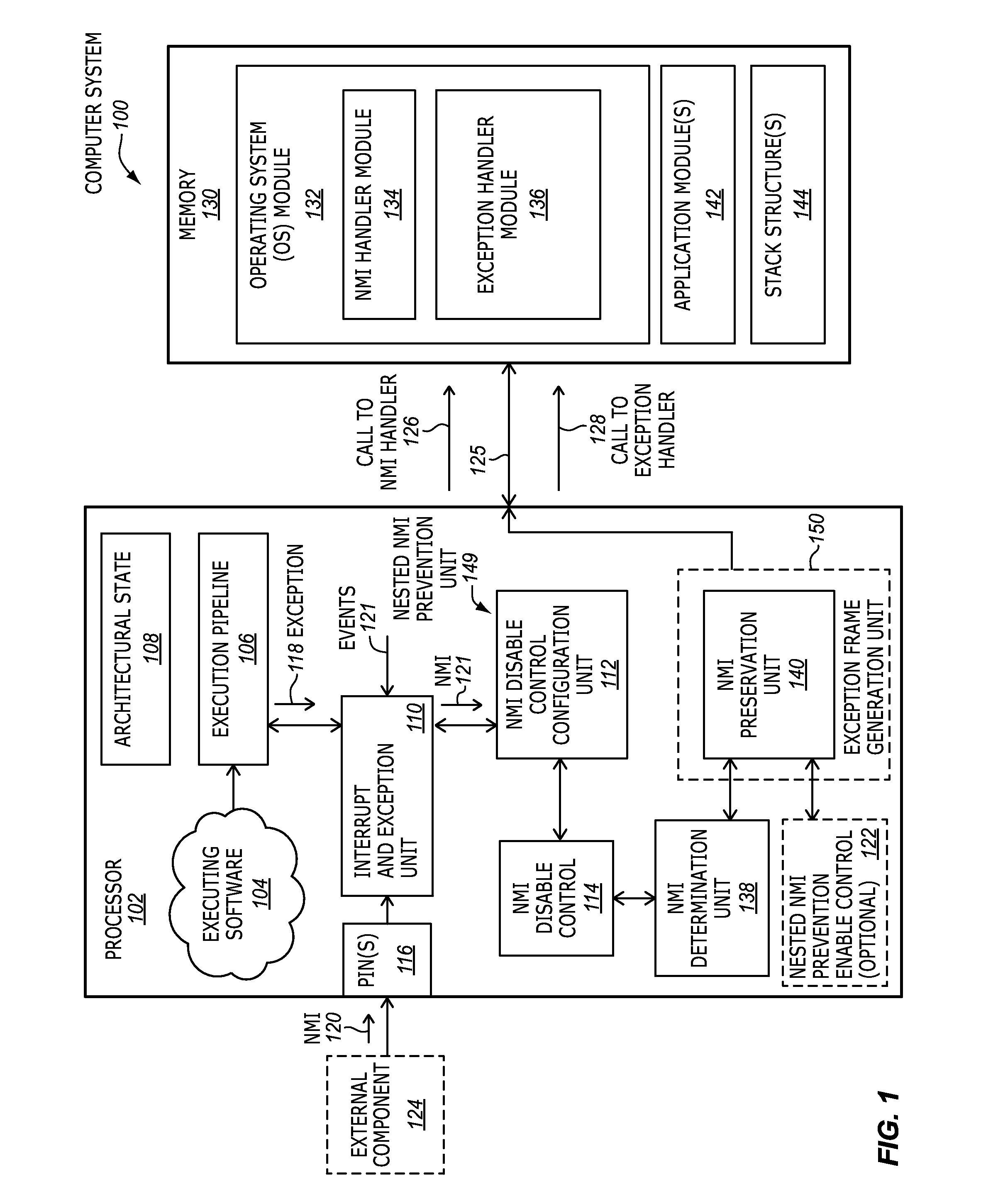

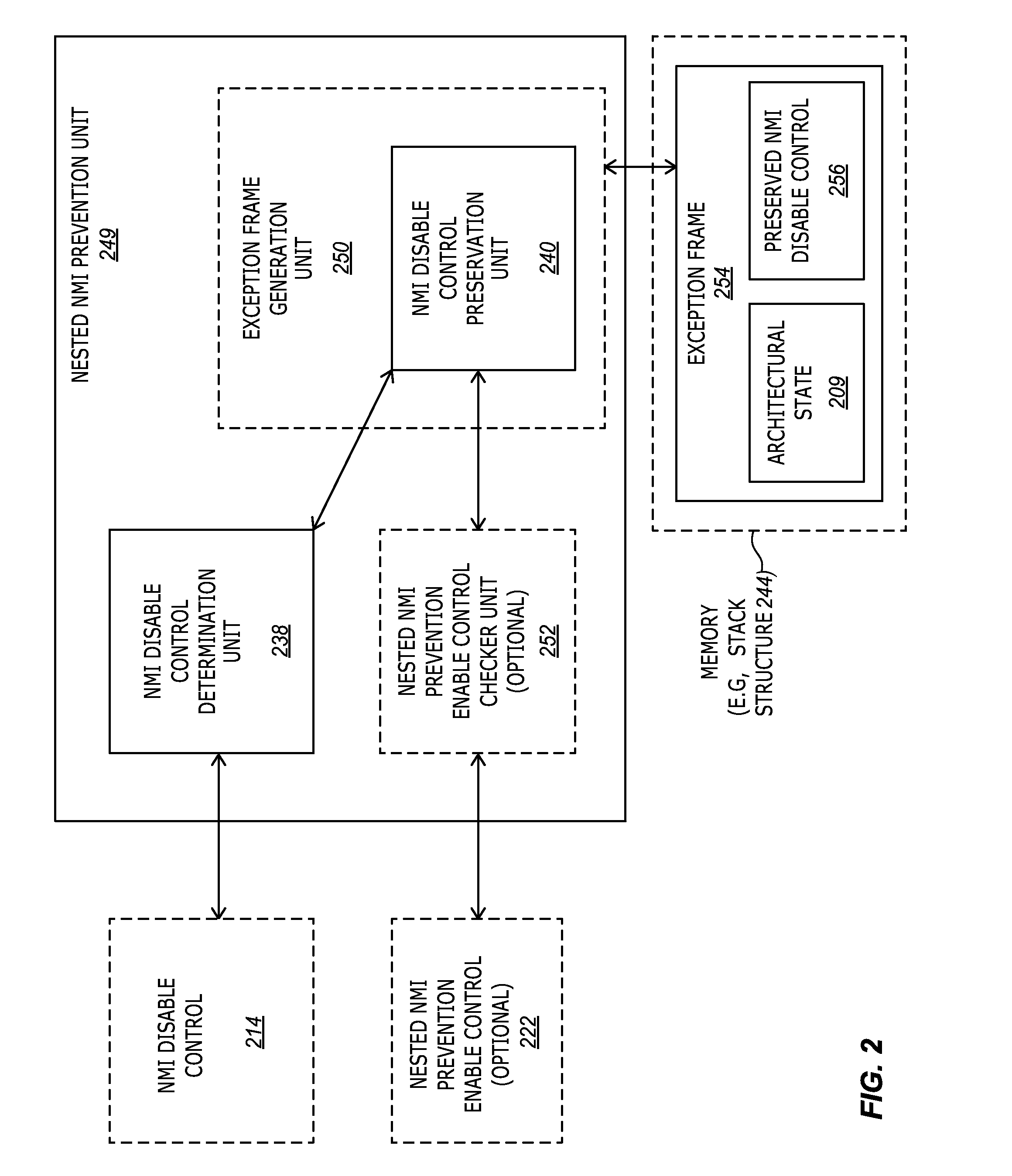

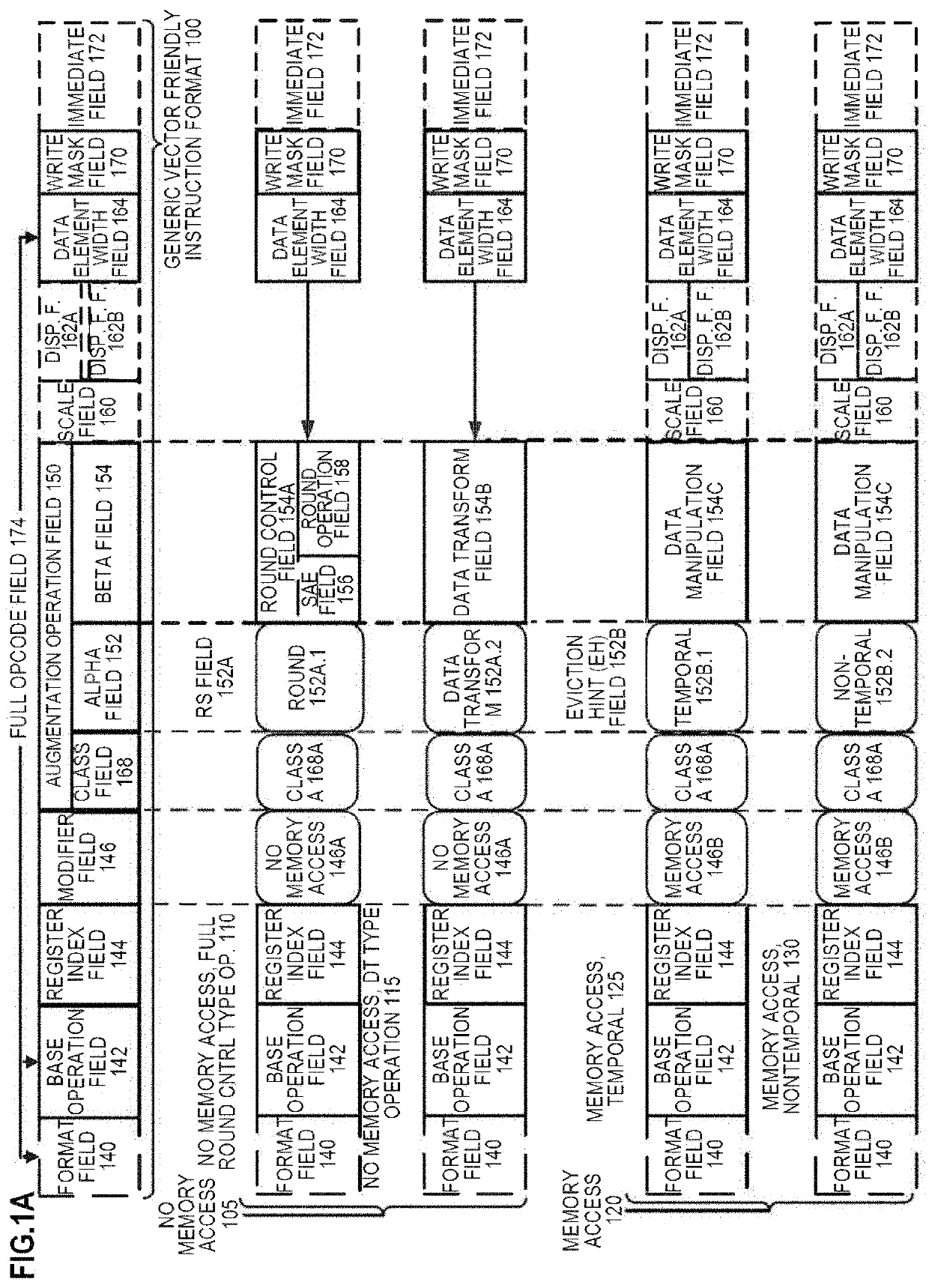

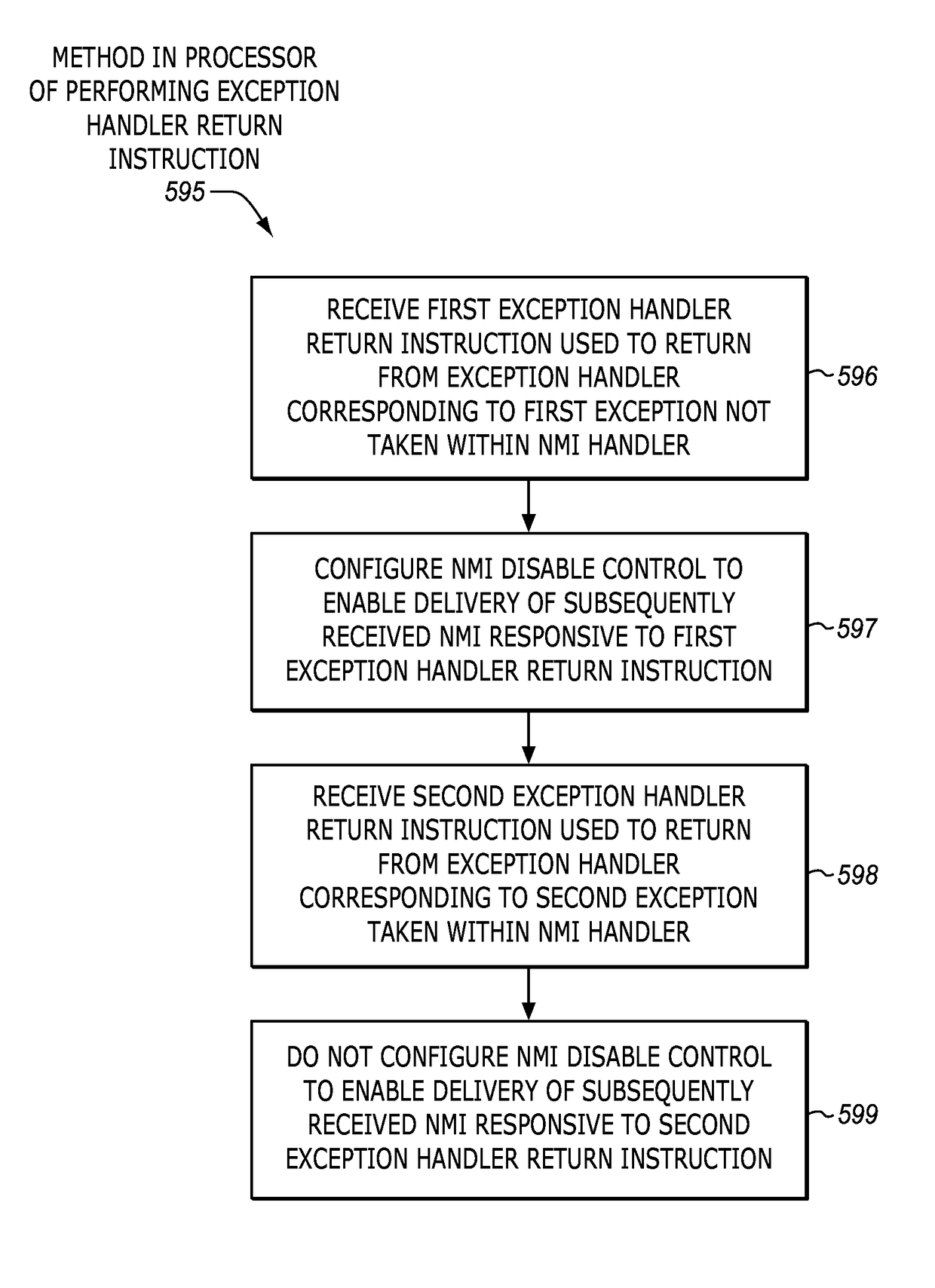

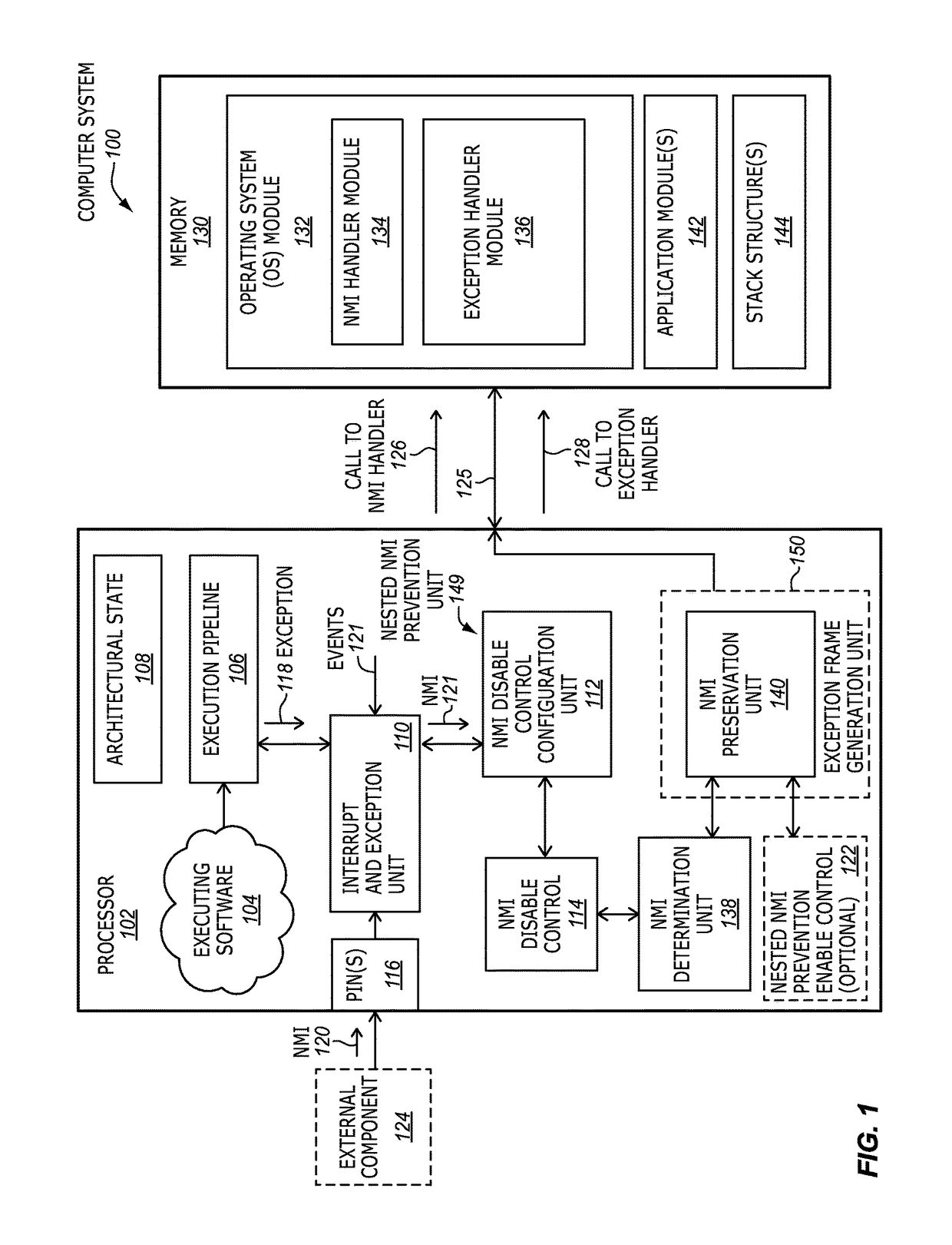

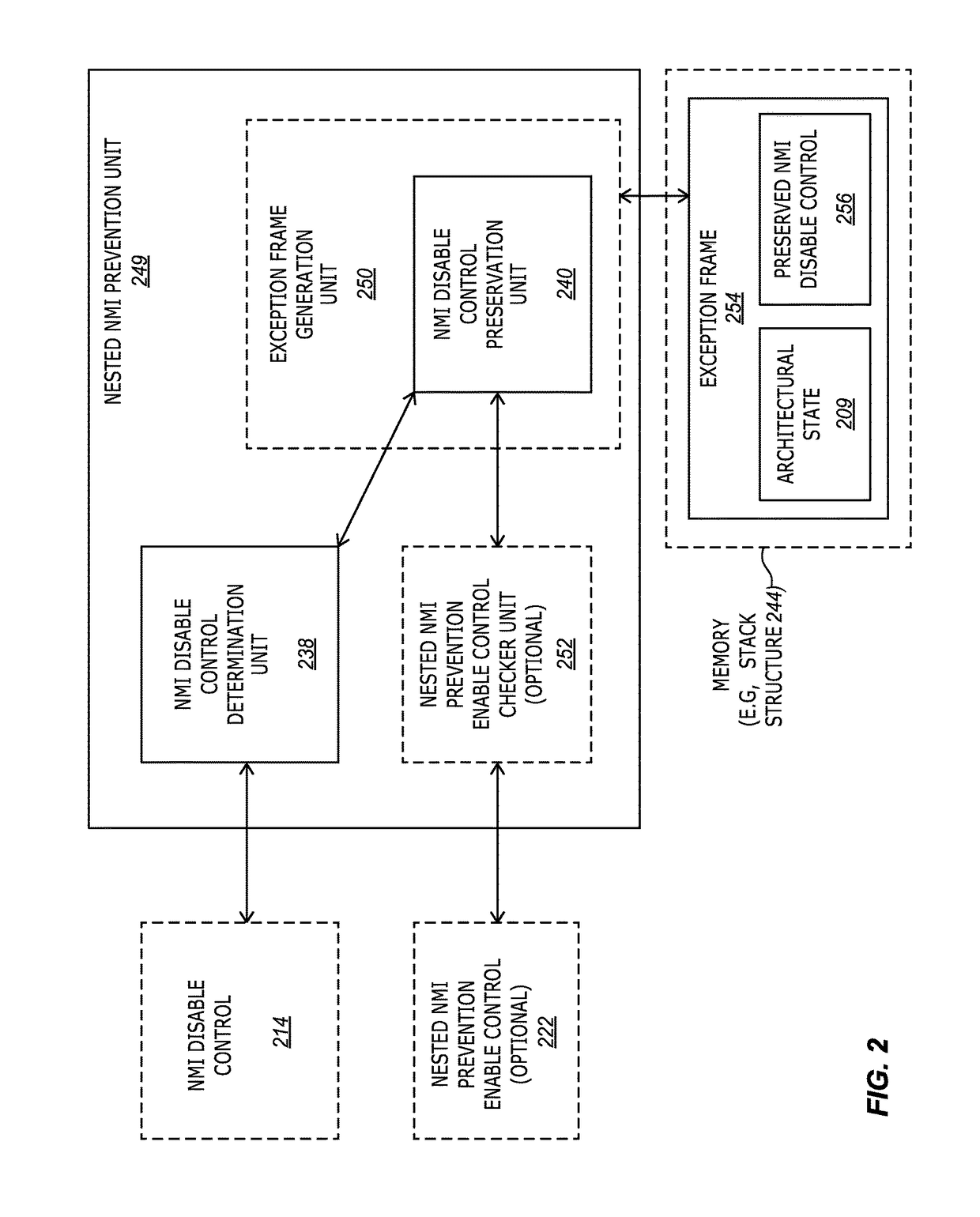

Avoiding premature enabling of nonmaskable interrupts when returning from exceptions

A processor of an aspect includes a decode unit to decode an exception handler return instruction. The processor also includes an exception handler return execution unit coupled with the decode unit. The exception handler return execution unit, responsive to the exception handler return instruction, is to not configure the processor to enable delivery of a subsequently received nonmaskable interrupt (NMI) to an NMI handler if an exception, which corresponds to the exception handler return instruction, was taken within the NMI handler. The exception handler return execution unit, responsive to the exception handler return instruction, is to configure the processor to enable the delivery of the subsequently received NMI to the NMI handler if the exception was not taken within the NMI handler. Other processors, methods, systems, and instructions are disclosed.

Owner:INTEL CORP

Real-time scheduler

InactiveUS6990669B1Facilitates real-time schedulingMultiprogramming arrangementsMemory systemsNon-maskable interruptAdvanced Programmable Interrupt Controller

Methods and computer-executable components for real-time scheduling of CPU resources are disclosed. A performance counter determines when to allocate CPU resources to a thread. When it is time to allocate the CPU resources, the performance counter issues a non-maskable interrupt to an advanced programmable interrupt controller (APIC). The APIC then issues a non-maskable interrupt to the CPU. In response to receiving the non-maskable interrupt, the CPU allocates resources to the thread.

Owner:MICROSOFT TECH LICENSING LLC

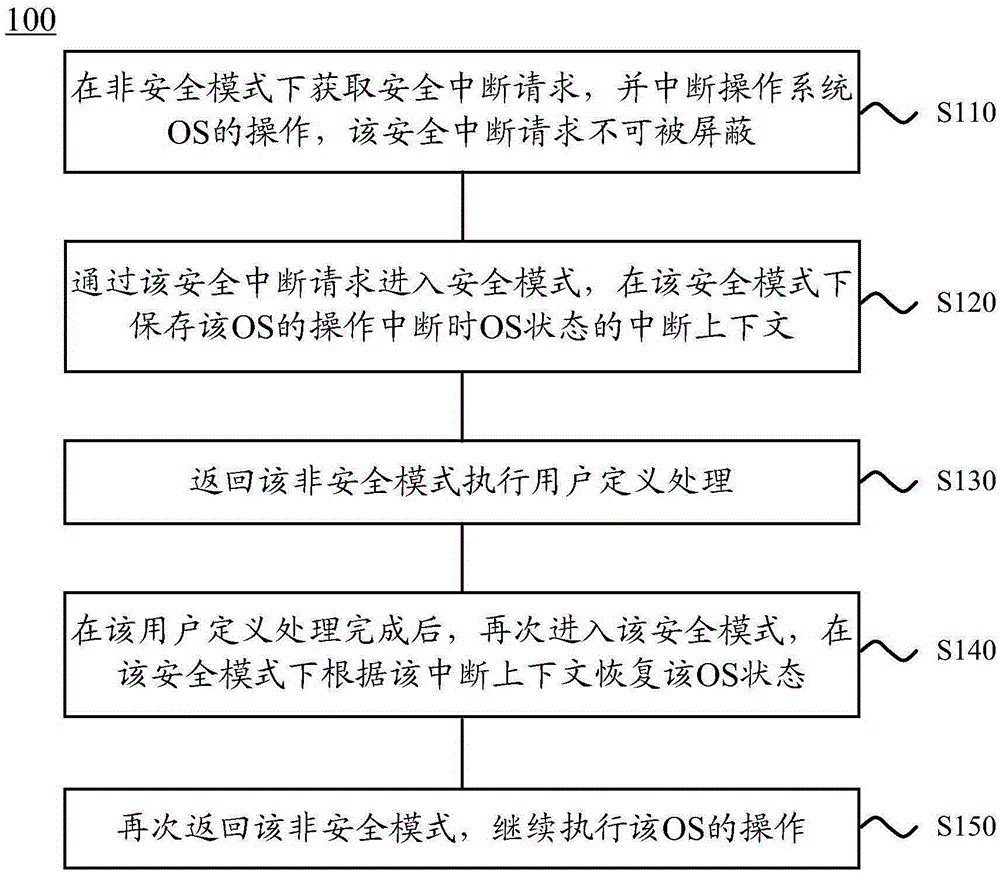

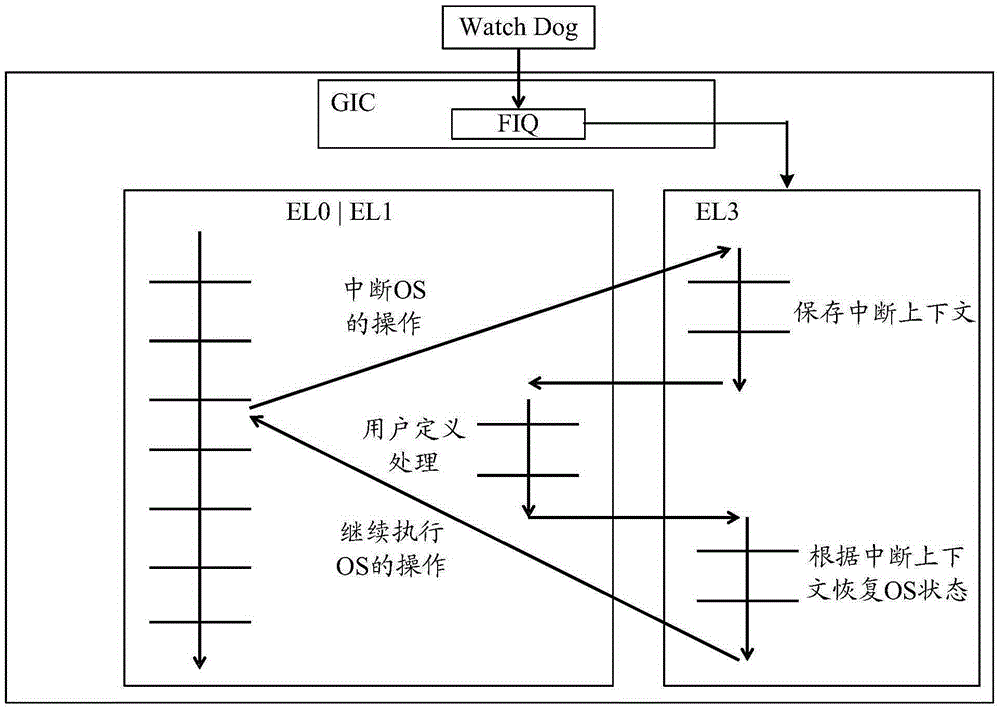

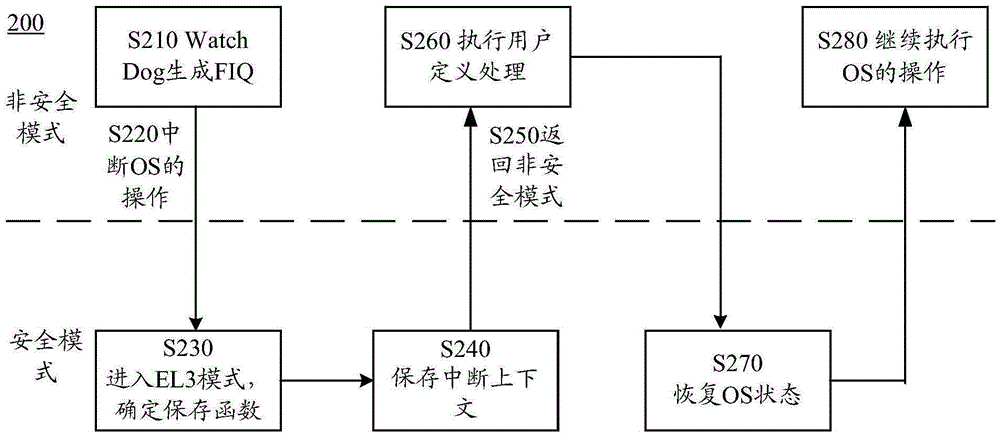

Method and device for executing non-maskable interrupt

ActiveCN105279021AImplement the NMI processProgram initiation/switchingData resettingNon-maskable interruptComputer science

The invention discloses a method and device for executing non-maskable interrupt. The method comprises the following steps: obtaining a safe interrupt request under an unsafe mode and interrupting the operation of an operating system OS, wherein the safe interrupt request is non-maskable; entering a safe mode through the safe interrupt request, and storing the interrupt context of the OS state when the operation of the OS is interrupted under the safe mode; returning to the unsafe mode to execute user defined processing; after the user defined processing is finished, entering the safe mode again and restoring the OS state according to the interrupt context under the safe mode; and returning to the unsafe mode again and continuing to execute the operation of the OS. According to the method and device for executing non-maskable interrupt, the NMI can be simply realized without hardware.

Owner:HUAWEI TECH CO LTD

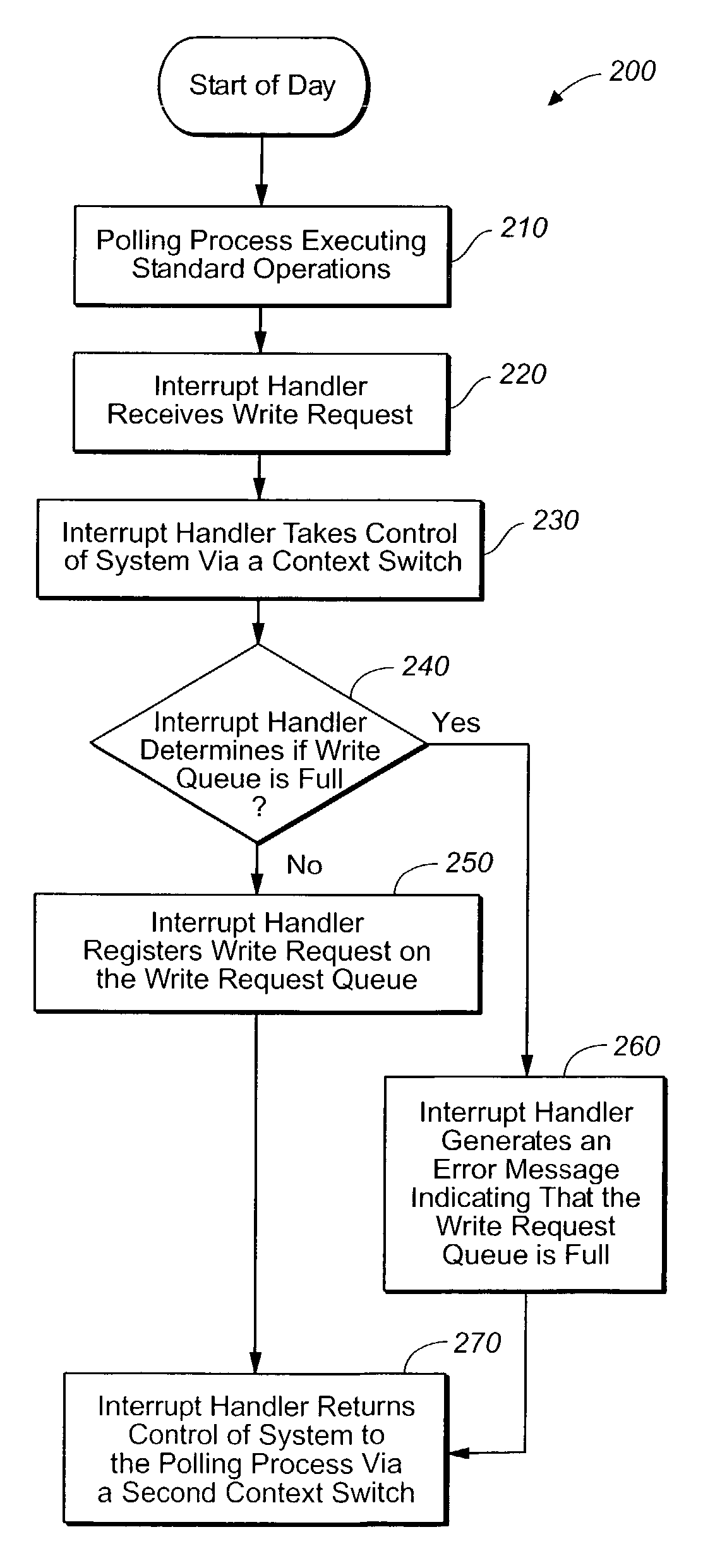

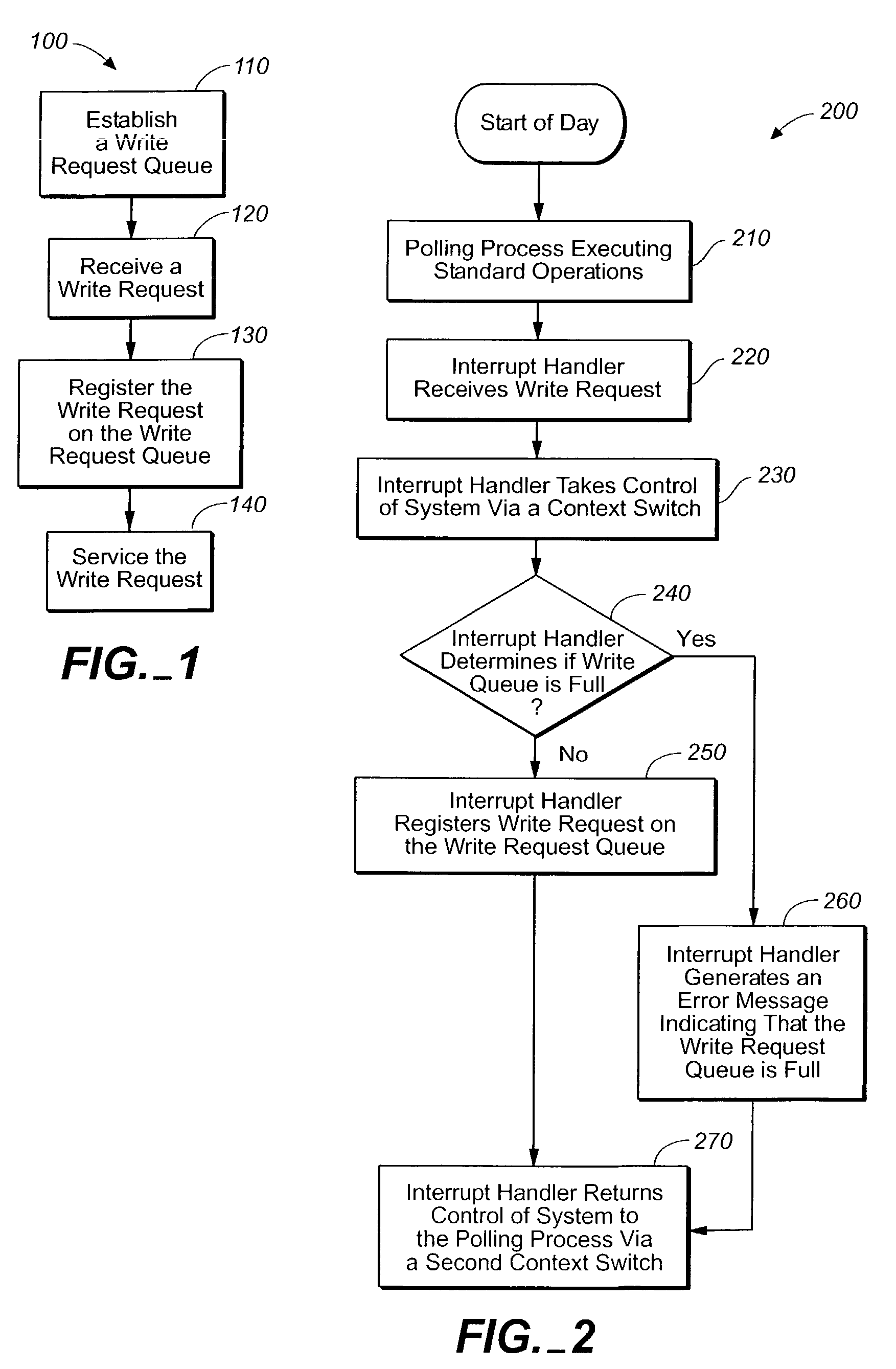

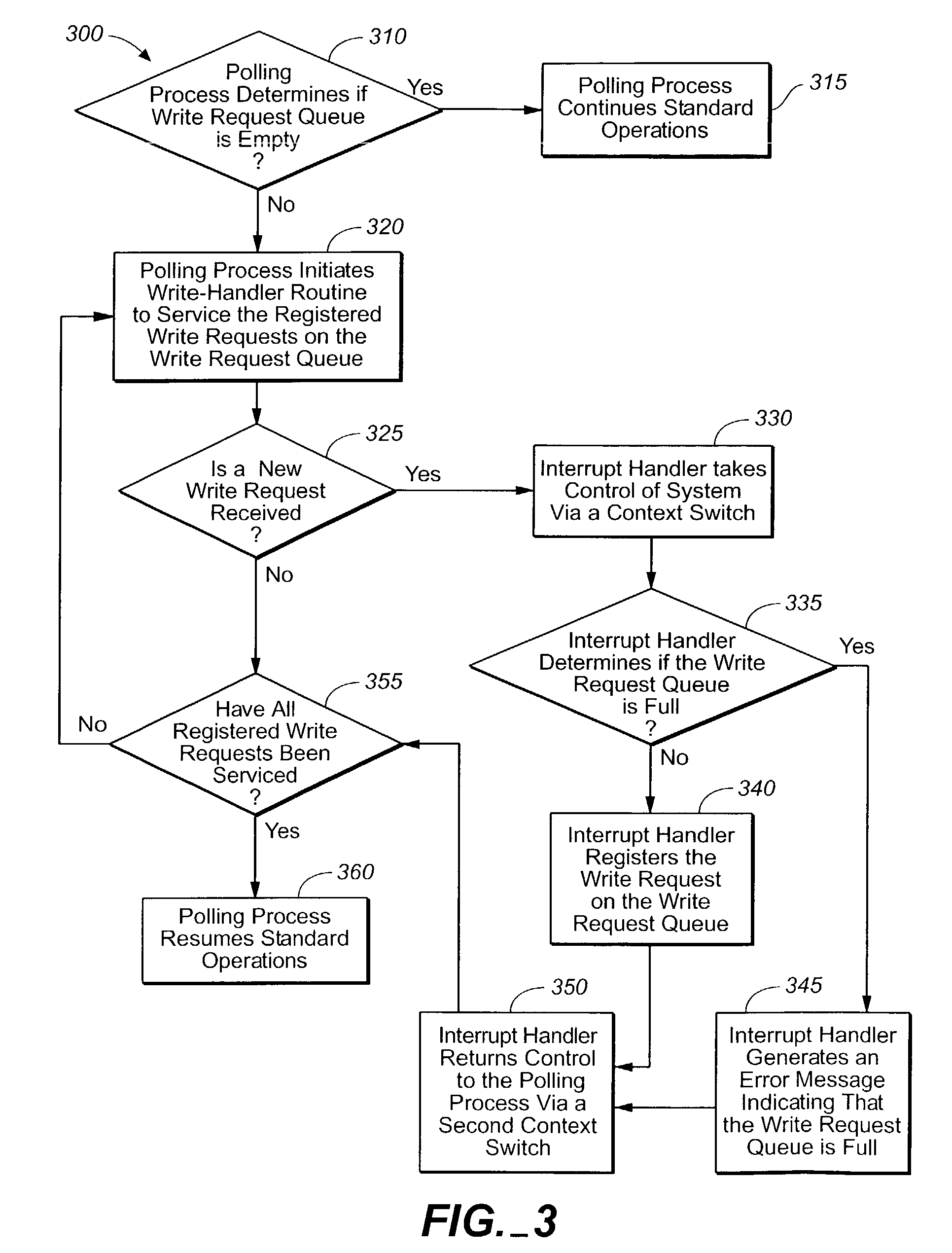

System and method for handling shared resource writes arriving via non-maskable interrupts (NMI) in single thread non-mission critical systems with limited memory space

InactiveUS7003610B2Quick serviceRule out the possibilityMultiprogramming arrangementsMemory systemsNon-maskable interruptCritical system

A system and method for handling shared resource writes arriving via non-maskable interrupts in single thread non-mission critical system with limited memory space includes a queue for providing temporary storage of a write request. The queue is accessible by lower or higher priority processes for the servicing of the write requests. Upon completion of service to the write requests the system returns control to the standard operations of the single thread system.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

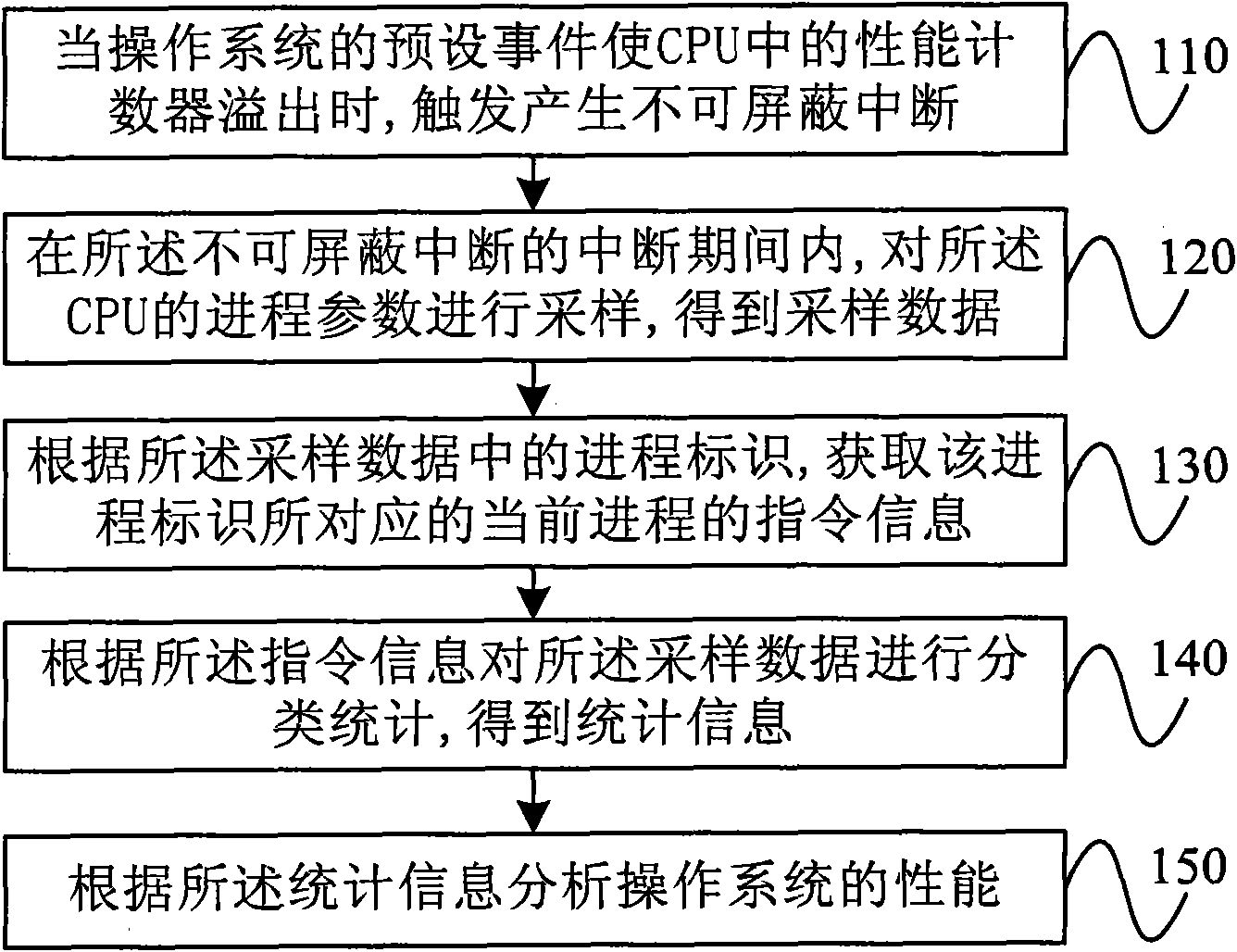

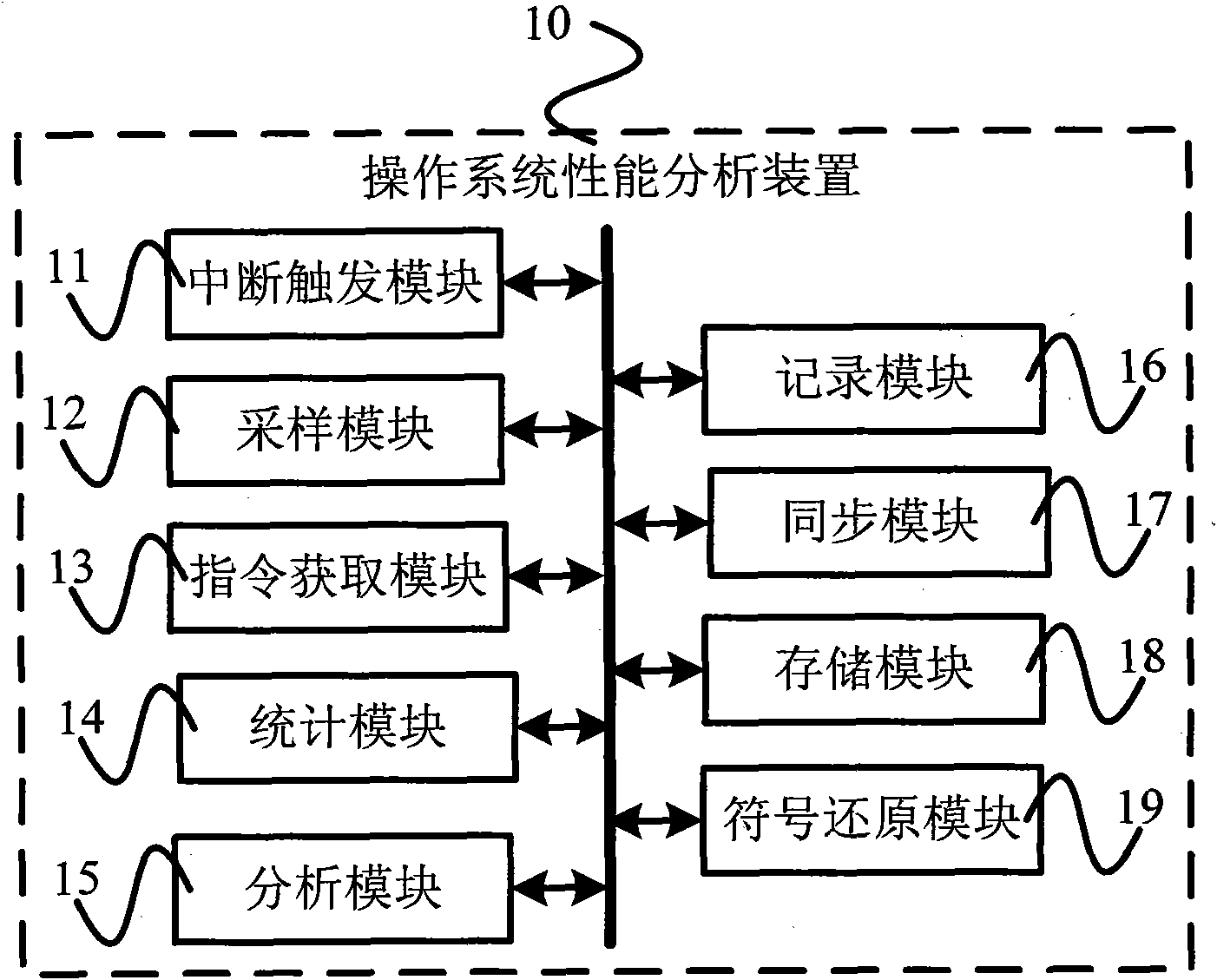

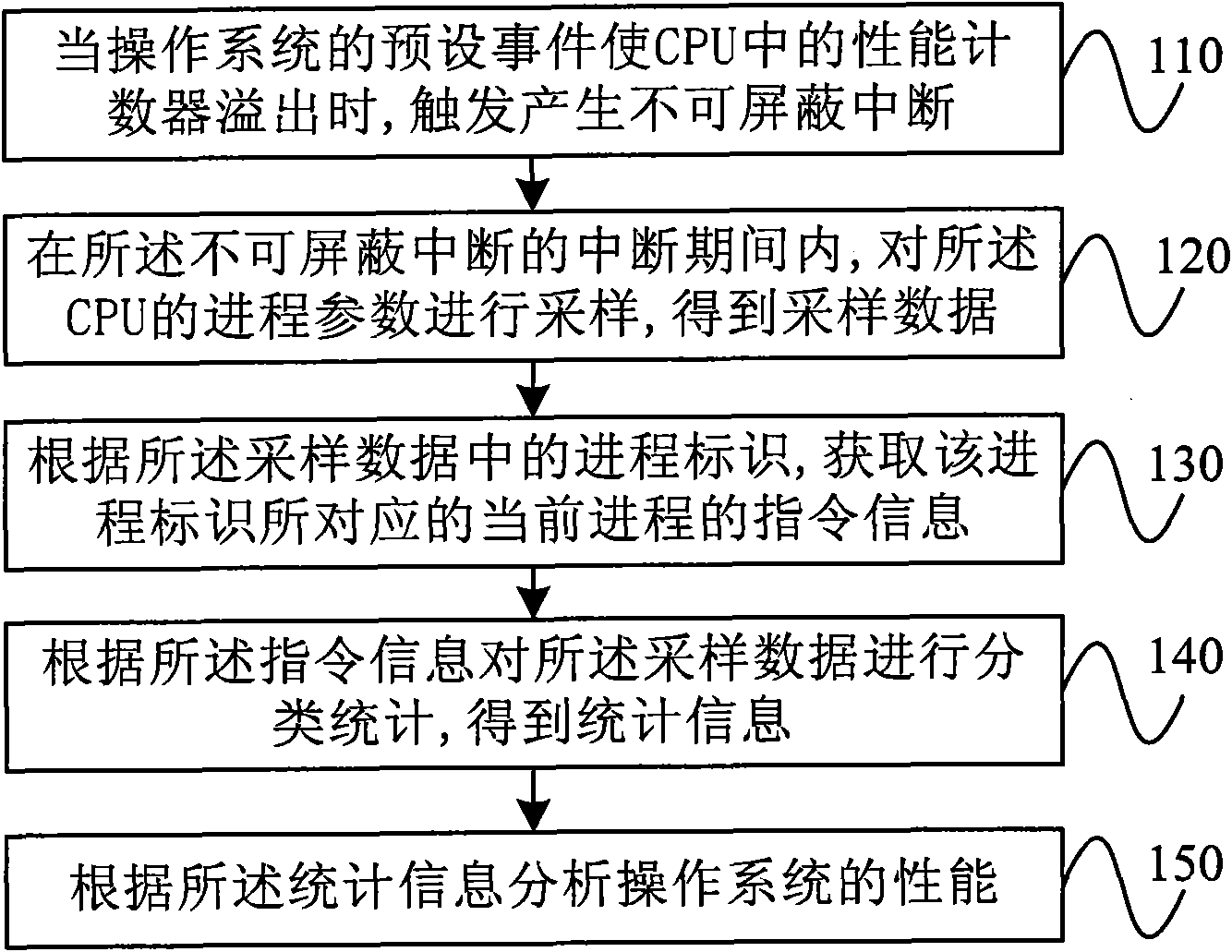

Operation system performance analysis method and device

InactiveCN102004678AQuality improvementImprove efficiencyError detection/correctionNon-maskable interruptInformation analysis

The invention provides an operation system performance analysis method and device. The method comprises the following steps: when a preset event in an operation system enables a performance counter in a central processing unit (CPU) to overflow, triggering to generate non maskable interrupt (NMI); during the interruption period of the NMI, sampling progress parameter of the CPU to obtain samplingdata; according to a process identification in the sampling data, acquiring command information of the current progress corresponding to the process identification; according to the command information, carrying out classified statistic on the sampling data to obtain statistic information; and according to the statistic information, analyzing the performance of the operation system. In the invention, the progress parameter is sampled when the preset event happens to obtain the statistical information for analysis, so that factors causing performance bottlenecks can be known under the condition of no error log, thereby improving the quality and efficiency of the operation system performance analysis.

Owner:北京以萨数据科技有限公司

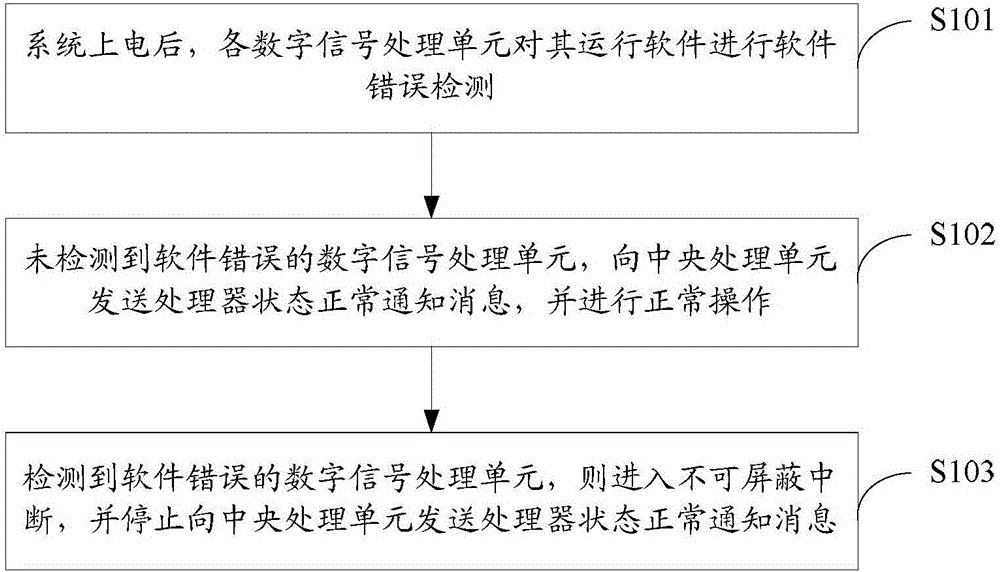

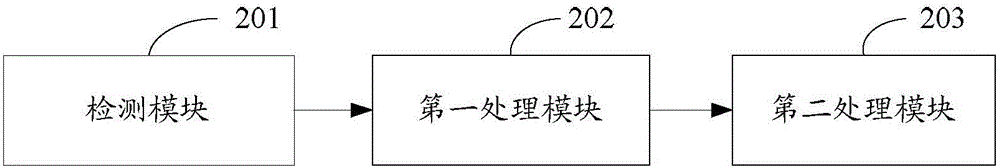

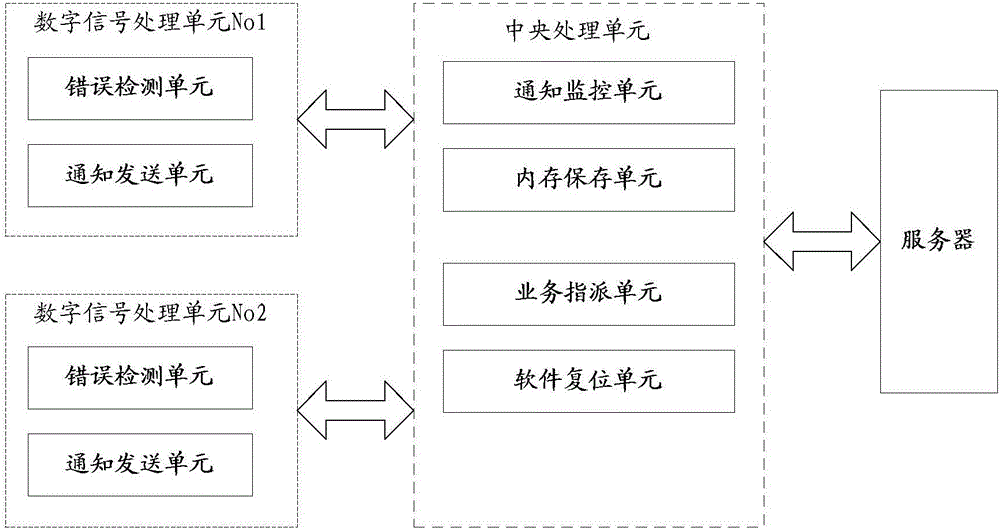

Software error field locating and processing method and apparatus

InactiveCN107526677AImprove the probability of false detectionDoes not cause an exception usingSoftware testing/debuggingDigital signal processingElectricity

The invention discloses a method and device for on-site location and processing of software errors, and relates to the technical field of embedded systems. The digital signal processing unit with a software error sends a processor status normal notification message to the central processing unit, and performs normal operation; the digital signal processing unit that detects a software error enters a non-maskable interrupt, and stops sending the processor to the central processing unit. Status normal notification message. In the present invention, while the processor self-detects software errors, other processors in the system are used to jointly detect software errors, thereby improving the detection probability of software errors.

Owner:SHANGHAI ZTE SOFTWARE CO LTD

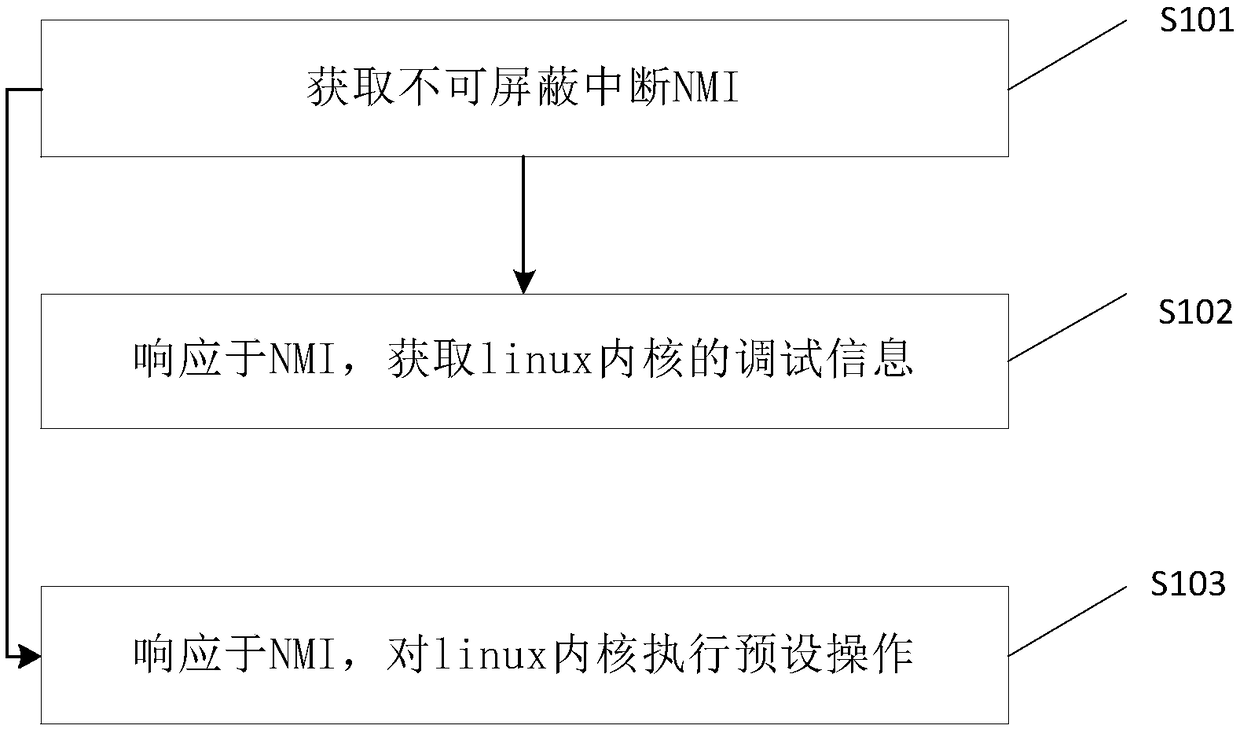

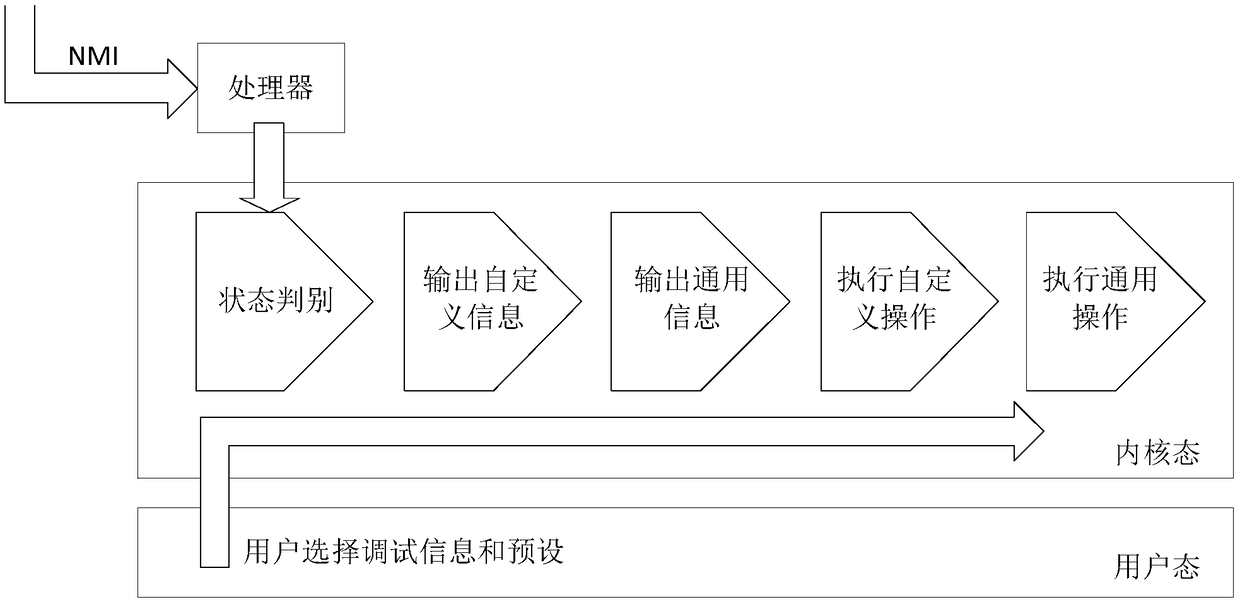

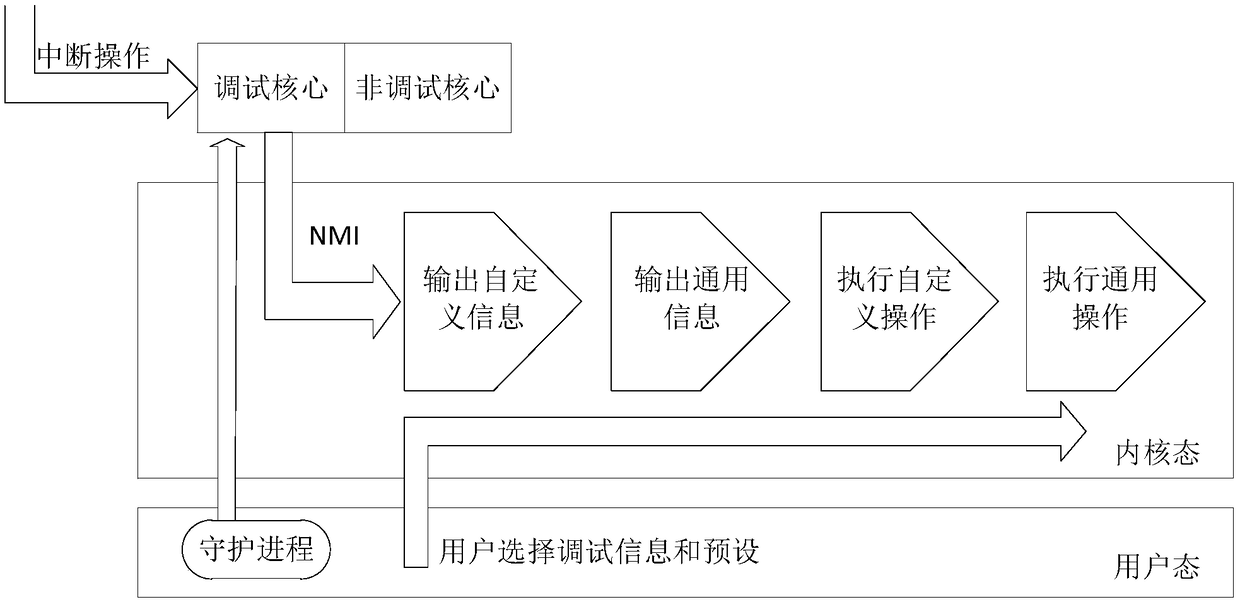

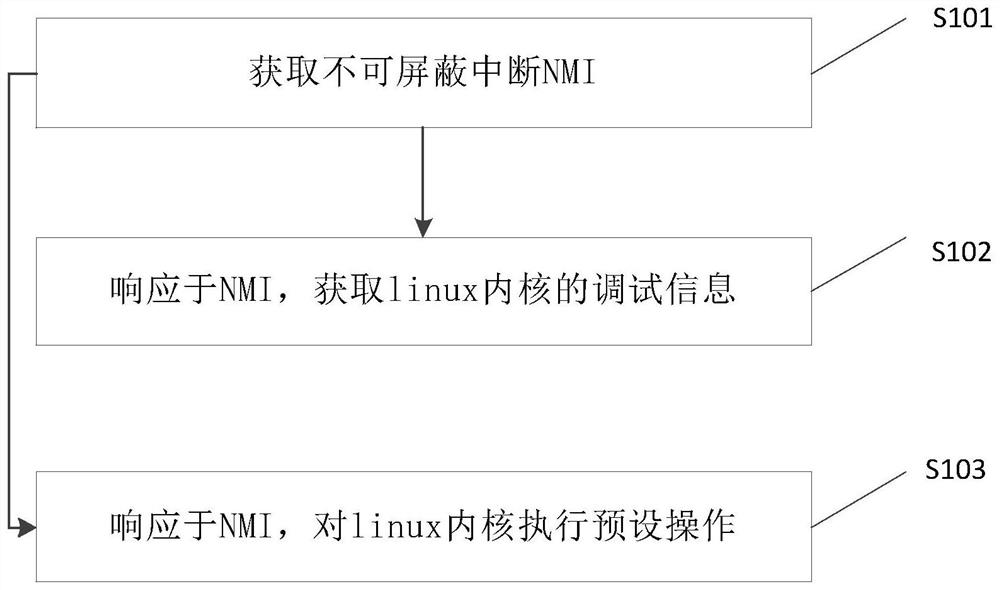

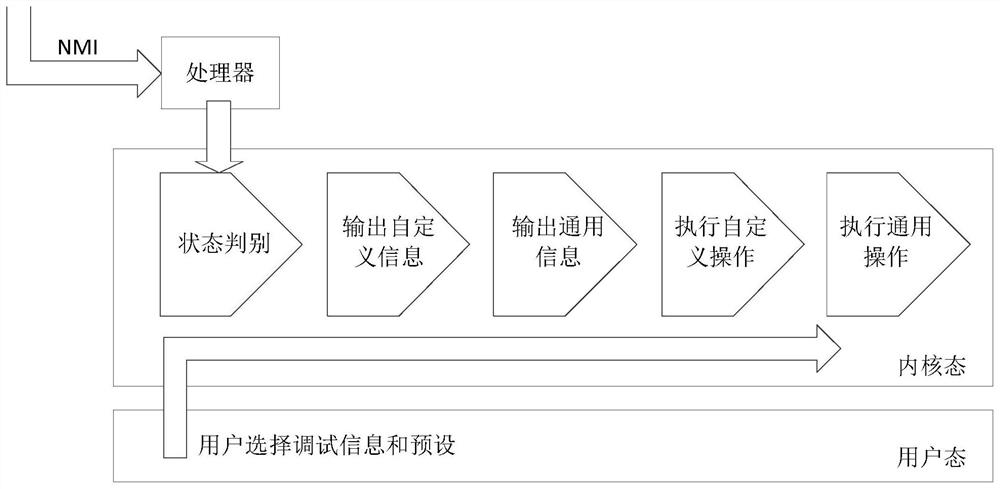

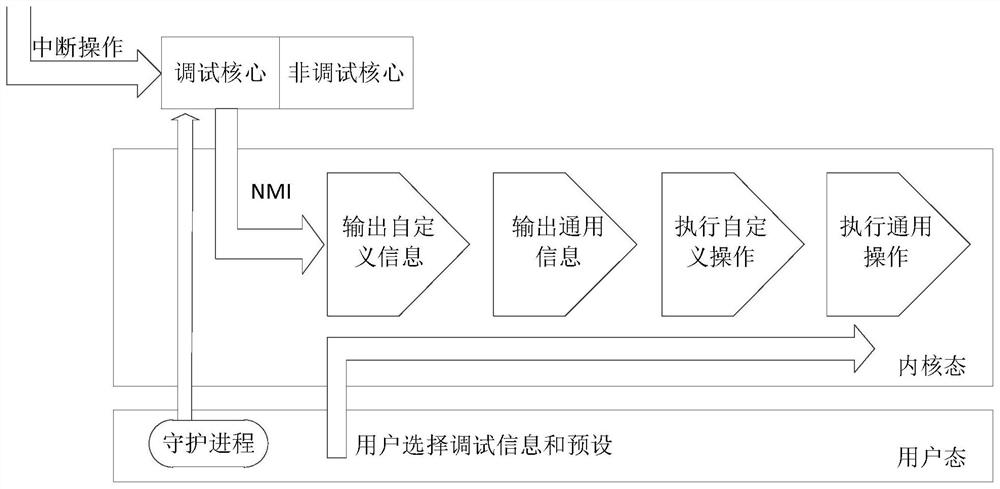

A linux kernel processing method and apparatus

ActiveCN109144873AReduce the impactImprove stabilitySoftware testing/debuggingComputer hardwareNon-maskable interrupt

Embodiments of the present application disclose a linux kernel processing method and apparatus, the method comprising steps acquiring a non-maskable interrupt NMI, obtaining debugging information of the linux kernel in response to the interrupt, and / or executing a preset operation on the linux kernel in response to the interrupt. Since NMI is an interrupt that cannot be masked by the processor, the processor can still obtain NMI interrupt when system exception occurs due to code failure in kernel state. In response to NMI, the processor can obtain debug information of the linux kernel and / or perform preset operation on the linux kernel. Through analyzing the debugging information of Linux kernel, we can get the debugging mode of kernel state code, in order to realize the debugging of kernel state code, the kernel of linux can be adjusted by executing the preset operation on the kernel of linux, so as to alleviate the influence of code failure on the kernel of linux, facilitate the acquisition of debugging information and the debugging of kernel state code, and improve the stability of the kernel of linux.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

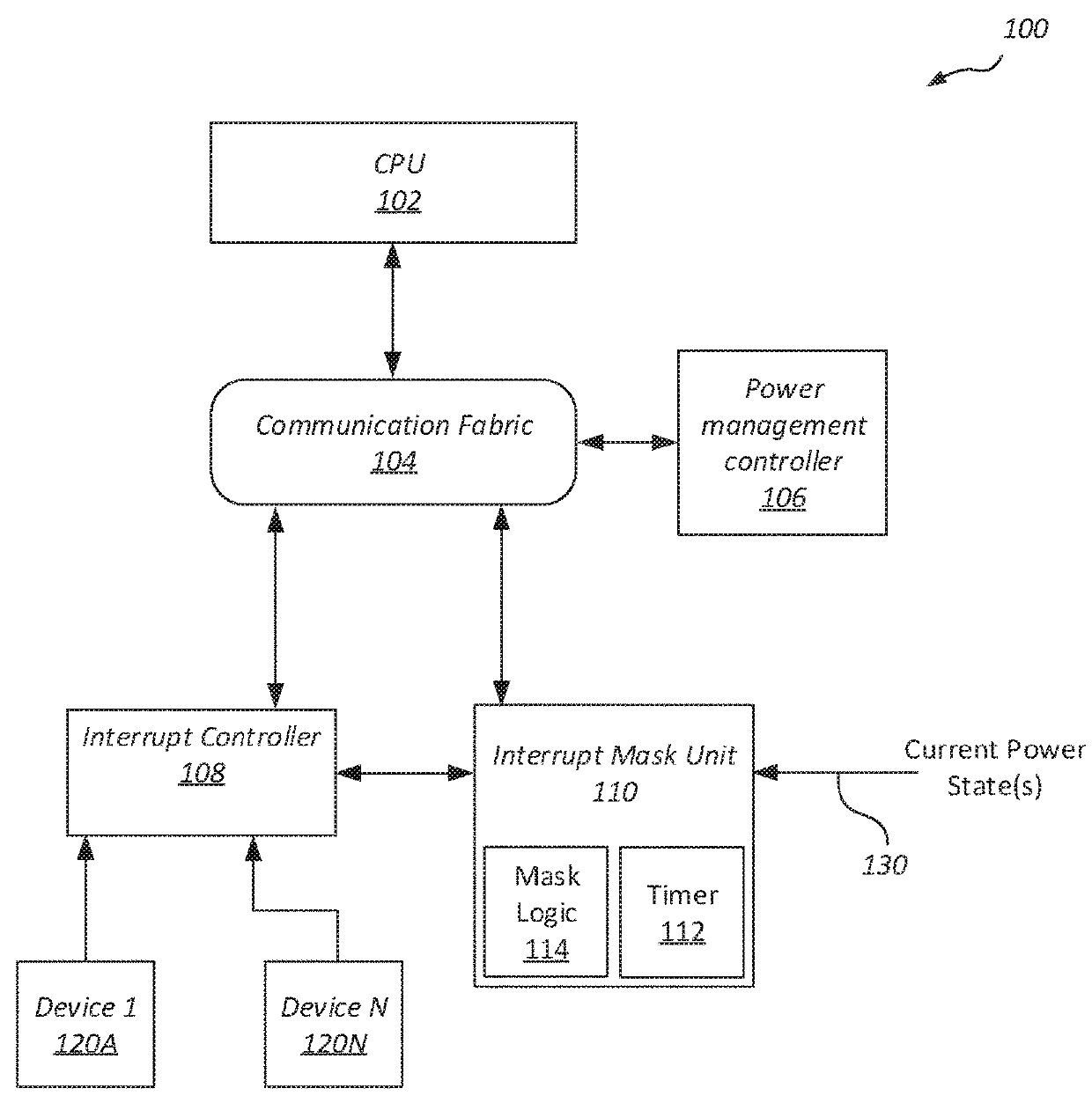

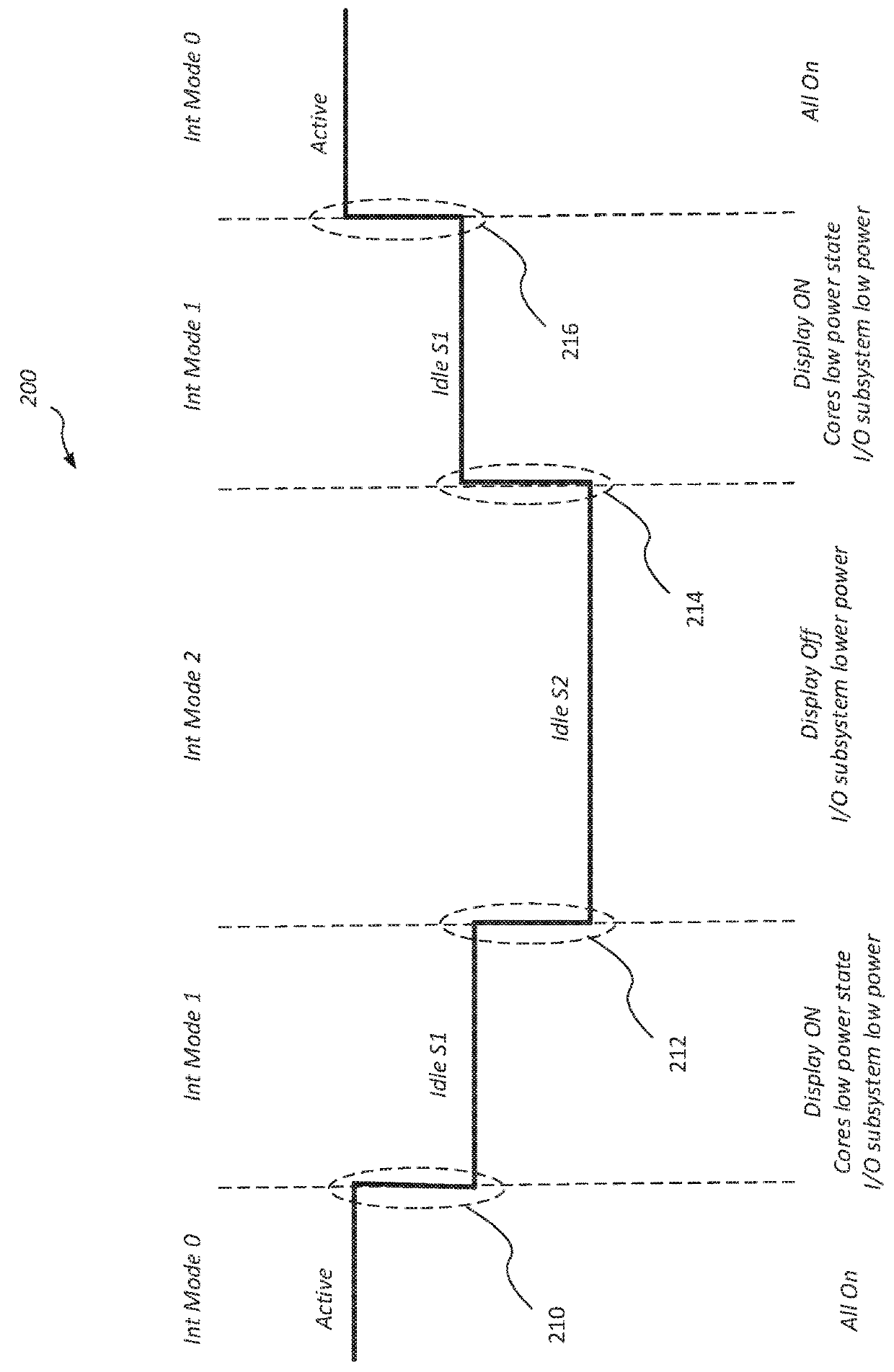

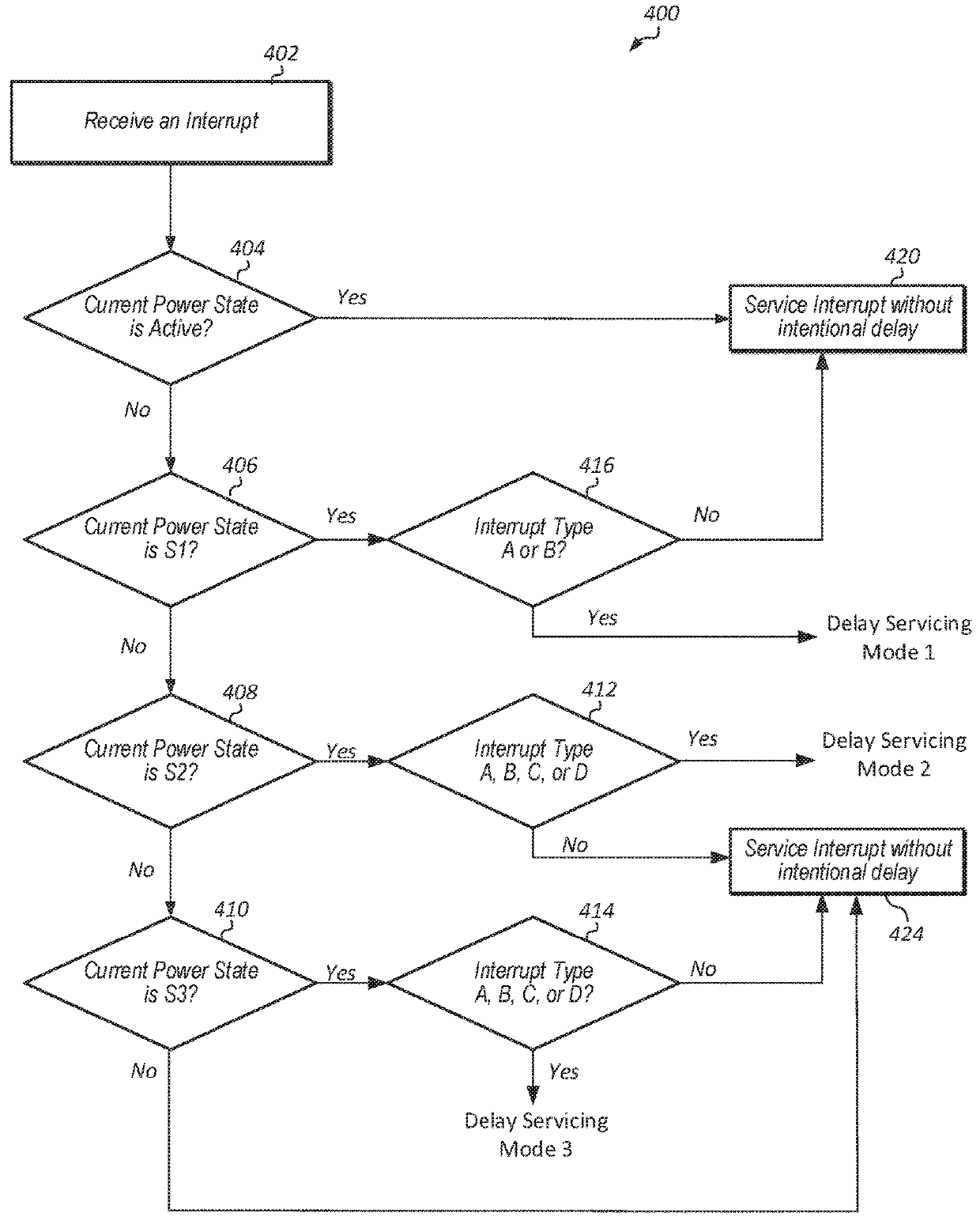

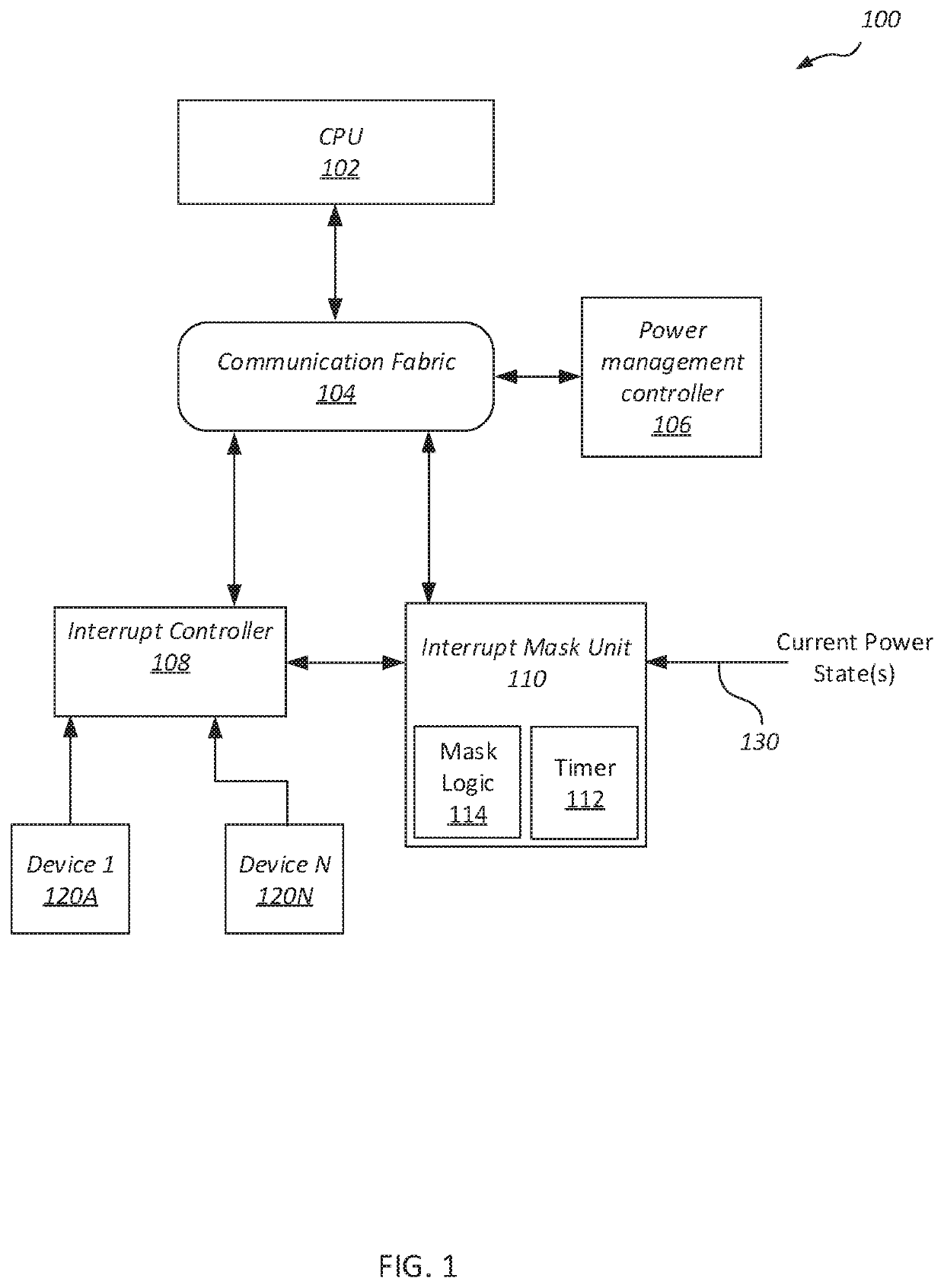

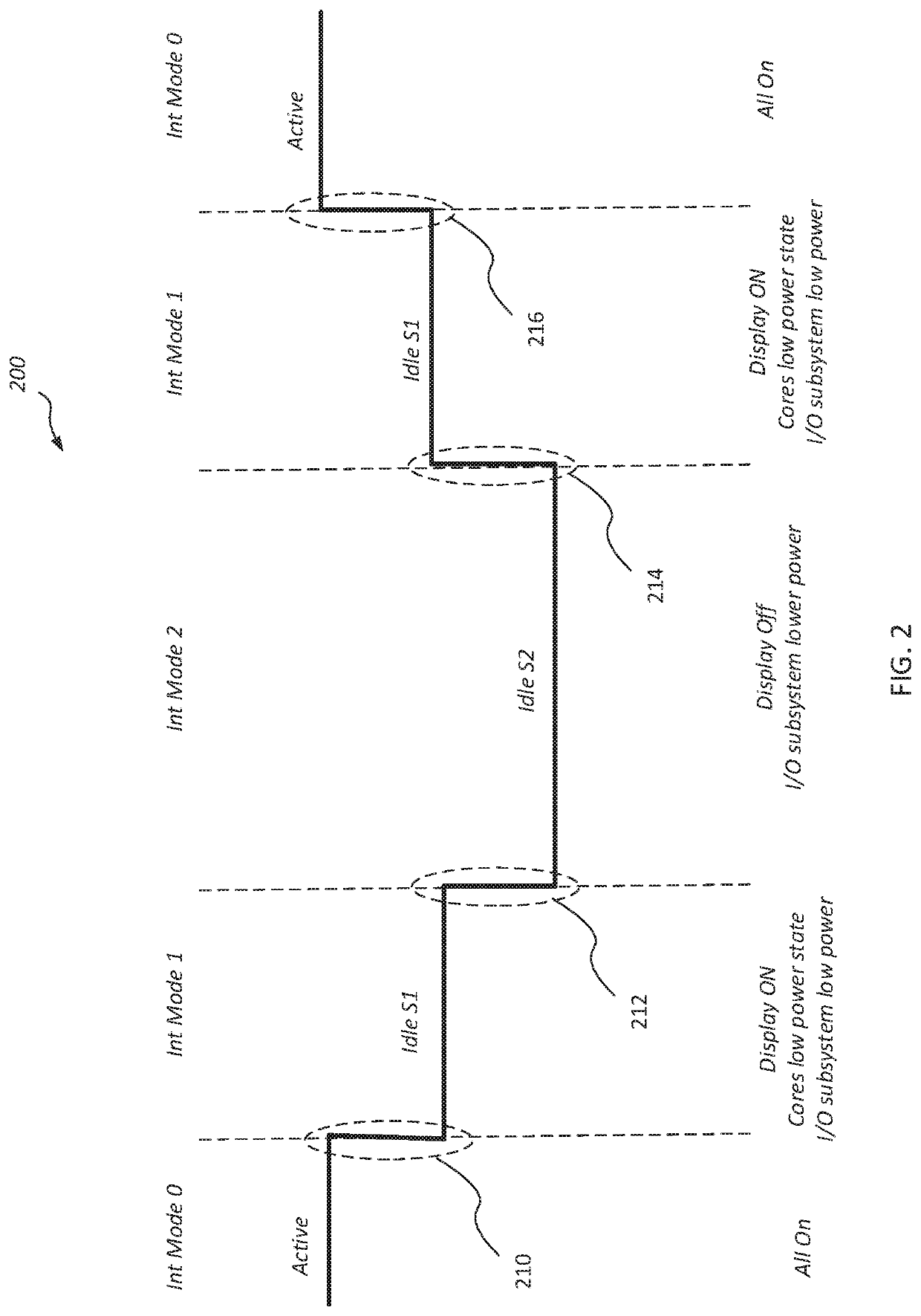

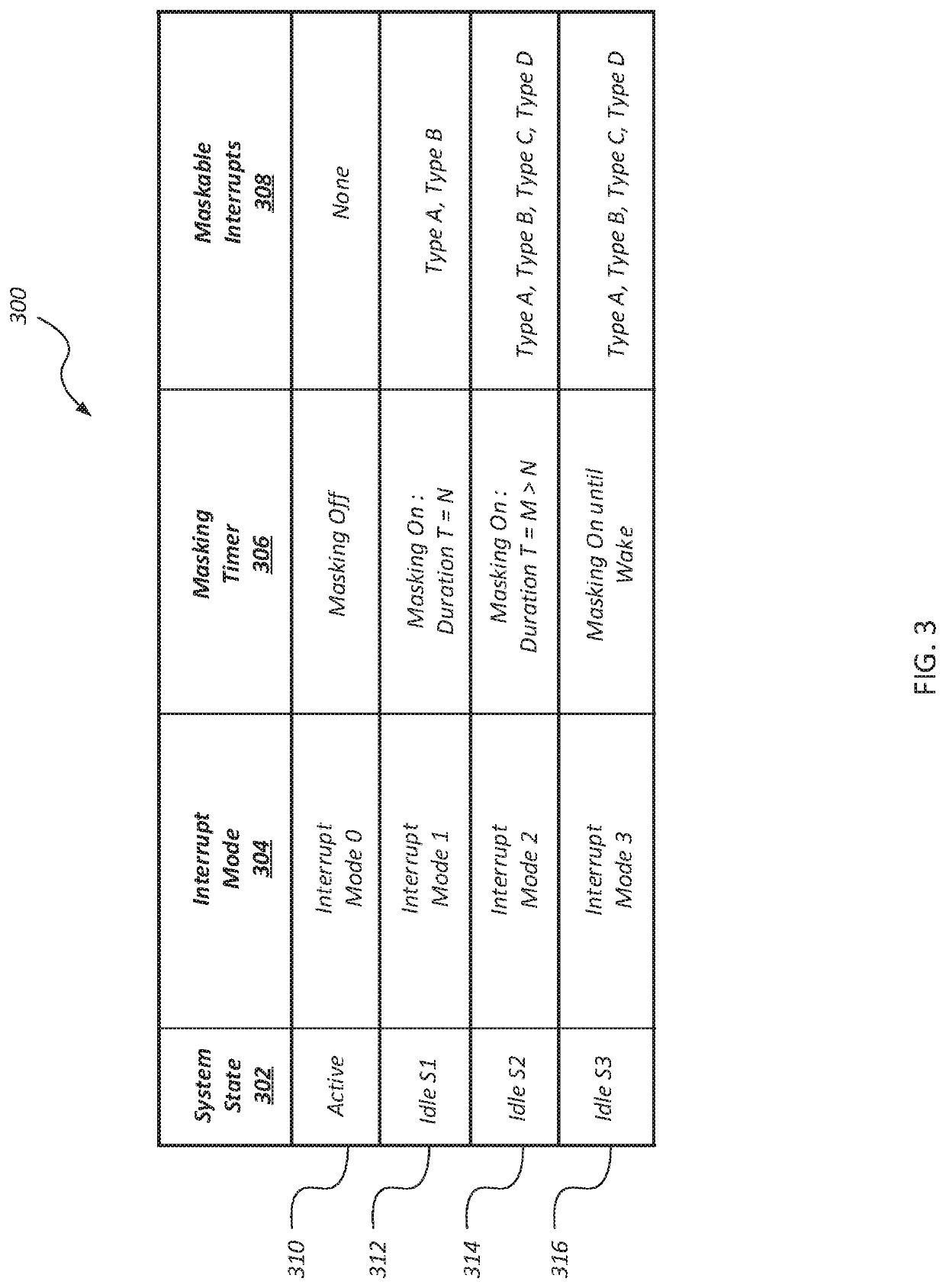

Dynamic Interrupt Rate Control in Computing Systems

ActiveUS20190163251A1Improve performanceIncreased power consumptionProgram initiation/switchingResource allocationNon-maskable interruptComputing systems

Systems, apparatuses, and methods for intentionally delaying servicing of interrupts in a computing system are disclosed. A computing system includes a processor that services interrupts generated by components of the computing system. An interrupt controller detects a received interrupt and intentionally delays servicing of the interrupt depending on various conditions. If the interrupt is a first type of interrupt and the processor is in a first power state, servicing of the interrupt is delayed by a first period of time. If the interrupt corresponds to the first type of interrupt and the processor is in a second power state, servicing of the interrupt is delayed for a period of time that is longer than the first period of time. If a non-maskable interrupt is received before expiration of either the first or second period of time, then servicing of any previously delayed interrupts is allowed to proceed.

Owner:ADVANCED MICRO DEVICES INC

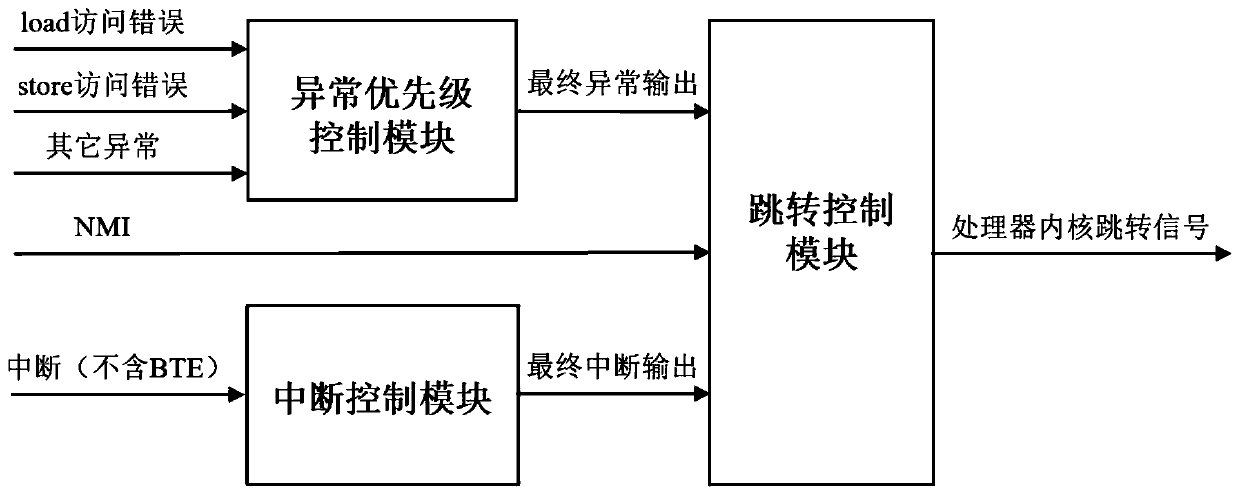

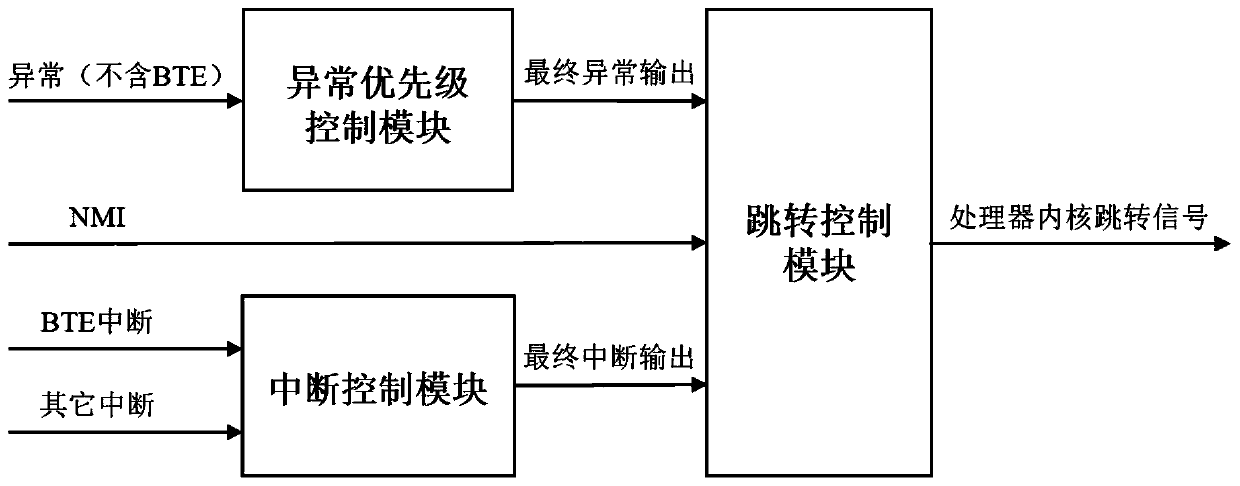

System and method for improving bus access error based on RISC-V architecture

ActiveCN110083473ADoes not interrupt processing flowIncrease flexibilityNon-redundant fault processingNon-maskable interruptRanking

The invention discloses a system for improving a bus access error based on RISC-V architecture. The system comprises an abnormal priority control module, an interrupt control module and a skip controlmodule. The system distributes interrupt numbers for the bus access error, takes the bus access error as interrupt sources for processing, and the abnormal priority control module is used for carrying out priority ranking on all abnormal types, selecting an abnormal type with the highest current priority and outputting the selected abnormal type to the skip control module; the interrupt control module is used for carrying out unified management on the bus access error and other interrupt sources, selecting the interrupt source with the highest current priority and outputting the interrupt source to the skip control module; and the skip control module is used for analyzing and processing input abnormal types, interrupt sources and unshielded interrupts and outputting analyzed and processedsignals to the processor core. According to the invention, abnormity report is changed to interrupt report for the bus access error, so that software control can be facilitated.

Owner:芯来智融半导体科技(上海)有限公司

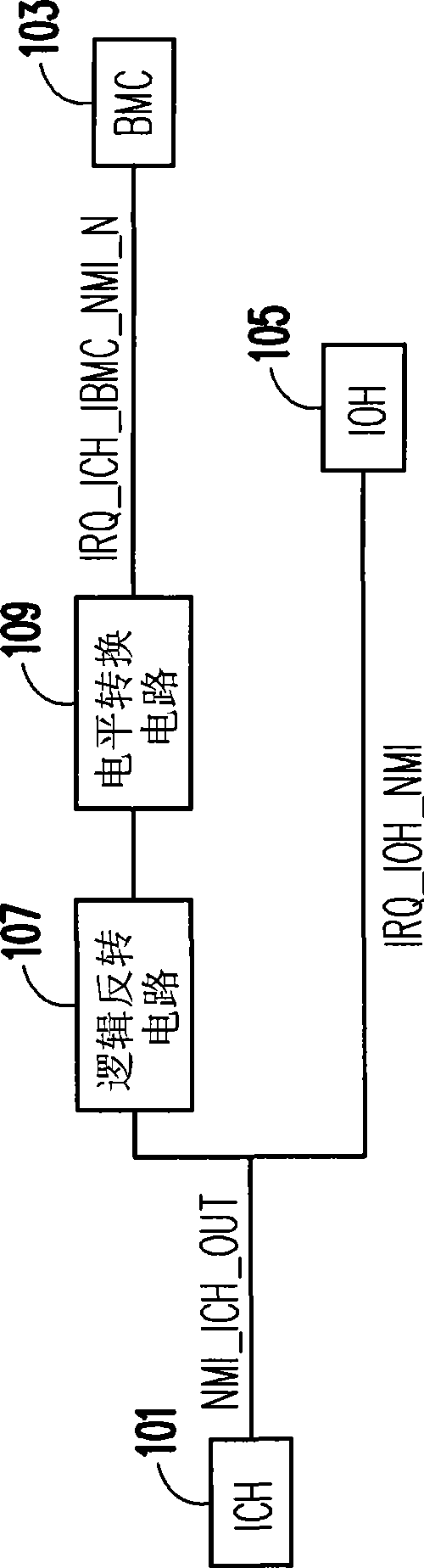

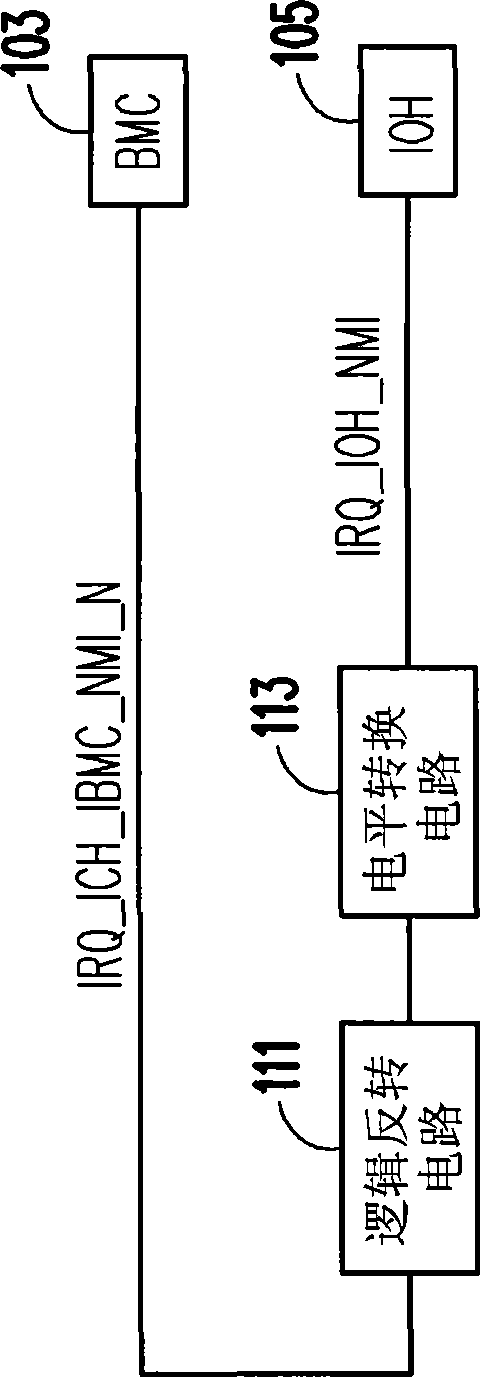

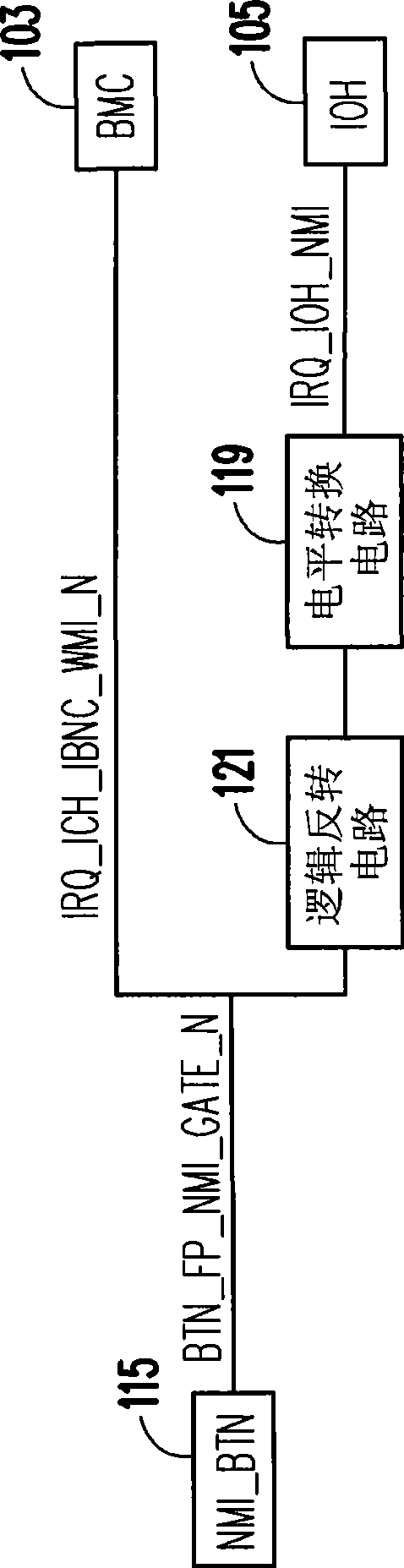

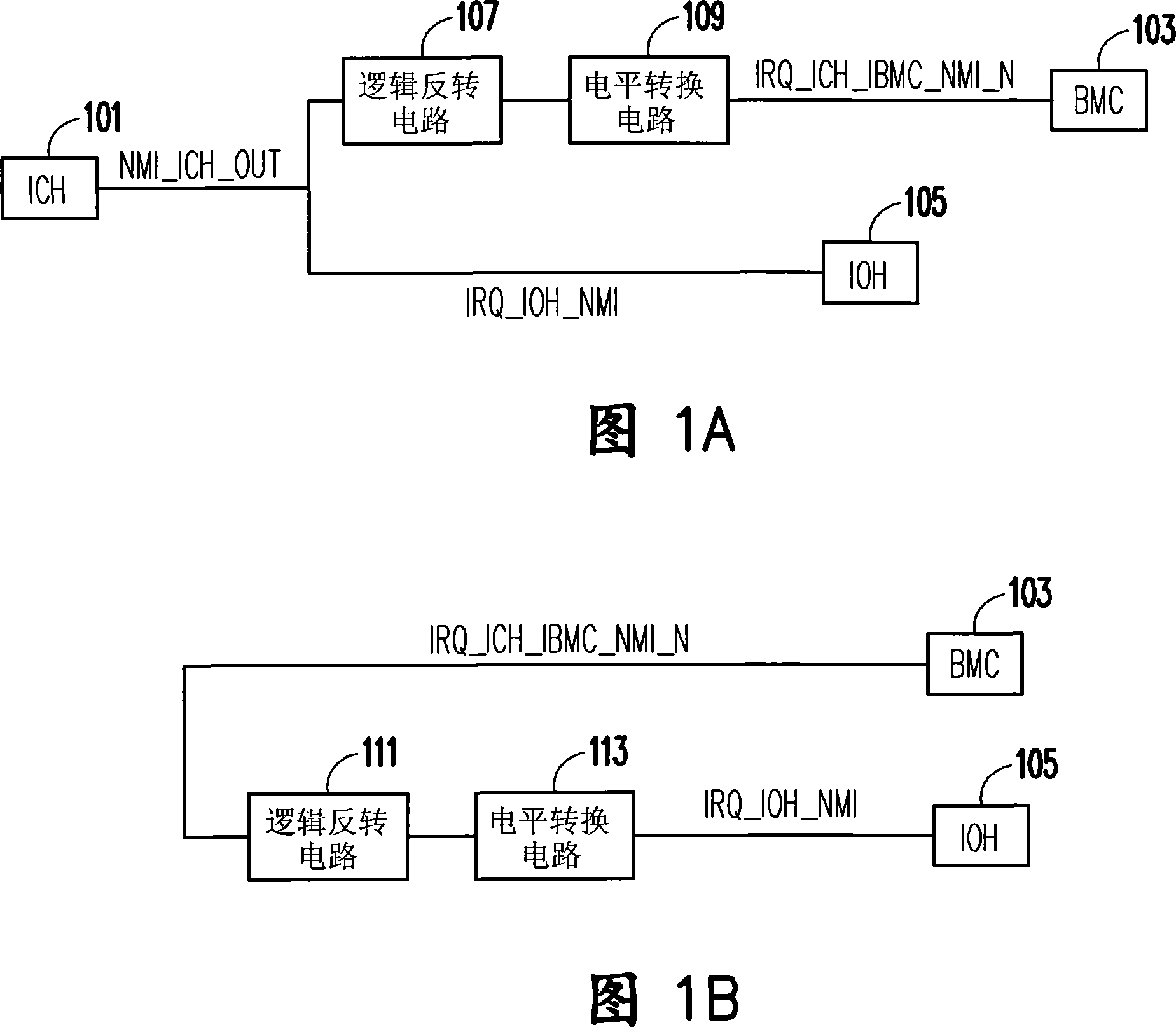

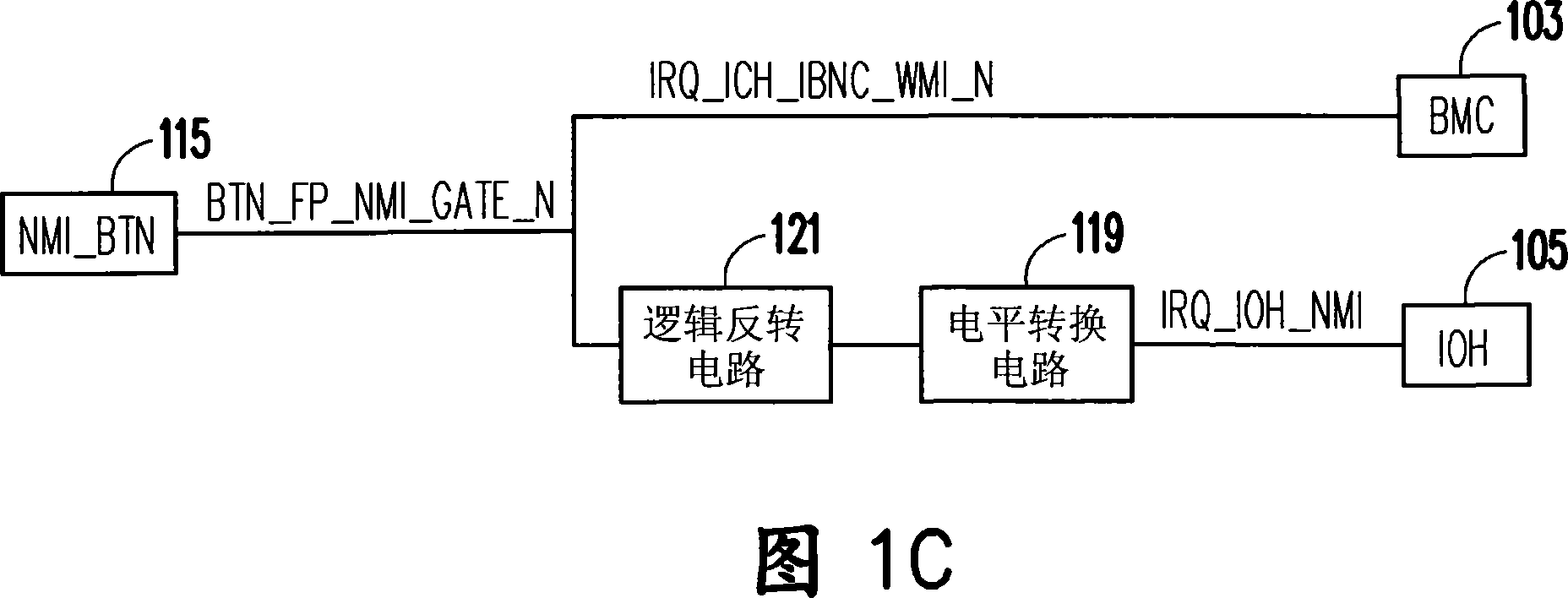

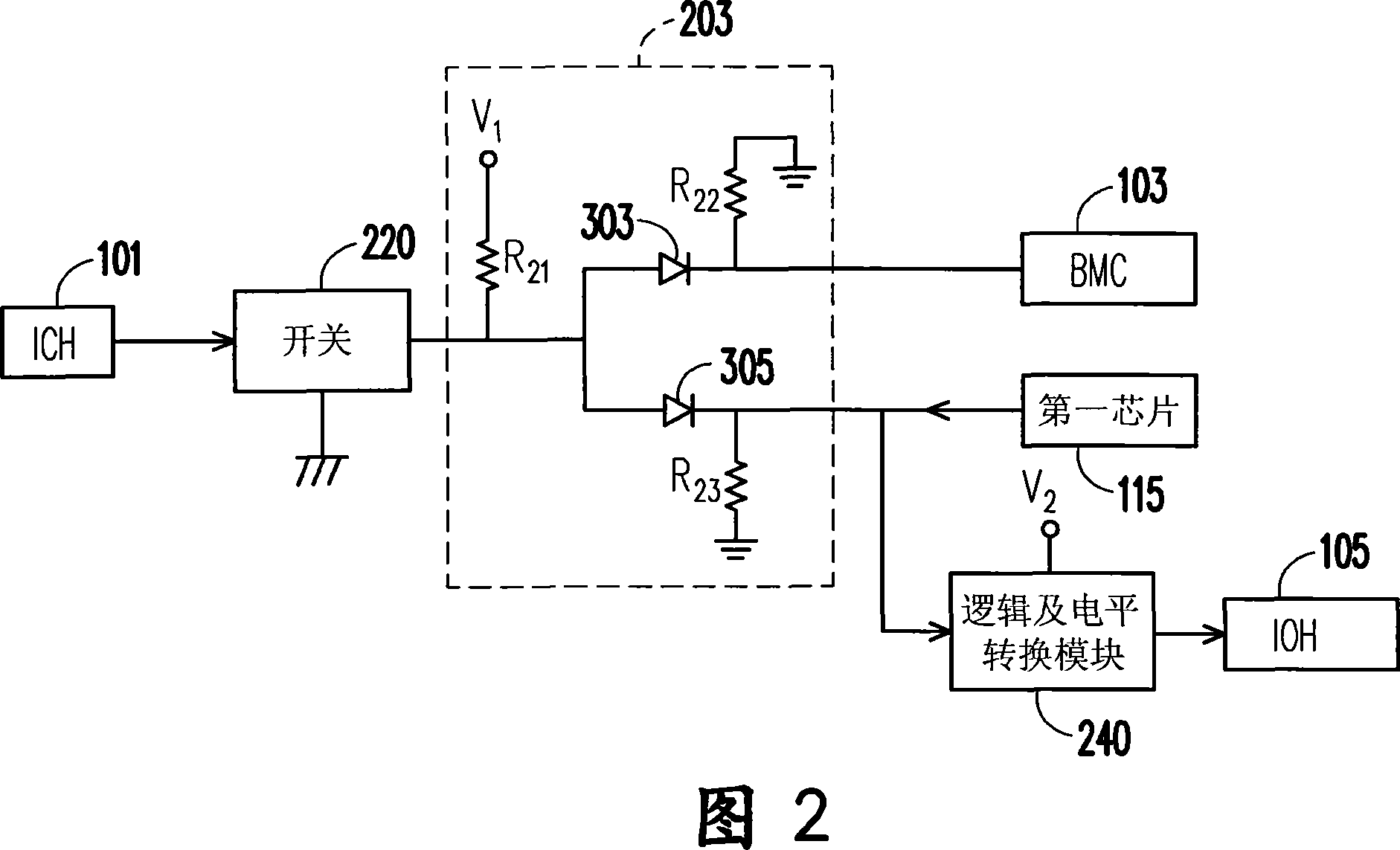

Conversion and transmission circuit for non-shielding interrupt request

InactiveCN101470680ALow costEasy to implementElectric digital data processingElectrical resistance and conductanceNon-maskable interrupt

A conversion transmission circuit of a non-maskable interrupt request is used to transmit the non-maskable interrupt request among a south bridge, a BMC, a first chip and an IOH of a central processor, which comprises a switch, an electrical level conversion module and a logic and electrical level conversion module, wherein the switch comprises a first end, a control end and a second end, the first end is grounded, the control end is coupled with the south bridge for receiving the control of the non-maskable interrupt request of the south bridge to conduct or cut off the first end and the second end. The electrical level conversion module comprises a first diode and a second diode, wherein the first diode is respectively coupled with the second end and a first power supply voltage through a first resistance after connecting with the positive electrode of the second diode, the negative electrode of the first diode is respectively coupled with the BMC and is coupled with the grounding voltage through a second resistance, and the negative electrode of the second diode is respectively coupled with the first chip and is coupled with the ground through a third resistance. The logic and electrical level conversion module is used to reversely transmit the signal of the input end to output, and makes the high electrical level to be in accordance with the electrical level of a second power supply voltage.

Owner:INVENTEC CORP

Dynamic interrupt rate control in computing system

ActiveUS10747298B2Improve performanceIncreased power consumptionProgram initiation/switchingResource allocationNon-maskable interruptController (computing)

Owner:ADVANCED MICRO DEVICES INC

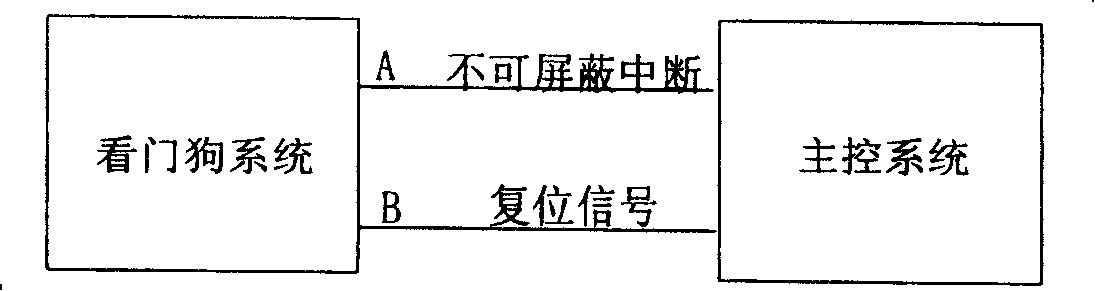

Method for preserving abnormal state information of control system

InactiveCN100395722CGuaranteed functionAvoid lossHardware monitoringData resettingComputer hardwareNon-maskable interrupt

It is a method to store the abnormal state information of the control system, which comprises the following steps: to set at least two degrees of counter in the watchdog system, and when the counter reaches the front degree value, the system triggers the non-shielding interval; the system stores the information easy to loose of the control system by use of the non-shielding interval; when the counter reaches the back degree value, the system triggers the reset signal to reset the control system.

Owner:王国忠

Apparatus and method to identify the source of an interrupt

An apparatus and method for processing non-maskable interrupt source information. For example, one embodiment of a processor comprises: a plurality of cores comprising execution circuitry to execute instructions and process data; local interrupt circuitry comprising a plurality of registers to store interrupt-related data including non-maskable interrupt (NMI) data related to a first NMI; and non-maskable interrupt (NMI) processing mode selection circuitry, responsive to a request, to select between at least two NMI processing modes to process the first NMI including: a first NMI processing mode in which the plurality of registers are to store first data related to a first NMI, wherein no NMI source information related to a source of the NMI is included in the first data, and a second NMI processing mode in which the plurality of registers are to store both the first data related to the first NMI and second data comprising NMI source information indicating the NMI source.

Owner:INTEL CORP

Anti-jamming method for computer central processing unit

InactiveCN101446919BChange the way of beingSimple methodSoftware testing/debuggingNon-maskable interruptAnti jamming

The invention discloses an anti-jamming method for a computer central processor, which comprises the following steps: 1, during the initialization of computer CPU, the maximum address occupied by the program thereof is read into an additional program maximum address register PCMAX; and 2, before the CPU fetches order codes according to the content of a program counter PC, the contents of the program counter PC and the program maximum address register PCMAX are input into an additional program address comparator PCP for comparison, wherein, when the former is equal to or smaller than the latter, the CPU executes normally, if not, the program address comparator PCP outputs an interruption signal to an additional non-maskable interruption source USINT to allow the non-maskable interruption source USINT to produce interruption and to lead the CPU into the interruption service program. The invention has a simple hardware design, less steps, is simple and convenient to be operated, and provides a simple solution to the problem that program interferes with a blank program storage area and an idle program storage area.

Owner:XIAN UNIV OF SCI & TECH

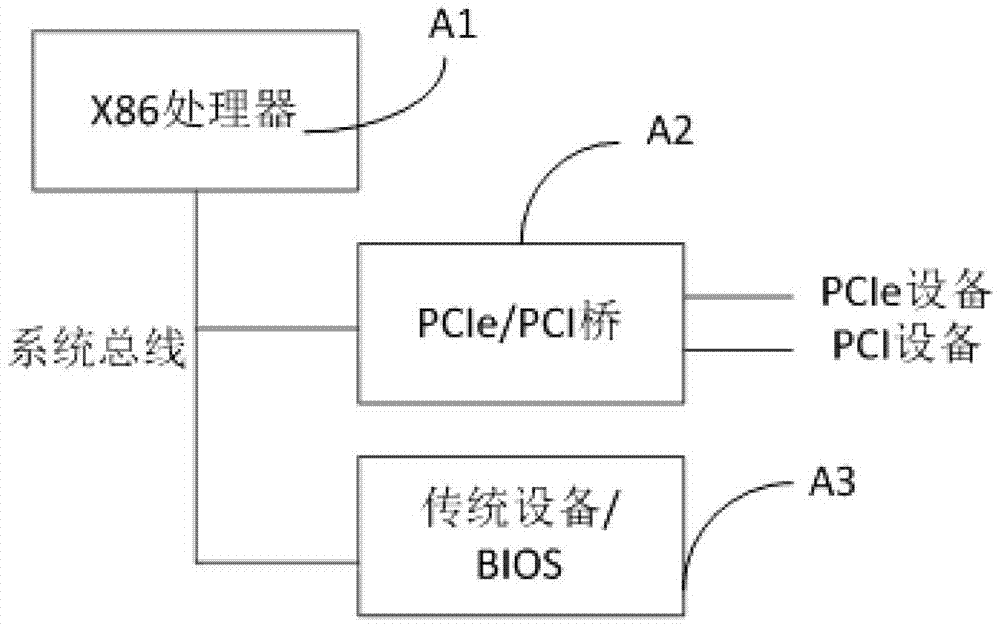

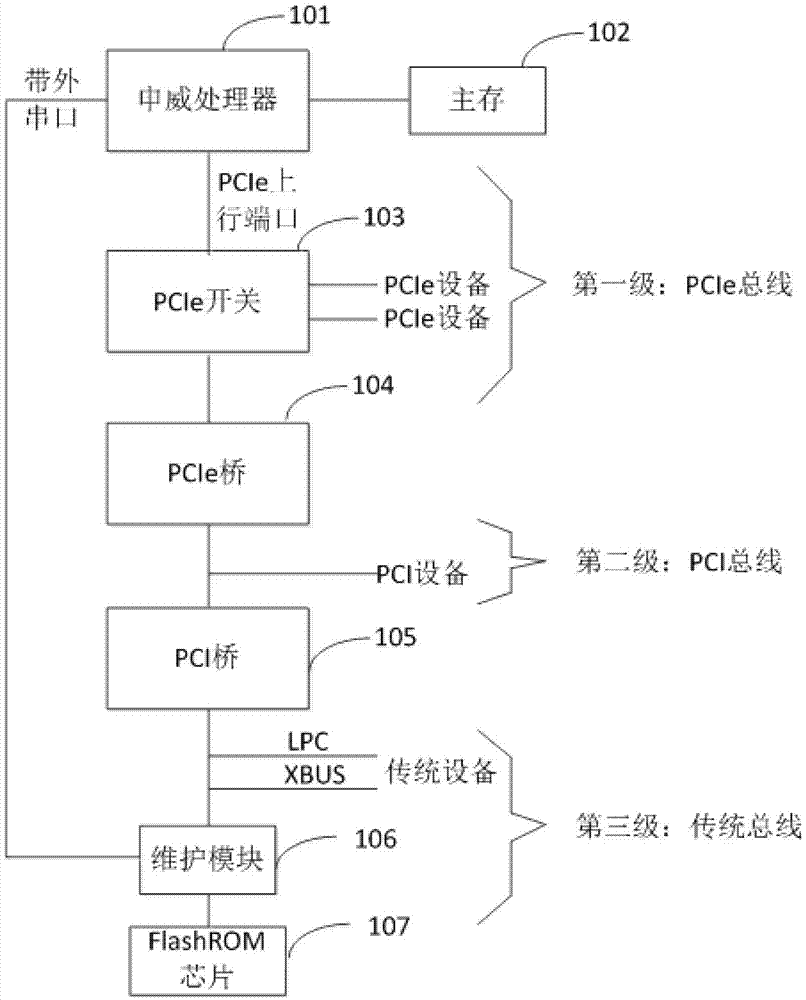

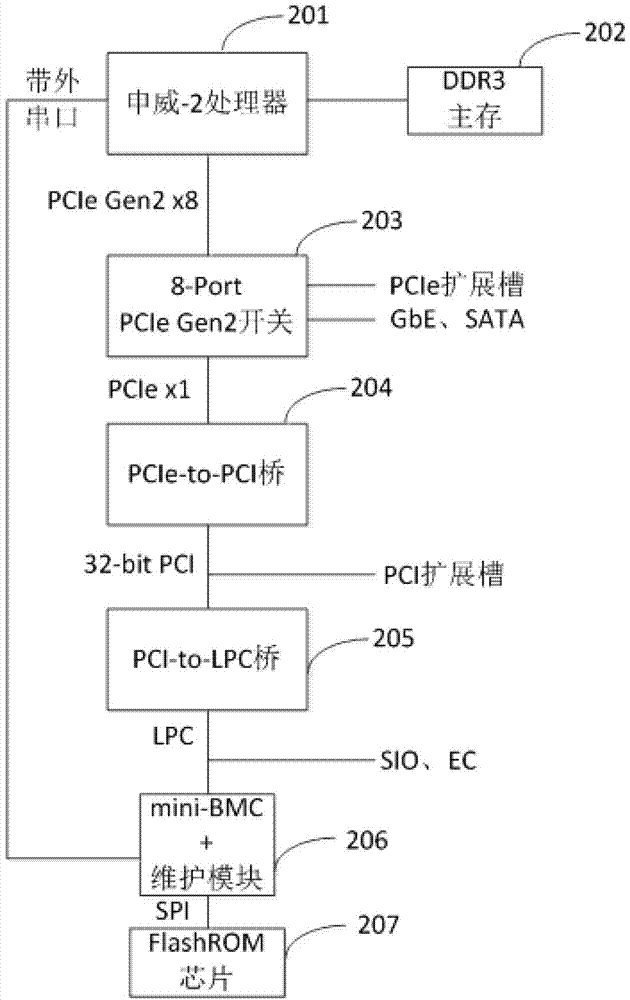

An IO extension architecture method based on standard pcie uplink port

The invention provides an input / output (I / O) framework expanding method based on a standard PCIe upstream port. Layering multistage bus expansion of the standard PCIe upstream port is used. A PCIe bus is arranged in a first stage, a PCI bus is arranged in a second stage, and a traditional bus is arranged in a third stage, wherein a basis input / output system (BIOS) is arranged in the traditional bus in a hanging mode. Initial configuration required by an SW processor and initial execution codes required by the SW processor are injected through a synchronous serial access out of a band, the initial execution codes achieve access configuration of a traditional device through only once depth-first enumeration, and the SW processor is enabled to rapidly obtain contents of the BIOS. Non-maskable interruption can be sent to a central processing unit (CPU) through the synchronous serial access out of the band, and be used for the aims of waking-up in a sleep state and the like.

Owner:JIANGNAN INST OF COMPUTING TECH

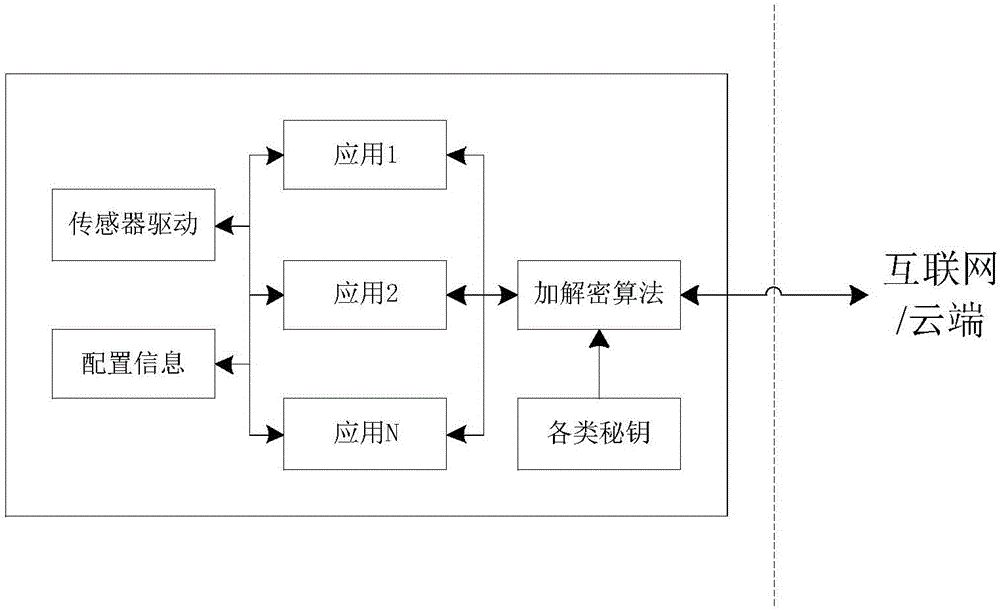

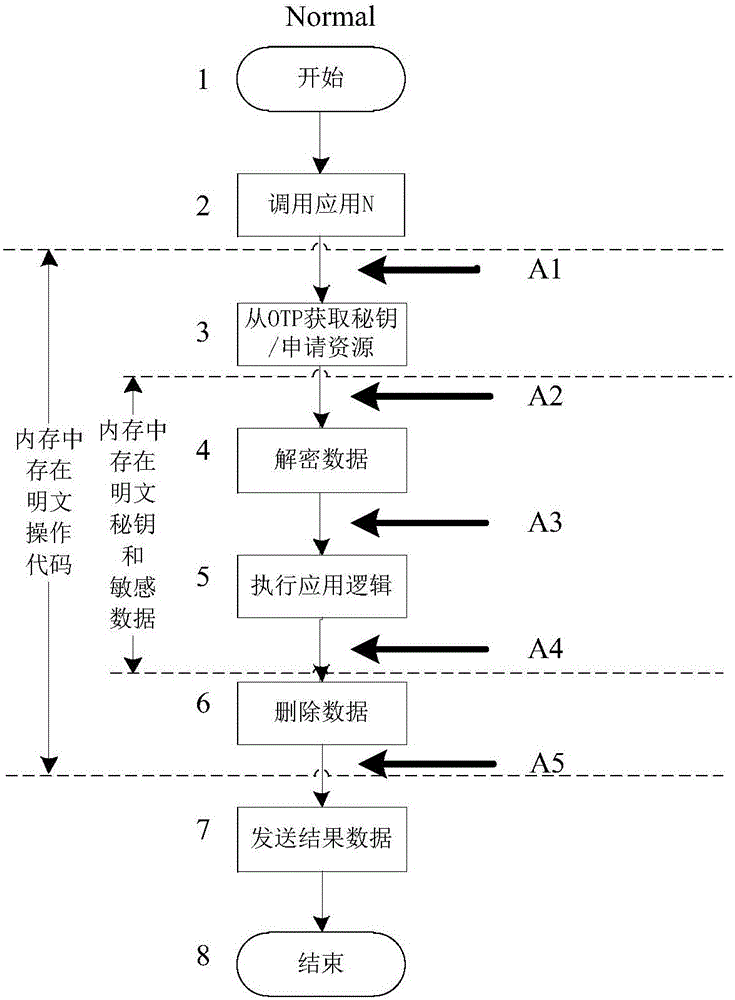

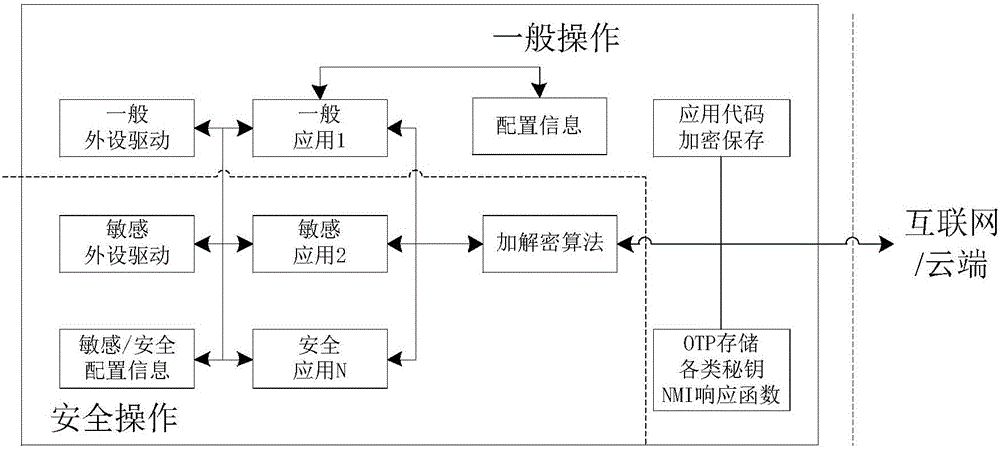

Method for improving product safety of Internet of Things through non-maskable interrupt

ActiveCN106295259AImprove versatilityAvoid attackProgram/content distribution protectionNon-maskable interruptOne time programmable

The invention discloses a method for improving product safety of Internet of Things through non-maskable interrupt. All safety applications / operations are executed in NMI (non-maskable interrupt). The method includes (1), calling a safety application / operation N by a system; (2), configuring a calling mark of the safety application / operation N; (3), triggering the NMI, and by judging the mark set in the step (2) via an NMI processing function, learning the called safety application / operation and acquiring parameters; (4), acquiring various secret keys needed for the safety application / operation N from OTP (one time programmable), and storing the secret keys into an applied resource; (5), acquiring plaintext data and codes through the secret keys; (6), executing logic, including data processing and result encrypting and signing, of the safety application / operation N; (7), deleting encrypted data and code plaintexts; (8), cleaning and releasing the applied resource, and quitting the NMI; (9), sending result data of the safety application / operation N; (10), ending calling of the safety application / operation N.

Owner:HANGZHOU SYNOCHIP DATA SECURITY TECH CO LTD

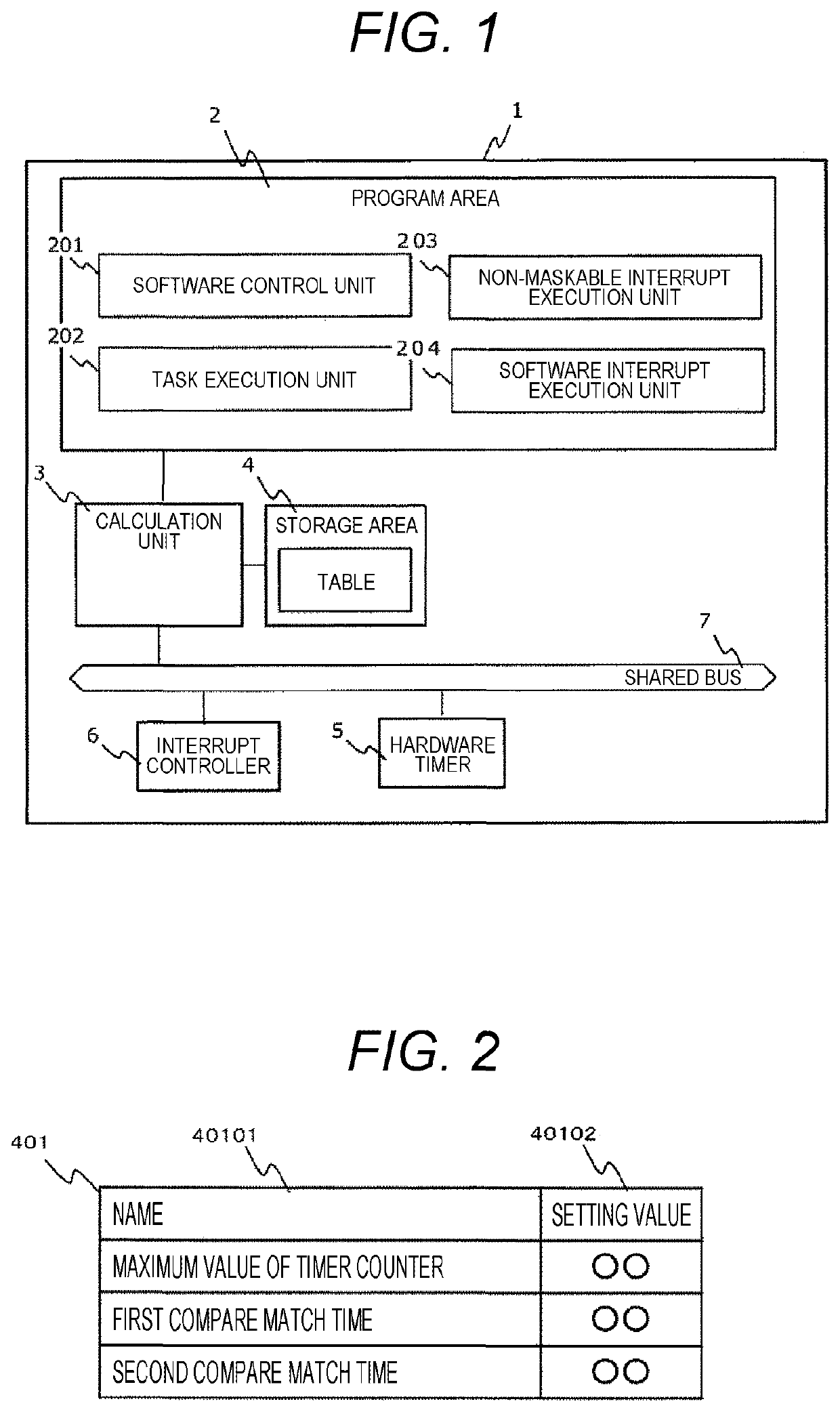

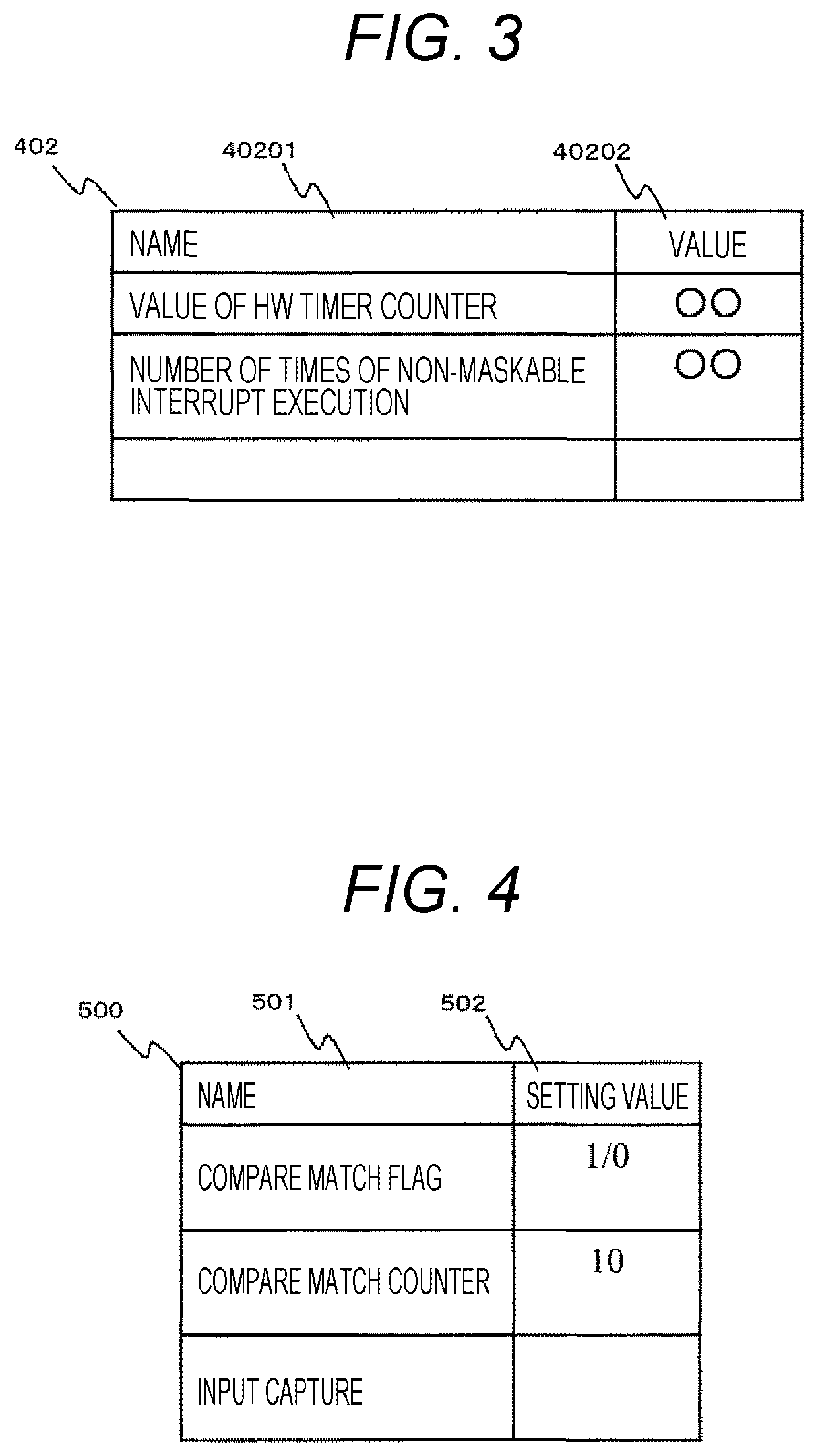

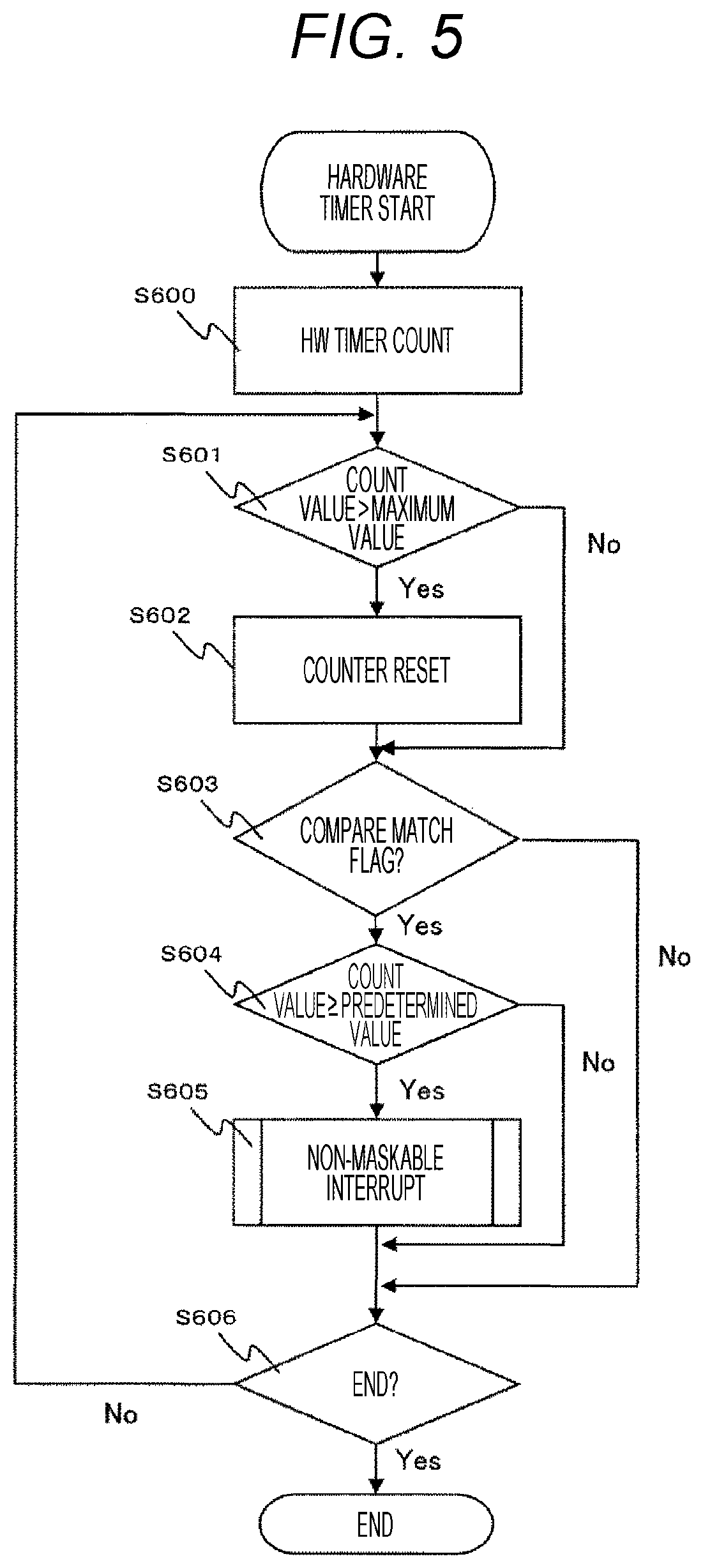

Vehicle control device

In the present invention, when an abnormality occurs in a task, regardless of whether a critical section is being executed, timeout detection is realized by determining whether the critical section (CS) is necessary for the design in a preset task execution time and a certain period of time to distinguish between necessary interrupt disable and abnormal interrupt disable. A vehicle control device includes task execution means for causing a system to execute a task, and interrupt processing means for performing an interrupt process at the time of execution of the task. A maskable interrupt and a non-maskable interrupt that is commanded to execute after the maskable interrupt are included, the maskable interrupt is commanded to execute during an interrupt disable time, and then the non-maskable interrupt is executed.

Owner:HITACHI ASTEMO LTD

Conversion and transmission circuit for non-shielding interrupt request

InactiveCN101470680BLow costEasy to implementElectric digital data processingElectrical resistance and conductanceNon-maskable interrupt

A conversion transmission circuit of a non-maskable interrupt request is used to transmit the non-maskable interrupt request among a south bridge, a BMC, a first chip and a north bridge, which comprises a switch, an electrical level conversion module and a logic and electrical level conversion module, wherein the switch comprises a first end, a control end and a second end, the first end is grounded, the control end is coupled with the south bridge for receiving the control of the non-maskable interrupt request of the south bridge to conduct the first end and the second end. The electrical level conversion module comprises a first diode and a second diode, wherein the first diode is respectively coupled with the second end and a first power supply voltage through a first resistance after connecting with the positive electrode of the second diode, the negative electrode of the first diode is respectively coupled with the BMC and is coupled with the grounding voltage through a second resistance, and the negative electrode of the second diode is respectively coupled with the first chip and is coupled with the ground through a third resistance. The logic and electrical level conversion module is used to reversely transmit the signal of the input end to output, and makes the high electrical level to be in accordance with the electrical level of a second power supply voltage.

Owner:INVENTEC CORP

Avoiding premature enabling of nonmaskable interrupts when returning from exceptions

A processor of an aspect includes a decode unit to decode an exception handler return instruction. The processor also includes an exception handler return execution unit coupled with the decode unit. The exception handler return execution unit, responsive to the exception handler return instruction, is to not configure the processor to enable delivery of a subsequently received nonmaskable interrupt (NMI) to an NMI handler if an exception, which corresponds to the exception handler return instruction, was taken within the NMI handler. The exception handler return execution unit, responsive to the exception handler return instruction, is to configure the processor to enable the delivery of the subsequently received NMI to the NMI handler if the exception was not taken within the NMI handler. Other processors, methods, systems, and instructions are disclosed.

Owner:INTEL CORP

A kind of linux kernel processing method and device

ActiveCN109144873BImprove stabilityImplement debuggingSoftware testing/debuggingNon-maskable interruptLinux kernel

The embodiment of the present application discloses a method and device for processing the linux kernel. By obtaining the non-maskable interrupt NMI, in response to the interrupt, the debugging information of the linux kernel is obtained, and / or, in response to the interrupt, a preset operation is performed on the linux kernel . Since NMI is an interrupt that the processor cannot mask, when the code in the kernel mode fails and causes a system exception, the processor can still obtain the NMI interrupt. In response to the NMI, the processor can obtain the debugging information of the linux kernel and / or The kernel performs preset operations. Among them, by analyzing the debugging information of the linux kernel, the debugging method of the kernel state code can be obtained, so as to realize the debugging of the kernel state code, and the adjustment of the linux kernel can be realized by performing preset operations on the linux kernel, so as to alleviate code failures The impact on the linux kernel is conducive to the acquisition of debugging information and the debugging of kernel mode code, and improves the stability of linux kernel operation.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

Thermal throttle control with minimal impact to interrupt latency

A computer-implemented method, data processing system, and processor for thermal regulation control with minimal impact on interrupt latency are provided. Monitors the setting of the interrupt status bit. In response to setting the interrupt status bit, it is determined whether the interrupt associated with the interrupt status bit is an unmasked interrupt. In response to an unmasked interrupt, the existing regulation mode is disabled and the interrupt is processed, wherein the interrupt latency of the integrated circuit is reduced. Monitors the clearing of the interrupt status bits. In response to clearing the interrupt status bit, the existing regulation mode is enabled.

Owner:IBM CORP

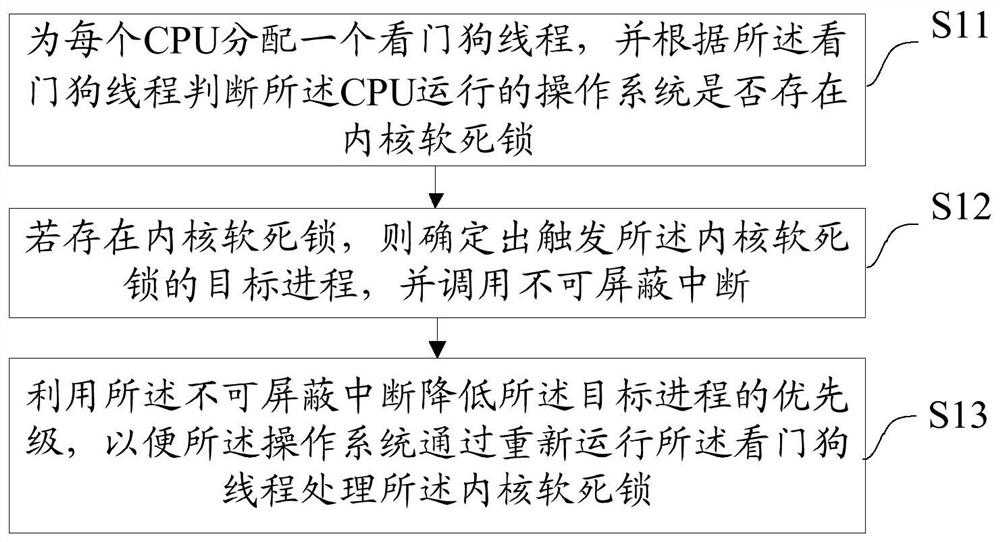

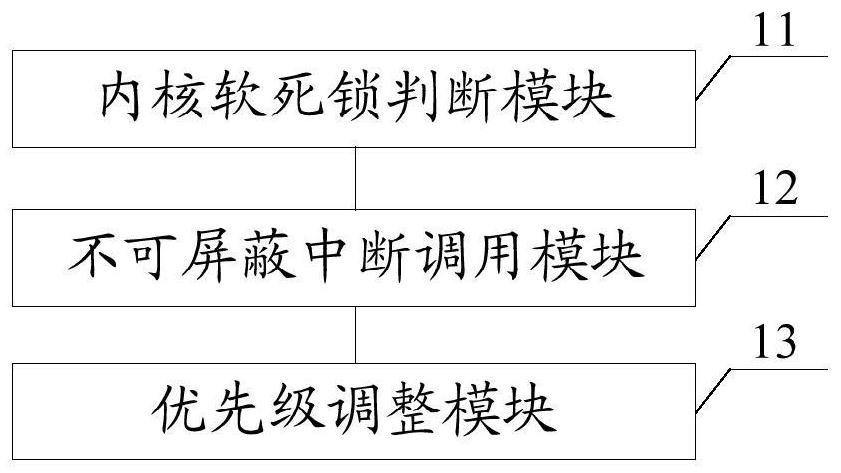

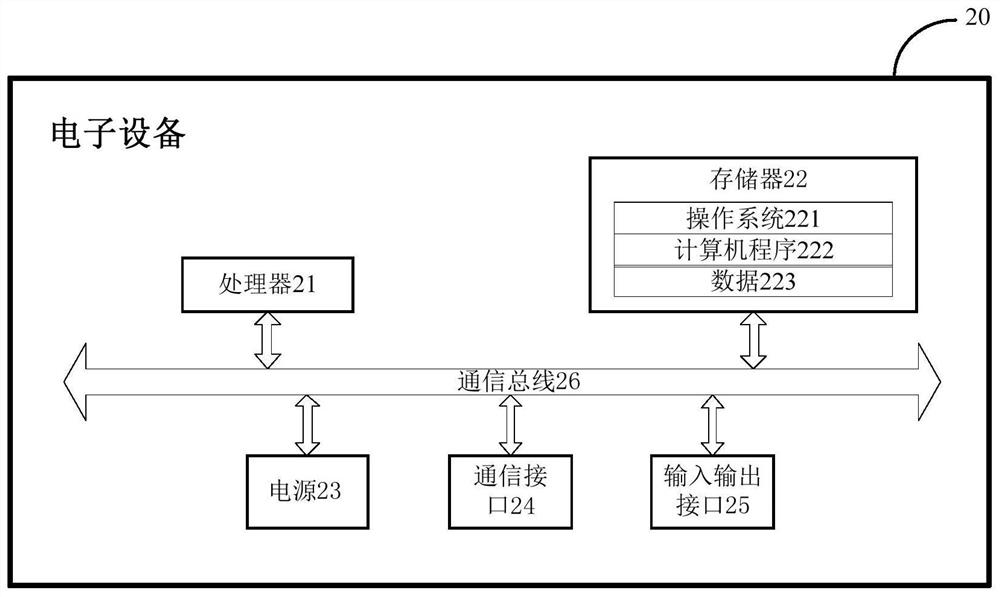

Kernel soft deadlock processing method and device, equipment and storage medium

PendingCN114003396ALower priorityImplement automatic repairProgram synchronisationNon-maskable interruptProcessing

The invention discloses a kernel soft deadlock processing method and device, equipment and a storage medium. The method comprises the following steps of distributing a watchdog thread for each CPU (Central Processing Unit), and judging whether an operating system operated by the CPU has kernel soft deadlock or not according to the watchdog thread; if the kernel soft deadlock exists, determining a target process for triggering the kernel soft deadlock, and calling non-maskable interrupt; and reducing the priority of the target process by using the non-maskable interrupt, so that the operating system processes the kernel soft deadlock by re-running the watchdog thread. Whether kernel soft deadlock occurs in the operating system or not is detected through the watchdog thread, if it is detected that kernel soft deadlock occurs, the priority of the target process triggering the kernel soft deadlock is lowered after the non-maskable interrupt is called, and therefore the operating system processes the kernel soft deadlock by running the watchdog thread again. According to the method, the problem of soft deadlock of the kernel in operation of the operating system is automatically repaired, and the use experience of a user is improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD