Patching method and patching device under multi-core environment

A patch and environment technology, applied in the field of patch methods and patch devices in a multi-core environment, can solve problems such as software logic confusion and errors, and achieve the effect of low synchronization time overhead and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

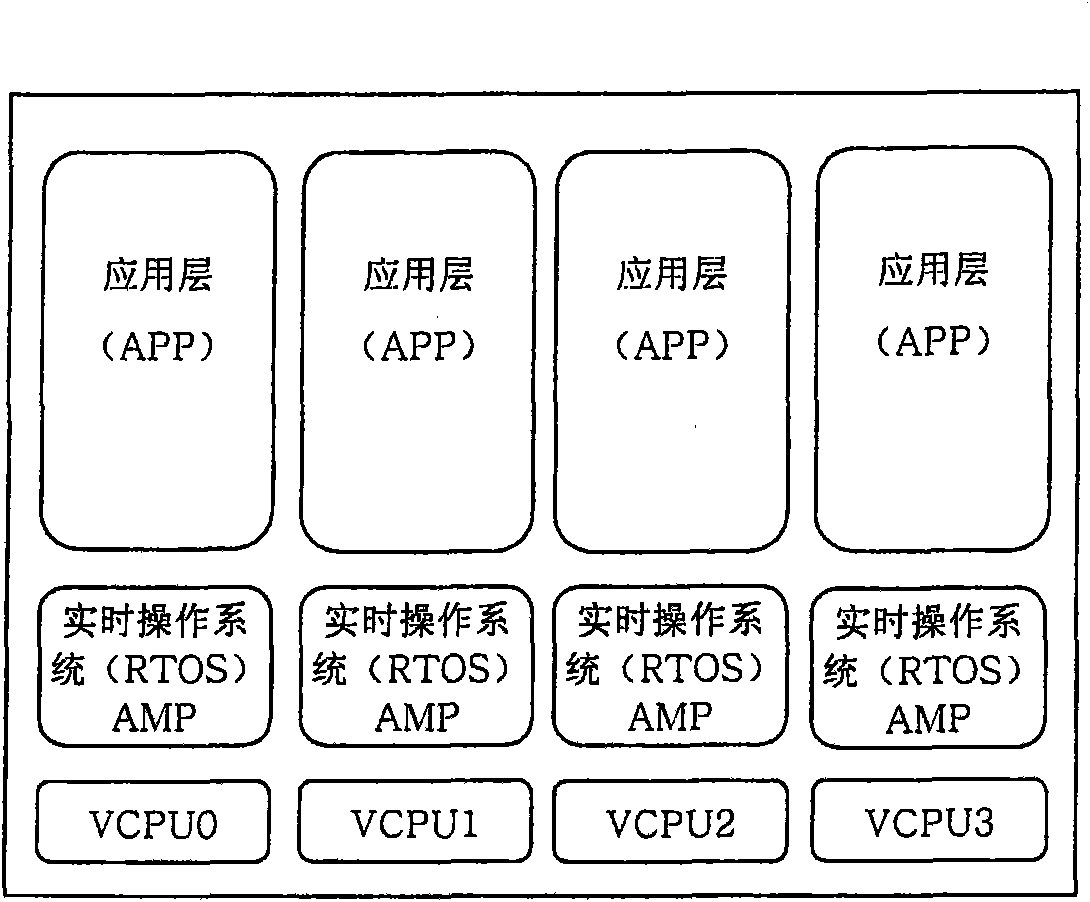

[0026] An embodiment of the present invention provides a patch device in a multi-core environment. Wherein, the patch device of the embodiment of the present invention is applied to a multi-core AMP system, figure 1 It is a logical schematic diagram of a multi-core AMP system in this embodiment, such as figure 1 As shown, from the perspective of the logic layer, the bottom layer is a multi-core processor hardware platform, including multiple VCPUs, such as VCPU0, VCPU1, VCPU2 and VCPU3; the middle layer is the operating system layer, and an independent operating system RTOS runs on each VCPU; Above the operating system layer is the APP application layer.

[0027] The VCPU of this embodiment is divided into a management VCPU and a target VCPU according to different functions. In this embodiment, the management VCPU is VCPU0, and other VCPUs (VCPU1, VCPU2, and VCPU3) of the shared code segment are the target VCPUs, and there are multiple VCPUs with the shared code segment. The...

Embodiment 2

[0059] This embodiment provides a patch method in a multi-core environment, the architecture of the multi-core environment can be found in figure 1 , the patching method in this embodiment includes a patching method applied to a patching device of a management VCPU and a patching method applied to a patching device of a target VCPU. The method of this embodiment realizes the synchronous activation of the patch on the target VCPU through the inter-core synchronization mechanism, and realizes the effective patch of the target VCPU in exception handling.

[0060] Figure 5 It is a schematic flow chart of a patch method in a multi-core environment in an embodiment of the present invention. It should be noted that the patch method in this embodiment can be applied to a patch device for managing VCPUs, such as Figure 5 Shown:

[0061] Step S501, sending an inter-core non-maskable interrupt to each target virtual CPU in the shared code segment target virtual CPU group, so that the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More