An IO extension architecture method based on standard pcie uplink port

A technology for extending the architecture and PCI devices, which is applied in the field of IO expansion architecture based on standard PCIe uplink ports, and can solve the problems that Shenwei processors cannot

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

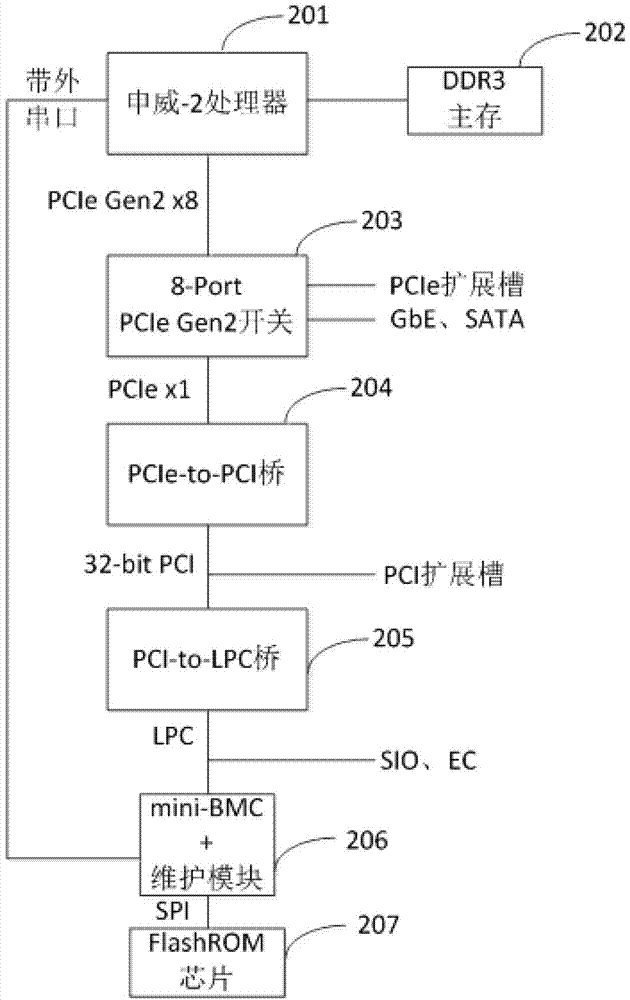

[0059] refer to Figure 5 As shown, one embodiment of the system startup method of the present invention includes: mini-BMC self-test 401, system configuration saving 402, initial configuration of Shenwei processor 403, initialization of Shenwei processor 404, BIOS path construction 405, fetching BIOS and executing 406.

[0060] Each step will be specifically described below.

[0061] mini-BMC self-test 401: After power-on (including standby power), it is the first to execute, including the self-test of the mini-BMC's own operating environment and the detection of system configuration. When the system is ready to start, perform the next step. System configuration save 402;

[0062] System configuration saving 402: mini-BMC saves some information needed for system start-up in Flash ROM, and then allows the maintenance module to perform the next step based on the information, and initially configures the Shenwei processor 403;

[0063] Initial configuration of Shenwei process...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More