System and method for improving bus access error based on RISC-V architecture

A RISC-V and bus technology, applied in the field of low-power kernel interrupt and exception handling, can solve problems such as uncontrollable programs and achieve the effect of increasing flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

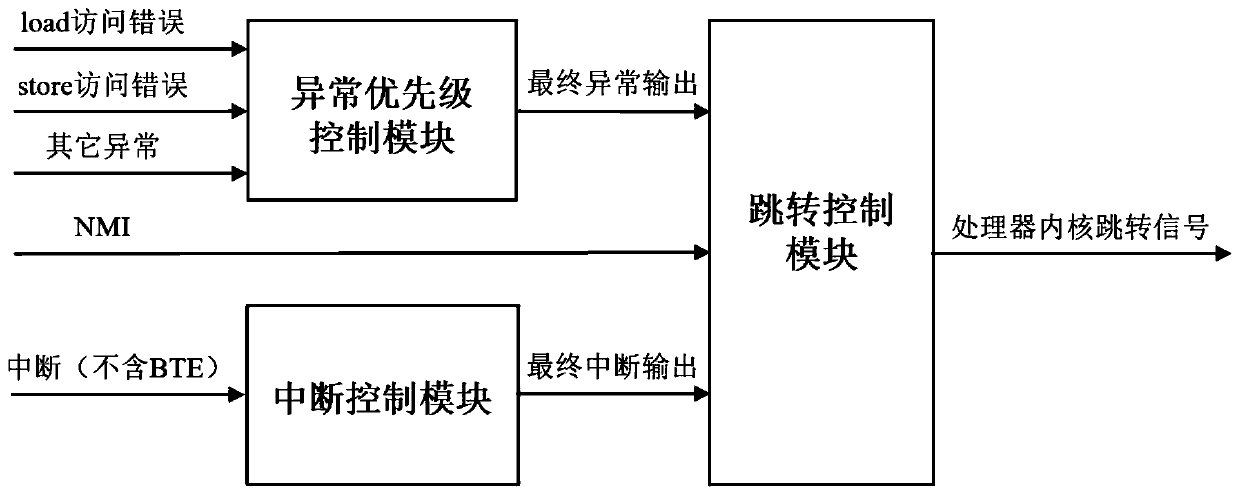

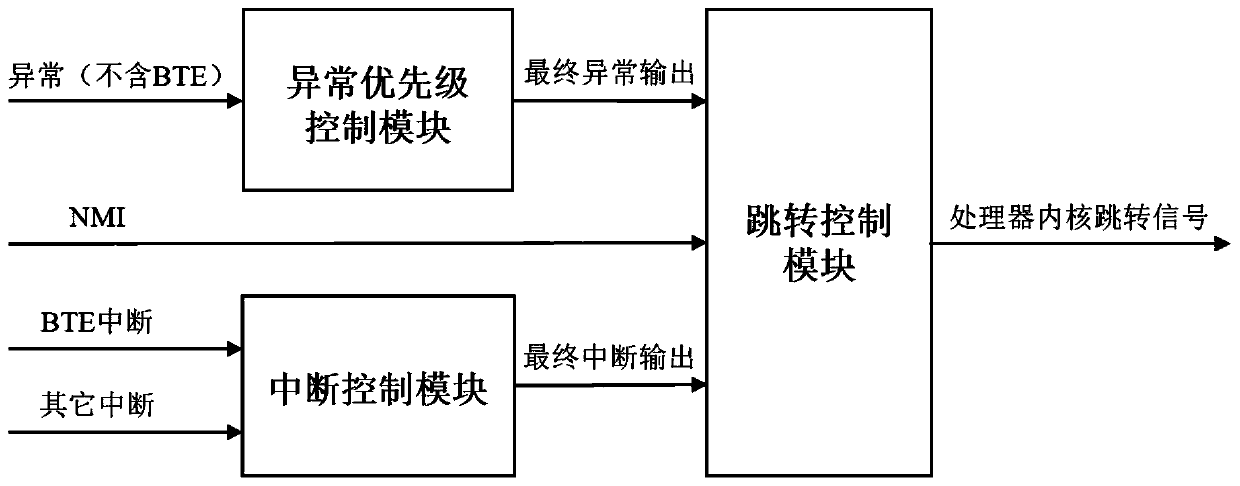

[0042] Such as figure 2 As shown, the present invention provides a system and method for improving bus access errors based on the RISC-V architecture, which is compared with the architecture defined by RISC-V (such as figure 1 ), change the bus access error (including load access error and store access error) from reporting exception to reporting interruption. The system includes: an abnormal priority control module, an interrupt control module, and a jump control module, wherein:

[0043] The exception priority control module is used to prioritize all exception types. The smaller the value of the corresponding exception code (Exception Code), the higher the priority. The exception type with the highest current priority is selected and output to the jump Control module

[0044] The interrupt control module is used for unified management of bus access error (BTE) and other interrupt sources, selects the interrupt source with the highest current priority and outputs it to the jump ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More