Static zero-consumption power-on resetting circuit

A reset circuit and electric reset technology, which is applied in the field of CMOS static zero-power power-on reset circuit and low-power SoC chip, can solve the problems of outstanding power consumption, current consumption, and increased power consumption of the circuit system to achieve chip occupation Small area, low static power consumption, simple and novel structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

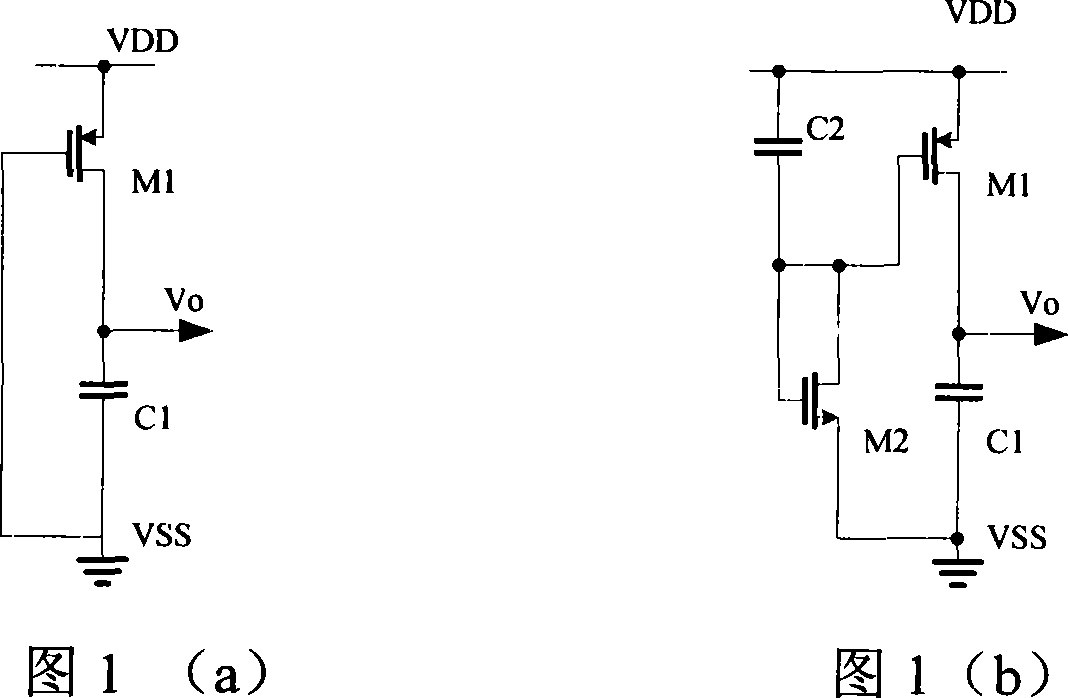

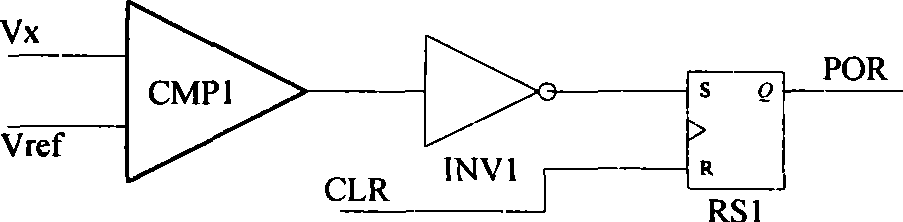

Method used

Image

Examples

Embodiment Construction

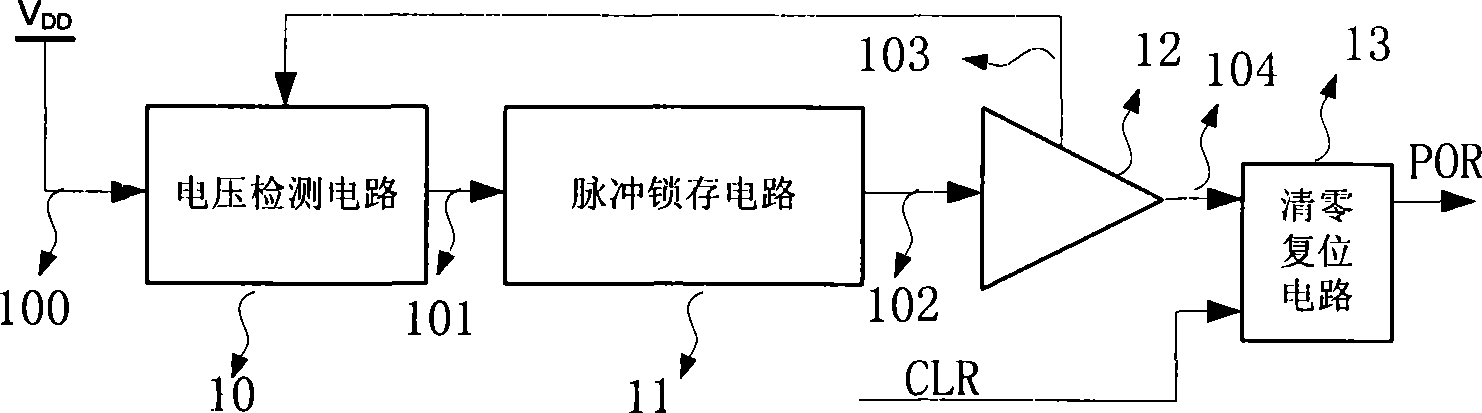

[0025] Below in conjunction with accompanying drawing and example the present invention is described in further detail.

[0026] see image 3 As shown, the static zero-power power-on reset circuit provided by the present invention includes a voltage detection circuit 10 , a pulse latch circuit 11 , an output buffer circuit 12 and a reset circuit 13 . One input terminal 100 of the voltage detection circuit 10 is connected to the external power supply VDD, the other input terminal 103 is connected to the enable output terminal of the output buffer circuit 12 , and the output terminal 101 is connected to the input terminal of the pulse latch circuit 11 . The output terminal 102 of the pulse latch circuit 11 is connected to the input terminal of the output buffer circuit 12, and the two output terminals of the output buffer circuit 12 are respectively connected to the input terminal 104 of the reset reset circuit 13 and the input terminal 103 of the voltage detection circuit 10. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More