Patents

Literature

168results about How to "Less cost" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

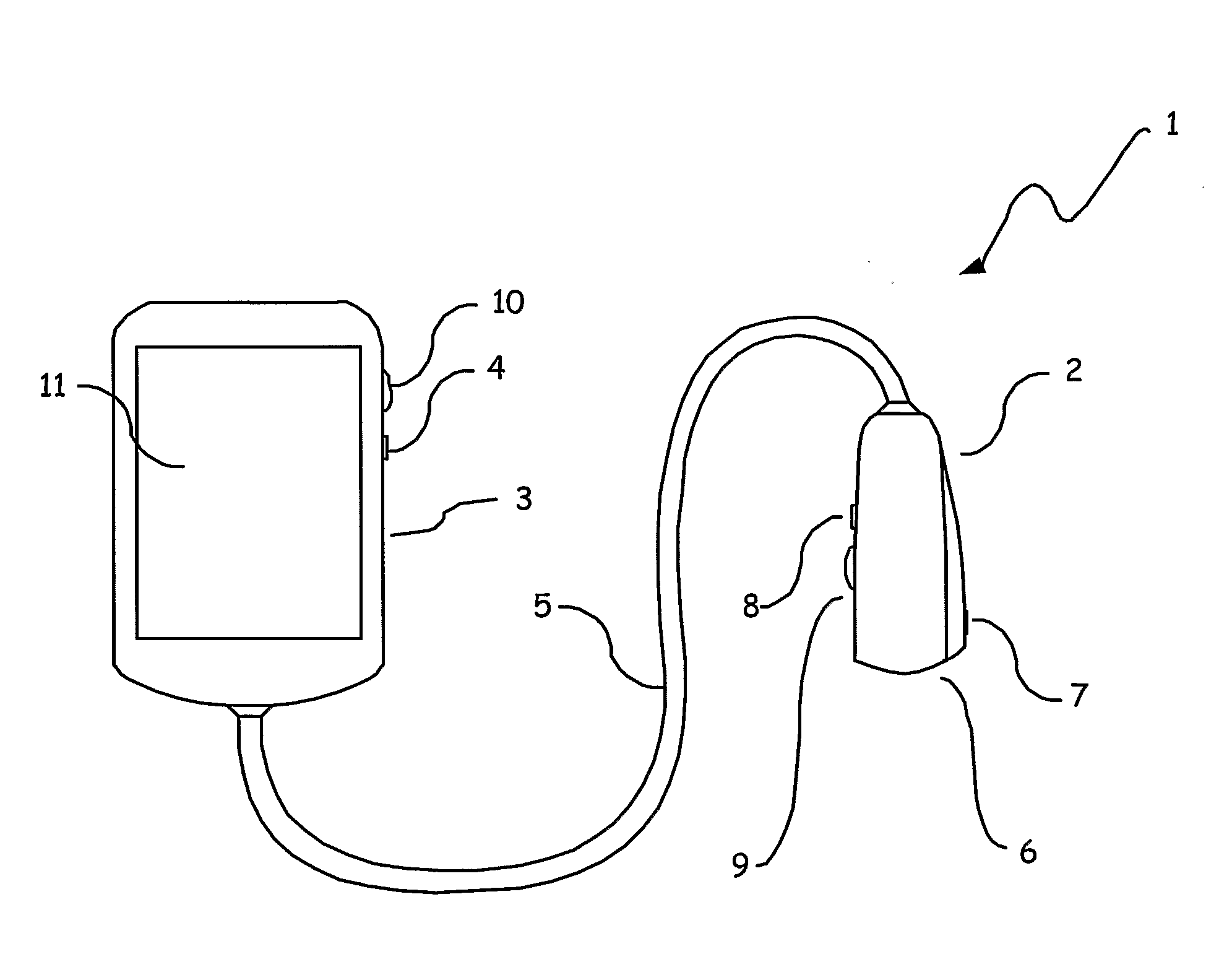

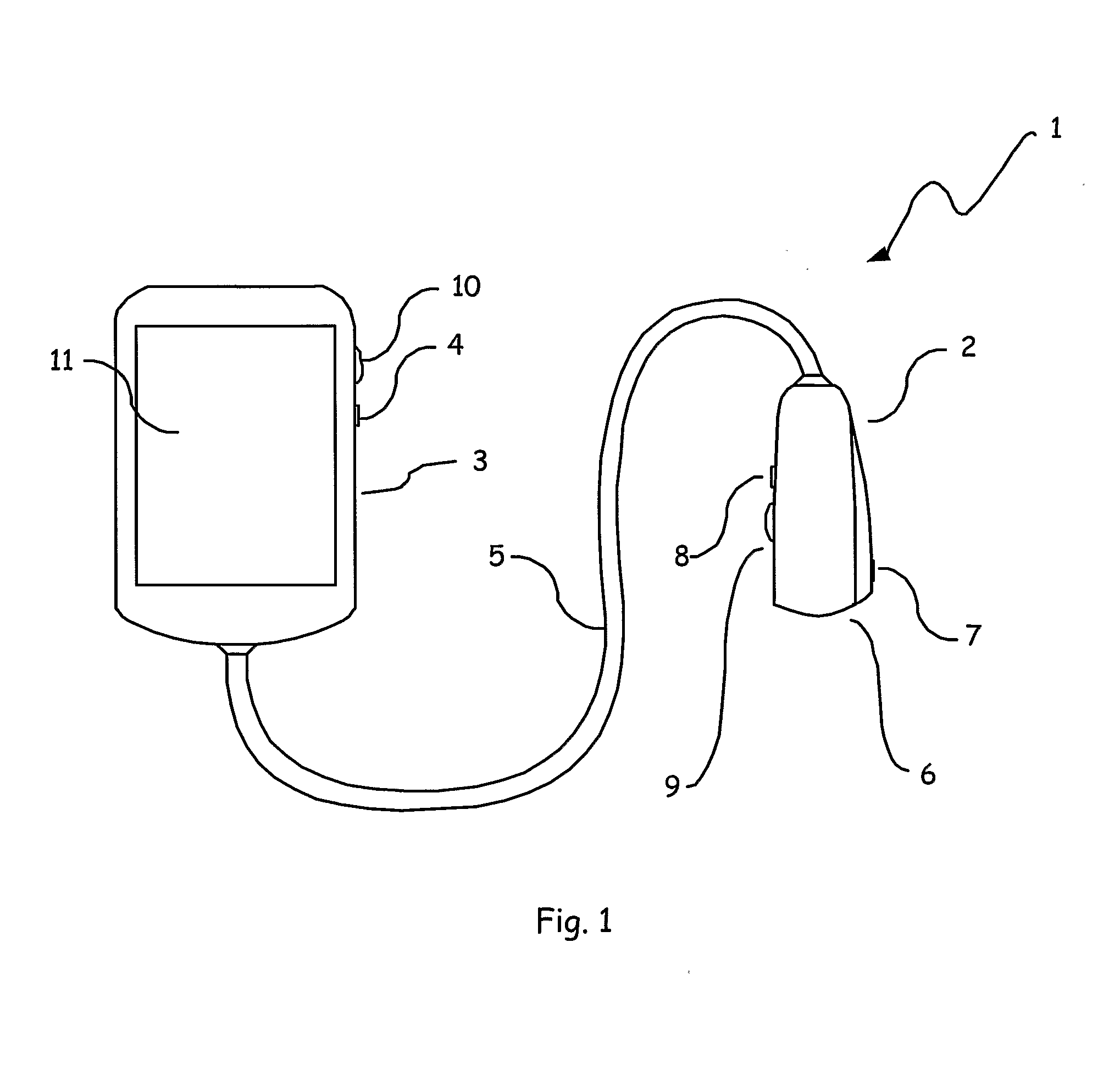

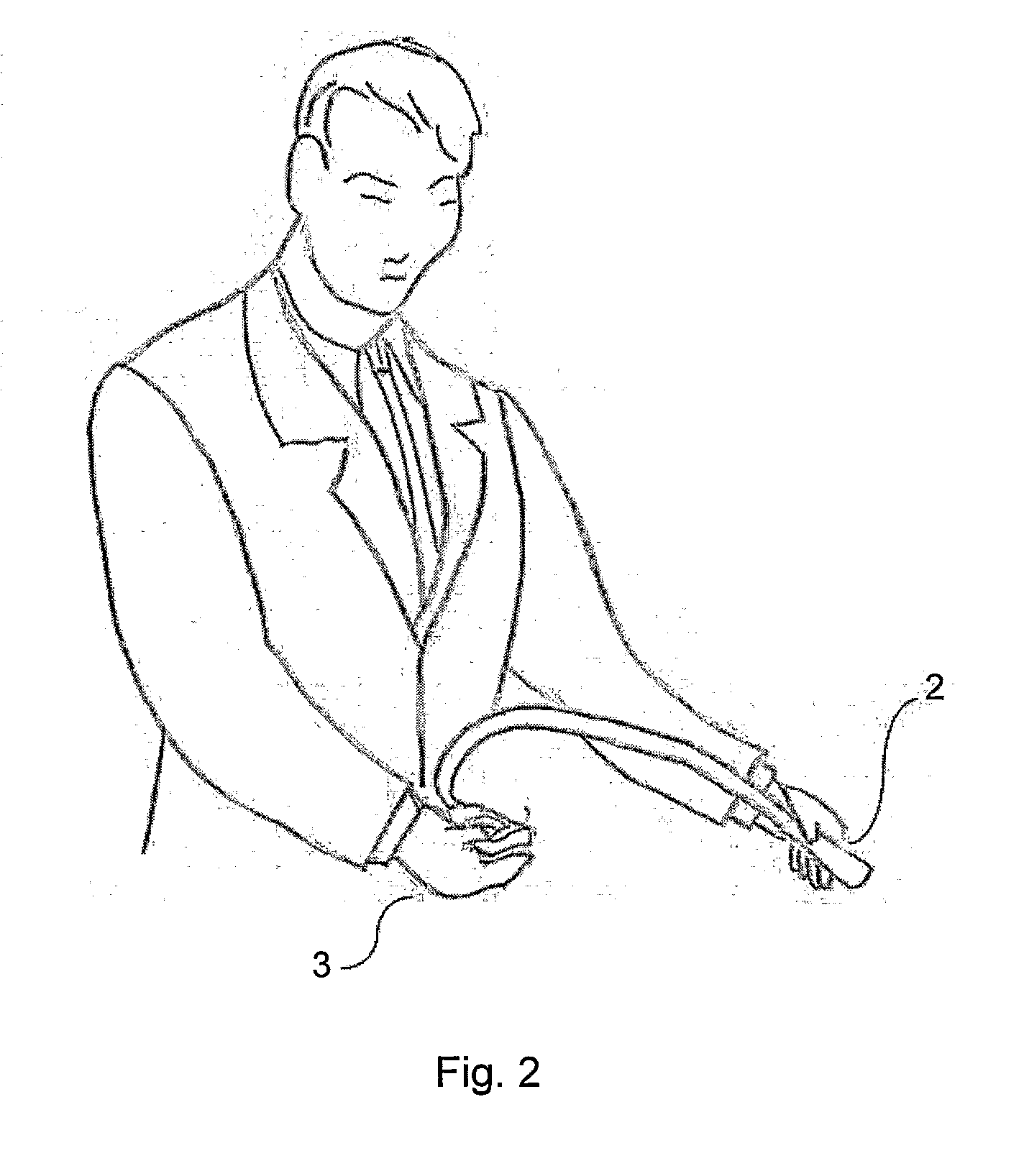

Ultrasound Measurement System and Method

InactiveUS20080281206A1Easy to optimizeImprove convenienceInfrasonic diagnosticsTomographyUltrasonic sensorTransducer

An ultrasound measurement system including a handheld display and processing means, an ultrasound transducer, a processing means of a substantially similar weight to the handheld display and processing means, and a transmission cable interconnecting the handheld display and processing means with the ultrasound transducer and processing means, the cable being of sufficient length to provide a means to mechanically locate the system around the neck of a user.

Owner:SIGNOSTICS LTD

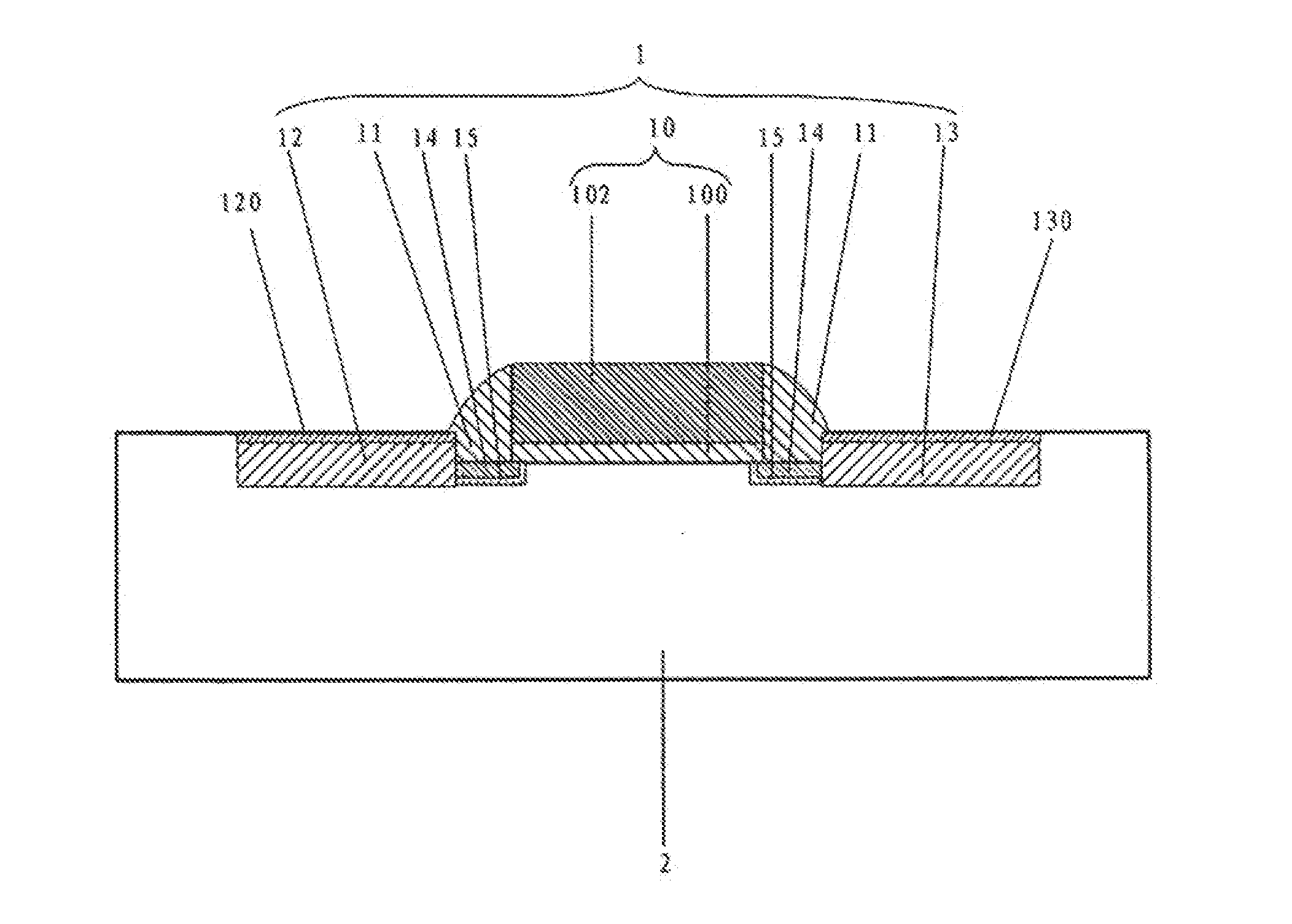

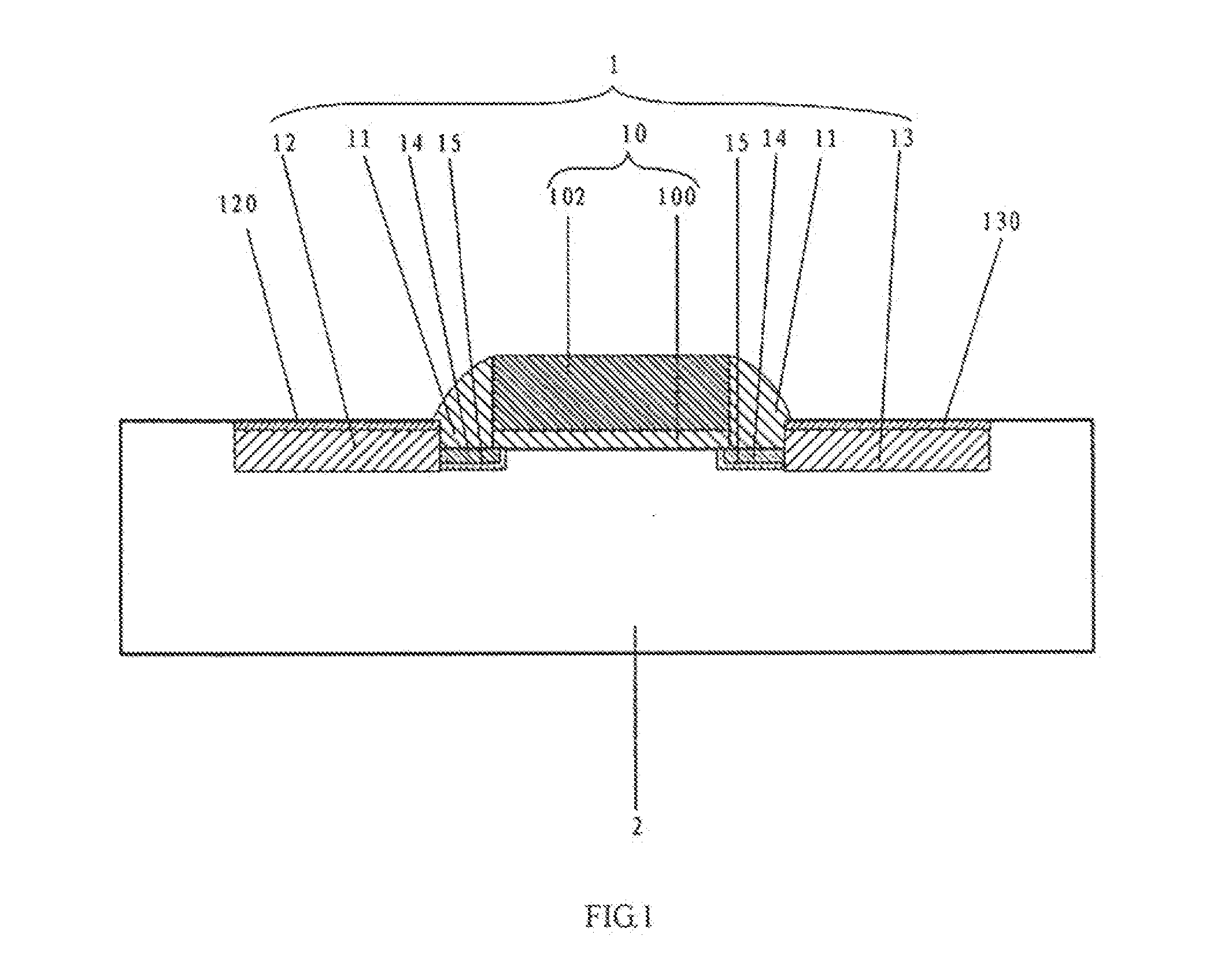

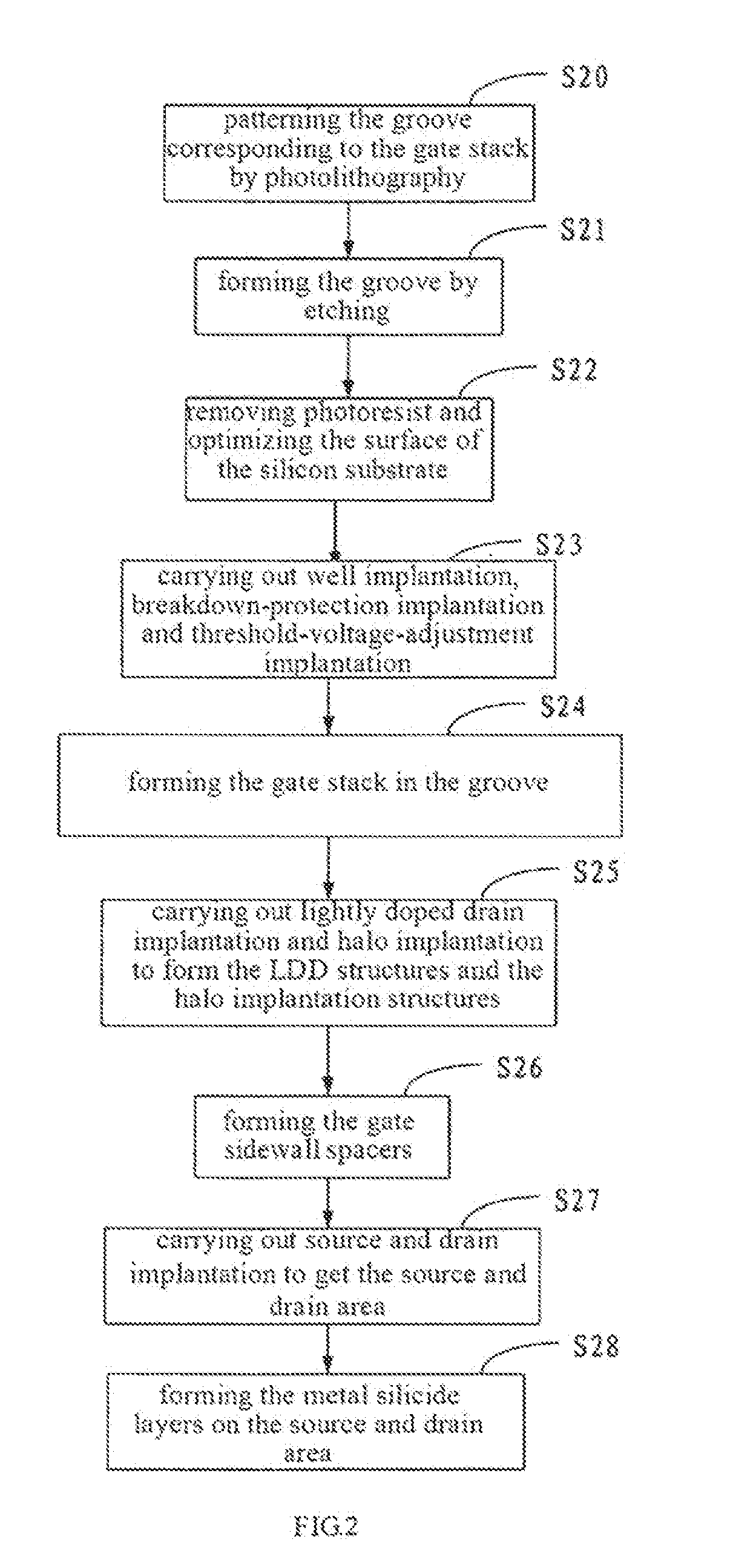

Mos transistor for reducing short-channel effects and its production

ActiveUS20110059588A1Suppression of short channel effectsReduce impactSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideGate stack

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

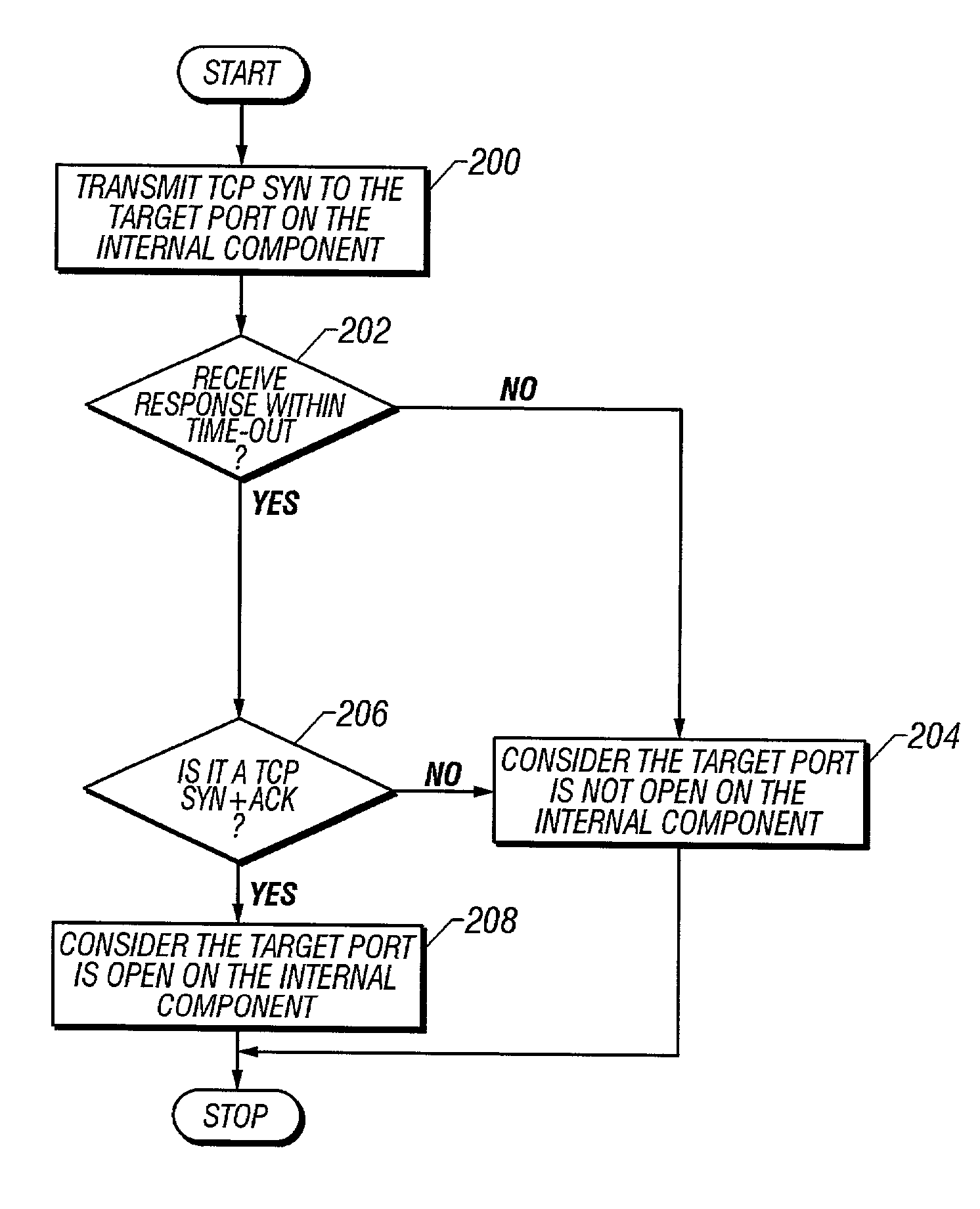

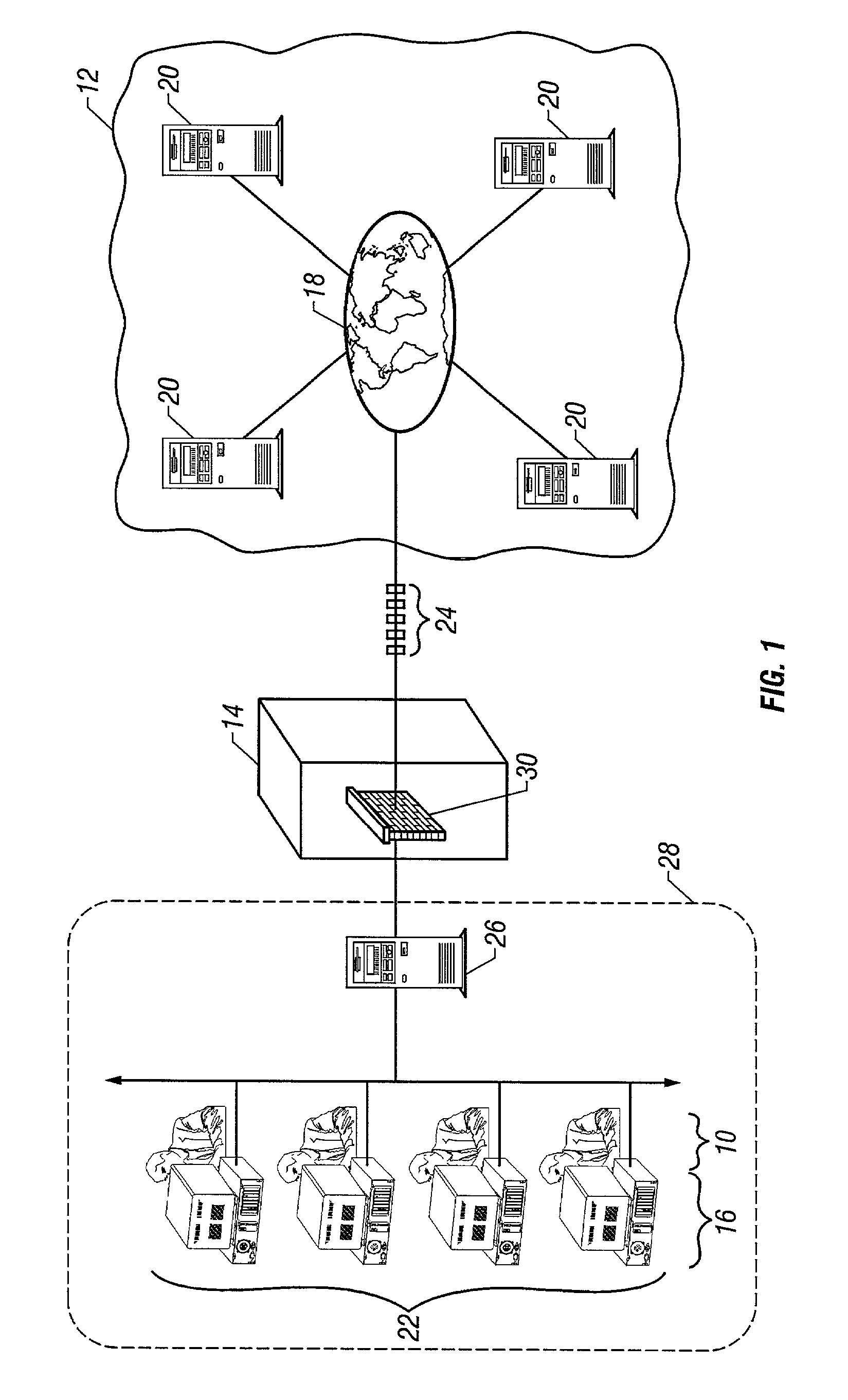

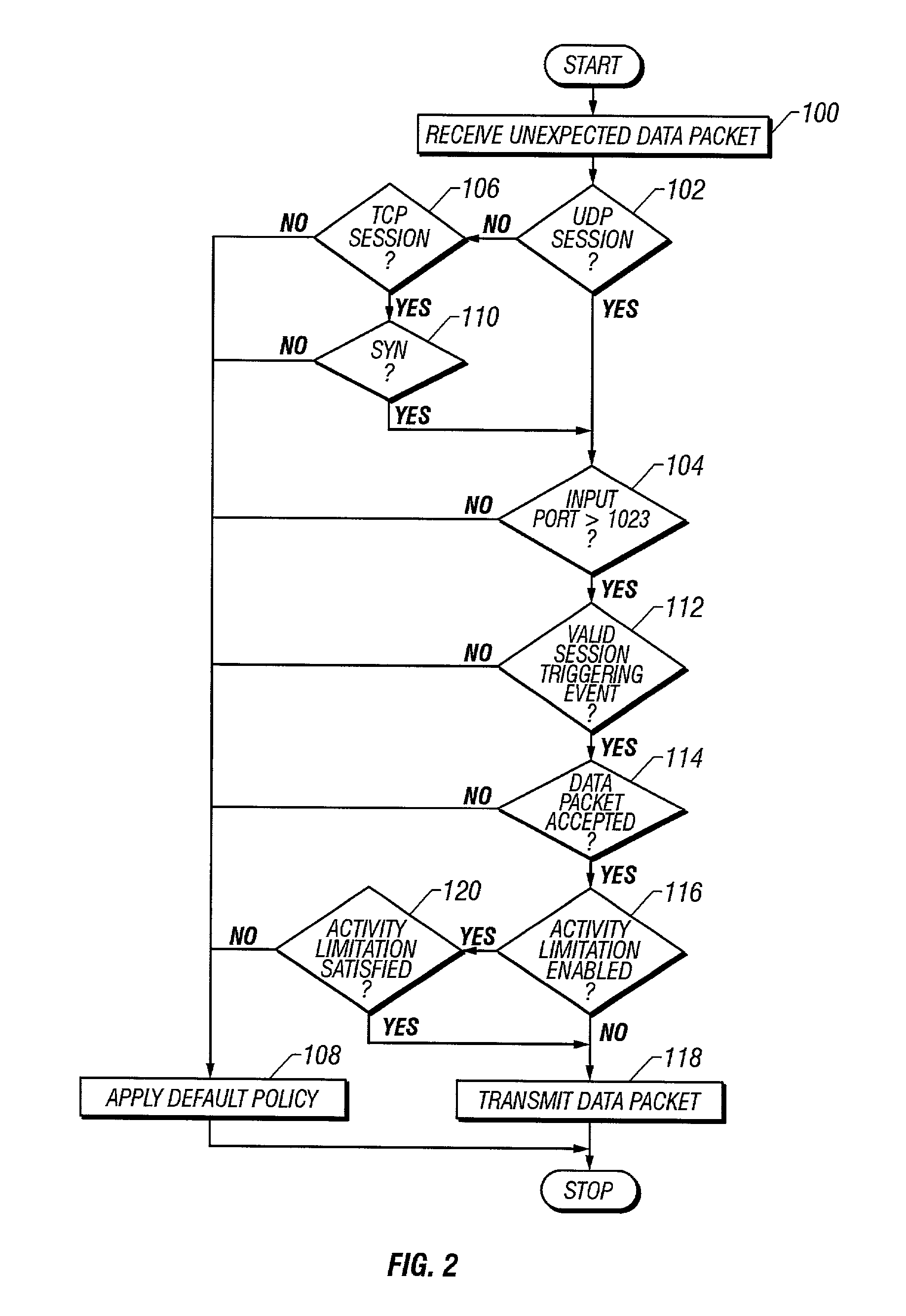

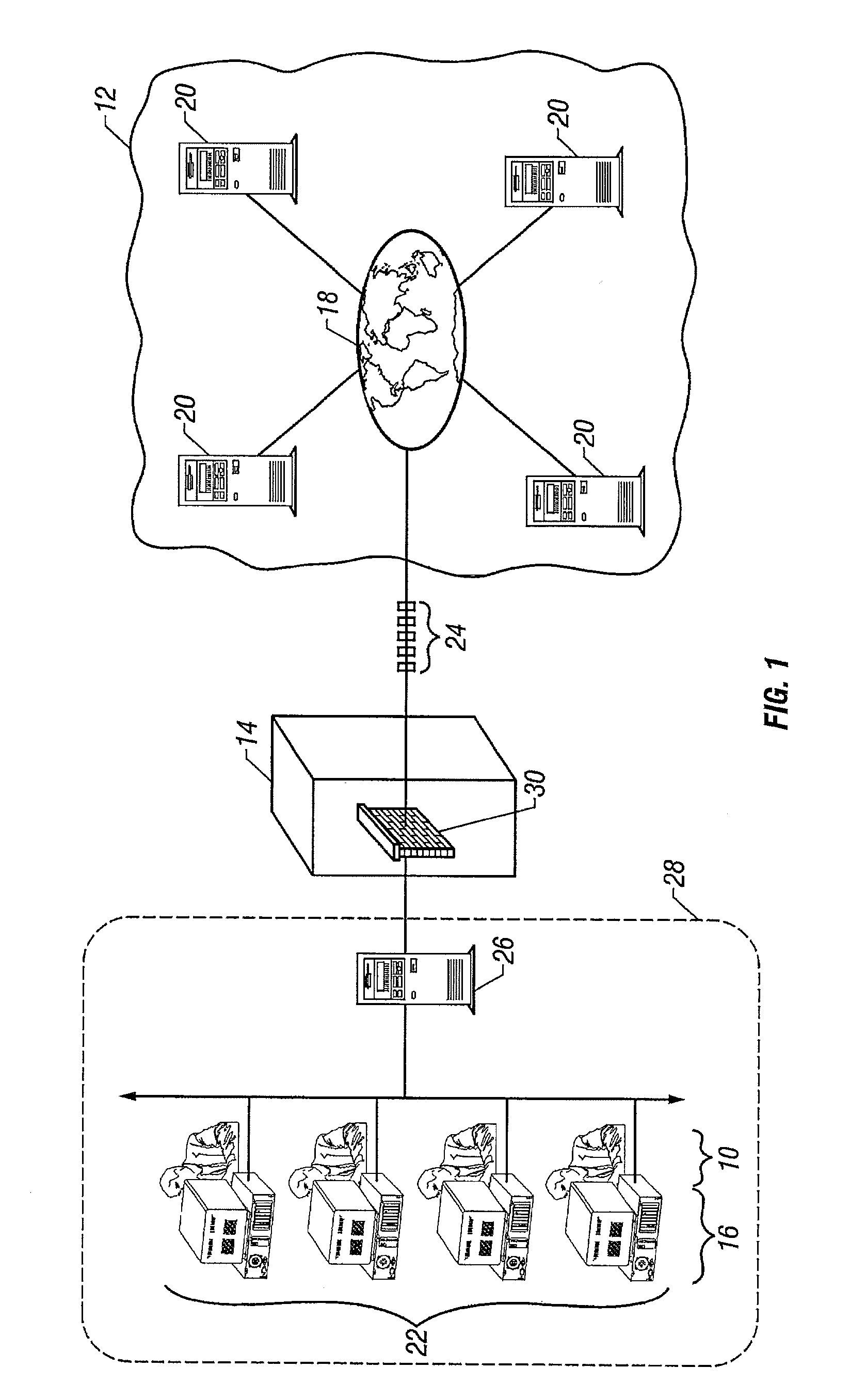

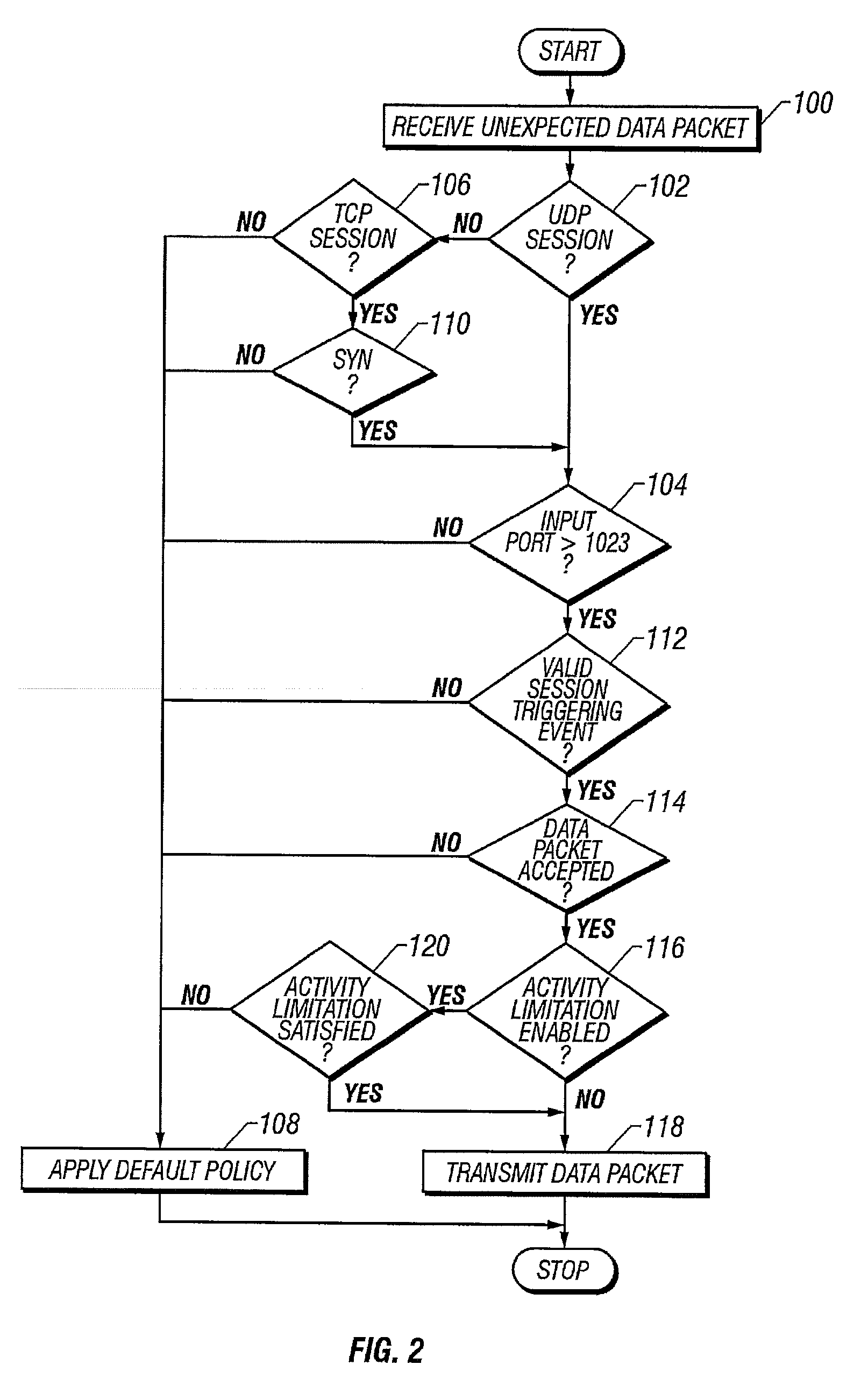

System and method for managing dynamic network sessions

ActiveUS7370353B2Well throughputLess hardware cost and memory requirementDigital data processing detailsMultiple digital computer combinationsClient-sideNetwork component

For an Internet Access Gateway operative between an area network and a public network, managing dynamic network sessions therebetween whereby a primary server on the public network in a primary session with a client of the area network initiates an additional session with an additional server on the public network, for which an unexpected data packet received at the gateway from the additional server is associated with the primary session, and accordingly allowed access to the area network through the gateway, provided the gateway received the data packet at an input port exceeding 1023, the additional session comprises a pre-defined Session Triggering Event, and at least one internal network component of the area network indicates willingness to receive the data packet. Wherefore, a preferred Application Level Gateway is thereby provided for firewall and NAT implementations to enhance network security.

Owner:ASHLEY LAURENT INC +1

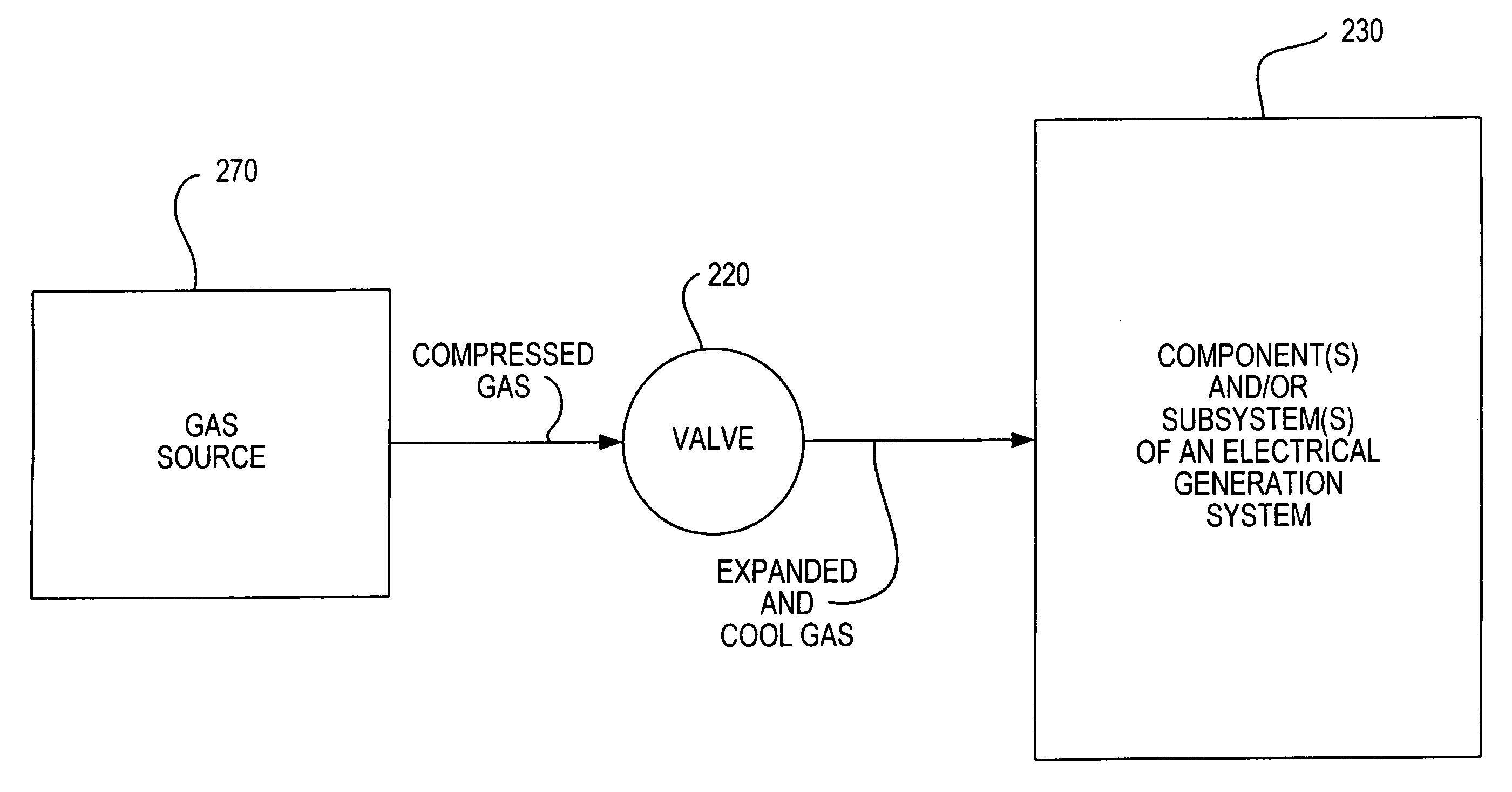

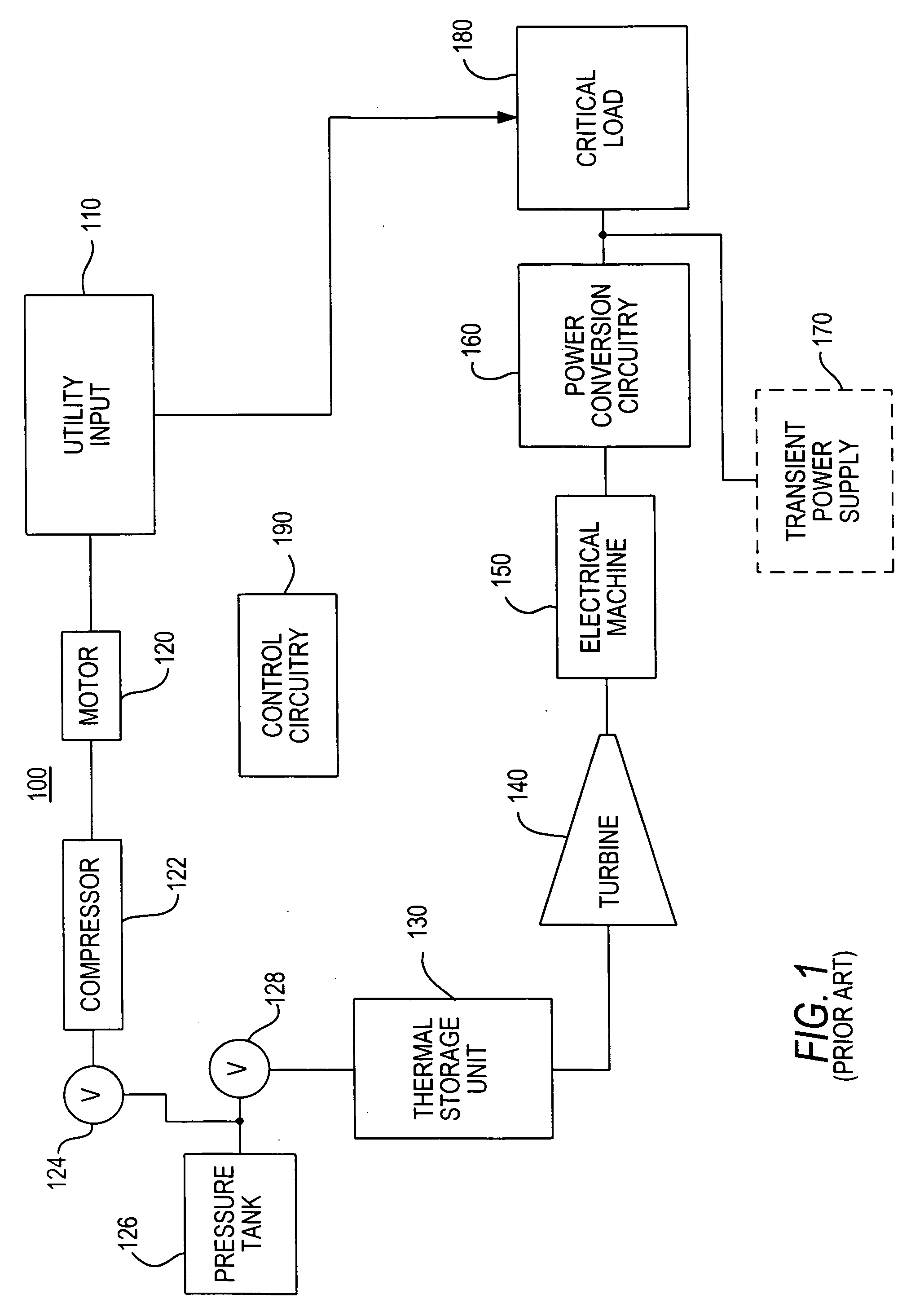

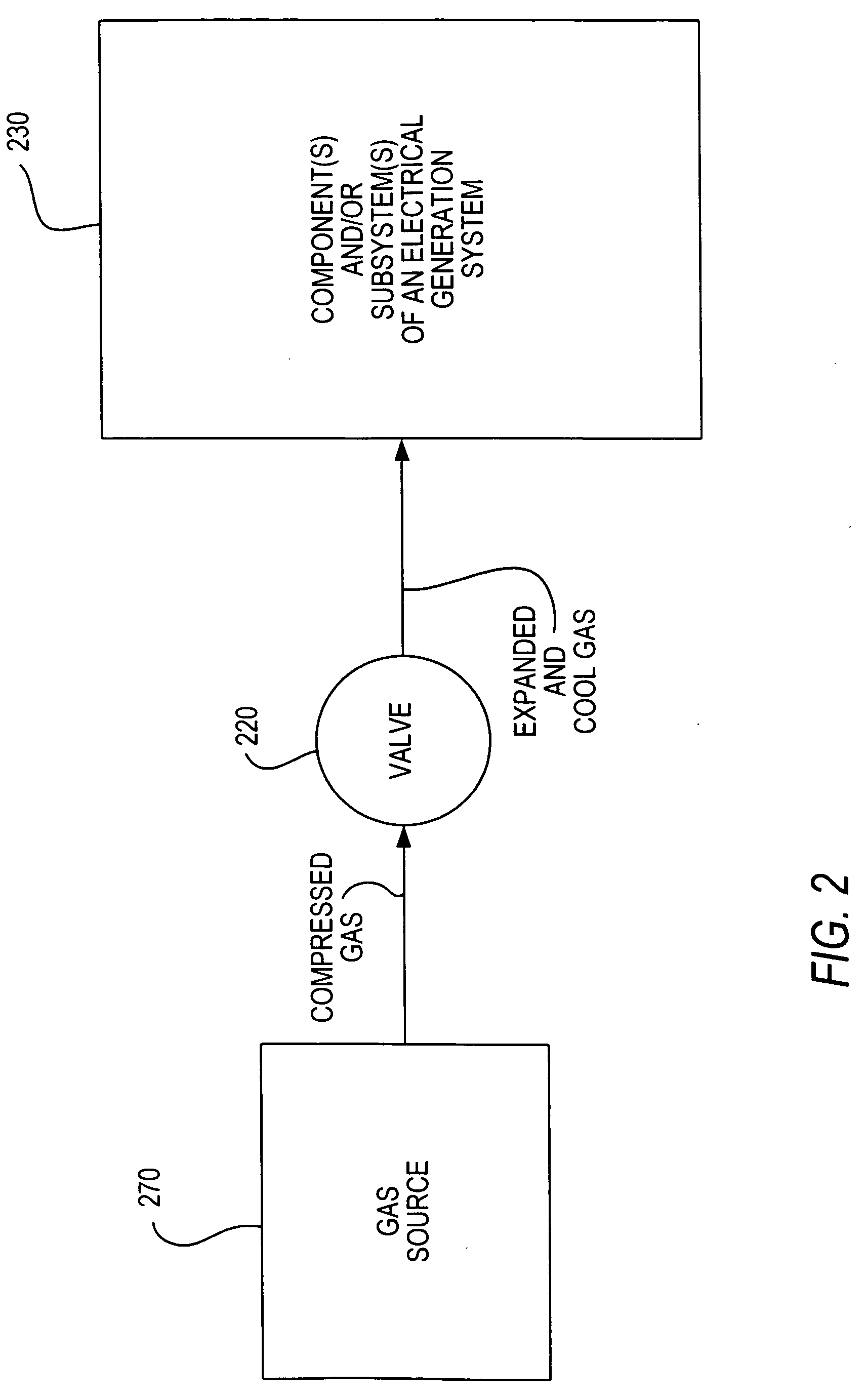

Systems and methods for providing cooling in compressed air storage power supply systems

InactiveUS20060059937A1Low operating temperatureLess costElectrical storage systemDomestic cooling apparatusElectric generatorEngineering

A system and method for cooling electrical machines (e.g., generators), sub-systems (e.g., power electronics), and components (e.g., bearings) in an electrical generation system such as a compressed air storage (CAS) energy system or a thermal and compressed air storage (TACAS) energy system is provided. Cooling is derived from the thermal expansion of a compressed gas, which may be the same gas used to drive a turbine-generator of CAS or TACAS energy system.

Owner:ACTIVE POWER INC

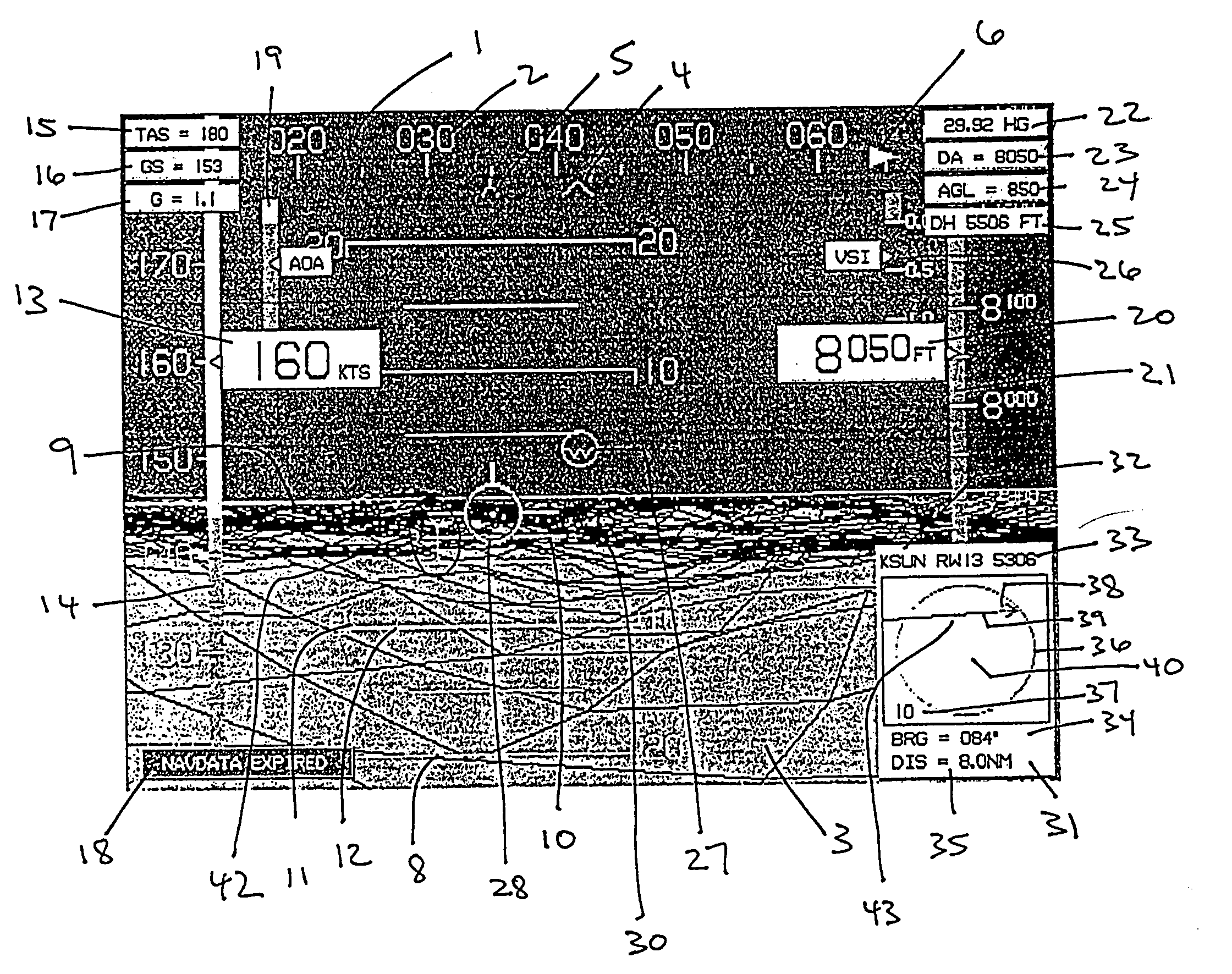

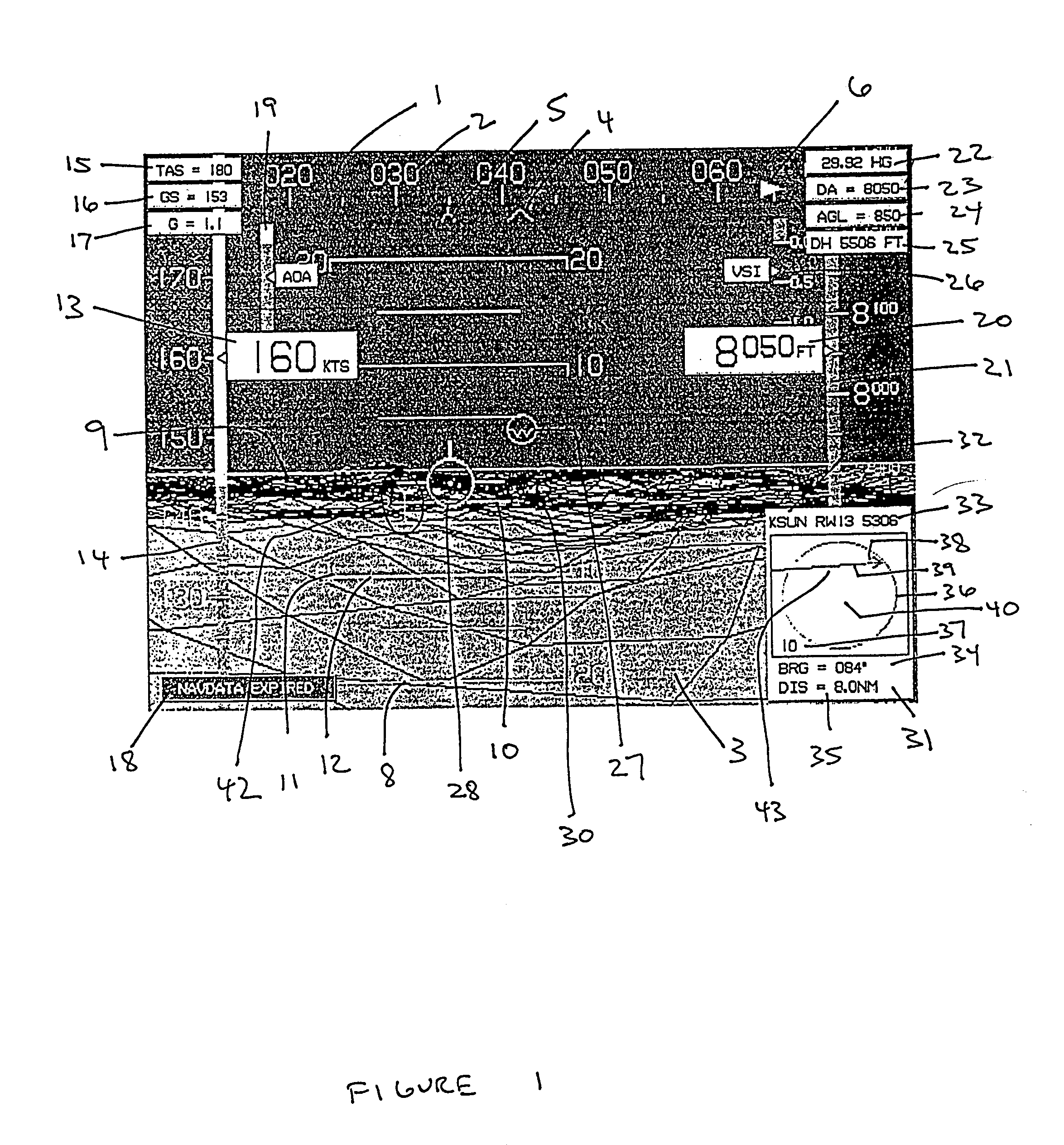

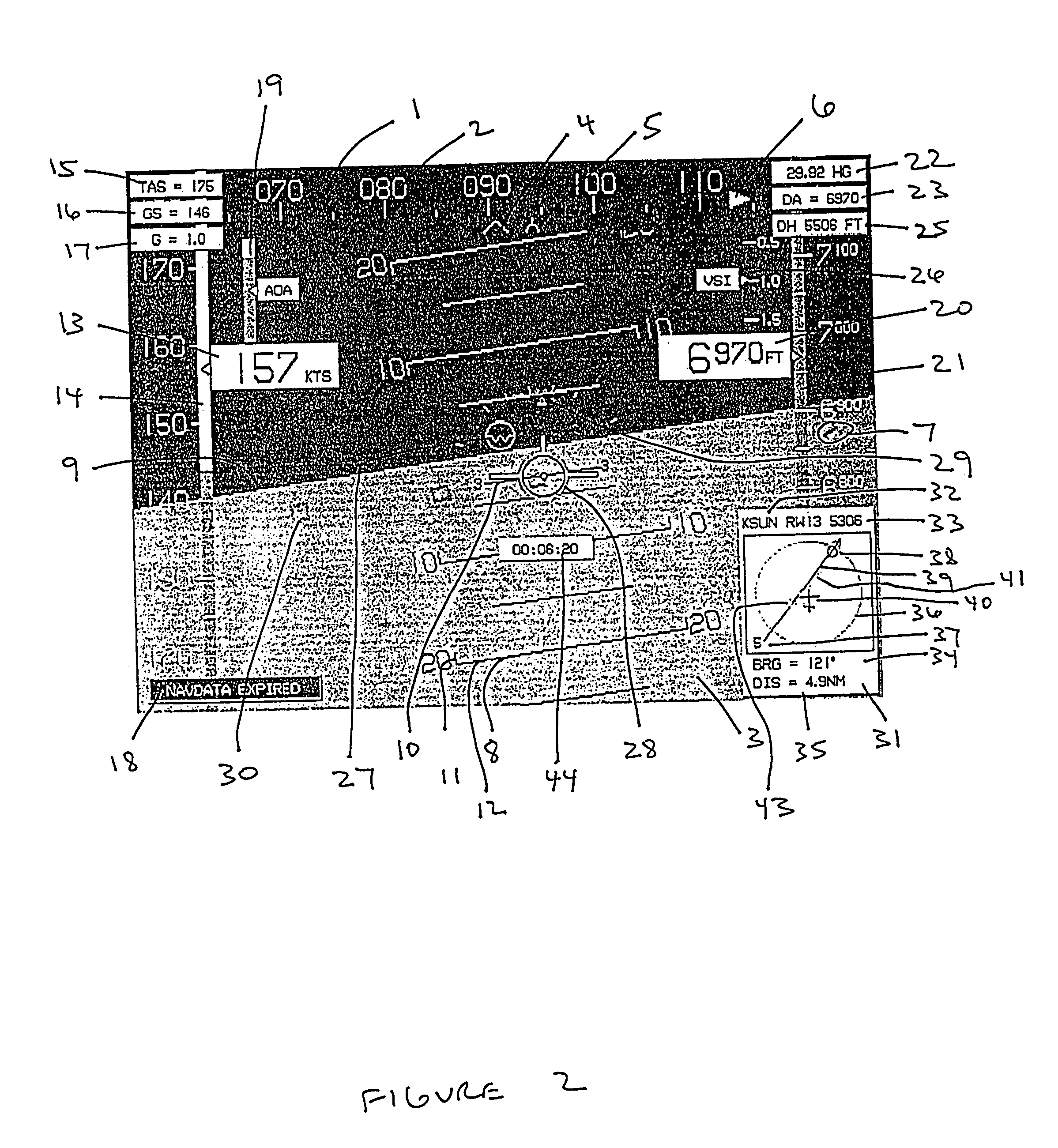

Electronic flight instrument displays

InactiveUS6985091B2Less costLess power consumptionDigital data processing detailsNavigation instrumentsDisplay devicePrimary flight display

The present invention is directed to novel primary flight displays, moving map displays and engine parameter displays for aircraft cockpits. These displays process data gathered from various aircraft sensors and, using an various electronic databases, generate intuitive symbols that aid the pilot. The present invention also uses various novel algorithms that use data gathered from inexpensive sensors to derive parameters normally requiring far more expensive sensors.

Owner:CHELTON FLIGHT SYST INC

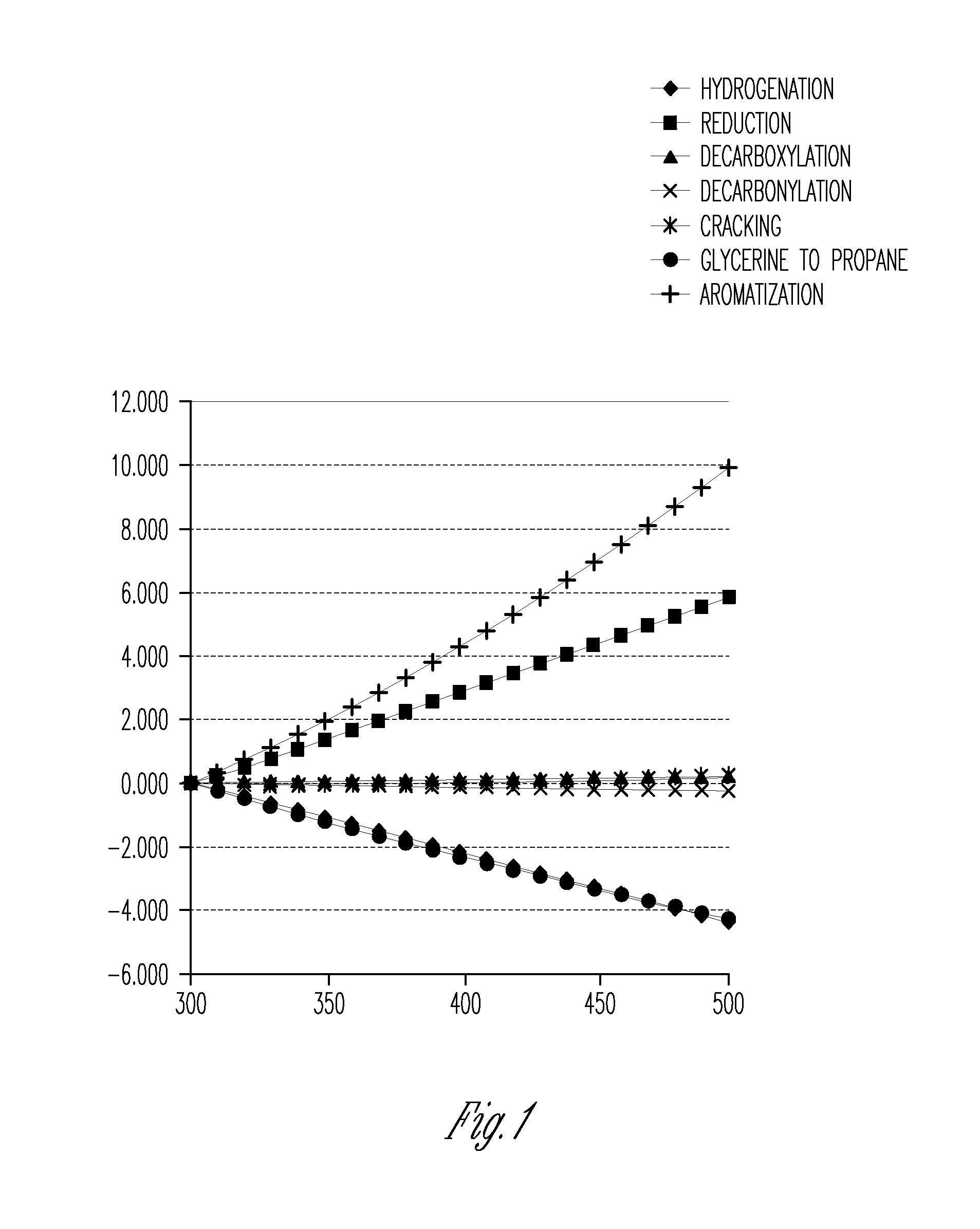

Process for the conversion of renewable oils to liquid transportation fuels

InactiveUS20120157734A1Efficient reductionEfficient processingBiofuelsSolid fuelsIsomerizationKerosene

The present invention relates to production of fuels or fuel blendstocks from renewable sources. Various embodiments provide a method of producing a hydrocarbon product by hydrotreating a feedstock including at least one of a renewable triacylglyceride (TAG), renewable free fatty acid (FFA), and renewable fatty acid C1-C5 alkyl ester (C1-C5 FAE) in the presence of a nonsulfided hydrotreating catalyst to produce a first product including hydrocarbons. In some examples, the first product can be subjected to further chemical transformations such as aromatization, cracking, or isomerization to produce a second product including hydrocarbons. In various embodiments, the first or second hydrocarbon product with minimal or substantially no further processing can be suitable as a liquid transportation fuel or fuel blendstock, including fuels such as gasoline, naptha, kerosene, jet fuel, and diesel fuels.

Owner:ENERGY & ENVIRONMENTAL RES CENT FOUNDATIO

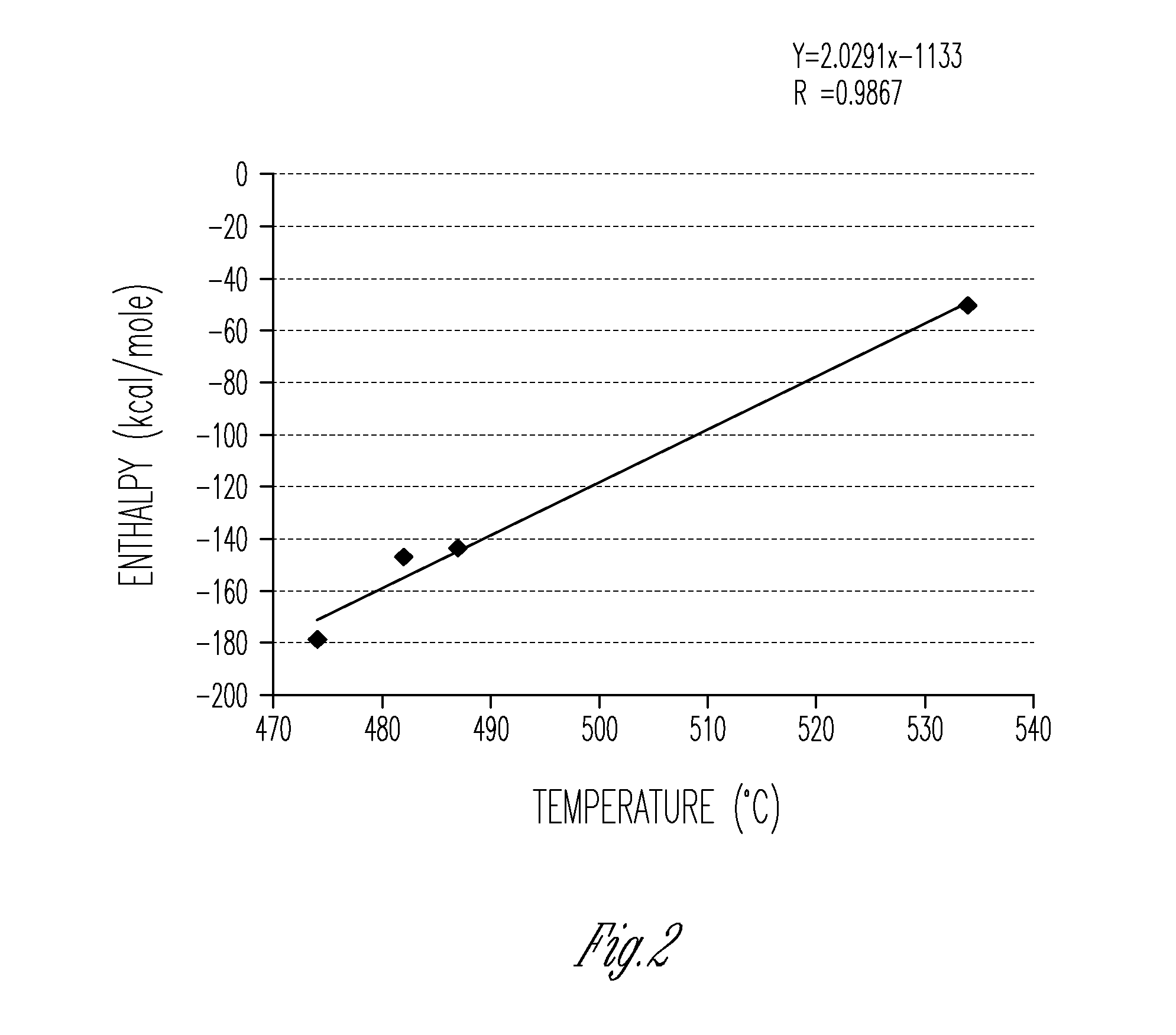

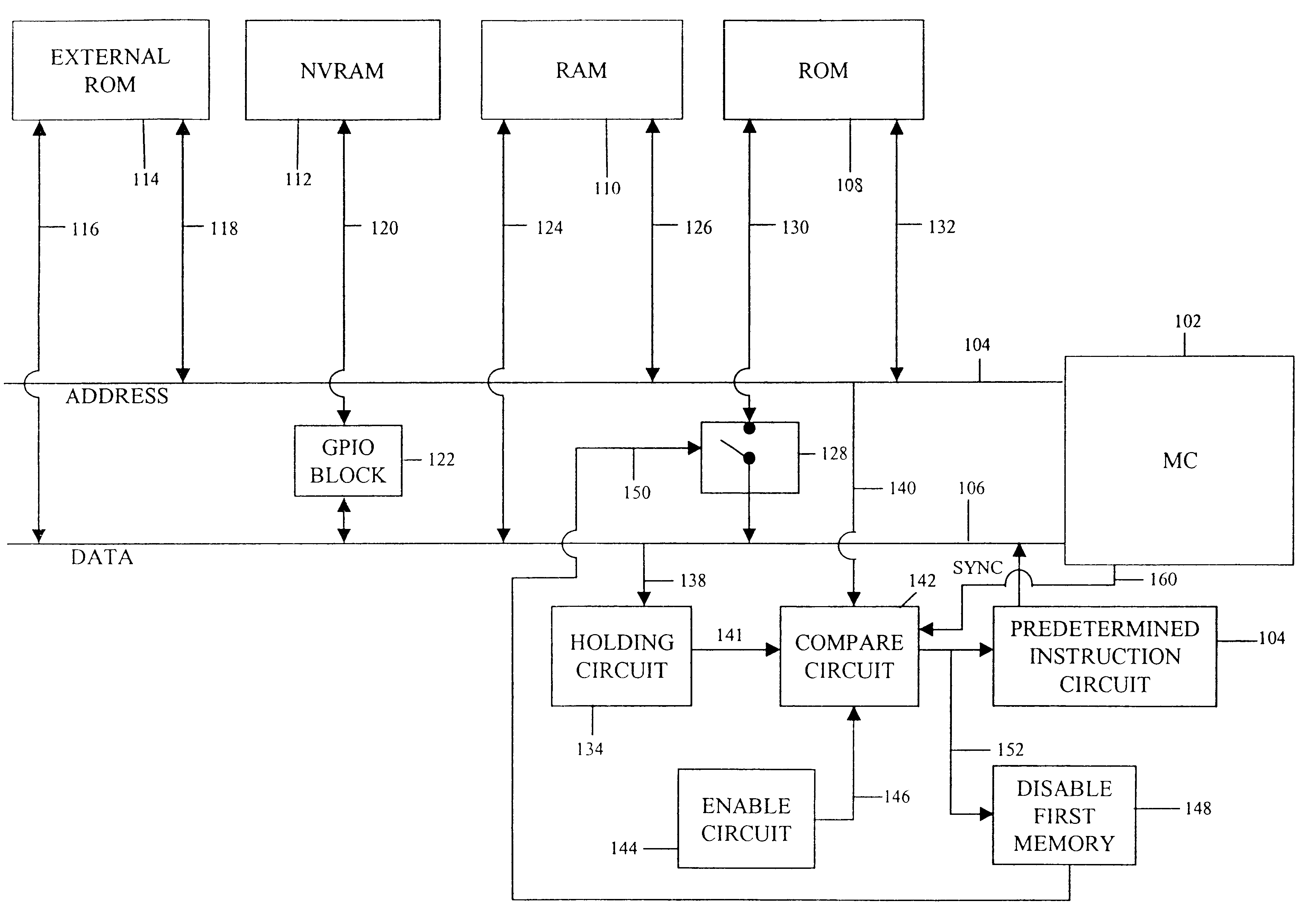

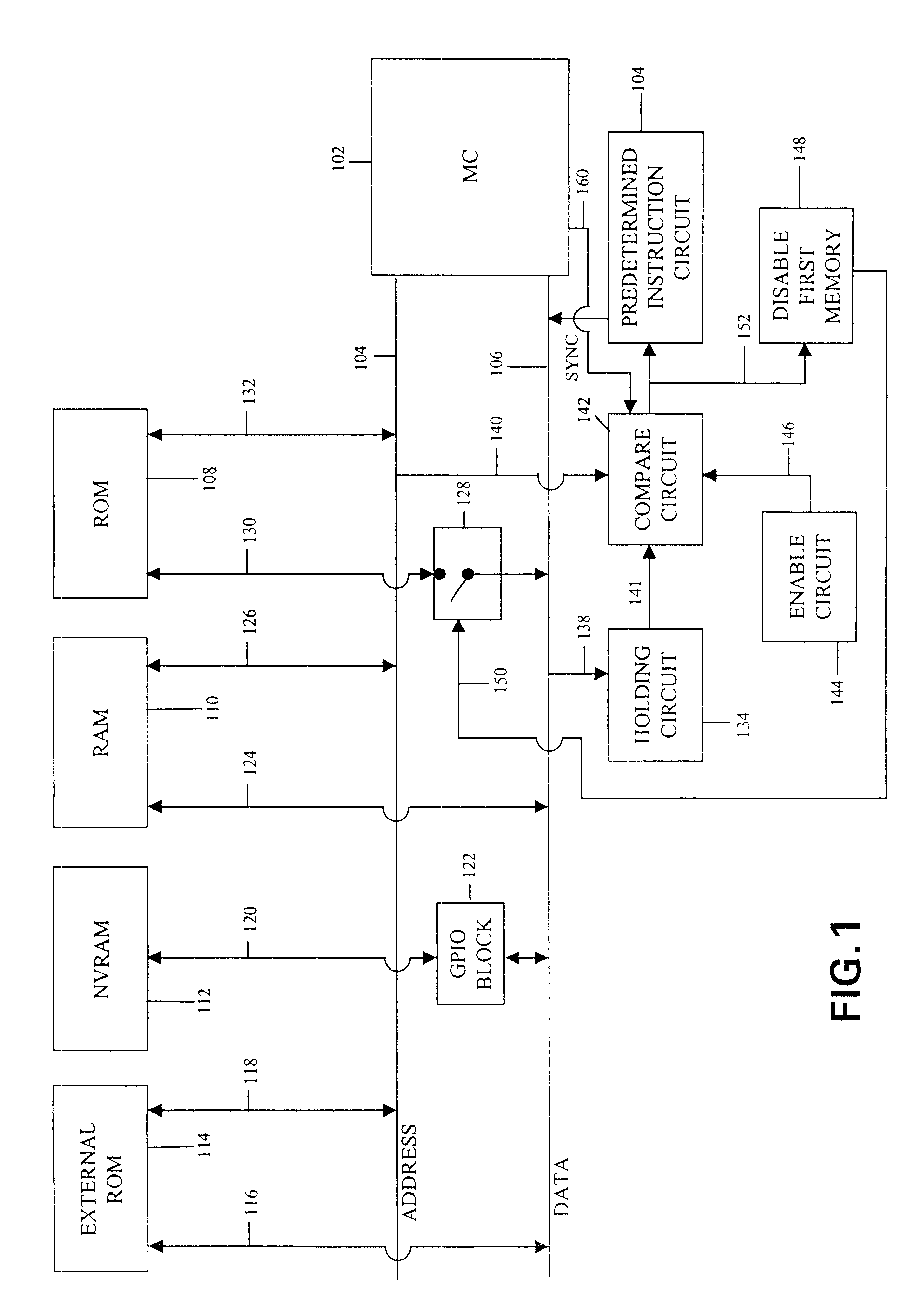

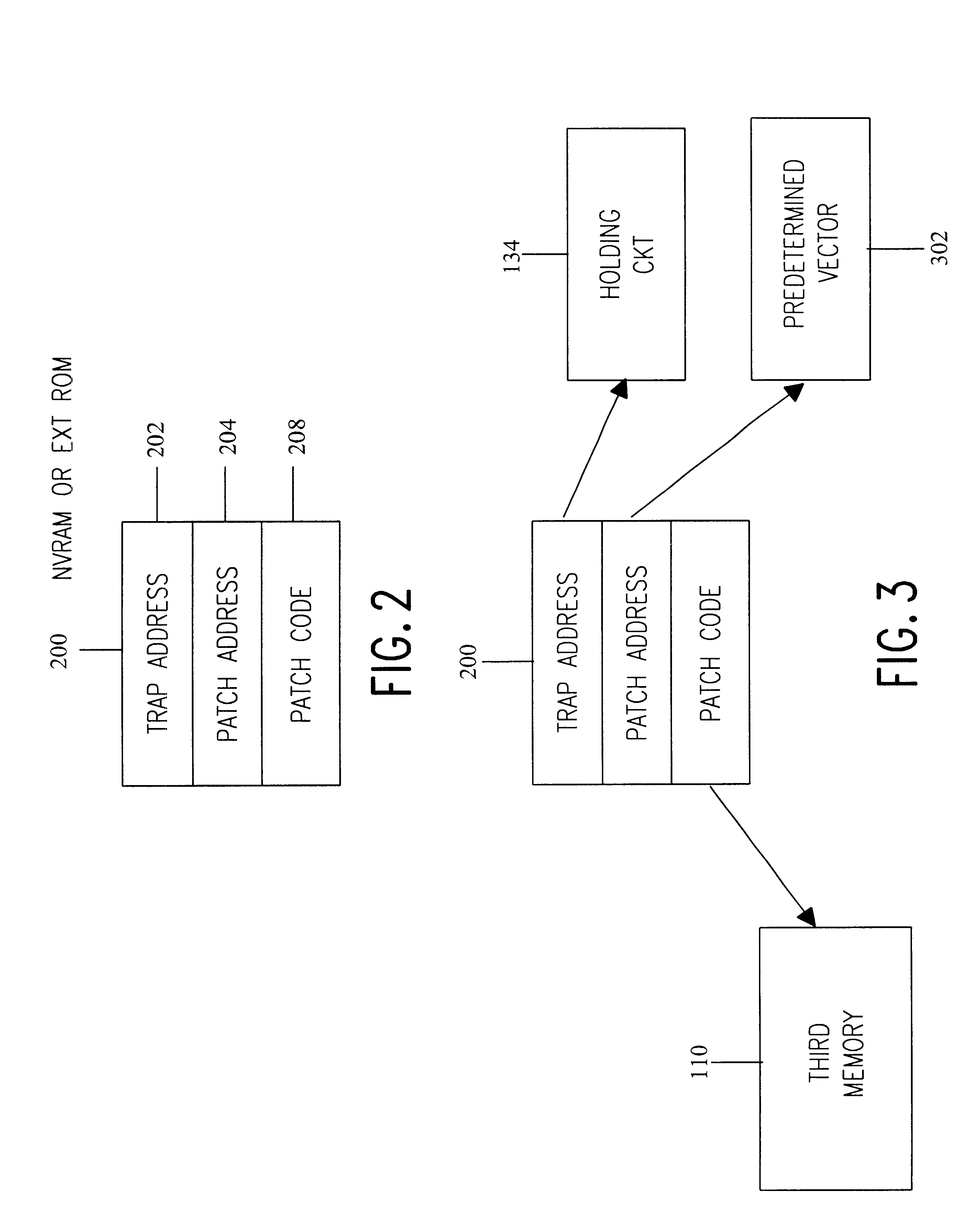

System and method for providing a trap and patch function to low power, cost conscious, and space constrained applications

InactiveUS6412081B1Less powerLess costEnergy efficient ICTProgram initiation/switchingPower-on resetElectricity

A system and method for providing a software trap and patch function to low power, cost conscious, and space constrained applications. When a programming error in a first memory is discovered, a data structure comprising a trap address, patch code, and patch address are stored in a second memory. A power-on-reset process detects the presence of the data structure, and in response thereto, enables the trap and patch function. In operation, upon the occurrence of a trap condition, the first memory is disconnected from the data bus and a predetermined instruction circuit is activated. Upon activation thereof, the predetermined instruction circuit, which comprises solely combinational circuitry, places the op code of the predetermined instruction on the data bus. In one embodiment, in which the predetermined instruction is a software interrupt instruction, a predetermined bit of the PSR is placed in a defined state responsive to the occurrence of a trap condition. Upon execution of the software interrupt instruction, the processor executes an interrupt request service routine. There, the predetermined bit of the PSR is examined to see if it is in the predefined state. If so, and the interrupt was caused by a trap condition in contrast to a software interrupt, the service routine causes the processor to execute the patch code in place of the error-containing code. If not, signifying a hardware interrupt, another service routine is executed.

Owner:SKYWORKS SOLUTIONS INC

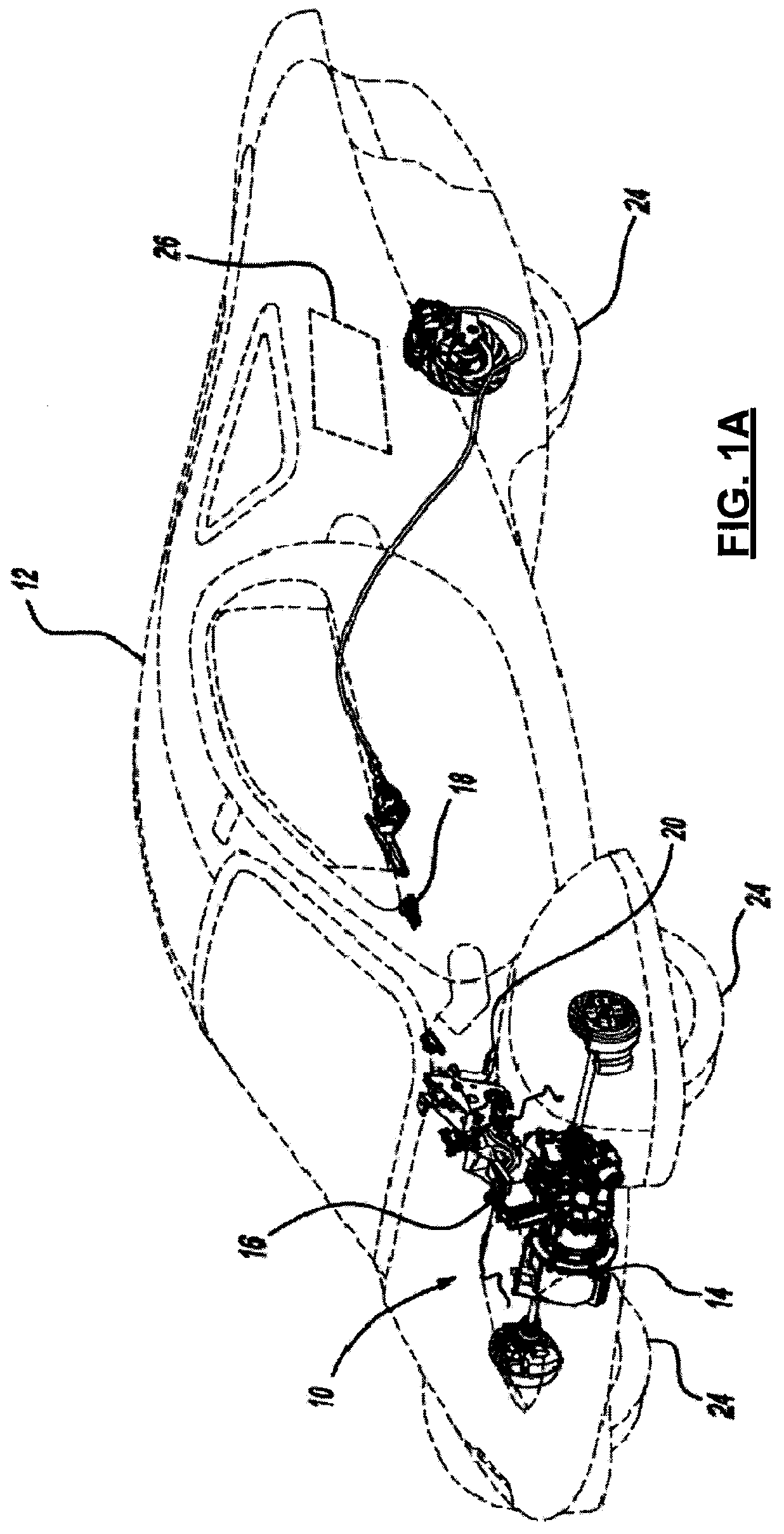

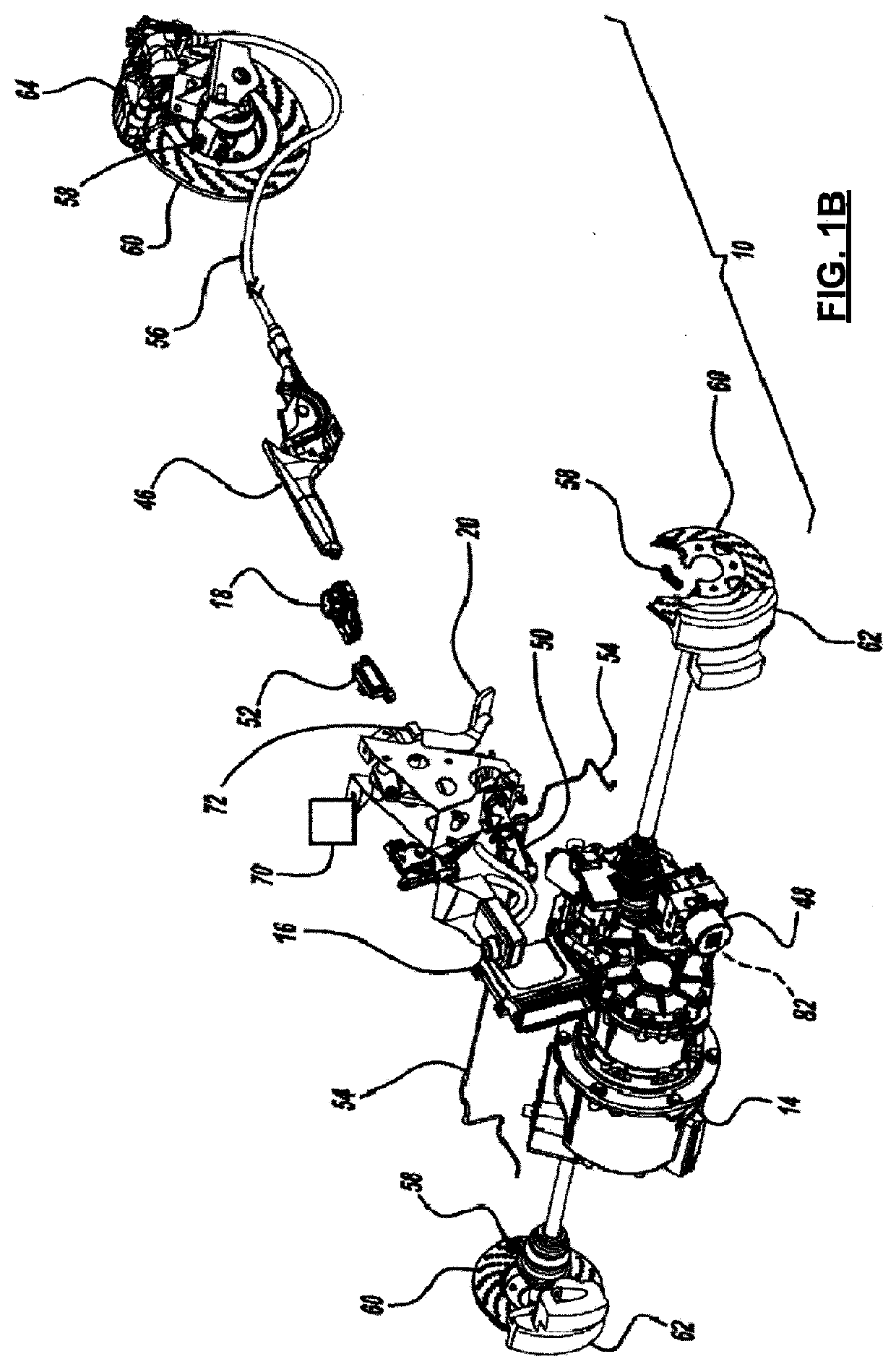

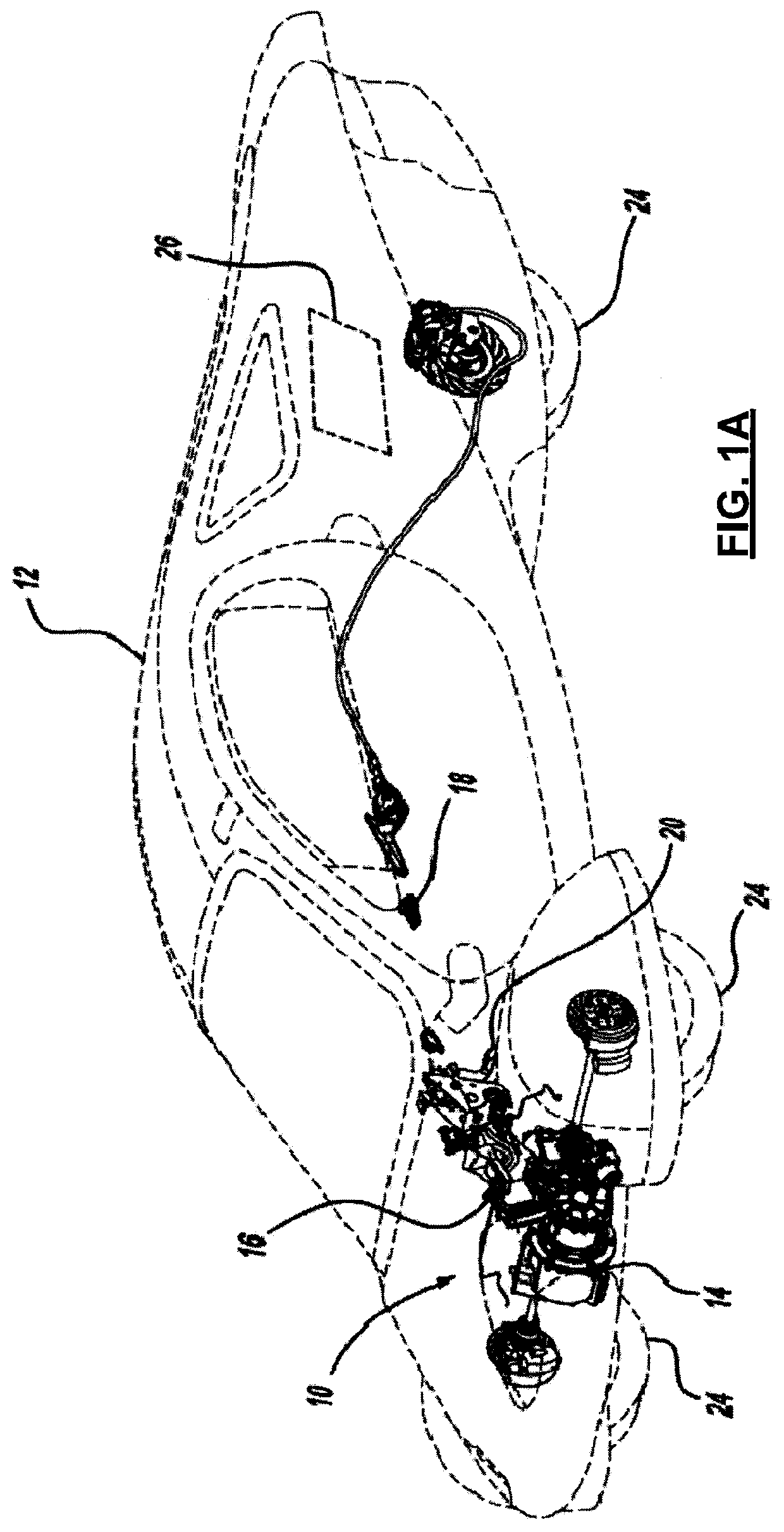

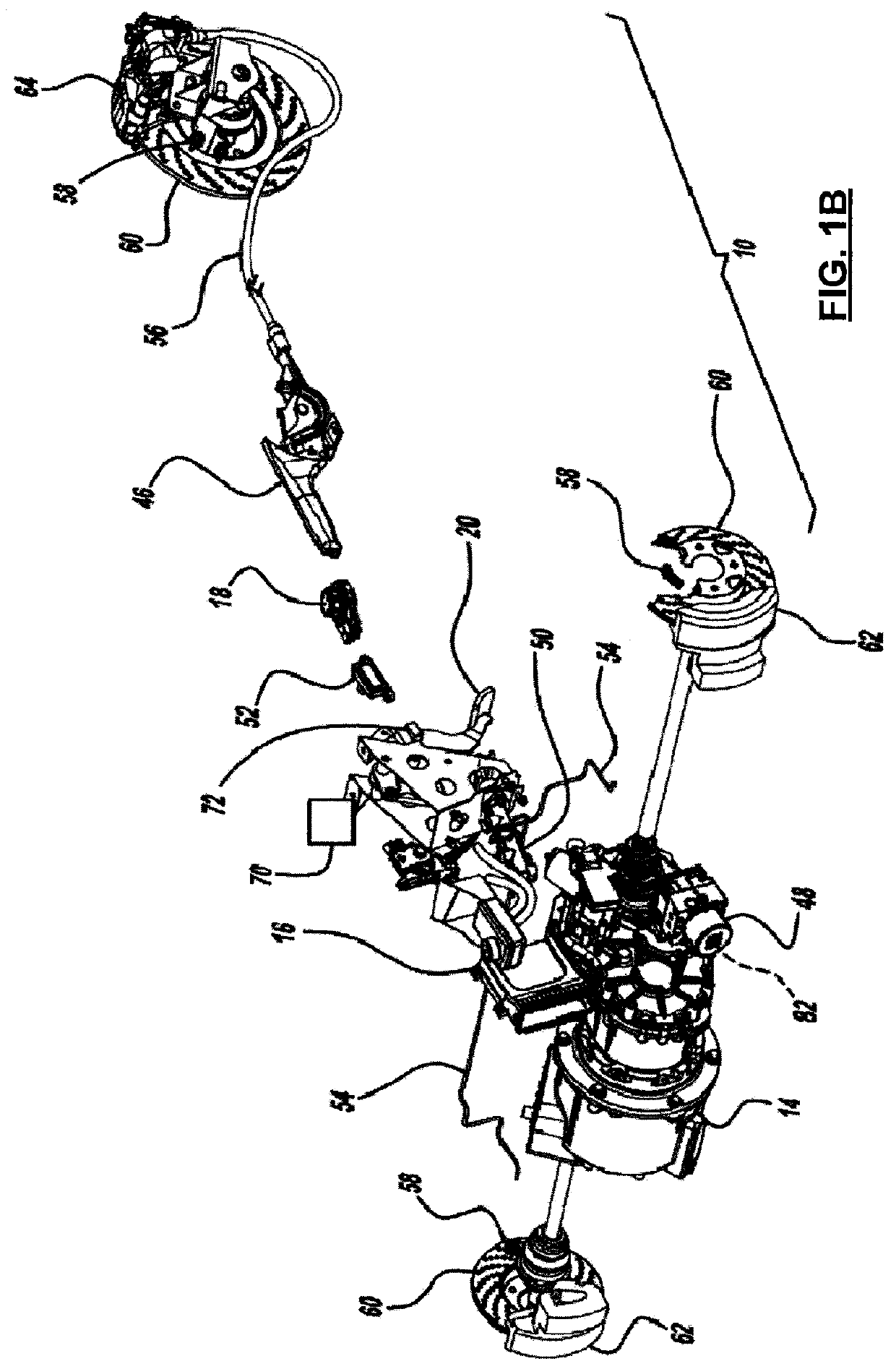

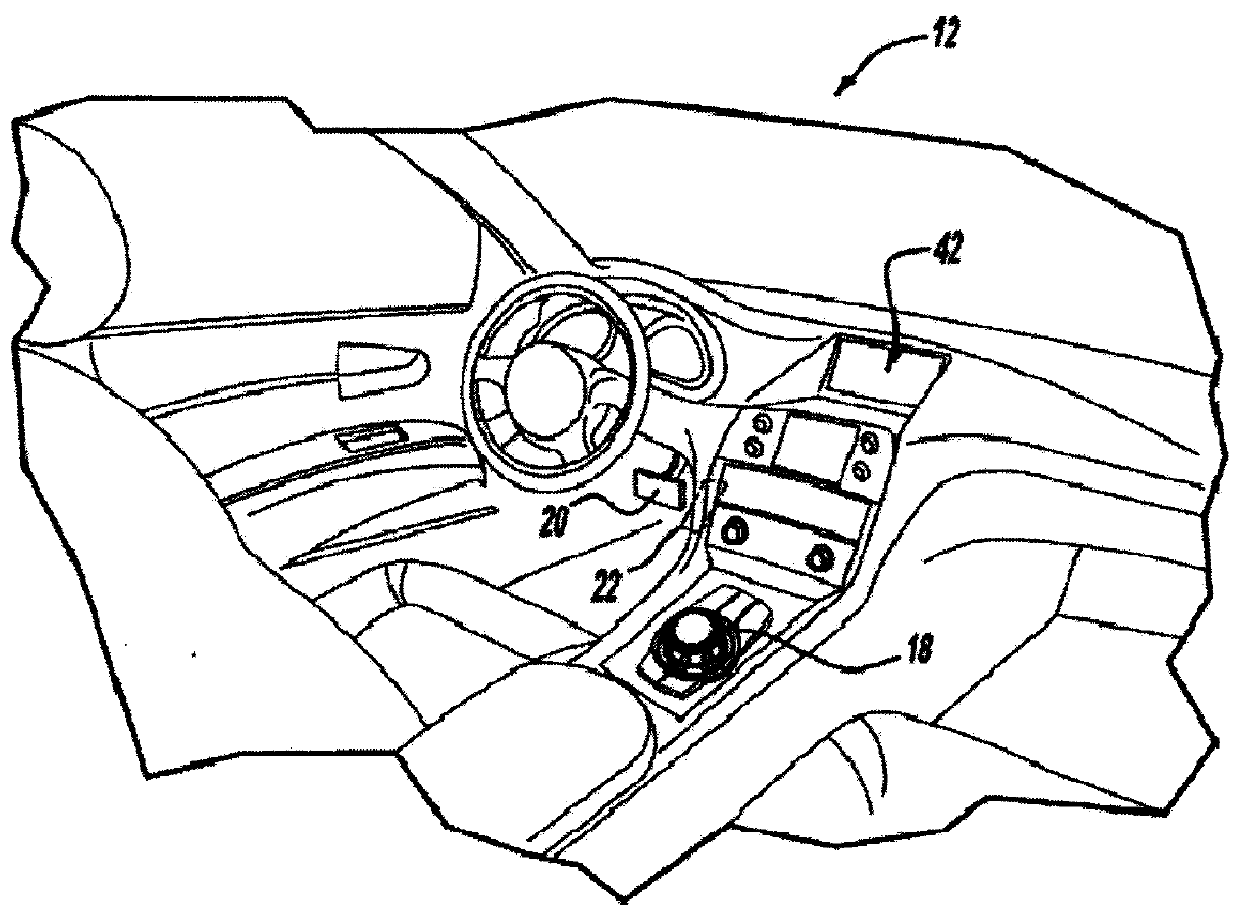

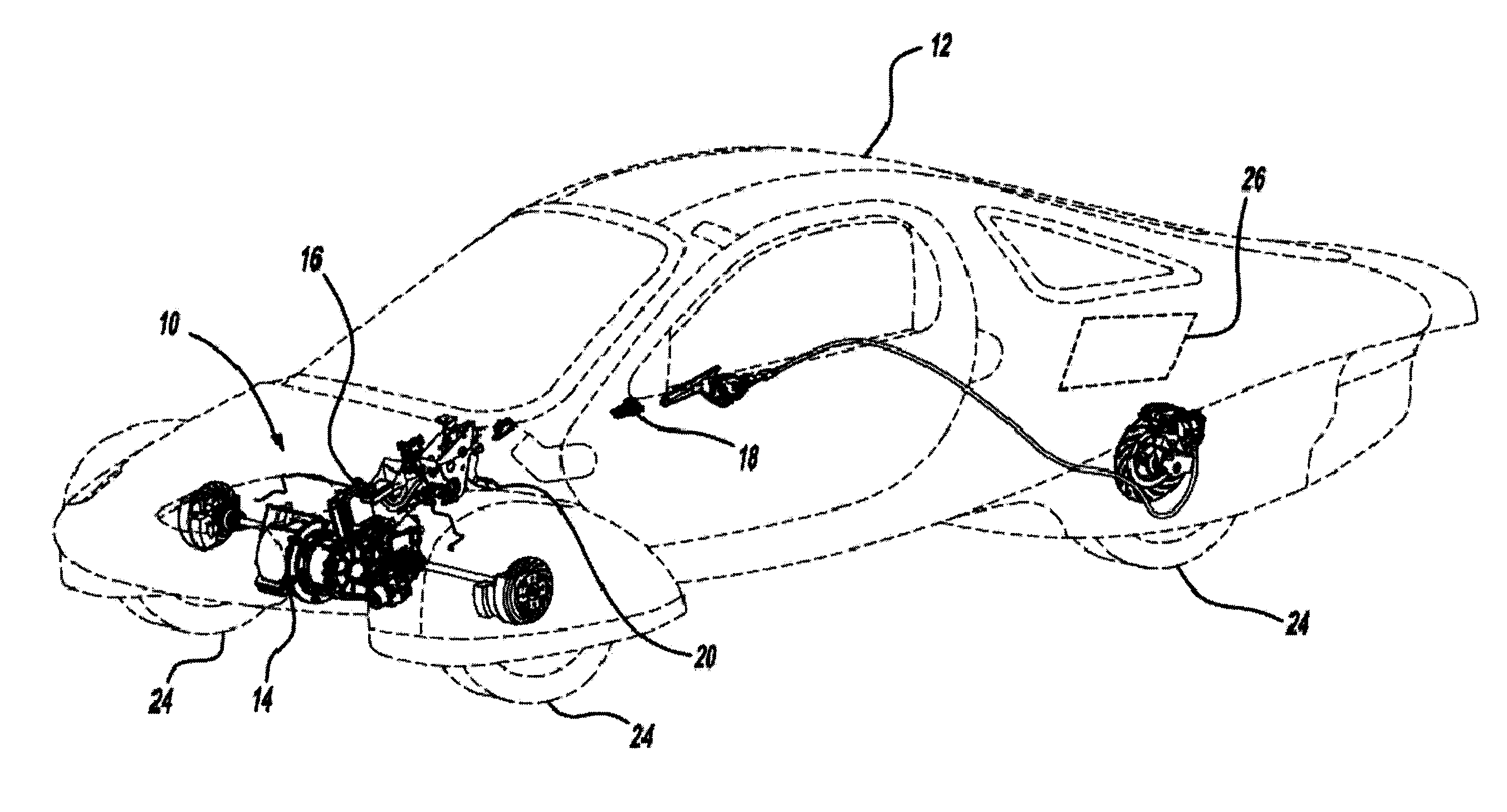

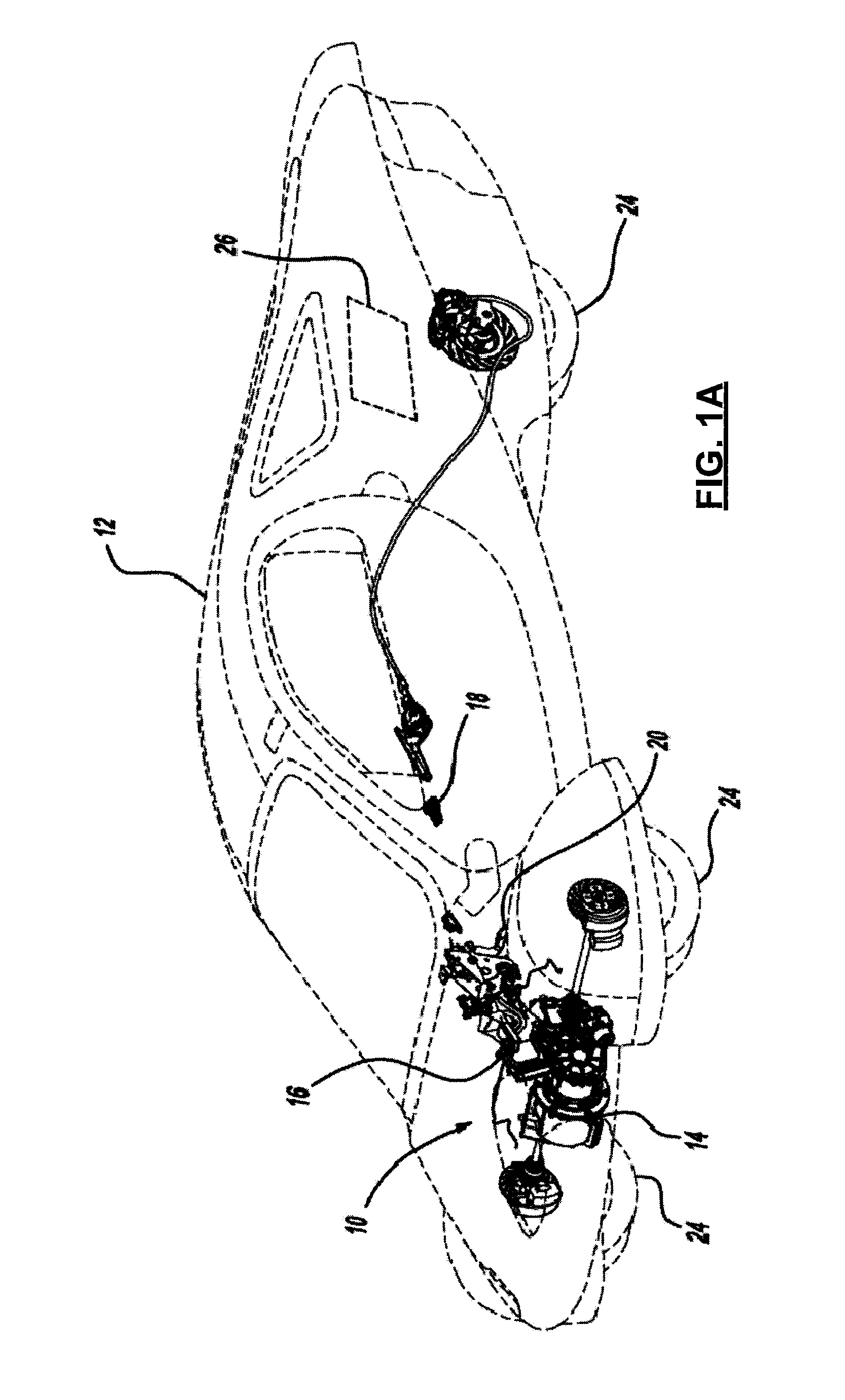

Regenerative braking system

InactiveUS20120139329A1Feel goodSmooth decelerationHybrid vehiclesBraking element arrangementsMobile vehicleRegenerative brake

An automotive vehicle braking system includes a regenerative brake system operable upon a deceleration request from at least one of an acceleration member and a braking member. At least a portion of the deceleration request is adjustable by a user when the deceleration request is provided by the acceleration member.

Owner:APTERA MOTORS

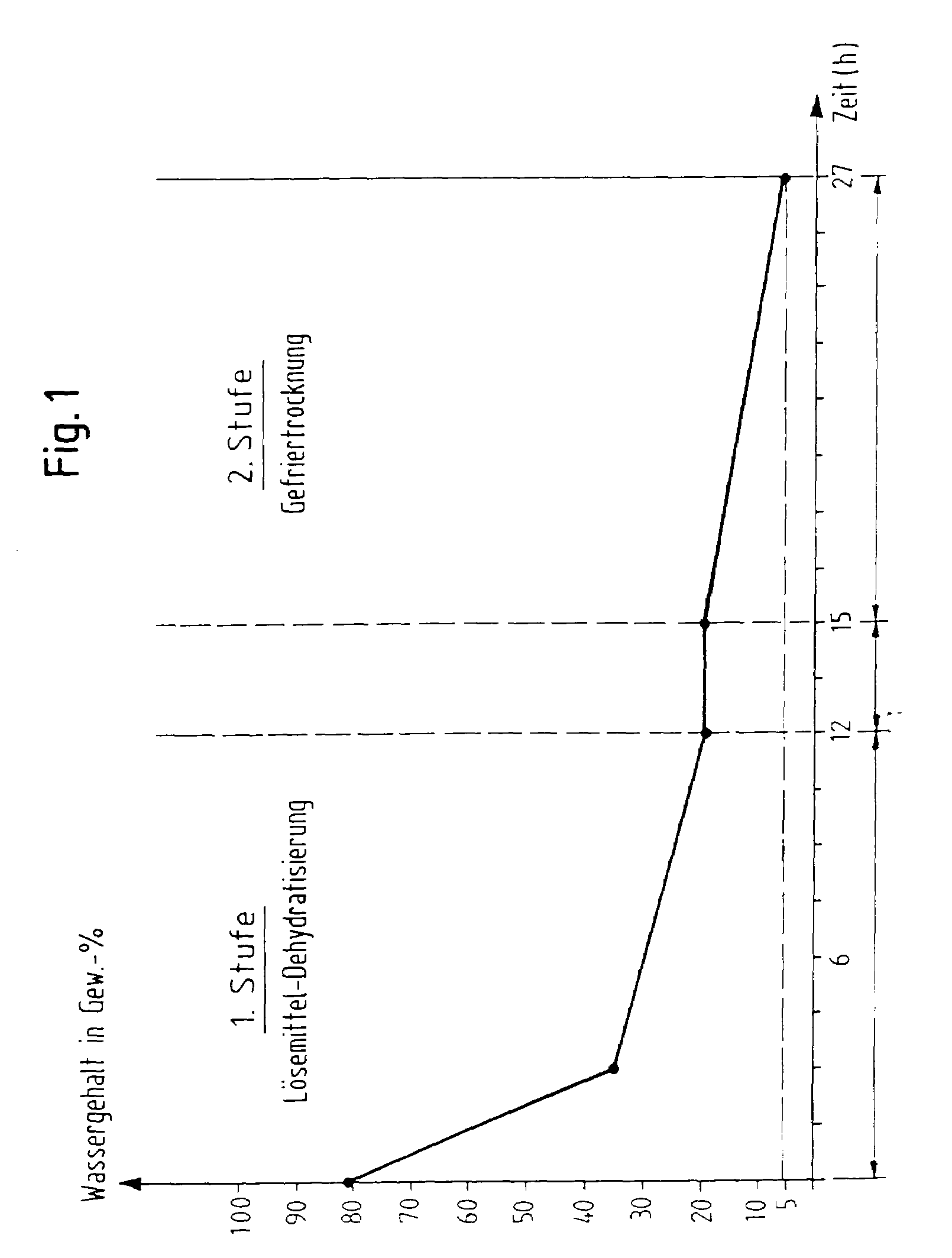

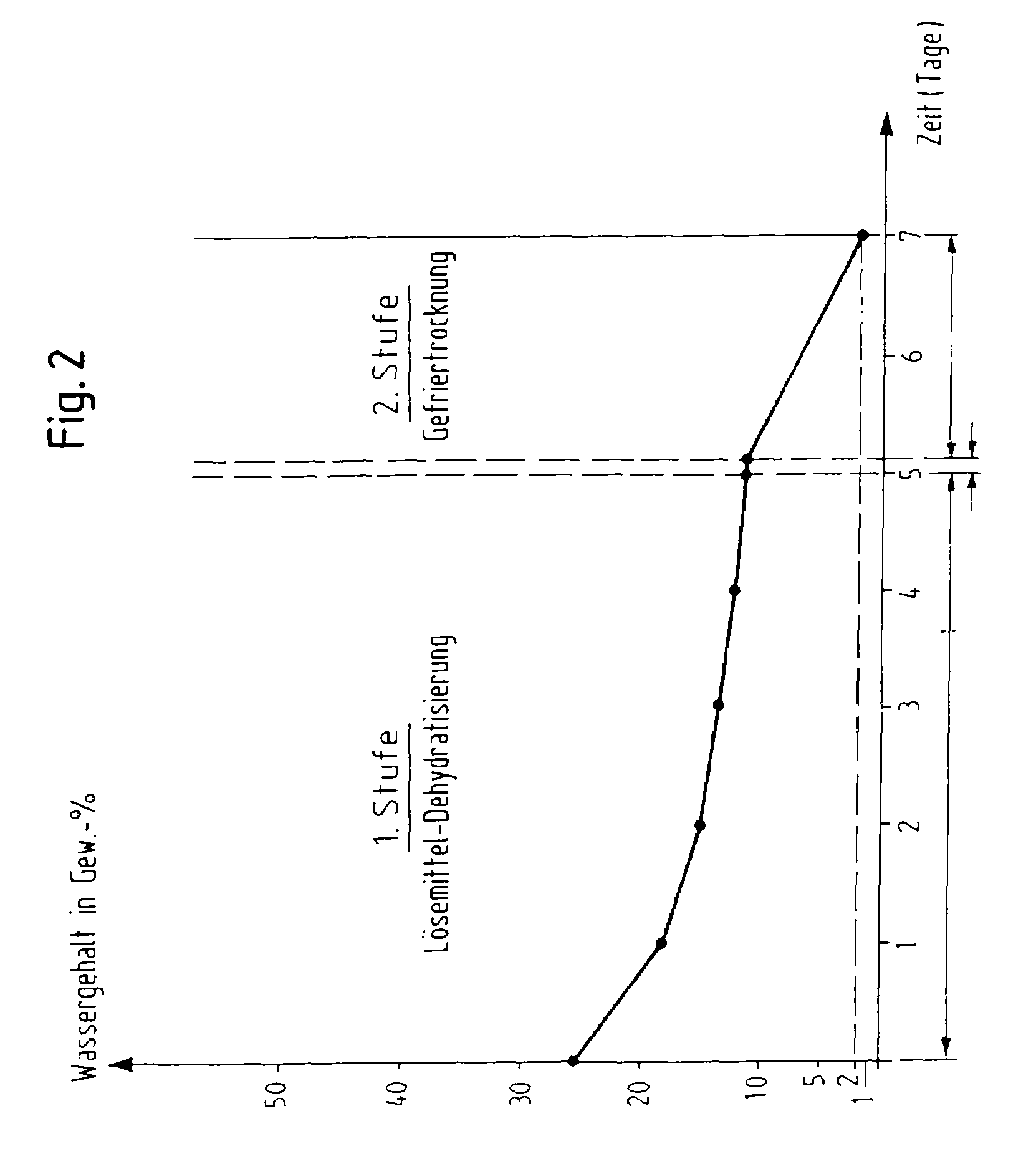

Method for dehydrating biological tissue for producing preserved transplants

InactiveUS6942961B1Dehydration fastEasy to operatePre-tanning chemical treatmentDead animal preservationFreeze-dryingSolvent

The invention relates to a two-step method for dehydrating biological tissues for producing preserved transplants. In a first step, the tissue is partially dehydrated with an organic, water-miscible solvent. In a second step, the tissue is dehydrated further by freeze drying.

Owner:TUTOGEN MEDICAL INC

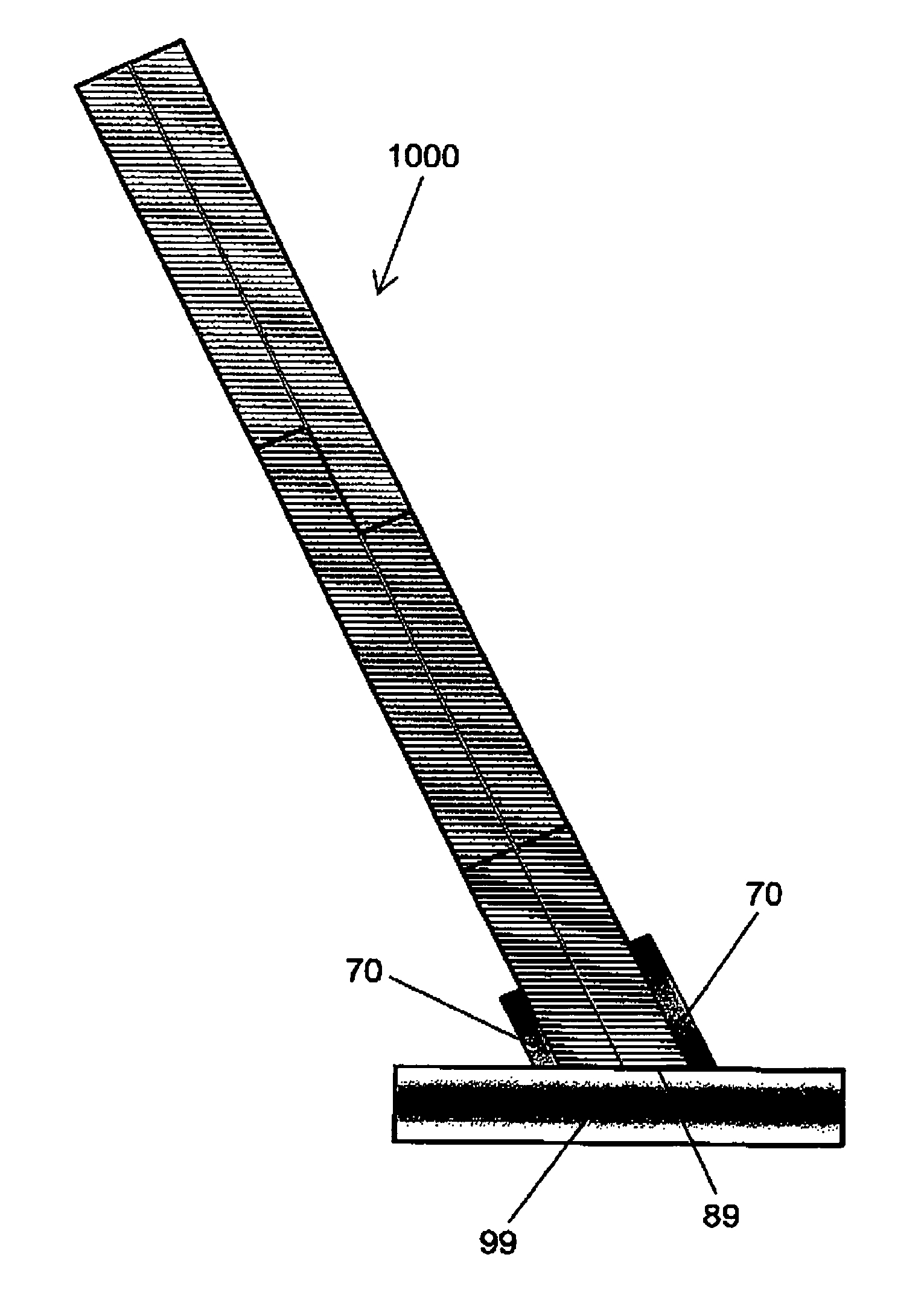

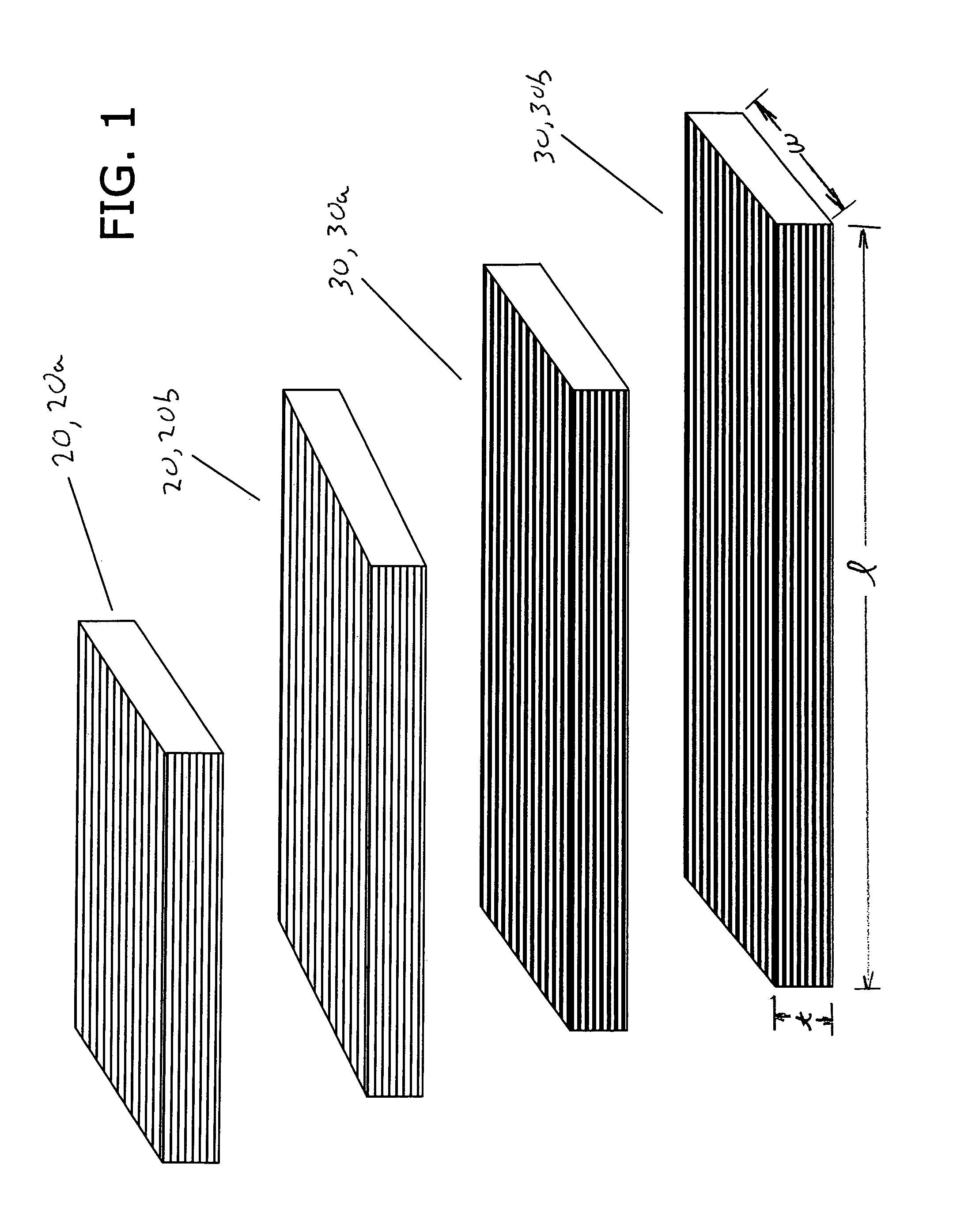

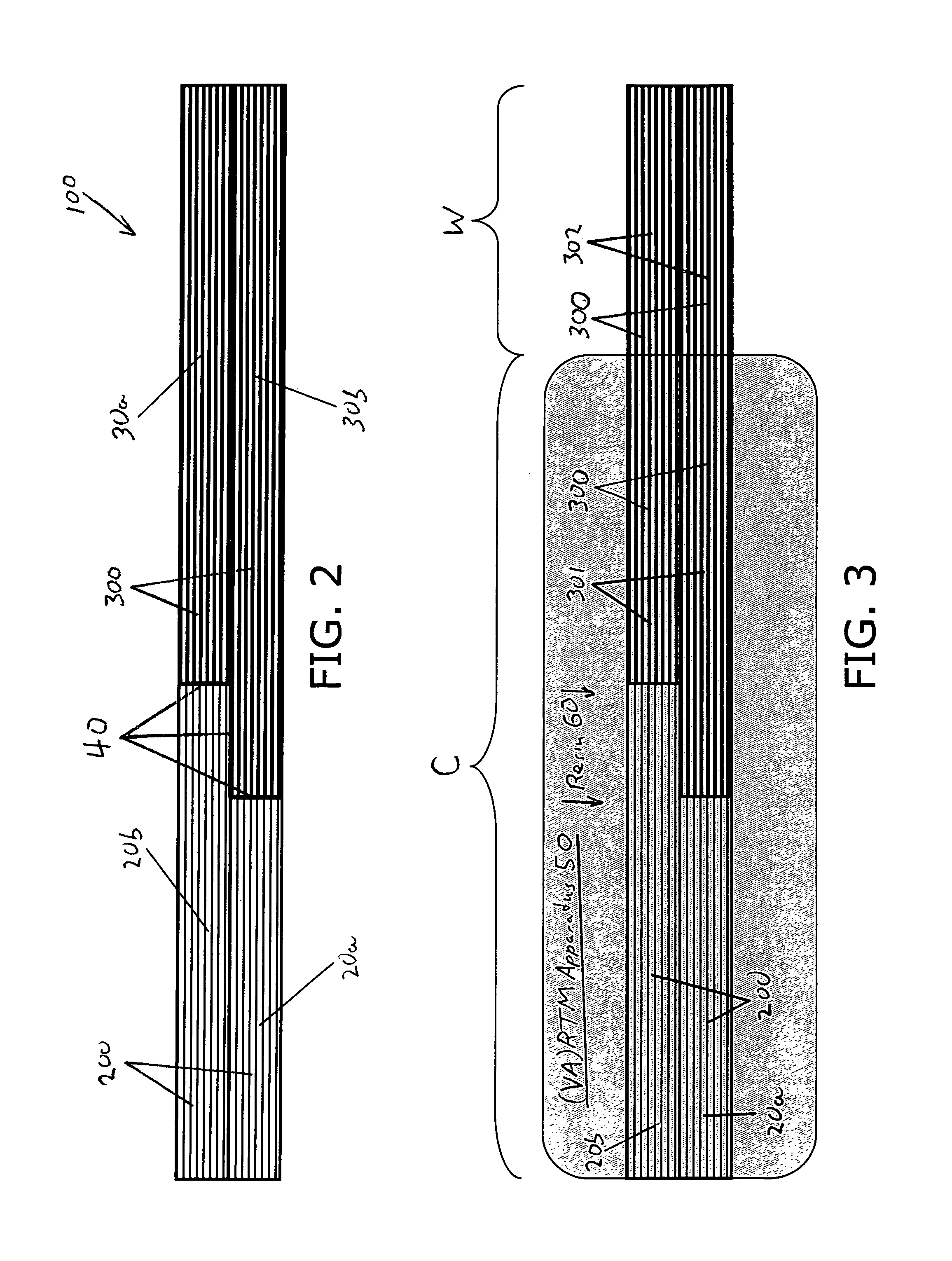

Hybrid composite welded joint

InactiveUS7959058B1Susceptibility to damageLess extensiveLamination ancillary operationsLaminationFiberMetal

The present invention's composite-to-metal attachment methodology—bolt-free and adhesive-free—features the implementation of an intermediary structure containing metallic fibrous material. The intermediary structure couples a first adherend (which contains nonmetallic fibrous material) with a second adherend (which contains metallic nonfibrous material). The intermediary structure's fibrous attribute is availed of for effecting its co-cure attachment to the first adherend. The intermediary structure's metallic attribute is availed of for effecting its weld attachment to the second adherend. According to typical inventive practice, respective panels of the first adherend and the intermediary structure are arranged and connected so as to describe a stepped configuration at the interface between the first adherend and the intermediary structure. The first adherend and a first portion of the intermediary structure are co-impregnated with a uniform resinous system and are co-cured. A second portion of the intermediary structure is welded with respect to the second adherend.

Owner:THE US SECREATRY OF THE NAVY CHIEF OF NAVAL RES OFFICE OF COUNSEL ATTN CODE OOCIP

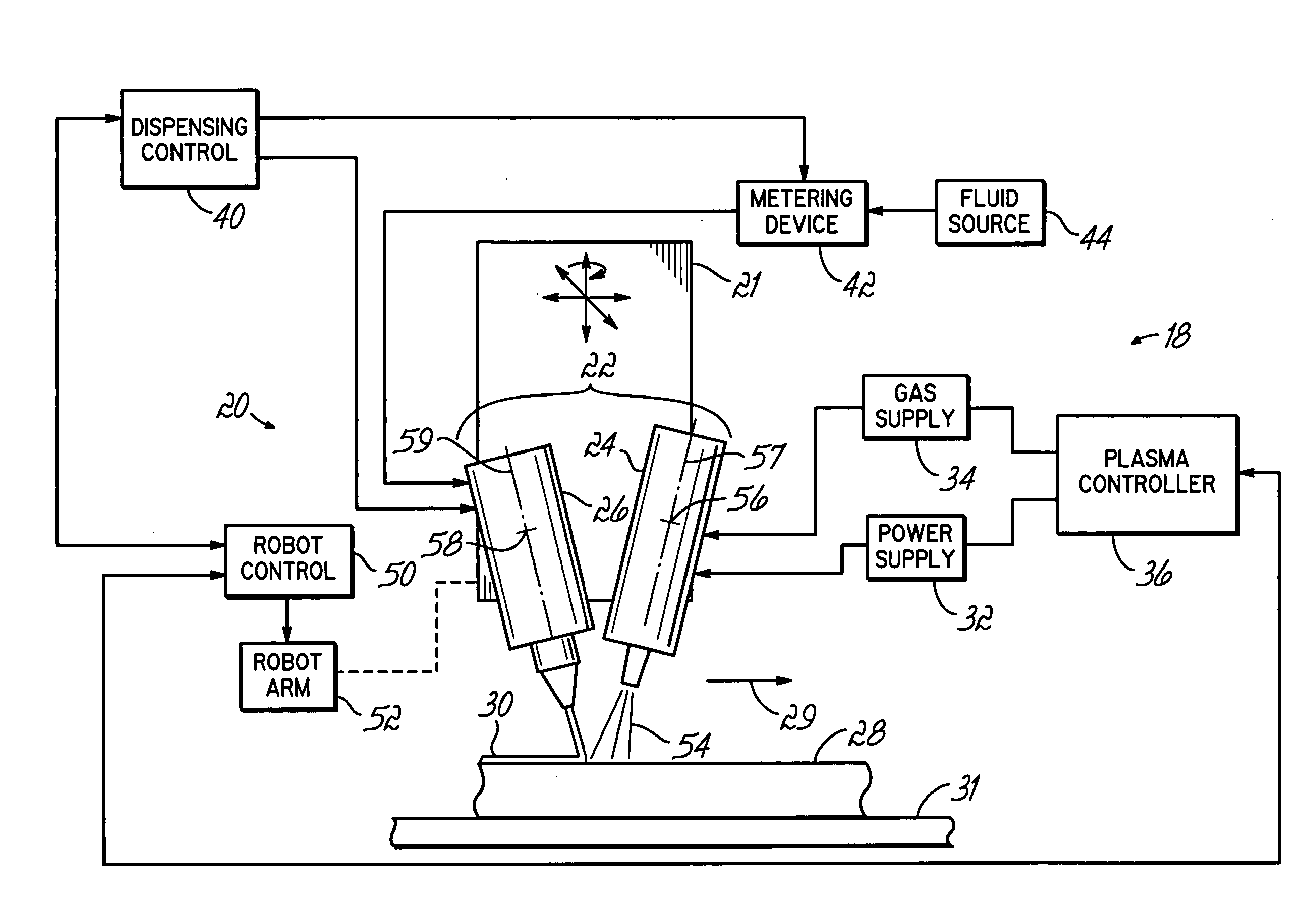

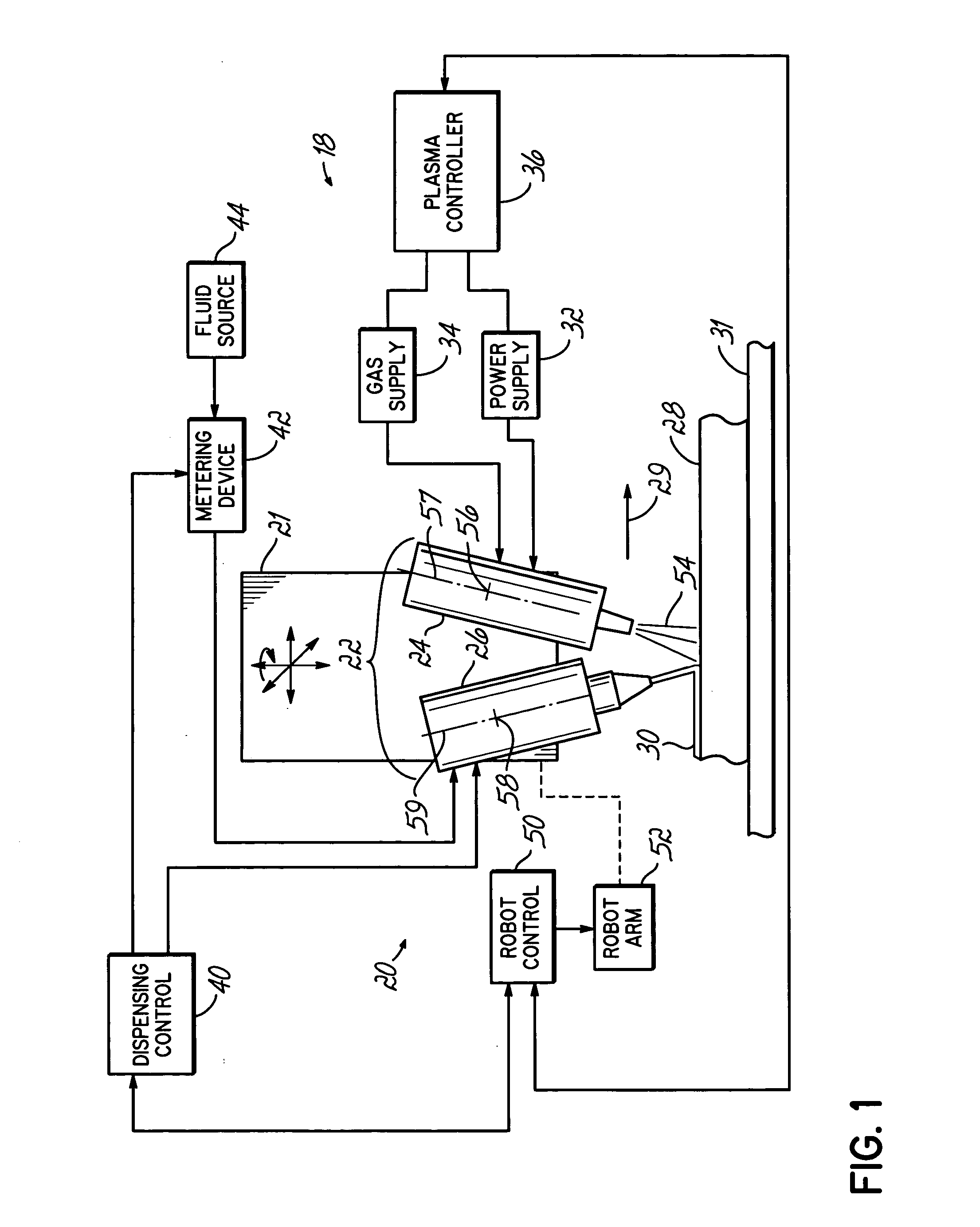

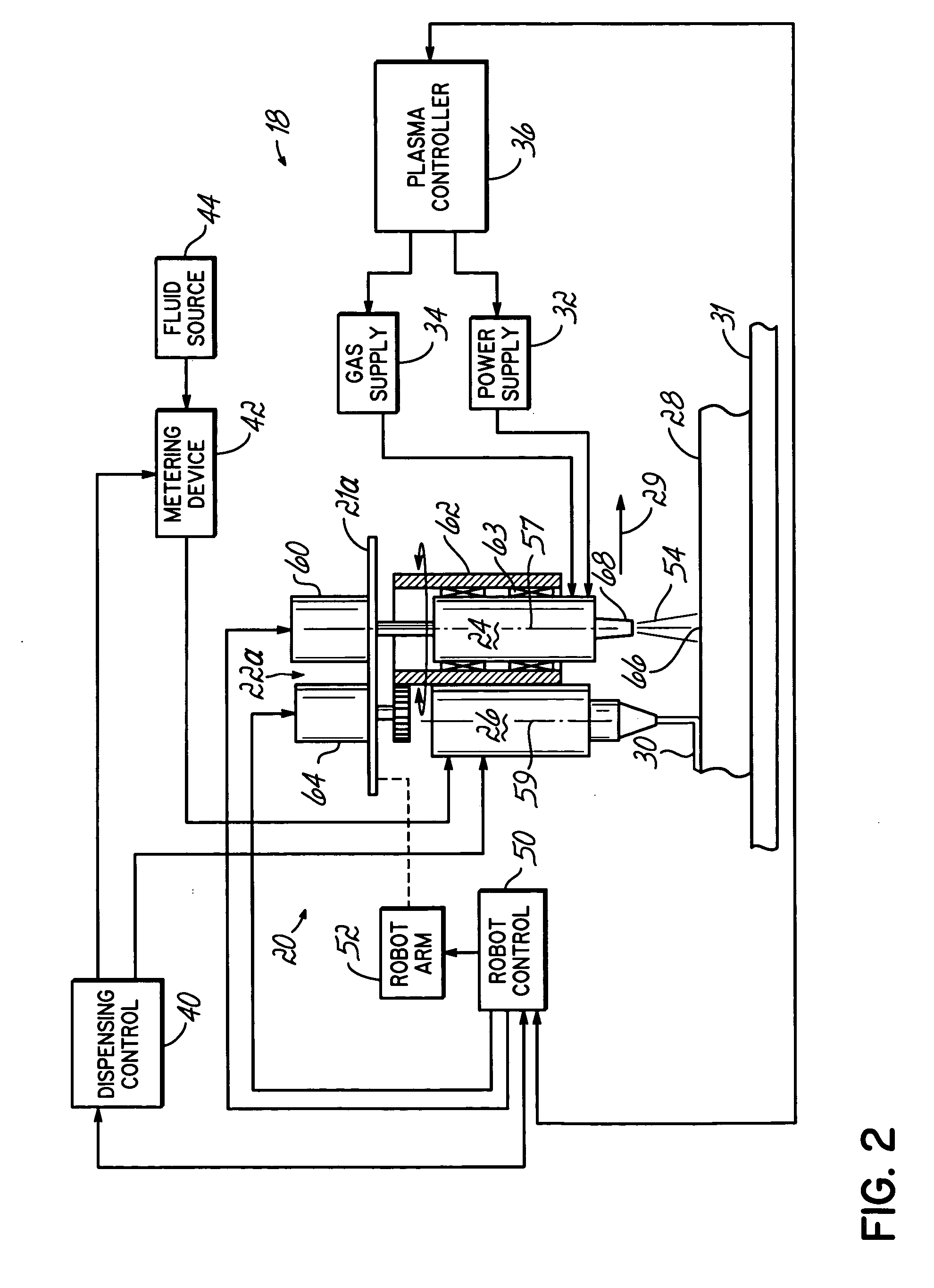

Apparatus and method for plasma treating and dispensing an adhesive/sealant onto a part

InactiveUS20060172081A1Minimal timeLess costMovable spraying apparatusPretreated surfacesPlasma treatmentPlasma processing

Owner:NORDSON CORP

Automotive vehicle brake system

InactiveUS20120139328A1Feel goodSmooth decelerationBraking element arrangementsDigital data processing detailsMobile vehicleRegenerative brake

An automotive vehicle braking system includes a hydraulic brake system in communication with a regenerative brake system. The regenerative brake system has both a fixed system logic portion and a user-adjustable system logic portion. The fixed system logic of the regenerative brake system is driven by a brake member displacement.

Owner:APTERA MOTORS

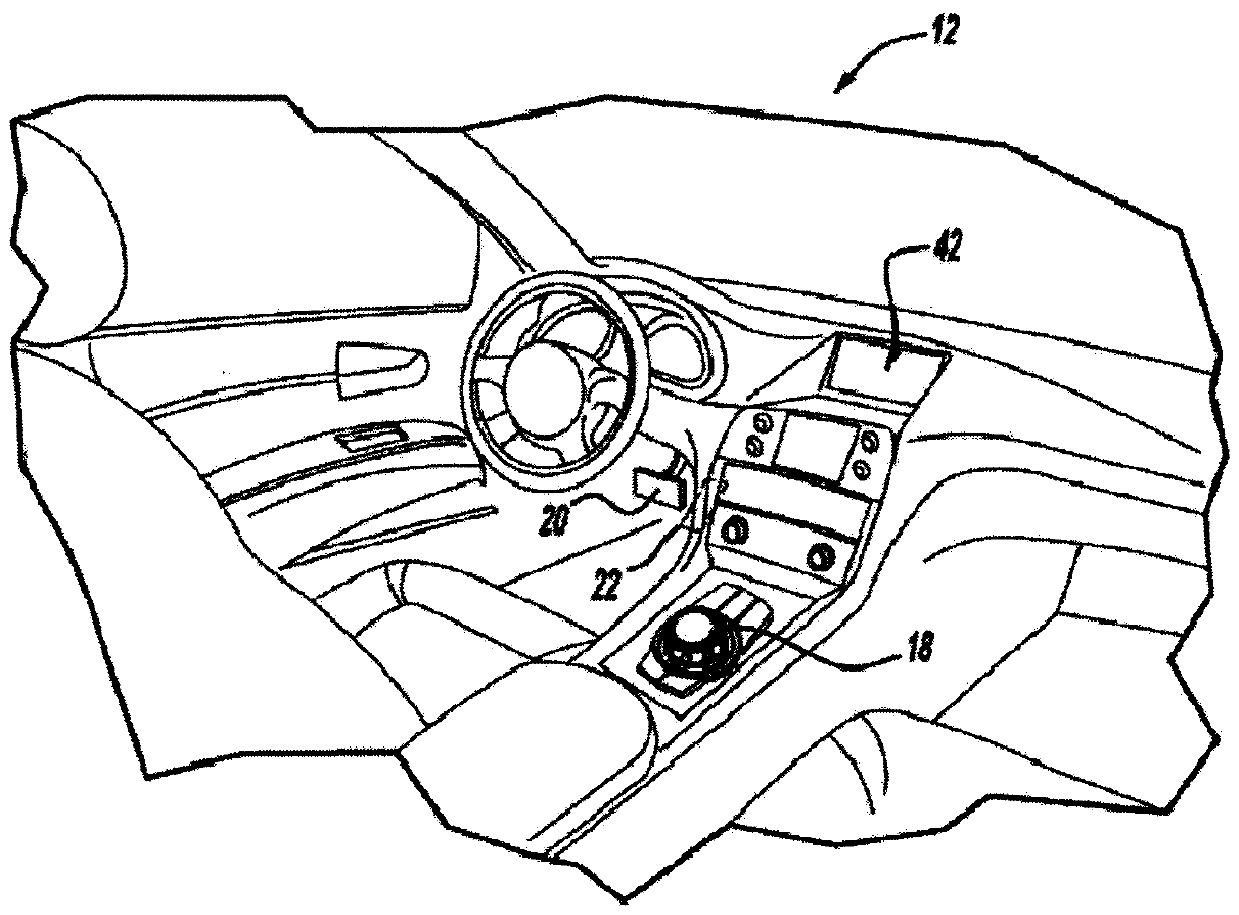

Automotive vehicle regenerative braking control system

InactiveUS20120138395A1Well mixedA large amountDynamo-electric brakes/clutchesAnalogue computers for trafficMobile vehicleRegenerative brake

An automotive vehicle braking system includes an electronic shift controller in communication with a vehicle control unit for manually adjusting a signal indicative of a regenerative braking intensity. The electronic shift controller communicates with the vehicle control unit through a gateway module for analyzing the signal indicative of the regenerative braking intensity.

Owner:APTERA MOTORS

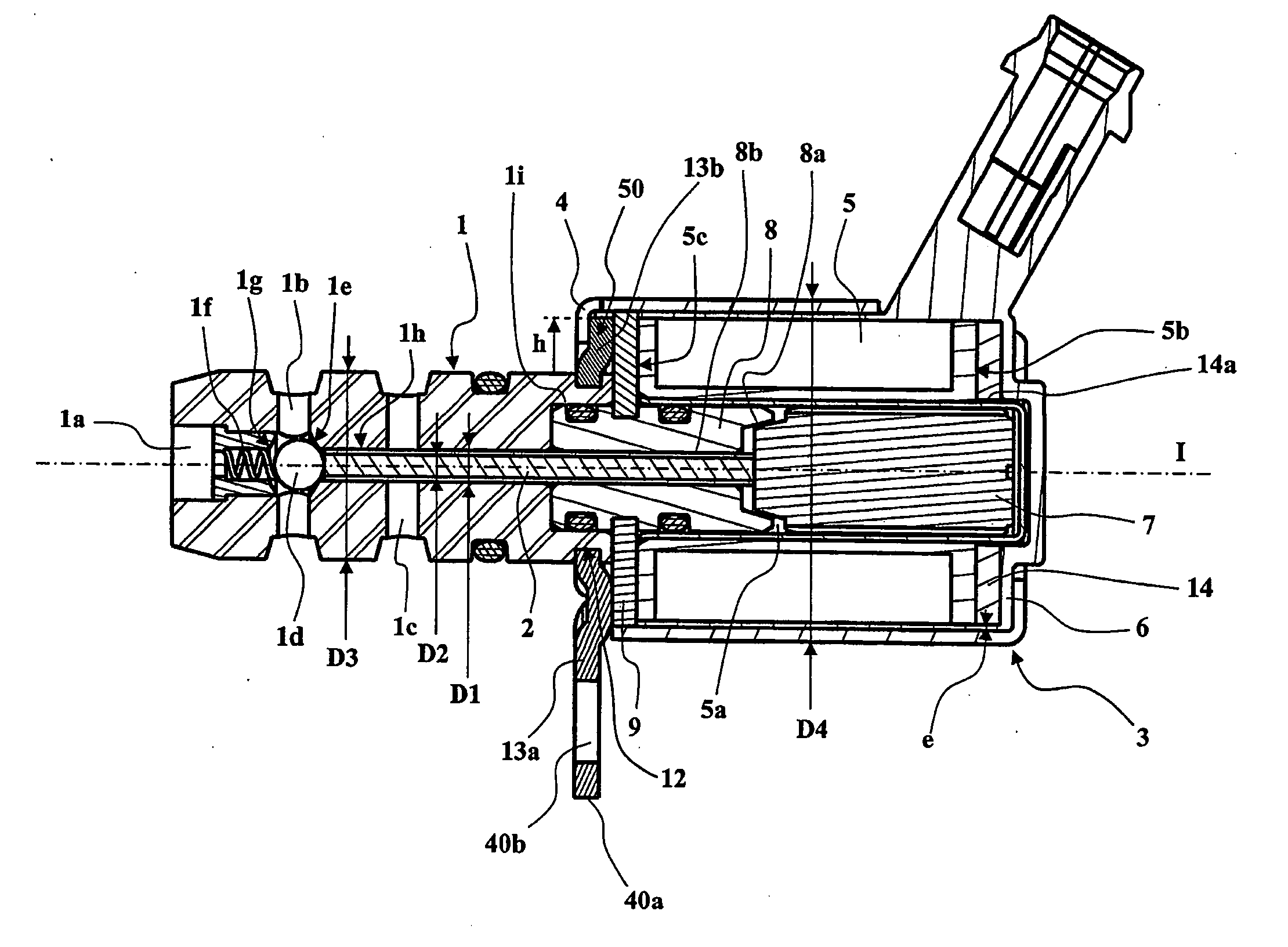

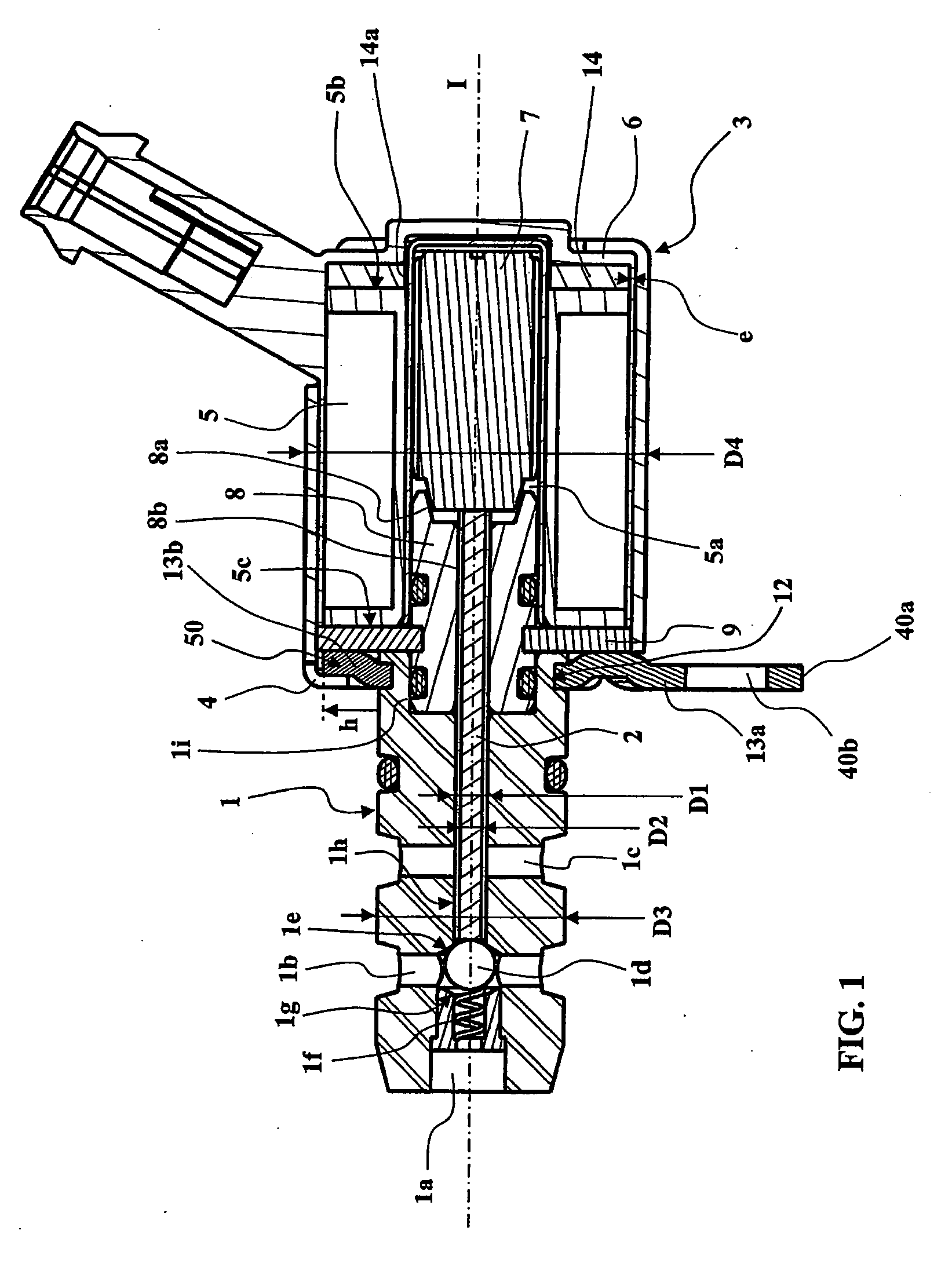

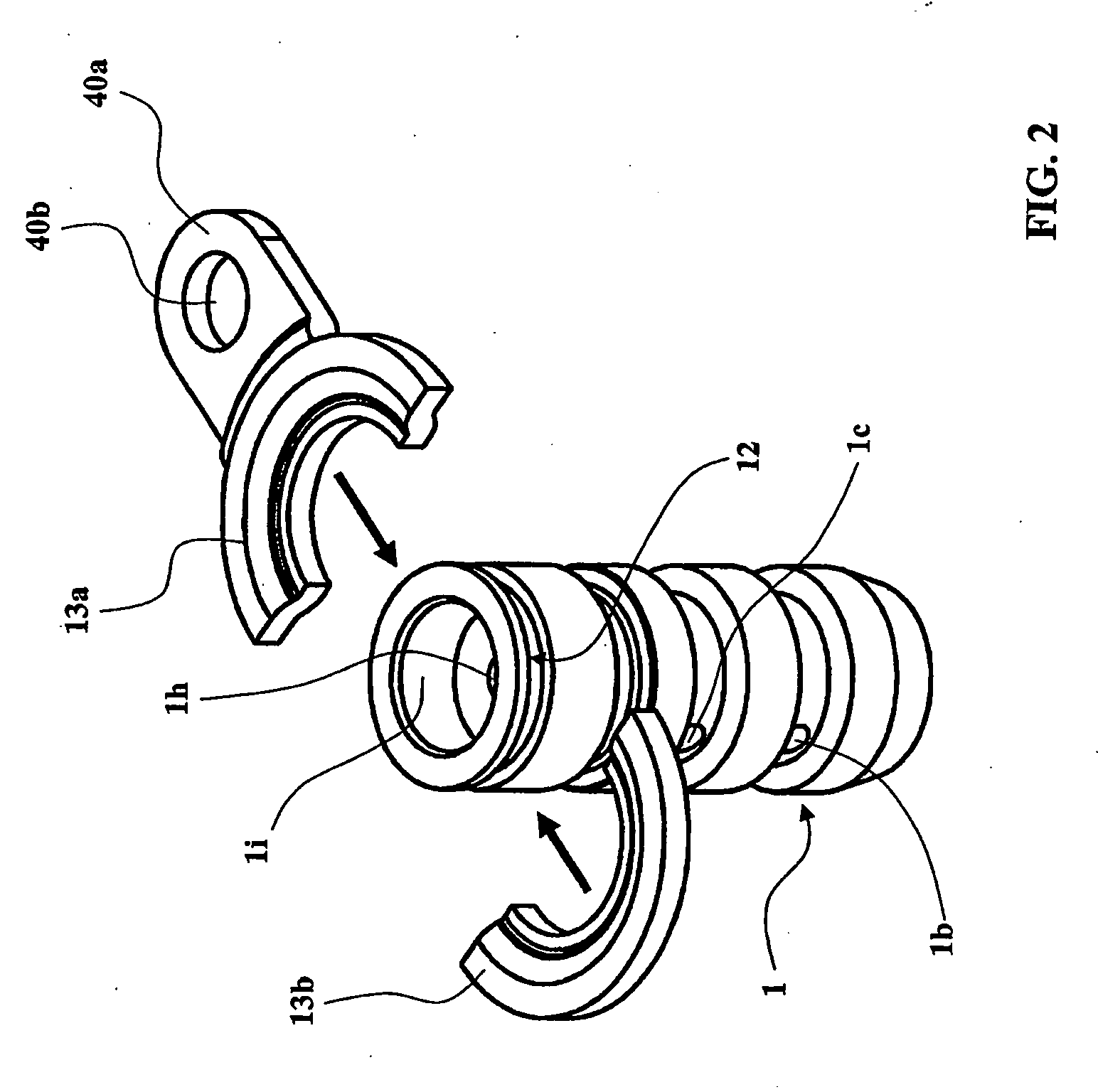

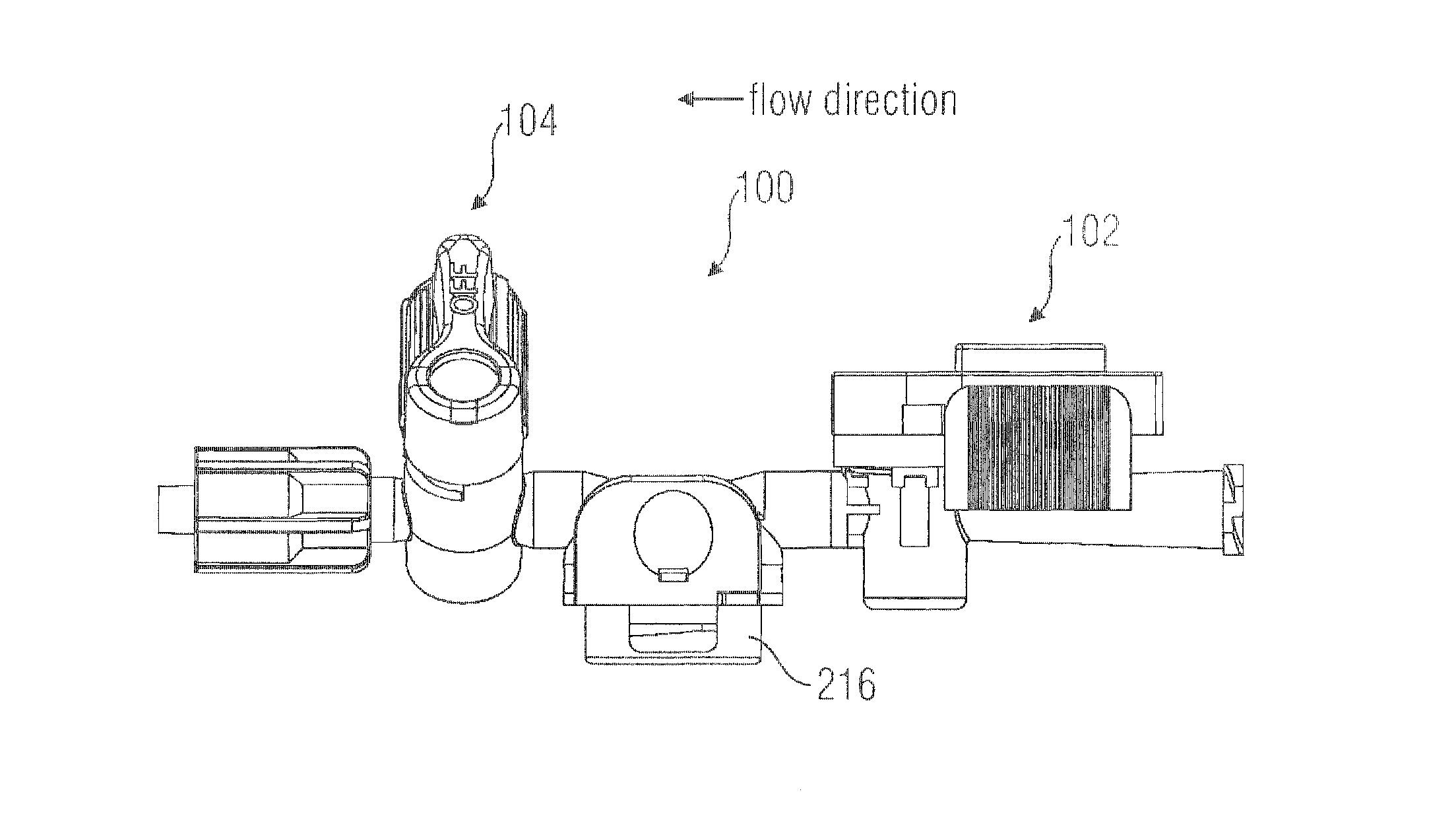

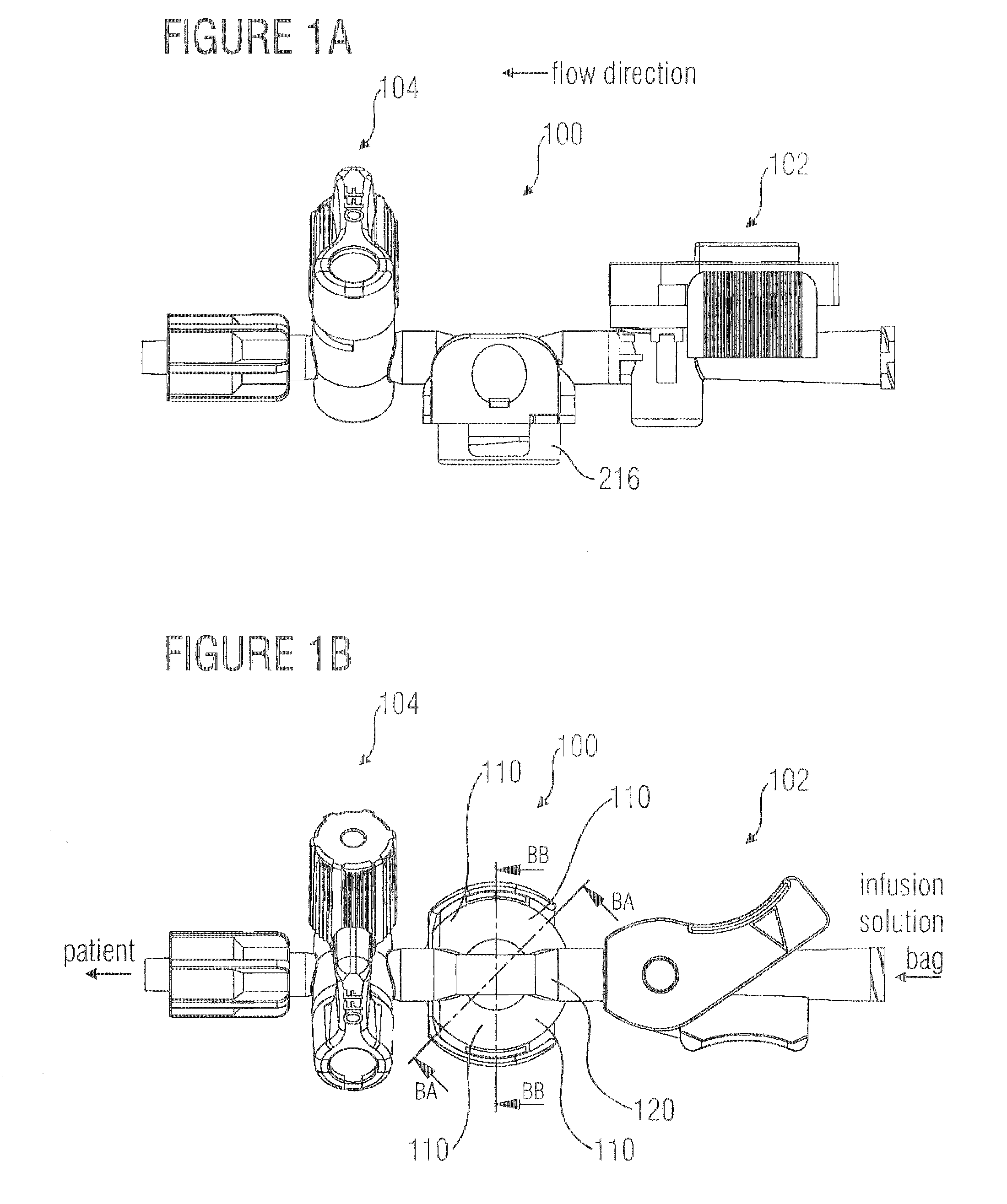

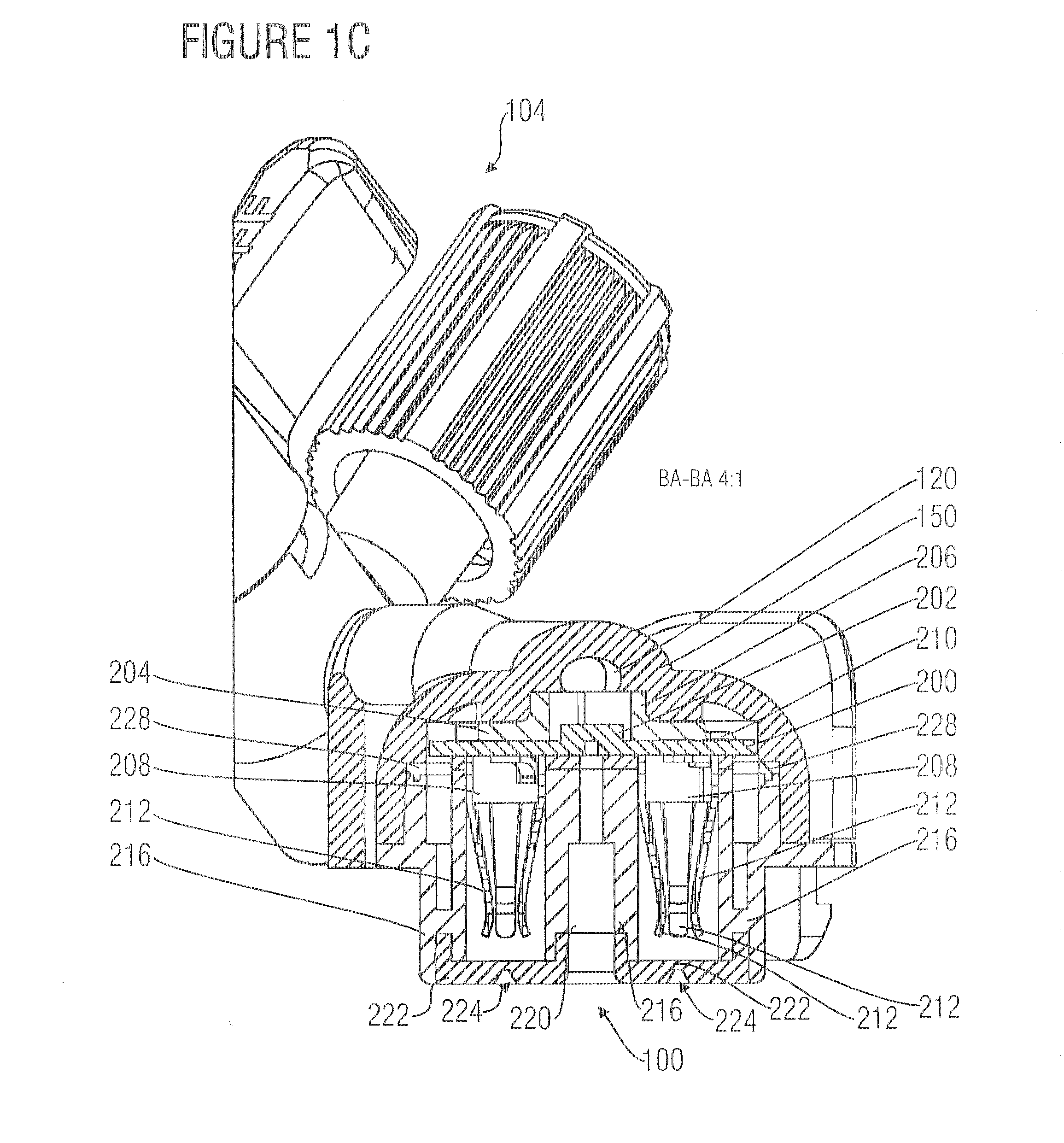

Solenoid valve with fitted shoulder

ActiveUS20060278838A1Less costReduce wasteOperating means/releasing devices for valvesMultiple way valvesVALVE PORTHydraulic circuit

Solenoid valve for controlling the flow of a fluid in a hydraulic circuit, comprising a valve body having at least one fluid duct, a stopper for allowing or preventing the flow of fluid in the fluid duct, a mechanical connection to actuate the stopper, an electromagnetic actuator arranged to actuate the mechanical connection, and a coupling between the electromagnetic actuator and the valve body via a jacket surrounding the electromagnetic actuator and engaged on a shoulder of the valve body. The jacket holds the electromagnetic actuator in axial engagement against the valve body in a direction of engagement. The shoulder comprises two matching half-washers engaged radially in a peripheral groove of the valve body.

Owner:BONTAZ CENT

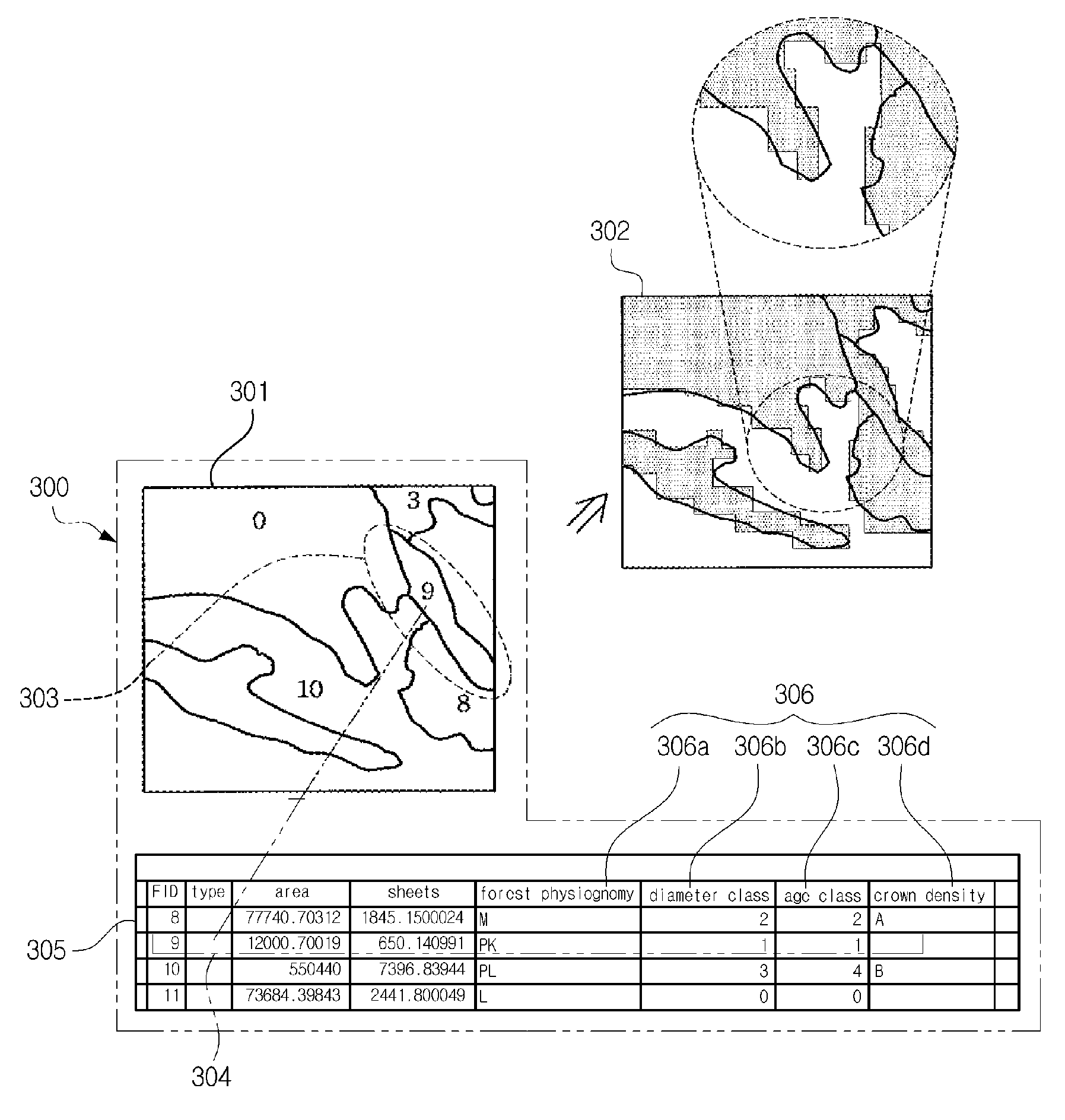

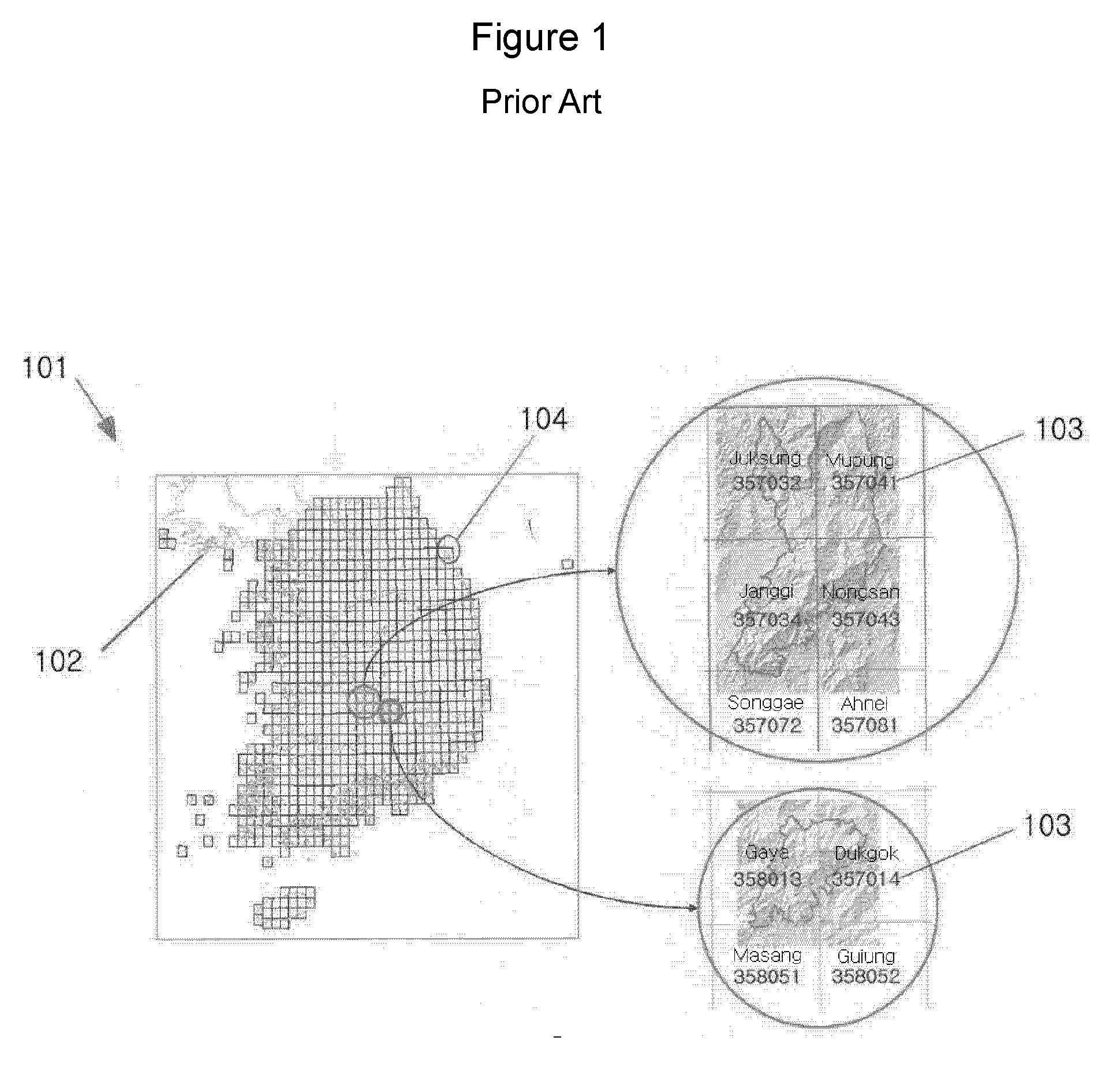

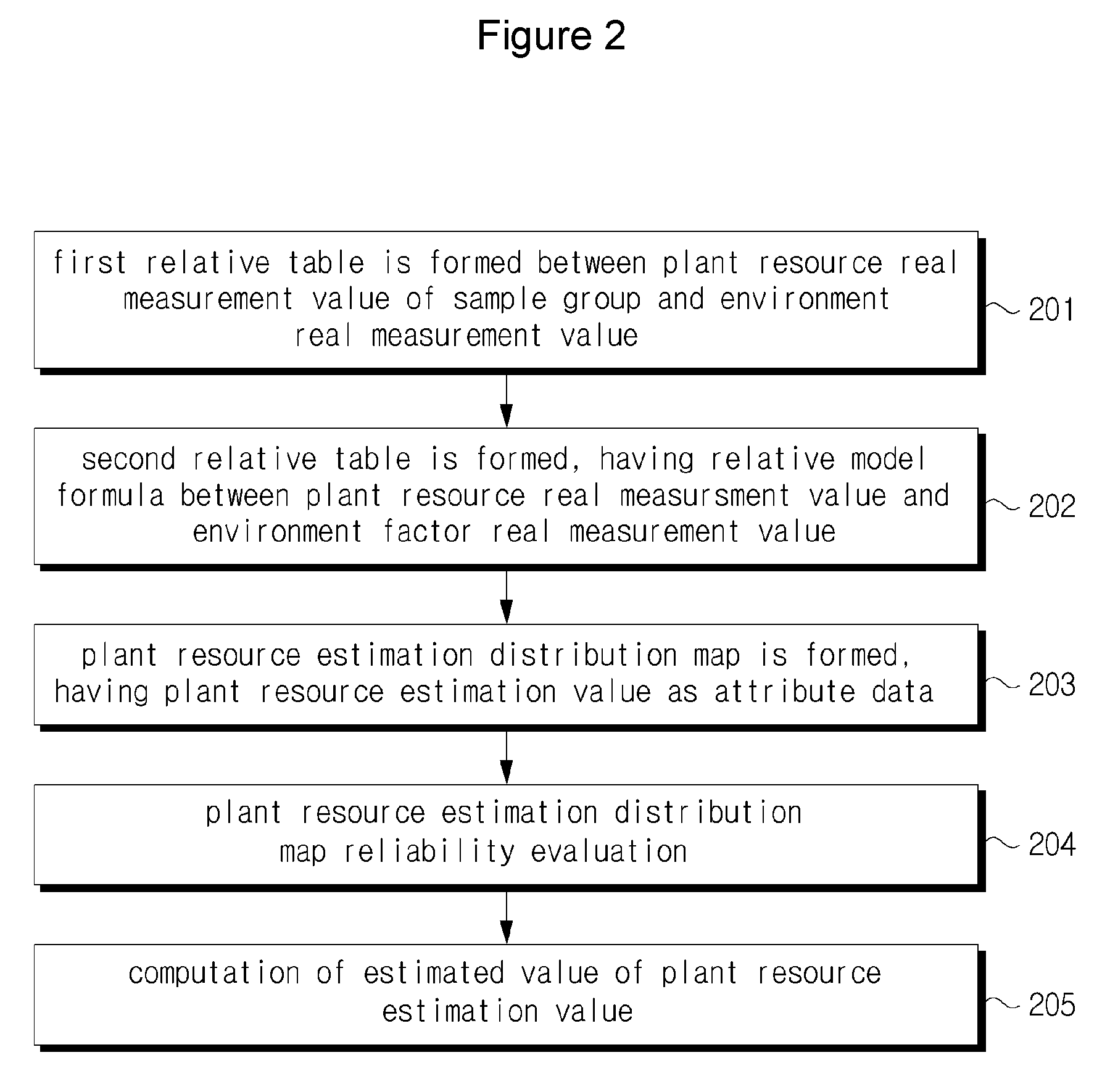

Method for quantifying plant resources using gis

A method for quantifying plant resource using a GIS is disclosed, in which it is possible to more efficiently quantify plant resources with less manpower, time and cost using a GIS when quantifying plant resources in a certain region. In the method, a sample group is extracted from mother groups having a plurality of distribution maps having a plurality of environment factors including IMI as attribute data, the IMI being obtained through a GIS preprocess. A relative model formula is obtained between a plant resource real measurement value of the sample group and an environment factor real measurement value and is related with the distribution map of the mother group, and the distribution maps are overlapped for thereby forming a plant resource estimation distribution map of the mother group.

Owner:NAT ARBORETUM KOREA FOREST SERVICE

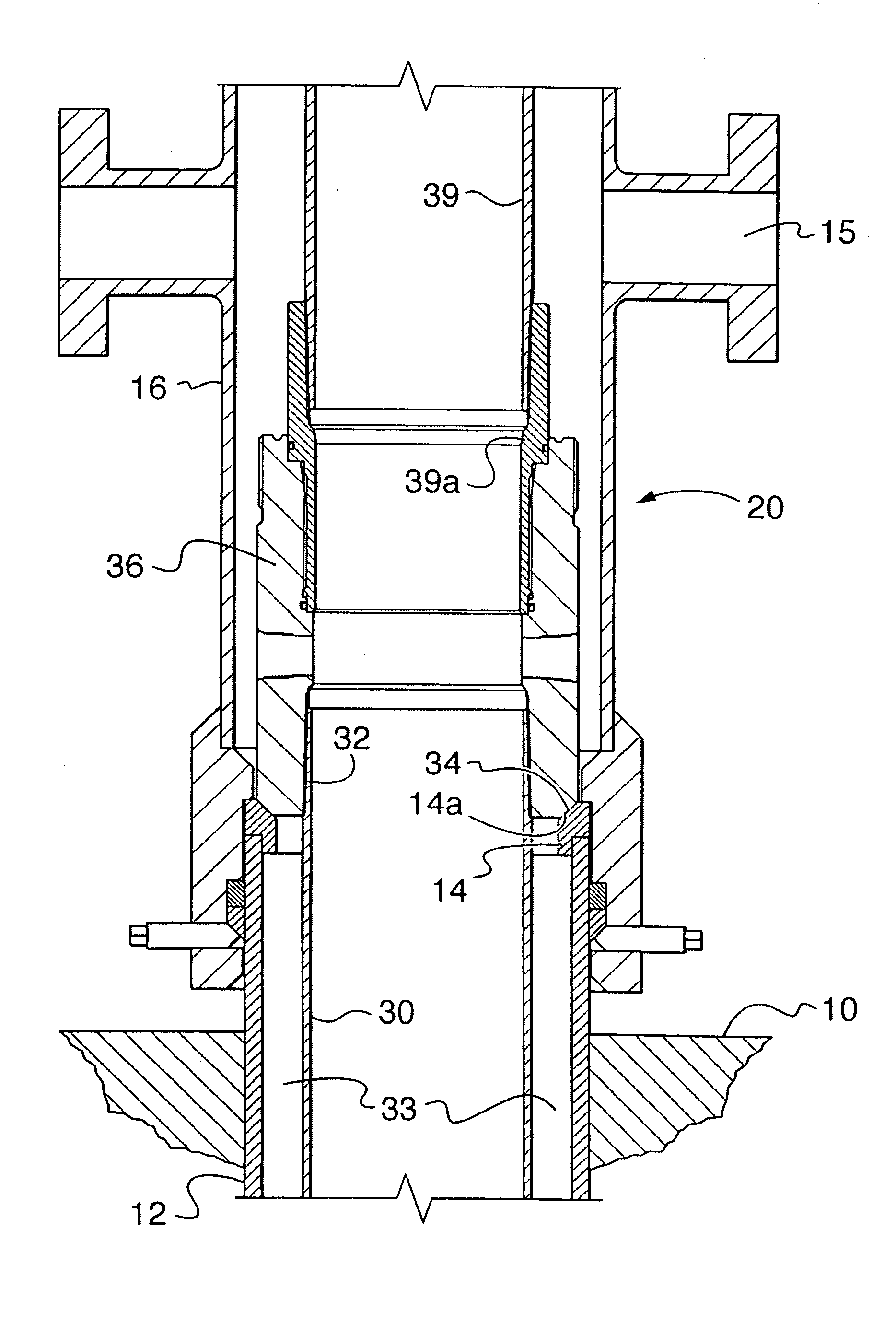

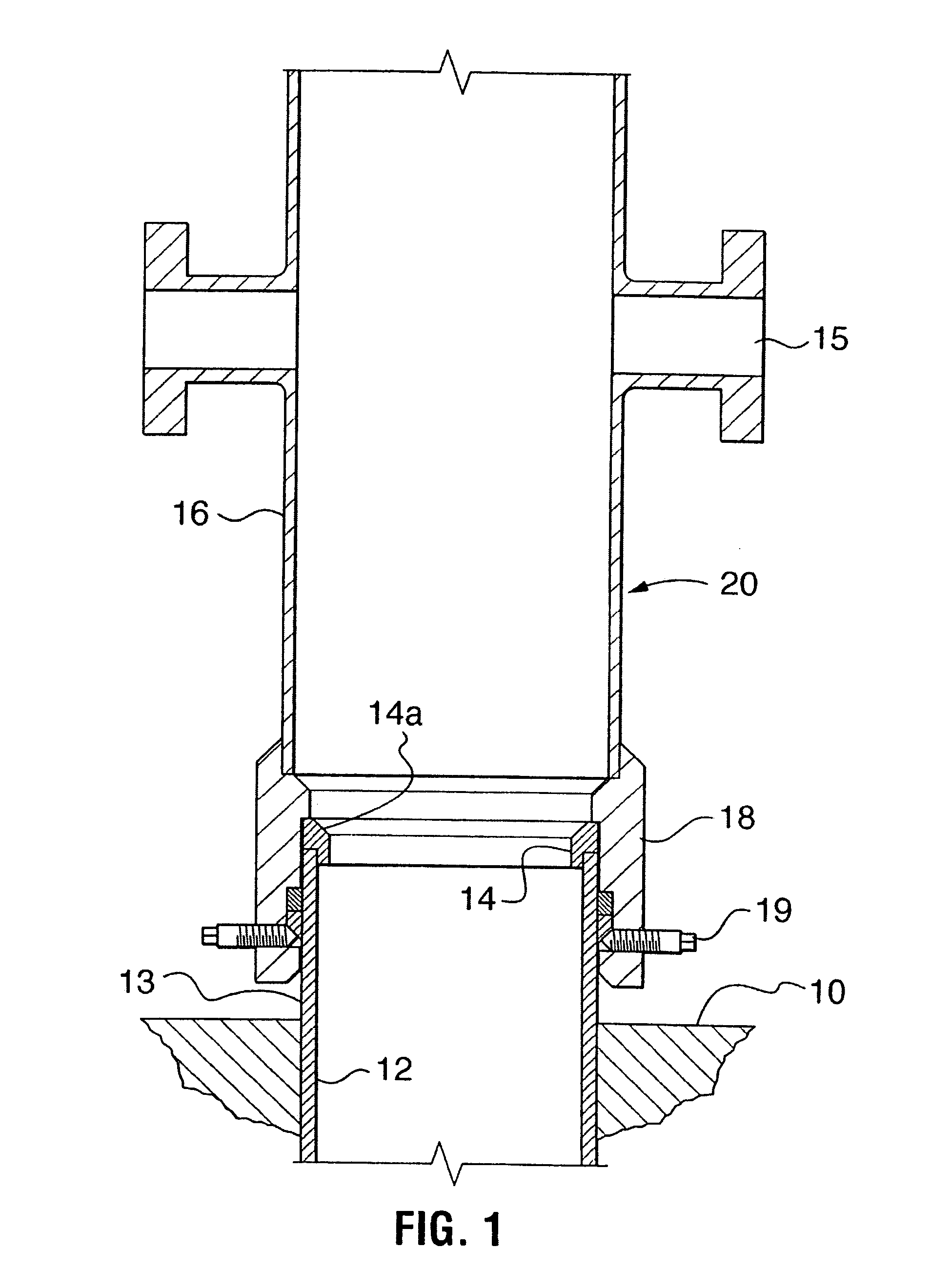

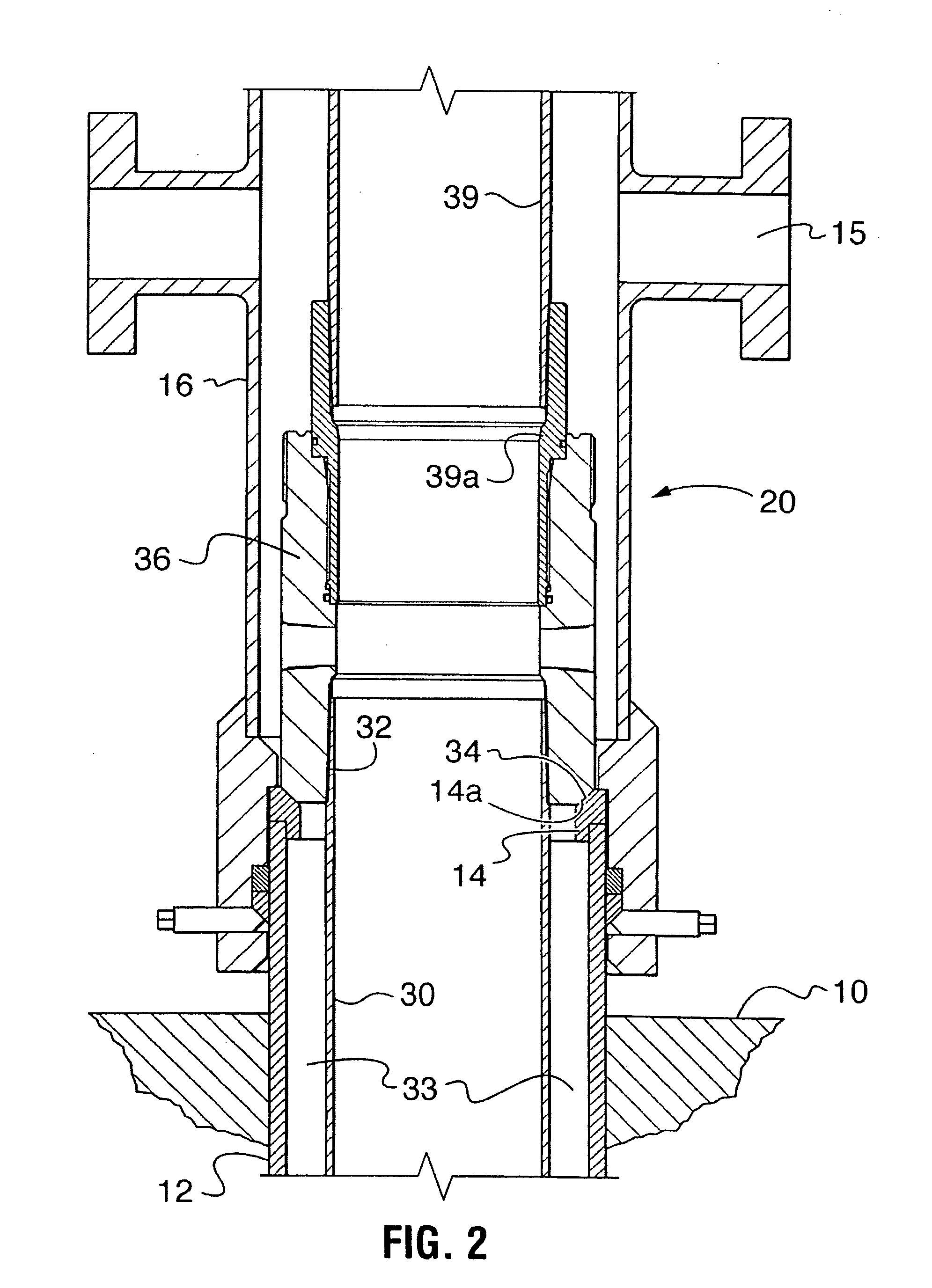

Hybrid wellhead system and method of use

A hybrid wellhead system is assembled using a plurality of threaded unions, such as spanner nuts or hammer unions, for securing respective tubular heads and a flanged connection for securing a flow control stack to a top of a tubing head spool. The tubing head spool is secured by a threaded union to an intermediate head spool. The intermediate head spool is secured by another threaded union to a wellhead. Each tubular head secures and suspends a tubular string in the well bore. The hybrid wellhead system is capable of withstanding higher fluid pressures than a conventional independent screwed wellhead, while providing a more economical alternative to a flanged, or ranged, wellhead system because it is less expensive to construct and faster to assemble.

Owner:WELLS FARGO BANK NAT ASSOC +1

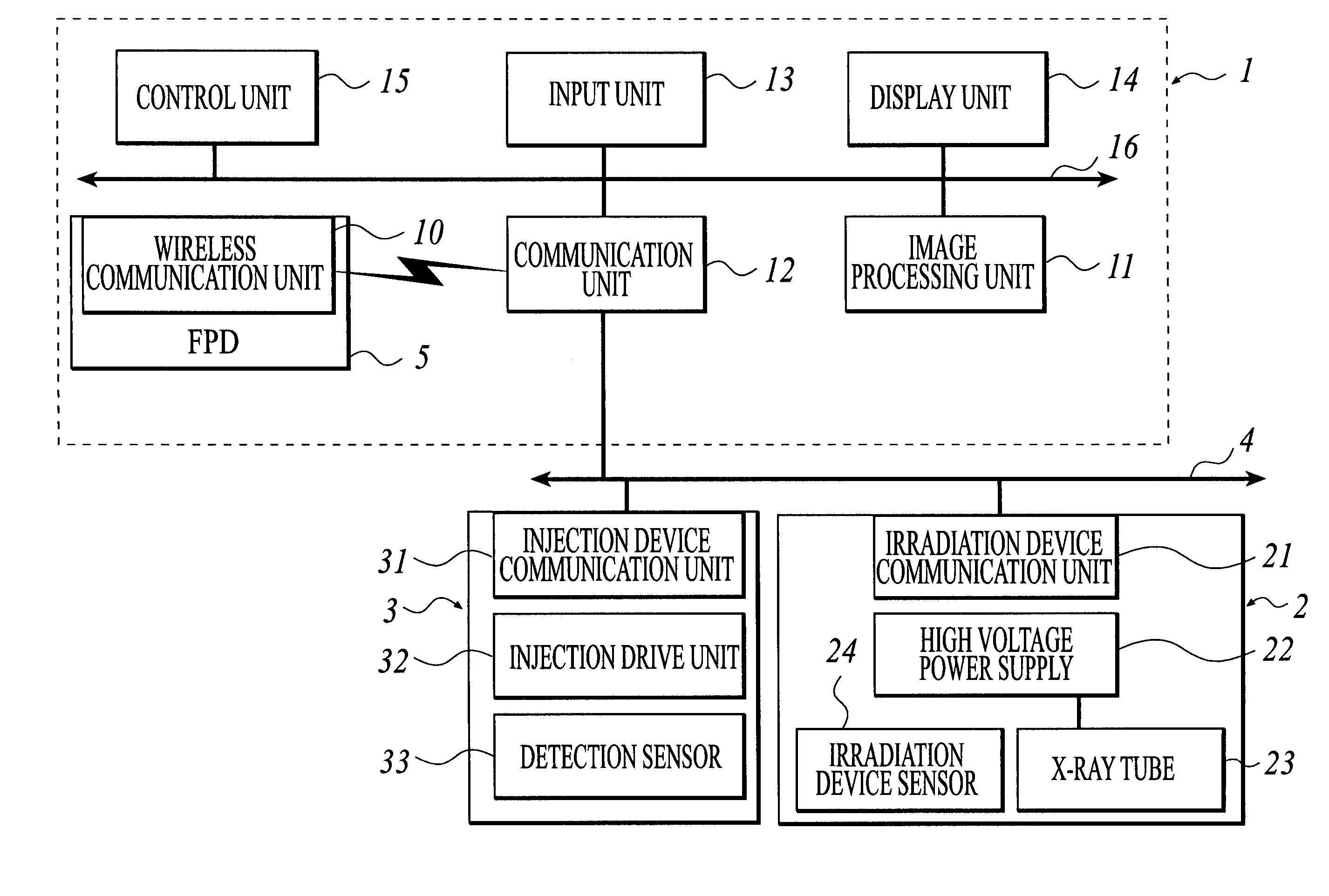

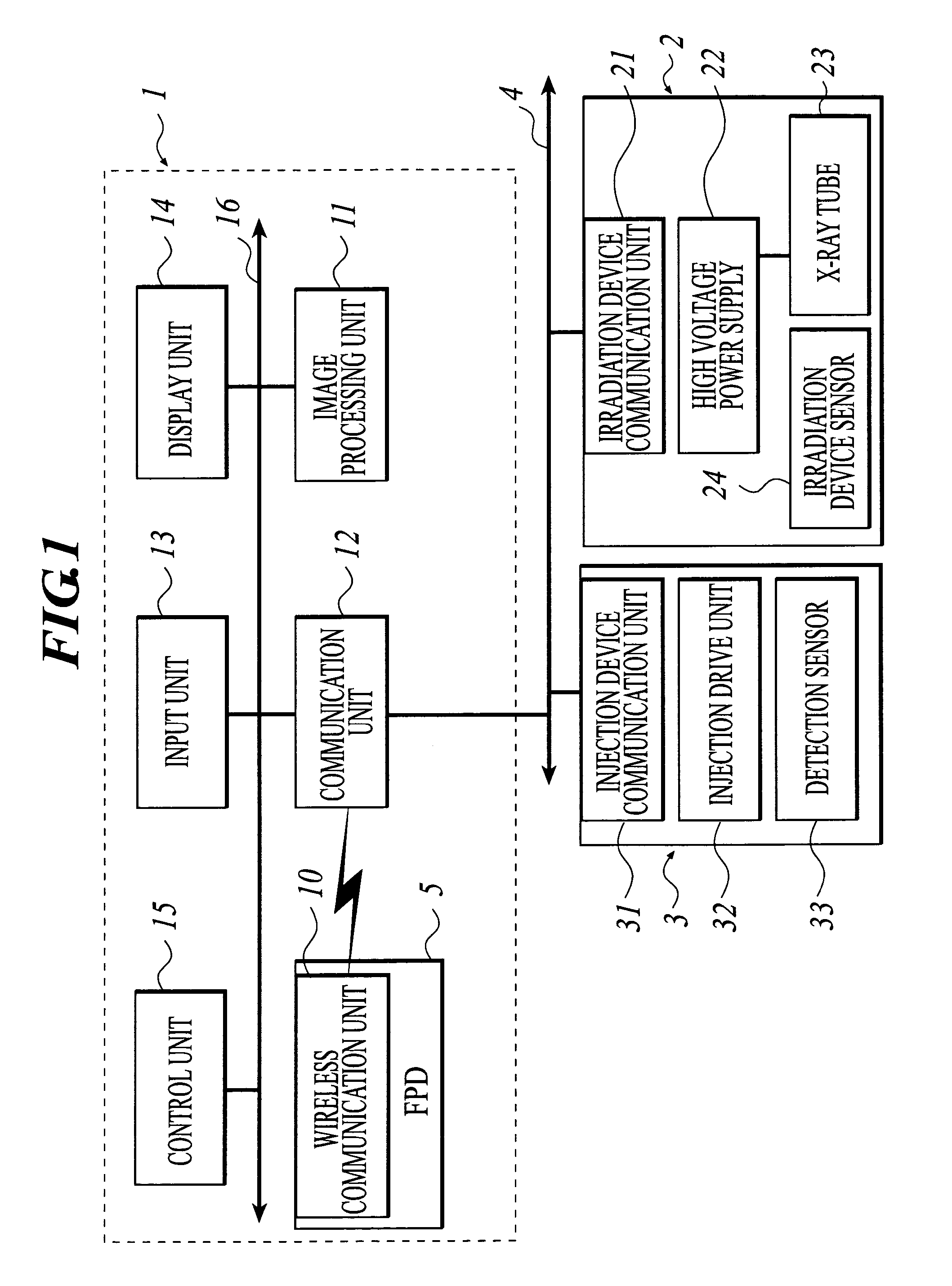

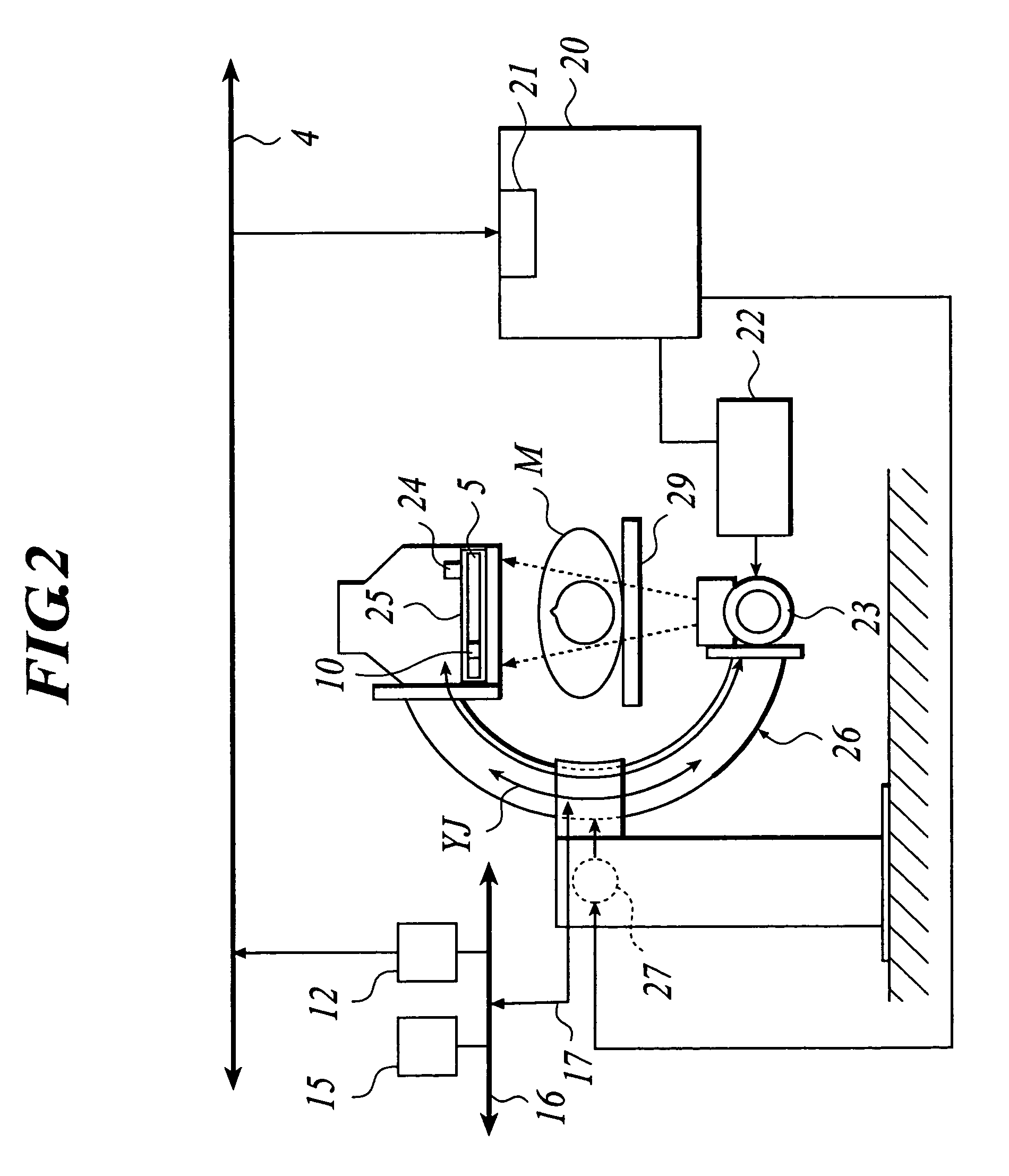

Radiographic imaging apparatus, radiographic imaging program and information recording medium

InactiveUS20050228273A1Improve efficiencyLess costDiagnostic recording/measuringSensorsCommunication unitImaging equipment

A radiographic imaging apparatus includes: a plane detection device to obtain radiographic image; an injection device communication unit to perform communication with an injection device which automatically injects a contrast agent; an irradiation device communication unit to perform communication with an irradiation device; an input unit; a control unit including a plurality of control modes including a linking mode of allowing linking among a timing contrast agent injection, a timing of obtaining a radiographic image and a timing of the irradiation, the control unit controlling the injection device, plane detection device and irradiation device in a control mode selected from the plurality of control modes; and a judgment unit to judge whether control in the linking mode by the control unit is possible, wherein selection of the linking mode is possible only when the judgment unit has judged that the linking mode is possible.

Owner:KONICA MINOLTA MEDICAL & GRAPHICS INC

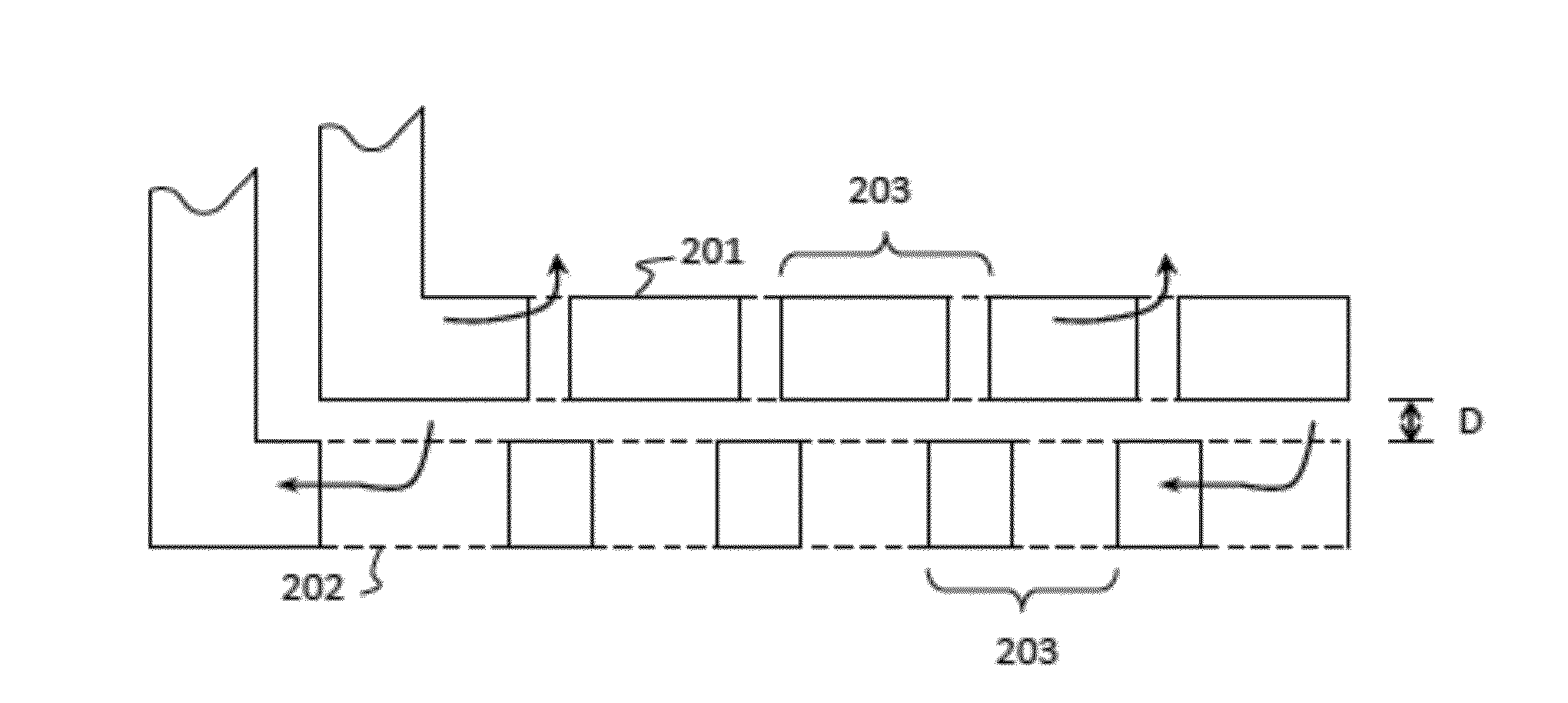

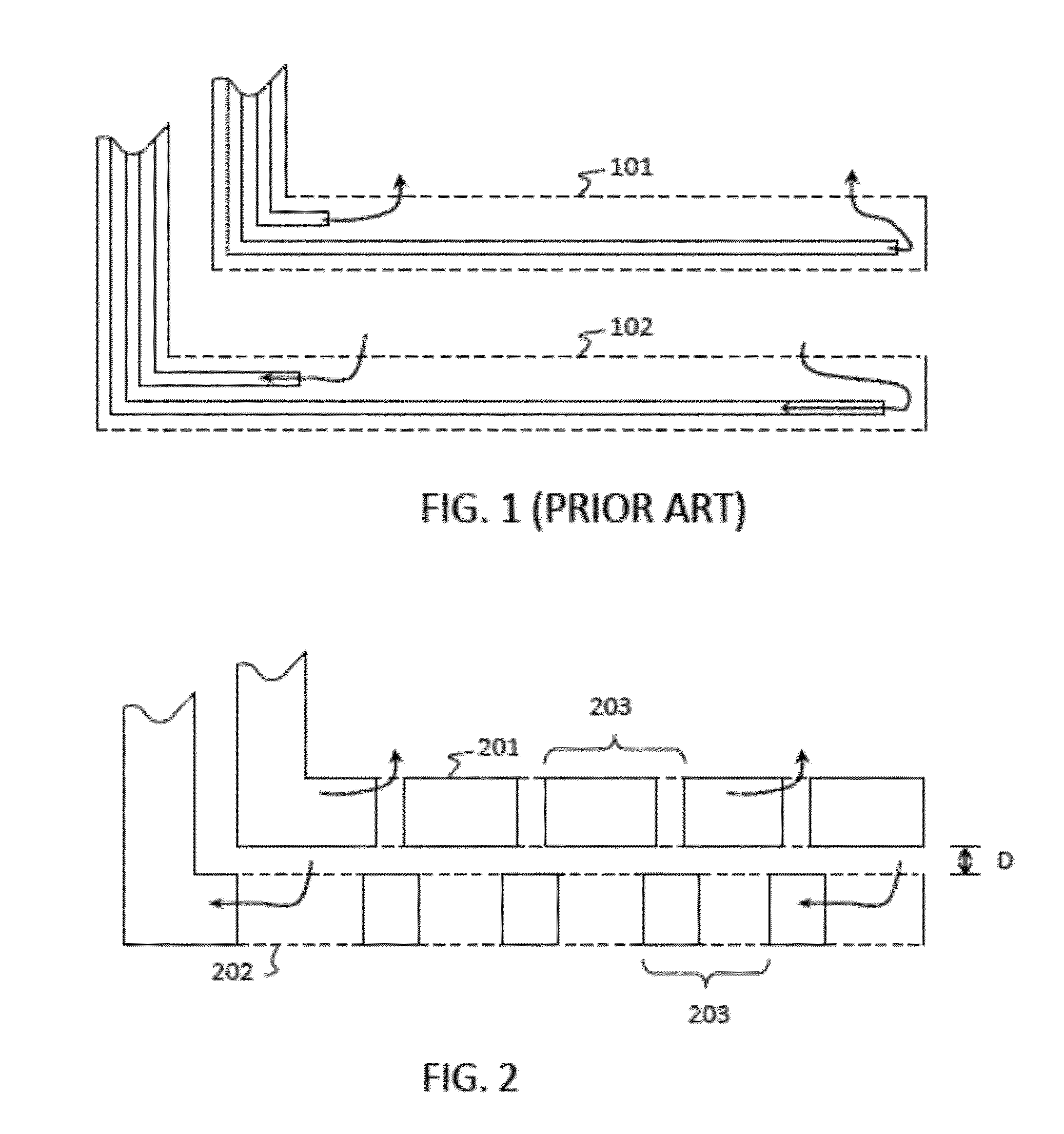

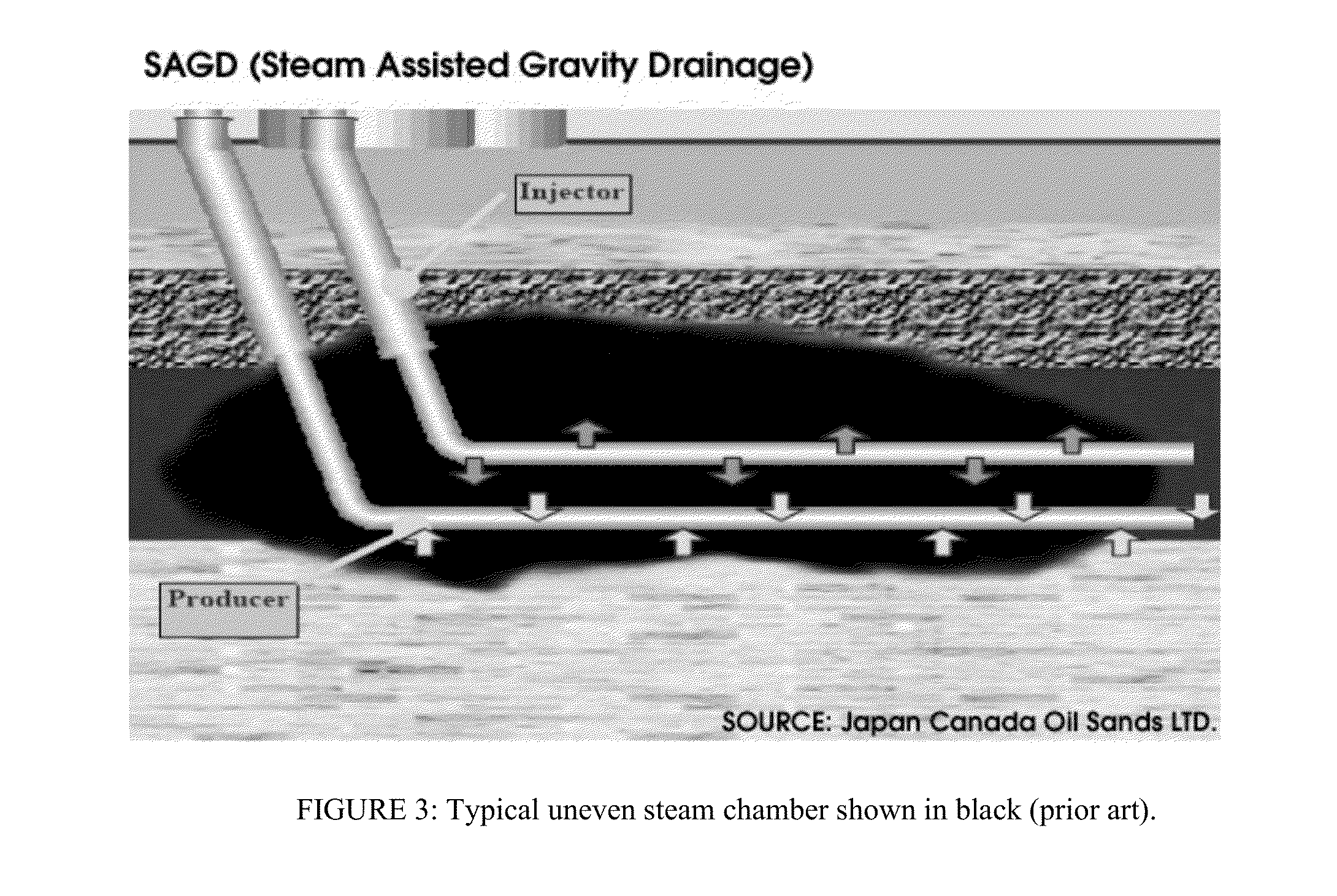

Sagd steam trap control

ActiveUS20130213652A1Reduce startup timeLow costFluid removalDrinking water installationStart up timeEngineering

This present disclosure describes methods and systems related to SAGD injection and / or production wells that utilize flow distribution control devices. Additionally, methods and systems using limited vertical spacing separating the wells are described. These methods and systems improve steam assisted gravity drainage (SAGD) oil production, reduce SAGD start-up time and costs, and improve overall SAGD performance.

Owner:CONOCOPHILLIPS CANADA RESOURCES +2

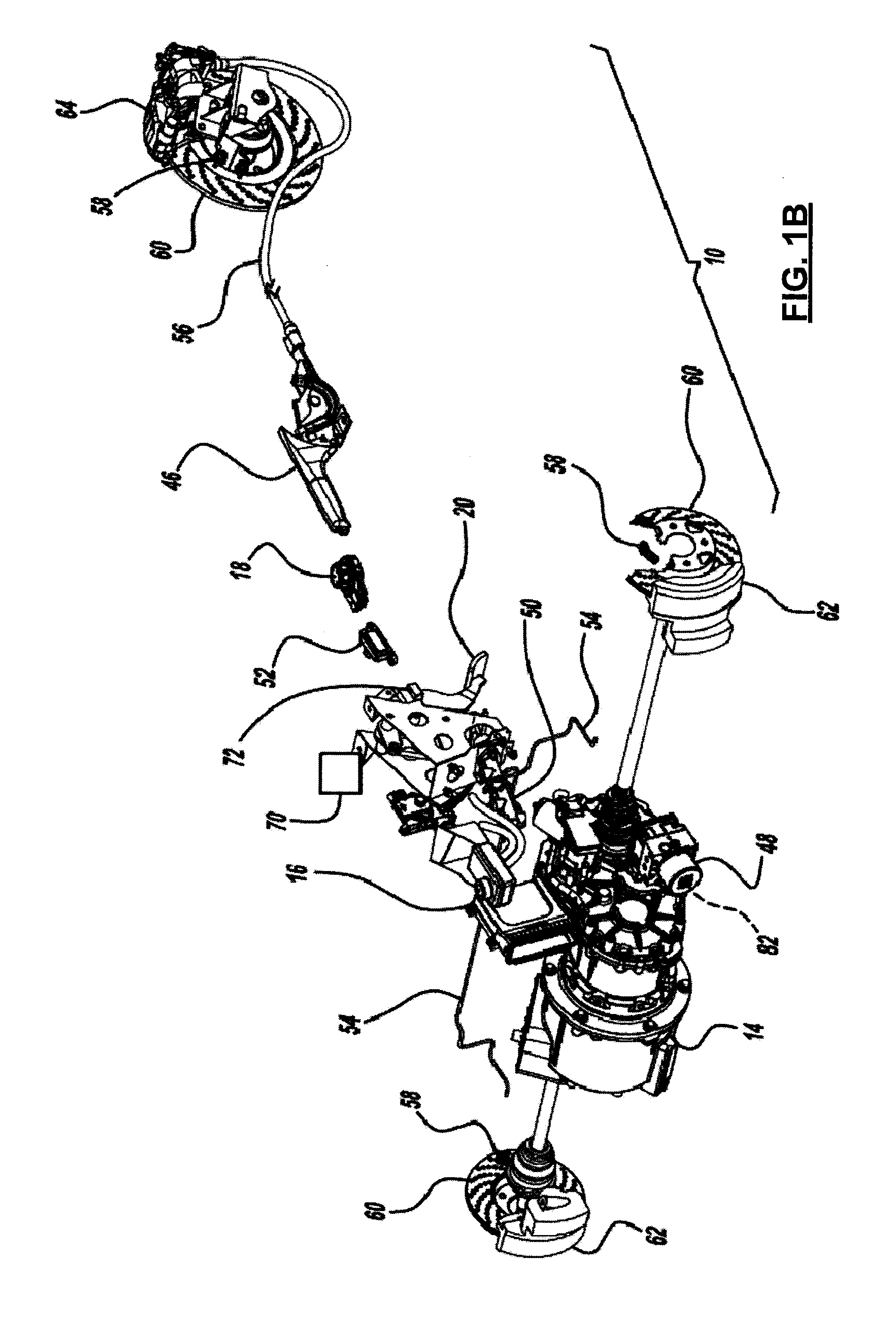

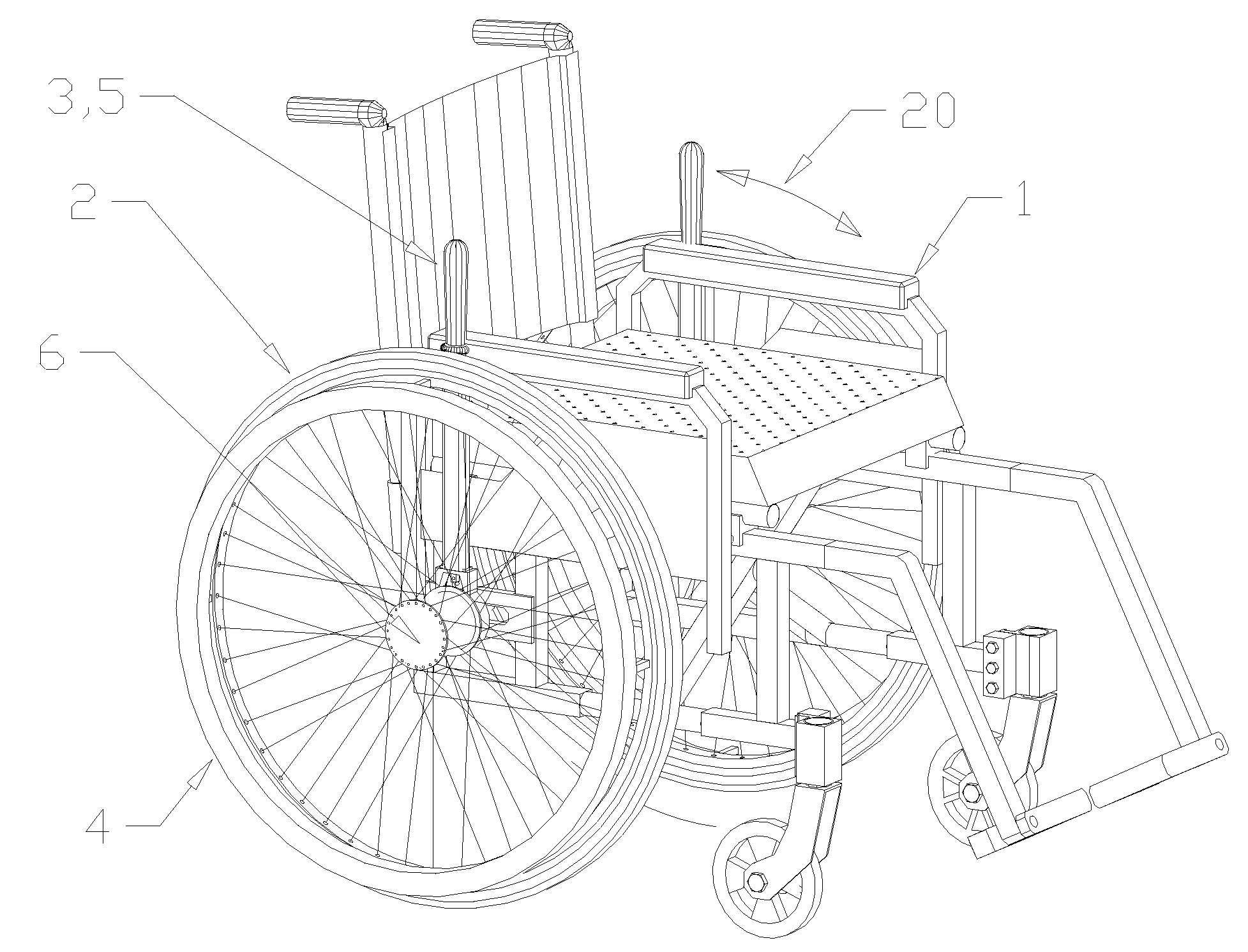

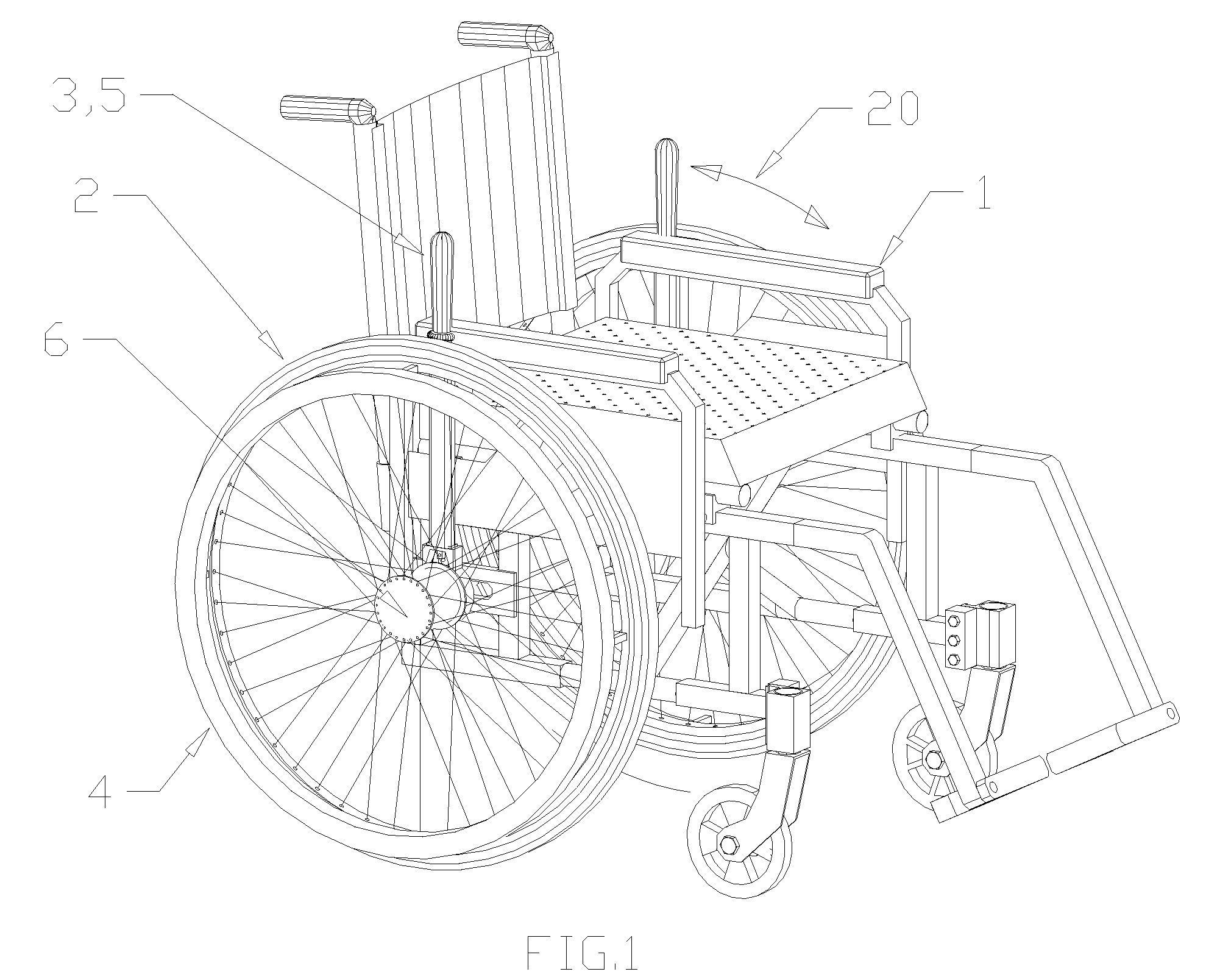

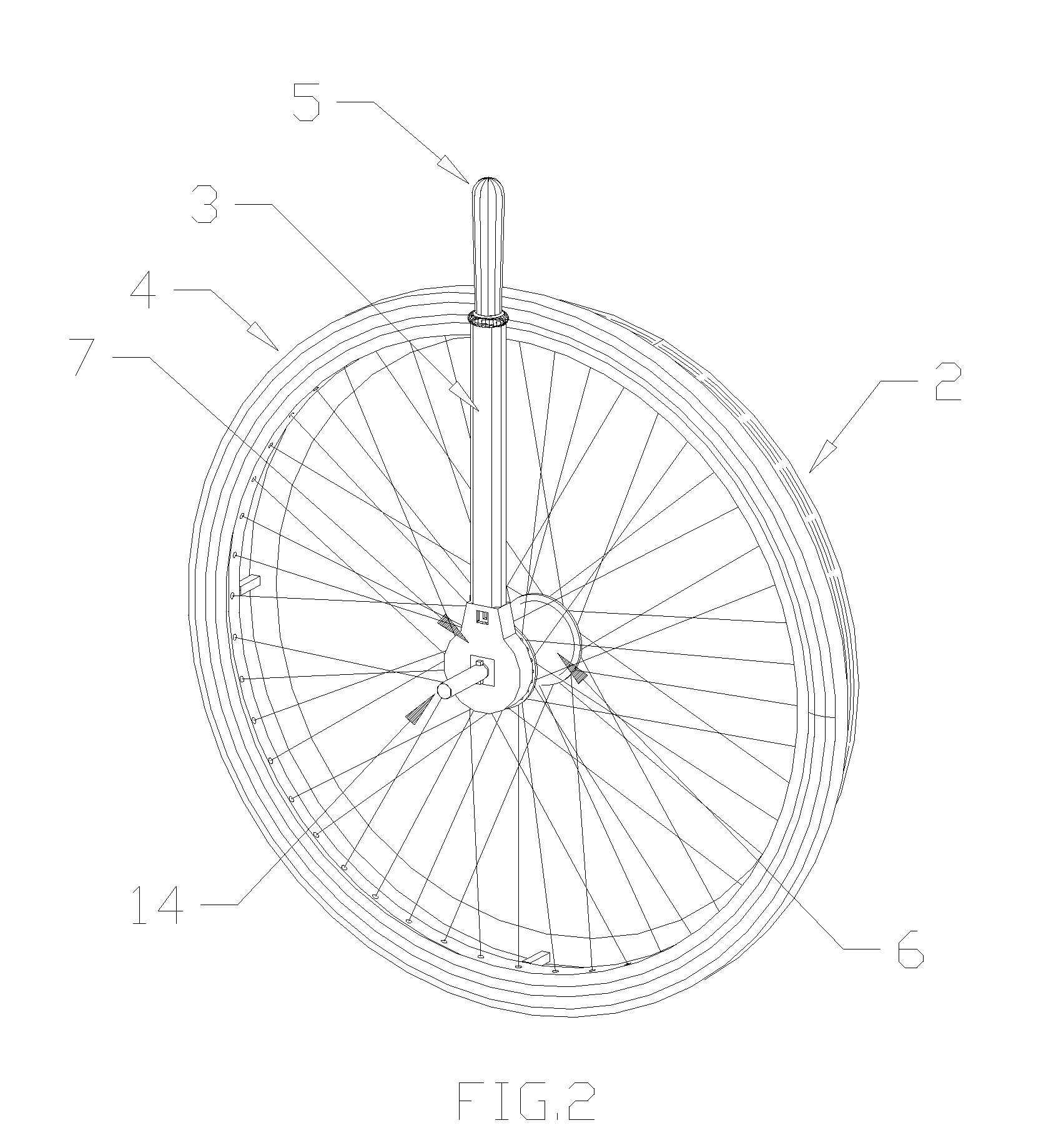

Lever Drive Wheelchair Transmission

InactiveUS20090206574A1Protection from damageLess complexityGearingWheelchairs/patient conveyanceWheelchair userEngineering

A manual propulsion mechanism for wheelchairs utilizes a lever pivotally mounted to the hub of each rear wheel such that the wheelchair user can propel the chair with push / pull movements of the levers. Forward and reverse propulsion directions are accomplished by a system of one-way reversible clutches contained in the propulsion wheel hubs which also allow the levers to be operationally disconnected such that the chair can freewheel. Operator control of direction shifting is through twisting motions imparted to the grip handles of the propulsion levers. In a preferred embodiment, improved ergonomics for propulsion direction changes are made possible by an improved short excursion clutch shifting mechanism that reduces the angle of arc through which the operator must twist the grip handle to effect the direction change. This allows the operator to retain a comfortable, stable grip on the grip handle while simultaneously propelling and controlling direction of movement.

Owner:GREEN STEVE C

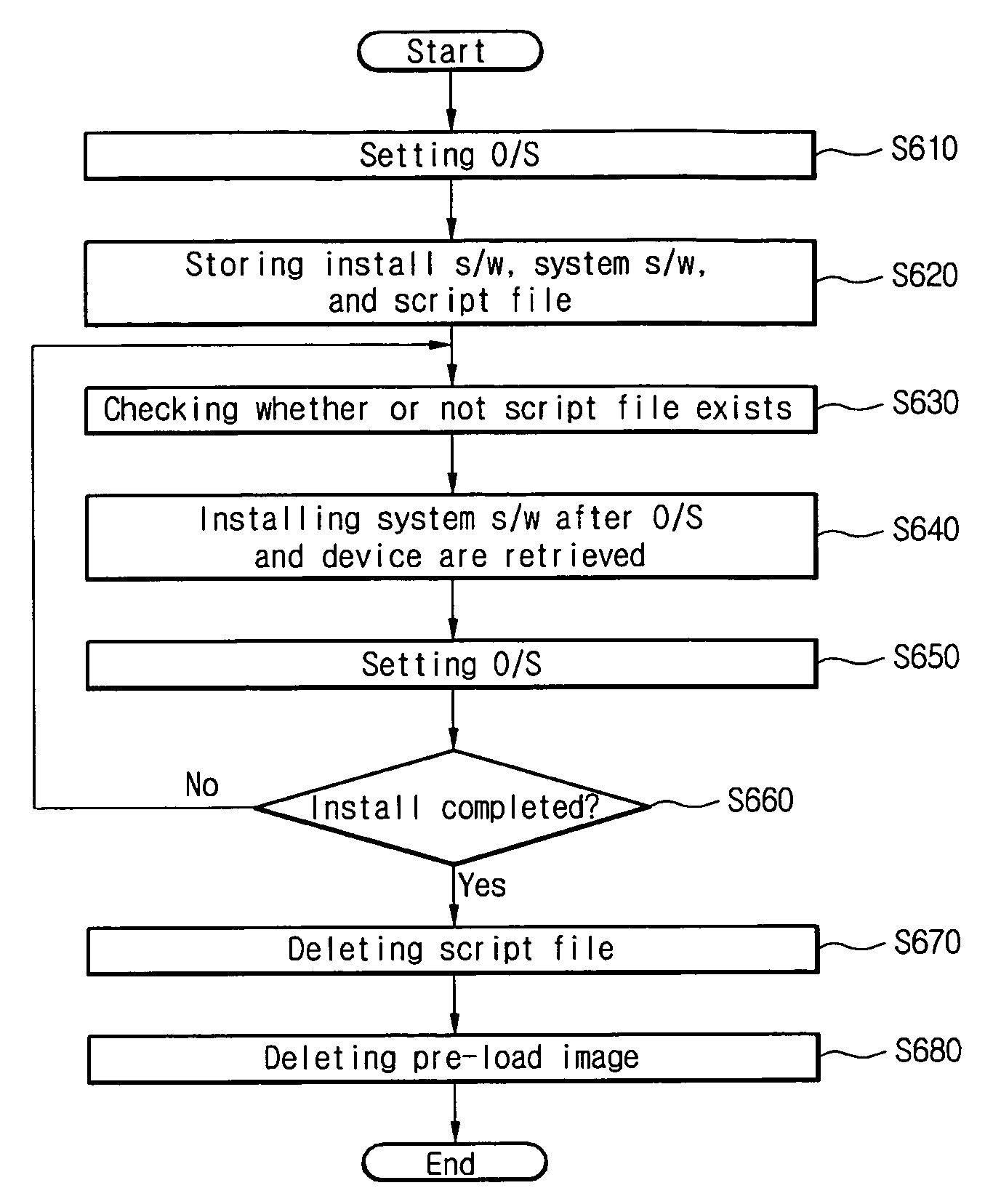

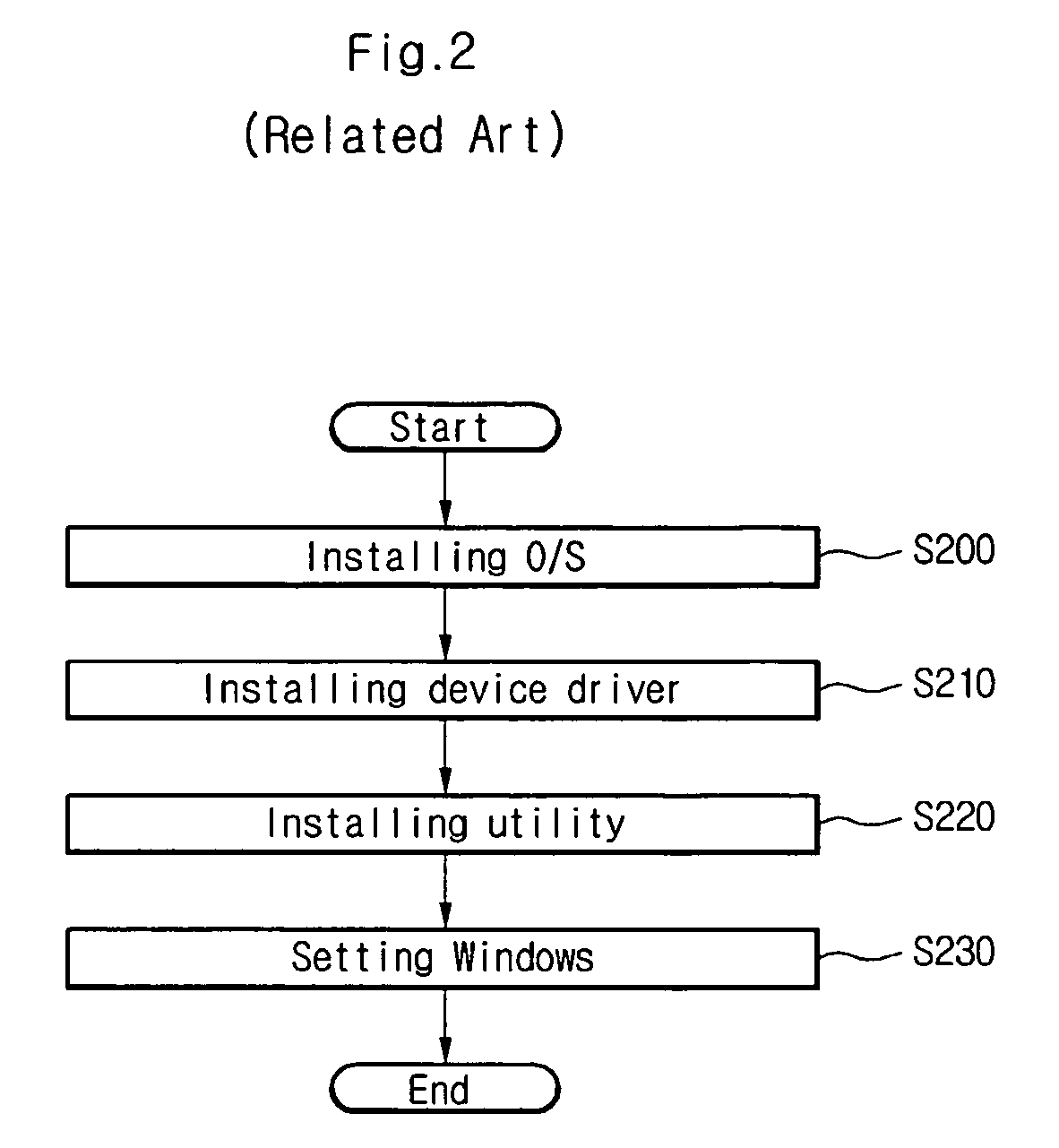

Computer system, system software installation method, and software installation method of portable computer

InactiveUS20070006220A1Less timeLess costProgram loading/initiatingMemory systemsSoftware engineeringControl unit

Embodiments of a computer system, and a software installation method thereof are described. An embodiment of a computer system can include a system for installing an O / S (Operating / System) and a part of system software; a storage unit for storing a plurality of system software, which can be installed depending on various O / Ses or devices; and a controlling unit for selectively installing system software, which is required for the system, among the stored plurality of system software.

Owner:LG ELECTRONICS INC

Method for manufacturing a fluid pressure measurement unit and a component for being used in a fluid pressure measurement unit

InactiveUS7373826B2Less costLess time consumingPrinted circuit assemblingLine/current collector detailsChip carrierElectrical and Electronics engineering

A fluid pressure measurement unit is manufactured by steps of providing a measurement element with a measurement chip arranged on a first chip carrier side and a plurality of socket-shaped terminal contacts for contacting contact terminals of the measurement chip, the socket-shaped terminal contacts protruding from a second chip carrier side opposite from the chip carrier first side; providing a housing element comprising a plurality of receiving holes in a housing element first side which are implemented to receive the socket-shaped terminal contacts when combining the housing element with the measurement element, wherein the receiving holes extend from the housing element first side to a housing element second side opposite from the housing element first side; and combining the measurement element and the housing element, wherein the second chip carrier side is opposite from the housing element first side and the socket-shaped terminal contacts are arranged in the receiving holes.

Owner:SMITHS MEDICAL DEUTLAND

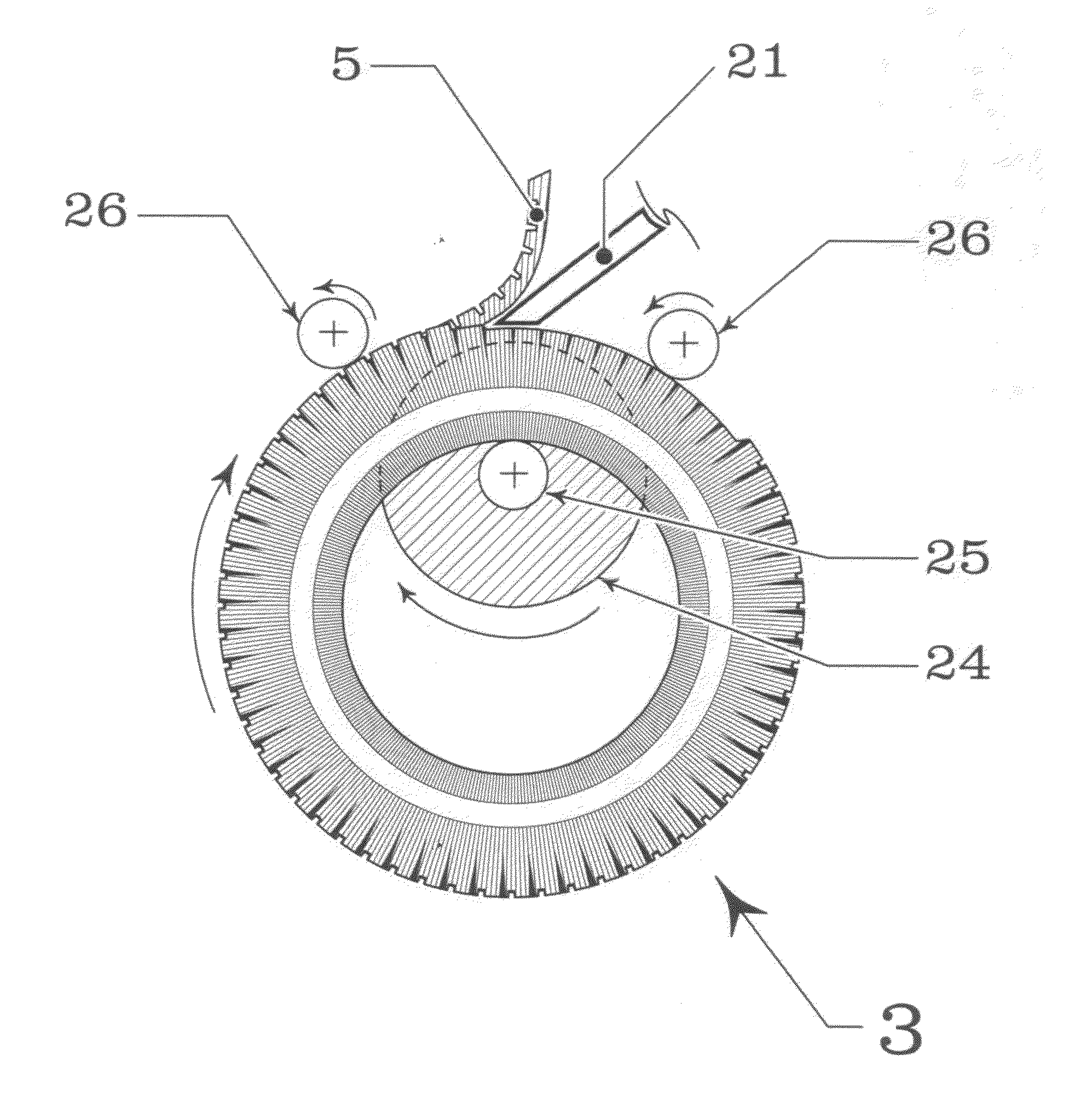

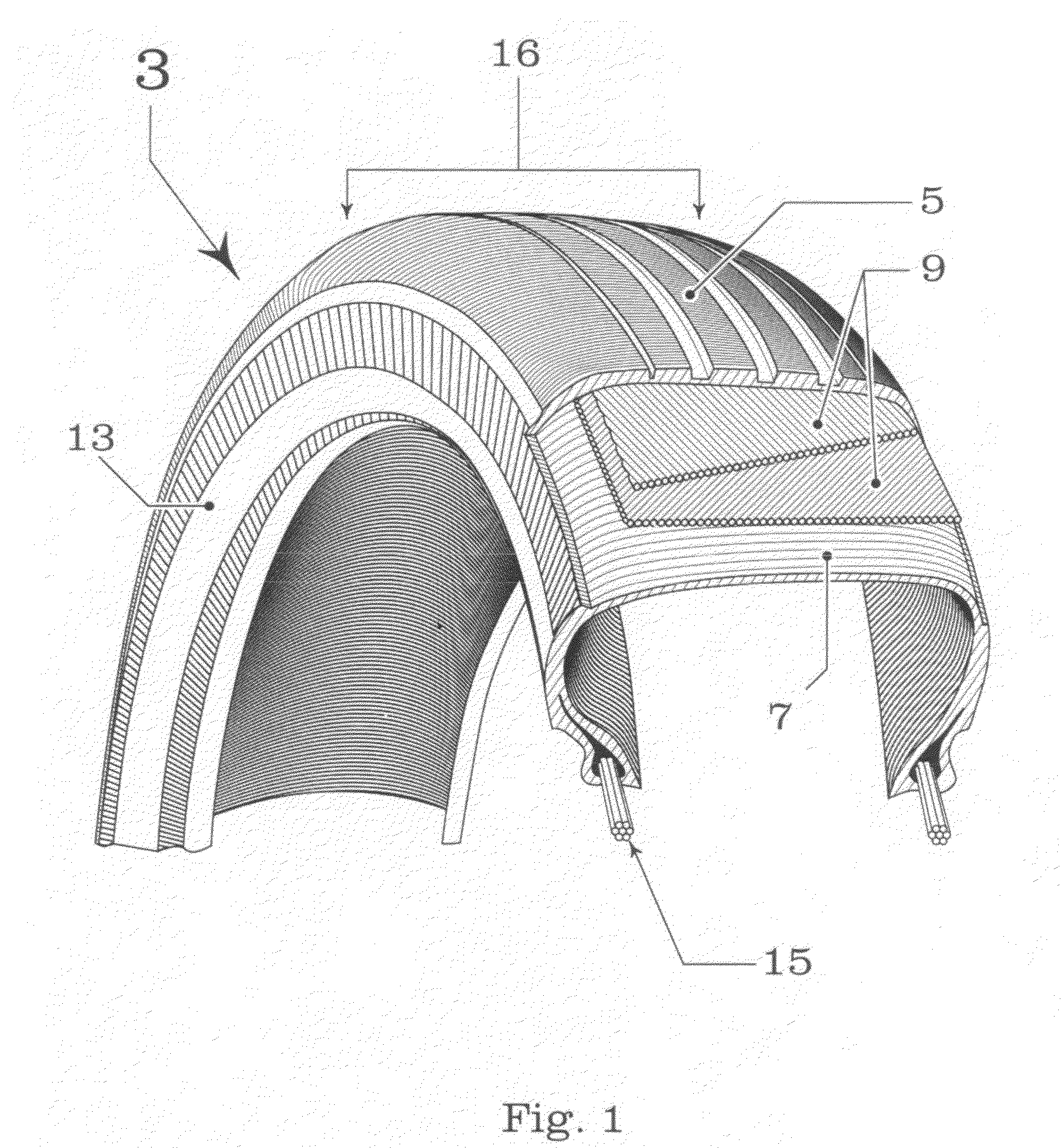

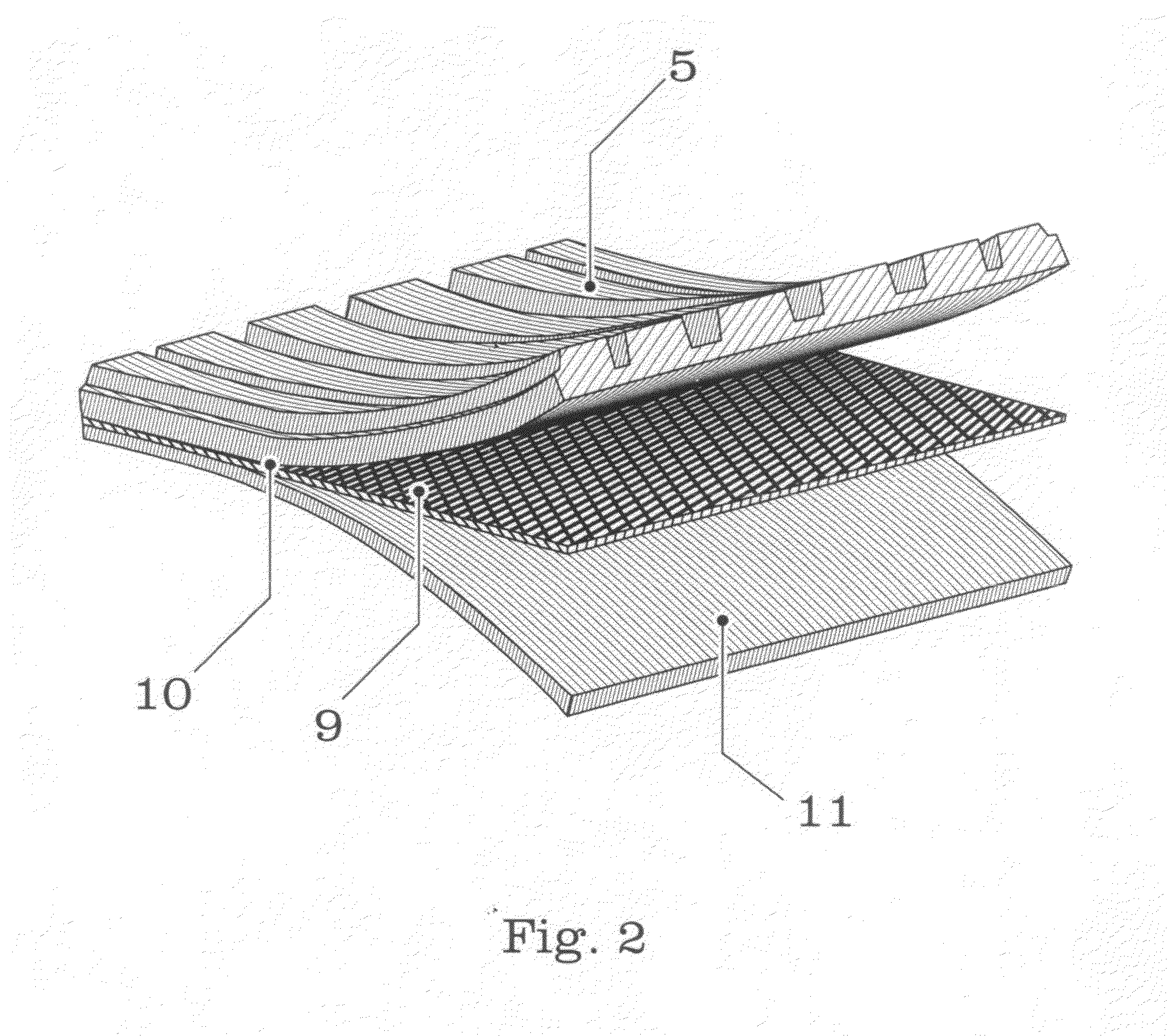

Recovery of high value rubber from tires

InactiveUS20110023668A1Less costReduces energy and maintenance requirementLamination ancillary operationsPaper/cardboard articlesEnvironmental resistanceSteel belt

A process for recovering rubber from a tire, the tire including a rubber tread block, a reinforced portion below the tread block portion, typically known as steel belting, and an inner liner that serves to hold the air pressure in the tire. The bead and sidewall are removed from the tire leaving a loop of tread material. Next, the loop is placed on several rollers of a rubber-separating machine to hold the loop in place. One or more cutting blades, preferably chisels, are positioned at the tread portion of the tire. The cutting blades are lowered into position. Access to the steel belting can be accomplished by making an initial cut through tread block to expose the steel belting. Once the blades are in place, the tread loop is placed in motion around the rollers. As the blades contact the steel belts, the cutting blades separate the tread rubber from the reinforced rubber at the interface between the tread rubber and the steel belts. The inner layer may also be removed in a similar fashion with blades positioned within the loop rather than above it.The ultimate goal of the present invention is to provide an environmentally and economically beneficial process that disposes of all the parts of the tire. Using the cutting blades or chisel(s) to separate the rubber in a tire's tread area from the embedded steel results in the following tire parts: 1) high value metal free rubber from the tread area; 2) the steel belt / thin layer of rubber / steel belt (with or without the inner liner); 3) the inner liner with polyester or similar fiber; 4) the metal free sidewall with polyester or similar fiber; and 5) the tire bead surrounded with rubber and polyester or similar fiber.

Owner:RUBBER RECOVERY SOLUTIONS

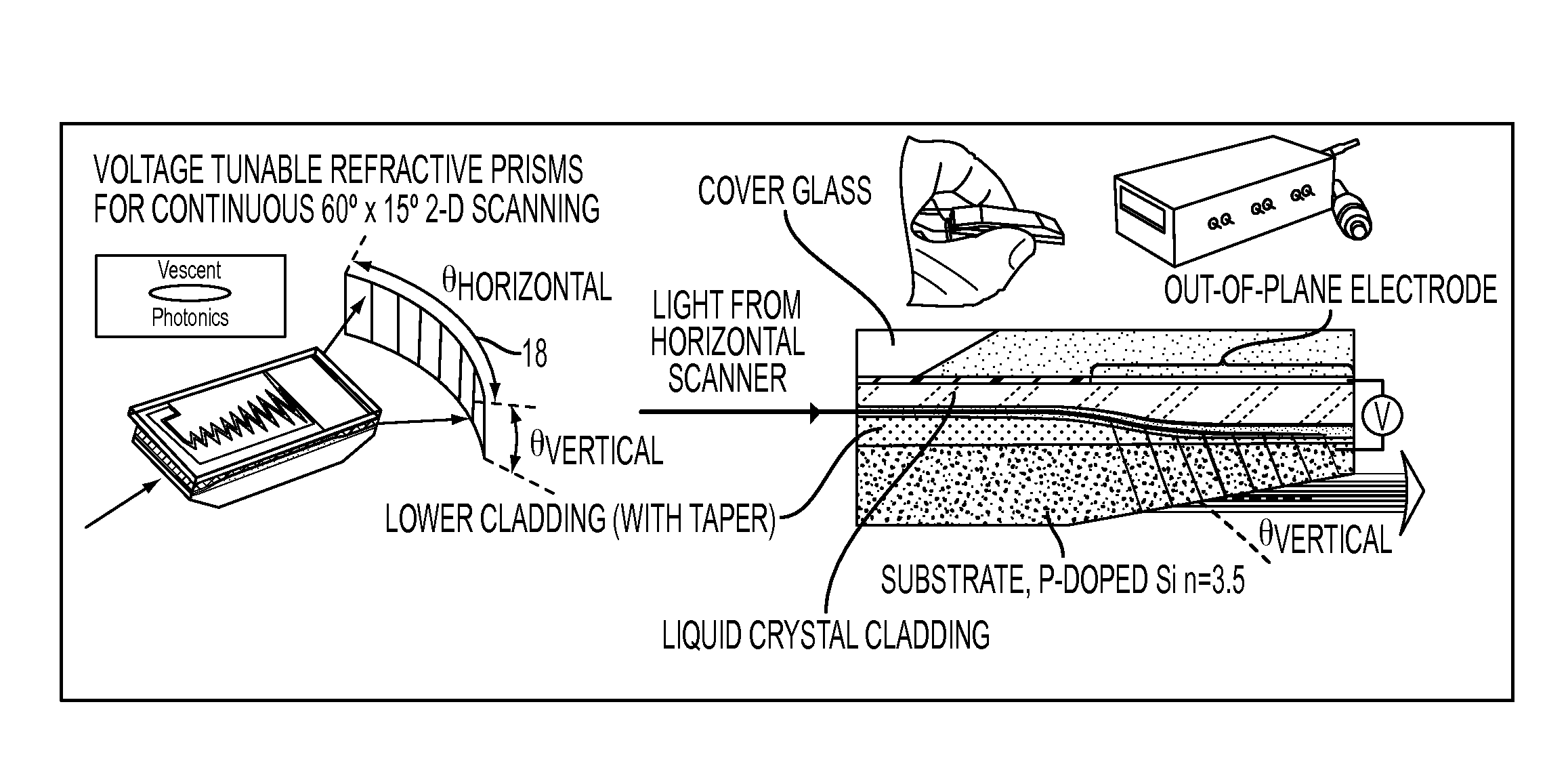

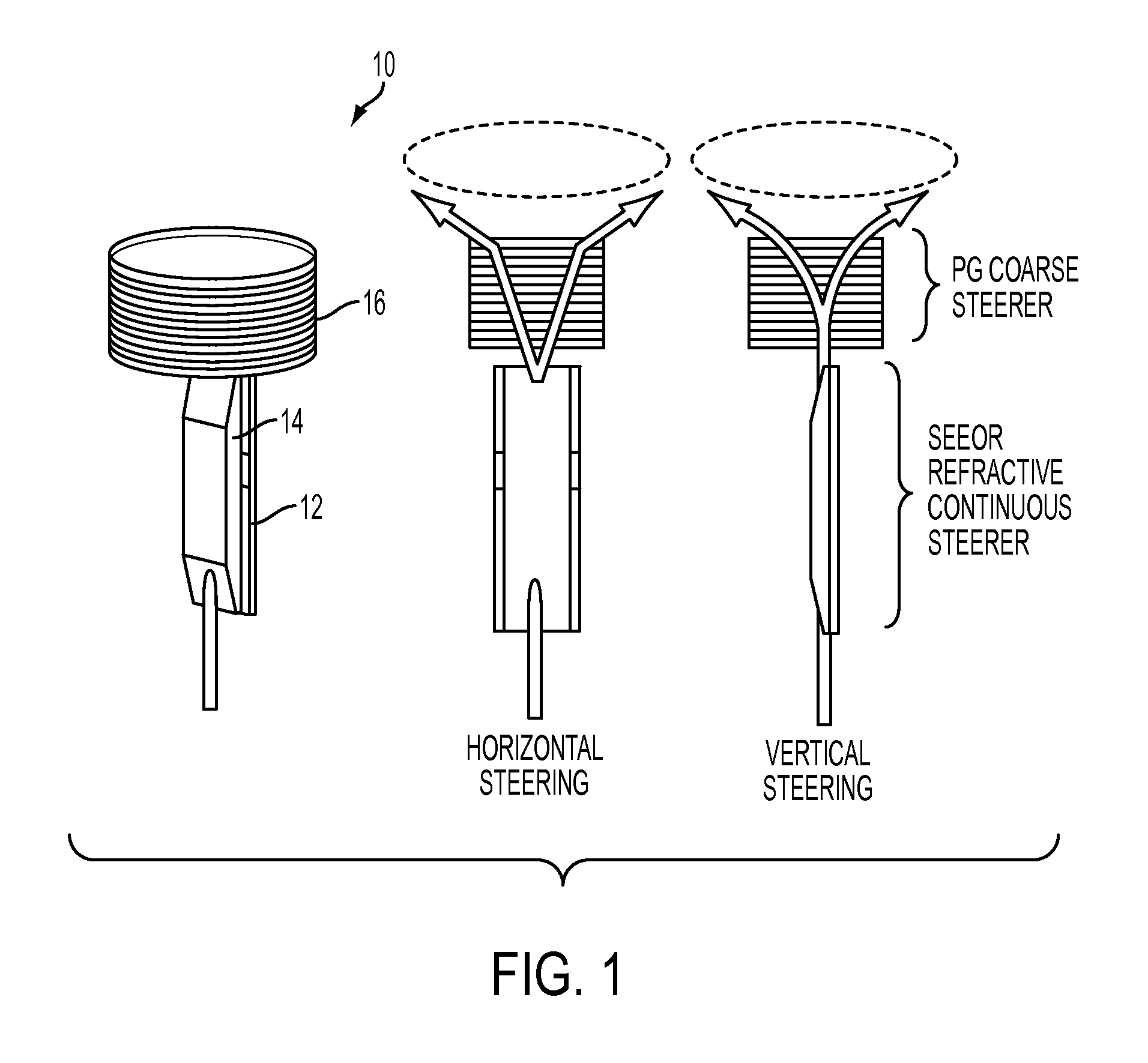

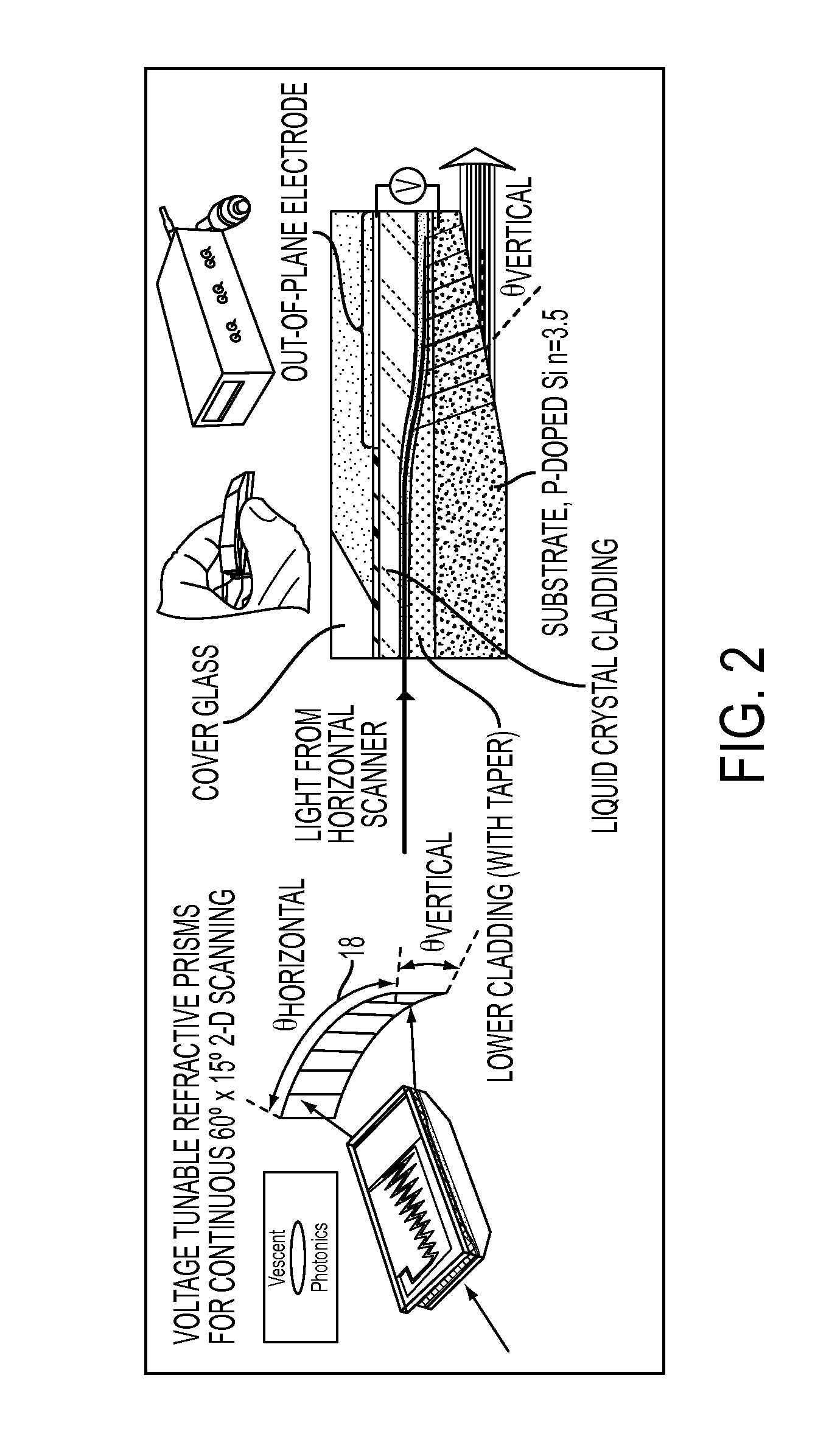

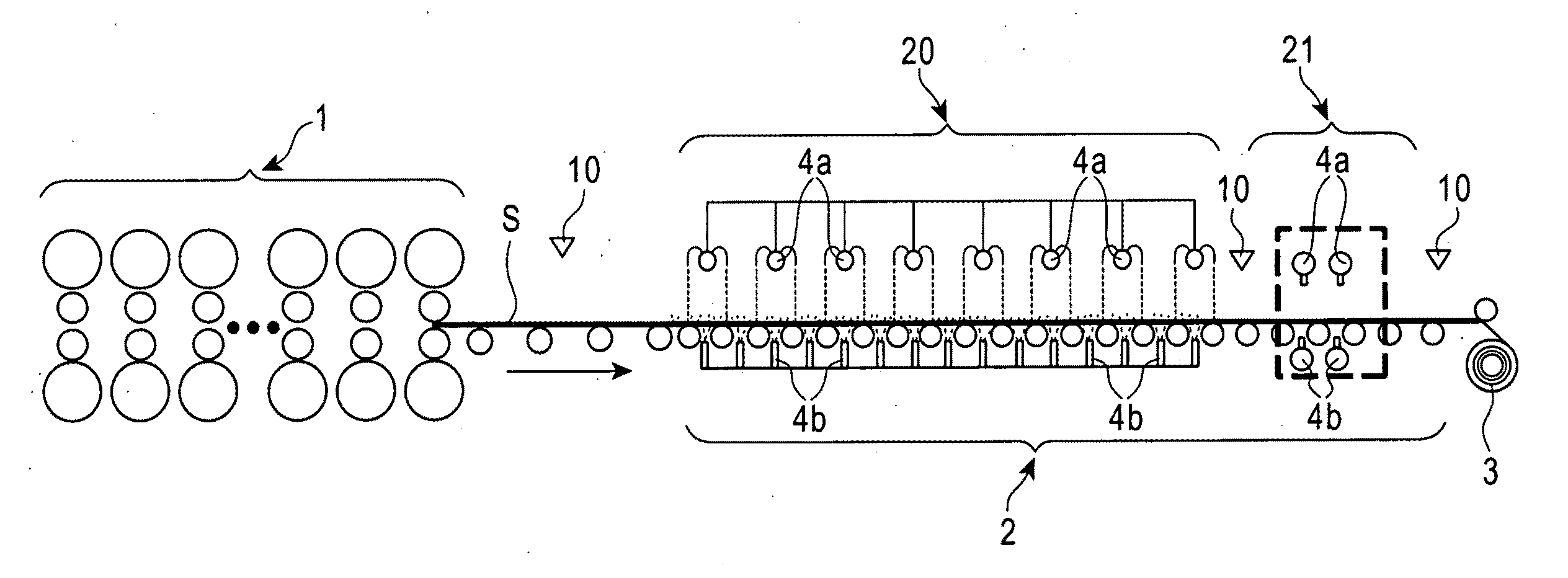

Non-mechanical beam steering tracking system

ActiveUS20150378242A1Less complexityLess costCoupling light guidesNon-linear opticsGratingBeam steering

A non-mechanical optical beam steering device includes one or more polarization gratings (PG) coupled to one or more Steerable Electro-Evanescent Optical Refractors (SEEOR). It provides the coarse steering advantage of the PG and also the continuous fine steering advantage of the SEEOR. The result is far less complexity, size, weight, and cost over the alternative non-mechanical beam steering approaches as well as considerably less complexity, size, weight, cost, scanning-time, and mechanical breakdown over the more traditional gimbaled mirrors commonly used.

Owner:THE GOVERNMENT OF THE UNITED STATES OF AMERICA AS REPRESENTED BY SEC OF THE NAVY

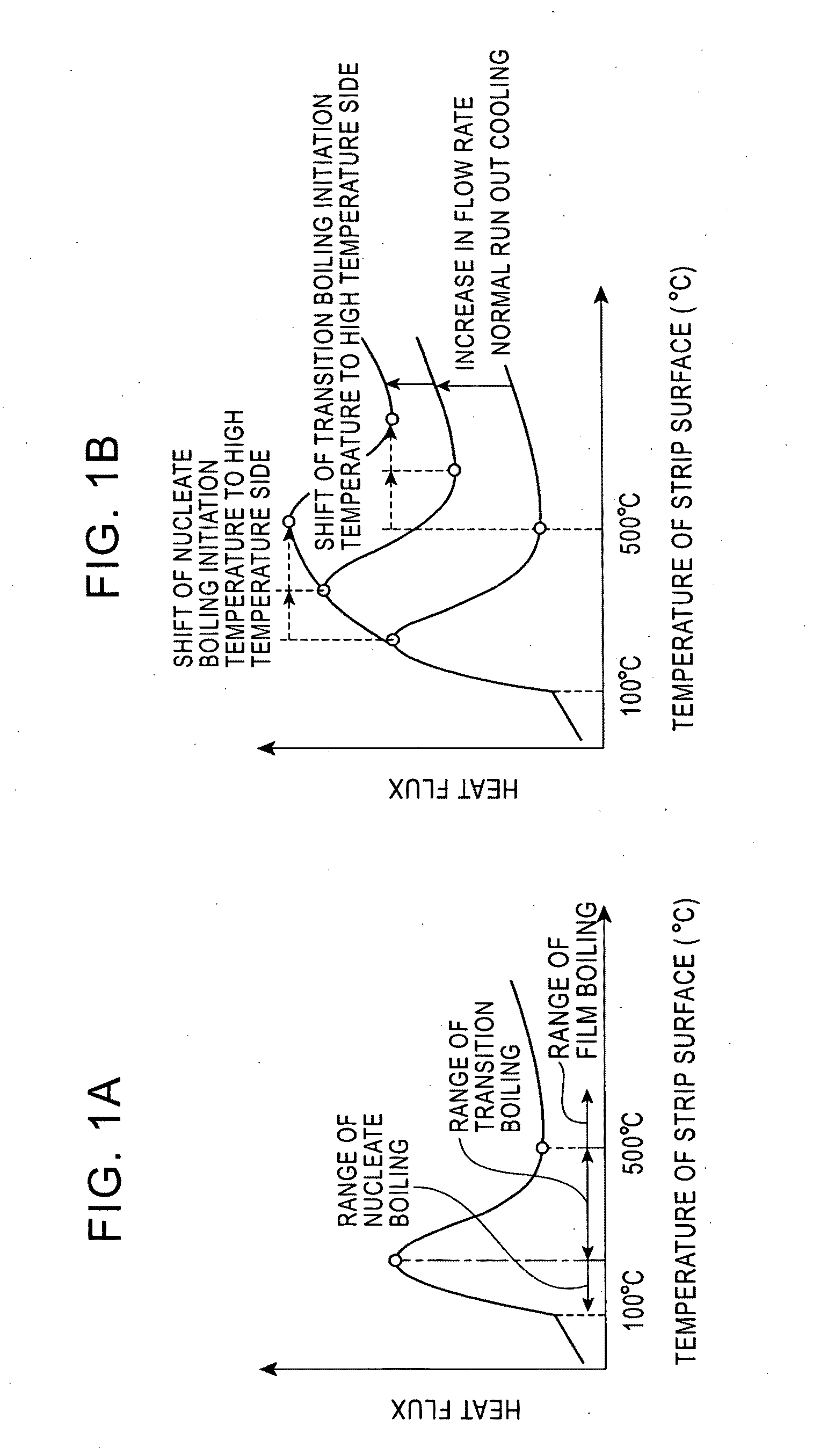

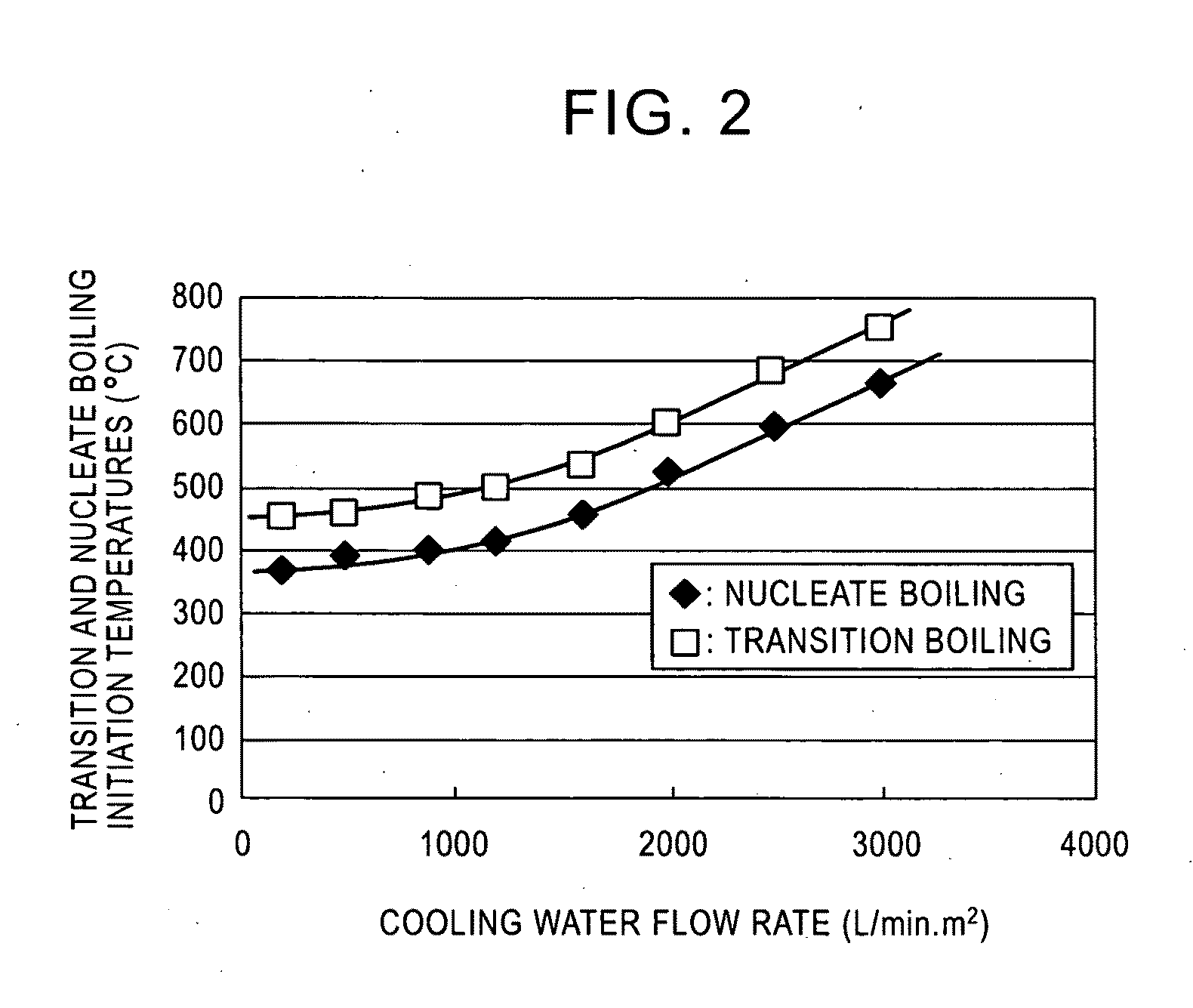

Method for cooling hot strip

ActiveUS20100192658A1Reduce temperature changesAvoid instabilityShaping toolsTemperature control deviceThermal instabilityWater flow

A method for cooling a hot strip with less facilities and processing costs in which the temperature variation of a strip after cooling is controlled to be small and a cooling end temperature can be precisely controlled particularly when the hot strip is cooled to the temperature range of 500° C. or less is provided. The method for cooling a hot strip, which is obtained after a hot rolling process, by bringing cooling water into contact with the hot strip, includes a first cooling step and a subsequent second cooling step. In this method, cooling is stopped at a strip temperature that is higher than a transition boiling initiation temperature in the first cooling step, and the cooling is conducted using the cooling water having a water flow rate that causes nucleate boiling in the subsequent second cooling step. Entering the temperature range of transition boiling can be completely prevented to avoid thermal instability in cooling resulting from the transition boiling, and the temperature variation of the strip after cooling is controlled to be small while the cooling end temperature can be precisely controlled.

Owner:JFE STEEL CORP

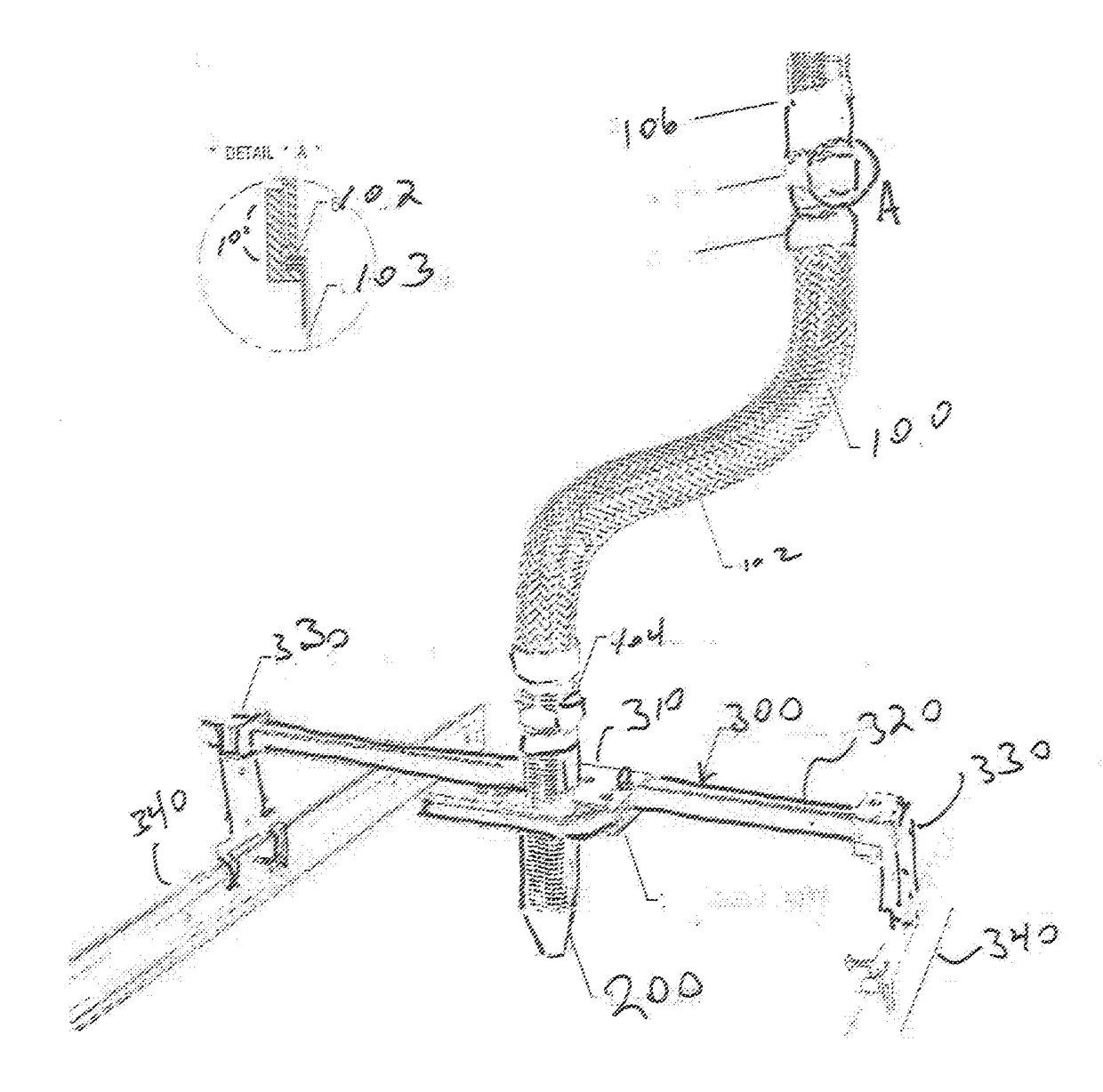

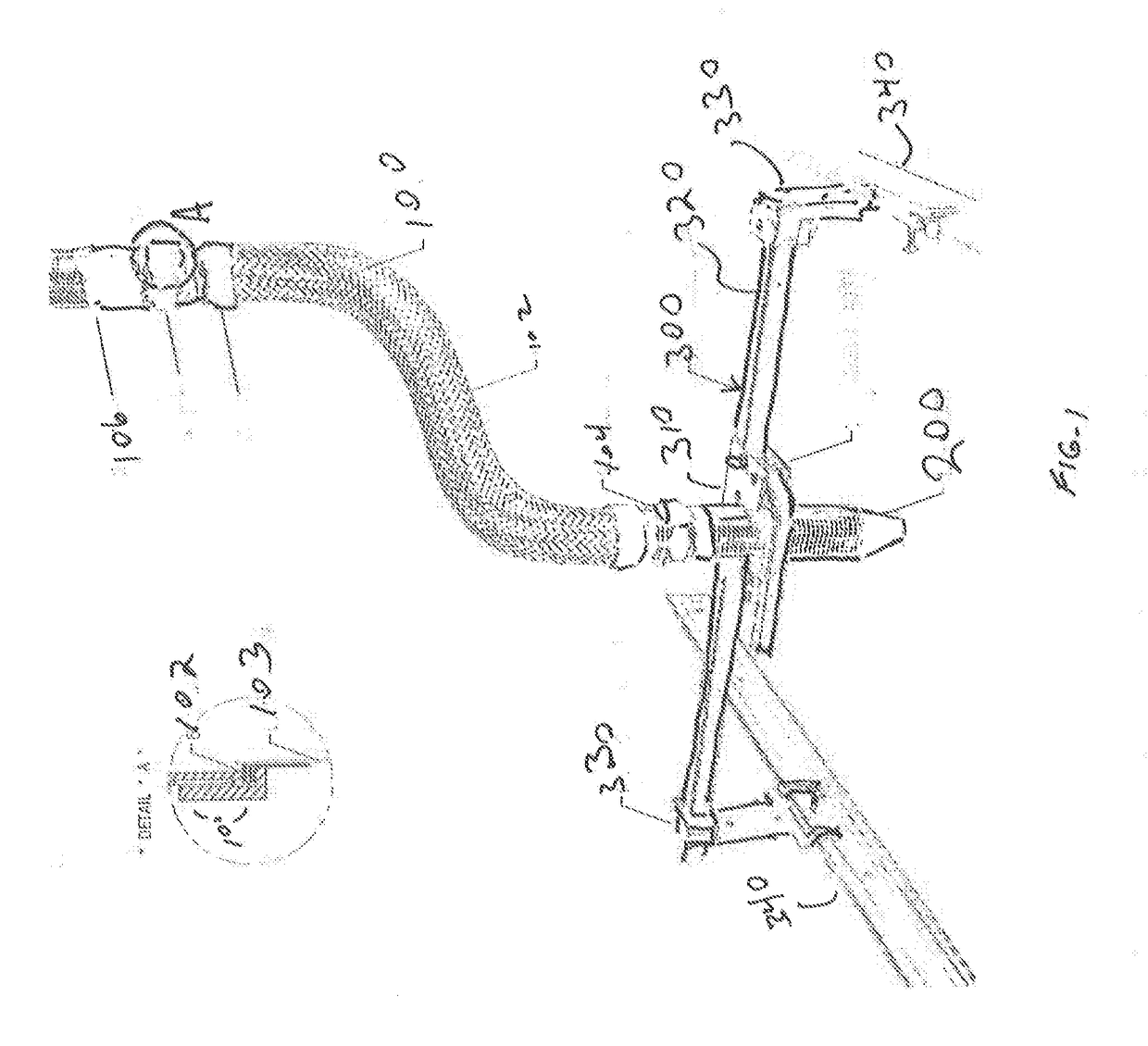

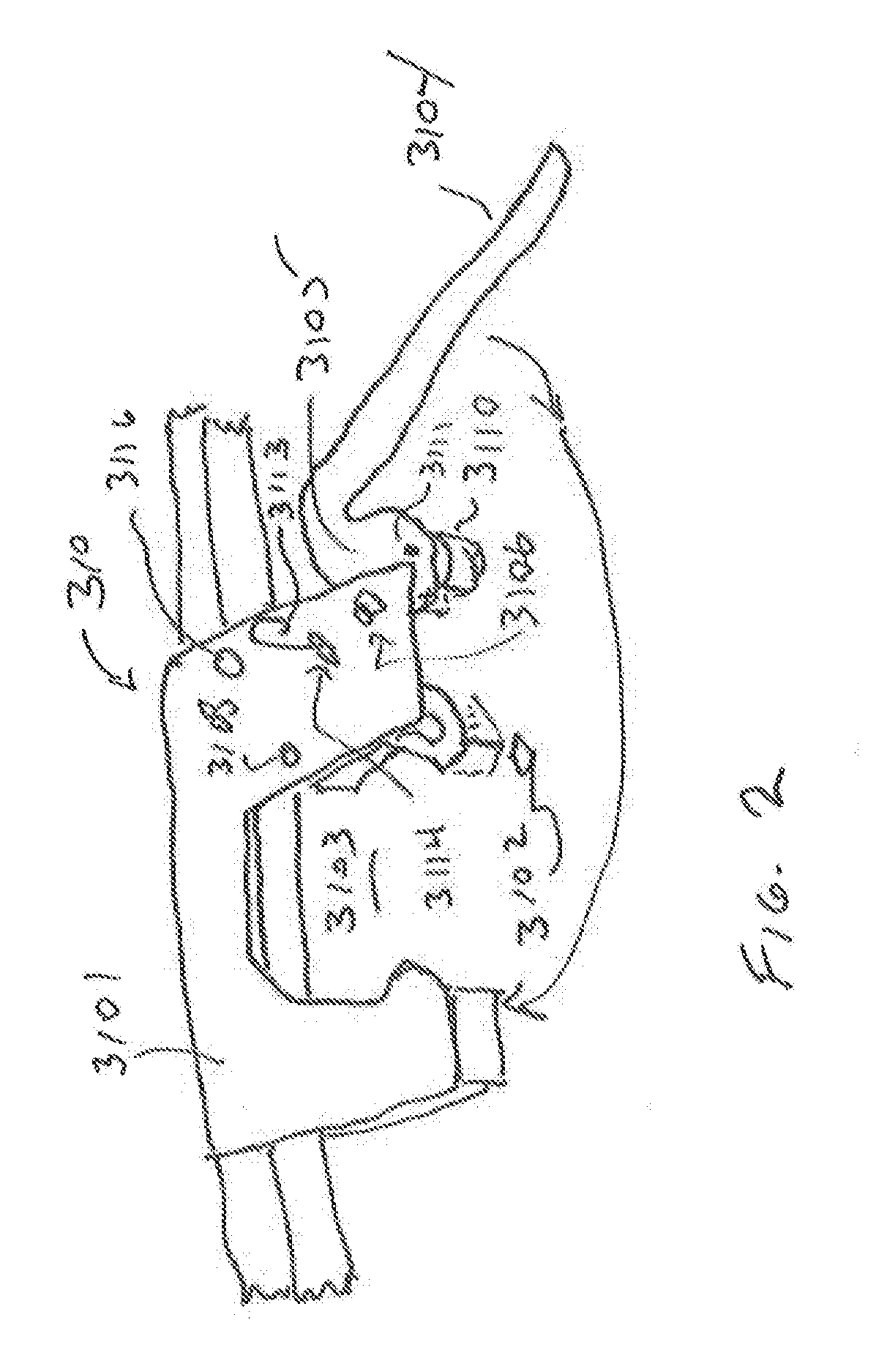

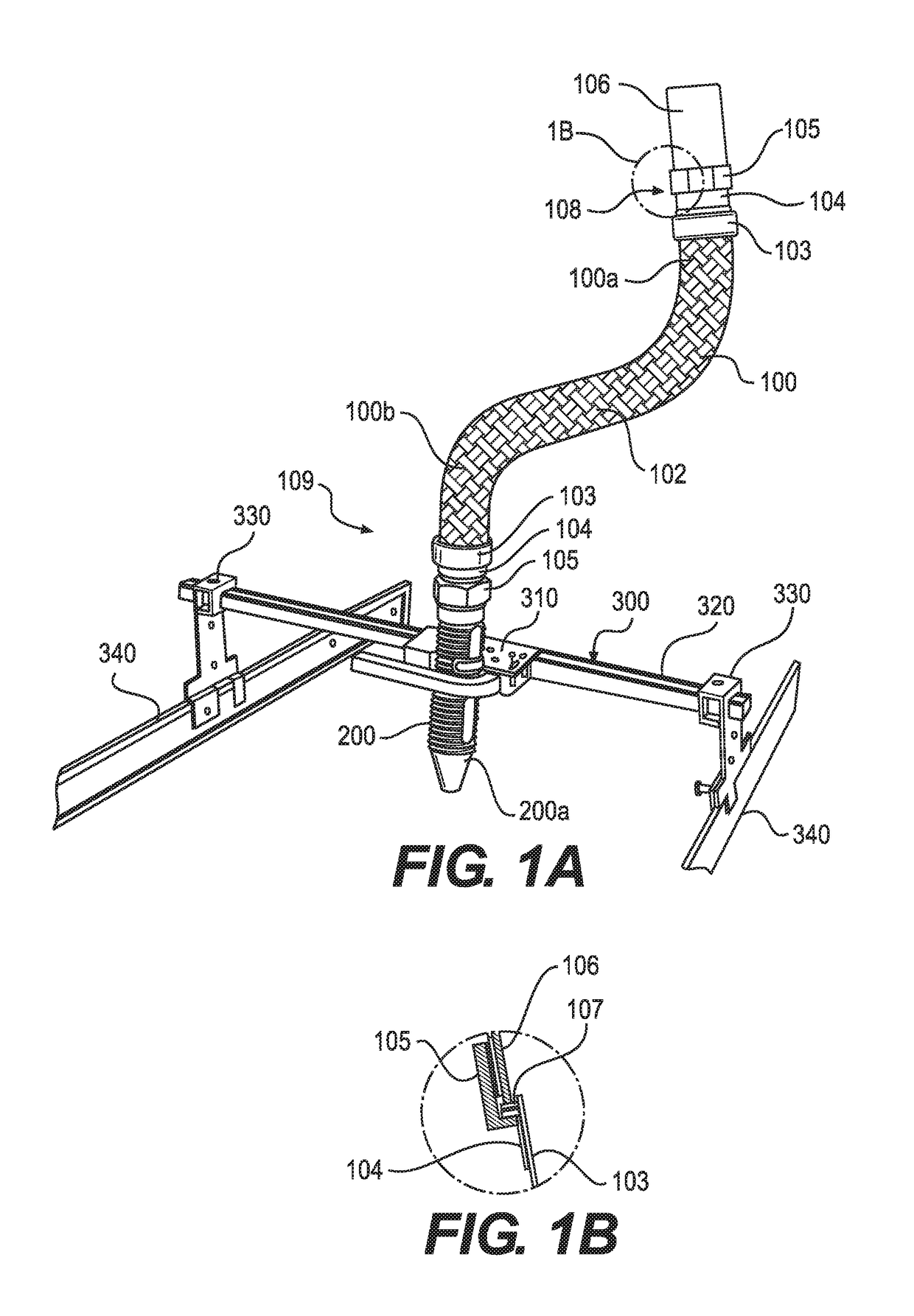

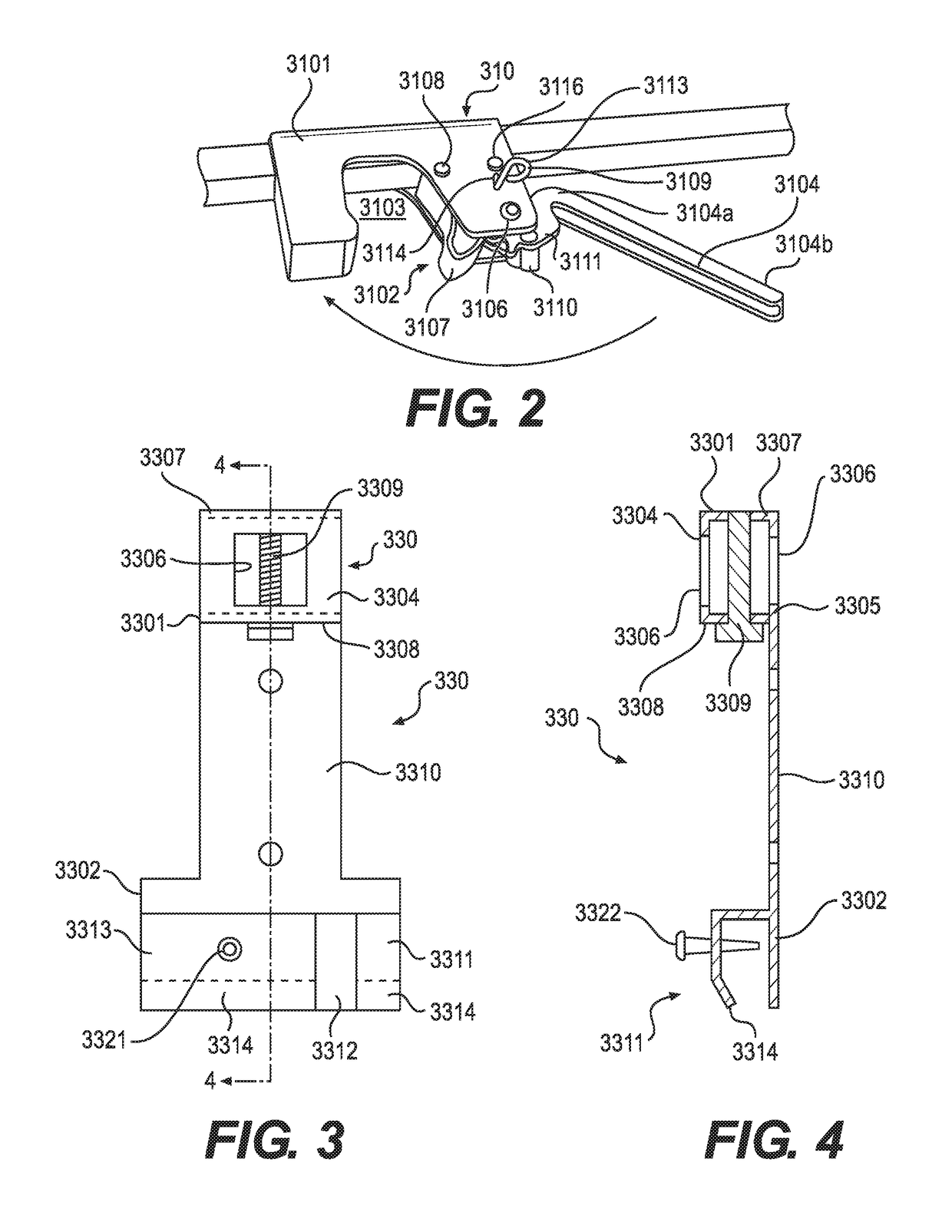

Bracket for installation of fire sprinklers

InactiveUS20170197101A1Less skilled labor timeLess skilled costPipe supportsSpraying apparatusFire sprinklerEngineering

A bracket has a length of bar stock, with end brackets that fit over a rail or bar that forms part of a suspended ceiling or the like. The end brackets may be secured permanently to the bar stock, or their location along the bar stock may be adjustable. A central bracket is mounted on, and can preferably slide along the length of, the bar stock. The central bracket defines a bay in front of the bar stock in which a sprinkler fitting is received, and a hinged lever at the front of the central bracket can be swung shut and locked, to secure the sprinkler in place. Preferably closing the lever also presses the fitting against the bar stock, and secures the central bracket in its location along the bar stock.

Owner:RELIABLE AUTOMATIC SPRINKLER

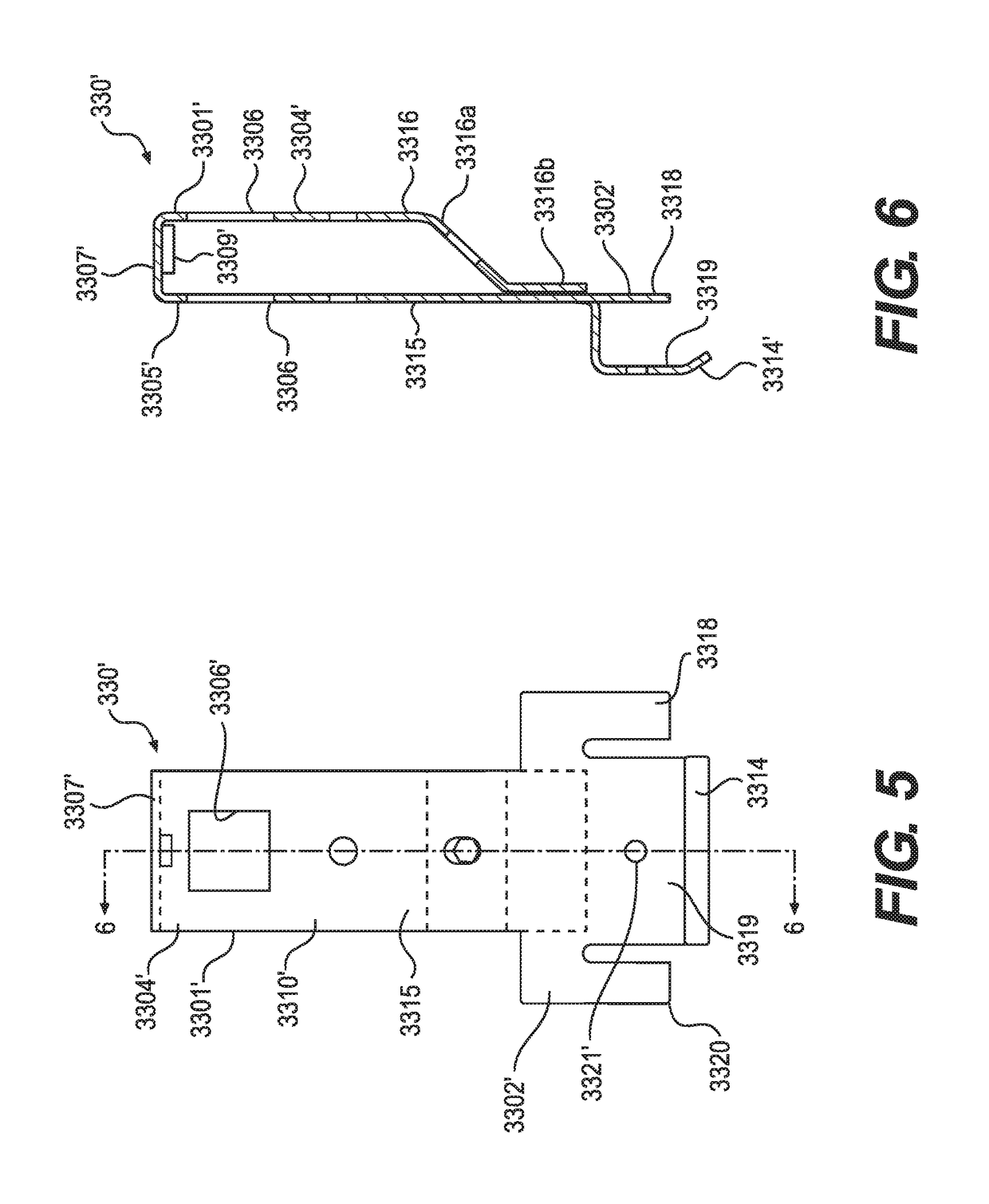

Bracket for installation of a fire protection sprinkler

ActiveUS10173088B2Reduce intensityQuick installationPipe supportsSpraying apparatusFire protectionMechanical engineering

A support bracket includes a support beam and a center bracket. The center bracket has a body that defines an opening to receive a sprinkler fitting, and a closure assembly, including a closure member having a first end rotatably connected to the body, and a second end having a handle. The closure assembly is movable between an open position and a closed position. When in the closed position, the closure assembly presses the sprinkler fitting against one of the body and the support beam, thereby urging the center bracket against the support beam to maintain the center bracket stationary relative to the support beam. In addition, the closure assembly includes a lock that engages with the closure assembly when the closure member moves from the open position to the closed position, and that prevents the closure member from returning from the closed position to the open position.

Owner:RELIABLE AUTOMATIC SPRINKLER

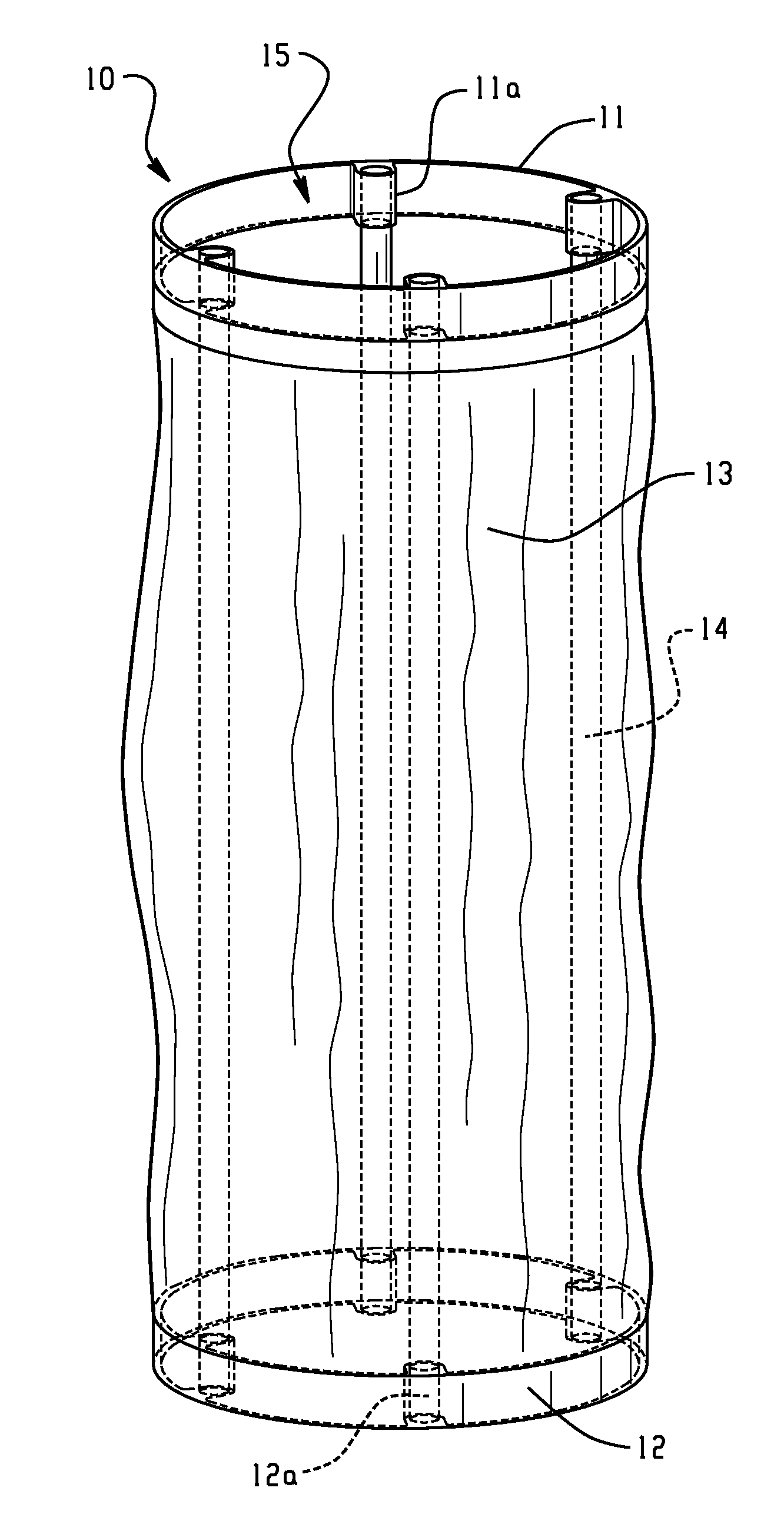

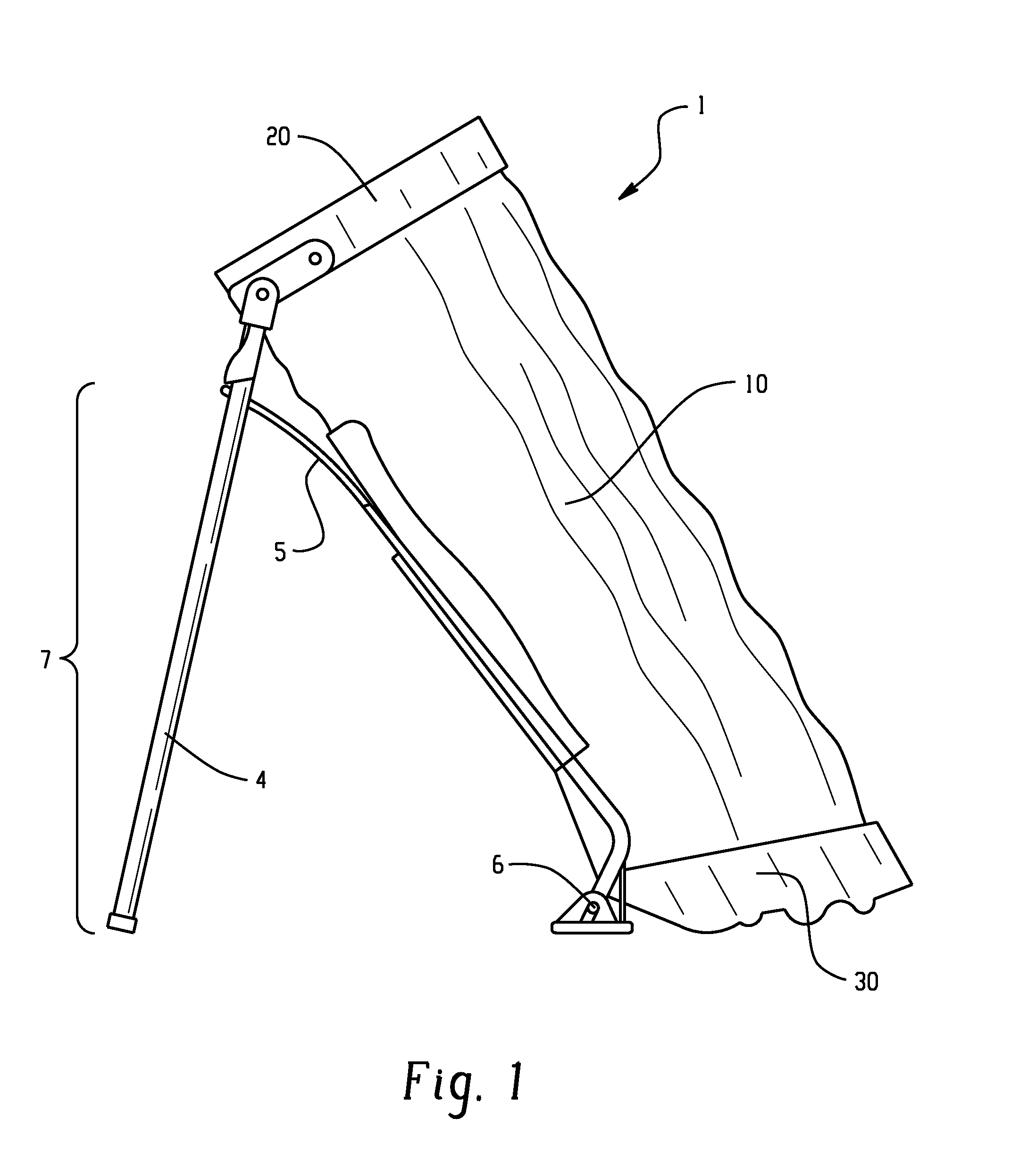

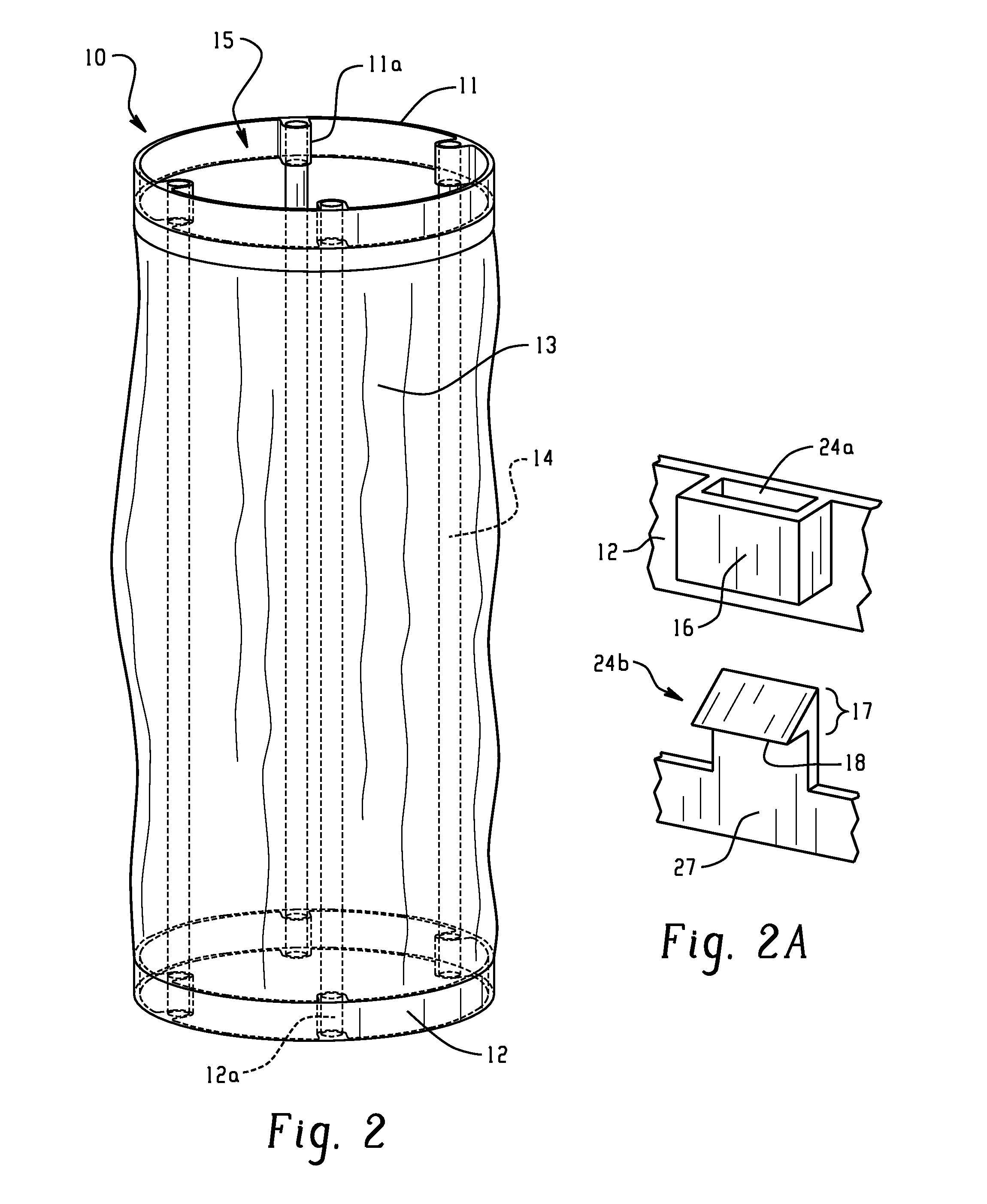

Golf Bag Kits

Golf bag kits including various components that may be selected and assembled to provide a finished golf bag. An embodiment of the golf bag kit comprises a golf bag shell or a golf bag shell sub-assembly, a bottom member capable of being permanently connected to the bottom portion of the golf bag shell, and a top member comprising top connectors capable of being permanently connected to the top portion to the golf bag shell. The golf bag kit may be shipped to the customer, distributor, and / or retailer as separate components for assembly. The golf bag shell sub-assembly may include an enclosure, a top collar, a bottom collar and stays extending between the top collar and the bottom collar.Alternatively, the golf bag kit may include a golf bag shell sub-assembly, a top member sub-assembly and a bottom member. The components may be selected from a plurality of component configurations.

Owner:DYNAMIC BRANDS

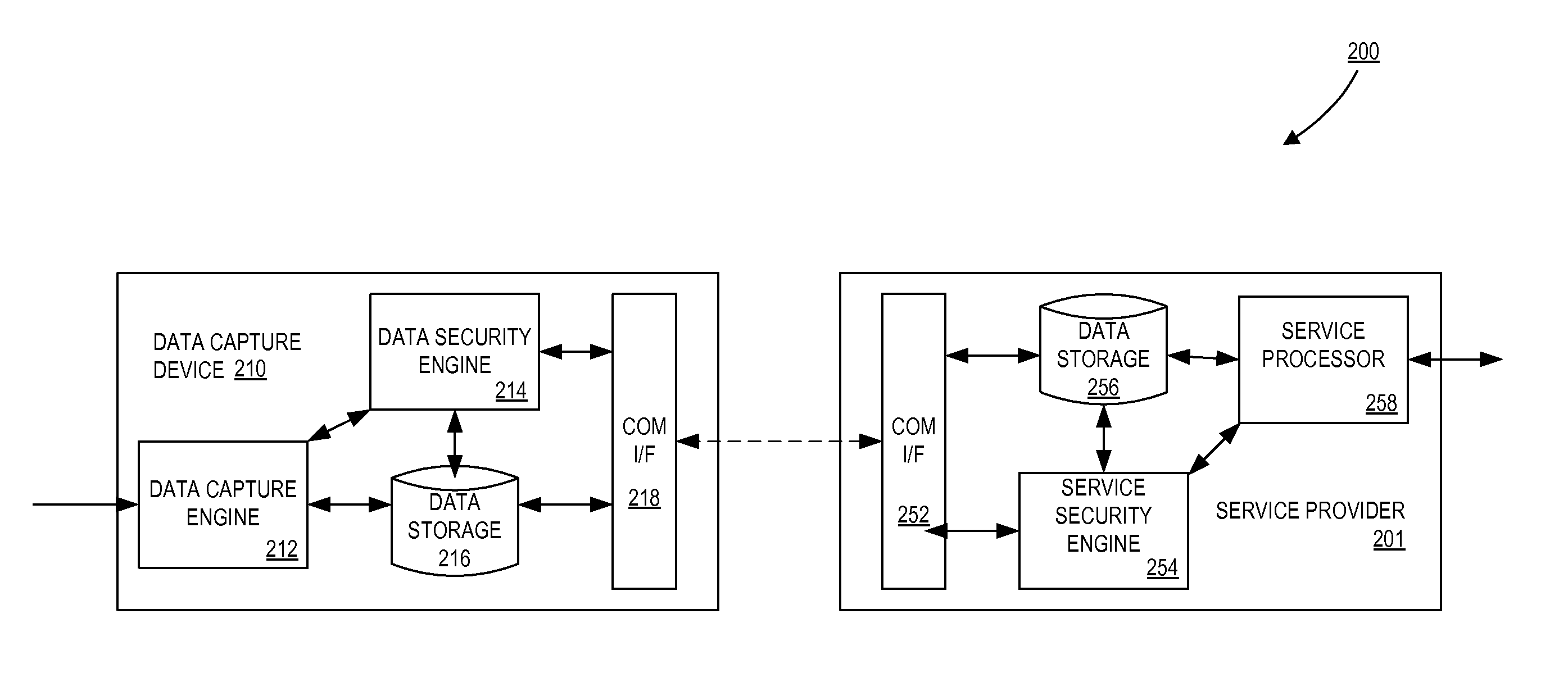

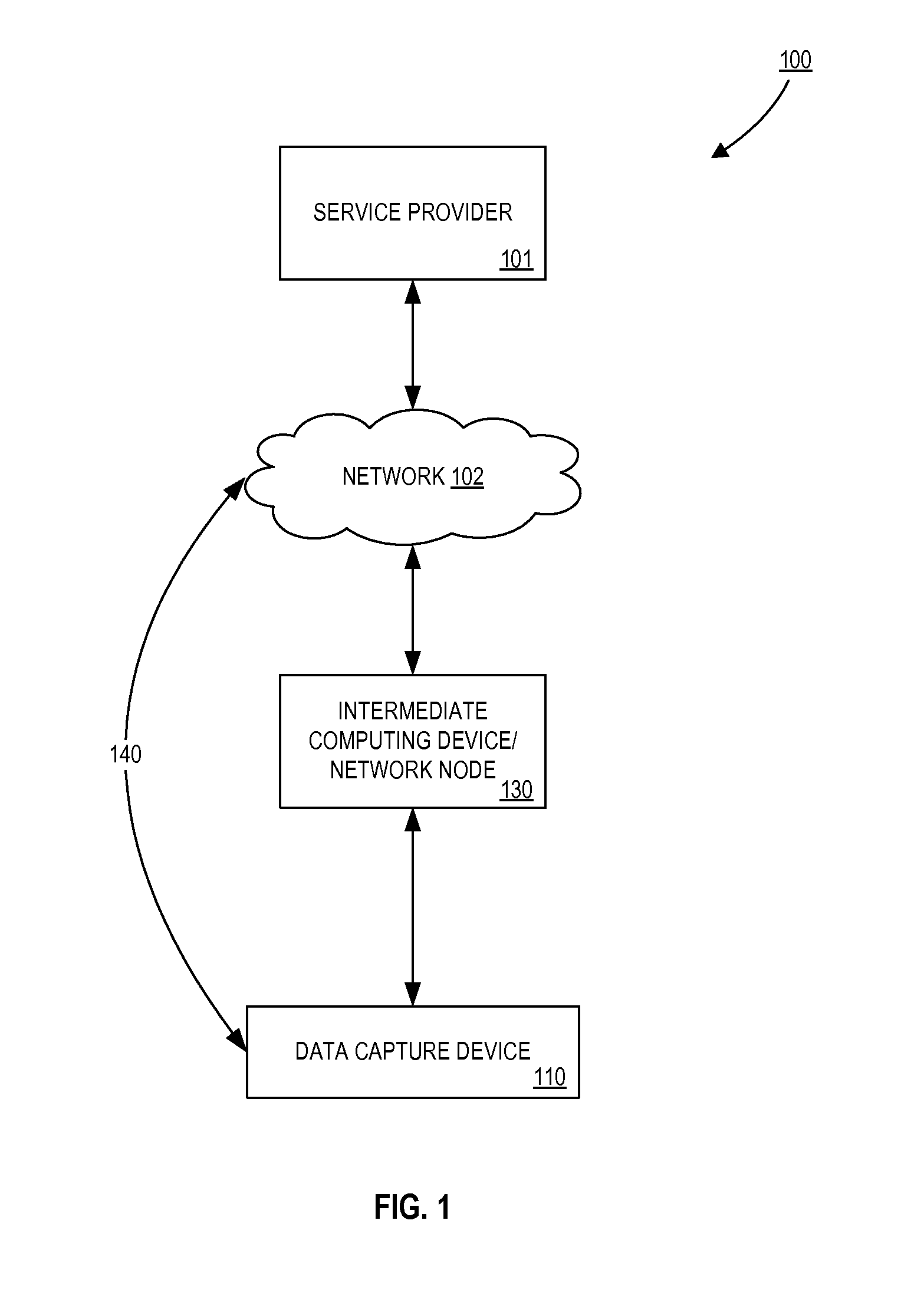

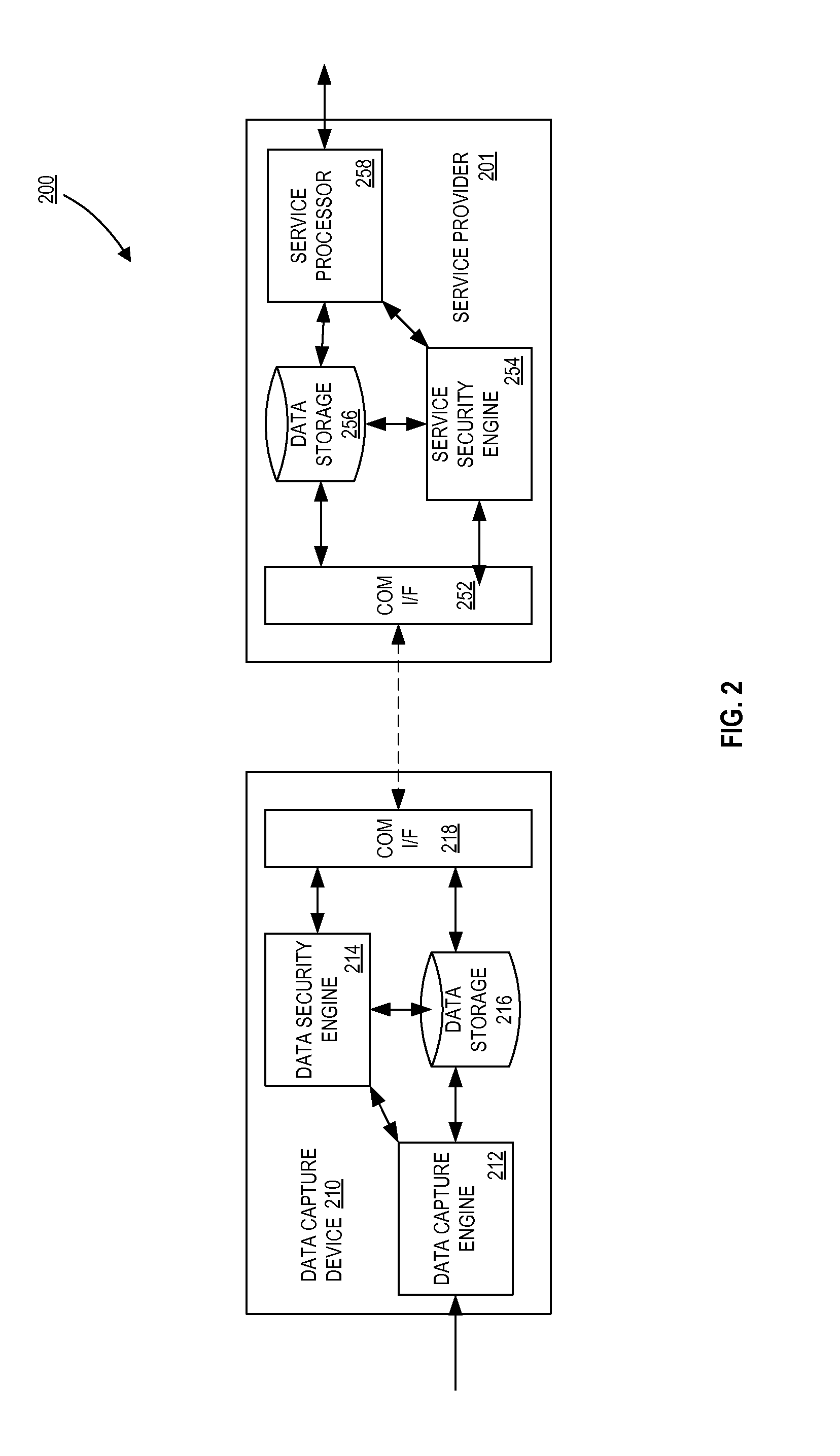

Method and apparatus for trust based data scanning, capture, and transfer

InactiveUS20130121490A1Data augmentationLess costSecret communicationSecuring communicationEncryptionService provider

A method and apparatus for enabling trust based data scanning and capture is described. The method may include capturing data with a data capture device. The method may also include encrypting the data with a first encryption key, encrypting the first encryption key with a second encryption key to generate a first encrypted key data, and encrypting the first encrypted key data with a third encryption key to generate a second encrypted key data. The method may also include transmitting the encrypted data and the second encrypted key data to a remote service provider over a network.

Owner:DOCUMENT CAPTURE TECH

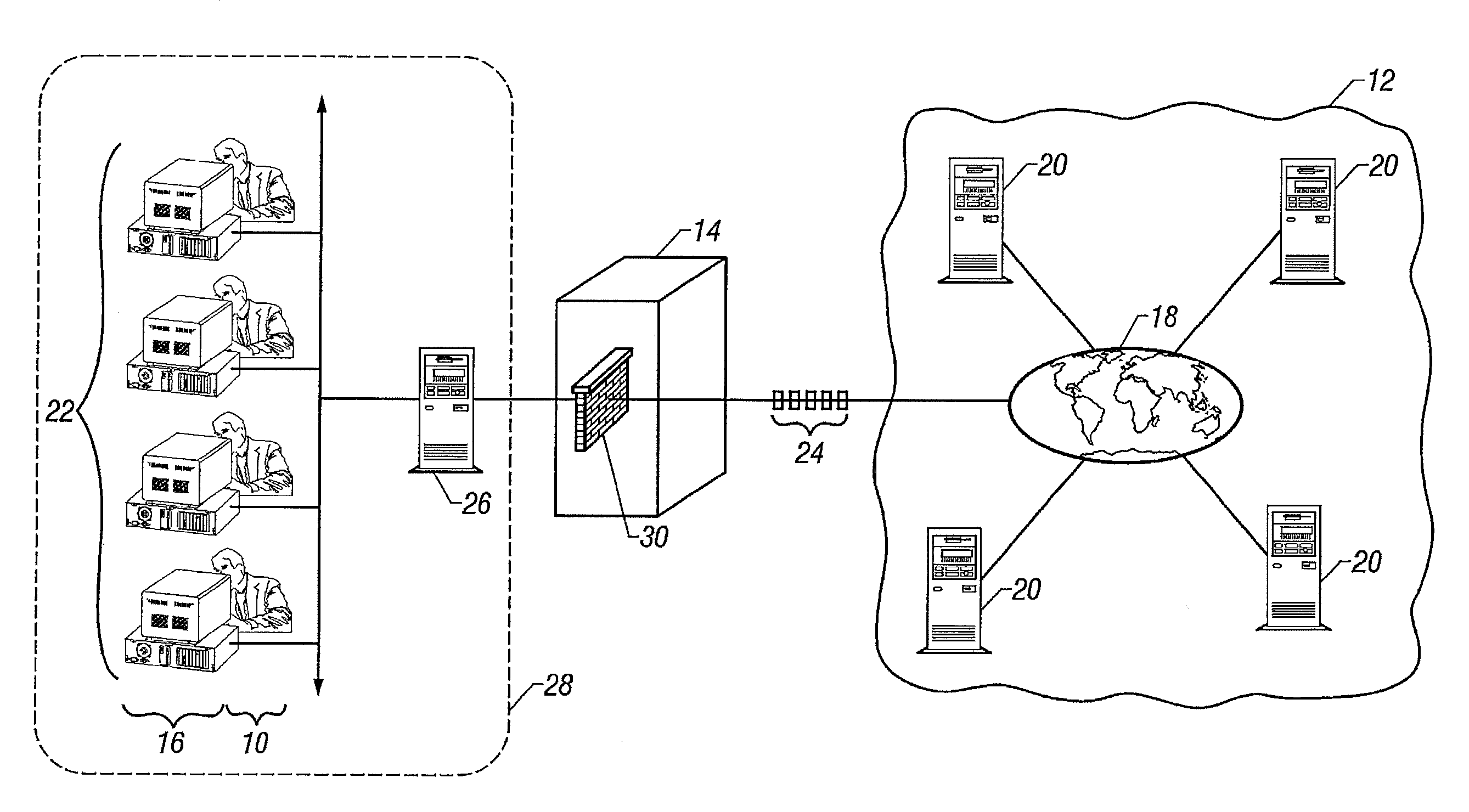

System and method for managing dynamic network sessions

InactiveUS20080267201A1Improve throughputLess costData switching by path configurationMultiple digital computer combinationsArea networkInternet access

For an Internet Access Gateway operative between an area network and a public network, managing dynamic network sessions therebetween whereby a primary server on the public network in a primary session with a client of the area network initiates an additional session with an additional server on the public network, for which an unexpected data packet received at the gateway from the additional server is associated with the primary session, and accordingly allowed access to the area network through the gateway, provided the gateway received the data packet at an input port exceeding 1023, the additional session comprises a pre-defined Session Triggering Event, and at least one internal network component of the area network indicates willingness to receive the data packet. Wherefore, a preferred Application Level Gateway is thereby provided for firewall and NAT implementations to enhance network security.

Owner:CISCO TECH INC

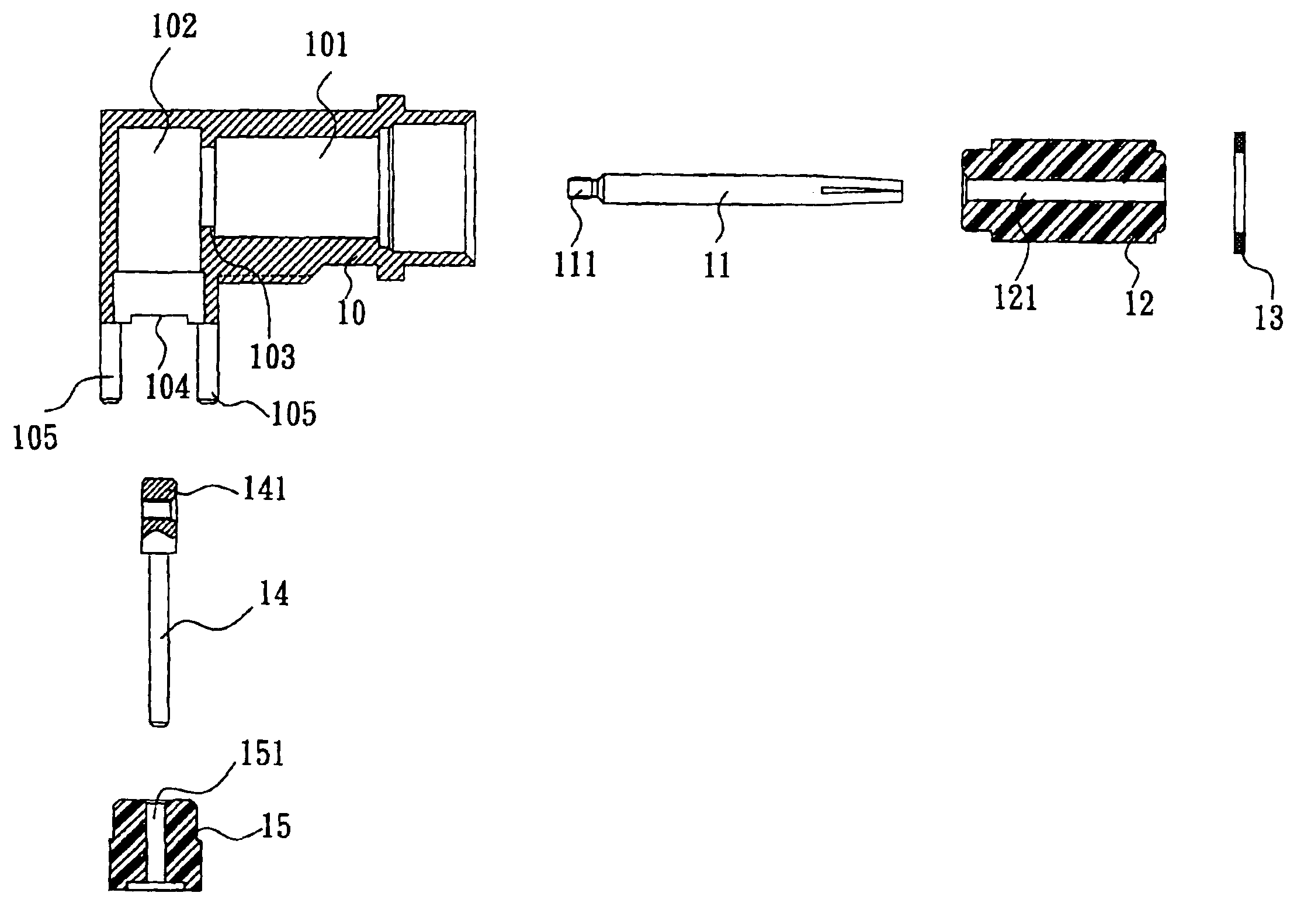

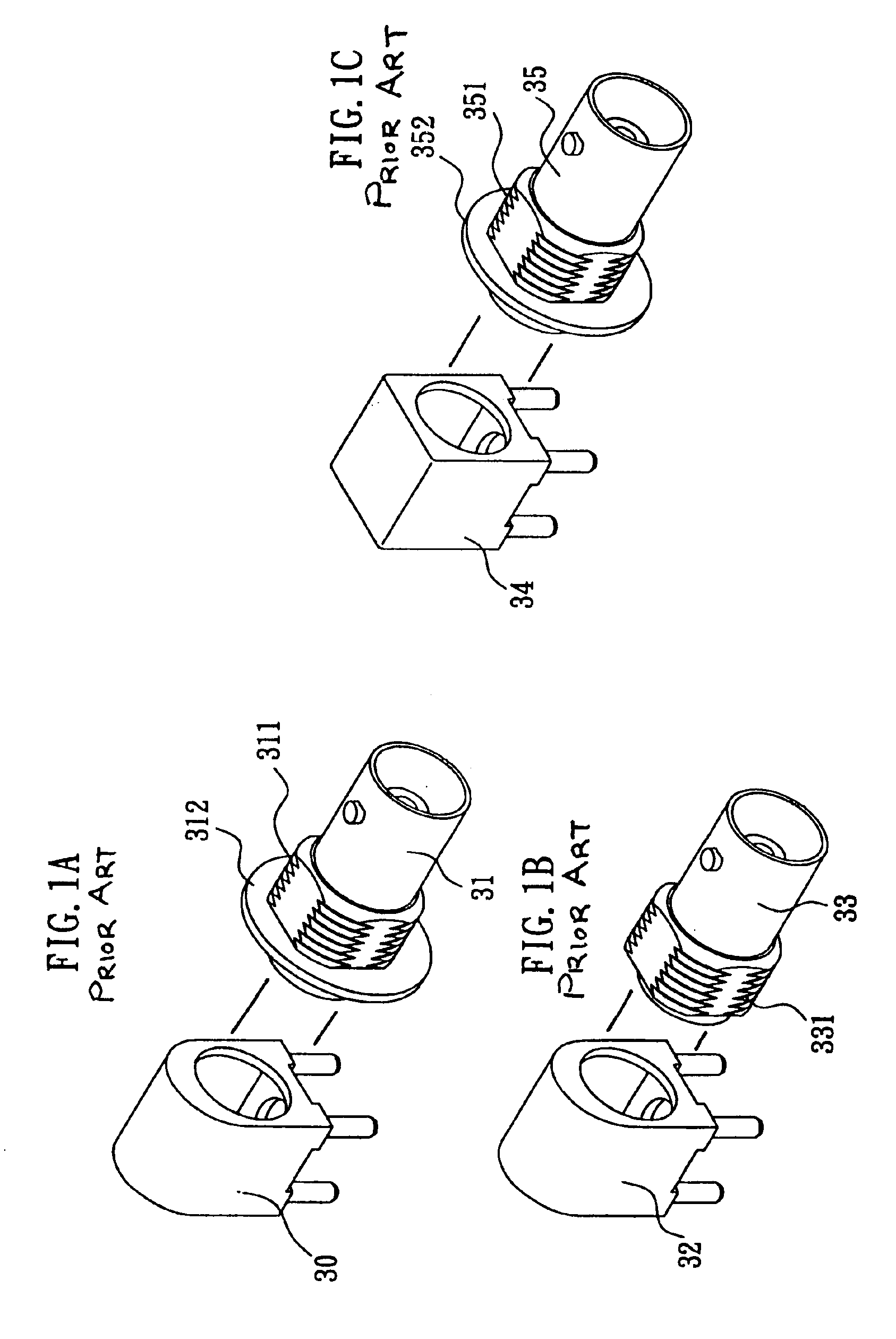

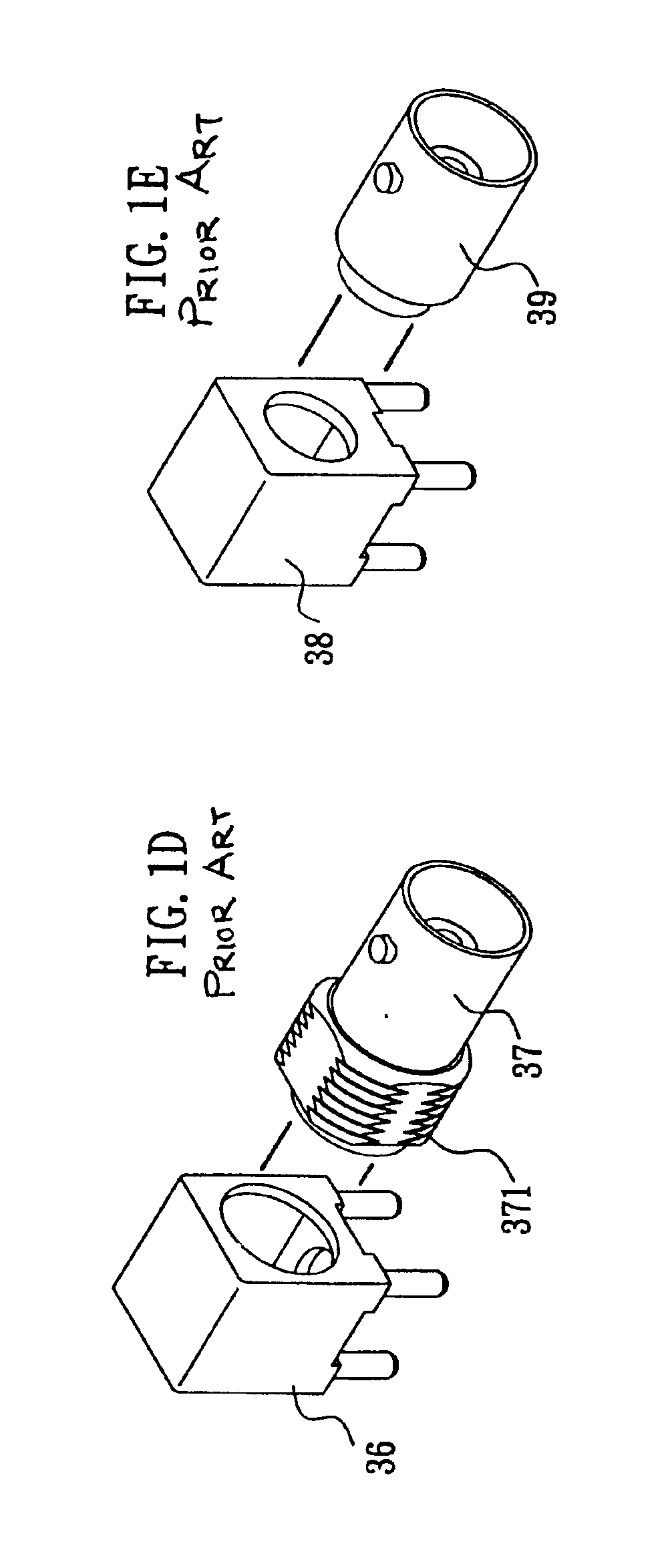

Module type mini BNC connector

InactiveUS6866543B2Quality improvementLess labor timeContact member manufacturingElectrically conductive connectionsEngineeringMechanical engineering

A module type mini BNC connector includes a metal outer casing, a front insulator, a terminal and a rear insulator. The metal outer casing is provided with a locating cylinder and a joining chamber with an opening communicates with the inner side of the locating cylinder. The front insulator is fitted in the locating cylinder with a piercing hole. The terminal has a front section and a rear section with the front section being joined to the piercing hole with a tail end extending to the joining chamber and the rear section being joined to the tail end. The rear insulator with a piercing hole is joined to the rear section of the terminal and is fitted to an inner side of the joining chamber at the opening thereof.

Owner:INSERT ENTERPRISE