Machine allocation of IC test processor and process for making the same

A technology for testing processors and machines, which is applied in the direction of electronic circuit testing, single semiconductor device testing, semiconductor/solid-state device testing/measurement, etc., and can solve problems affecting the execution efficiency of IC test processors and interruption of work in test areas, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

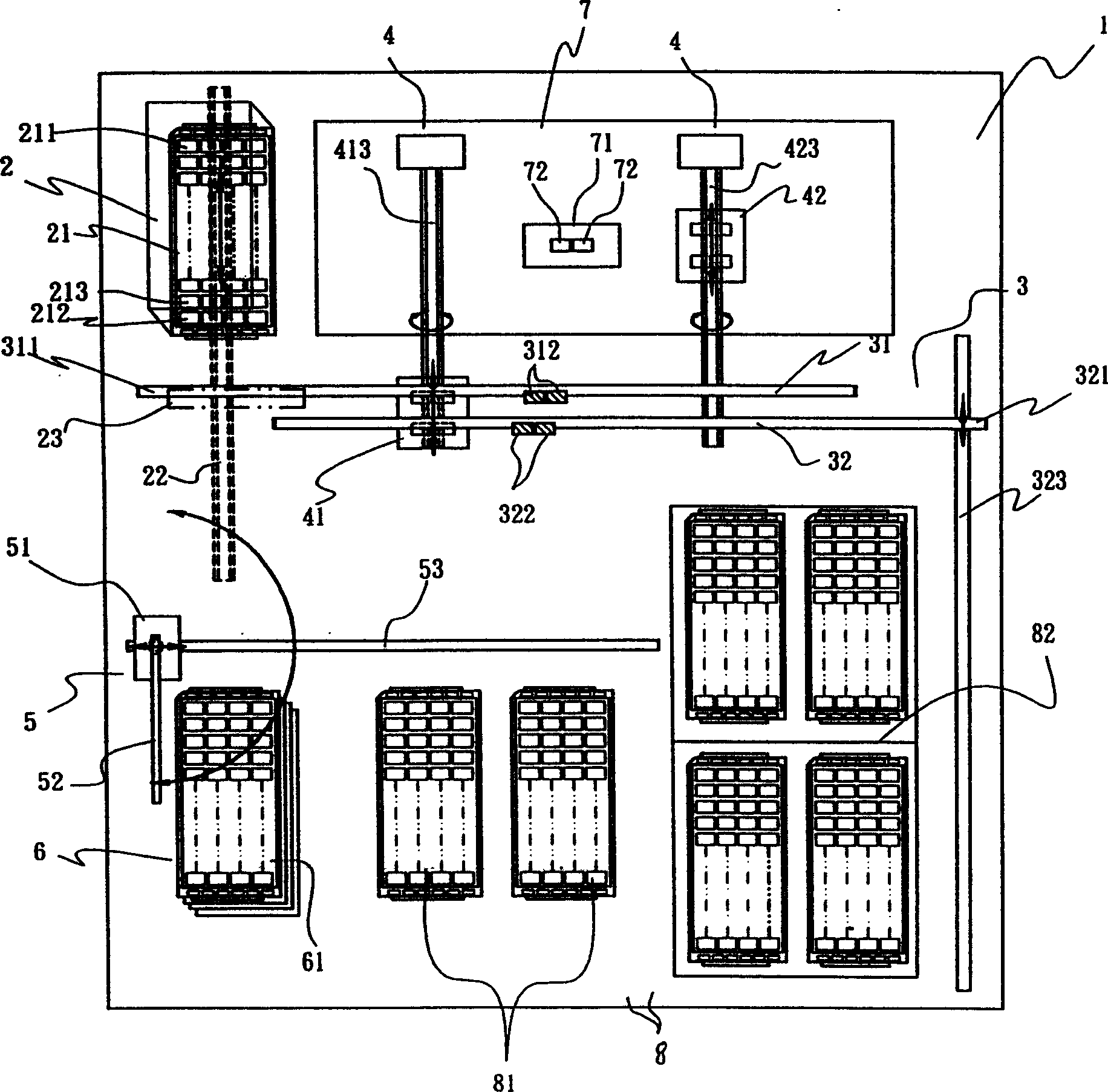

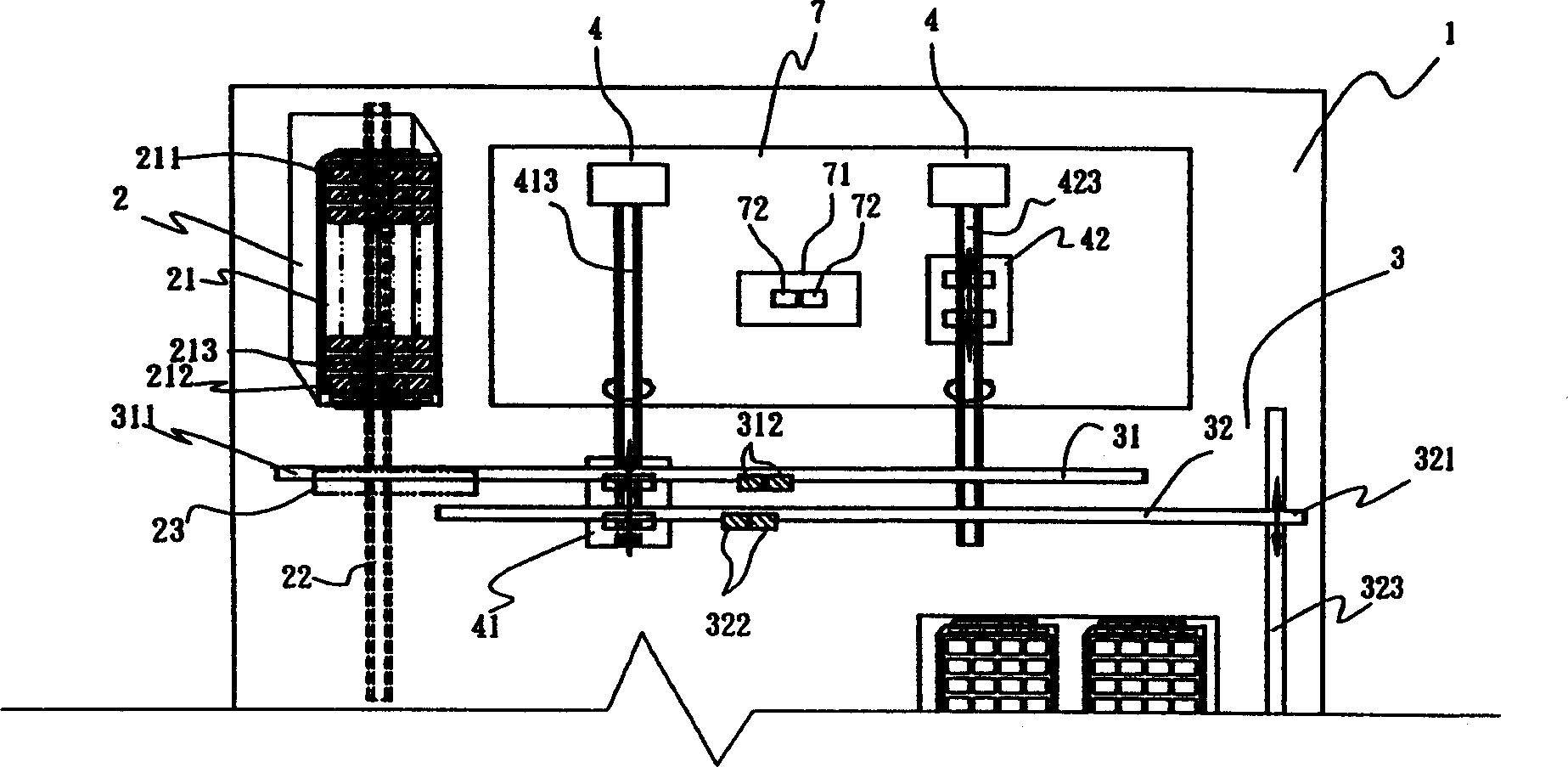

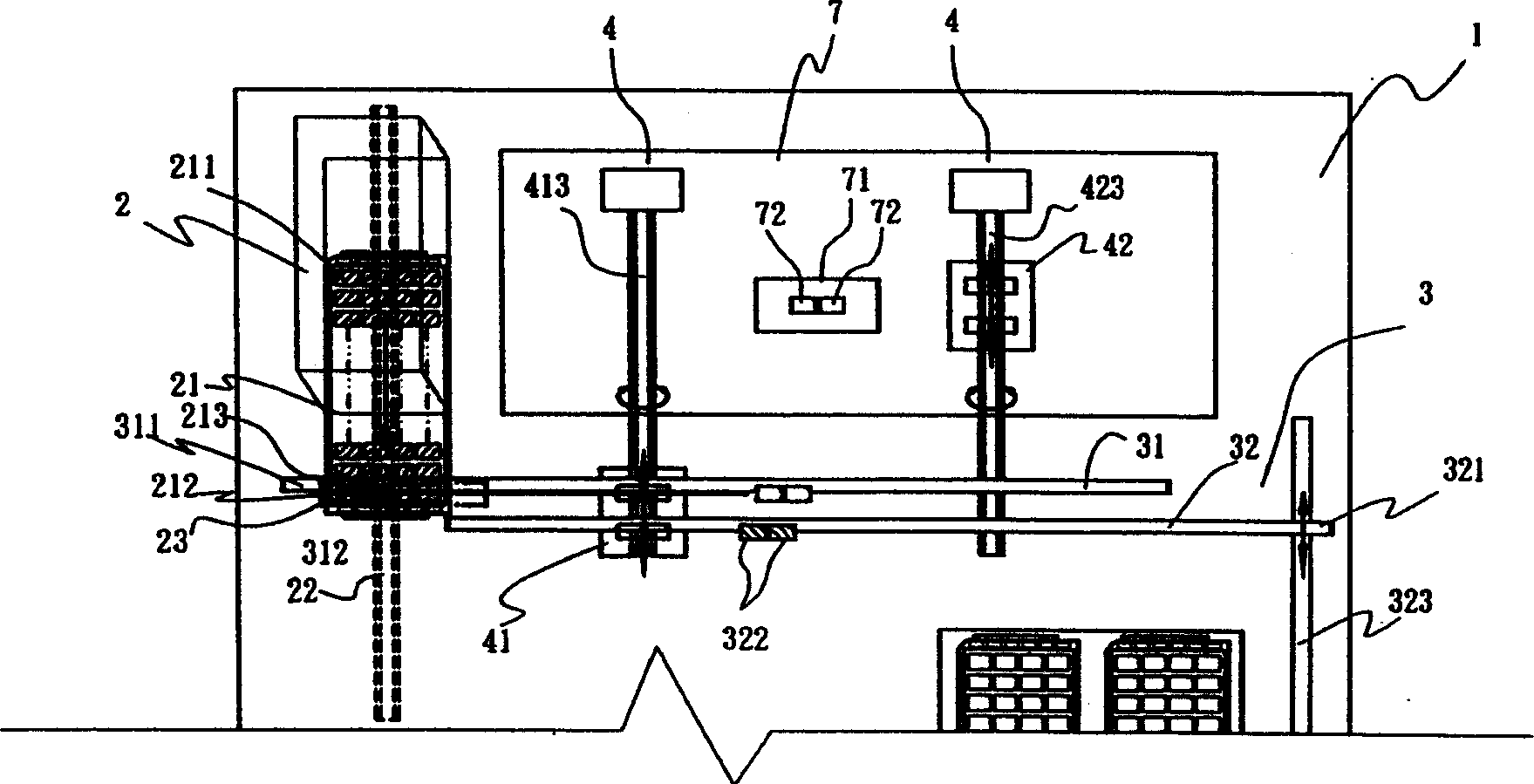

[0054] Please refer to figure 1 The main structure shown is a small machine 1, and the machine 1 is equipped with a stacking feeding buffer part 2, an empty tray dispatching mechanism 5, an empty IC tray dispatching mechanism, a double IC delivery arm 31 in the testing part, and a testing part Double IC delivery arm 32, reciprocating transport temporary storage disk, IC test area 7, IC completion test placement area 8 and other mechanisms, its features are:

[0055]Stacked feeding buffer: located on the far side of the machine, it is a stacked feeding tray filled with ICs to be tested. Each feeding tray can be used for lifting and conveying in the Z-axis direction; and the bottom feeding tray can be moved by Y The axis transmission mechanism moves in the Y-axis direction; the empty IC tray dispatching mechanism; it is composed of a base of the X-axis transmission mechanism and its cantilever. The cantilever is equipped with a vacuum suction cup, and a central axis on the base ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More