IC (integrated circuit) testing device and method

A test device and a technology to be tested are applied in the direction of measuring devices, electronic circuit tests, and electrical measurements. It can solve the problems of tight IO pins of controllers, increased costs, and insufficient controllers, so as to reduce costs, simplify structures, and The effect of saving resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

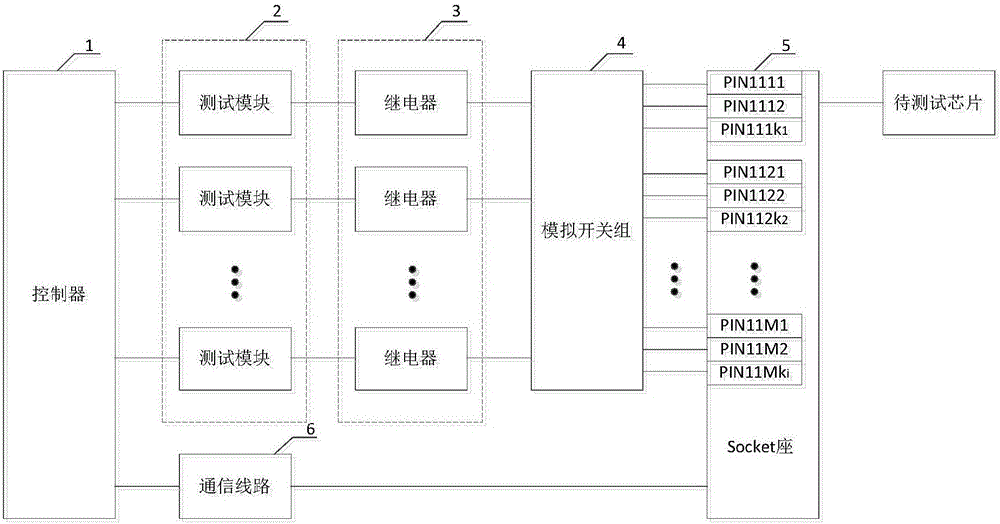

[0048] Please refer to figure 1 , figure 1 A schematic structural view of an IC testing device provided by the present invention, the testing device includes:

[0049] controller 1;

[0050] Specifically, the controller 1 here is used to control the peripheral modules in the IC testing device to complete the testing of the chip to be tested.

[0051] Socket 5 connected with the chip to be tested and used to connect the chip to be tested with the test device;

[0052] Socket 5 is used to connect the chip to be tested and the test device, so as to connect all the resources of the chip to be tested to the test device. For different packages and different types of chips to be tested, the connection between the chip to be tested and the test device can be completed by replacing different Socket seats 5. In addition, an adapter board can also be added to complete the connection between different chips to be tested and the test device. Connection.

[0053] N test modules 2 are u...

Embodiment 2

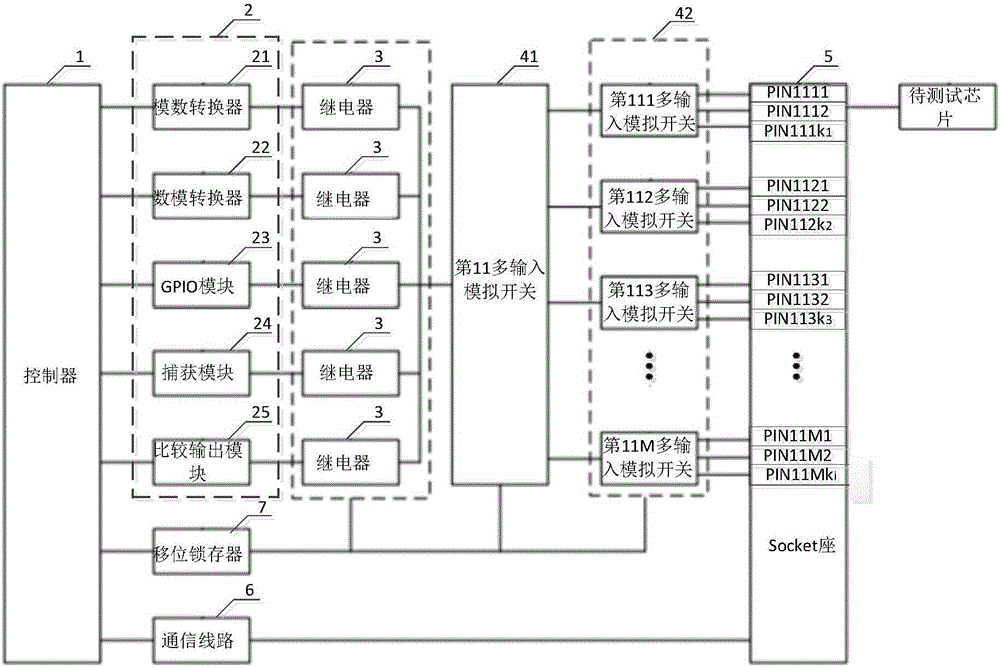

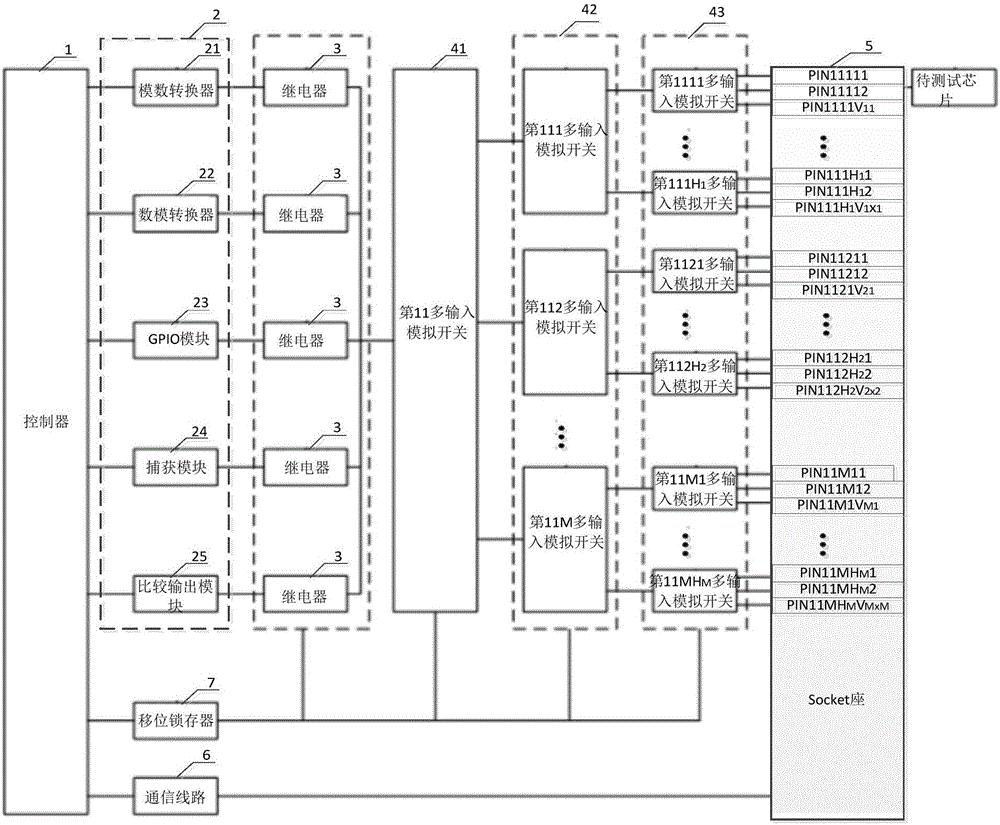

[0061] Please refer to figure 2 and image 3 ,in, figure 2 and image 3 All are structural schematic diagrams of another IC testing device provided by the present invention; on the basis of the IC testing device provided in Embodiment 1:

[0062] As preferably, the testing device also includes:

[0063] One end is connected to the controller 1, and the other end is respectively connected to the control end of the analog switch group 4 and the control ends of N relays 3. The shift latch 7 is used to receive the serial input of the controller 1. control the control terminal of the analog switch group 4 and the control signals of the N relays 3, and output the control signals to the analog switch group 4 and the relays 3 in parallel correspondingly when the chip to be tested is tested.

[0064] It can be understood that, in order to further save the IO resources of the controller 1, the IC testing device provided by the present application also includes a shift latch 7, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More