Patents

Literature

72 results about "Ip processing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

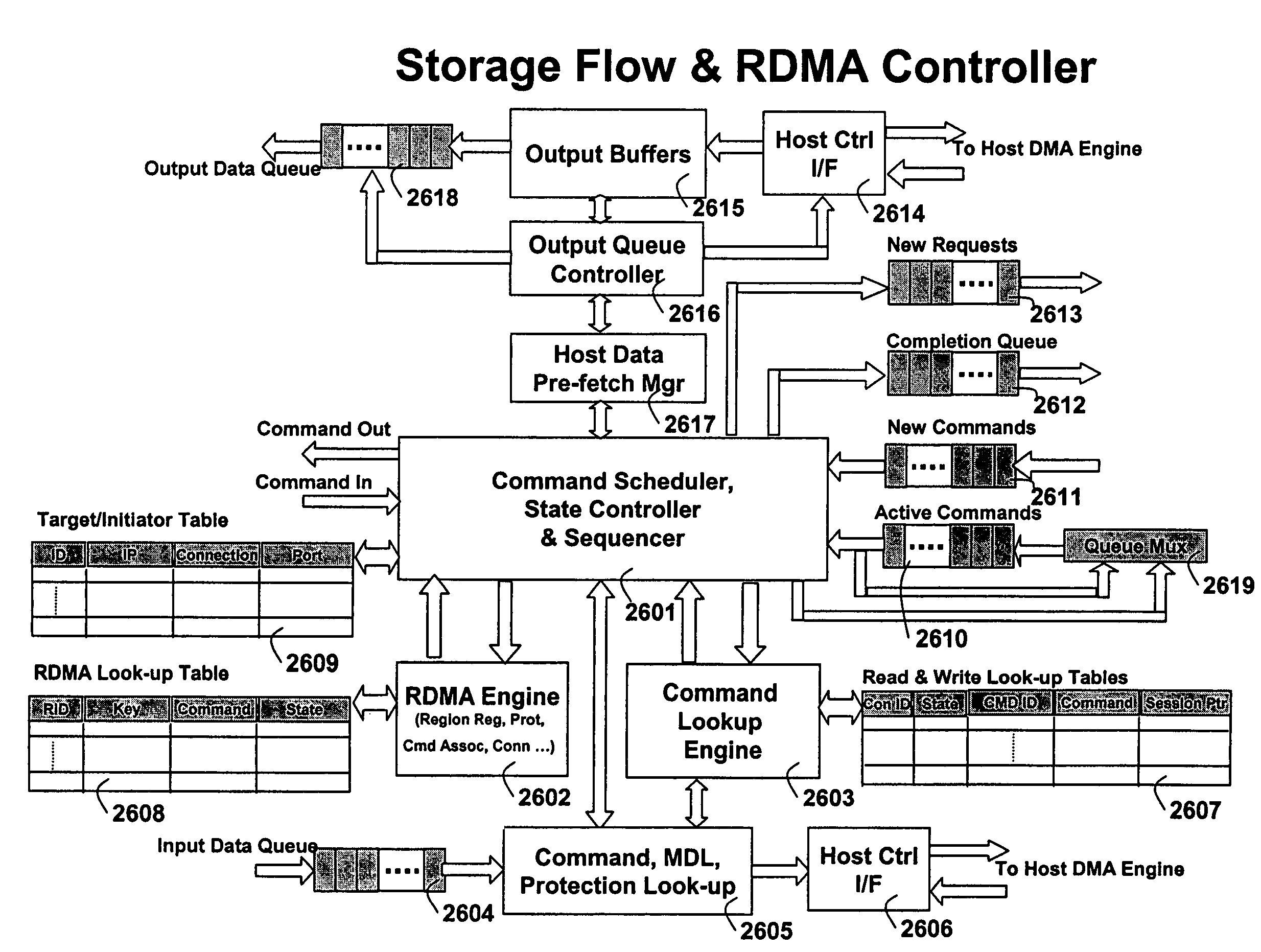

TCP/IP processor and engine using RDMA

ActiveUS7376755B2Sharply reduces TCP/IP protocol stack overheadImprove performanceMultiplex system selection arrangementsMemory adressing/allocation/relocationTransmission protocolInternal memory

A TCP / IP processor and data processing engines for use in the TCP / IP processor is disclosed. The TCP / IP processor can transport data payloads of Internet Protocol (IP) data packets using an architecture that provides capabilities to transport and process Internet Protocol (IP) packets from Layer 2 through transport protocol layer and may also provide packet inspection through Layer 7. The engines may perform pass-through packet classification, policy processing and / or security processing enabling packet streaming through the architecture at nearly the full line rate. A scheduler schedules packets to packet processors for processing. An internal memory or local session database cache stores a TCP / IP session information database and may also store a storage information session database for a certain number of active sessions. The session information that is not in the internal memory is stored and retrieved to / from an additional memory. An application running on an initiator or target can in certain instantiations register a region of memory, which is made available to its peer(s) for access directly without substantial host intervention through RDMA data transfer.

Owner:MEMORY ACCESS TECH LLC

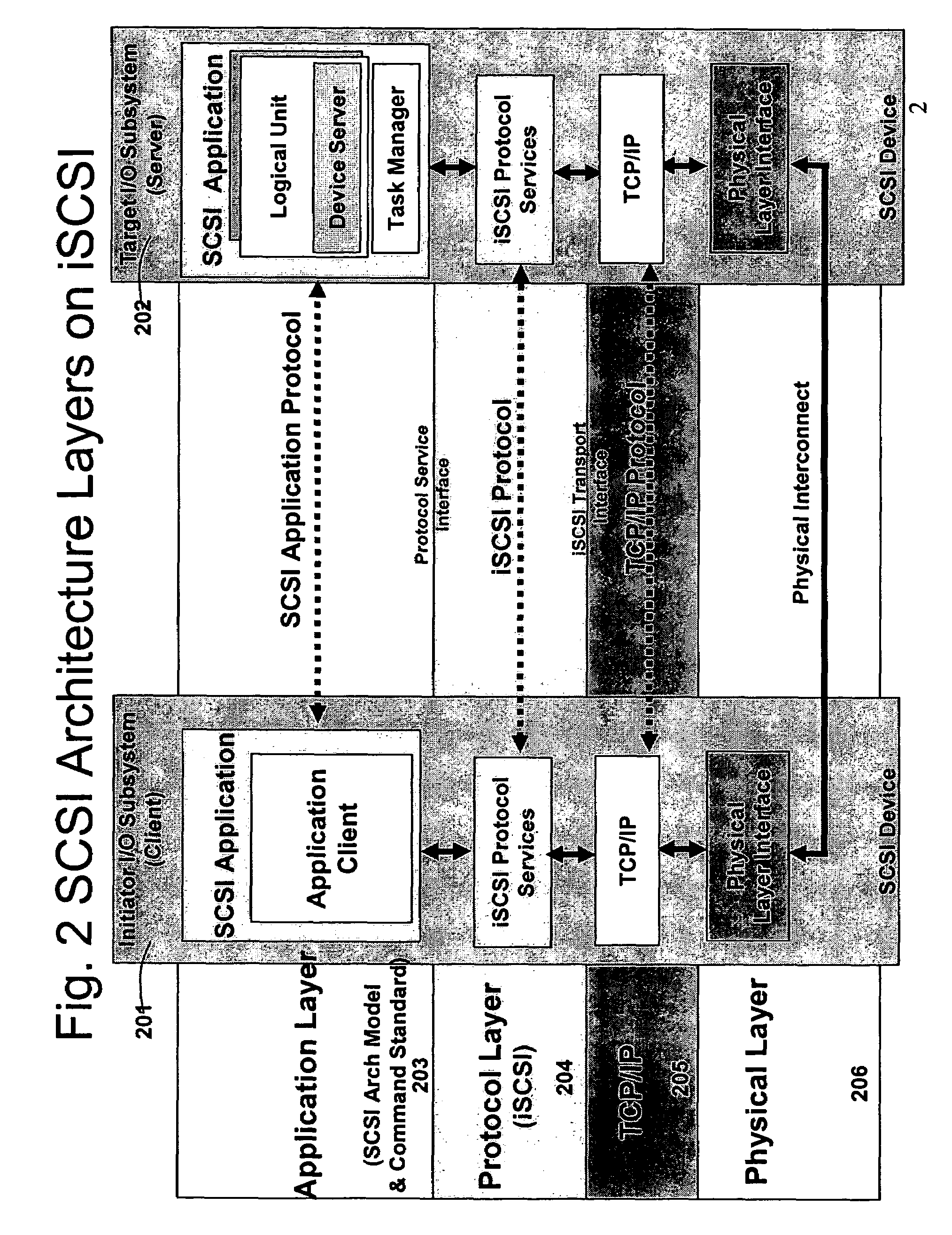

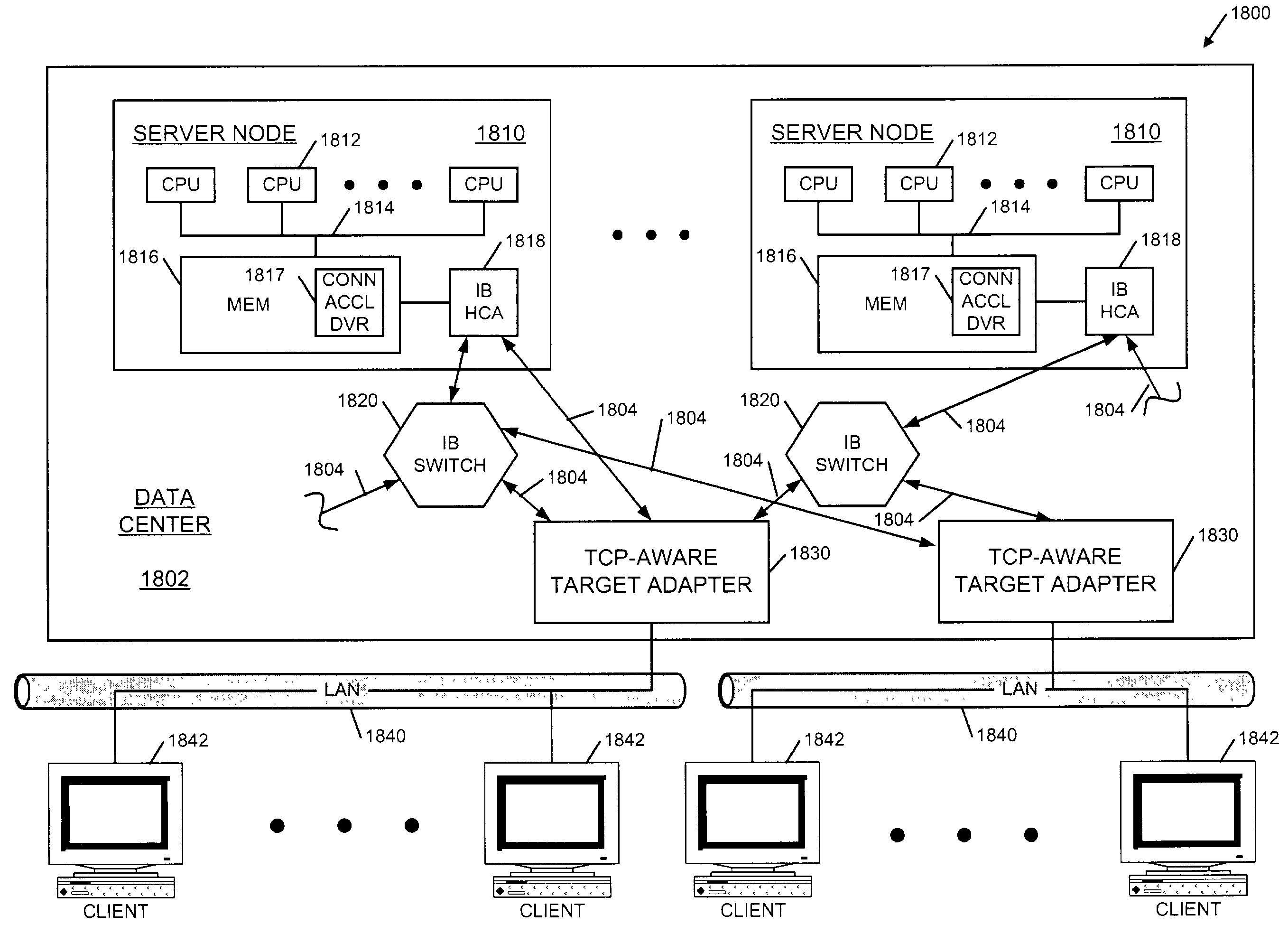

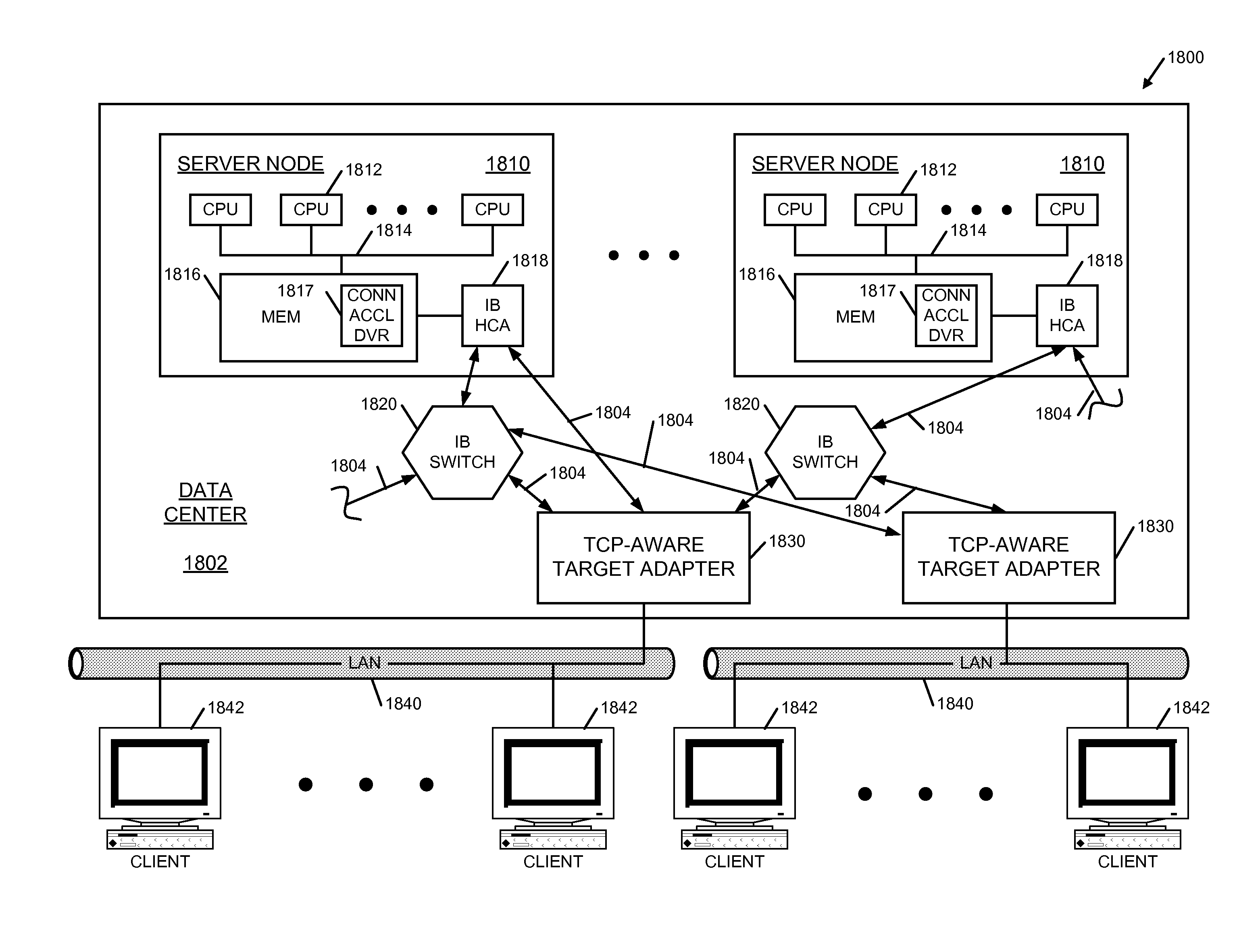

Infiniband TM work queue to TCP/IP translation

InactiveUS7149817B2Increase capacityFast data transferMultiple digital computer combinationsMemory systemsDirect memory accessIp processing

A TCP-aware target adapter for accelerating TCP / IP connections between clients and servers, where the servers are interconnected over an Infiniband™ fabric and the clients are interconnected over a TCP / IP-based network. The TCP-aware target adapter includes an accelerated connection processor and a target channel adapter. The accelerated connection processor bridges TCP / IP transactions between the clients and the servers. The accelerated connection processor accelerates the TCP / IP connections prescribing Infiniband remote direct memory access operations to retrieve / provide transaction data from / to the servers. The target channel adapter is coupled to the accelerated connection processor. The target channel adapter supports Infiniband operations with the servers, including execution of the remote direct memory access operations to retrieve / provide the transaction data. The TCP / IP connections are accelerated by offloading TCP / IP processing otherwise performed by the servers to retrieve / provide said transaction data.

Owner:INTEL CORP

Work queue to TCP/IP translation

InactiveUS7149819B2Increase capacityFast data transferMultiple digital computer combinationsSecuring communicationIp processingTransaction data

An apparatus and method are provided to offload TCP / IP-related processing, where a server is connected to a plurality of clients, and the plurality of clients is accessed via a TCP / IP network. TCP / IP connections between the plurality of clients and the server are accelerated. The apparatus includes an accelerated connection processor and a target channel adapter. The accelerated connection processor bridges TCP / IP transactions between the plurality of clients and the server, where the accelerated connection processor accelerates the TCP / IP connections by prescribing remote direct memory access operations to retrieve / provide transaction data from / to the server. The target channel adapter is coupled to the accelerated connection processor. The target channel adapter executes the remote direct memory access operations to retrieve / provide the transaction data. The TCP / IP transactions are accelerated by offloading TCP / IP processing otherwise performed by the server to retrieve / provide transaction data.

Owner:INTEL CORP

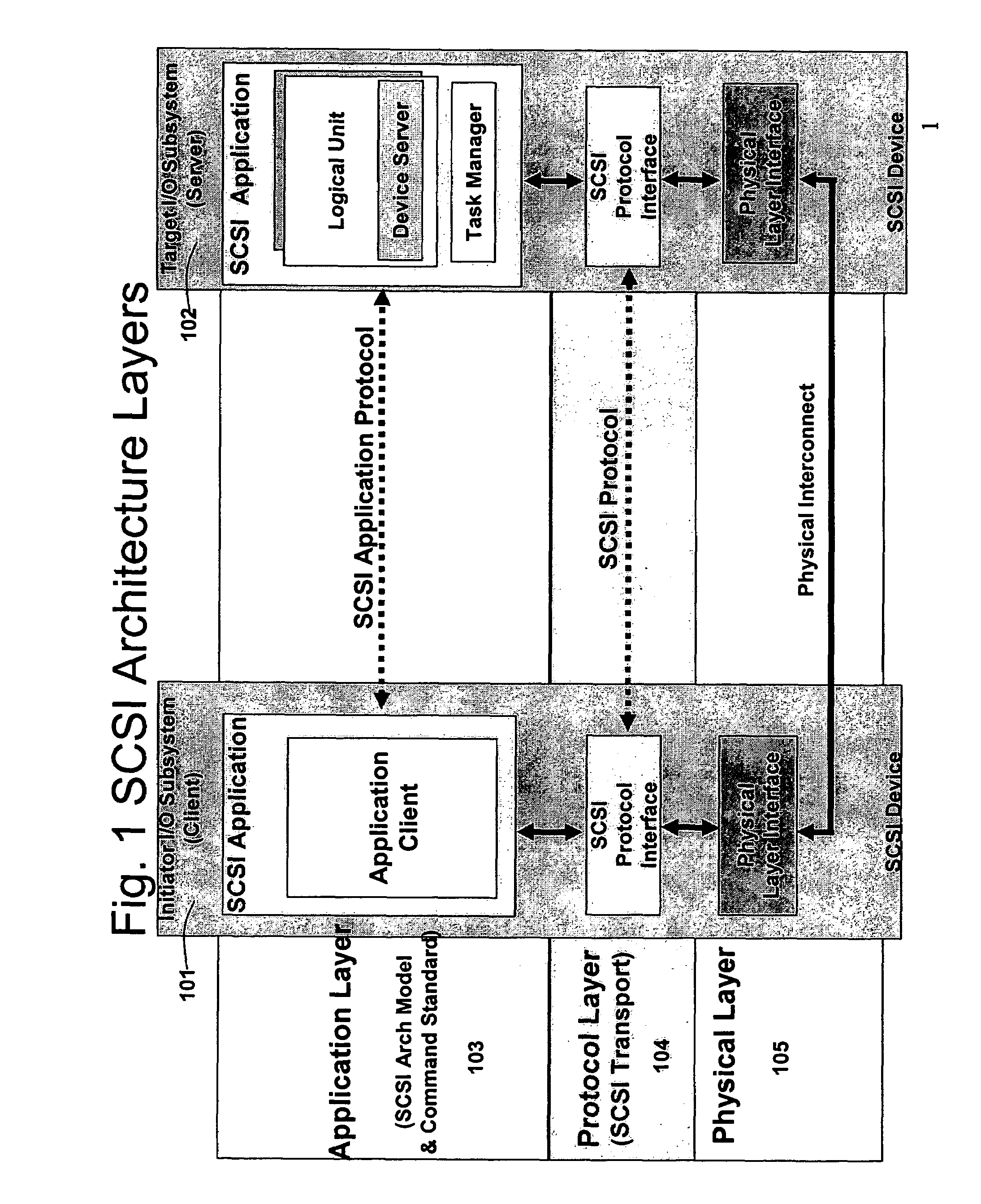

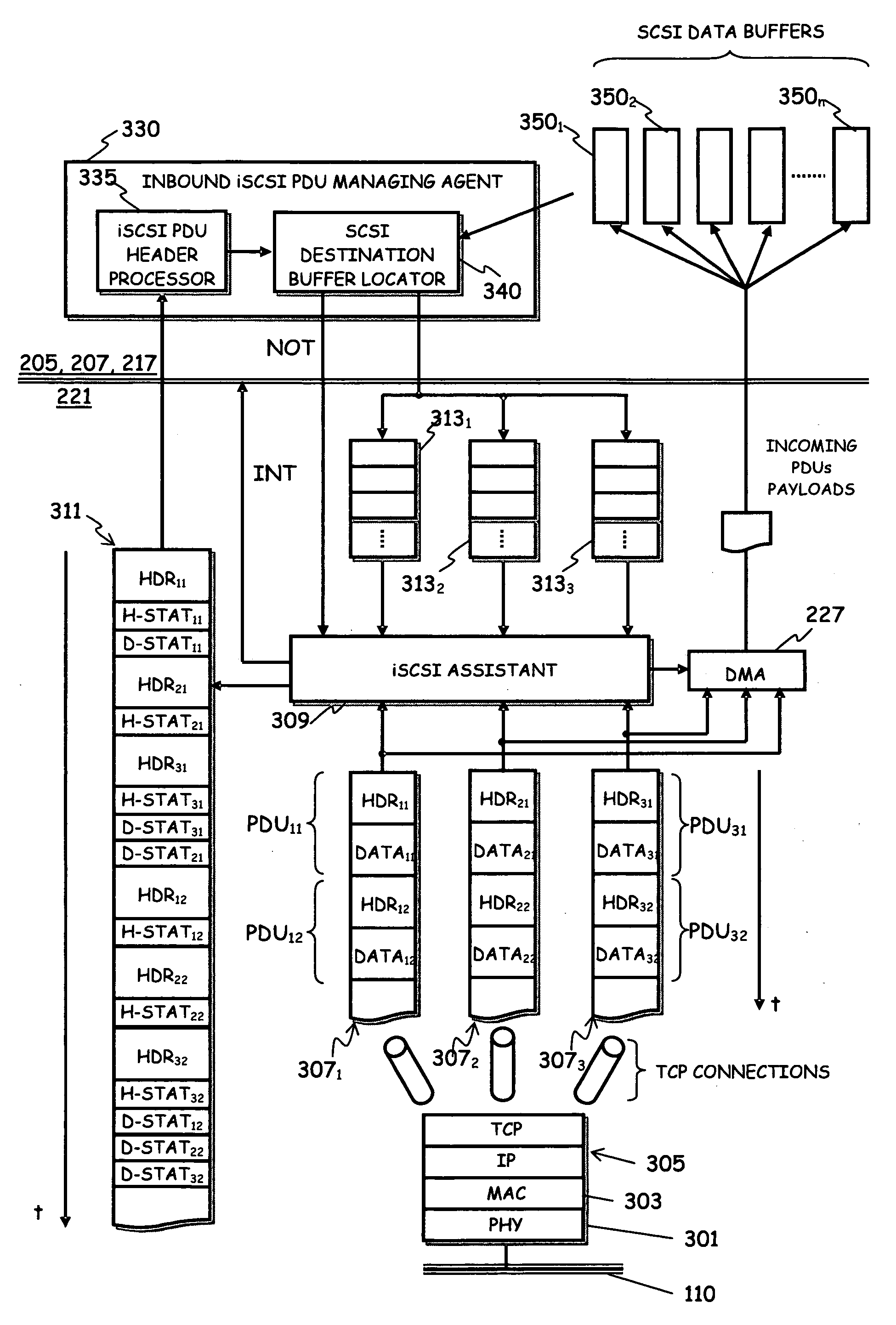

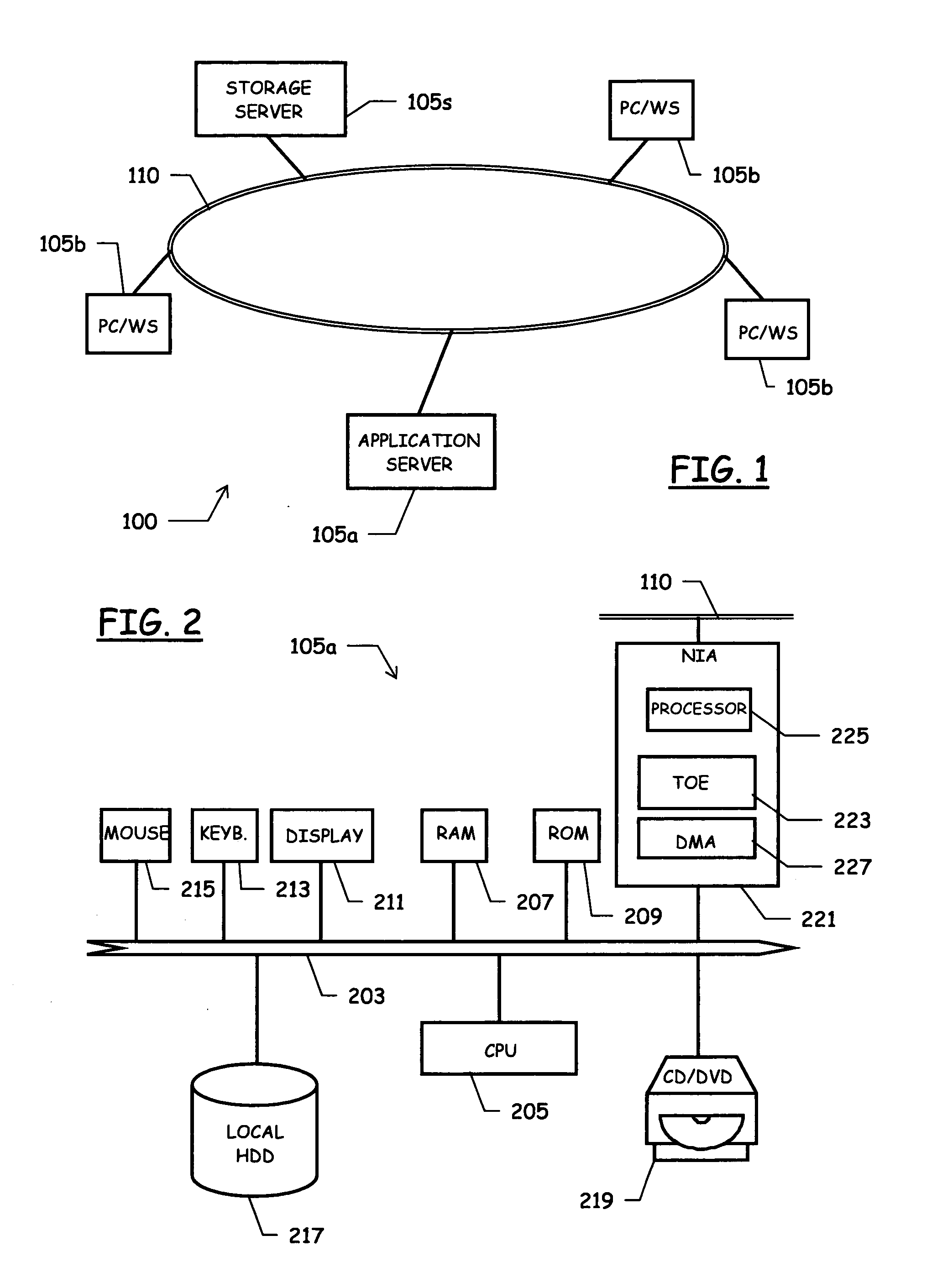

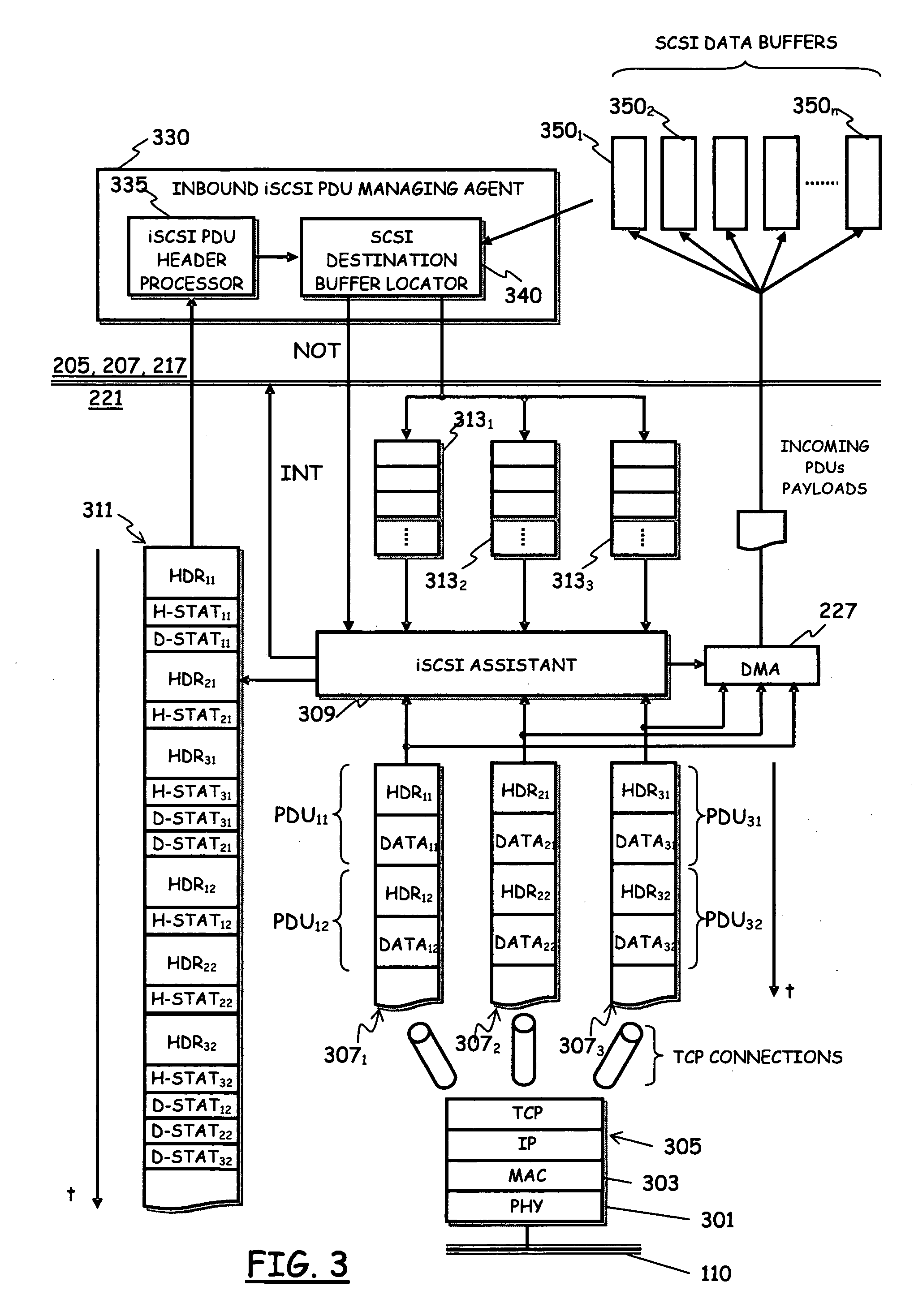

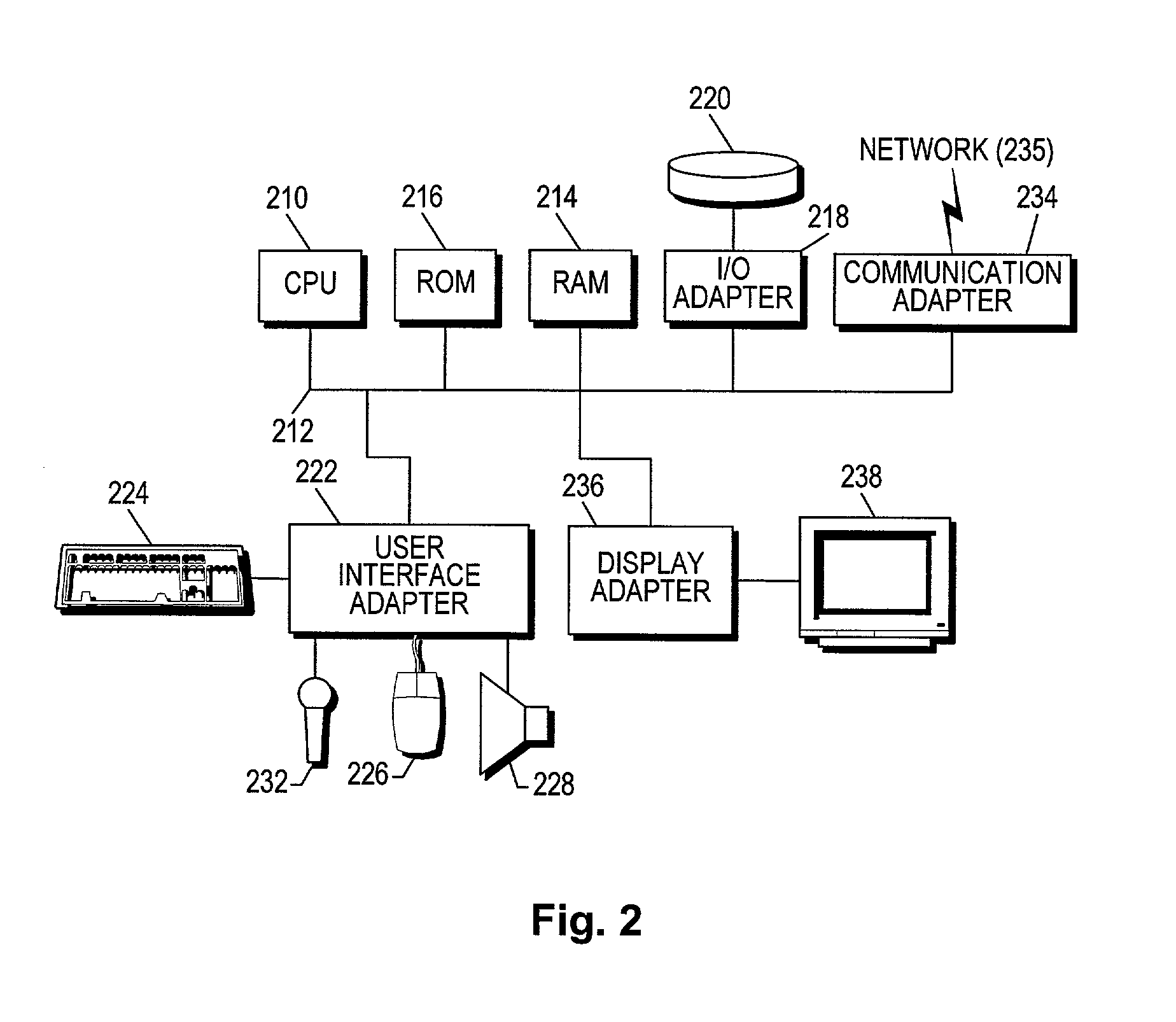

Method of offloading iSCSI TCP/IP processing from a host processing unit, and related iSCSI TCP/IP offload engine

InactiveUS20060056435A1Reduce the burden onData switching by path configurationData streamIp processing

A method of offloading, from a host data processing unit (205), iSCSI TCP / IP processing of data streams coming through at least one TCP / IP connection (3071,3072,3073), and a related iSCSI TCP / IP Offload Engine (TOE). The method including: providing a Protocol Data Unit (PDU) header queue (311) adapted to store headers (HDR11, . . . , HDR32) of iSCSI PDUs received through the at least one TCP / IP connection; monitoring the at least one TCP / IP connection for an incoming iSCSI PDU to be processed; when at least a iSCSI PDU header is received through the at least one TCP / IP connection, extracting the iSCSI PDU header from the received PDU, and placing the extracted iSCSI PDU header into the PDU header queue; looking at the PDU header queue for ascertaining the presence of iSCSI PDUs to be processed, and processing the incoming iSCSI PDU based on information in the extracted iSCSU PDU header retrieved from the PDU header queue.

Owner:IBM CORP

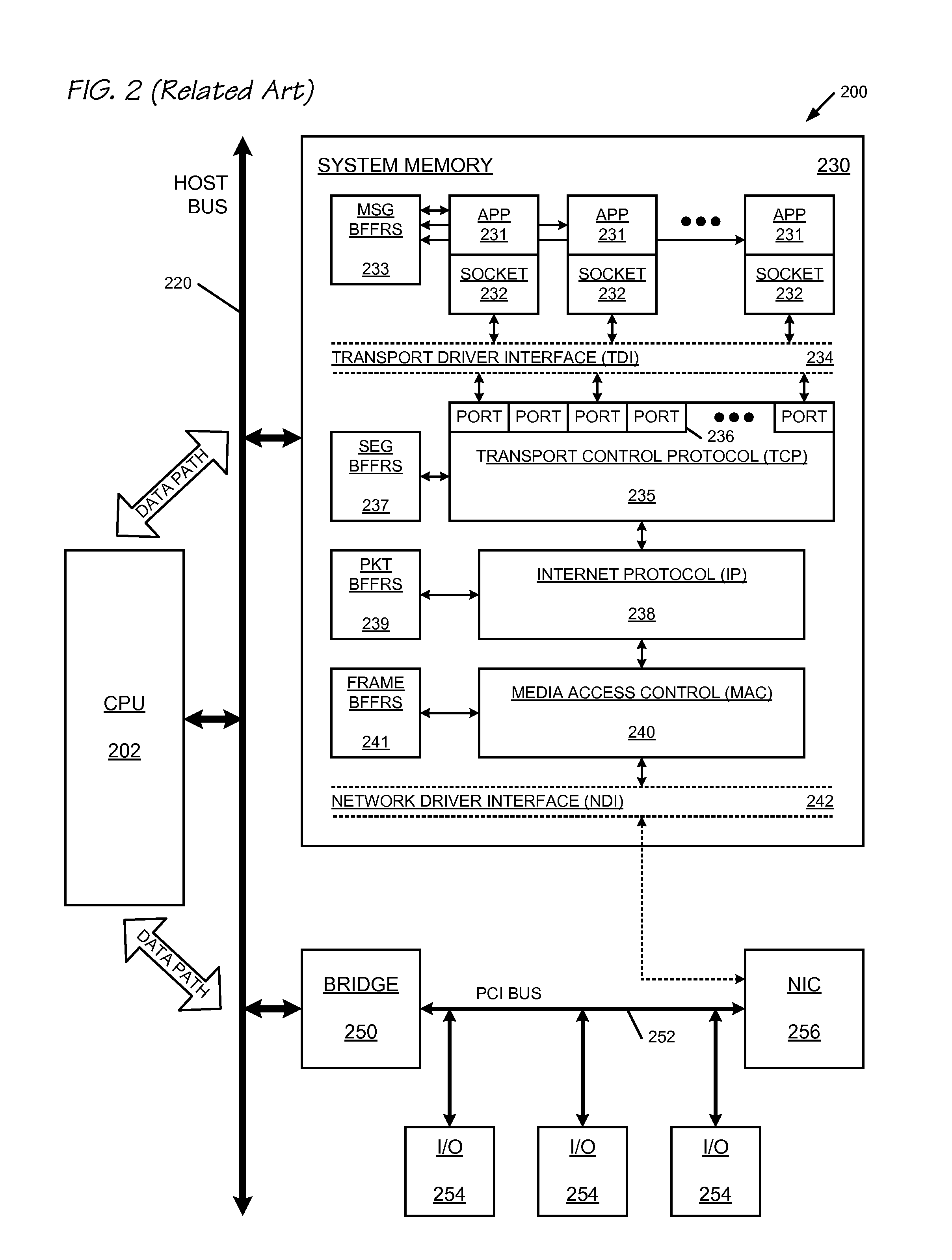

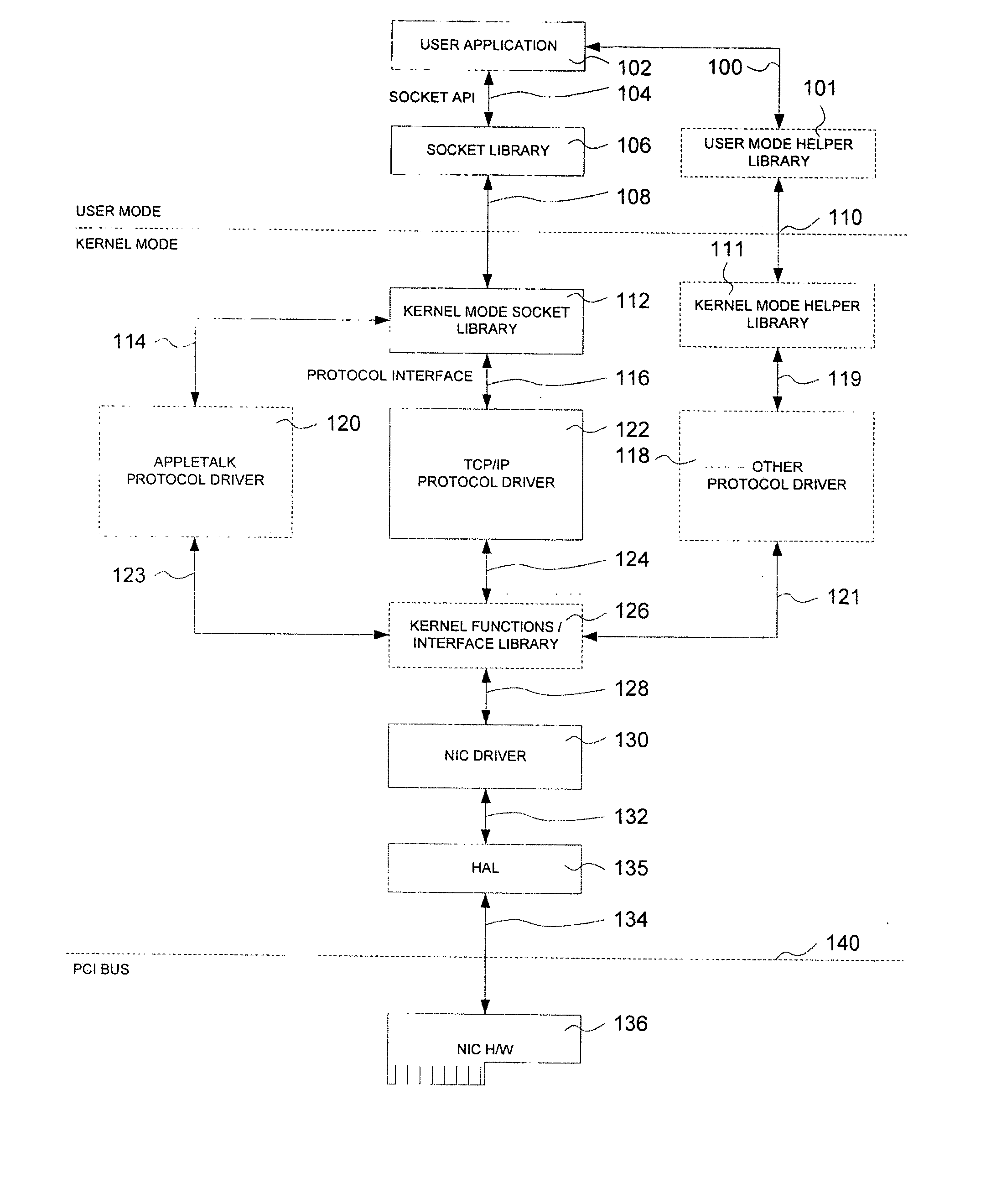

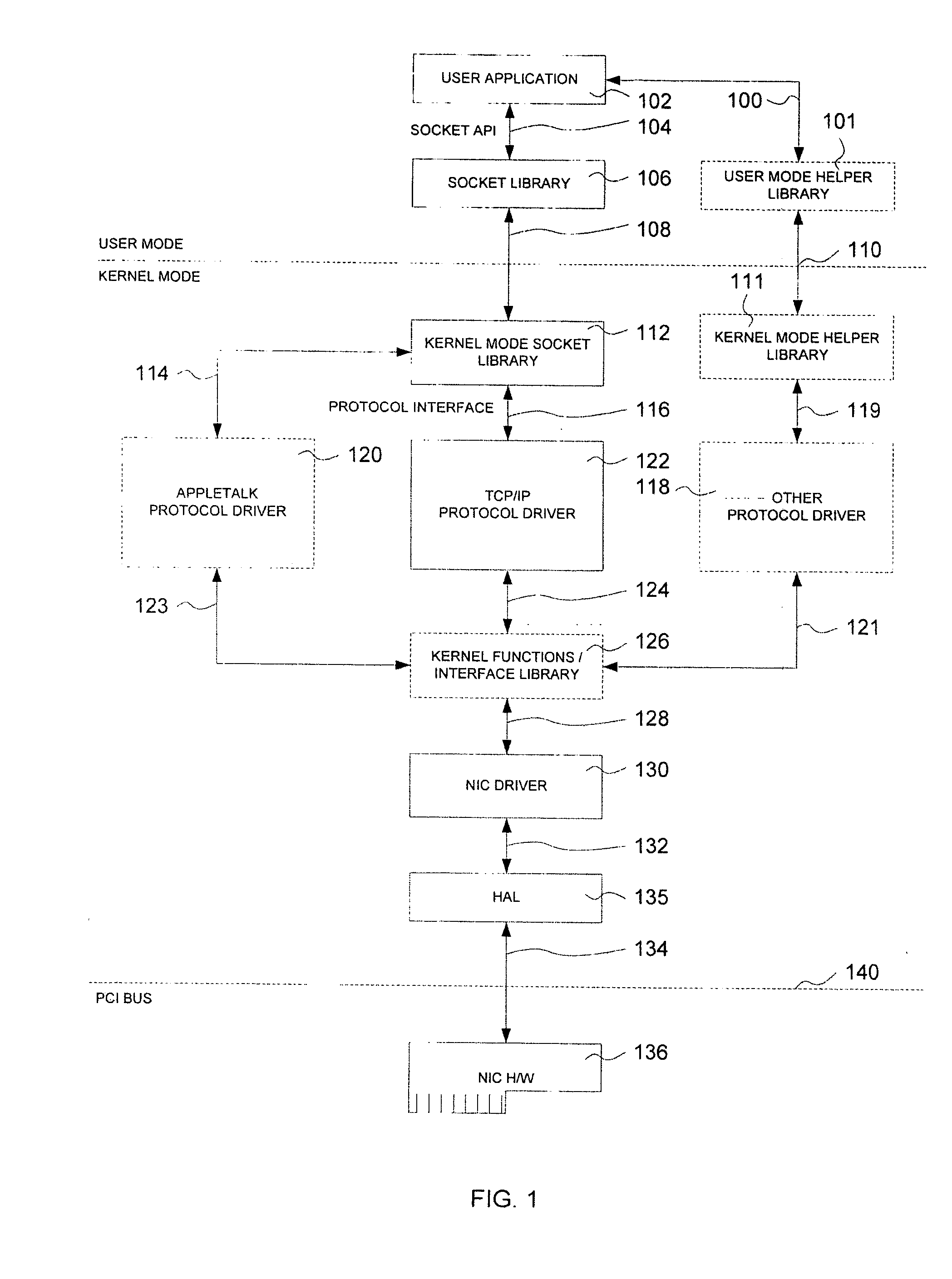

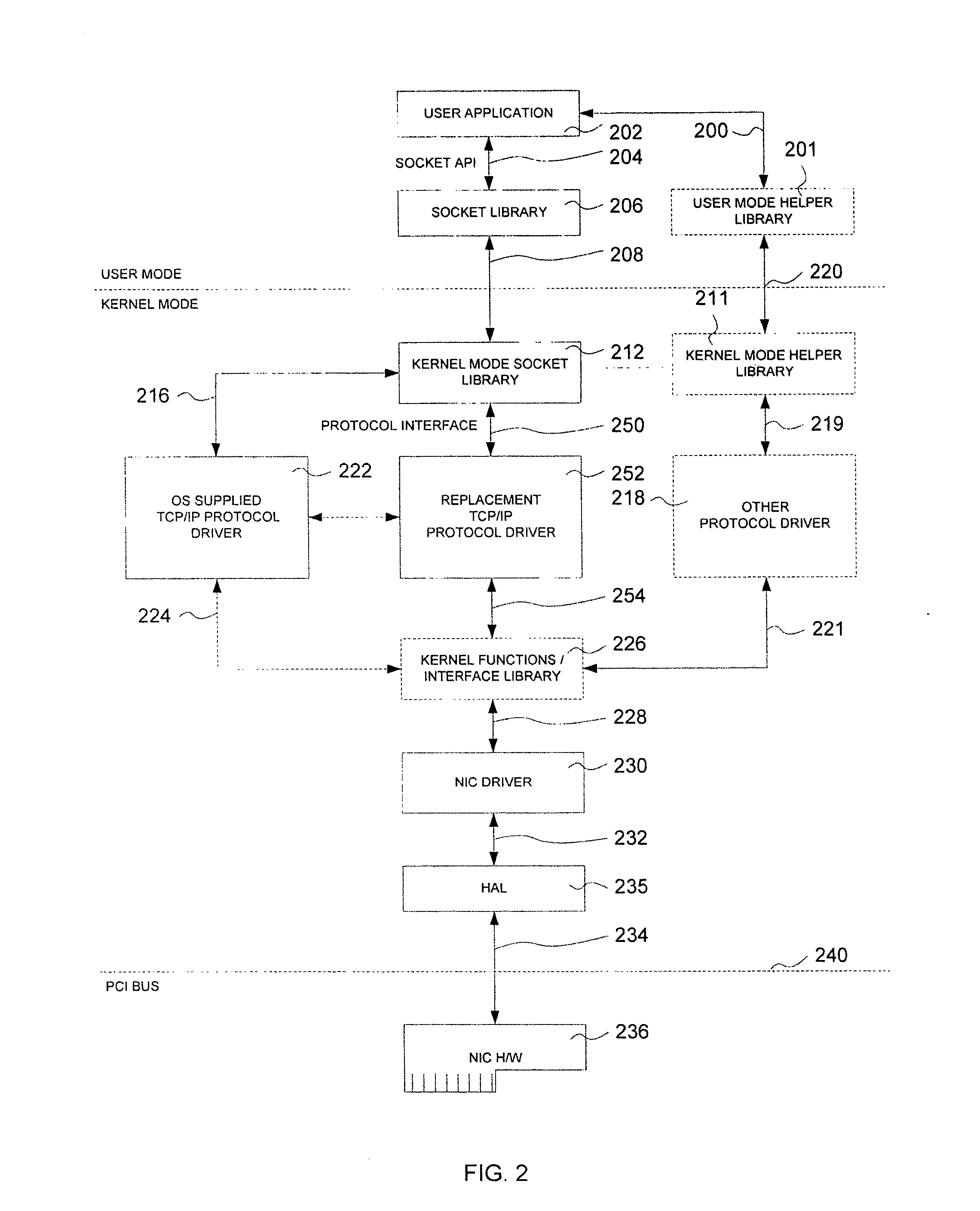

Methods and apparatus for offloading TCP/IP processing using a protocol driver interface filter driver

InactiveUS20050086349A1Resource allocationMultiple digital computer combinationsIp processingNetwork connection

A method for optimizing a network connection between a first device and a second device, the first device comprising a first packet protocol and a second packet protocol, the first packet protocol comprising a connection setup portion, the second protocol comprising a data transfer portion. The method includes initiating the network connection from the first device to said second device using the first packet protocol. The method further includes receiving an acknowledgement from the second device; and, initiating a data transfer between the first device and the second using the second packet protocol.

Owner:ADAPTEC

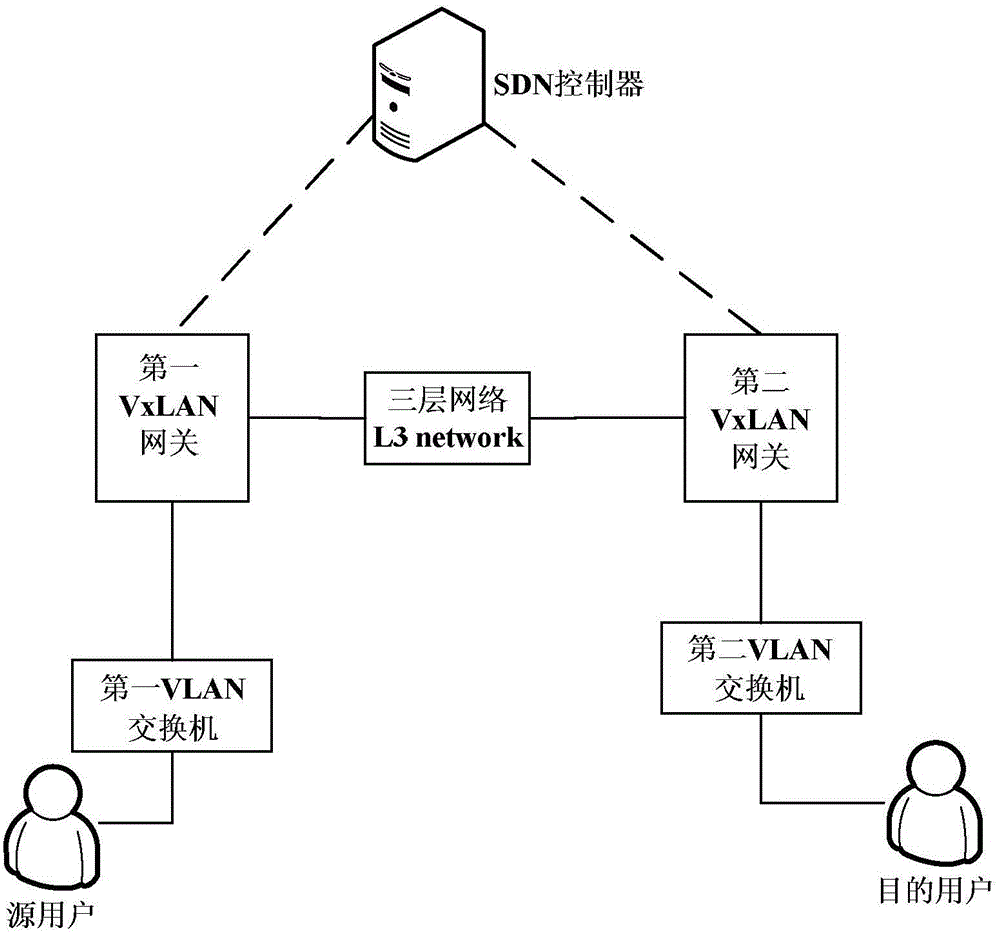

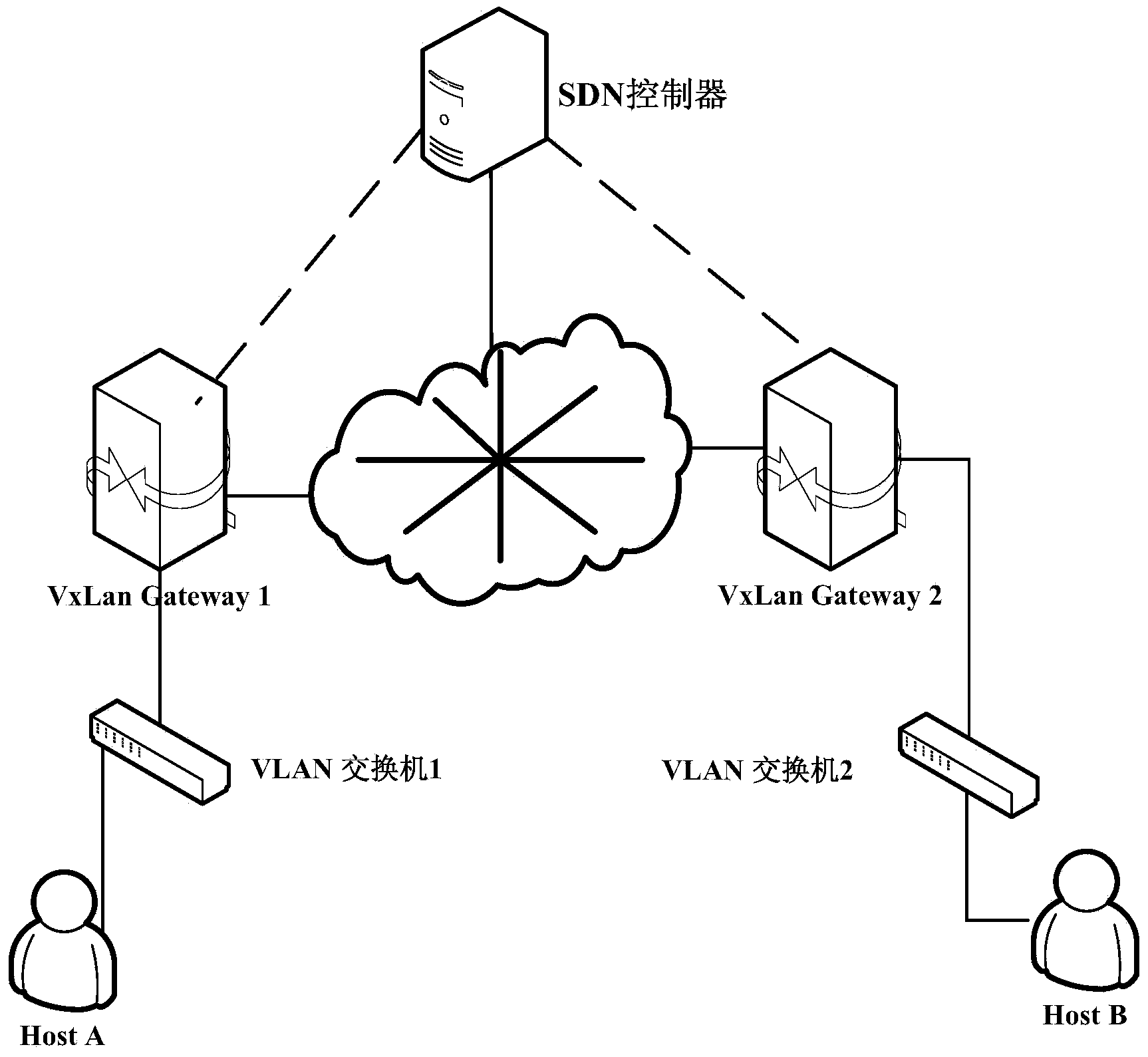

System and method for achieving multi-service priorities

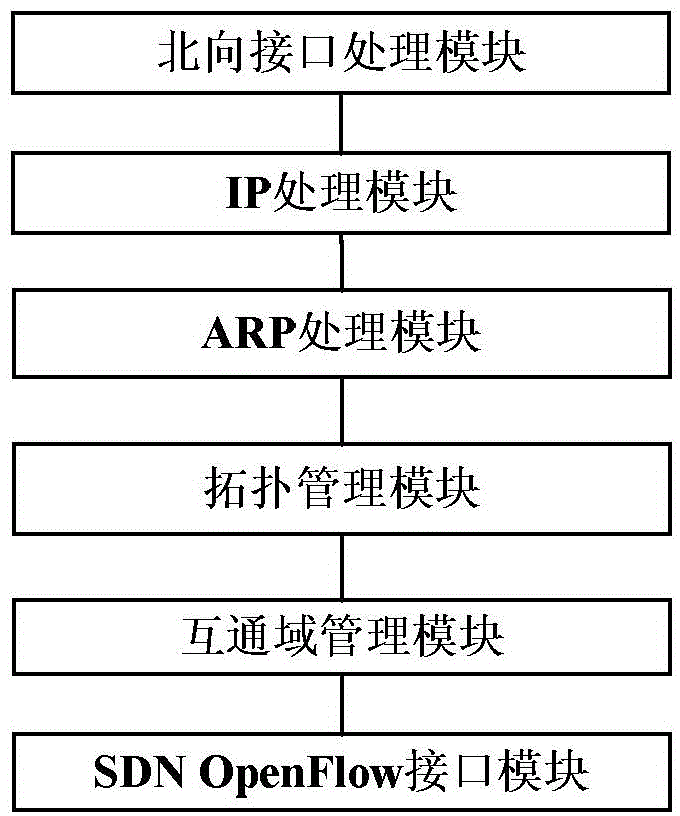

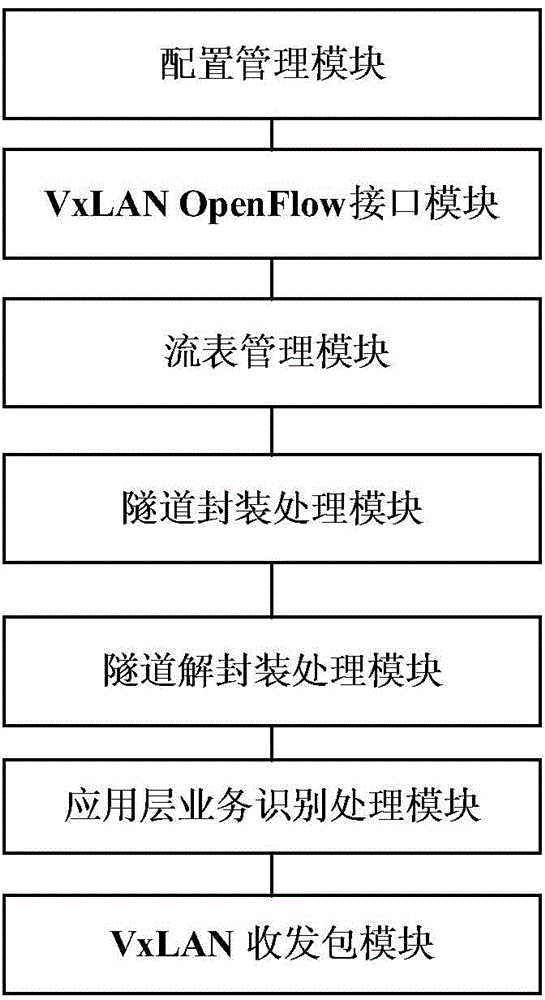

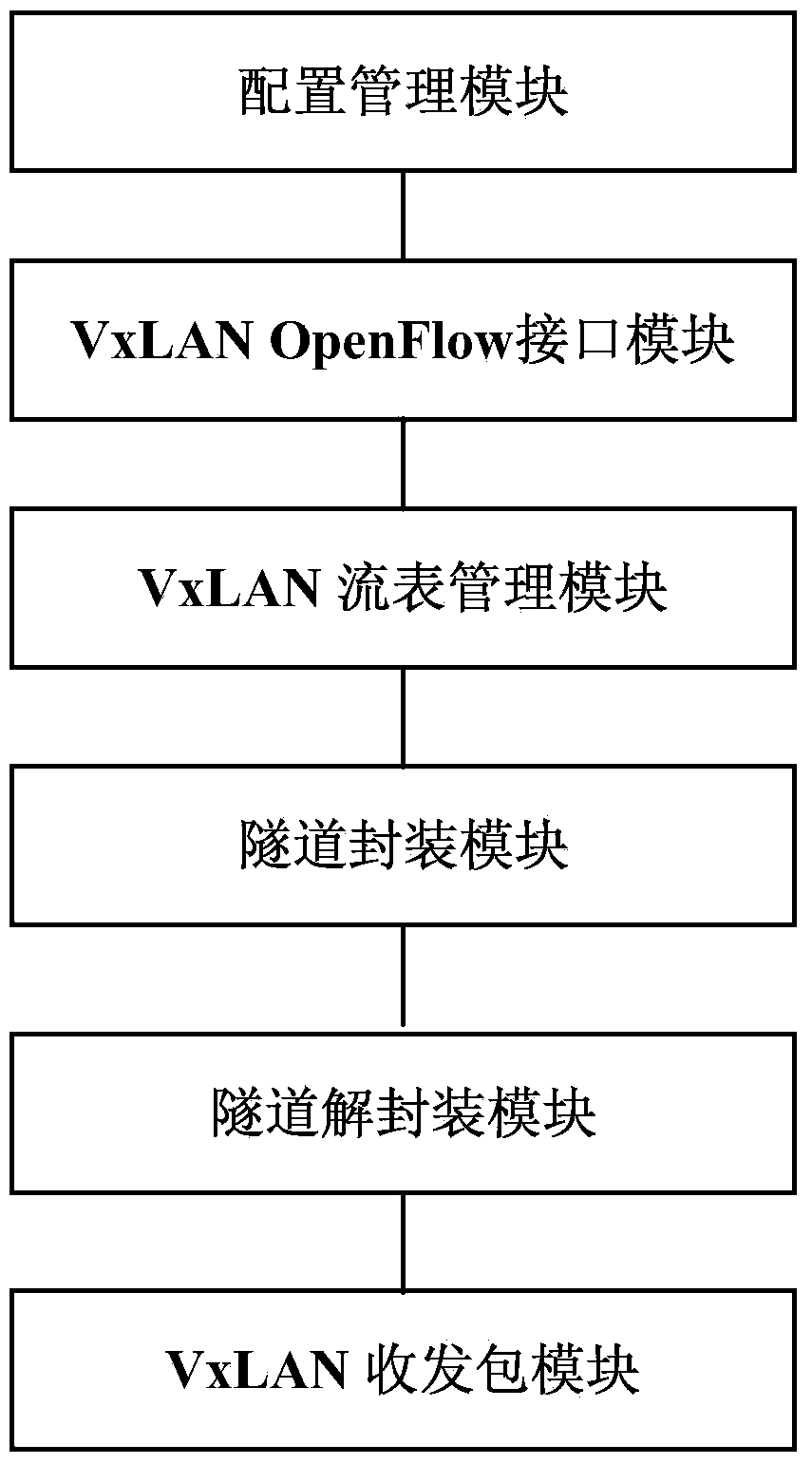

ActiveCN104468384AQuick identificationThe identification processing module performs business identification on data packets quicklyNetworks interconnectionTopology managementIp processing

The invention provides a system and method for achieving multi-service priorities and relates to the technical field of computer communication. The system comprises an SDN controller, at least one VxLAN gateway and at least two VLAN switches. The SDN controller comprises a northbound interface processing module, an IP processing module, an ARP processing module, a topology management module, an interflow domain management module and an SDN OpenFlow interface module. Each VxLAN gateway comprises a configuration management module, a VxLAN OpenFlow interface module, a flow table management module, a tunnel encapsulation processing module, a tunnel decapsulation processing module, an application layer service recognition processing module and a VxLAN receiving and transmitting package module. Each VLAN switch comprises a VLAN receiving and transmitting package module and a VLANID module. According to the system and the method, the performance of hardware is not required, a special communication processor does not need to be used, and the equipment cost is lowered.

Owner:WUHAN GREENET INFORMATION SERVICE

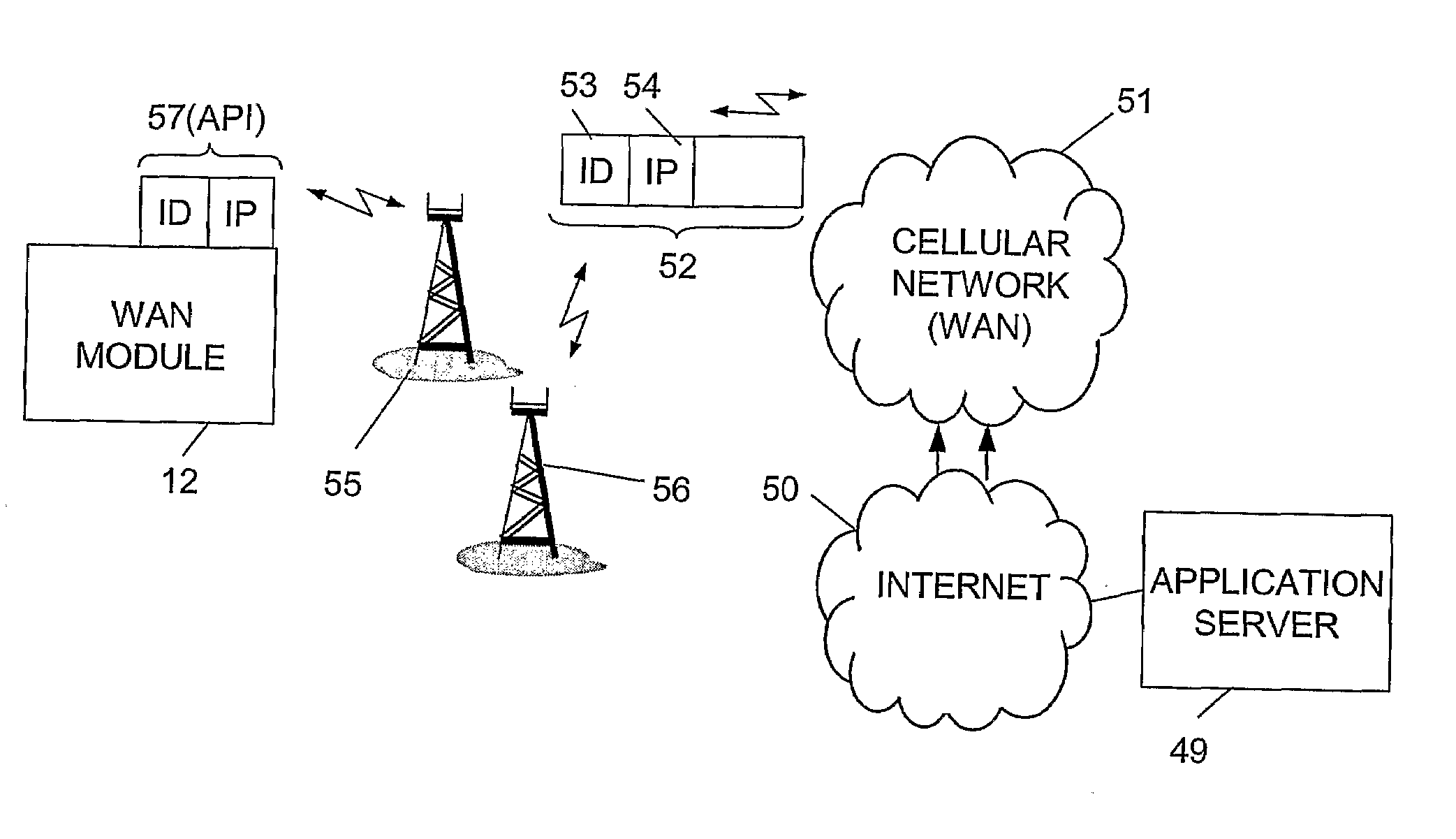

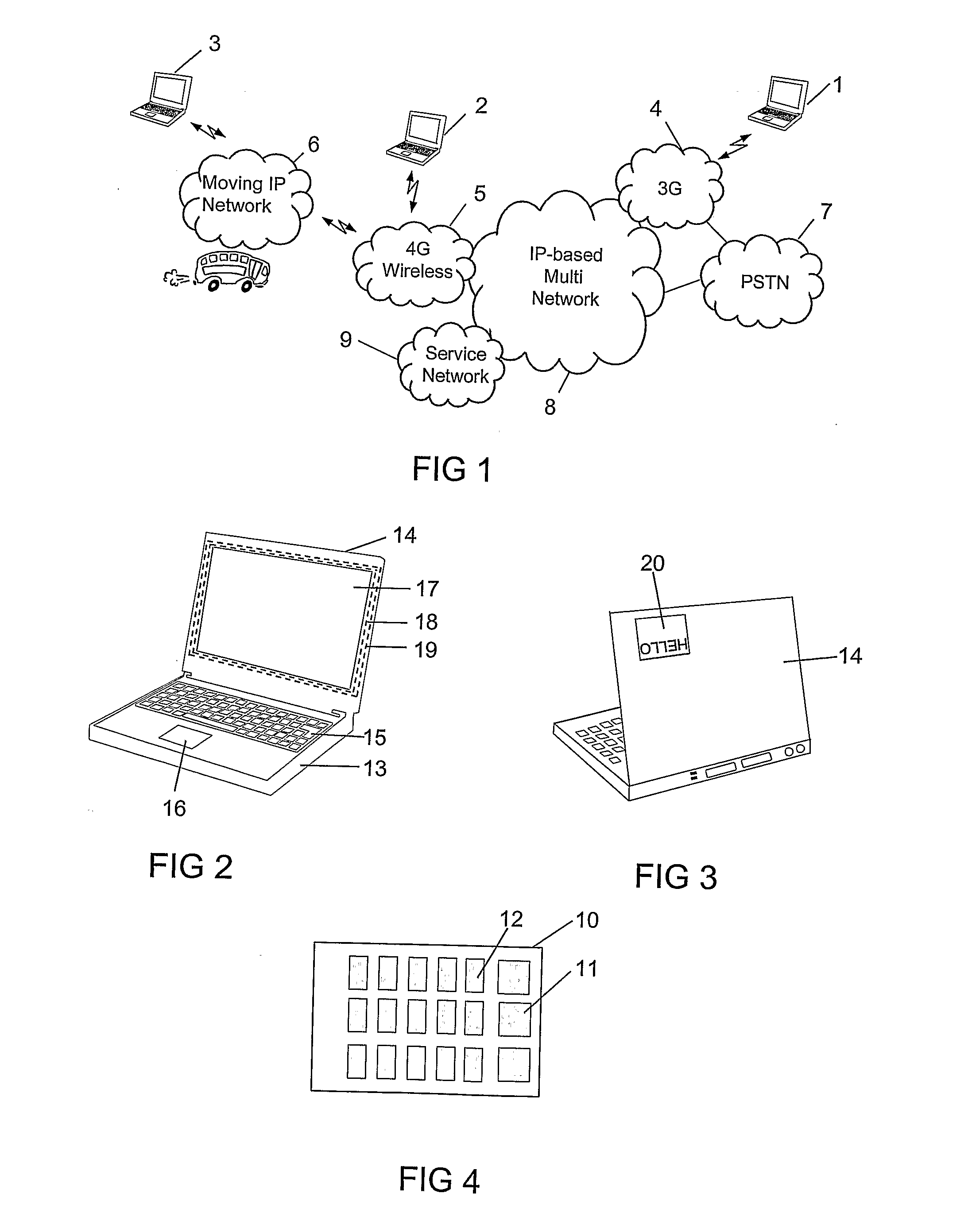

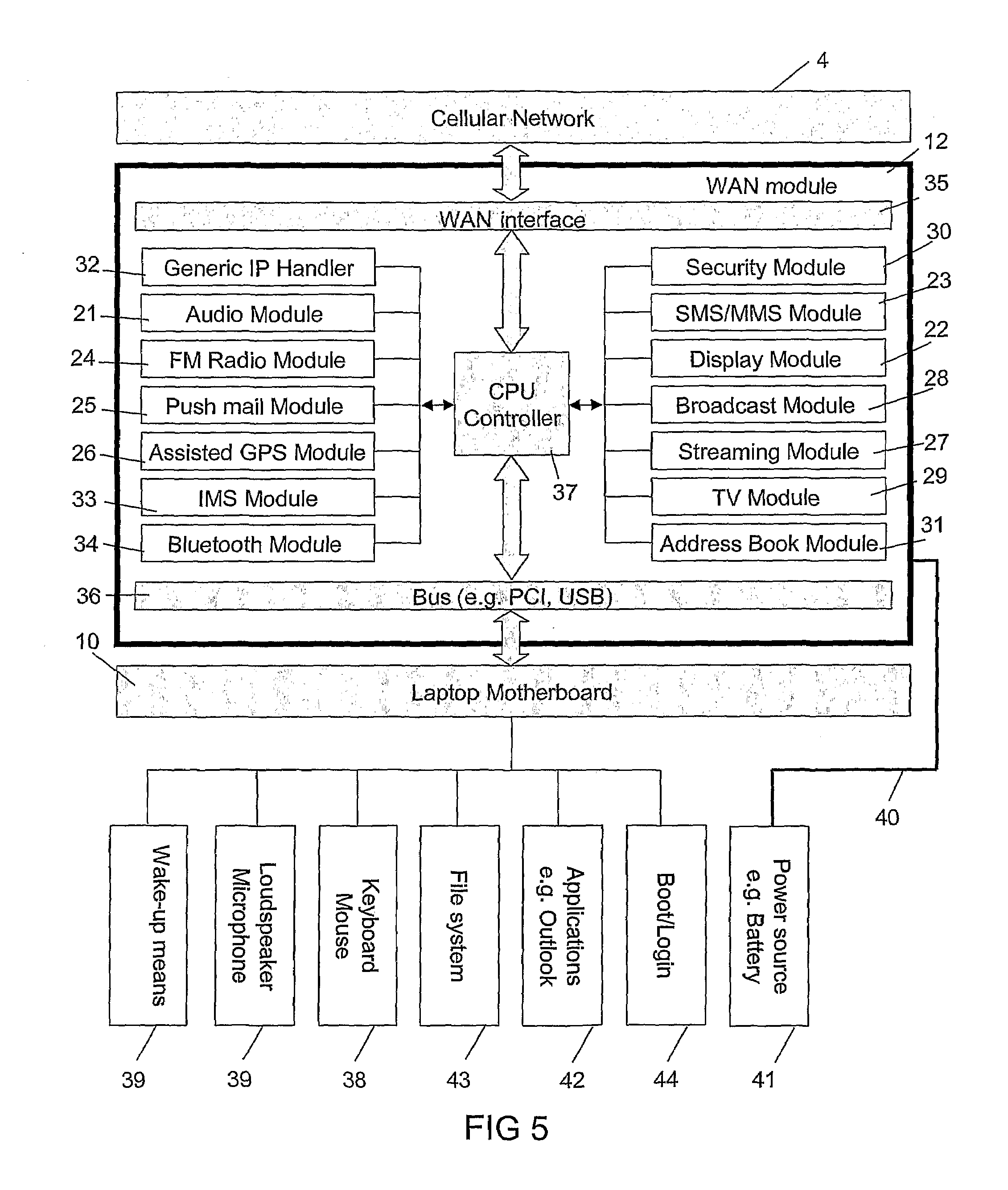

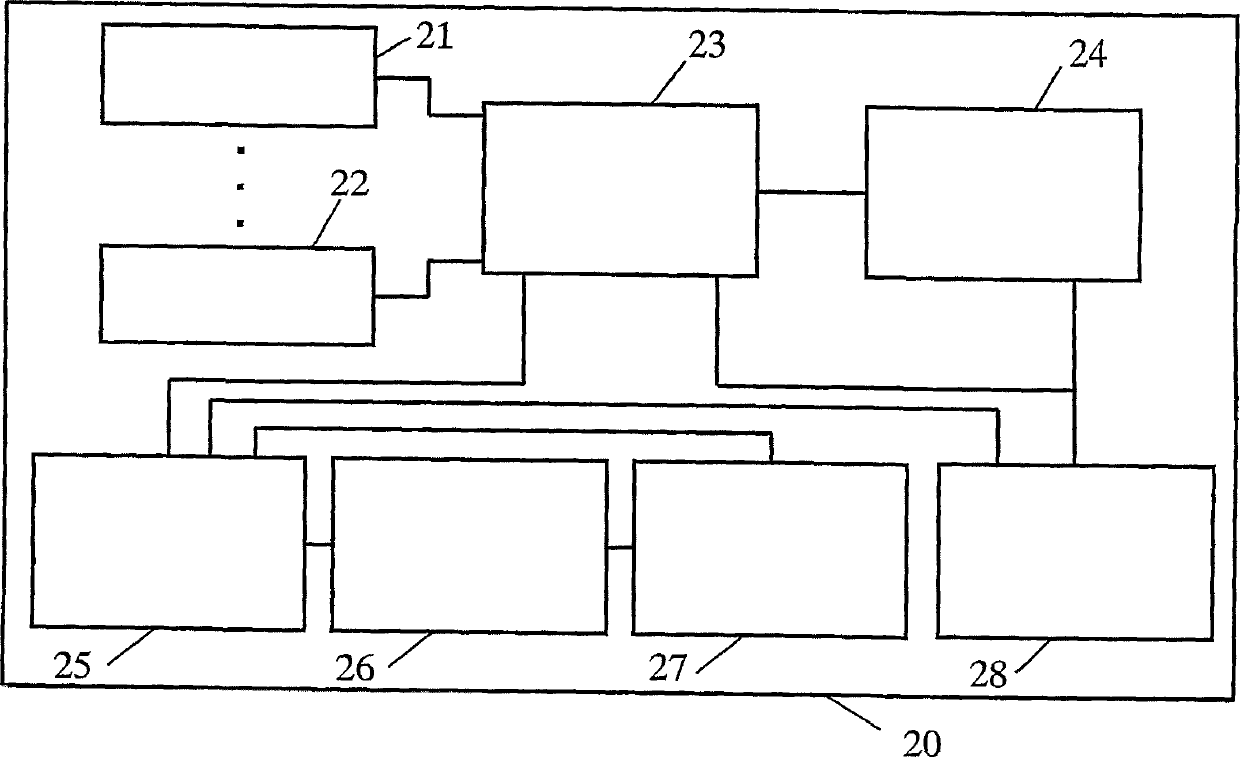

Integrated Portable WAN Module In Computer

InactiveUS20090197652A1Increase bitrateImprove performancePower managementEnergy efficient ICTIp processingDisplay device

The invention relates to an integrated portable computer (1) and WAN module (12). The WAN module comprises a cell phone platform provided with a plurality of functional modules (21-34). The WAN module is connected to a battery (41) of the portable computer so as to supply power to the WAN module and allow operation of the functional modules while the portable is in operating mode as well as while the portable computer is in sleeping mode. A casing (13, 14) of the portable computer is provided with an extra display (20) allowing notification and also presentation of a received instant message while the computer is in sleeping mode. The casing (13, 14) of the computer is provided with a plurality of antennas (17-19). Examples of functional modules are a push mail module (25), an IMS module (33), a streaming media module (27), a security module (30) and a generic IP handler module (32).

Owner:TELEFON AB LM ERICSSON (PUBL)

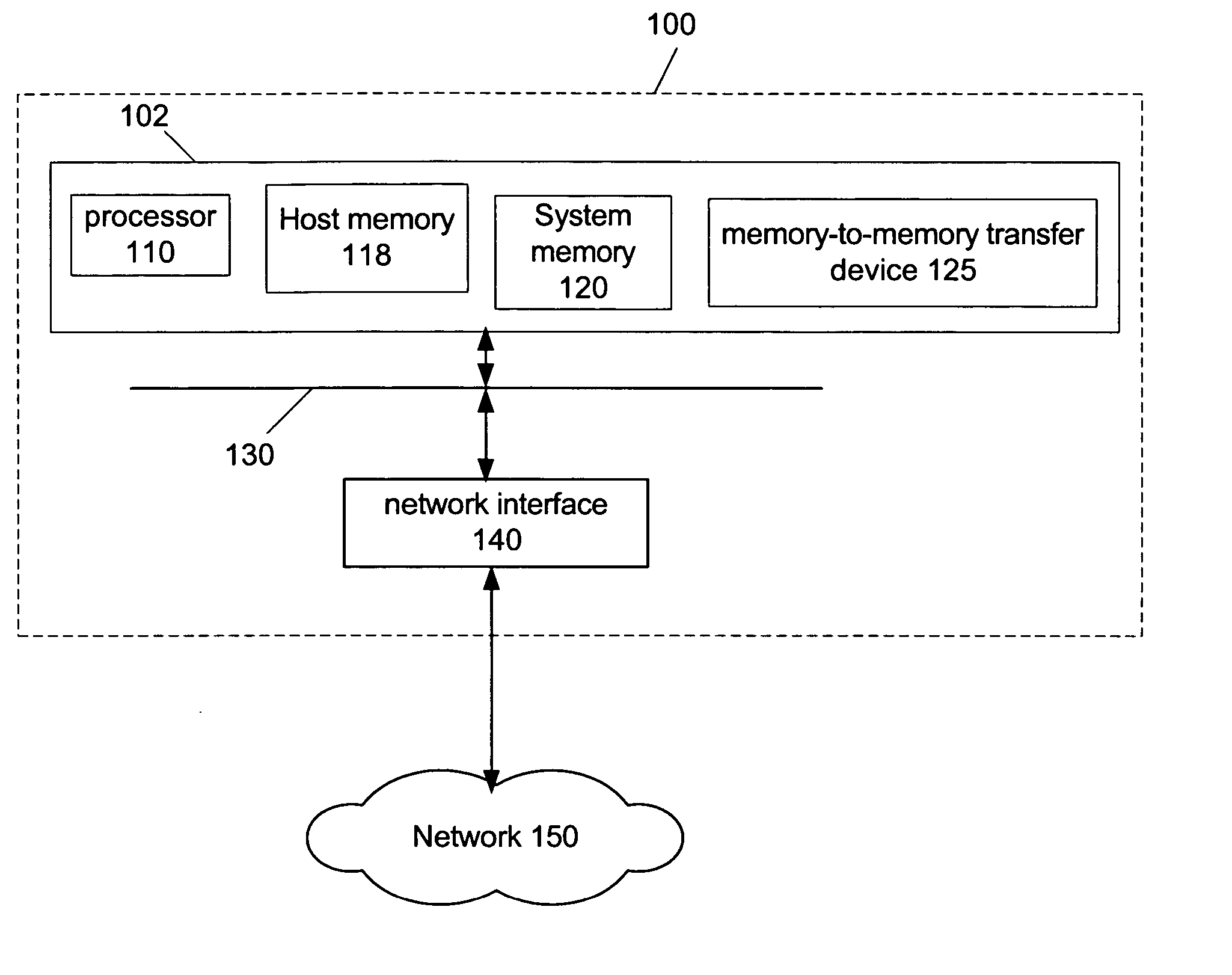

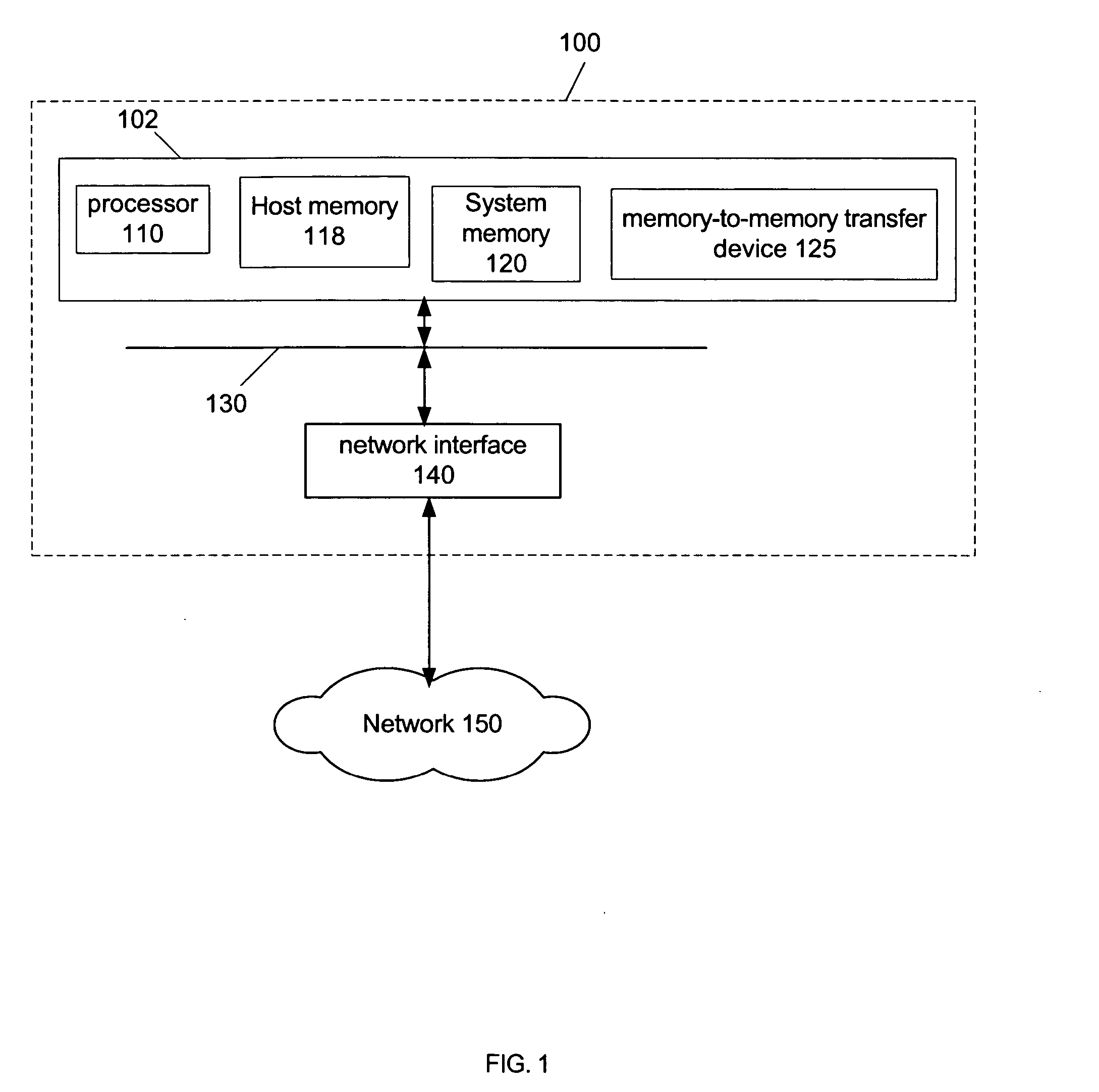

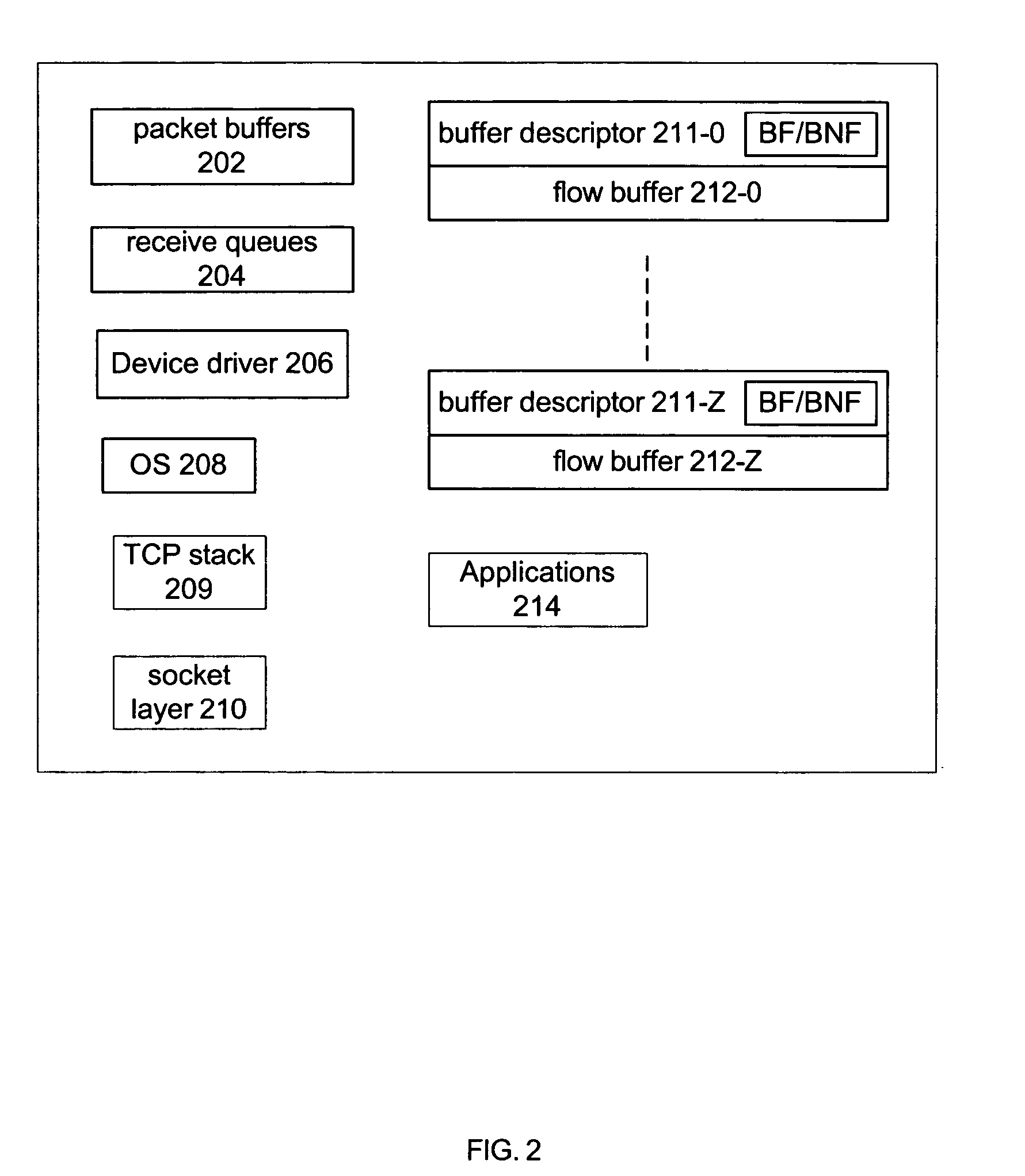

Techniques to reduce latency in receive side processing

Techniques for accelerating network receive side processing of packets. Packets may be associated into flow groupings and stored in flow buffers. Packet headers that are available for TCP / IP processing may be provided for processing. If a payload associated with a header is not available for processing then a descriptor associated with the header is tagged as indicating the payload is not available for processing.

Owner:INTEL CORP

Selective acceleration of transport control protocol (TCP) connections

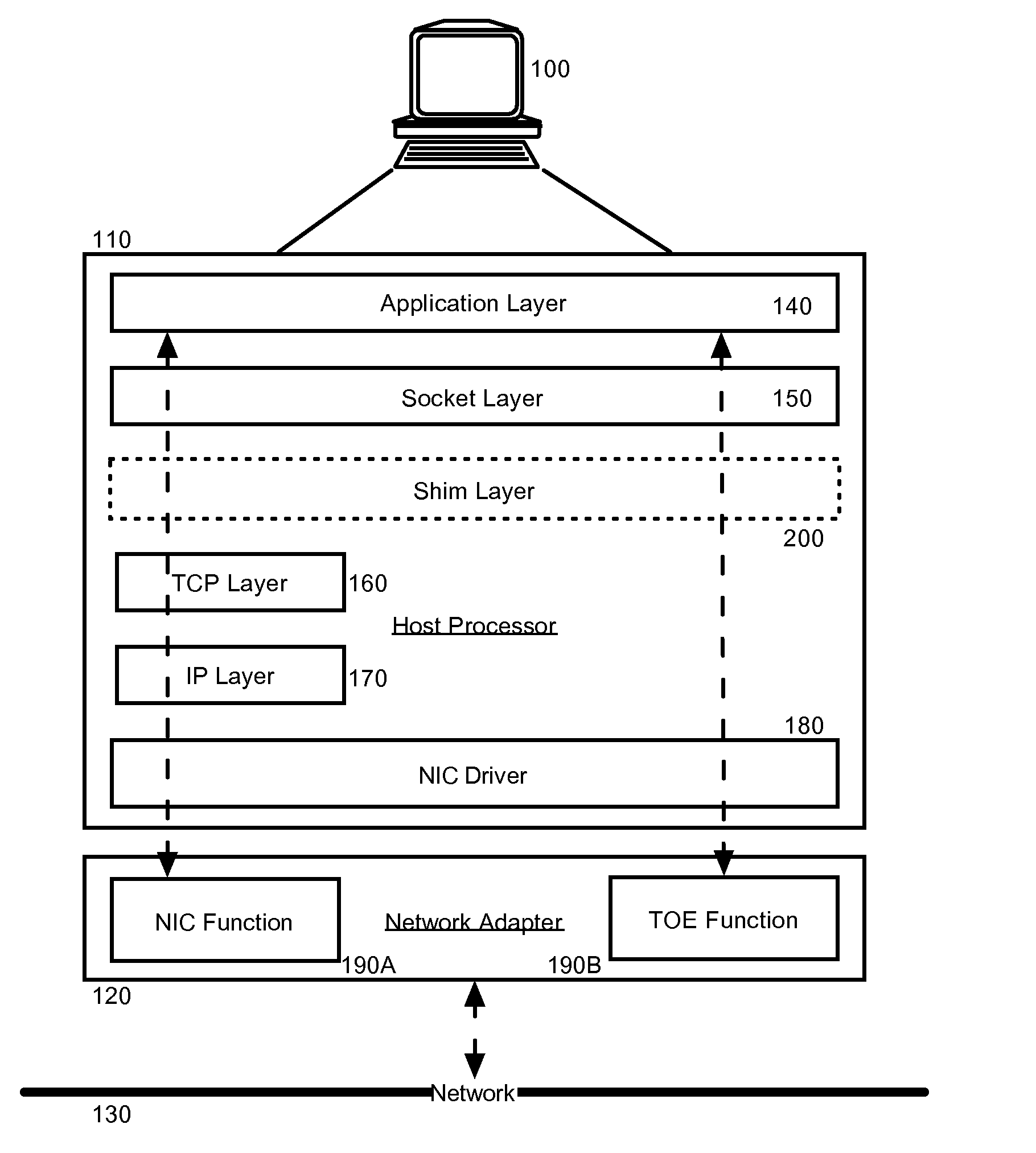

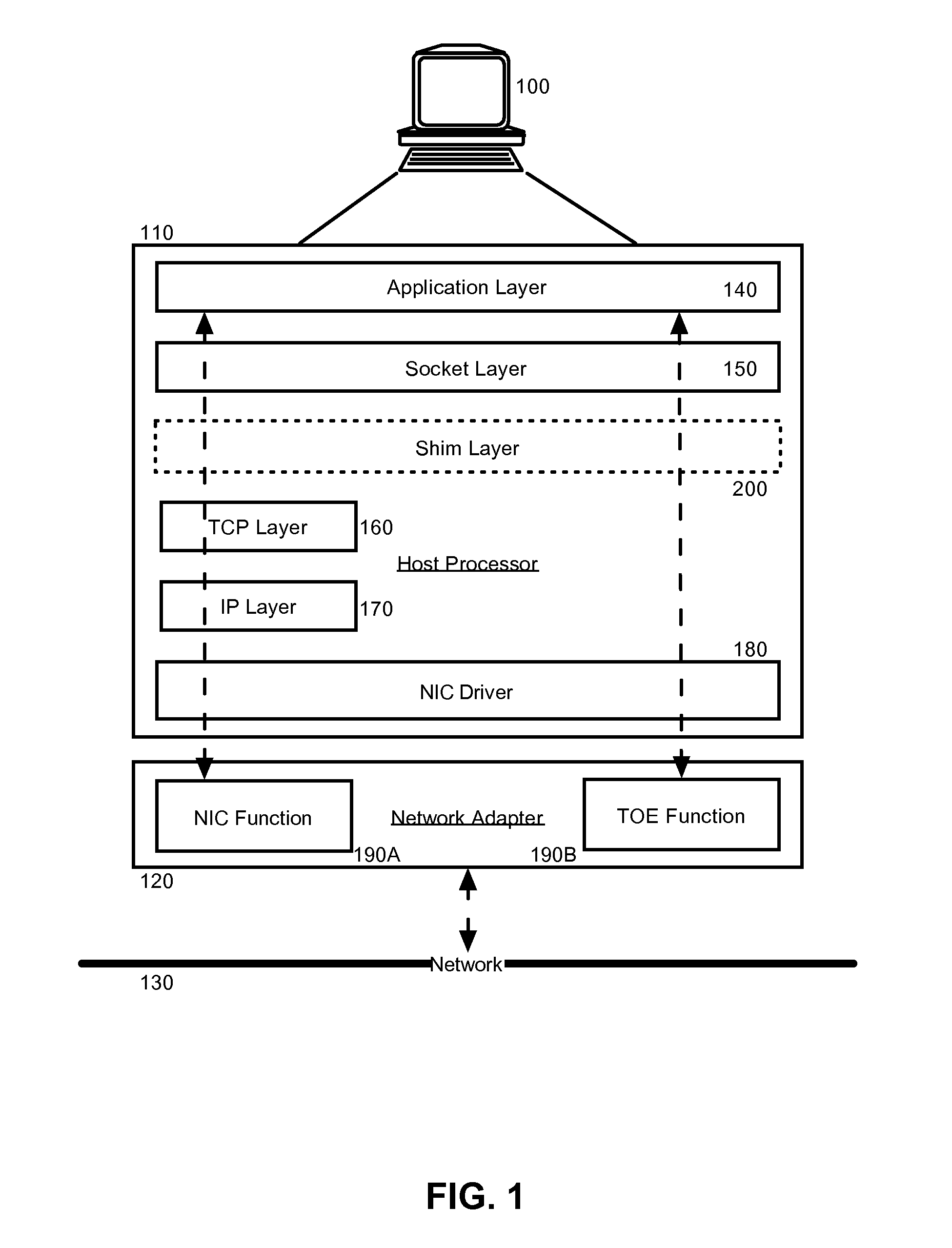

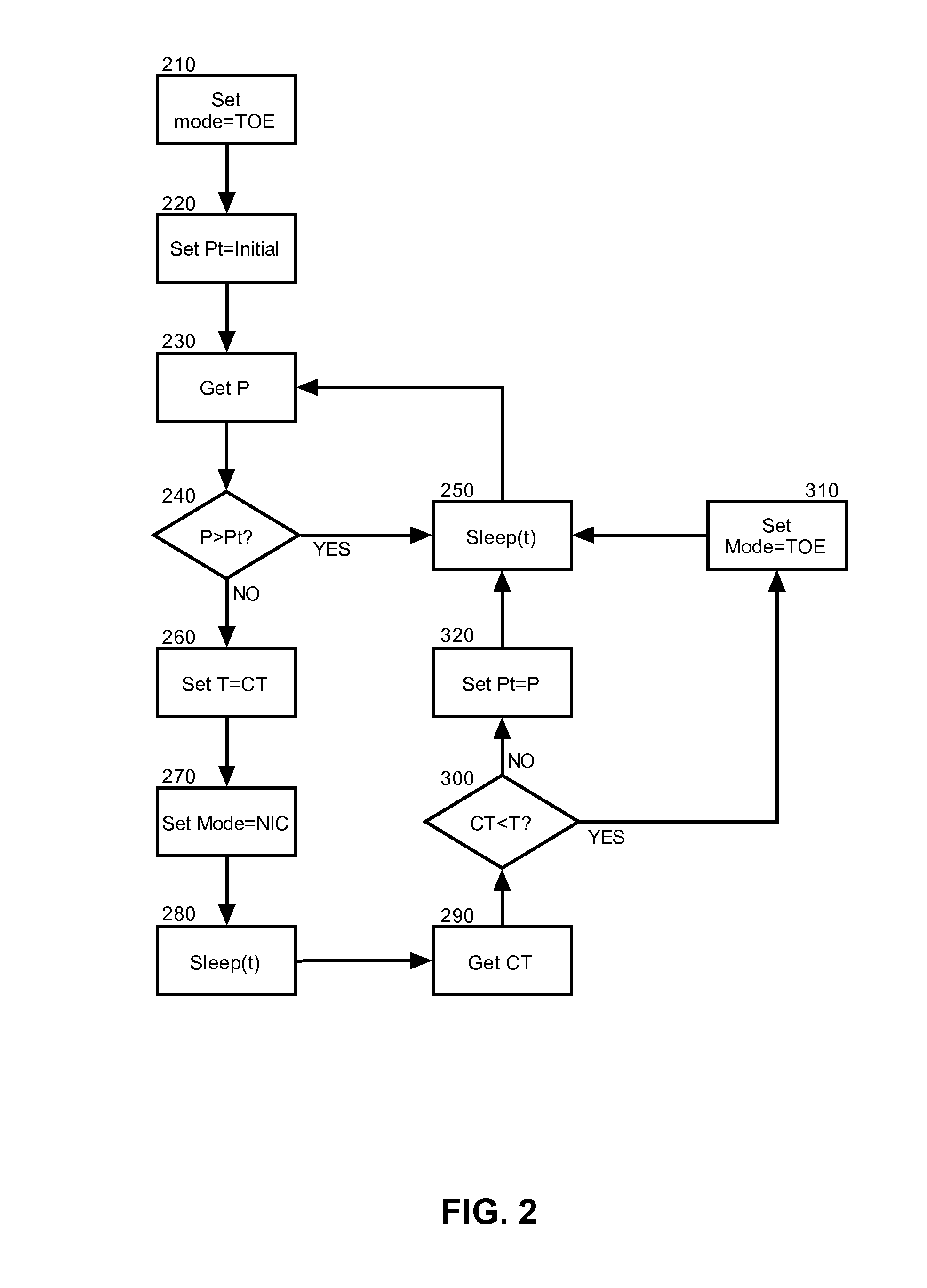

InactiveUS20080120426A1Multiple digital computer combinationsTransmissionIp processingRTP Control Protocol

Embodiments of the present invention address deficiencies of the art in respect to TCP processing and provide a novel and non-obvious method, system and computer program product for selectively accelerating TCP connections. In one embodiment of the invention, a method of selectively accelerating TCP connections in TCP / IP based inter-process communications can be provided. The method can include establishing a TCP connection for TCP / IP inter-process communications, observing a block size for the TCP connection, and switching between TCP / IP processing in a host processor and TCP / IP processing in a TOE in a network adapter coupled to the host processor based upon the observed block size exceeding a threshold value.

Owner:IBM CORP

ARP broadcast restraining system and method for achieving VxLAN based on SDN framework

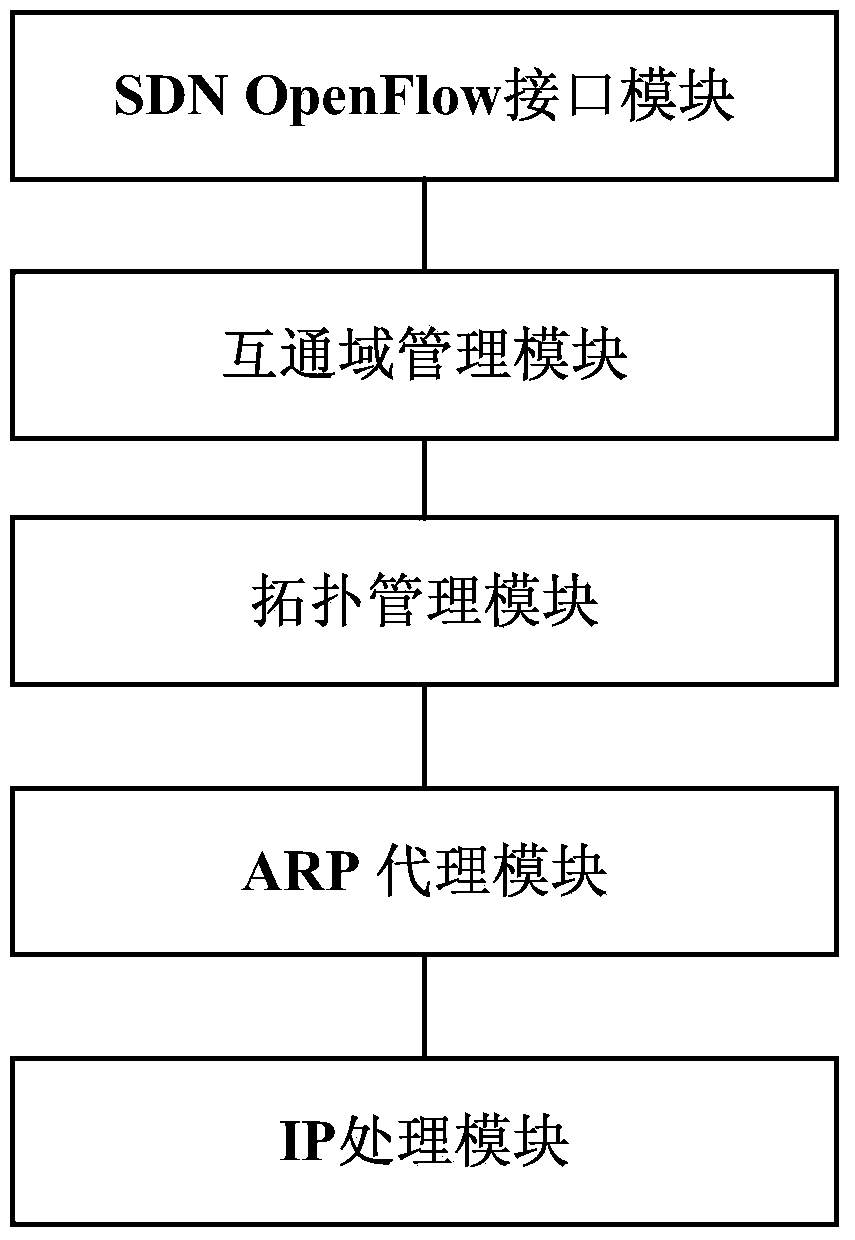

ActiveCN104320267AReduce the number of passesEasy to useSpecial service provision for substationTopology managementIp processing

The invention discloses an ARP broadcast restraining system and method for achieving a VxLAN based on an SDN framework and relates to the field of the VxLAN in a data center. The system comprises an SDN controller, VxLAN Gateways and VLAN interchangers. The SDN controller comprises an SDN OpenFlow interface module, a communication domain management module, a topology management module, an ARP proxy module and an IP processing module, wherein all the modules are sequentially connected. Each VxLAN Gateway comprises a configuration management module, a VxLAN OpenFlow interface module, a flow meter management module, a tunnel encapsulation module, a tunnel decapsulation module and a VxLAN package receiving and sending module, wherein all the modules are sequentially connected. Each VLAN interchanger comprises a VLAN package receiving and sending module and a VLAN ID module. The system and method are easy to achieve, the number of transmission times of ARP broadcast messages can be remarkably reduced, ARP broadcast in various scenes can be avoided, the broadcast restraining effect is good, and the system and method can be used by people conveniently.

Owner:WUHAN GREENET INFORMATION SERVICE

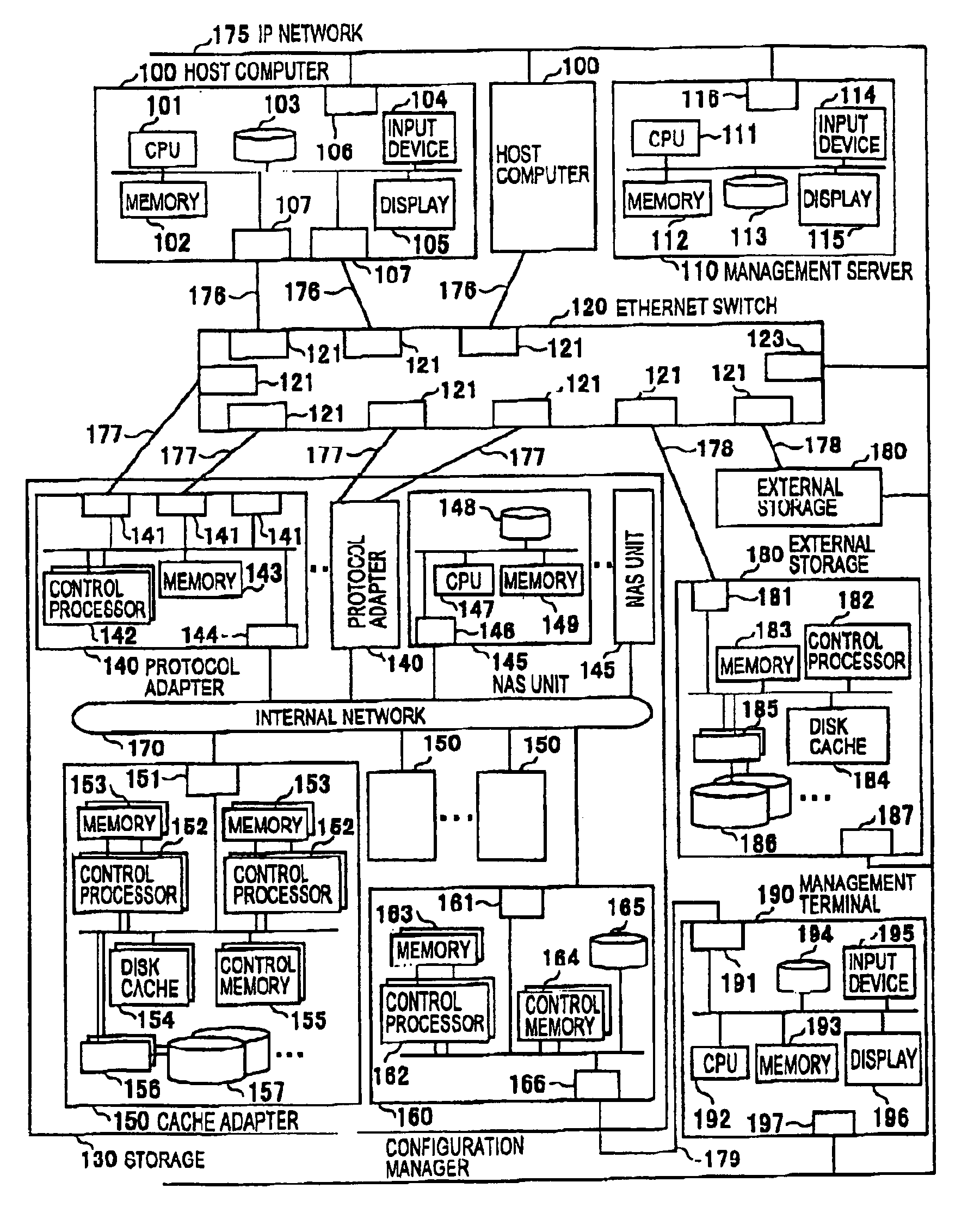

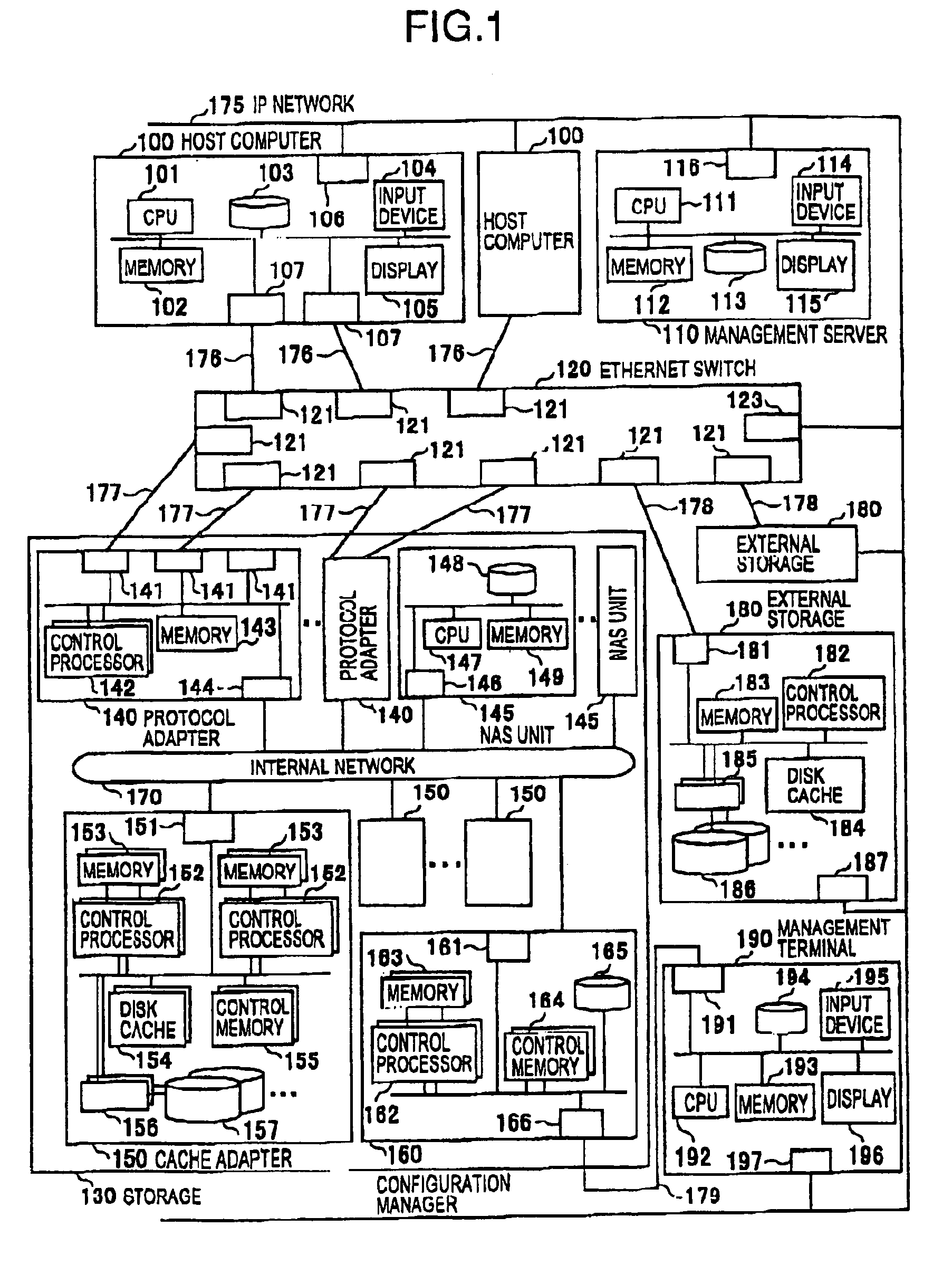

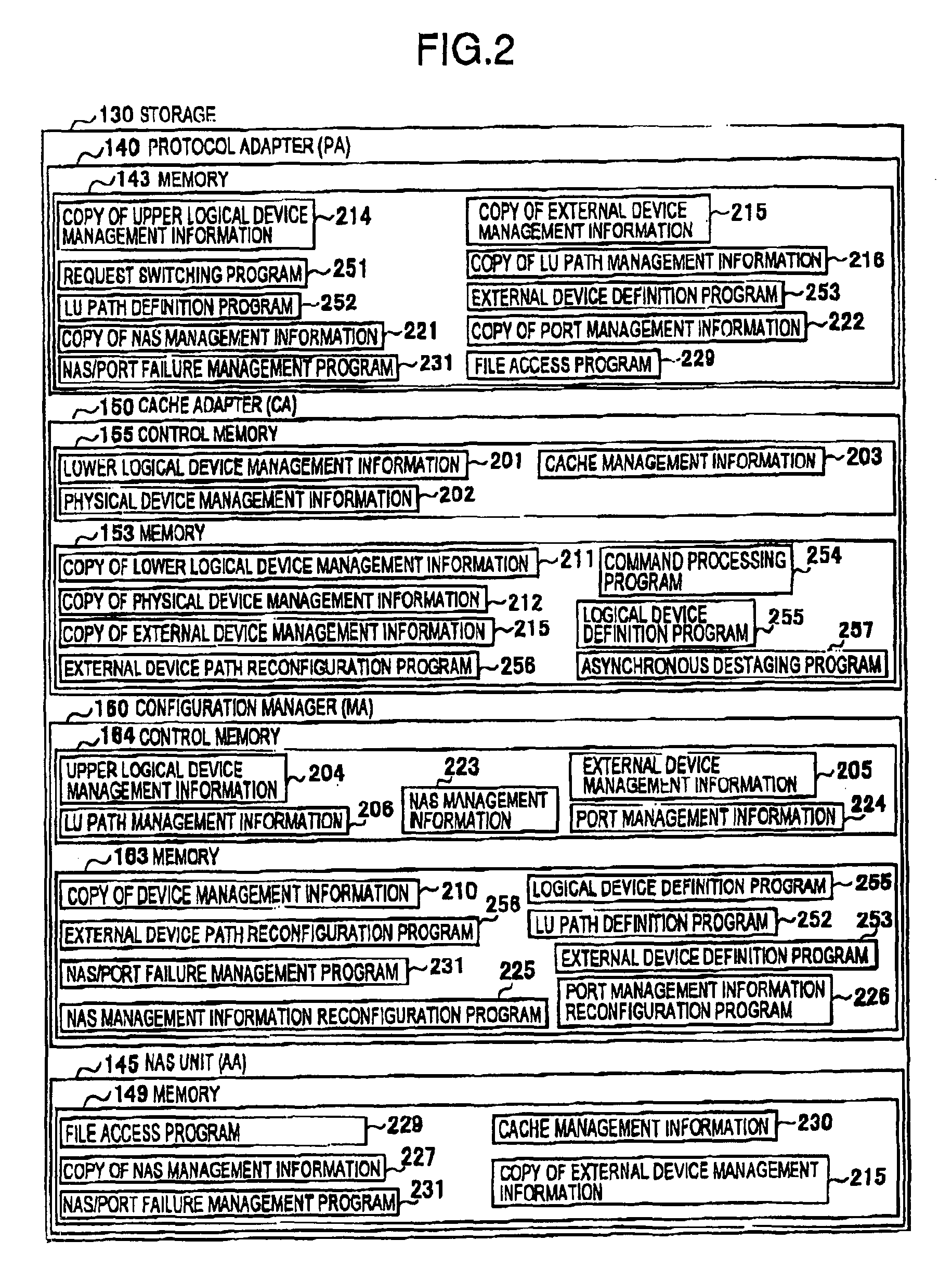

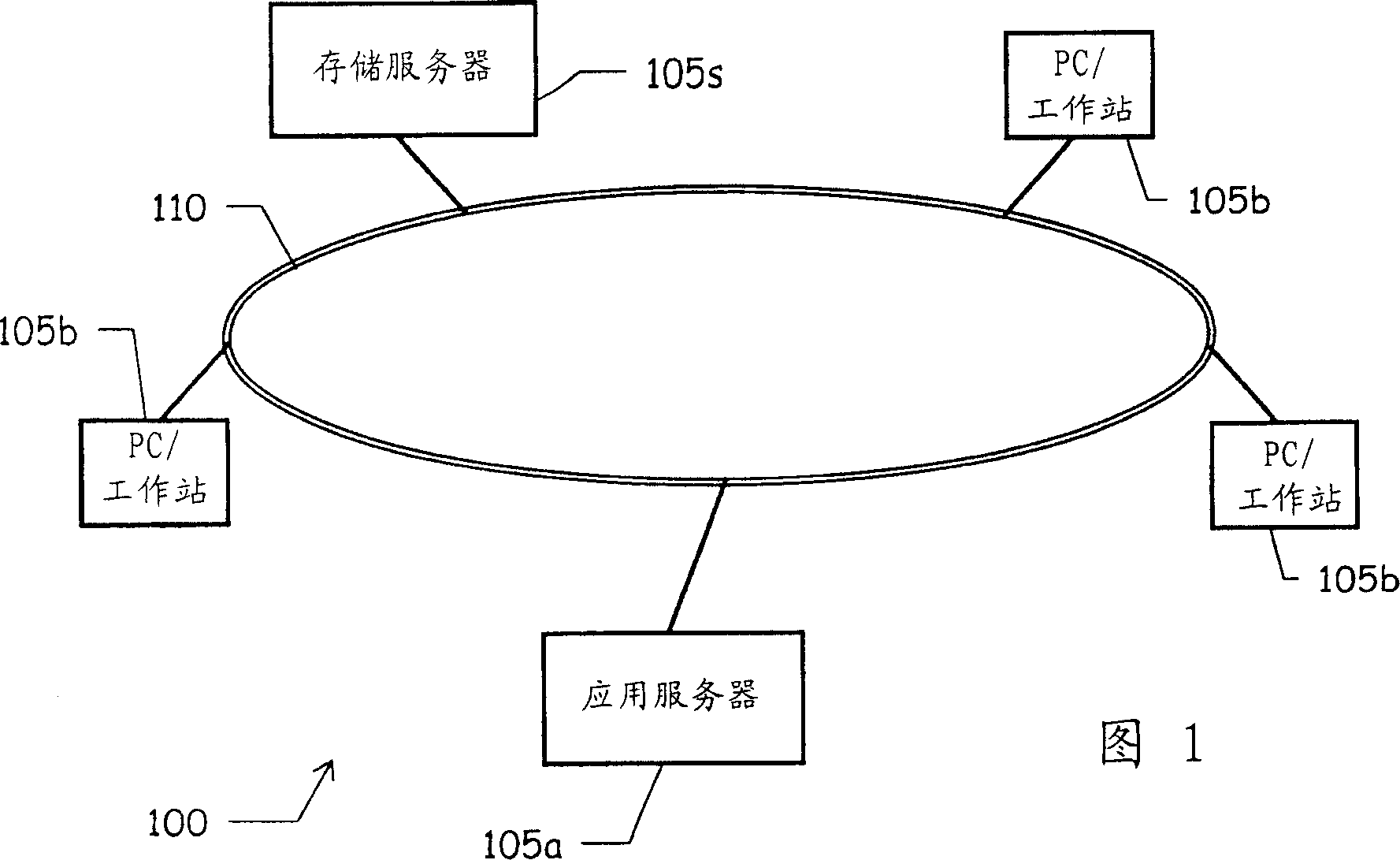

Storage system

ActiveUS6950914B2Input/output to record carriersDigital computer detailsExternal storageIp processing

Owner:GOOGLE LLC

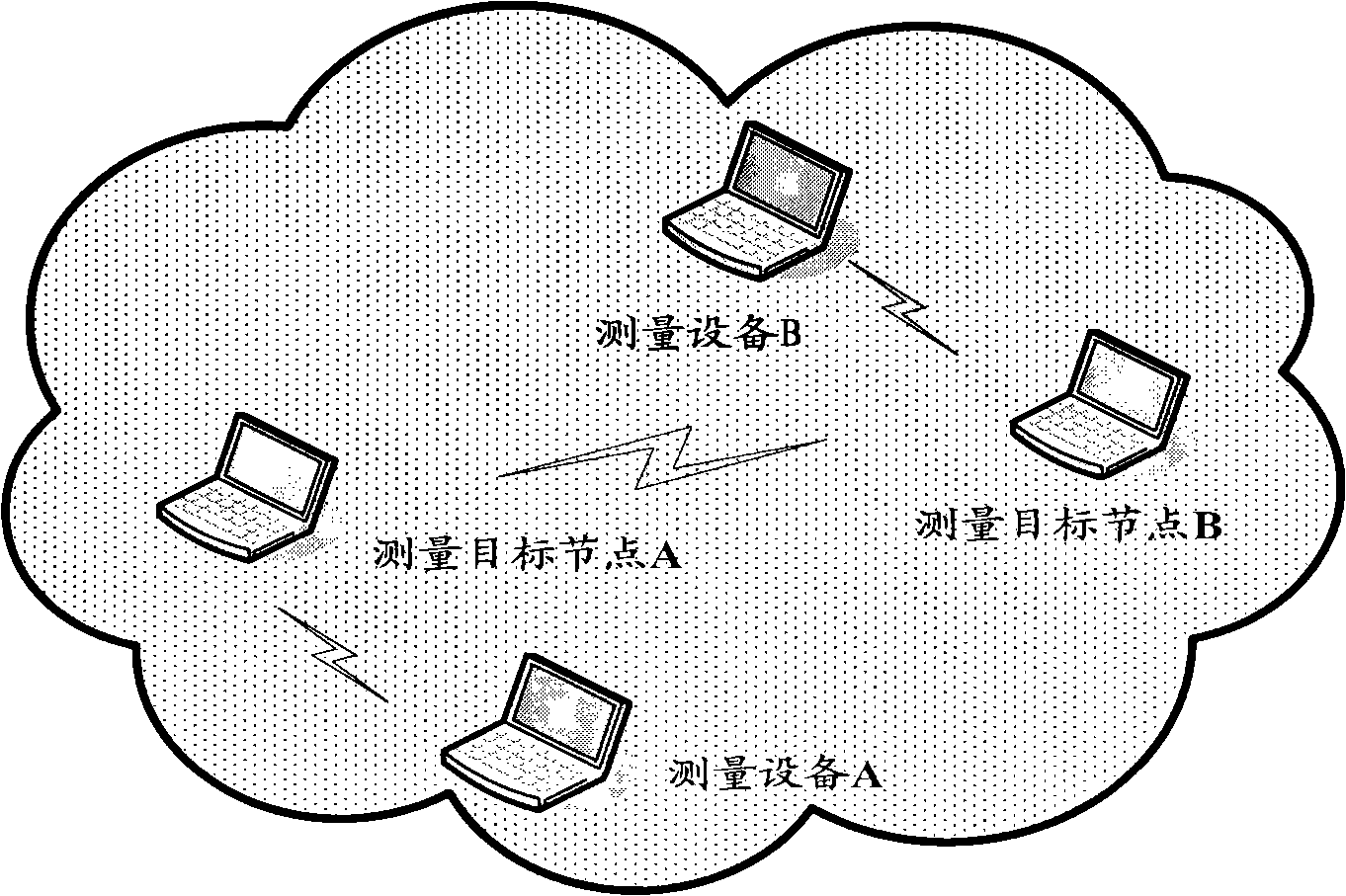

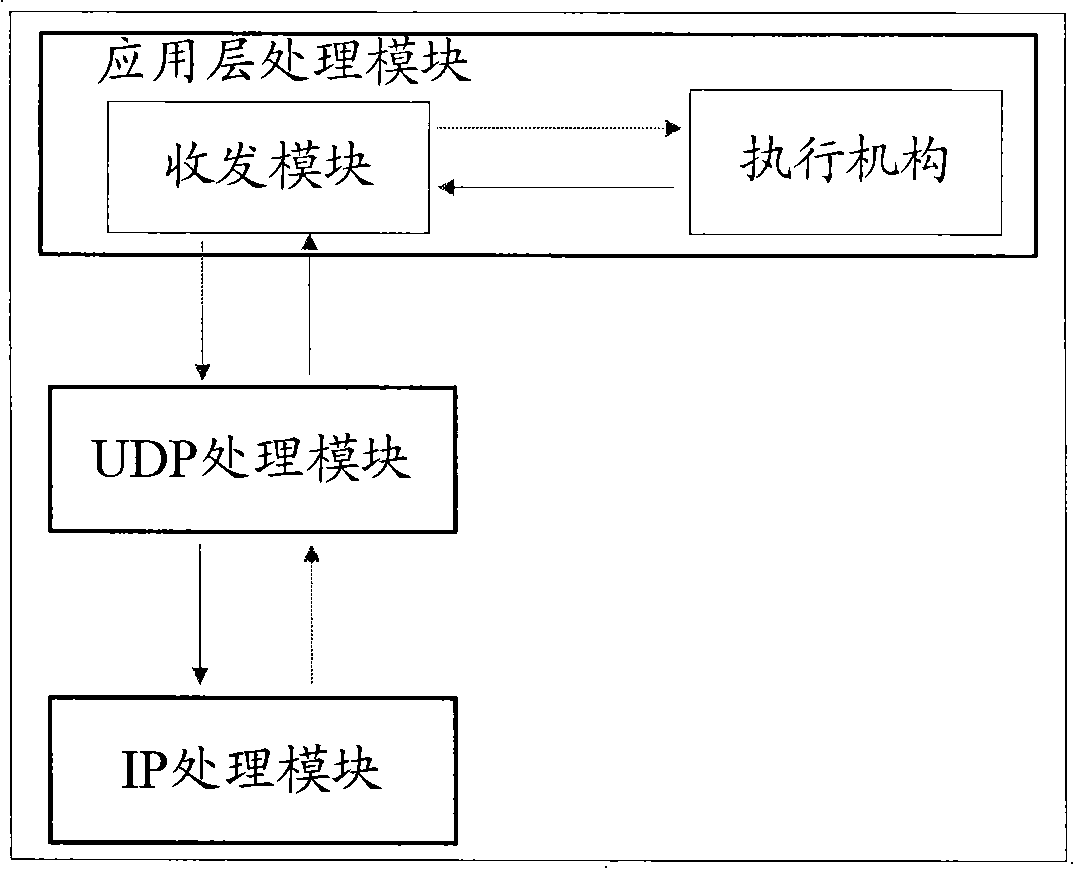

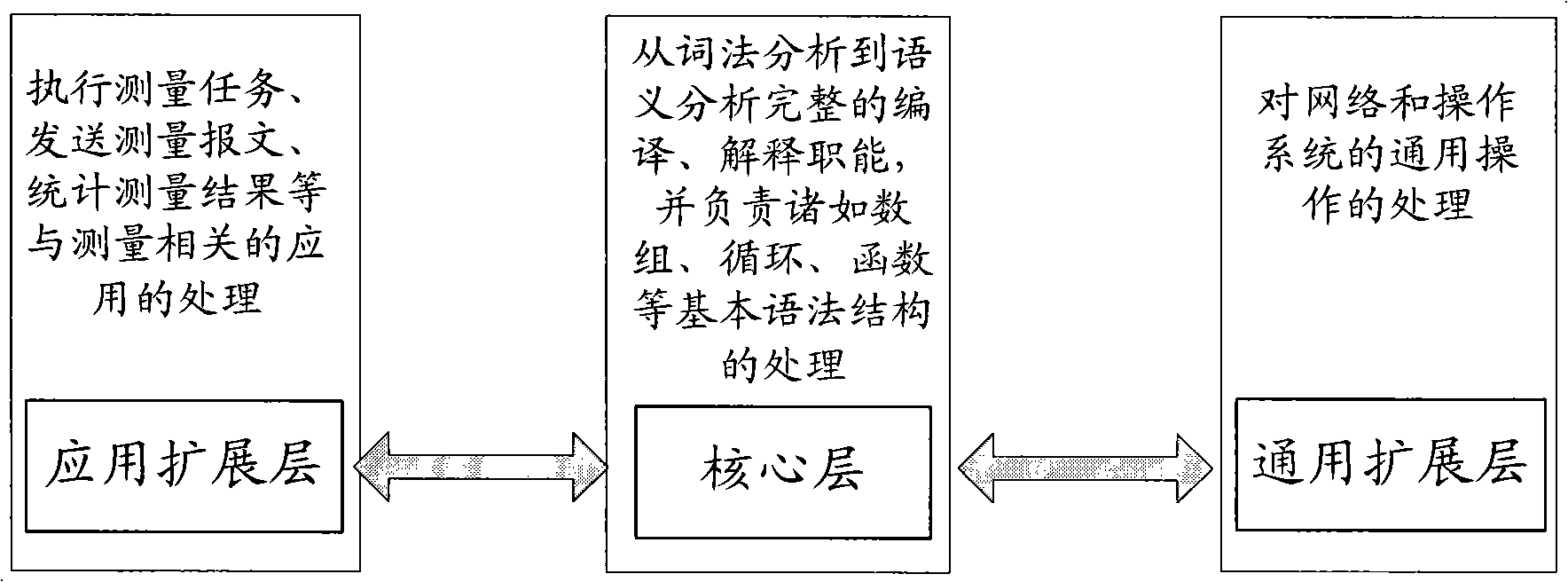

Interposition type measurement node for self-organization network and measurement method thereof

InactiveCN101304345ASolve difficult to deployFix fixityData switching networksTransient stateOperational system

The invention relates to an interventional measurement node which is used for self-organized network and comprises an application level processing module, a UDP processing module and an IP processing module. The interventional measurement node is a network node which can route and exchange data for other nodes and has measurement capability. The measurement node can process and redirect the data of other nodes, can response to the measurement request initiated by other nodes and can help to collect the constantly changeable routes or other information in network to help people to understand the transient state and the normal state of network topology. When being the intermediate node of the network, the interventional measurement node can adopt three transmission modes for data message according to IP elective contents: direct forwarding, copy forwarding and process forwarding, thus causing the intermediate node to receive the message. The interventional measurement node uses the executive mechanism of the application level processing module to execute measurement tasks and acquire the support of the network / an operating system and collects network performance information of the intermediate node, then the network performance information is added to the message to be transmitted to a destination node, so the interventional measurement of the self-organized network is completed.

Owner:BEIJING UNIV OF POSTS & TELECOMM

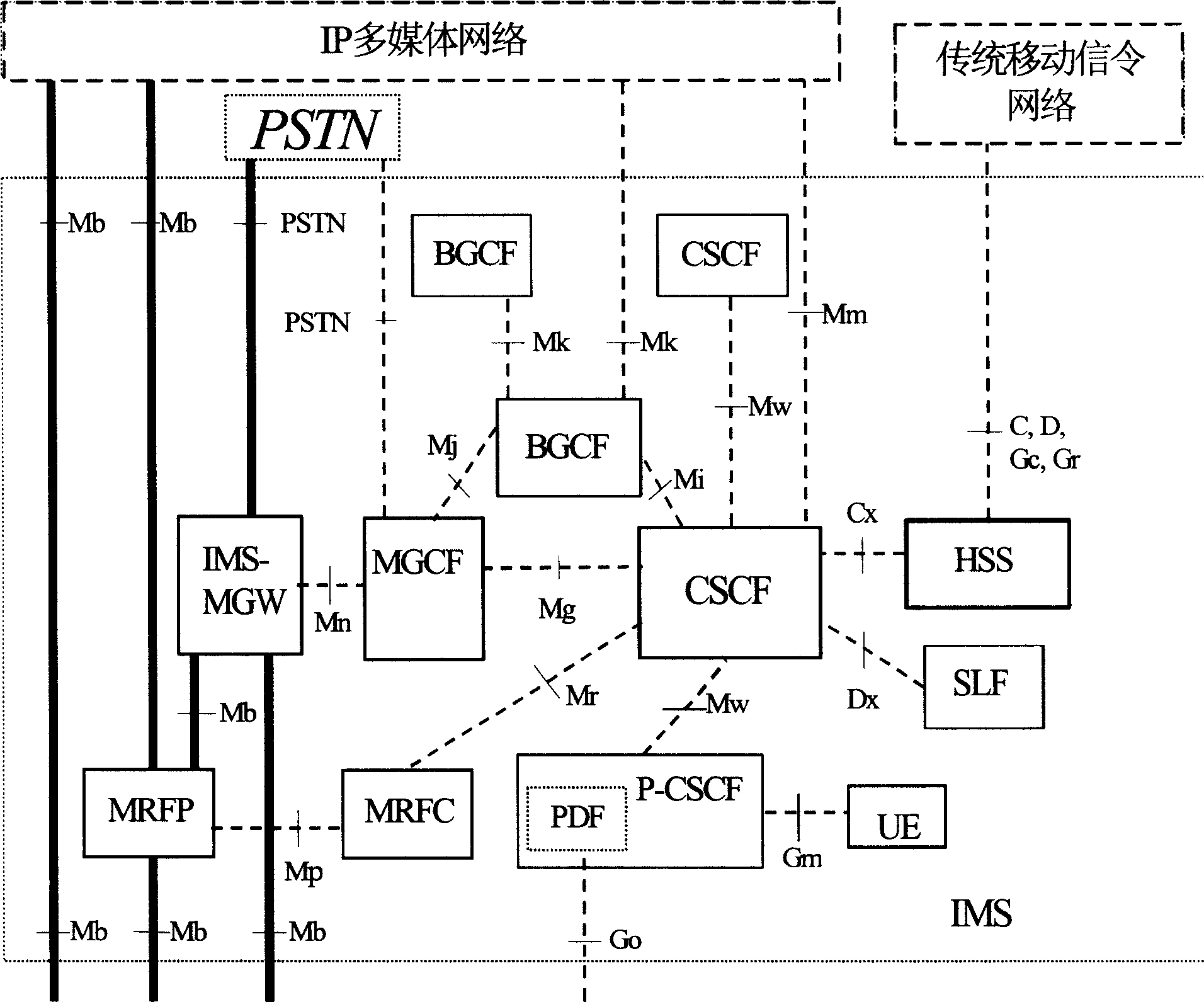

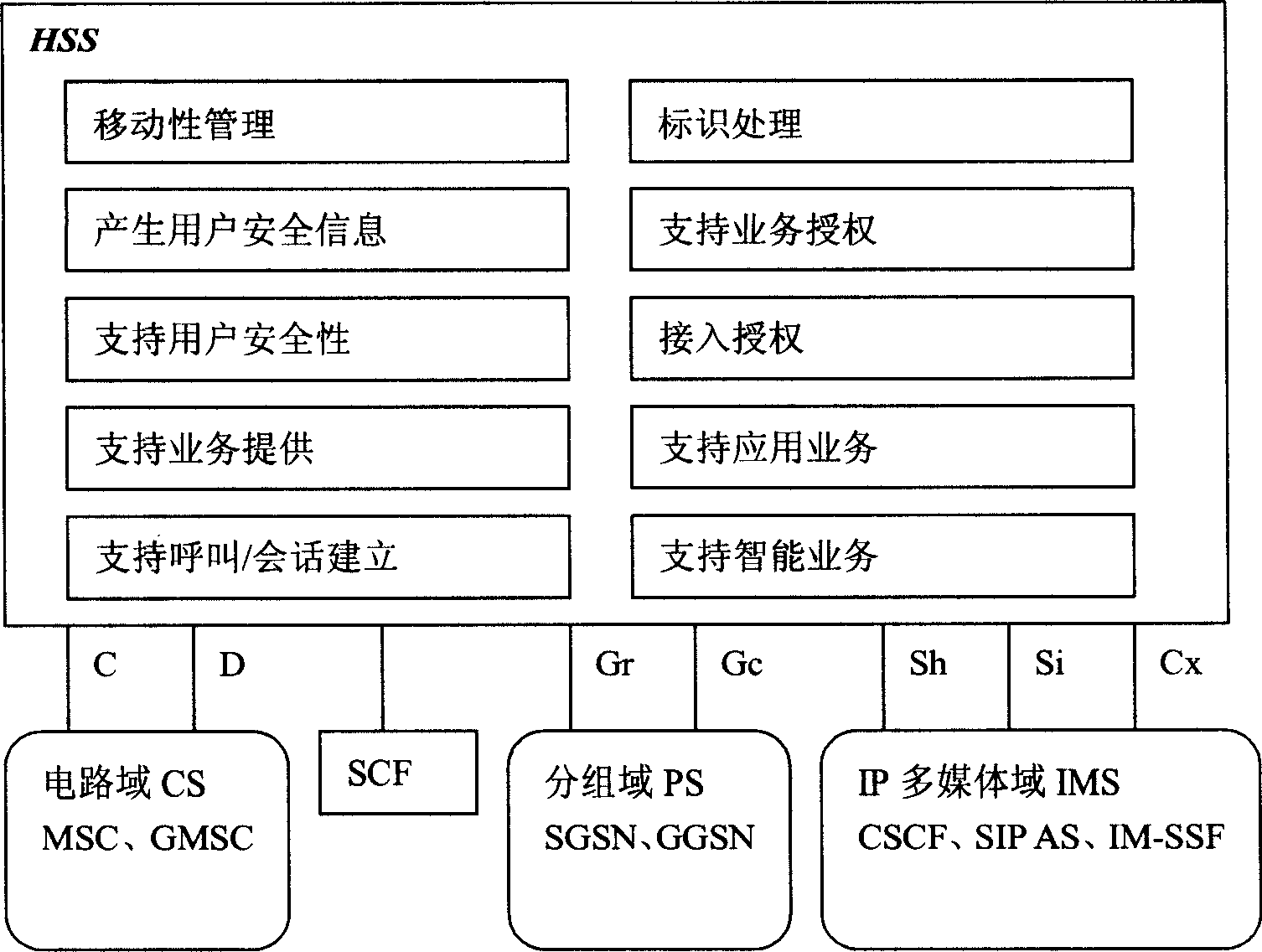

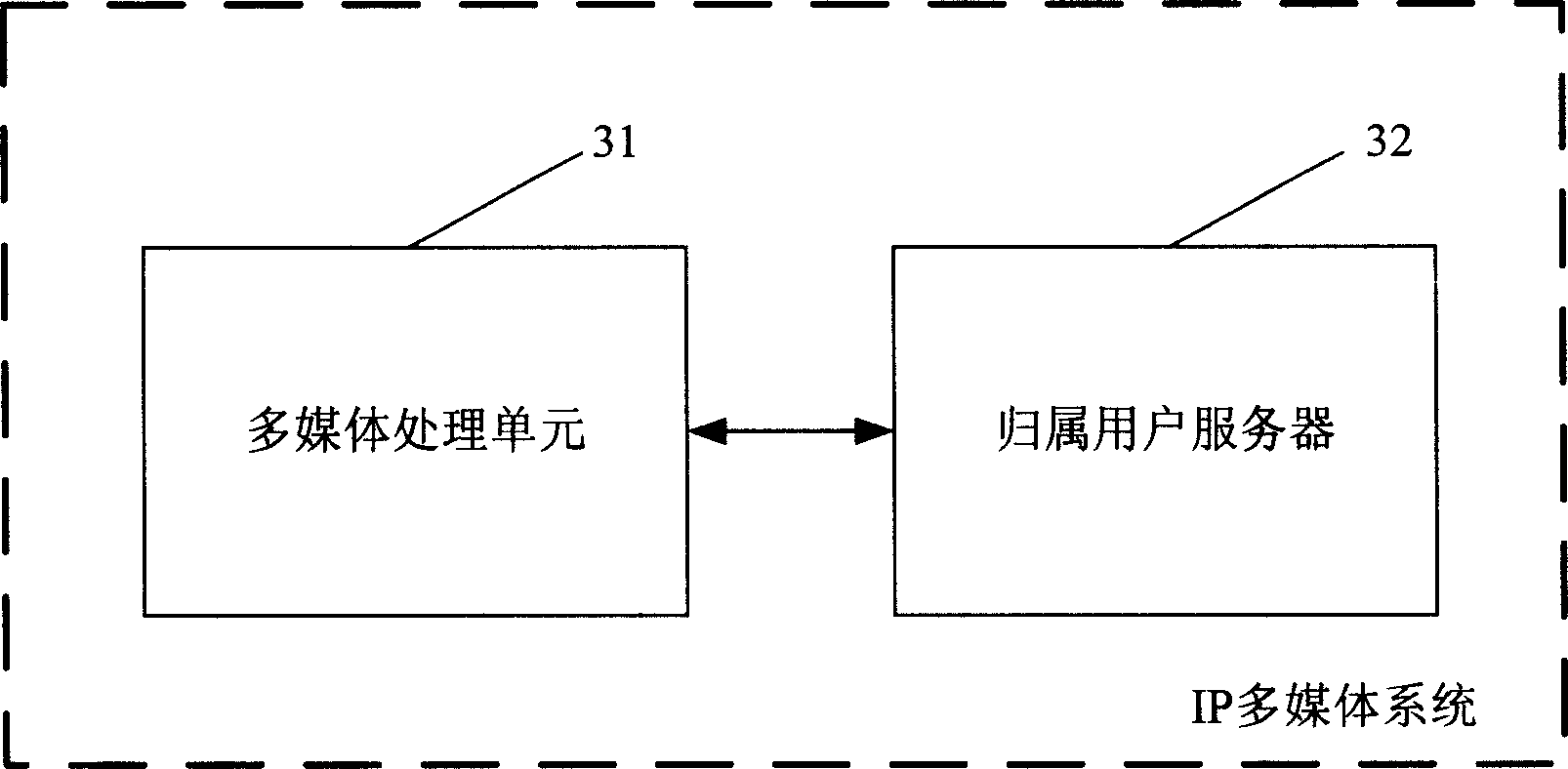

Multimedia system

This invention discloses an IP multimedia system including an IP multimedia process unit for processing user network acc control, call / session control and service process, an attribute user server being a functional entity independent of load networks including IP process interface relating to said IP multimedia process unit used to record related user and service information needed by the multimedia process unit and support the IP system functions to match with the IP unit to finish the network acc control, call / session control and service process of users. The HSS in IMS of this invention only includes IMS function and the non-IMS function is not included, which can provide general IMS to access different load networks.

Owner:HUAWEI TECH CO LTD

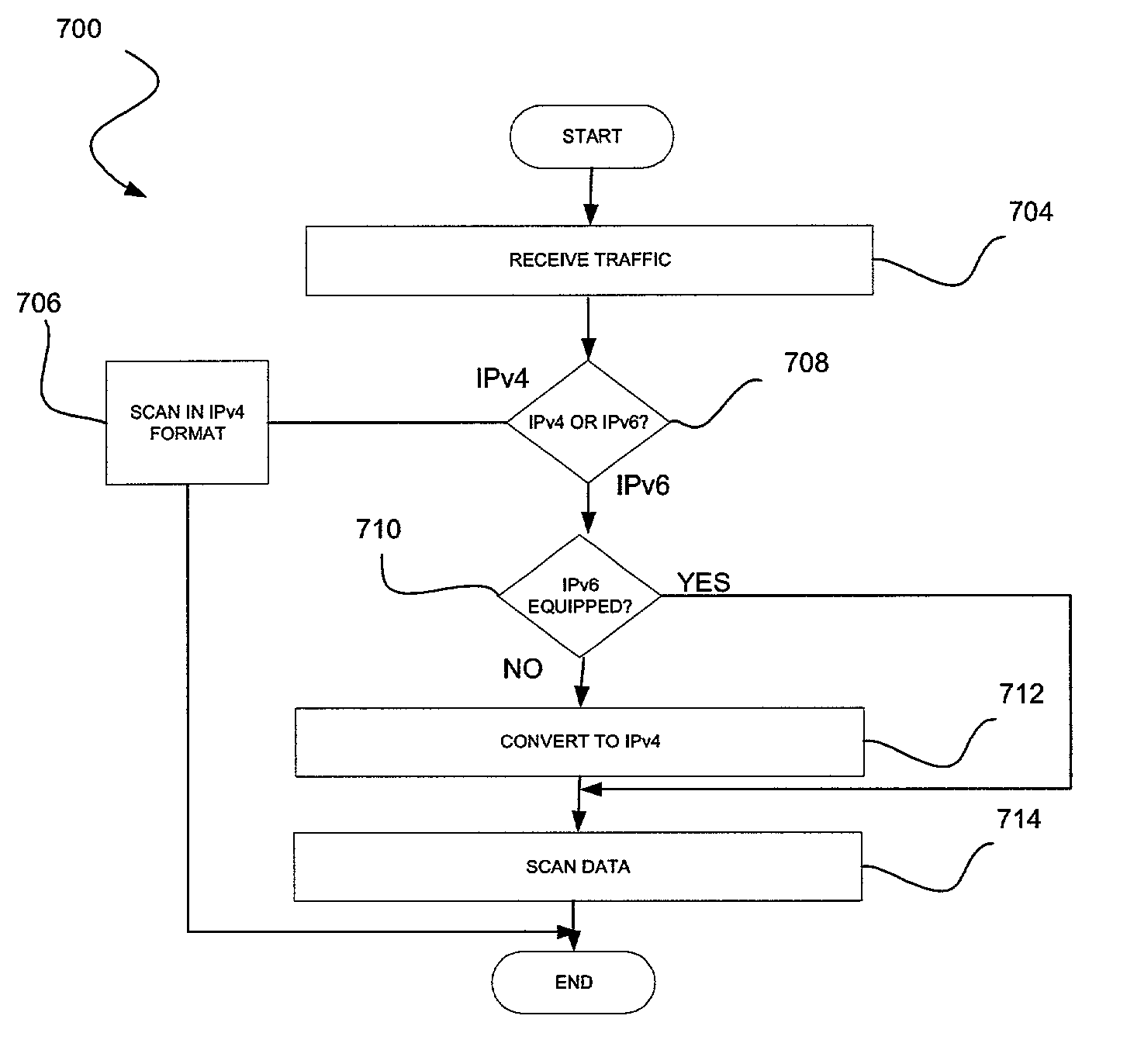

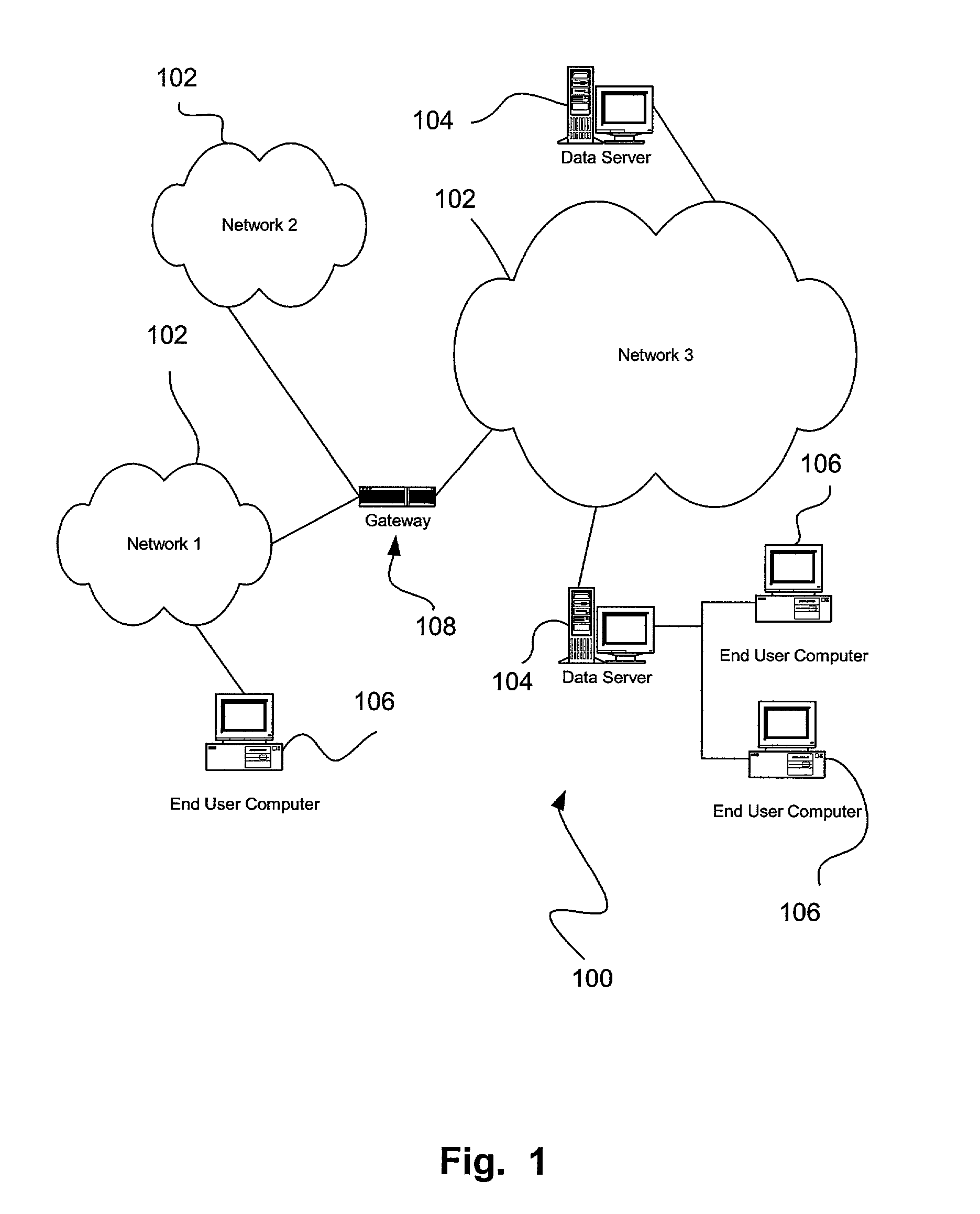

System and method for facilitating IPv6 protocol usage by an application program

A system, method and computer program product are provided for translating between Internet Protocols (IP's). Initially, data is received over the Internet utilizing a first IP. Such data is adapted for being processed by an application program. Next, it is determined whether the application program can process data received over the Internet utilizing the first IP. If it is determined that the application program can not process data received over the Internet utilizing the first IP, the data is converted from the first IP to a second IP that the application program is capable of processing.

Owner:MCAFEE LLC

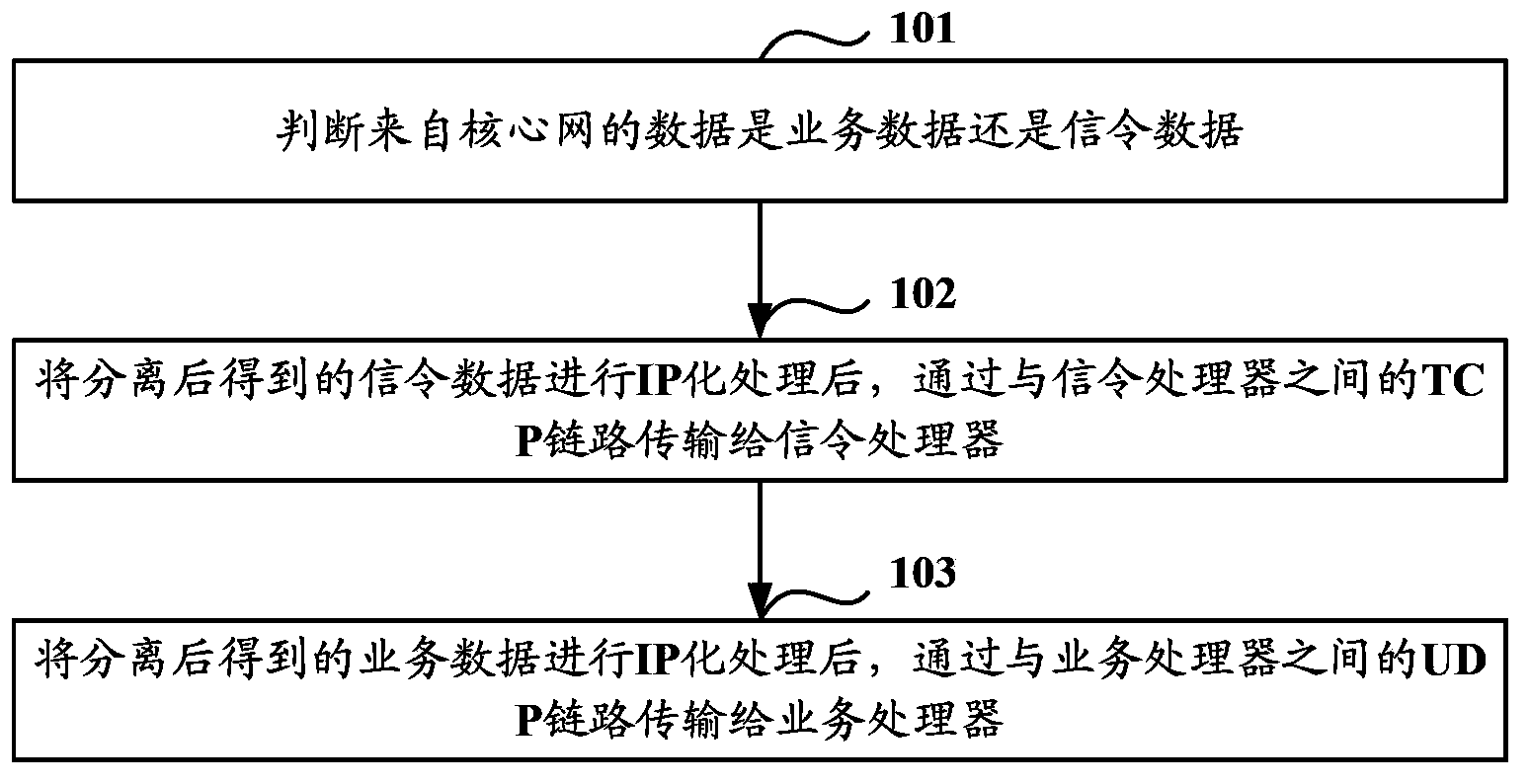

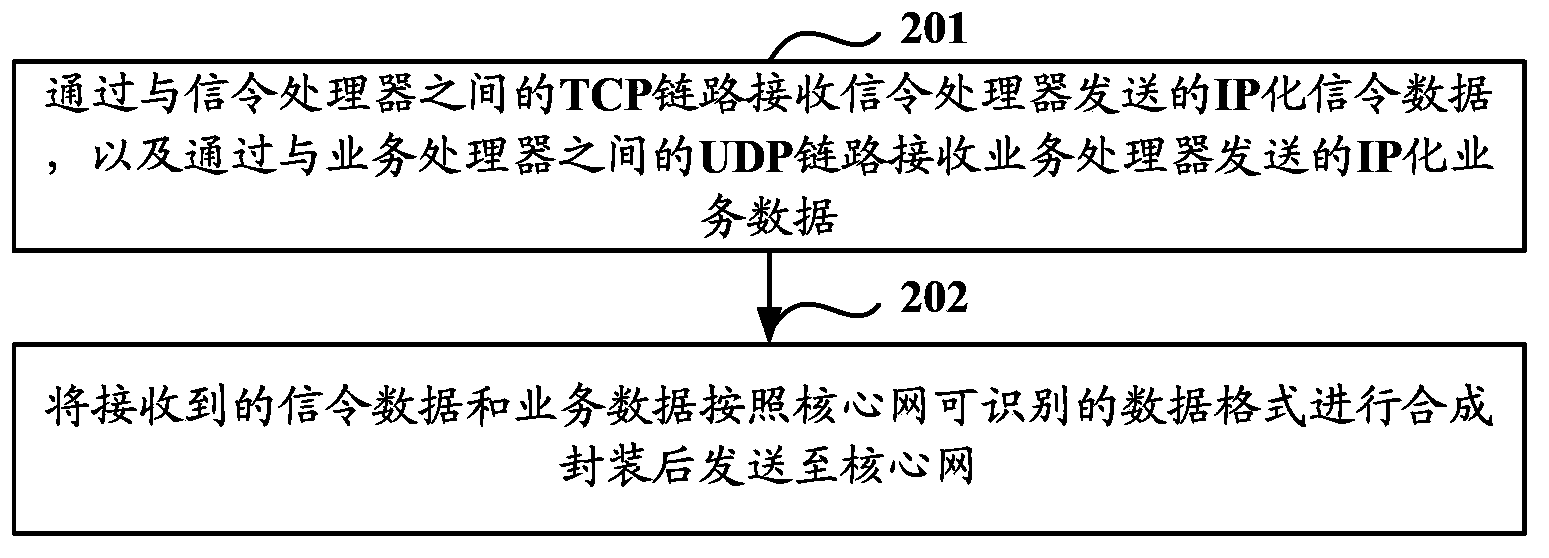

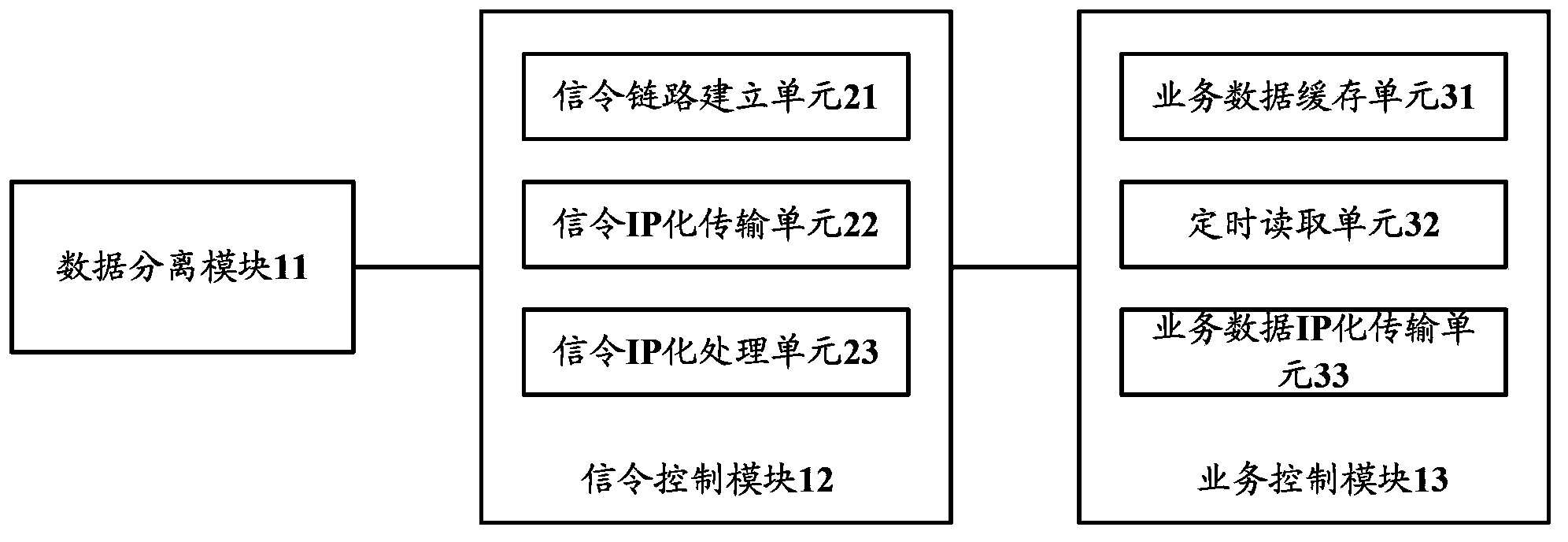

Data transmission method and device

InactiveCN103581138ASolve problems where there is a mismatchNetwork traffic/resource managementWireless network protocolsIp processingData transmission circuit

The invention discloses a data transmission method and device. The data transmission method and device are characterized in that received data are separated into signaling data and service data, IP processing is carried out on the separation signaling data, then the signaling data are transmitted to a signaling processor through a TCP link between the data transmission device and the signaling processor, IP processing is carried out on the separation service data, then the service data are transmitted to a service processor through a UDP line between the data transmission device and the service processor, and therefore the problem that in the prior art, the IP data transmission technology used in a base station is not matched with the data transmission technology supported by the core network is solved.

Owner:COMBA TELECOM SYST CHINA LTD

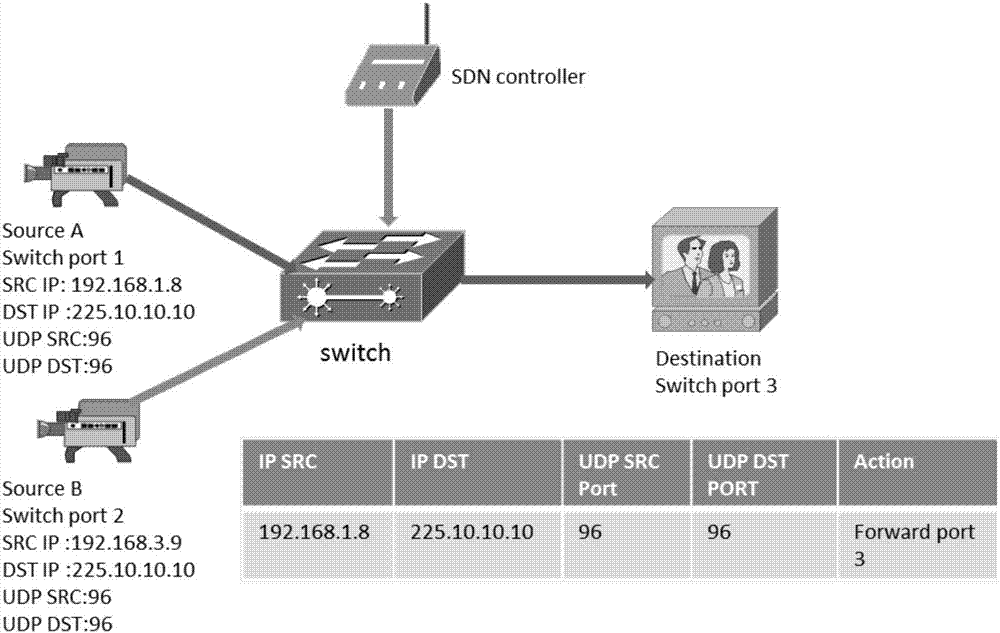

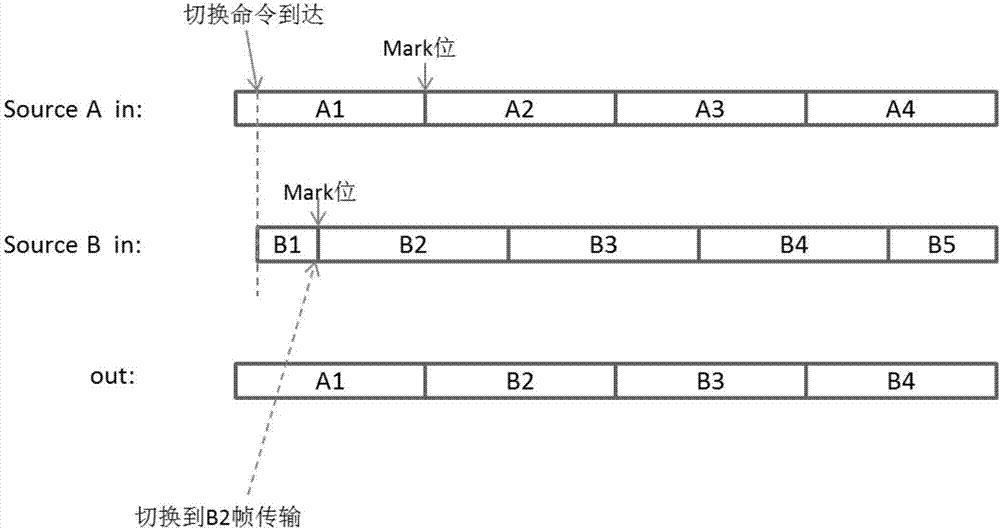

SDN switch based video precise switching method

The invention discloses an SDN (Software Defined Network) based video precise switching method. The SDN based video precise switching method comprises the steps of controlling video stream switching through a flow table sent by the SDN; and caching video streams and finishing precise switching by the switch. By adoption of the technical scheme, precise video switching (precise switching) of the video stream based on the switch is realized based on the SDN in an IP processing process of the media video production.

Owner:COMMUNICATION UNIVERSITY OF CHINA

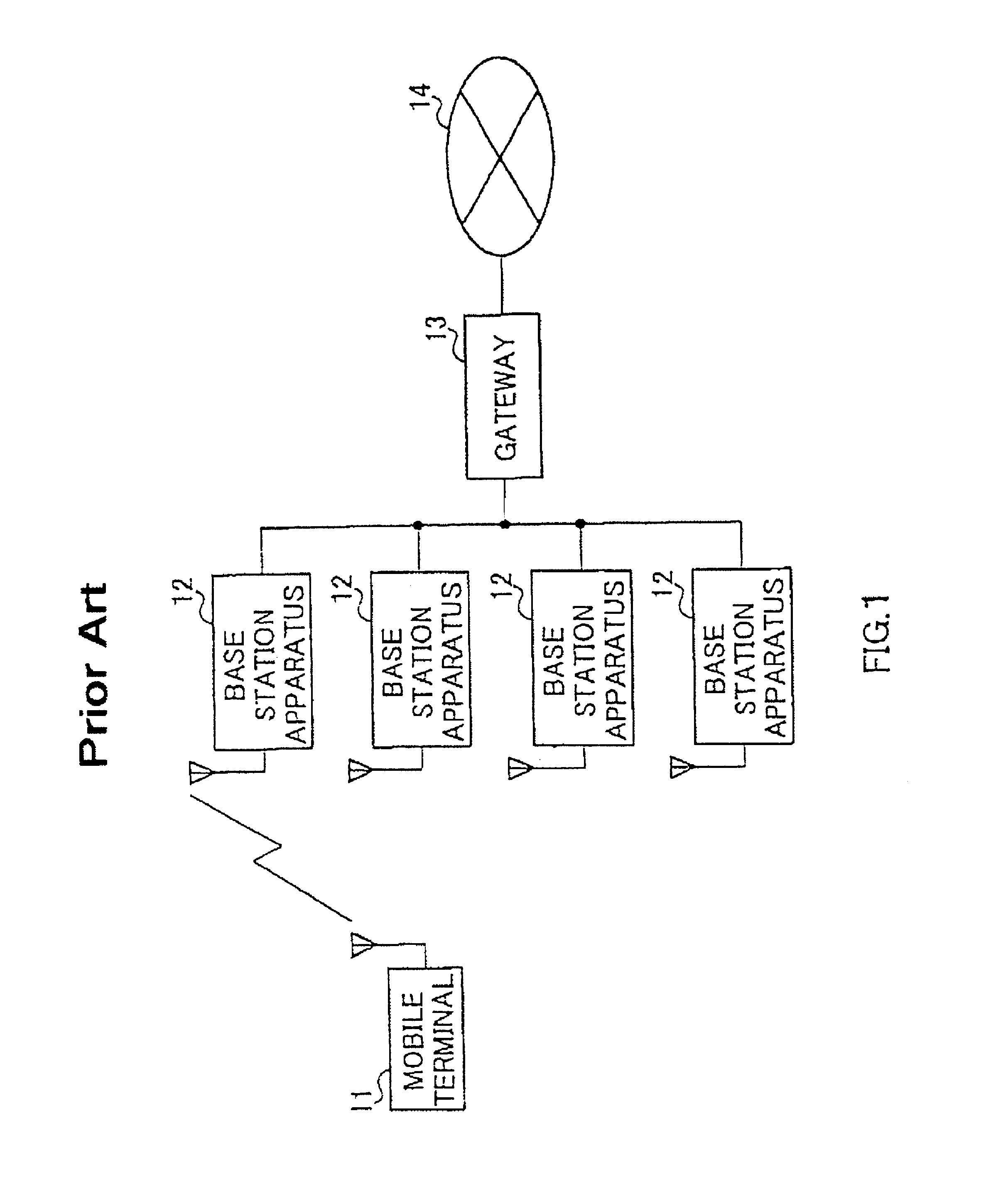

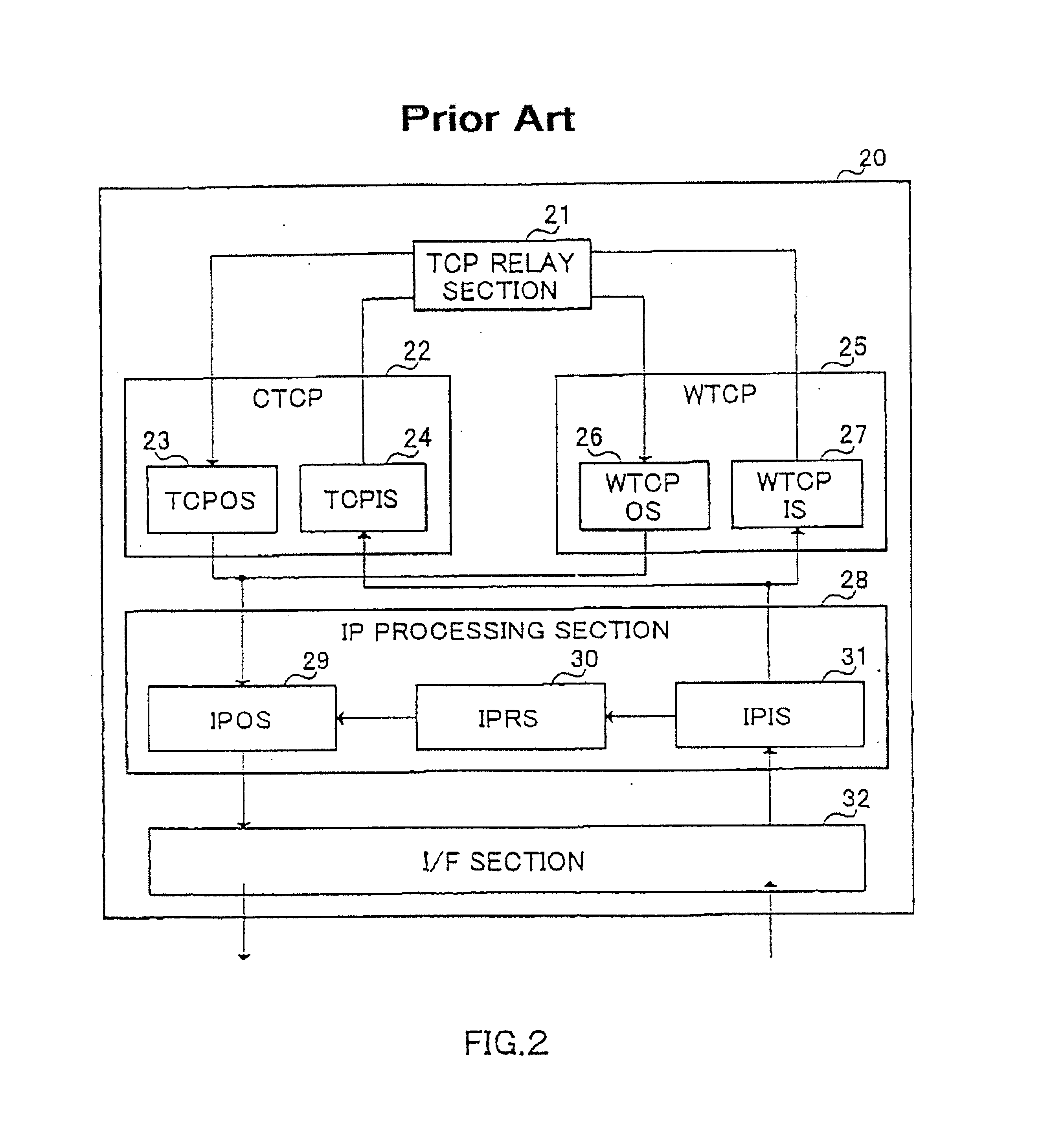

Base station apparatus, mobile terminal apparatus and wireless access system using the apparatuses

InactiveUS7209480B2Eliminate overheadImprove throughputNetwork traffic/resource managementTime-division multiplexApplication serverIp processing

A base station serves as a relay node between a mobile terminal and an application server on a backbone network. The base receives a radio packet from the mobile terminal through a wireless I / F section, and transfers the radio packet to a IP processing section, a TCP input section and a protocol relay section successively in this order. At this point, with respect to the packet, the IP header is processed and then removed in the IP processing section, the TCP header is processed and then removed in a TCP processing section, and the data is transferred to a protocol relay section along with the TCP segment information described in both headers. The protocol relay section has a conversion table, and performs proxy processing based on the table.

Owner:PANASONIC CORP

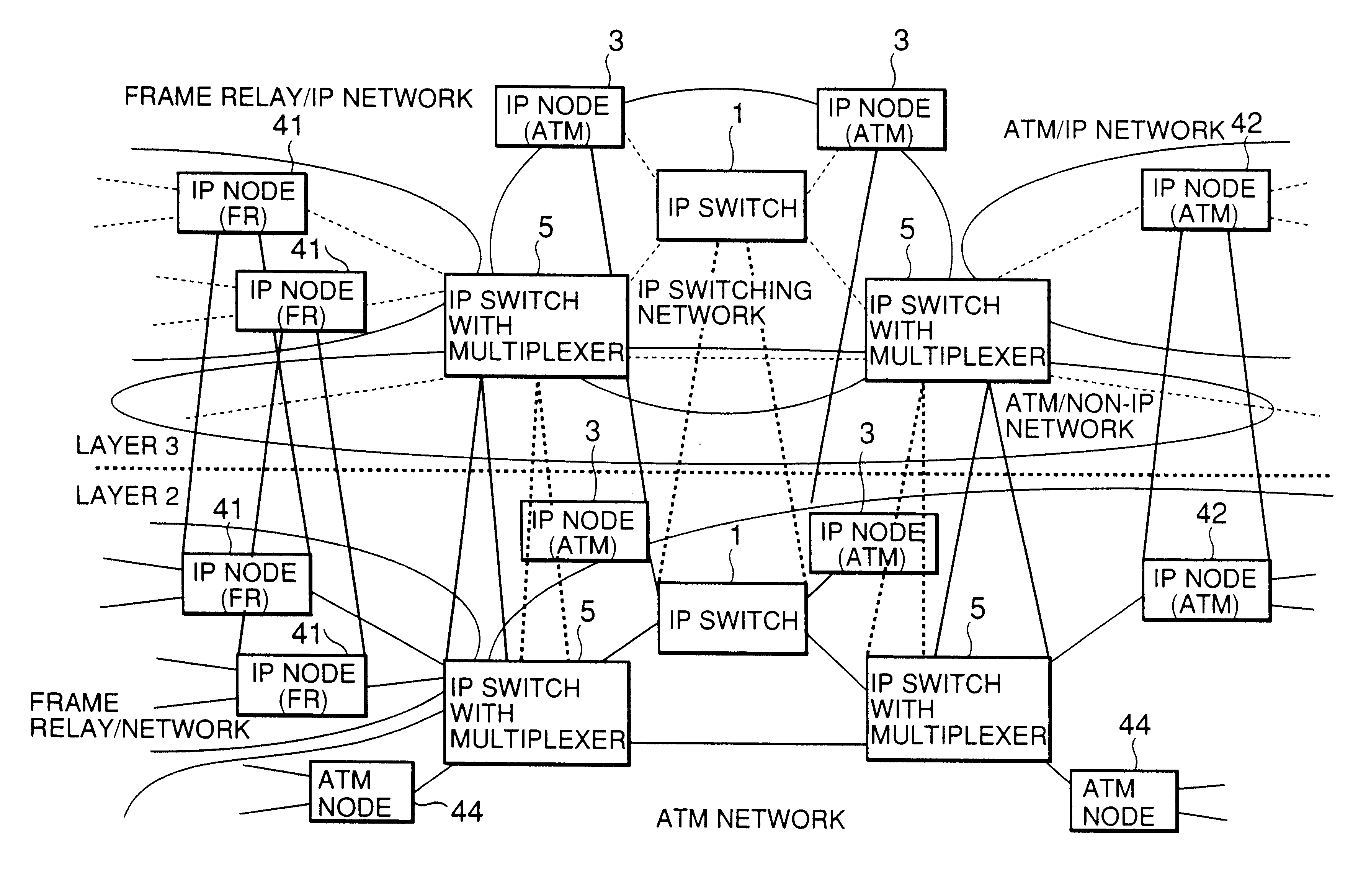

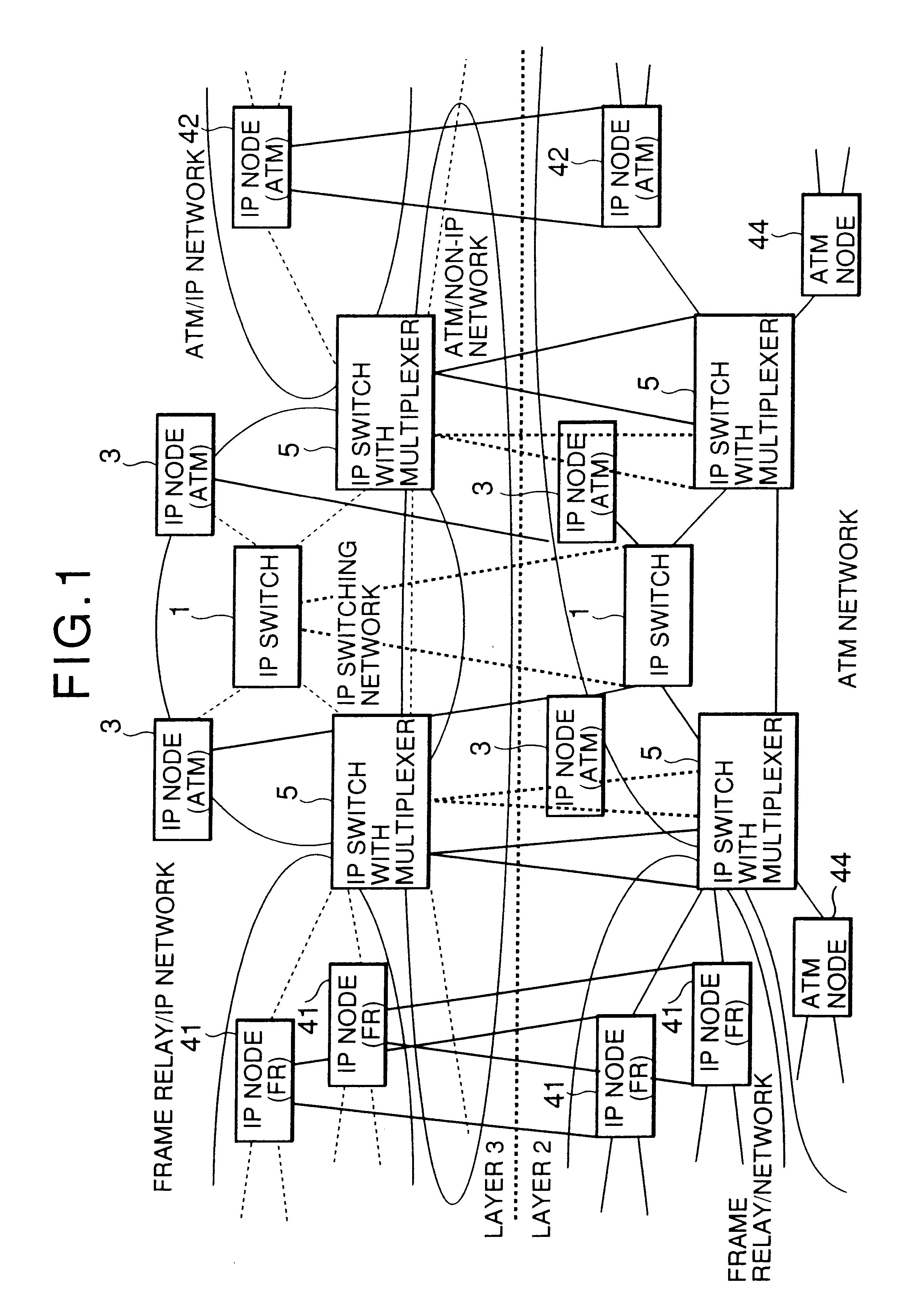

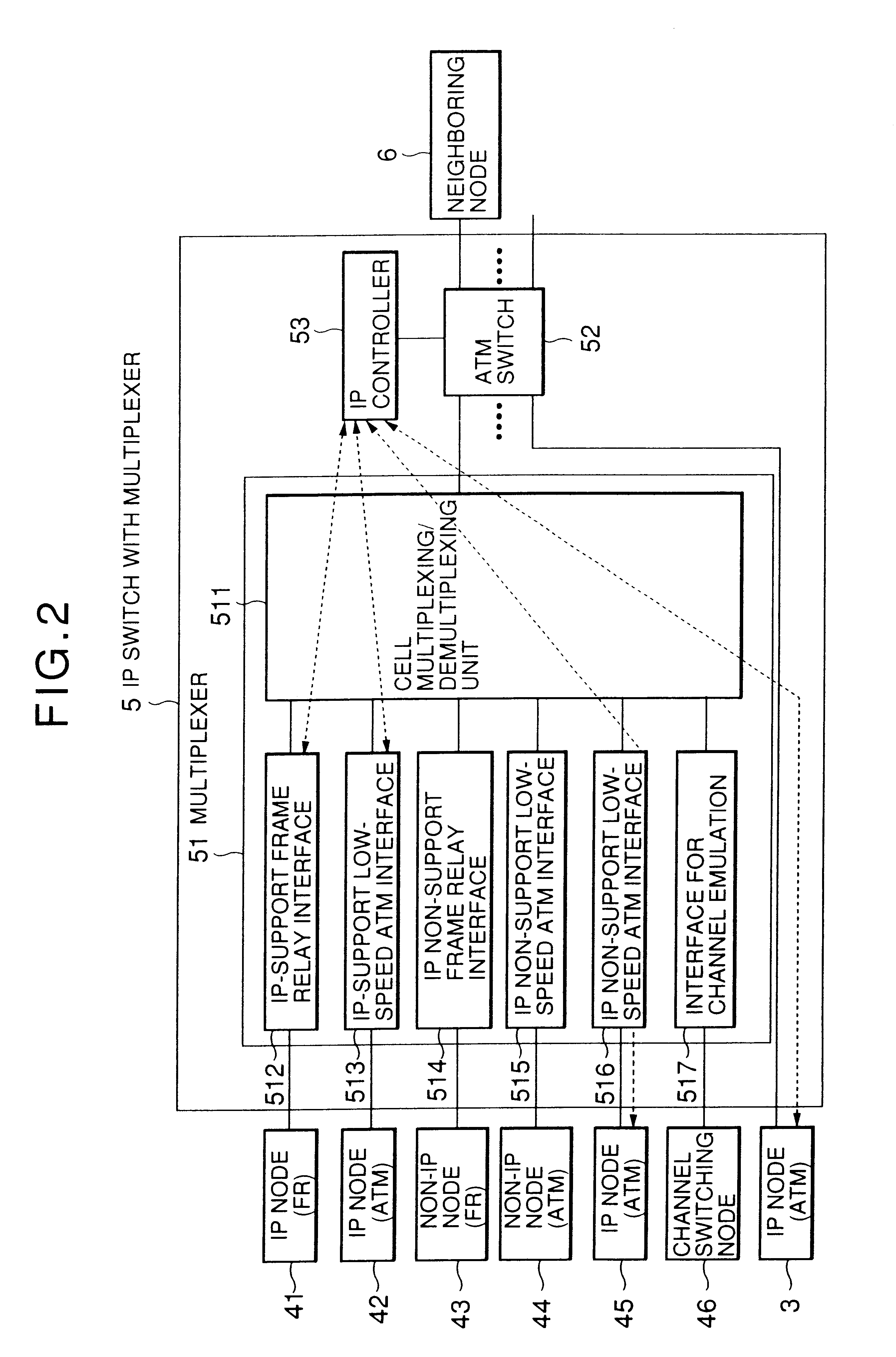

Router apparatus using ATM switch

InactiveUS6980553B2Increase diversityReduce variationTime-division multiplexData switching by path configurationMultiplexingComputer network

A router apparatus 5 is provided with an ATM switch, an IP controller for performing routing control as a controller for layer 3, plural kinds of interfaces which are individually provided to plural transmission paths in which various communications are performed, and a cell multiplexing / demultiplexing unit, and manages the cell communications between respective parts on the basis of identification information. The input packet is subjected to IP processing in an interface to be converted to a cell in a common format, and the cell is serially multiplexed with a cell from another interface on a cell basis, and transmitted to the ATM switch at the cell multiplexing / demultiplexing unit. Each interface and each cell multiplexing / demultiplexing unit sets and switches the identification information for the header portion of the packet and the cell to be communicated by using a table in which the corresponding relationship of the identification information is registered.

Owner:HITACHI LTD

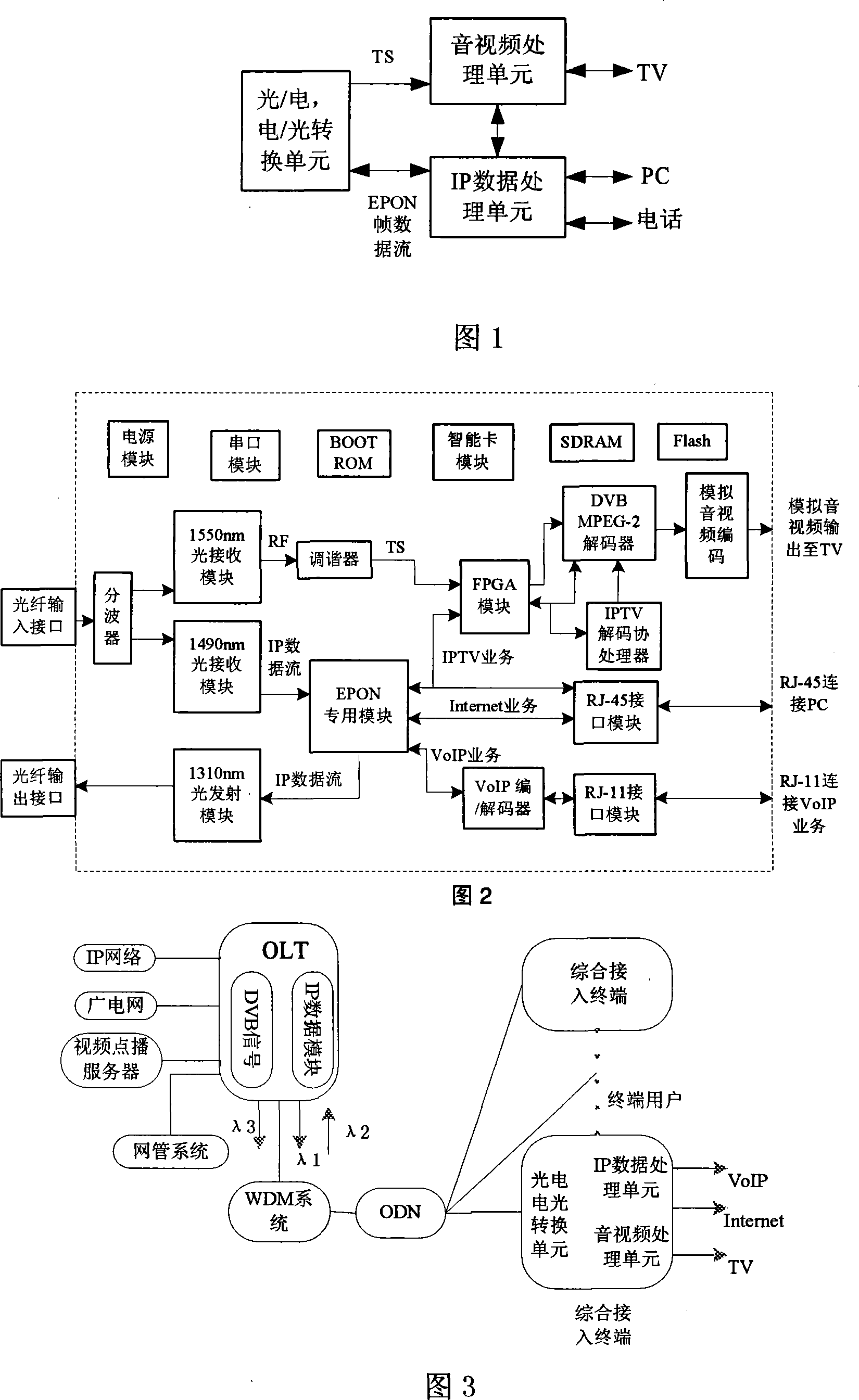

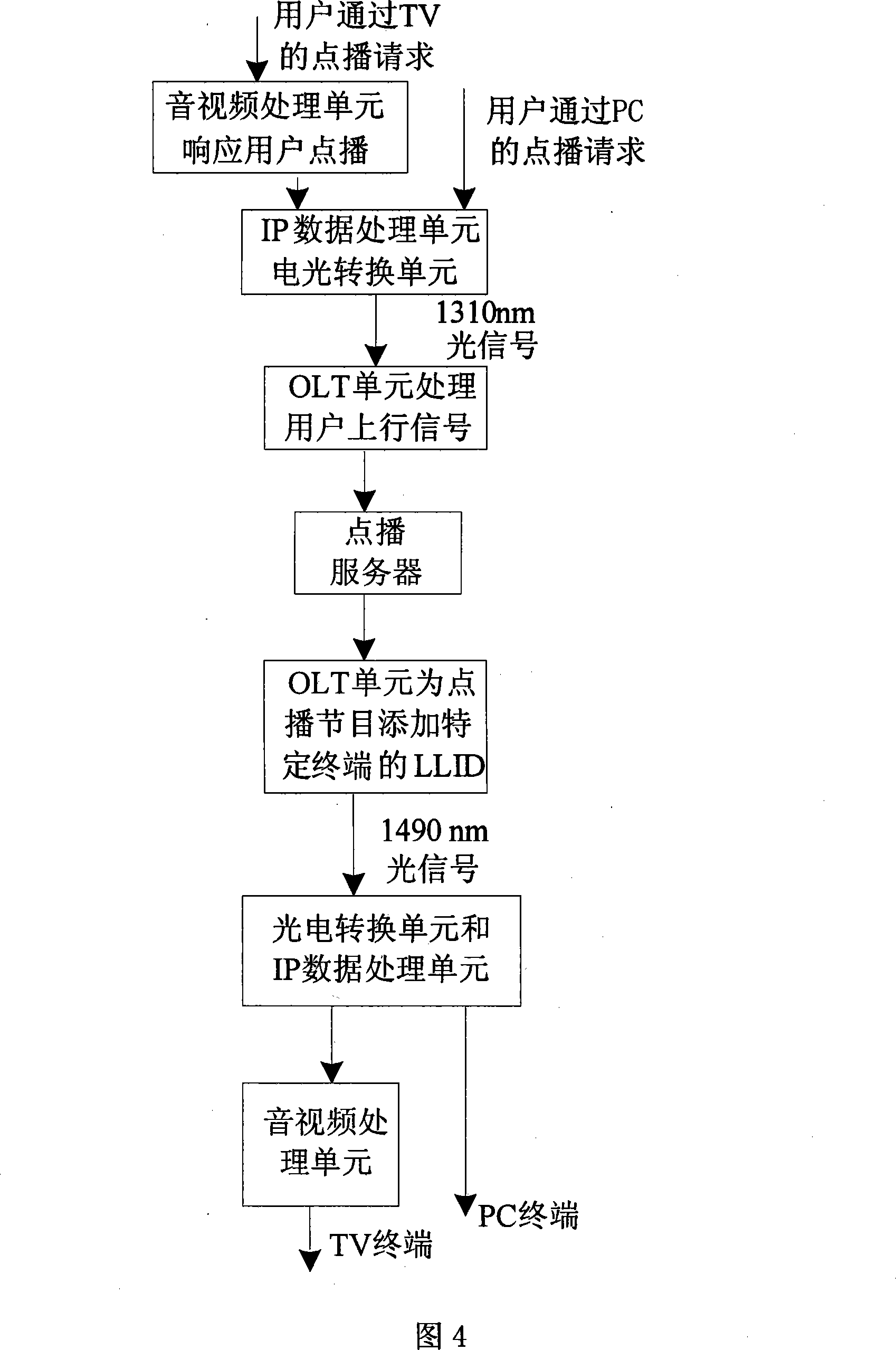

An integrated access terminal under FTTH condition

InactiveCN101242461AInformativeRealize multi-service integrationPulse modulation television signal transmissionTelephonic communicationFiberTerminal system

The present invention provides an integrated access terminal under the condition of Fiber To The Home (FTTH). The terminal mainly includes a photoelectric conversion unit, an audiovideo signal processing unit and an IP processing unit three main function units, completing the integrated access of video, audio, data services. Digital television service of DVB standard and IP service based on the EPON protocol are loaded on two wavelengths utilizing WDM technology, completing the signal transmission utilizing another three wavelengths. For audio / video businesses, the access system can support DVB, IPTY service modes and two display terminals of television and individual computer, substantial utilizing respective advantages of the DVN, IPTV service video and advantages of television and individual computer as display terminal. In addition, the access terminal system also can complete Internet service and VoIP service access by EPON transport protocols.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

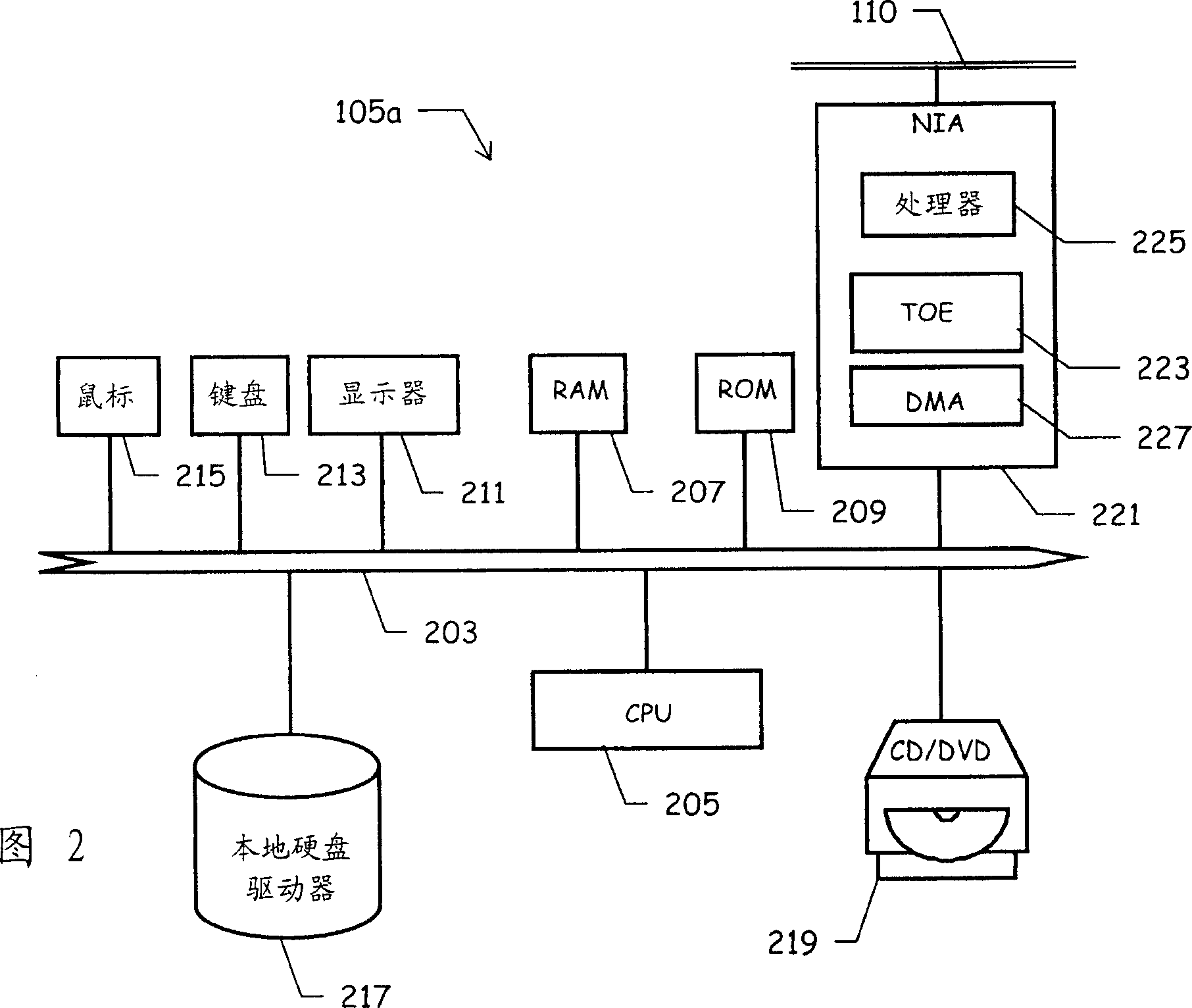

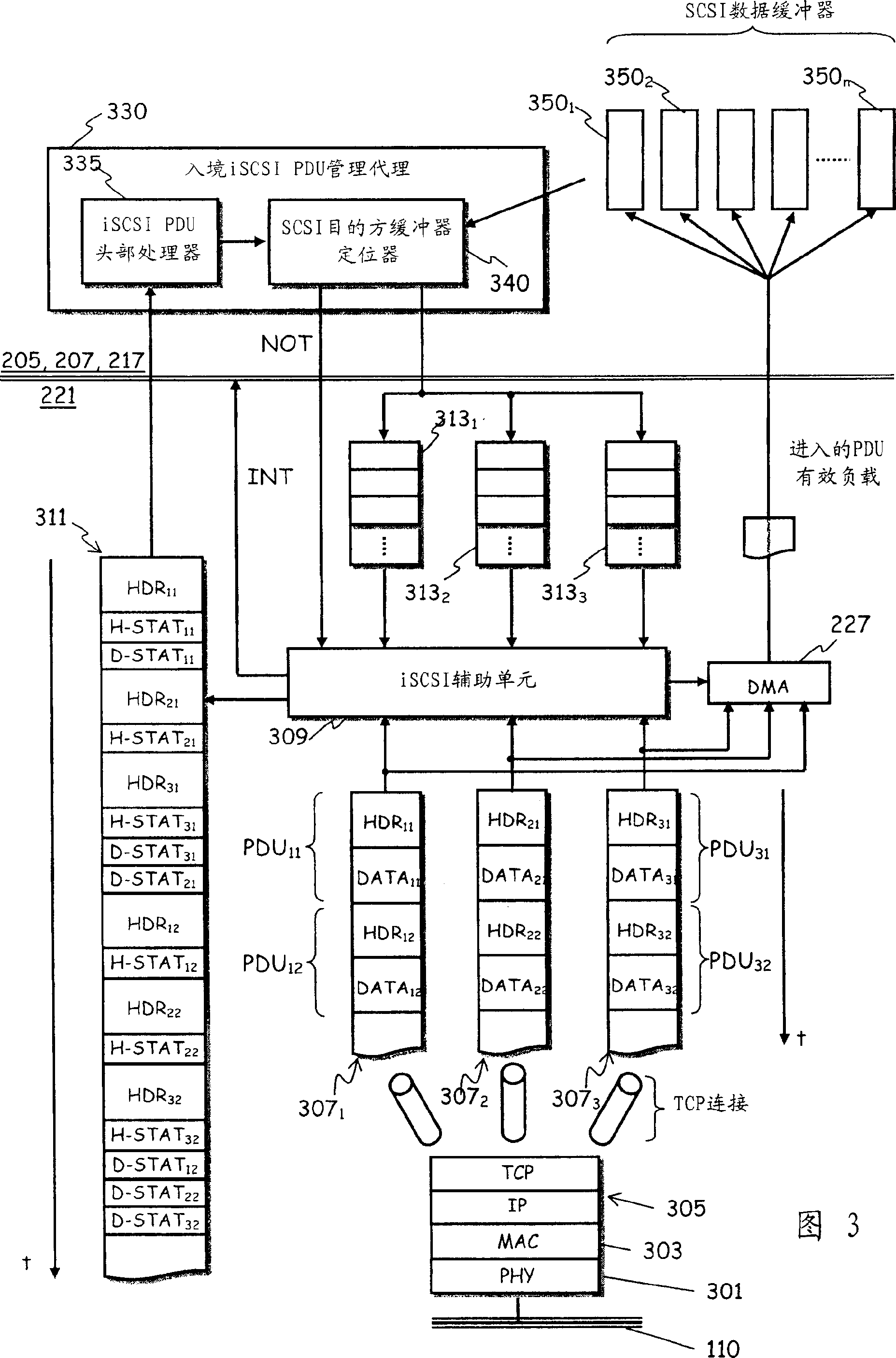

Method of offloading iscsi tcp/ip processing from a host processing unit, and related iscsi tcp/ip offload engine

InactiveCN1747444AOffload computationally heavy processingData switching networksData processing systemInformation processing

A method of offloading, from a host data processing unit ( 205 ), iSCSI TCP / IP processing of data streams coming through at least one TCP / IP connection ( 307 1 ,307 2 ,307 3), and a related iSCSI TCP / IP Offload Engine (TOE). The method including: providing a Protocol Data Unit (PDU) header queue ( 311 ) adapted to store headers (HDR11, . . . , HDR32) of iSCSI PDUs received through the at least one TCP / IP connection; monitoring the at least one TCP / IP connection for an incoming iSCSI PDU to be processed; when at least a iSCSI PDU header is received through the at least one TCP / IP connection, extracting the iSCSI PDU header from the received PDU, and placing the extracted iSCSI PDU header into the PDU header queue; looking at the PDU header queue for ascertaining the presence of iSCSI PDUs to be processed, and processing the incoming iSCSI PDU based on information in the extracted iSCSU PDU header retrieved from the PDU header queue.

Owner:INT BUSINESS MASCH CORP

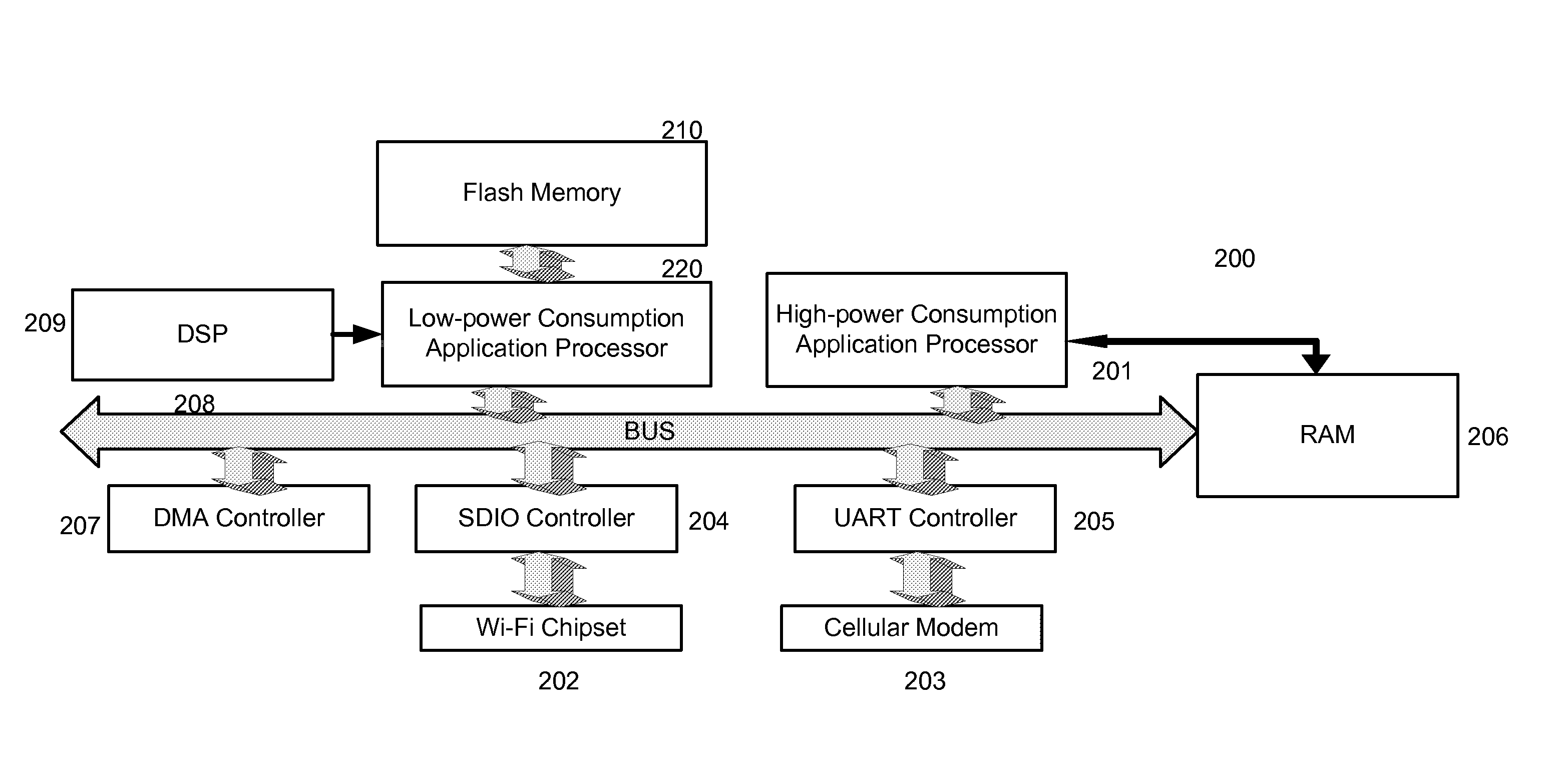

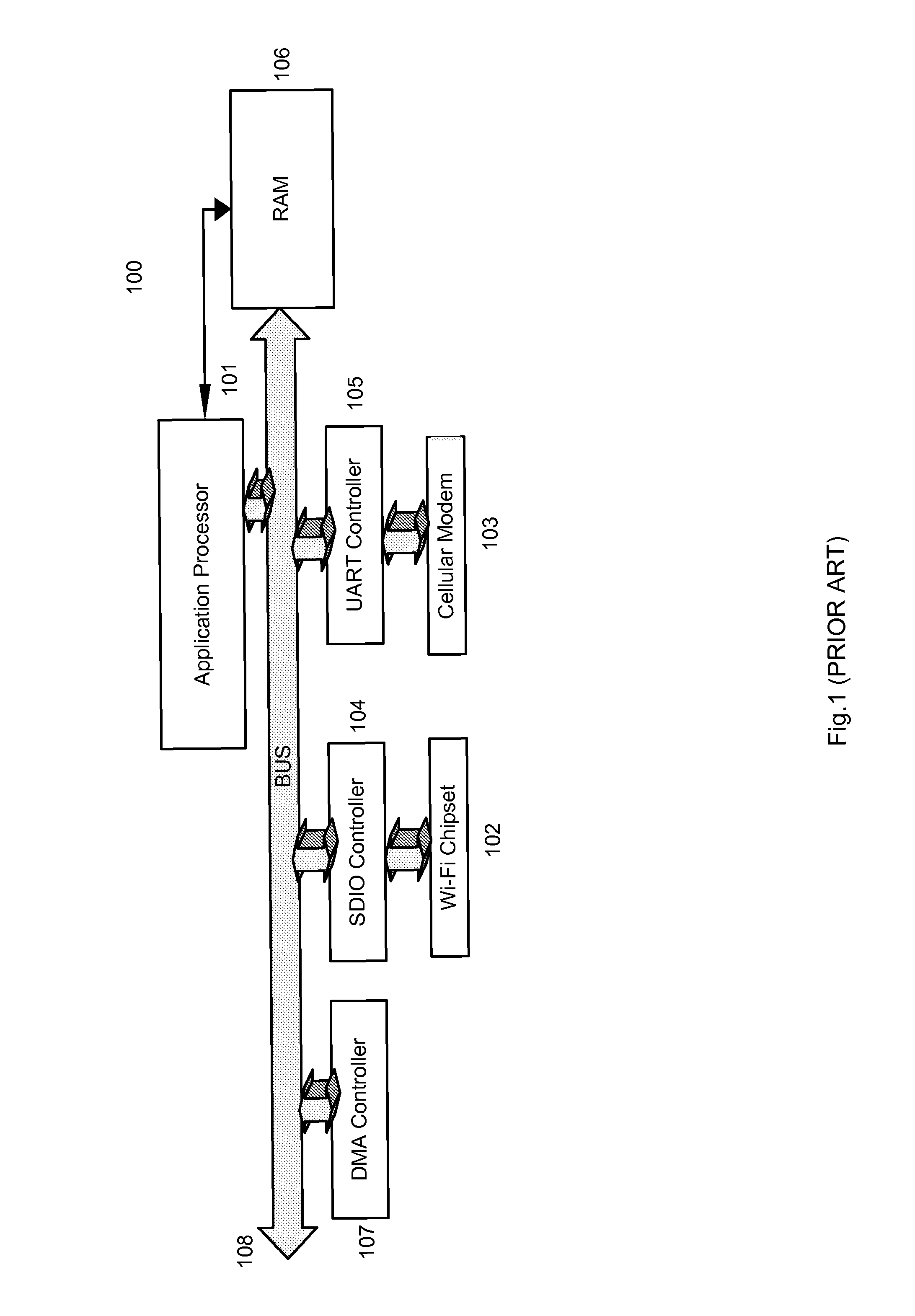

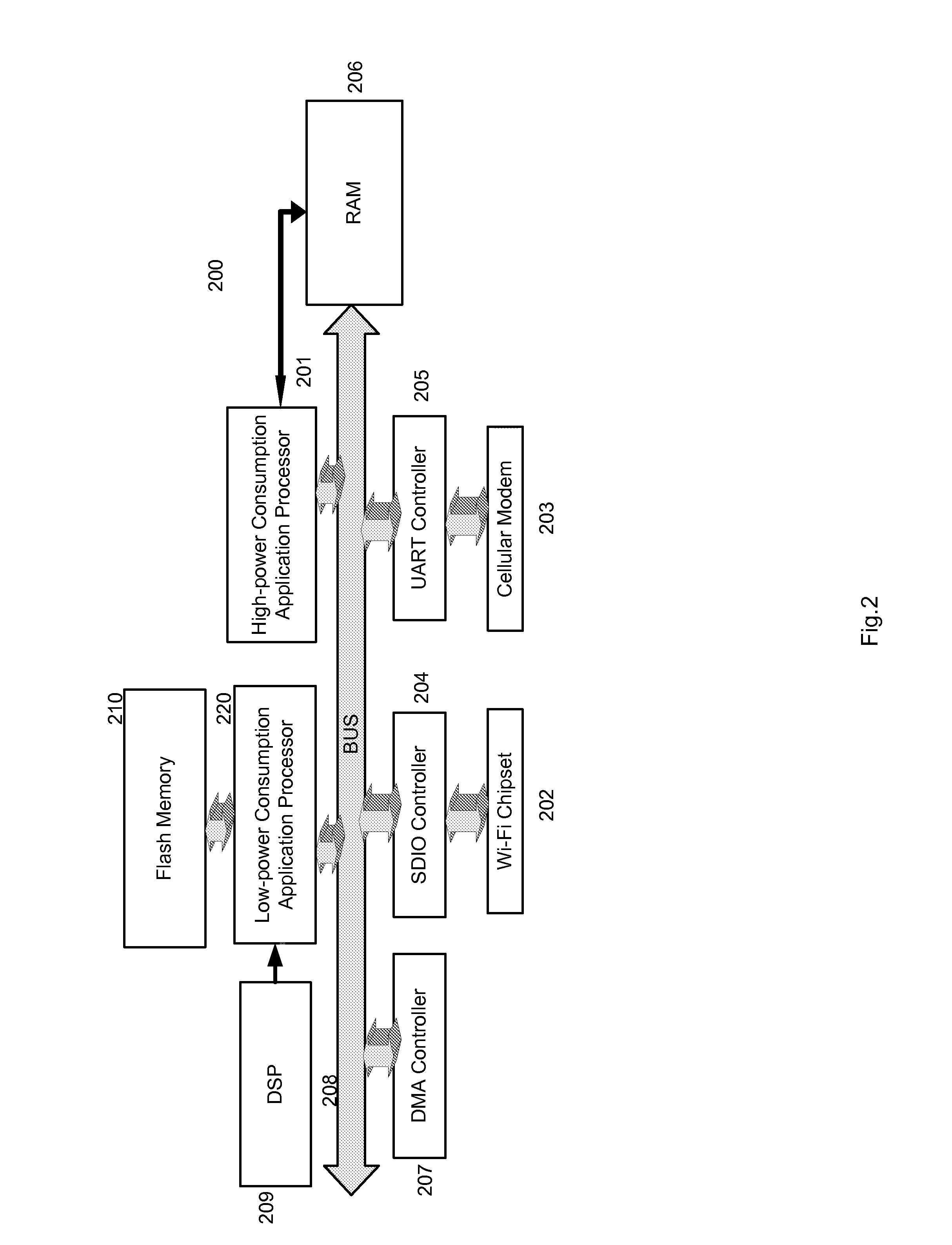

Method and apparatus for reducing power consumption in a multimode terminal when performing IP communications

An apparatus for reducing power consumption in an IP (Internet Protocol) communications device. The apparatus may include a high-power consumption main application processor and a low-power consumption application processor to share processor functions. The high-power consumption application processor may carry out functions related to the user interface of the device, signaling and control path. The low-power consumption application processor may implement IP processing, voice signal processing and video signal processing.

Owner:MARVELL ASIA PTE LTD

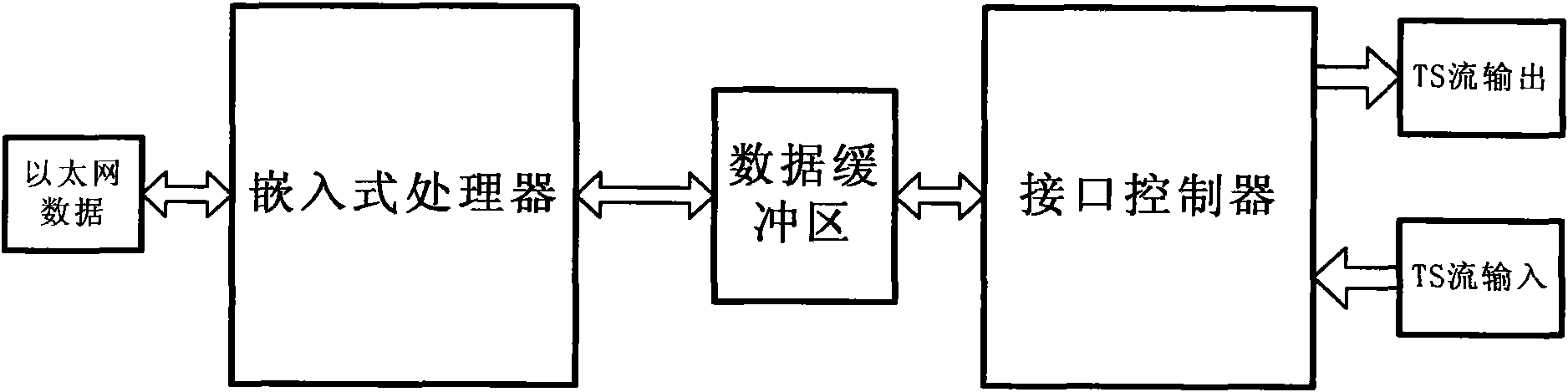

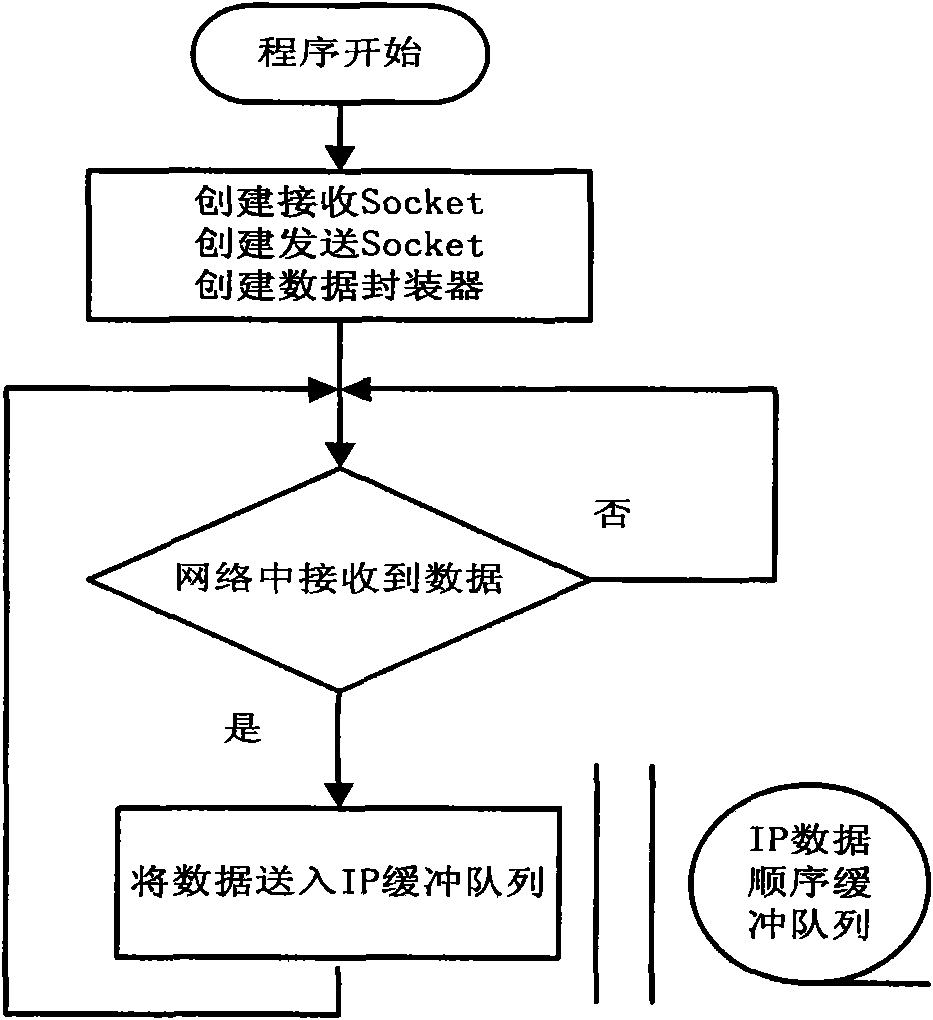

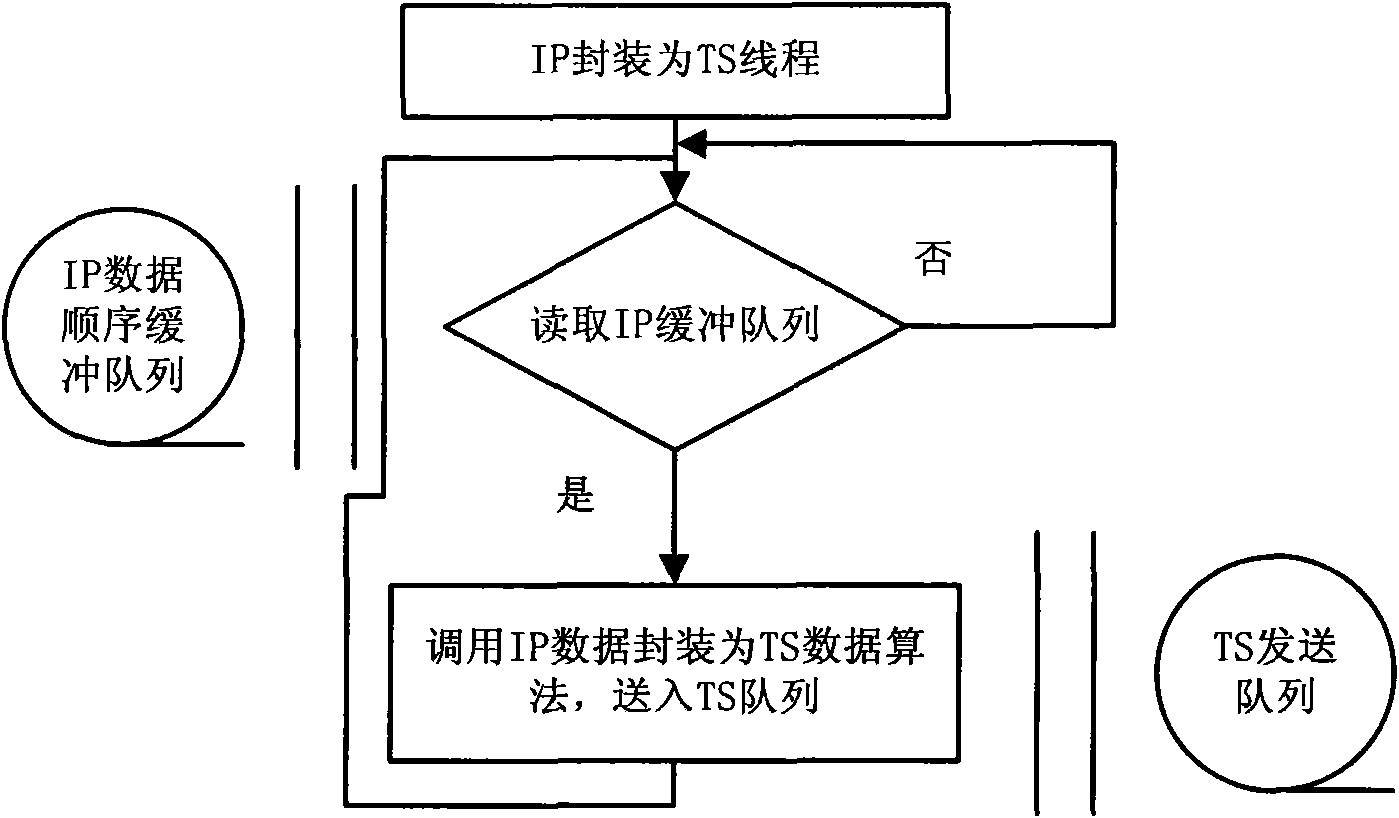

Gateway realization method for converting Ethernet data and digital video streaming

InactiveCN101610407AObvious advantageGood effectPulse modulation television signal transmissionNetwork connectionsDigital videoIp address

The invention provides a gateway realization method for converting Ethernet data and digital video streaming. The method comprises the following steps: format of network data and format of television video streaming data are mutually converted, namely, interconversion between IP packet and MPEG-2 TS streaming; an embedded processor adopts combination of double buffering configuration and single buffering configuration and configures a boot operation script so that the two configurations are converted from one to another; the double buffering configuration evens flow rate at an IP processing layer and processes each buffer area by a plurality of threads; the single buffering configuration adopts a mode of data buffering under a driving procedure state; an upper layer application program of an embedded system adopts a self-adaptive adjacency list method to automatically acquire the adjacency list in respective network segment and send the adjacency list to an opposite terminal to be converted; IP packet packaging thread and TS unlocking thread realize interconversion from IP format to TS format; and TS receiving thread and TS sending thread execute a complete reverse function in the embedded system. The two sides of wireless equipment can use IP address of the same net segment or the different network segments to work and realize long-distance bidirectional transmission or long-distance unidirectional transmission.

Owner:BEIJING UNIV OF CHEM TECH

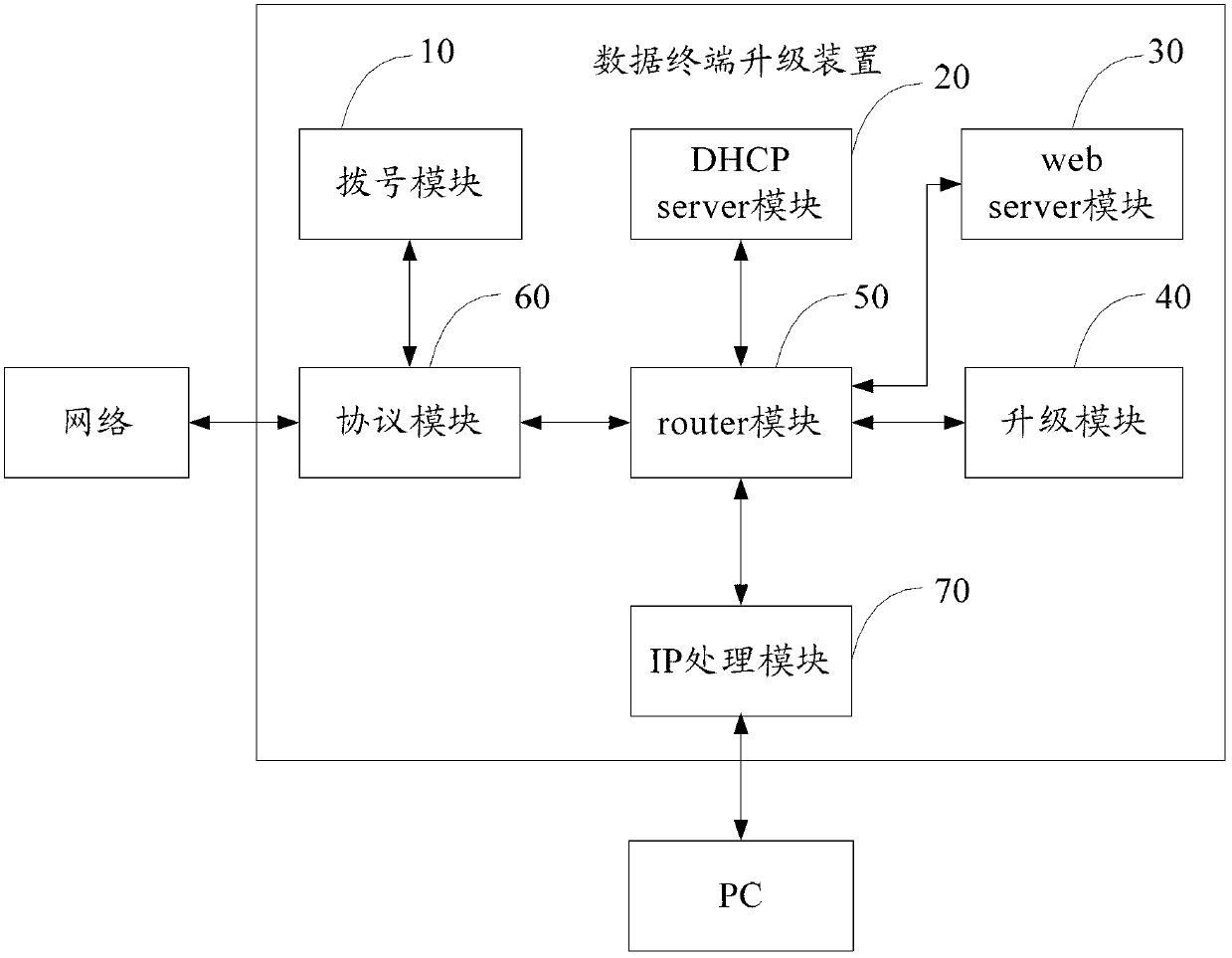

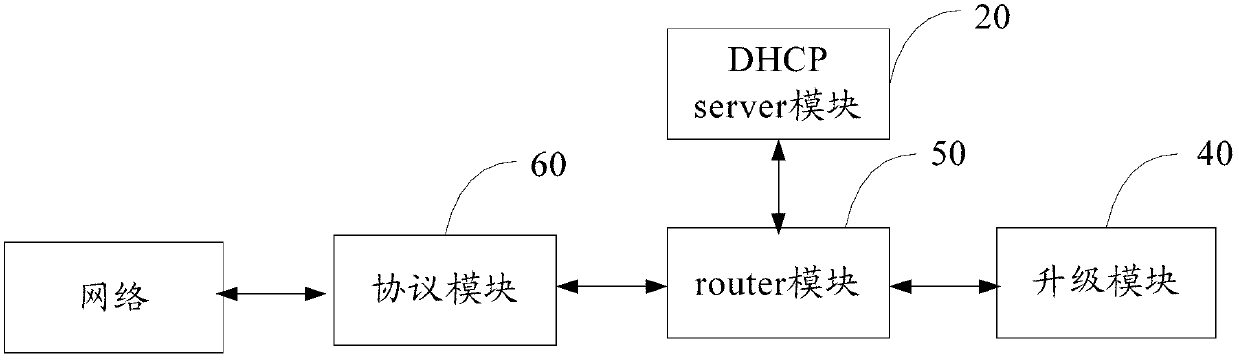

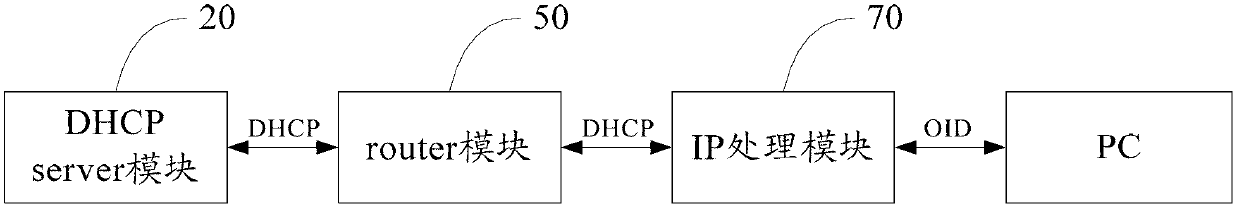

Data terminal upgrading device and method

ActiveCN103220330AReduce correlationRealize the drive-free functionSoftware engineeringProgram loading/initiatingData terminalPrivate IP

The invention relates to a data terminal upgrading device and method. The device comprises a dialing module, a protocol module, a dynamic host configuration protocol (DHCP) server module, a router module, an IP processing module, an upgrading module and a web server module. The dialing module is used for completing dialing procedures, the upgrading module obtains private IP addresses from the DHCP server module, request message for detecting whether a new version exists or not is sent to a version server through the router module and the protocol module, and if the request message exists, the new version is downloaded from the version server, the new version is written into a flash of a data terminal, and the data terminal automatically starts up to complete upgrading. The data terminal upgrading device and method enables an upgrading process, a web server visiting process and a PC net playing process of the data terminal under a win8 operating system to be independent, reduces correlation between a data terminal upgrading process and a PC operation system, and further achieves a driving-free function through Microsoft win8 logo identification.

Owner:ZTE CORP

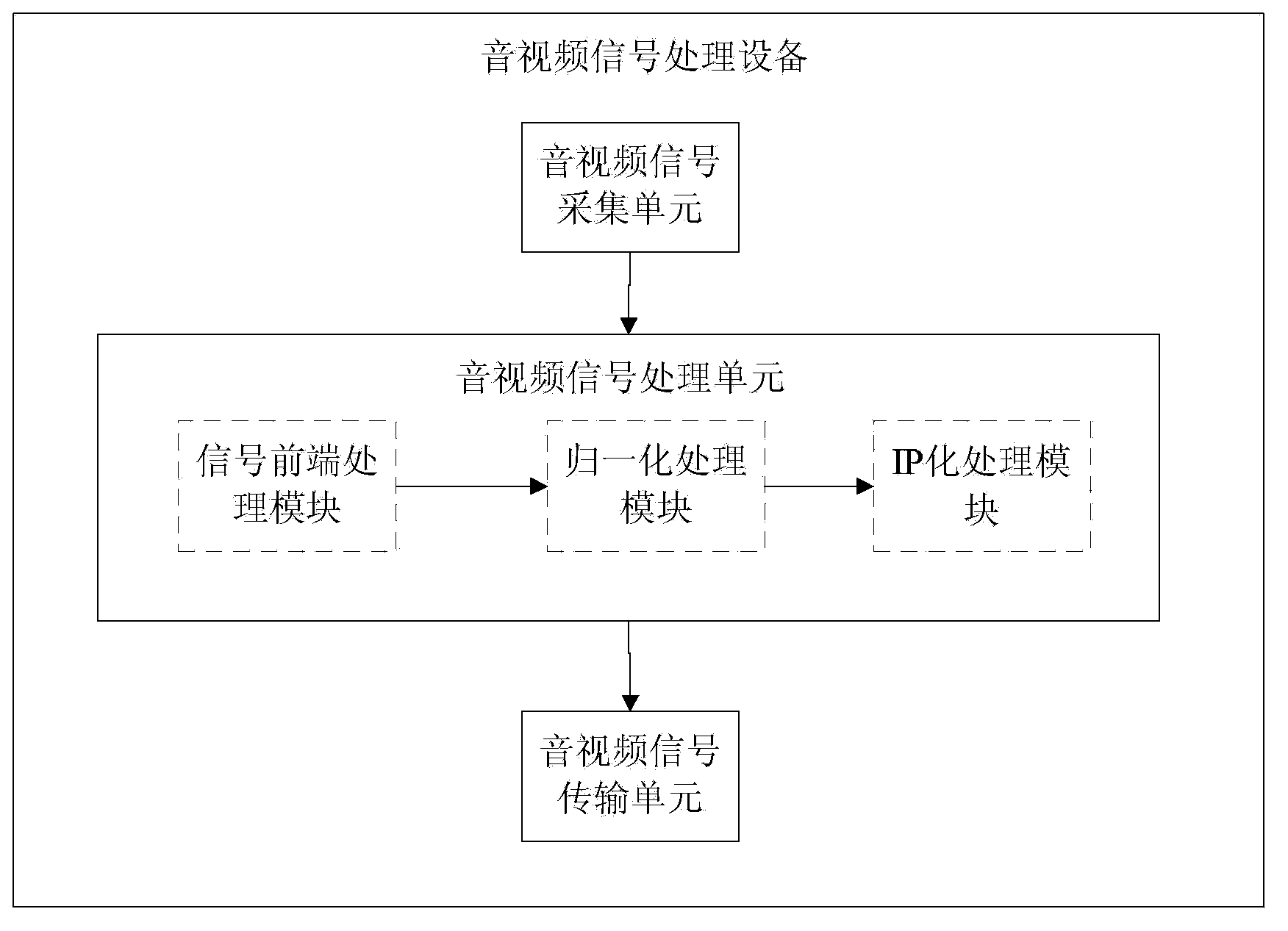

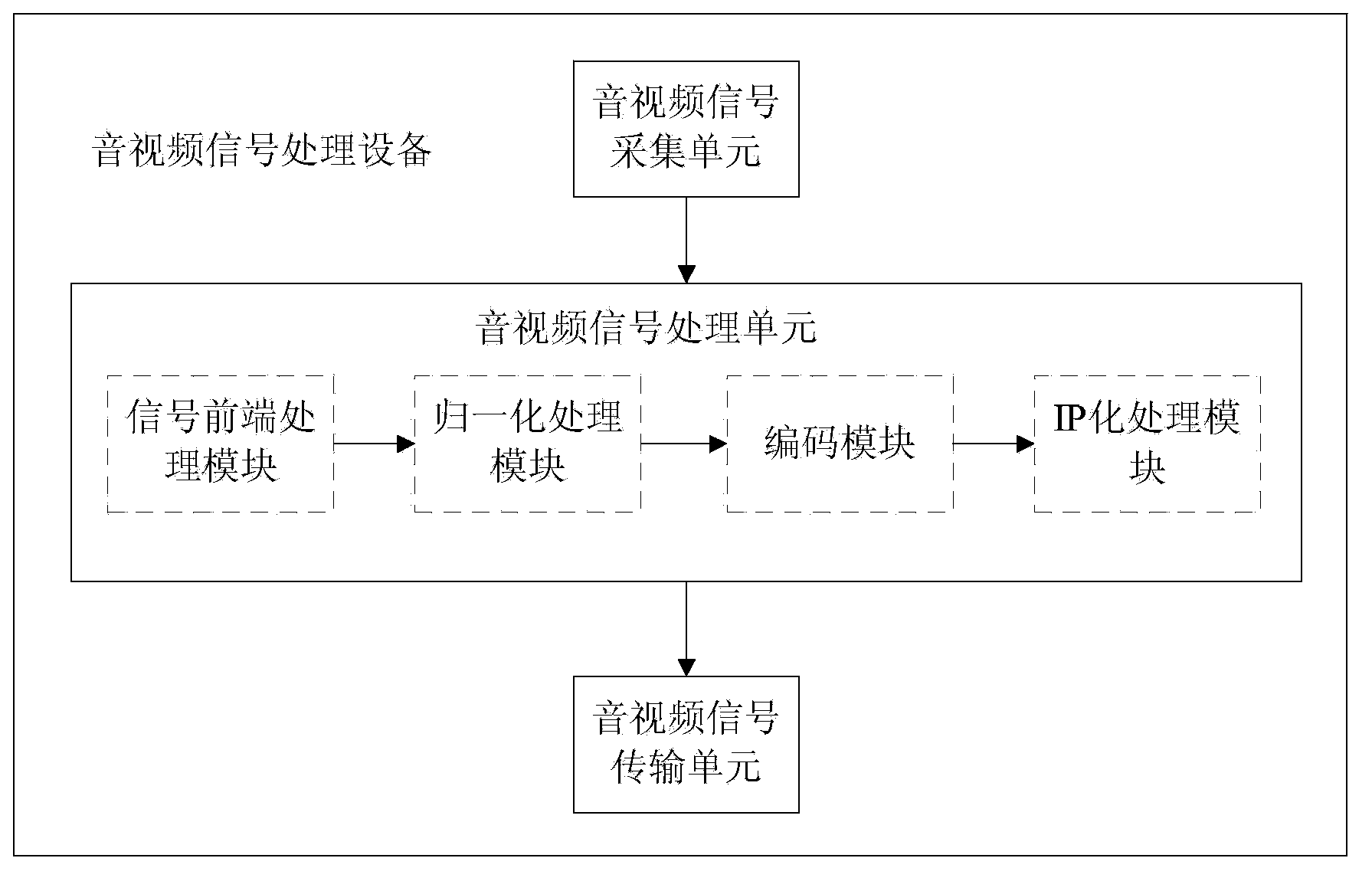

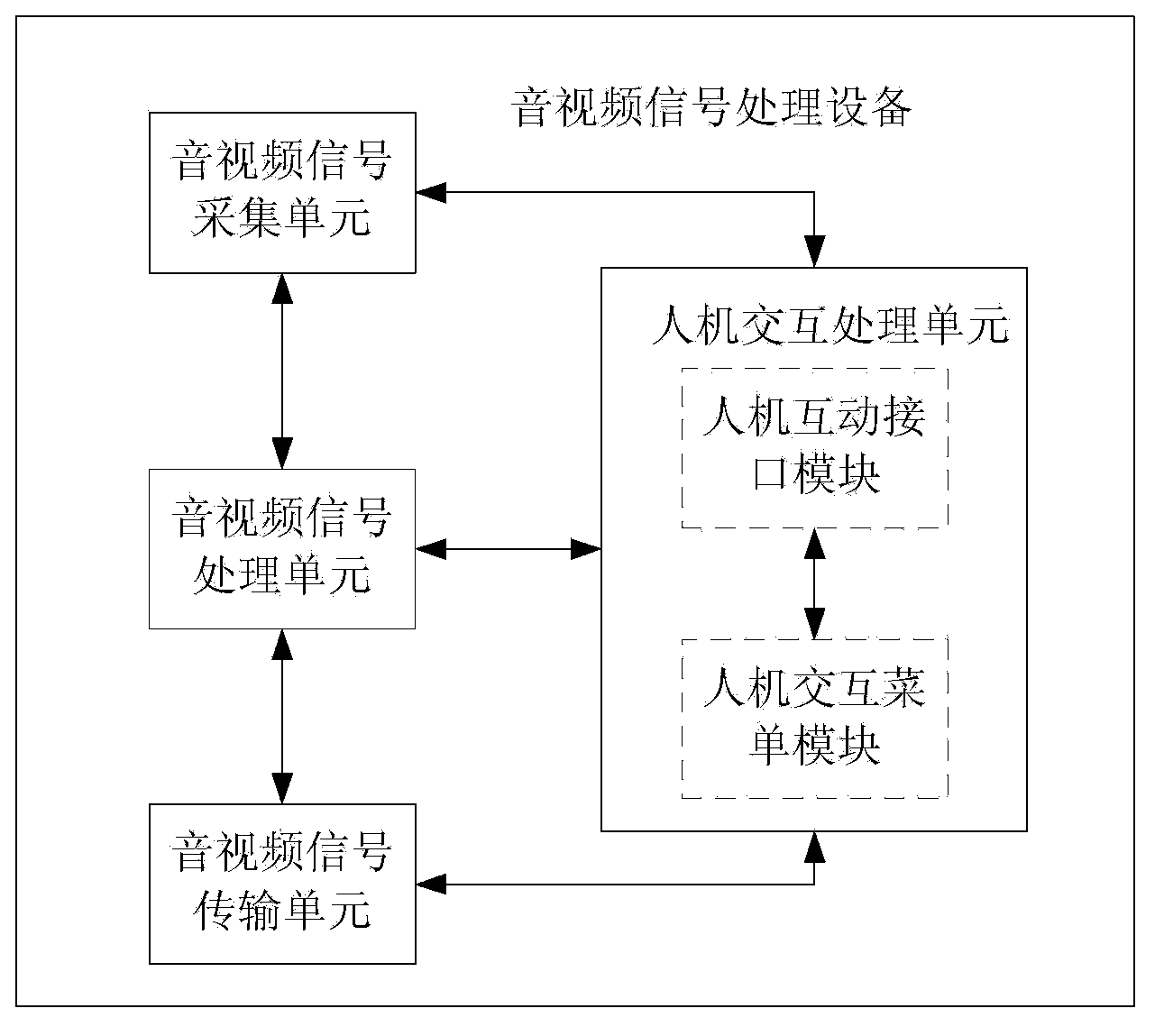

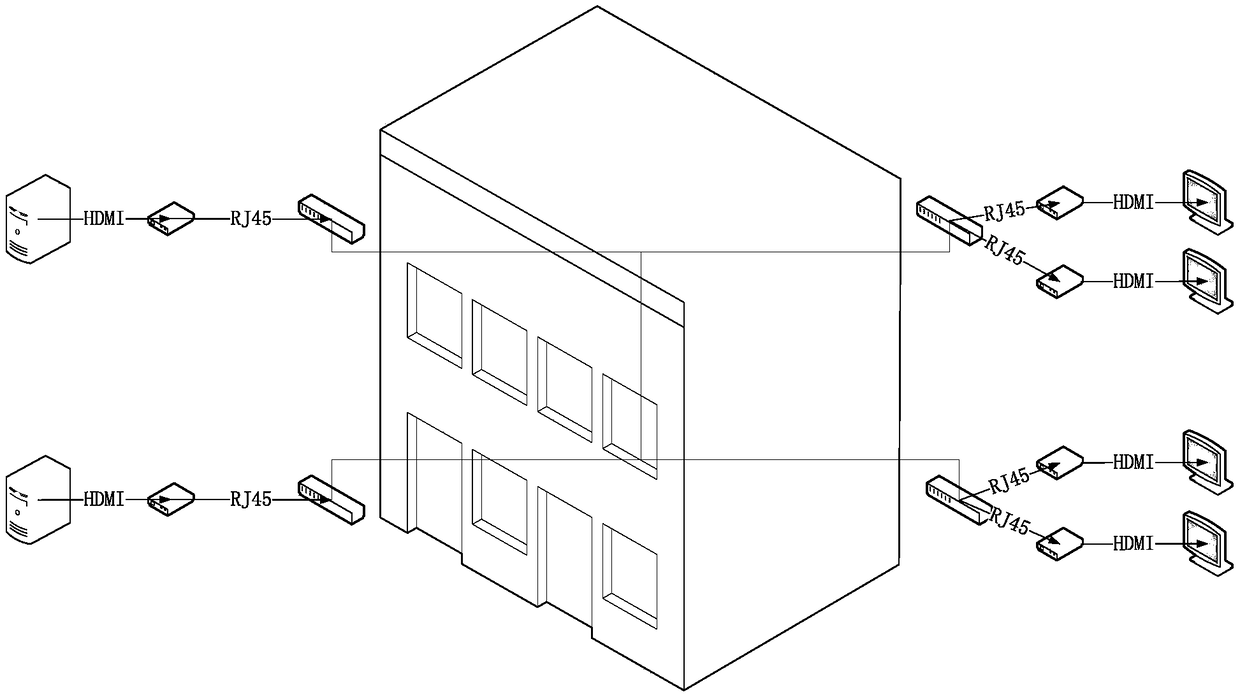

Audio-and-video signal processing device, playing device, system and method

ActiveCN103856808AReduce upgrade costsAvoid duplication of investmentTwo-way working systemsSelective content distributionIp processingVideo transmission

This invention relates to an audio-and-video signal processing device, a playing device, a system and a method. The audio-and-video processing device is used for connecting to one or more than one audio-and-video signal playing devices. The audio-and-video signal processing device comprises an audio-and-video signal acquisition unit, an audio-and-video signal processing unit and an audio-and-video signal transmission unit. The audio-and-video signal acquisition unit is used for collecting one or more than one external audio-and-video signals; the audio-and-video signal processing unit is used for processing the collected audio and video signals and the processing comprises the IP processing. The audio-and-video transmission unit is used for outputting the audio and video signal which has gone through the IP processing in an IP broadcasting manner. The audio-and-video signal processing device, the playing device, the system and the method provided by the invention reduces the cost for upgrading and updating of the television and eliminates the repeat investment on the resource equipment.

Owner:ZTE CORP

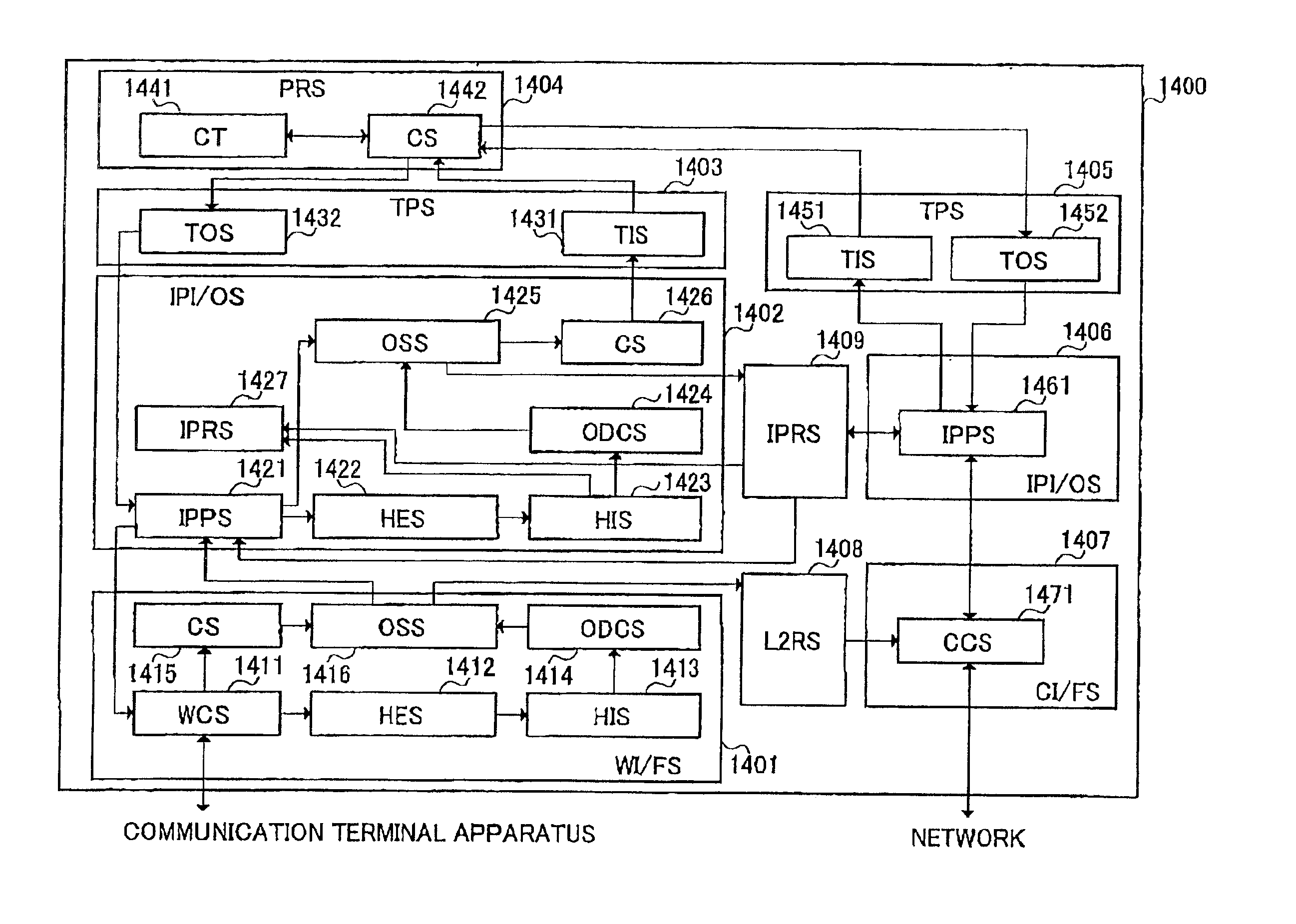

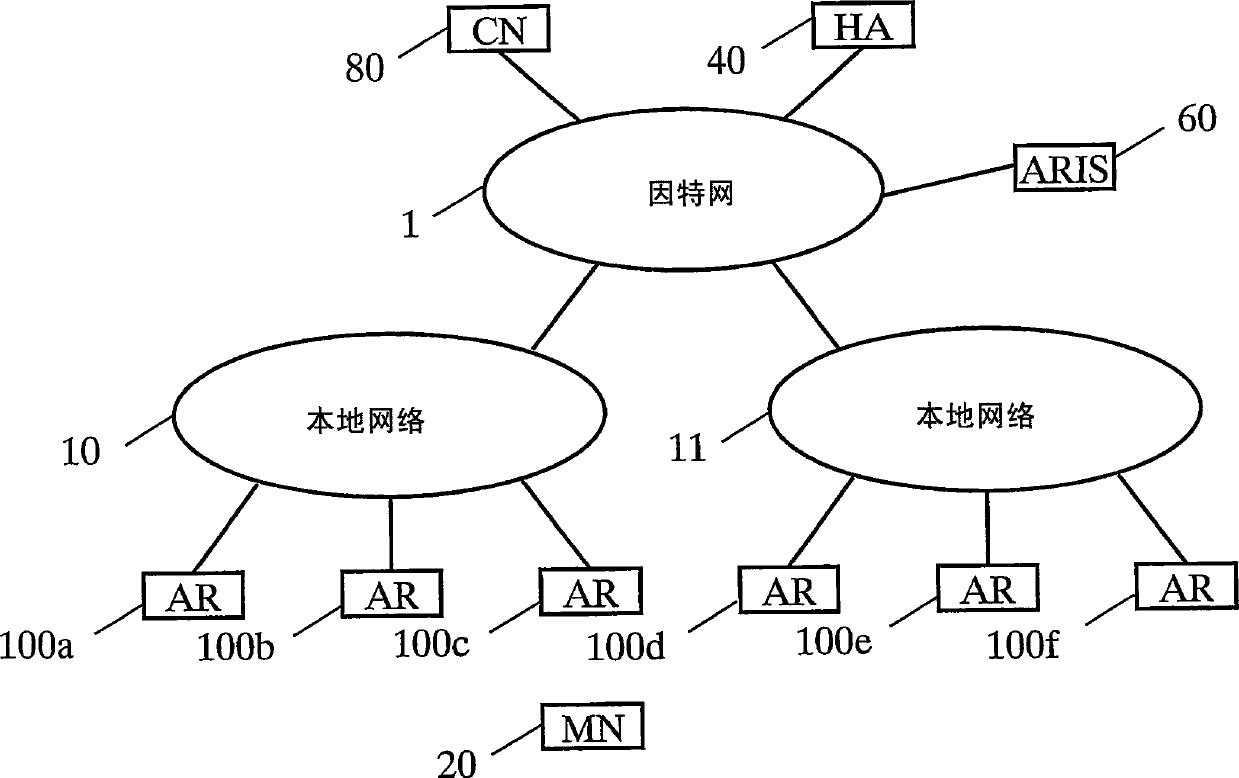

Mobile communication method, mobile communication apparatus, home agent apparatus, access router information server apparatus, and mobile communication system

InactiveCN1853384AReduce lossNetwork traffic/resource managementWireless network protocolsCommunications systemPacket loss

A mobile communication apparatus (20) comprises a mobile IP / high-speed mobile IP processing part (25); an access router searching part (28) for acquiring information related to access router apparatuses; a high-speed mobile IP compliance determining part (27) for determining whether the access router apparatuses comply with a high-speed mobile IP; and a high-speed mobile IP control part (26) for controlling the contents of a message produced by the mobile IP / high-speed mobile IP processing part (25). According to this, even if any of access router apparatuses does not comply with the high-speed mobile IP, the procedure of high-speed mobile IP can be implemented, thereby reducing packet loss.

Owner:PANASONIC CORP

Processing methods, device, equipment and systems for IPsec protocol and medium

InactiveCN109450960AImprove data processing capabilitiesSimple designTransmissionData compressionIp processing

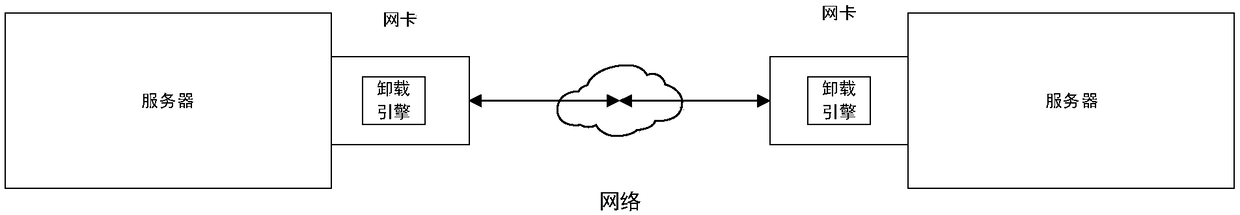

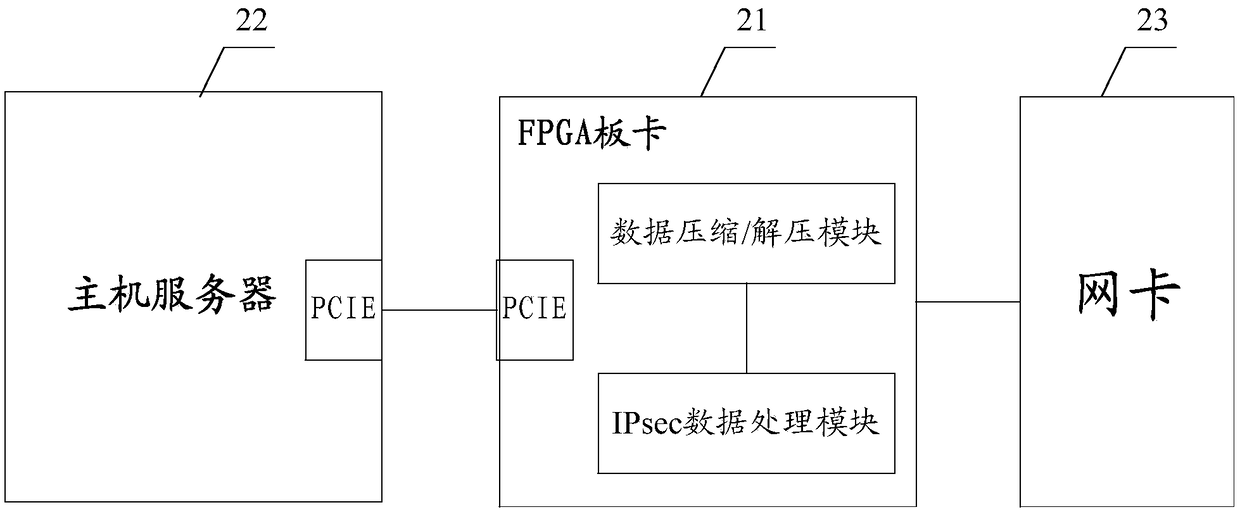

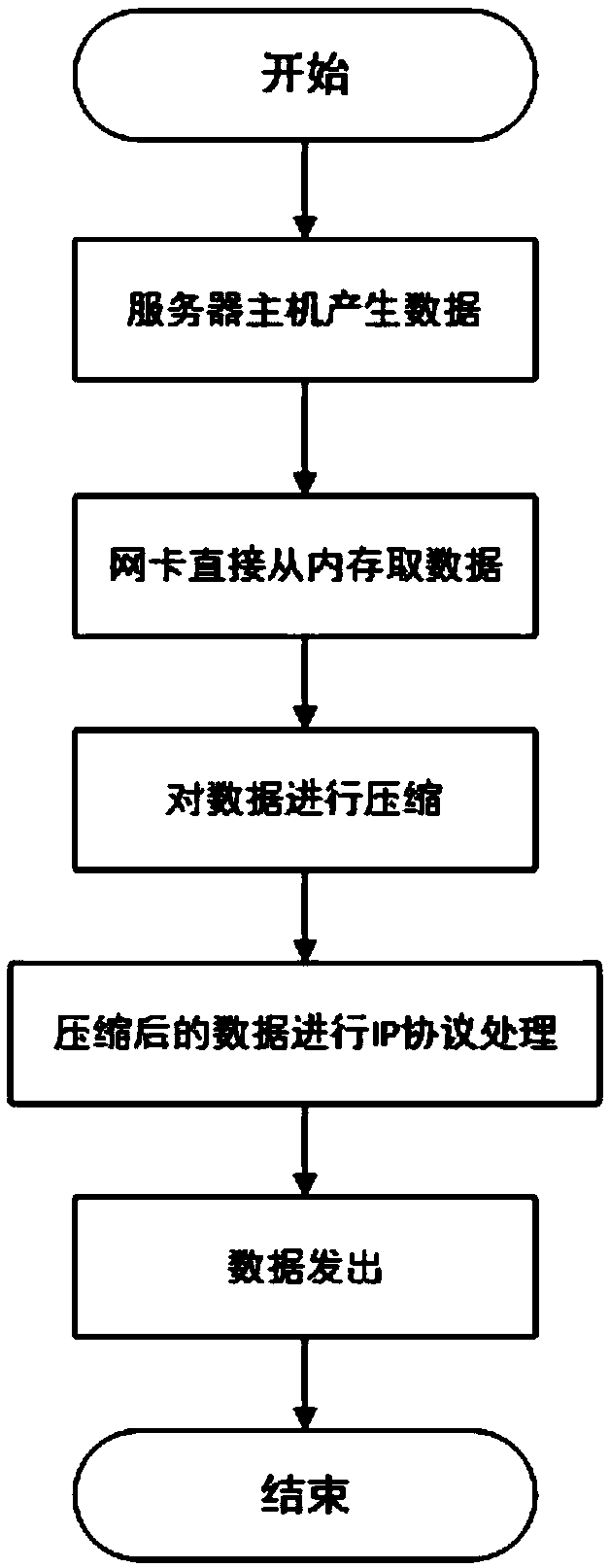

The embodiment of the invention discloses processing methods, device, equipment and system for an IPsec (Internet Protocol Security) protocol and a computer readable memory medium. The system comprises an FPGA board card, a host server and a network card. The FPGA board card and the host server carry out data communication through PCIE (Peripheral Component Interconnect Express). The FPGA board card is connected with the network card. The FPGA board card comprises a data compression / decompression module which is used for compressing to-be-processed data read by slave and host server memories and decompressing IP data packets sent by the network card, and an IPsec data processing module which is used for carrying out IP processing on the data. The processing methods, the device, the equipment and the systems are simple in design, clear in structure and are convenient for realization. Hardware acceleration is carried out on IPsec protocol processing through utilization of the FPGA. A network card structure can be customized through utilization of the FPGA. Through compression of the data, practical data bandwidths can exceed optical fiber limitation, so network bandwidths are improved. According to task change or increase of data volume, the network card can be changed without changing server hardware, so cost is reduced.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

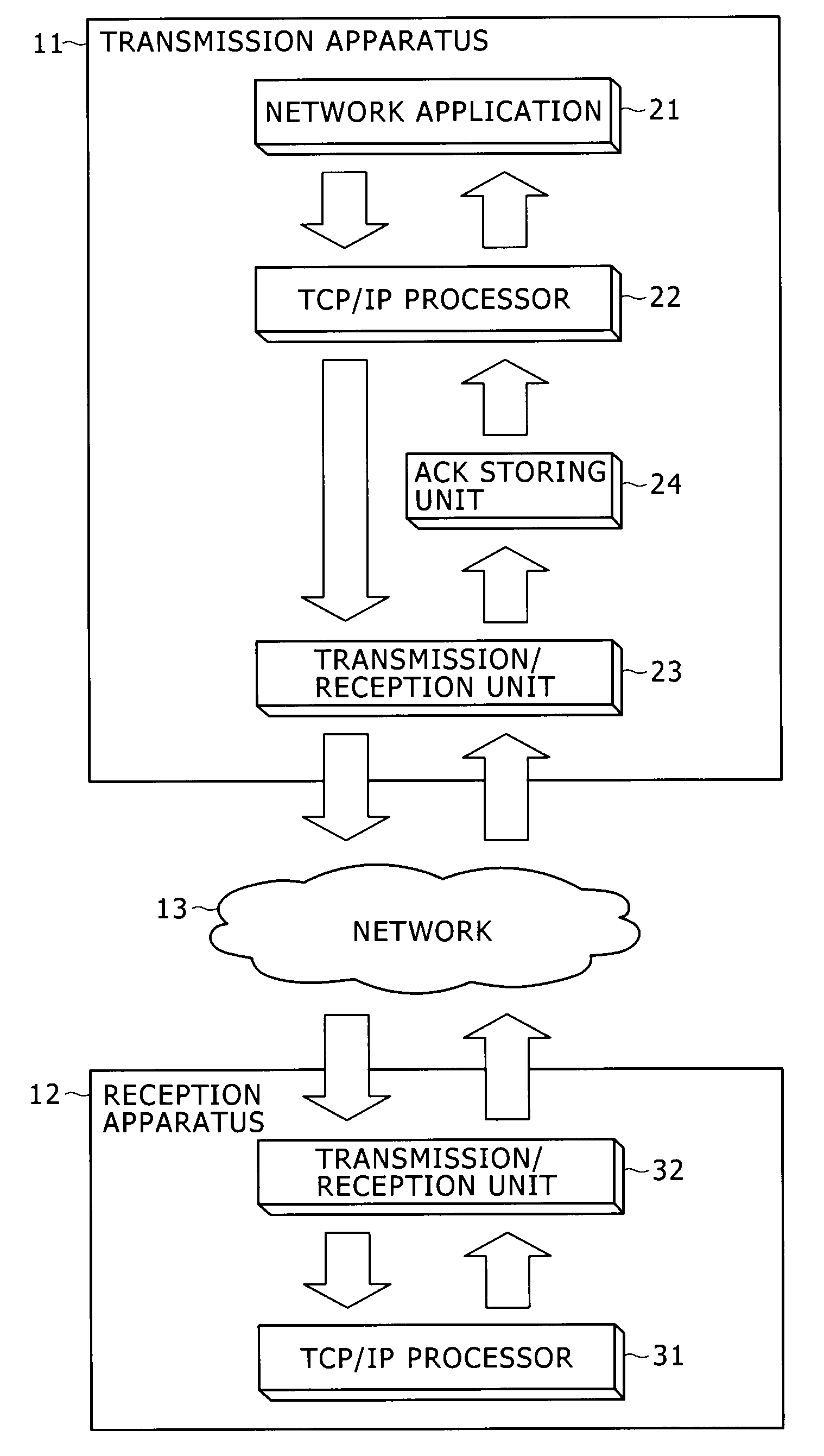

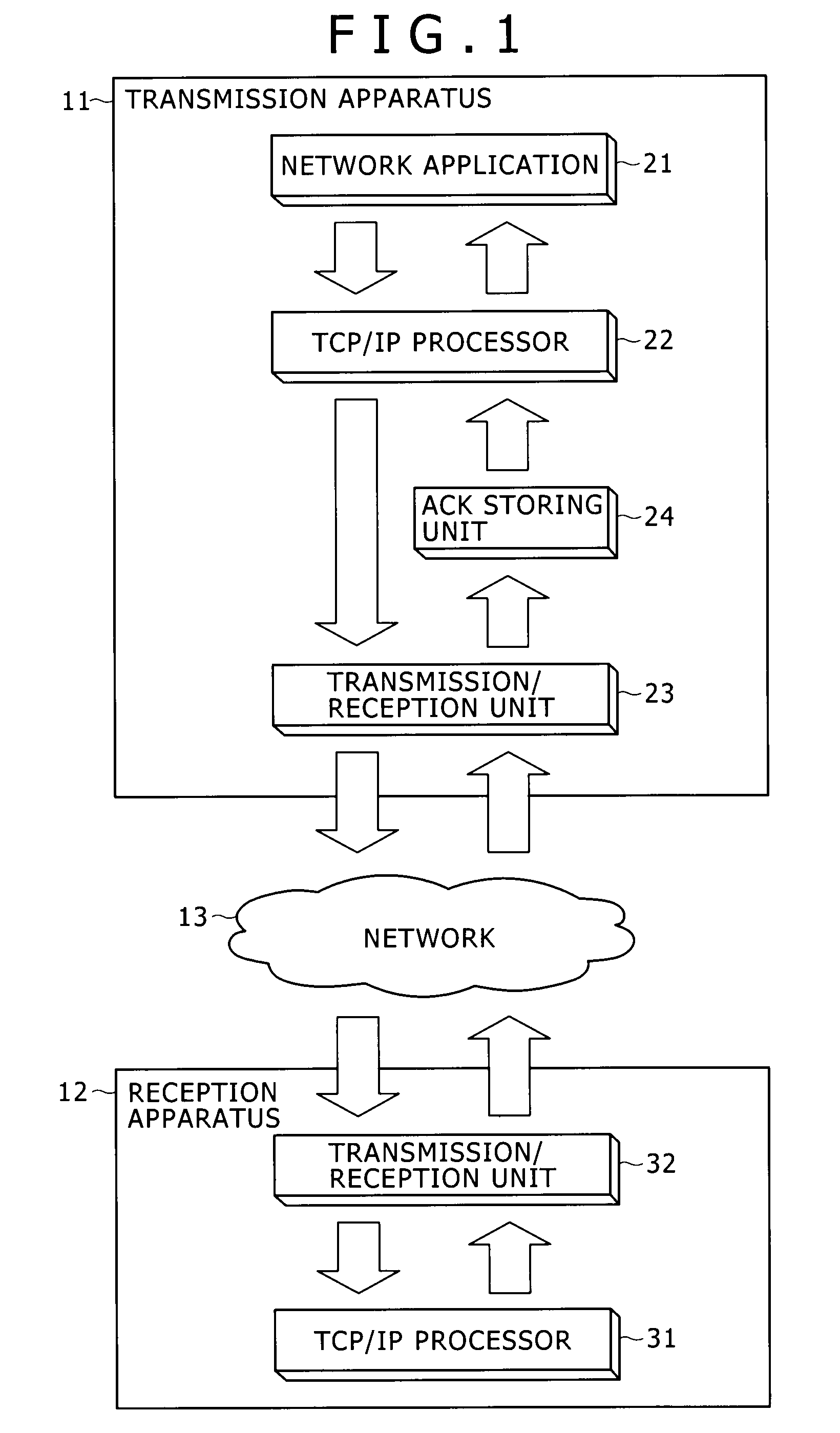

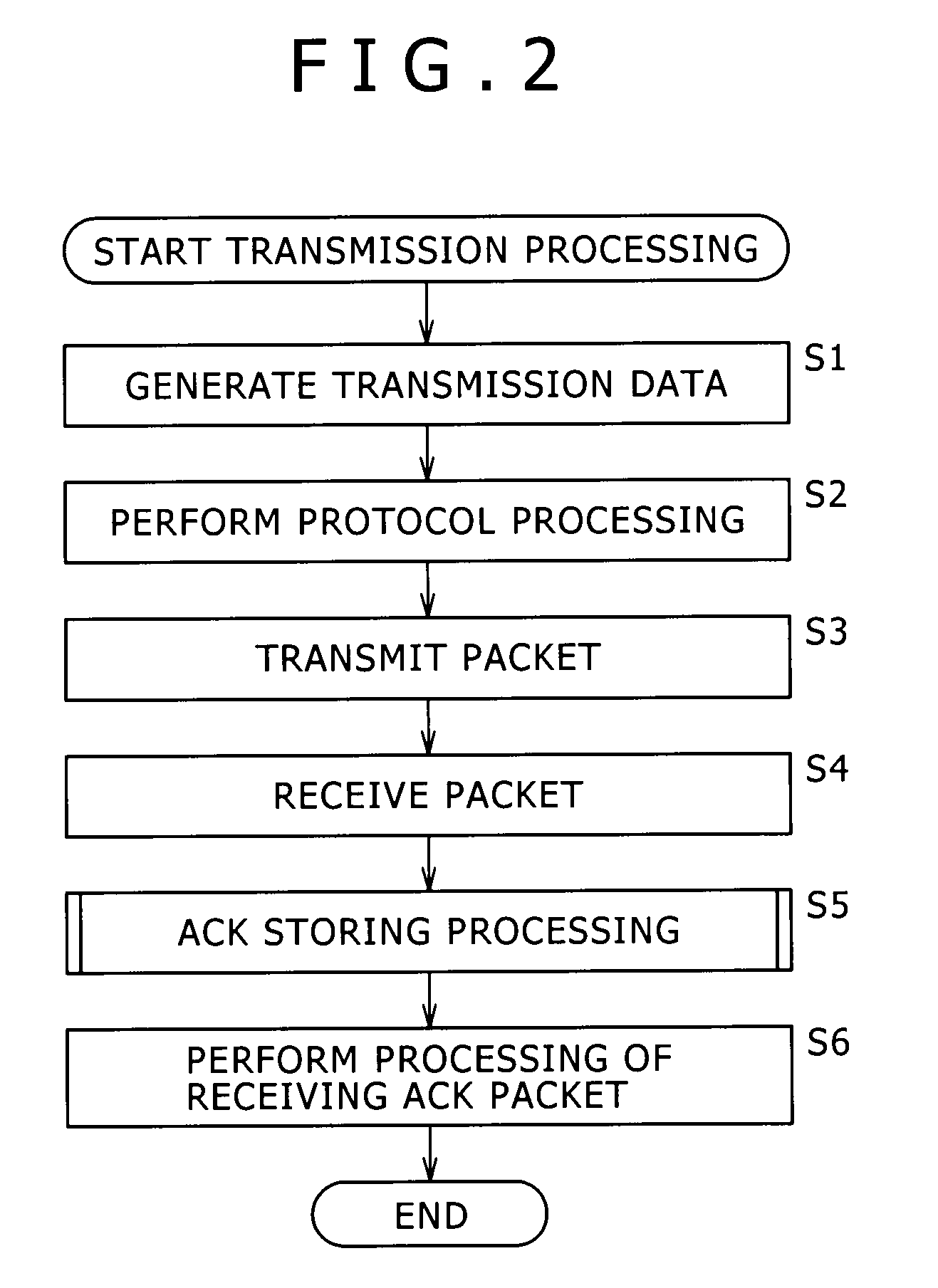

Transmission apparatus, transmission method, and program

ActiveUS20090252162A1Increase speedReduce stepsError preventionData switching by path configurationIp processingReal-time computing

Disclosed herein is a transmission apparatus including a receiving unit configured to receive ACK packets transmitted from a reception apparatus in response to transmission data items, an ACK storing unit configured to store a latest ACK packet which is last received among the ACK packets, and a TCP / IP processing unit configured to perform processing of receiving an ACK packet in accordance with the latest ACK packet supplied from the ACK storing means at a predetermined timing.

Owner:SONY CORP

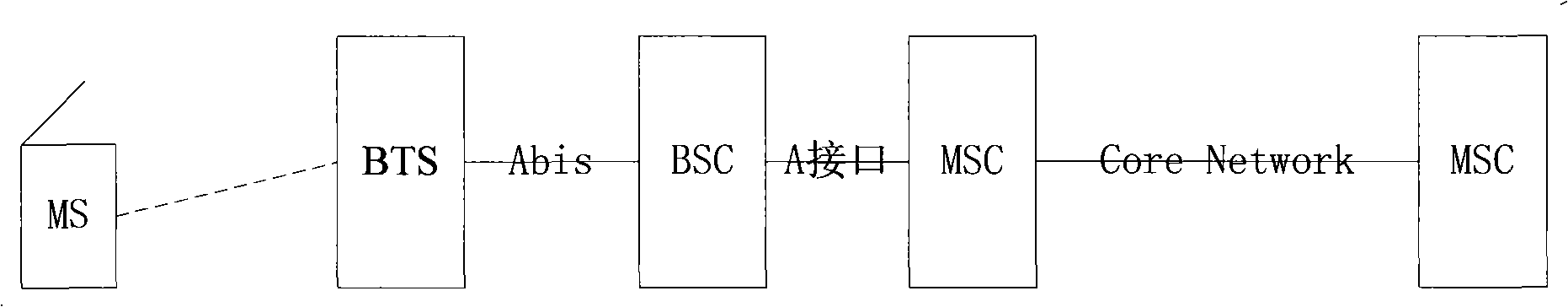

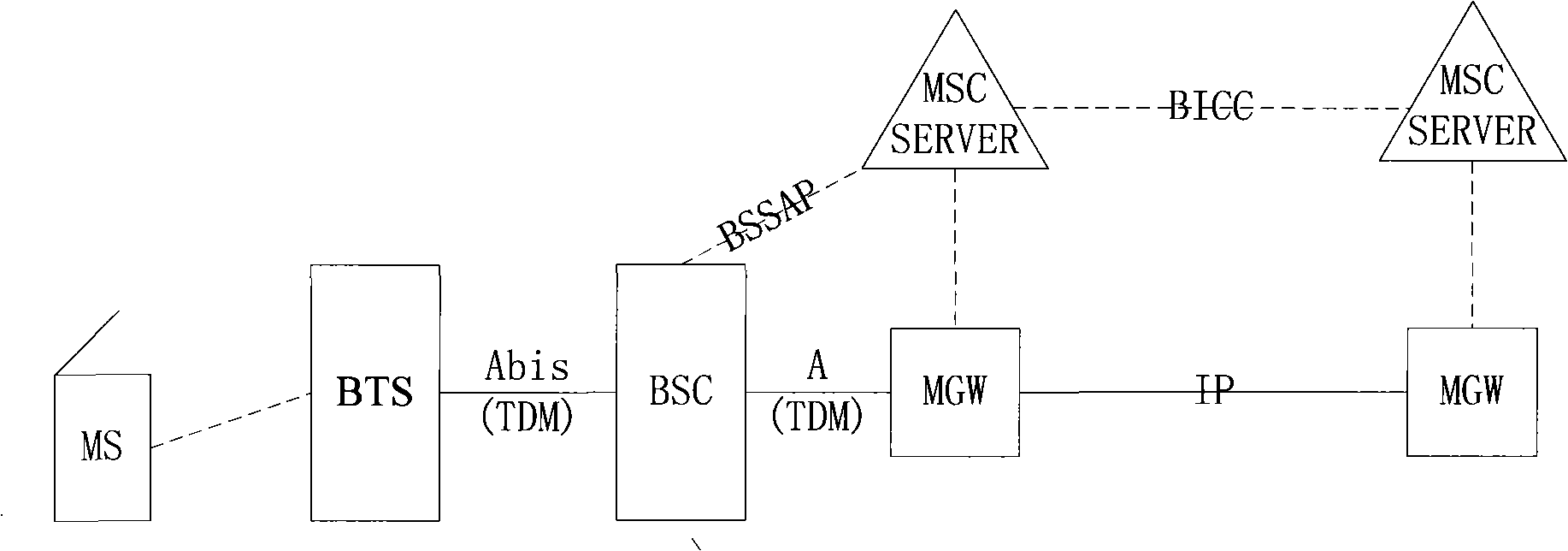

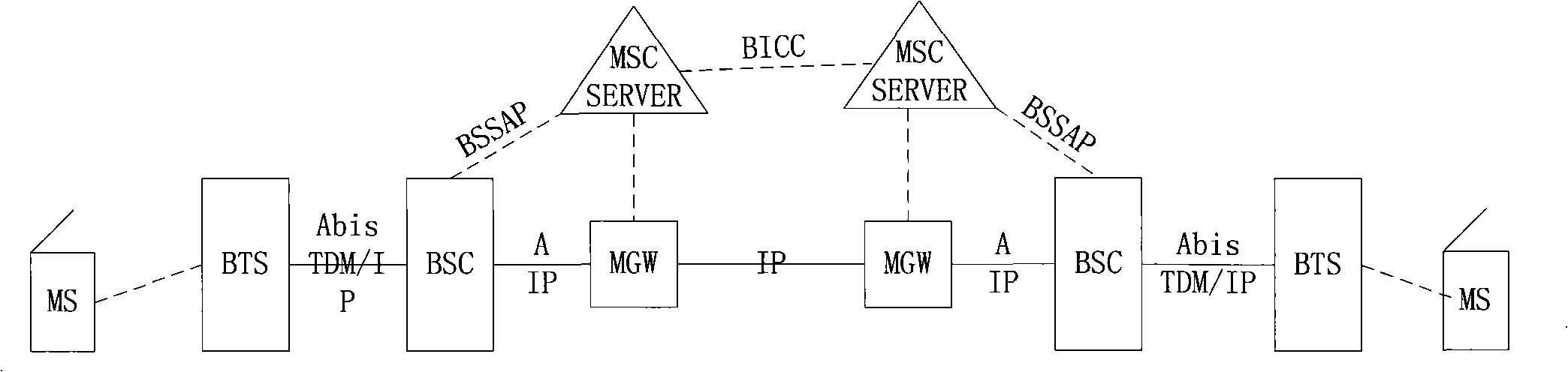

Method, device and system for implementing IP A interface in second generation mobile communication system

ActiveCN101316379AAvoid codec conversionImprove voice qualityNetwork traffic/resource managementSpeech analysisIp processingMobile communication systems

The invention discloses a method, equipment and a system for causing an A interface to obtain the IP, which are used for realizing the IP processing to the A interface between a base-station control device and a media gateway. The method of the invention mainly includes that the base-station control device carries out the removal of the encapsulation of a rate adapter unit TRAU to received wireless side data so as to obtain the static-load data of a compressed voice code, the static-load data of a compressed voice code is then encapsulated into an IP packet; the IP packet is sent to the mediagateway by the A interface between the base-station control device and the media gateway. Therefore, the method, the equipment and the system can realize the non-code conversion of the path wholly orpartially so as to improve the voice quality and save the equipment cost. Simultaneously, the transmission by the compressed code can also reduce the transmission consumption and the transmission cost, and improve the transmission utilization.

Owner:HUAWEI TECH CO LTD

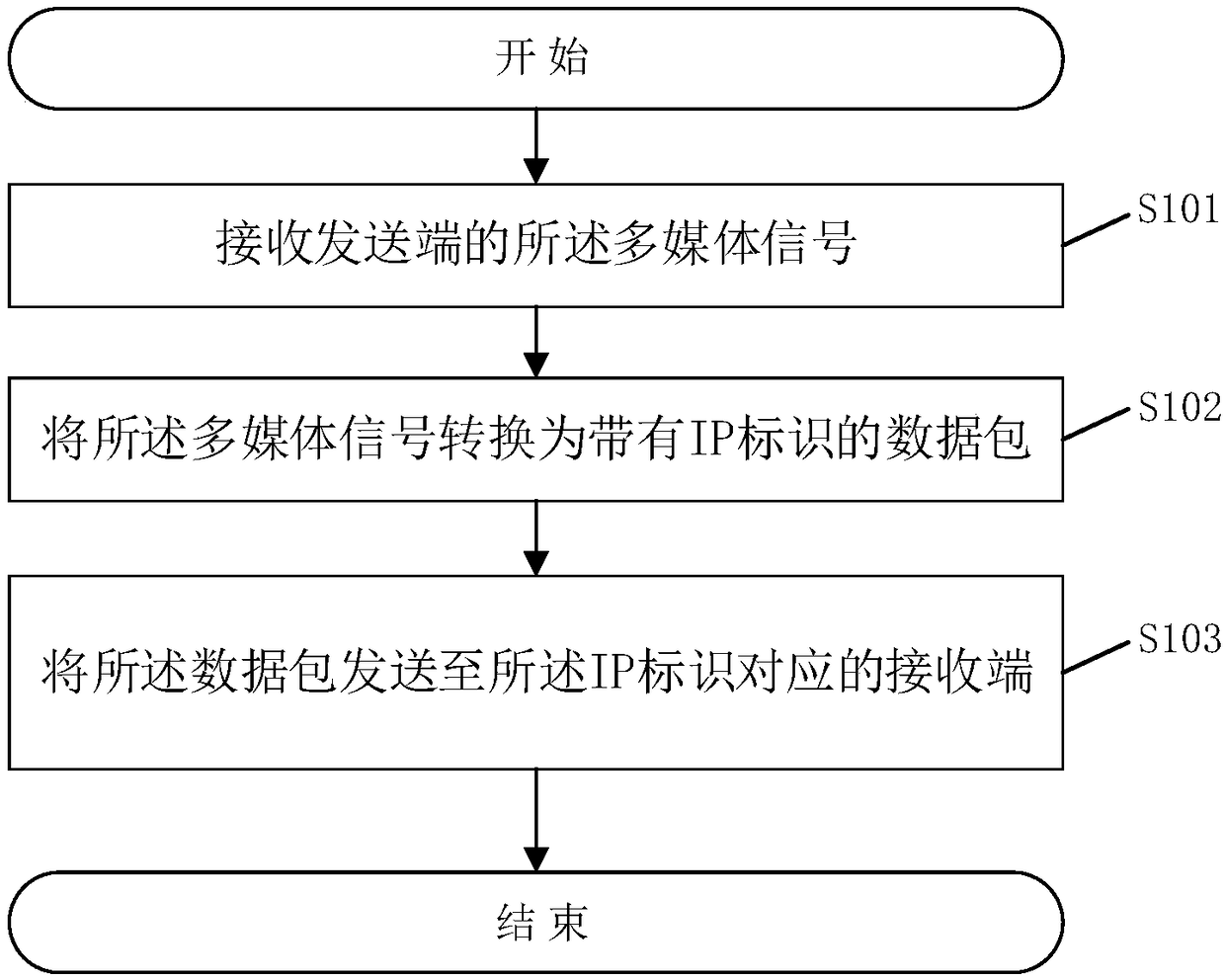

Multimedia signal transmission method, multimedia signal transmission system, and related apparatuses

InactiveCN109412979ASmooth transmissionEasy to troubleshootTelevision system detailsColor television detailsIp addressTransfer procedure

The invention provides a multimedia signal transmission method, comprising the following steps: receiving a multimedia signal of a transmitting end; converting the multimedia signal into a data packetwith an IP identifier; and transmitting the data packet to a receiving end corresponding to the IP identifier. According to the multimedia signal transmission method provided by the invention, by performing the IP processing on the multimedia signal, the multimedia signal is delivered and transmitted according to the IP address. The transmission process is limited only by the capacity of a switch. Once the switch has sufficient capacity, the stable transmission of the multimedia signal can be guaranteed. Furthermore, for the multimedia signals containing the IP identifier, it is easier to perform troubleshooting when signal loss occurs. The invention further provides a multimedia signal transmission system, a computer readable storage medium, and a network switch, which have the beneficial effects described above.

Owner:GUANGDONG POWER GRID CO LTD +1

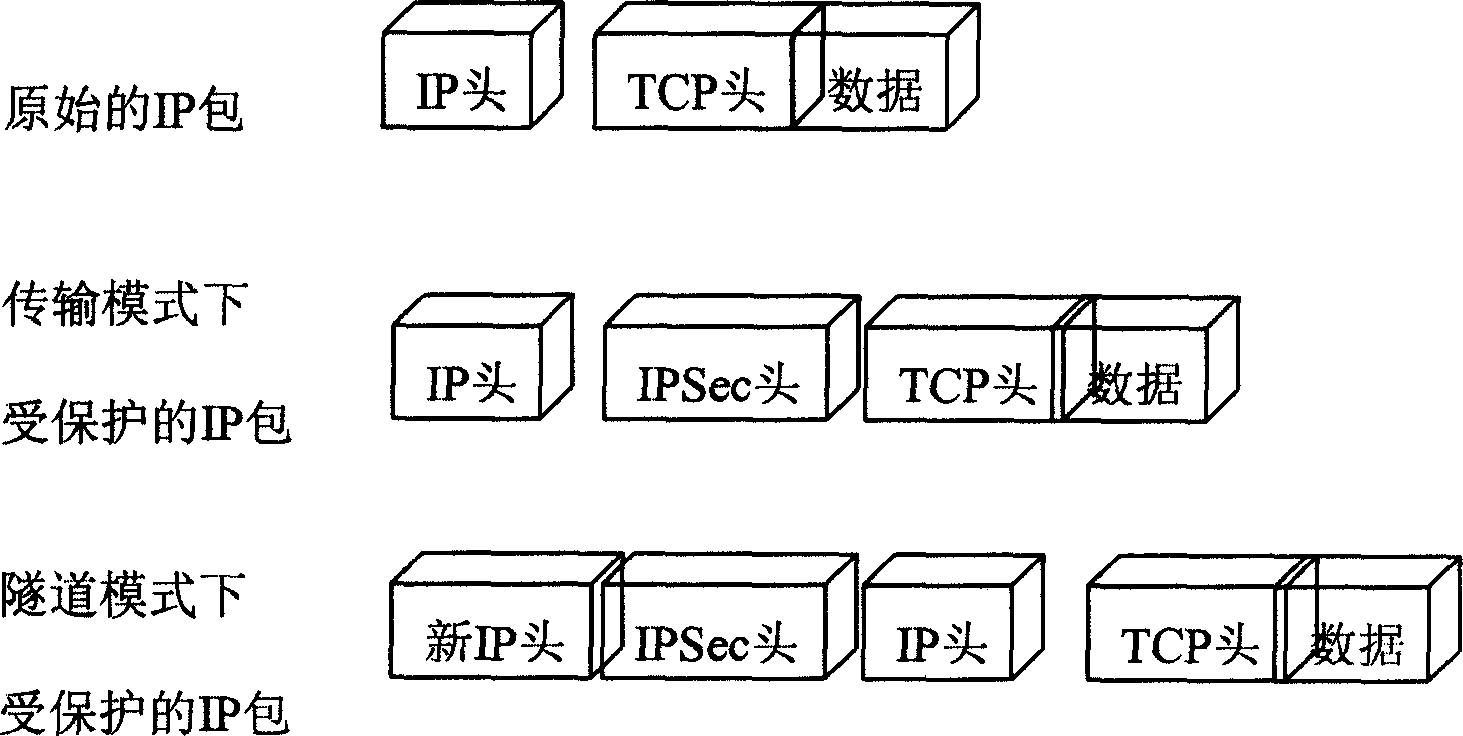

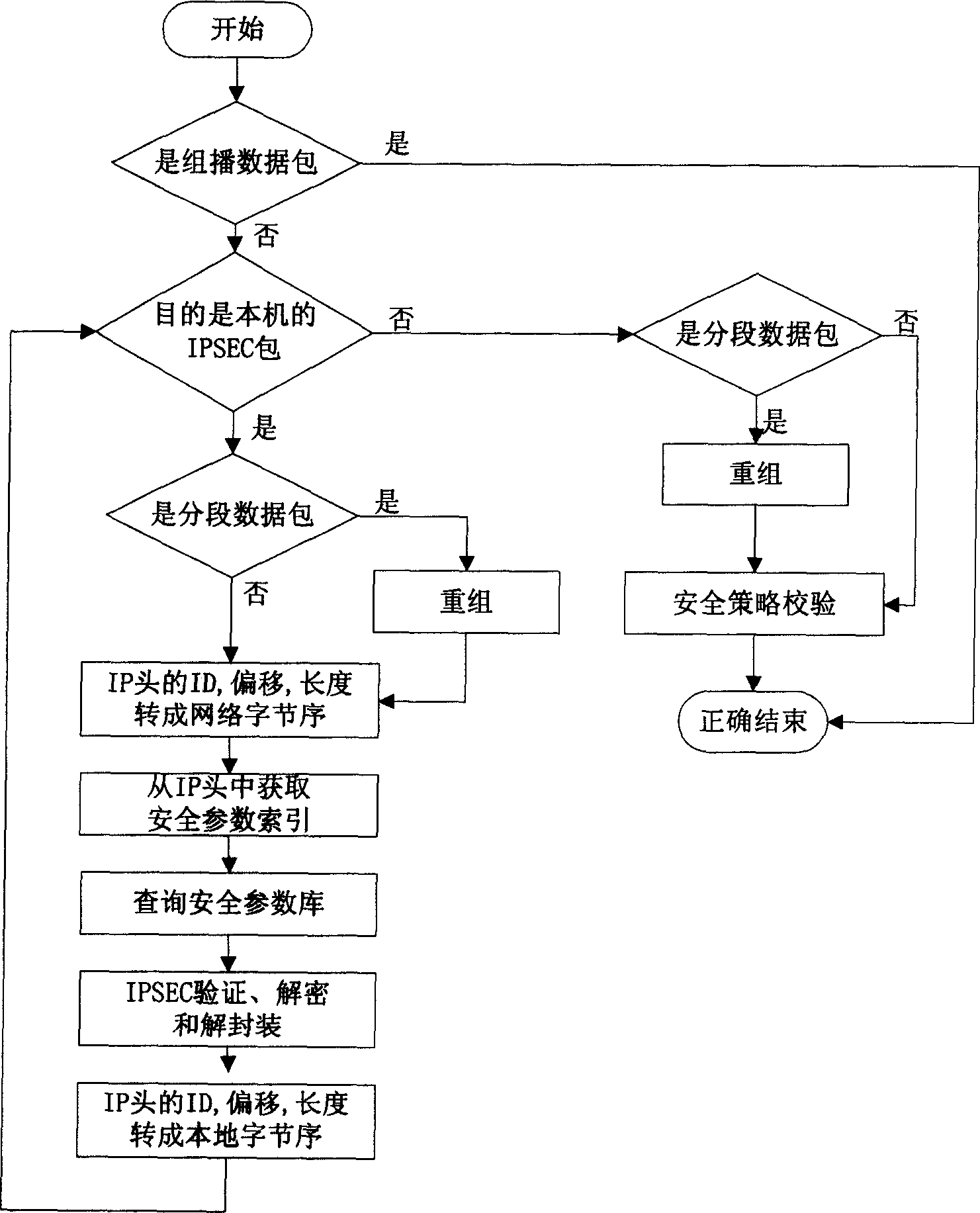

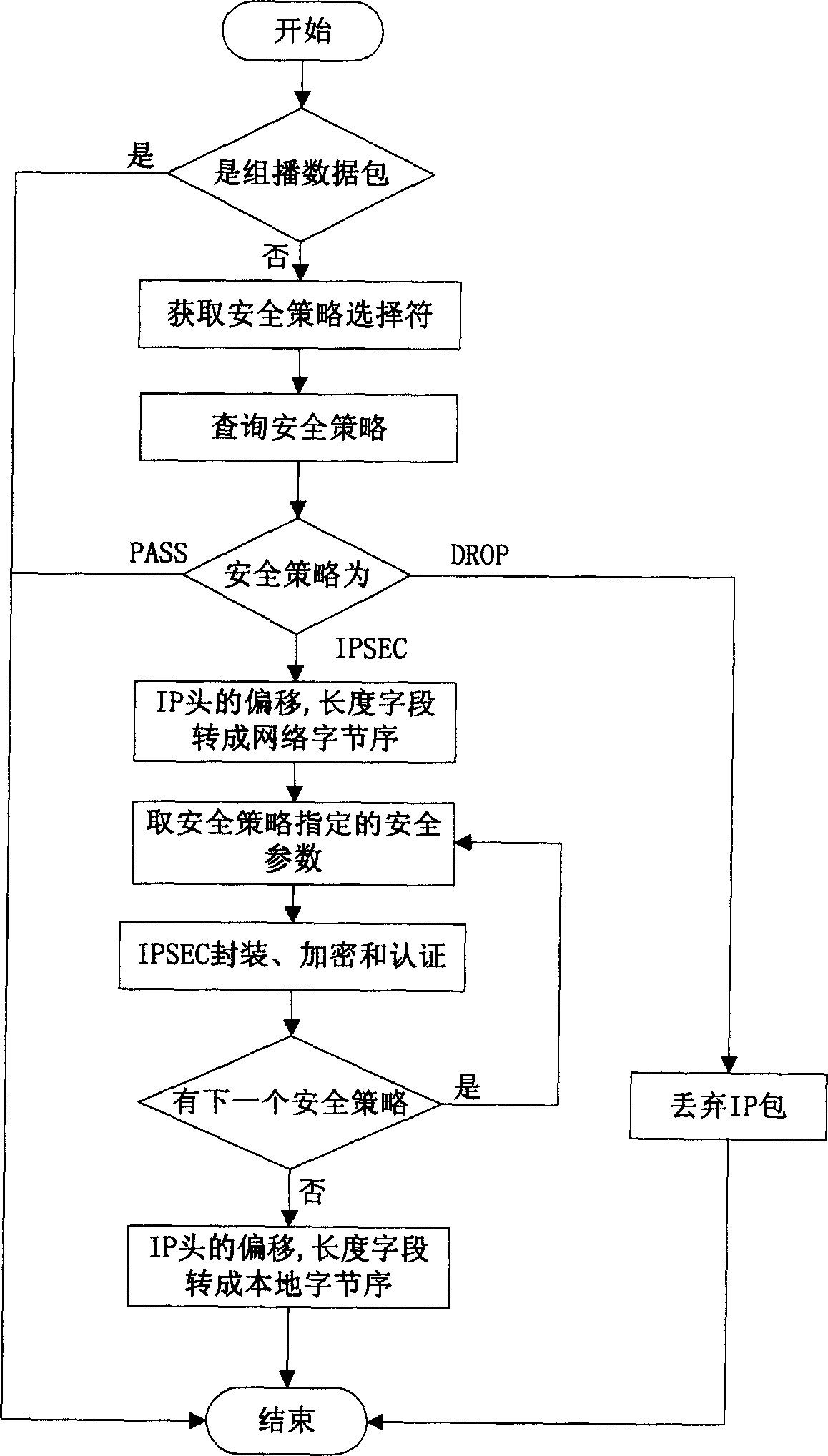

A method for embedding IPSEC in IP protocol stack

InactiveCN1545292AOvercome weaknessFunction increaseUser identity/authority verificationData switching networksIp processingIPsec

The invention discloses a method to insert IPSEC in IP protocol stack, including the following steps: 1, during the IP input processing course of IP protocol stack, after IP processing is basically completed, inserting IPSec input processing flow; 2, during the IP output processing course, after IP processing is basically completed, inserting IPSec output processing flow. By this method, compared with existing techniques, it overcomes the disadvantage of inserting modes of Free SWAN and KAME and can implement complete IPSec funciotns such as safety policy inspection for transmitted IP packages, safety policy inspection for non-IPSec package in local computer, supporting inserted safety policy, supporting high safety particle size, etc.

Owner:ZTE CORP