Relay protection system and special multi-core Soc chip architecture thereof

A relay protection, multi-core technology, applied in the architecture with a single central processing unit, electrical digital data processing, general-purpose stored program computers, etc., can solve problems affecting the operation stability and reliability of relay protection products. Complexity and other issues to achieve the effect of improving reliability and stability and simplifying the multi-chip hardware architecture

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

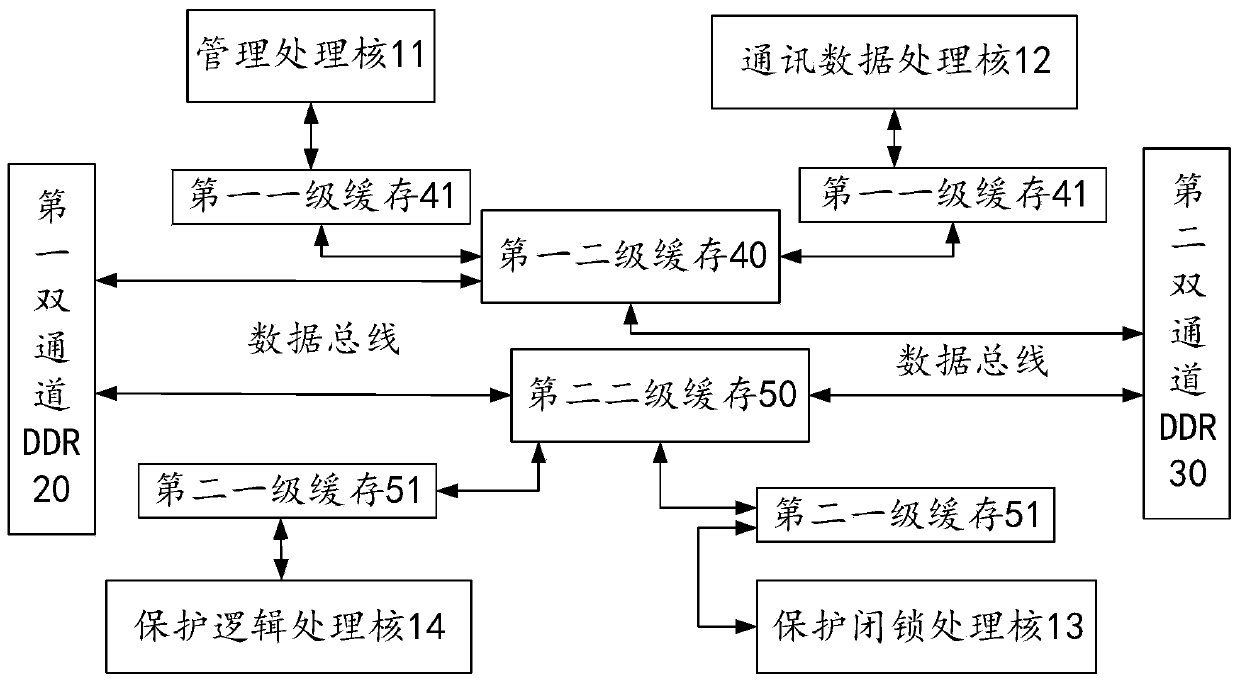

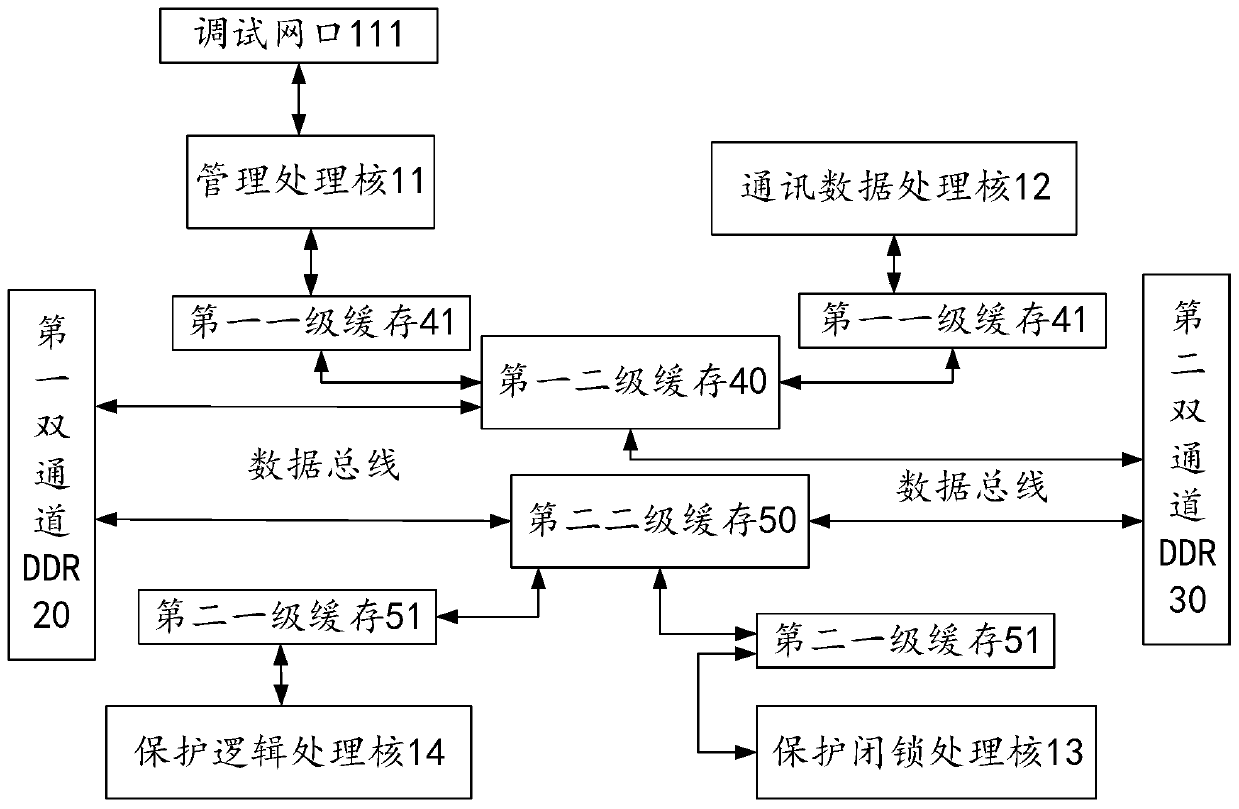

[0032] figure 1 It is a frame diagram of the multi-core Soc chip architecture dedicated to the relay protection system described in the embodiment of the present invention.

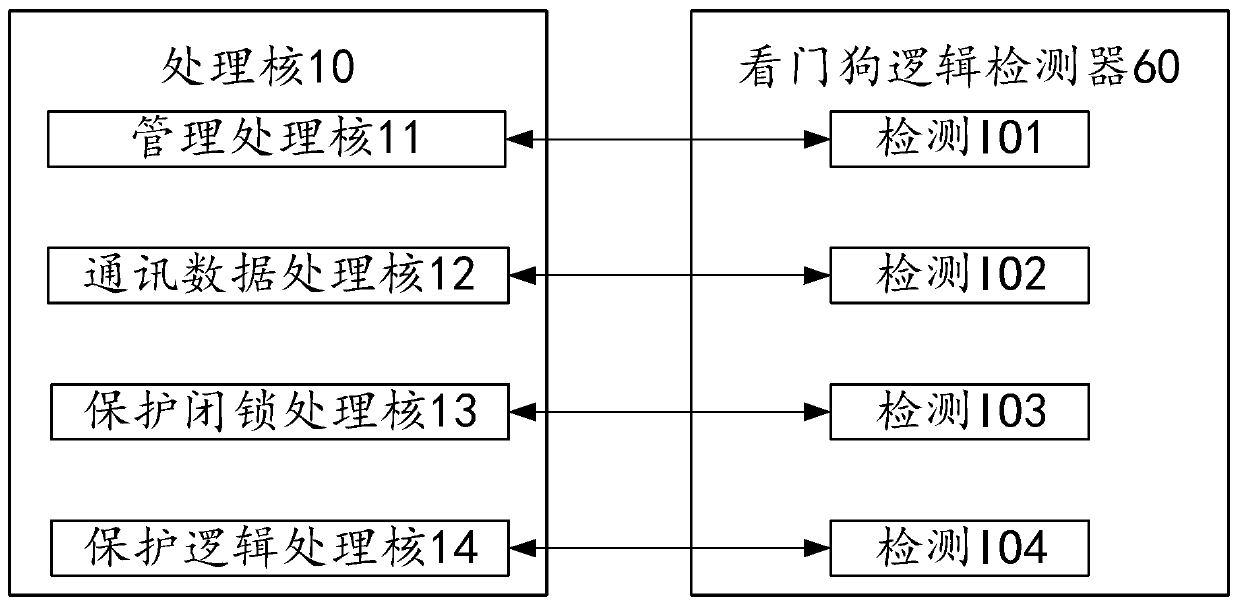

[0033] Such as figure 1 As shown, the embodiment of the present invention provides a special multi-core Soc chip architecture for a relay protection system, which is used for a relay protection system. The multi-core Soc chip architecture dedicated for a relay protection system includes at least four processing cores 10, a first dual channel DDR20 and the second dual-channel DDR30, the four processing cores 10 are management processing core 11, communication data processing core 12, protection lock processing core 13, and protection logic processing core 14; the first dual-channel DDR20 and the second dual-channel DDR30 The first secondary cache 40 and the second secondary cache 50 are connected between them; the management processing core 11 and the information data processing core 12 are respectively c...

Embodiment 2

[0061] The embodiment of the present invention also provides a relay protection system, including the multi-core Soc chip architecture dedicated to the relay protection system described in the first embodiment.

[0062] What needs to be said is that the multi-core Soc chip architecture dedicated to the relay protection system has been described in detail in the first embodiment, so it will not be described one by one in this embodiment.

[0063] The relay protection system adopts the multi-core Soc chip architecture dedicated to the relay protection system instead of the structure design of several chips and several card boards used in the existing relay protection system. The multi-core Soc chip architecture dedicated to the relay protection system simplifies The original complex multi-chip hardware architecture also avoids the low reliability and stability of the relay protection system caused by the unstable connection of the multi-chip hardware structure. The multi-core Soc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More