Patents

Literature

80 results about "Multicore computing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Definition. Multicore computing is the computational technique that joins parallel programming strategies and parallel processors (multicore processors) to make efficient computations possible.

Systems and method for transaction stall detection and propagating the result in a multi-core architecture

ActiveUS20100325495A1Multiple digital computer combinationsNon-redundant fault processingEmbedded systemMulticore architecture

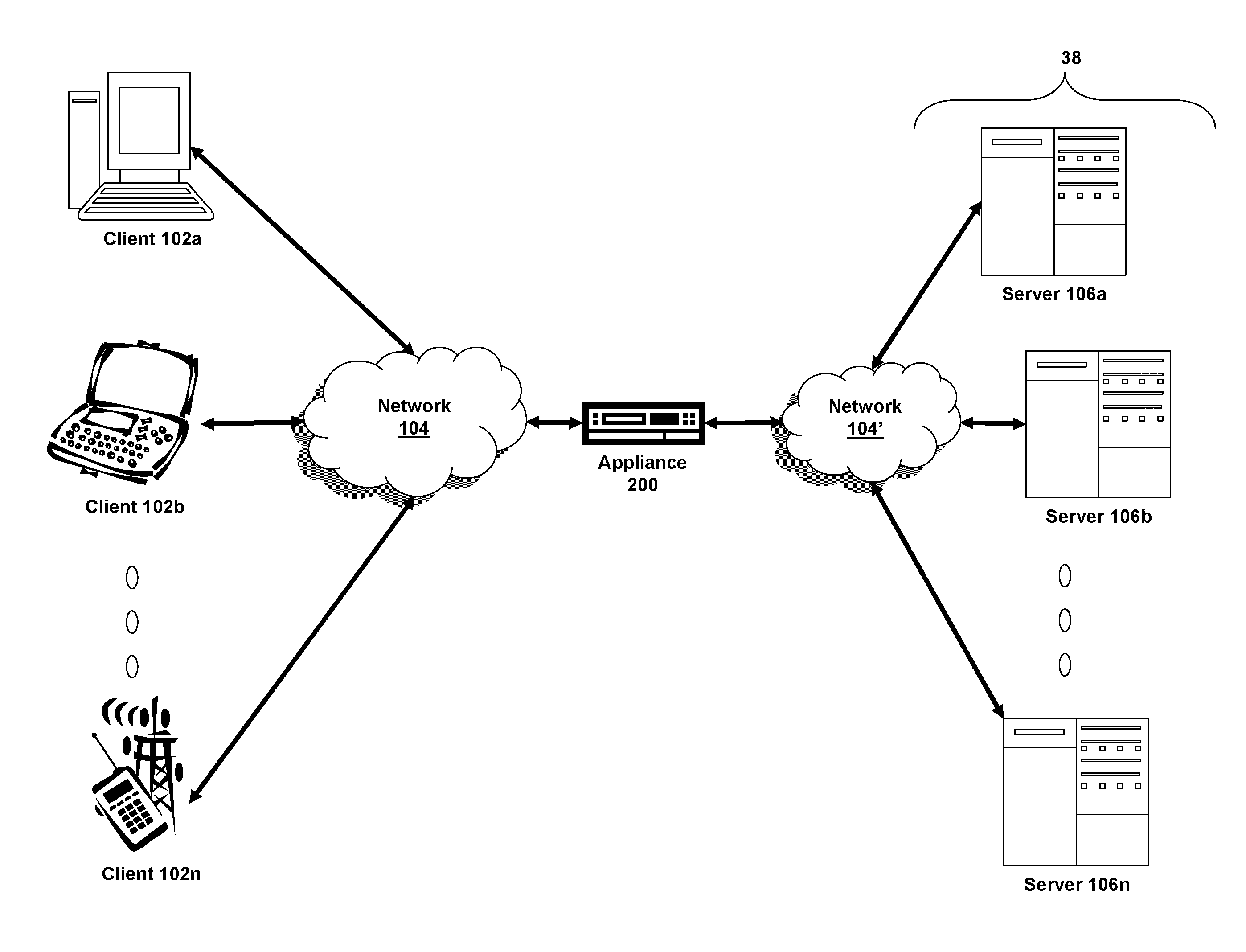

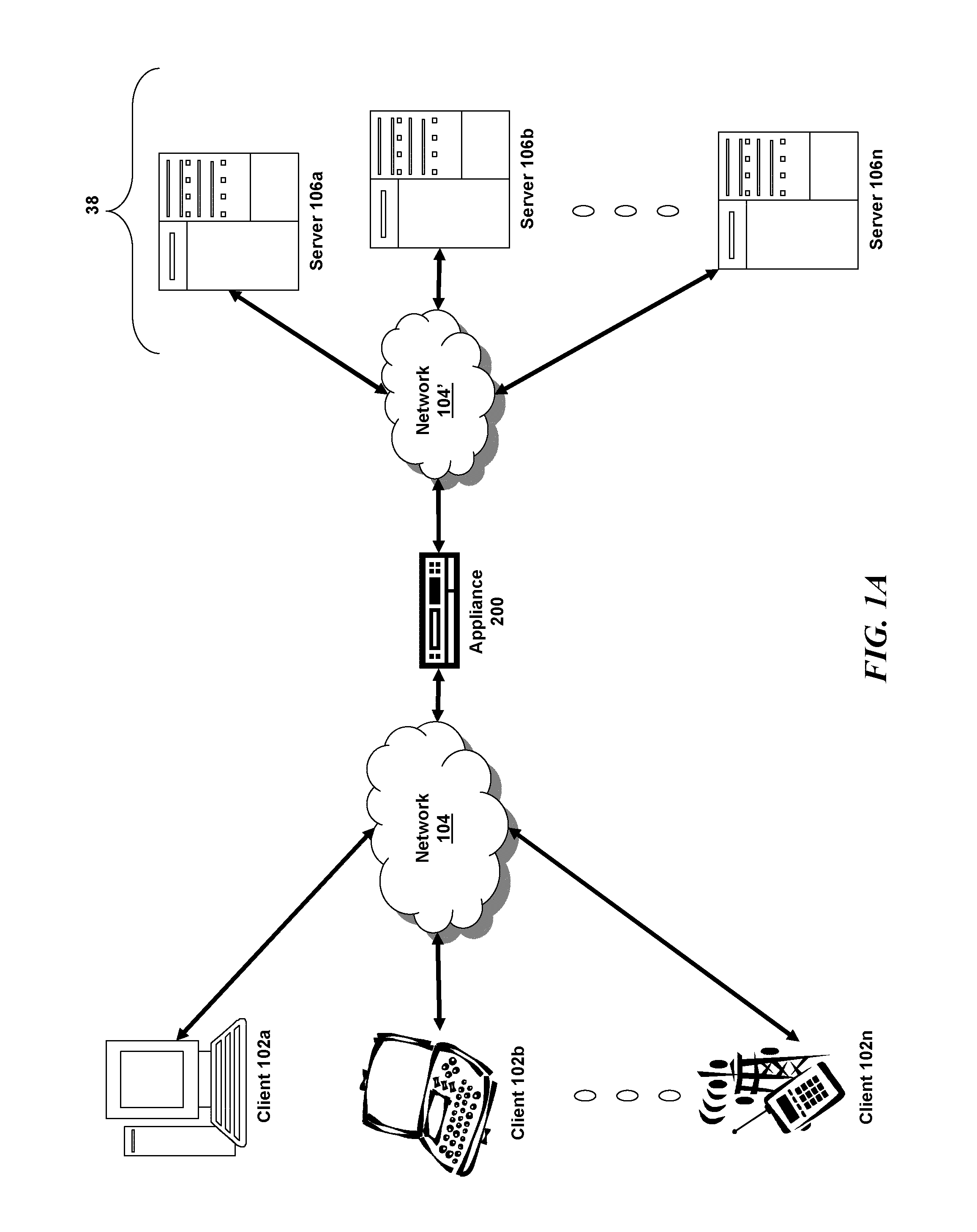

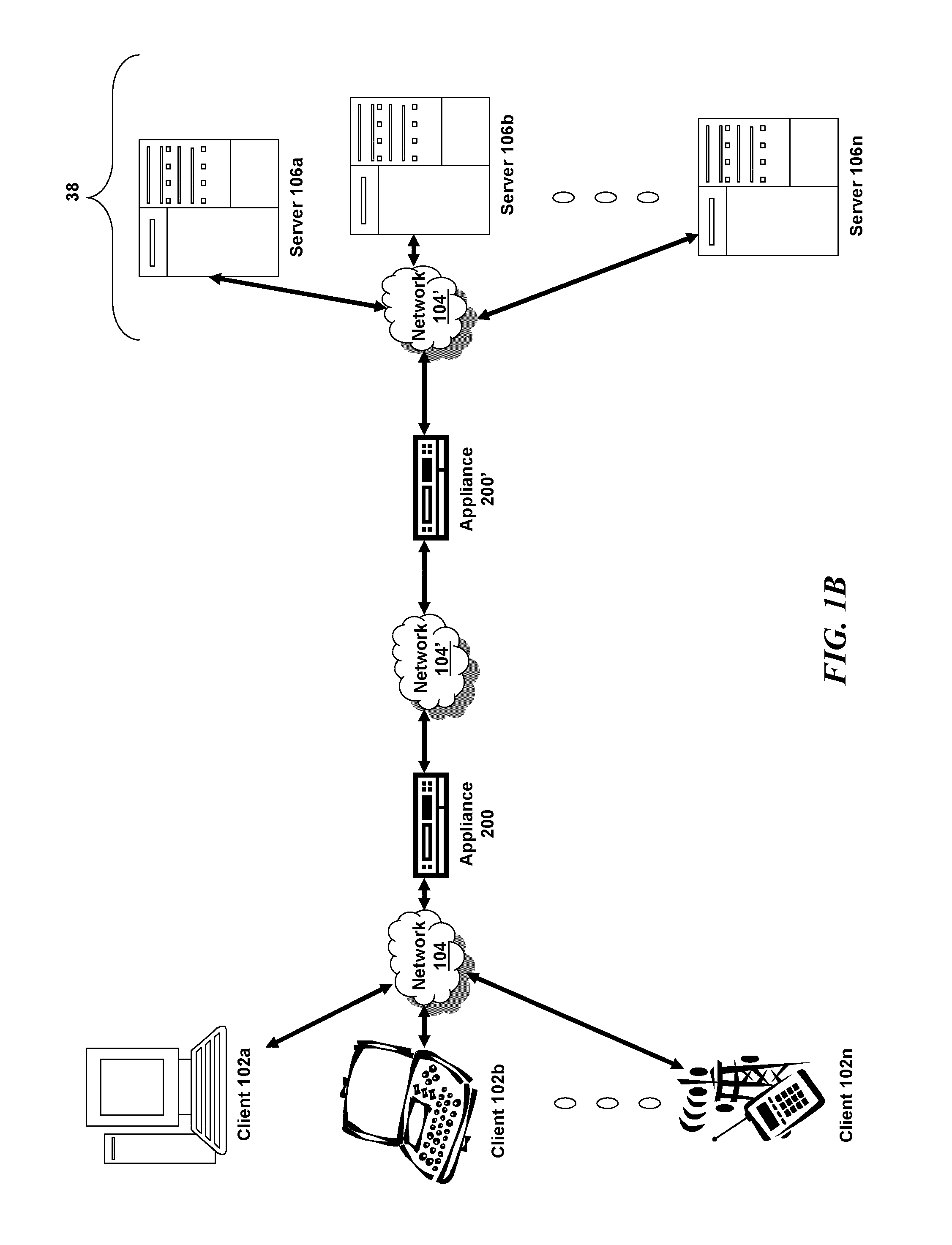

The present invention is directed towards systems and methods for determining failure in and controlling access to a shared resource in a multi-core system. In some embodiments of a multi-core system, individual cores may share the same resource. Additionally, the resource may occasionally fail or need to be reset, and the period during which the resource is being reset may be non-instantaneous. In an embodiment without coordination between the cores, one core experiencing a failure may reset the resource. During the period in which the resource is resetting, another core may interpret the reset as a failure and reset the resource. As more cores interpret the resets as failures, they will trigger resets, quickly resulting in the resource being constantly reset and unavailable. Thus, in some embodiments, a coordination system may be utilized to determine failure of a shared resource and control resets and access to the shared resource.

Owner:CITRIX SYST INC

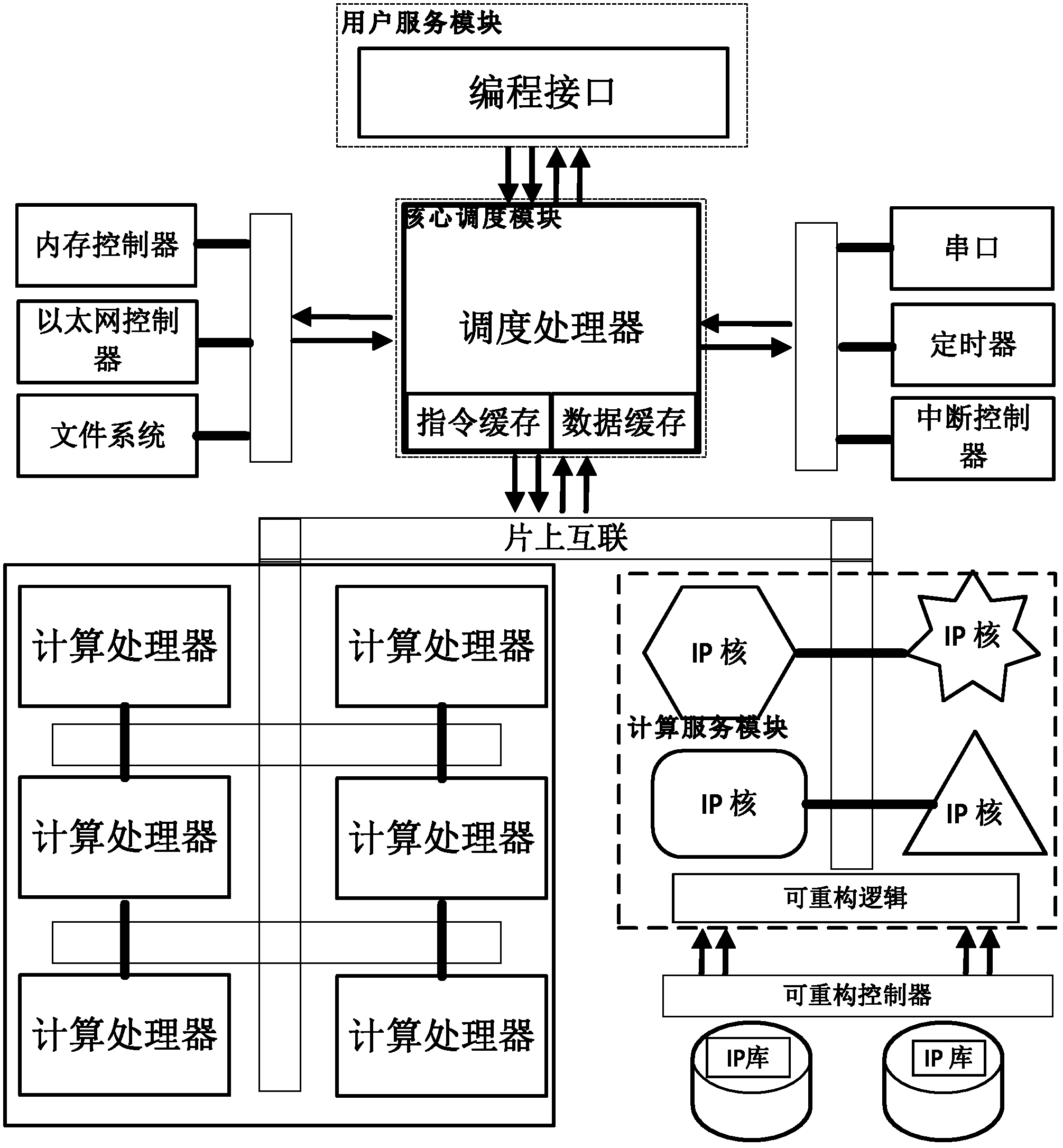

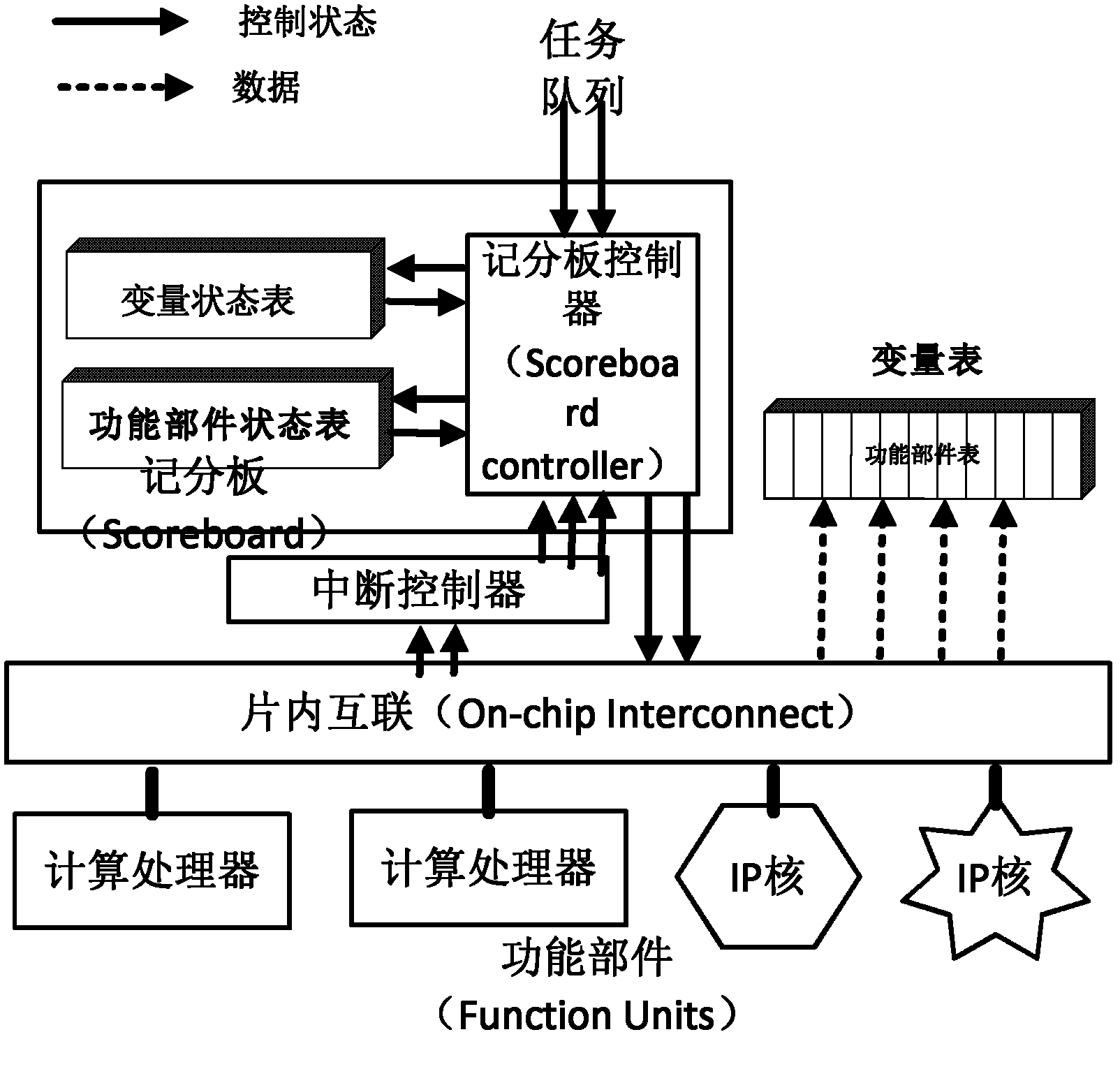

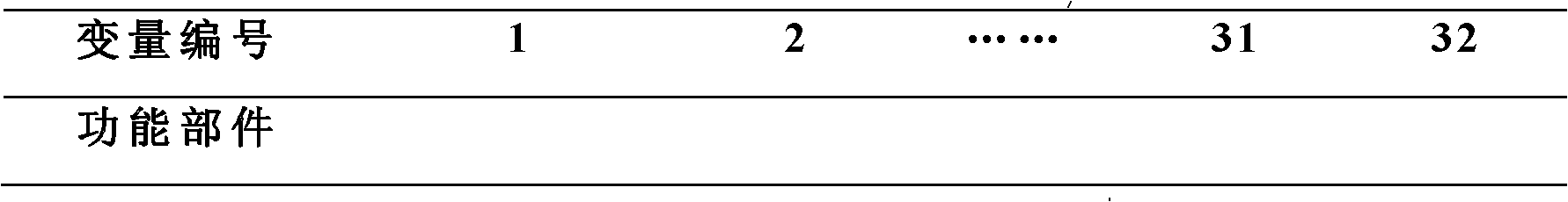

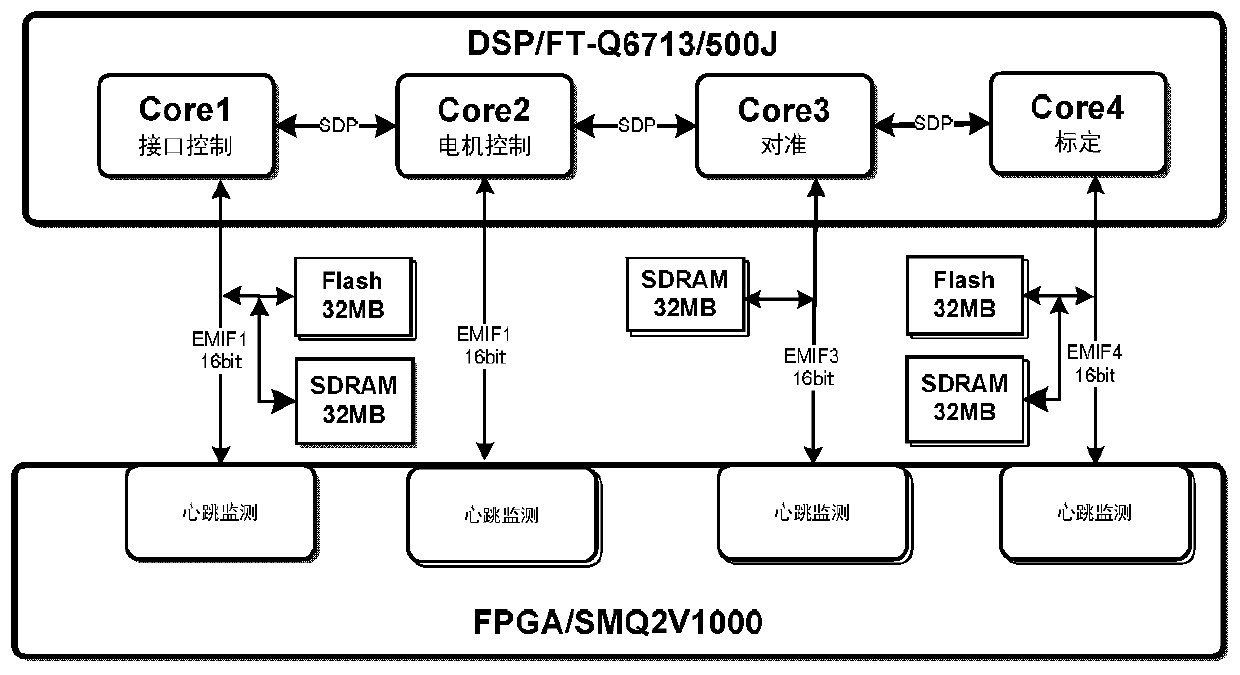

Scheduling system and scheduling execution method of multi-core heterogeneous system on chip

ActiveCN102360309AEliminate spurious correlationImprove throughputResource allocationData dependenceMulticore computing

The invention discloses a scheduling system and a scheduling execution method of a multi-core heterogeneous system on chip. The scheduling system comprises a user service module which provides tasks needed to be executed and is suitable for a plurality of heterogeneous software and hardware, and a plurality of computing service modules for executing a plurality of tasks on a multi-core computing platform on chip; the scheduling system is characterized in that a core scheduling module is arranged between the user service module and the computing service modules, and the core scheduling module is used for accepting a task request of the user service module, recording and judging a data dependence relation among different tasks to schedule the task request to different computing service modules for execution in parallel; the computing service modules are packaged as IP (Internet Protocol) cores, and realize dynamic loading of the IP cores via a reconfigurable controller; and the computing service modules are in on chip interconnections with a plurality of computing processors of the multi-core heterogeneous system on chip, and accept instructions of the core scheduling module to execute different types of computing tasks. The scheduling system improves the platform throughput rate and the system performance by monitoring the relativity of the tasks and executing automatic parallelization in the running process.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

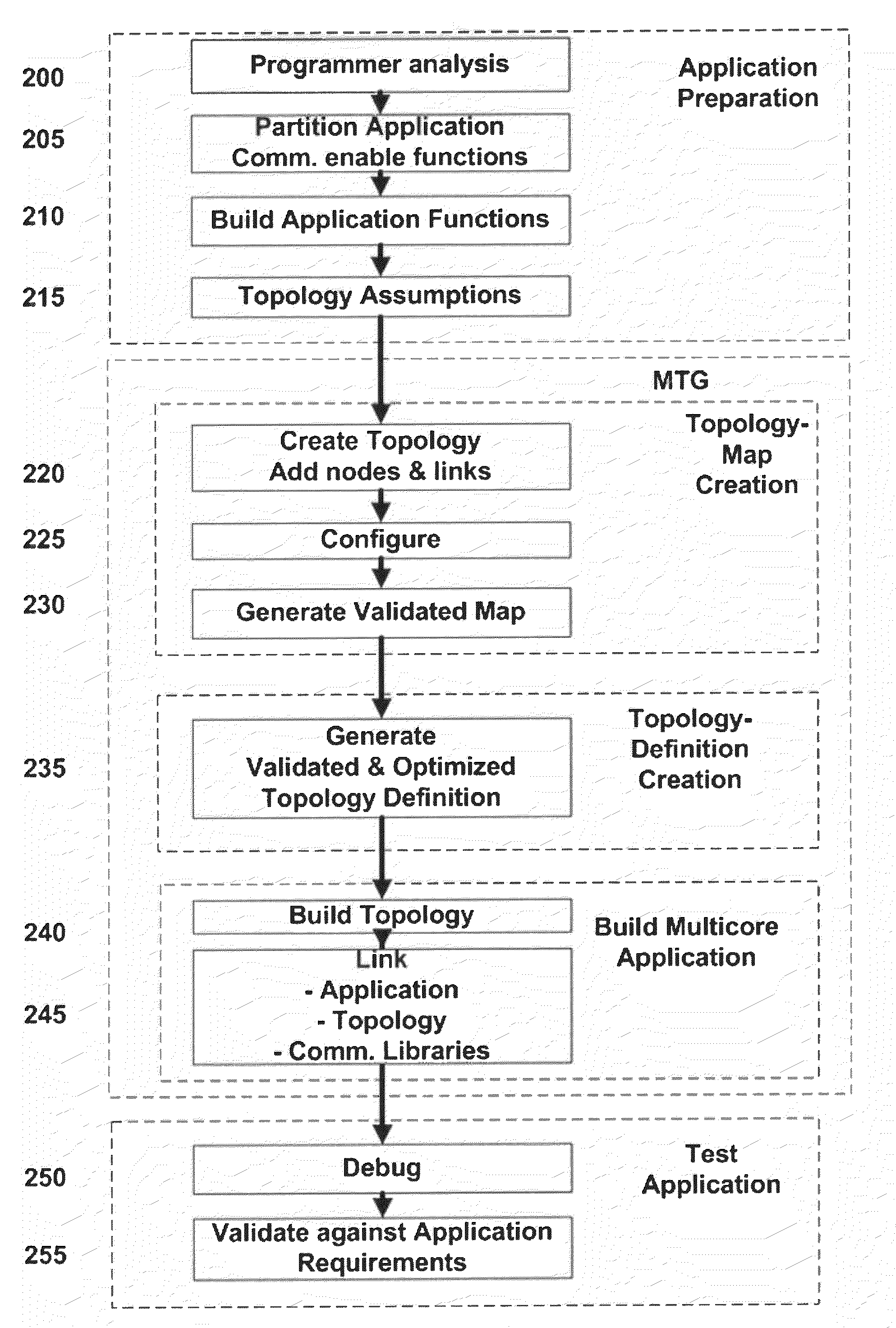

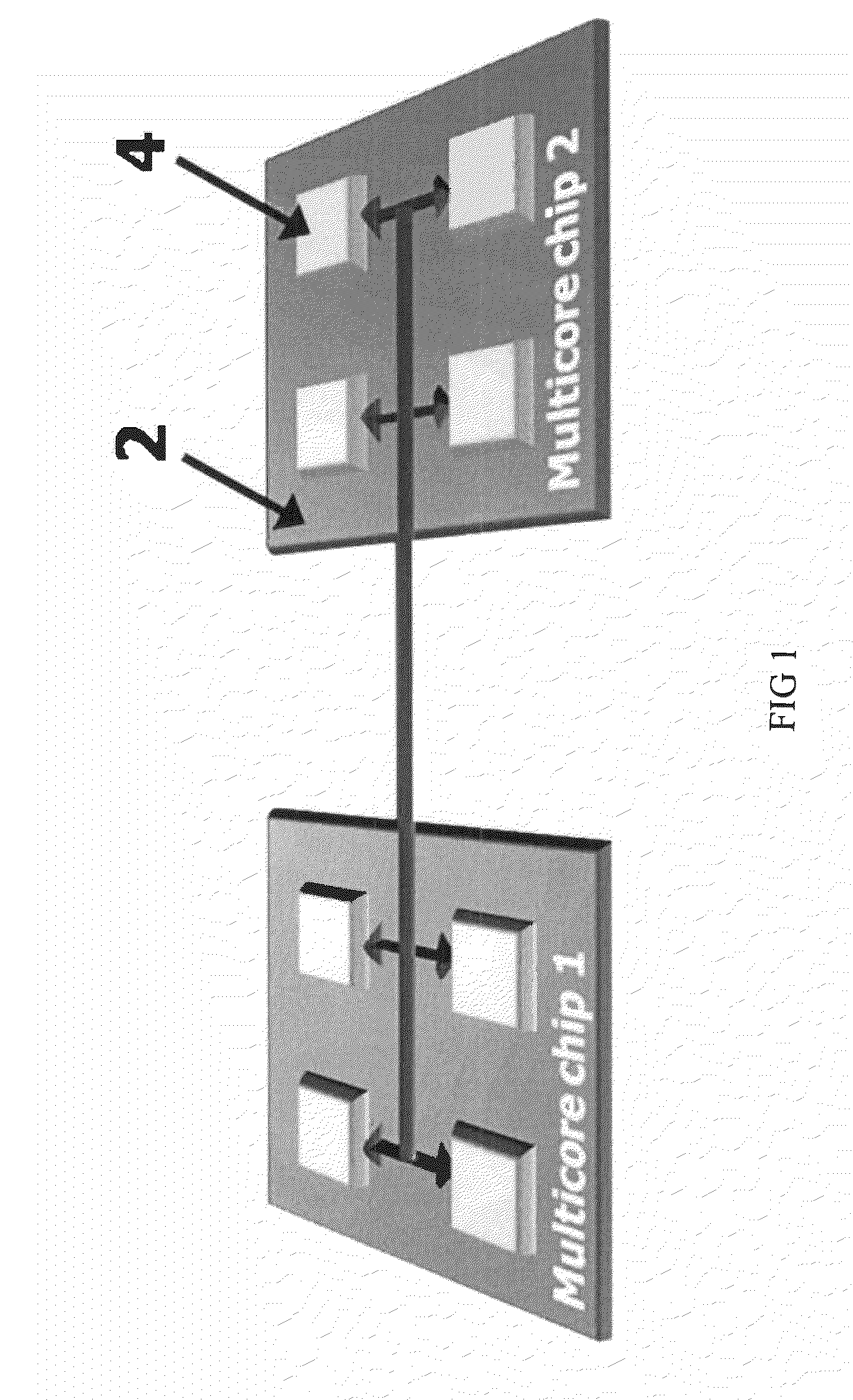

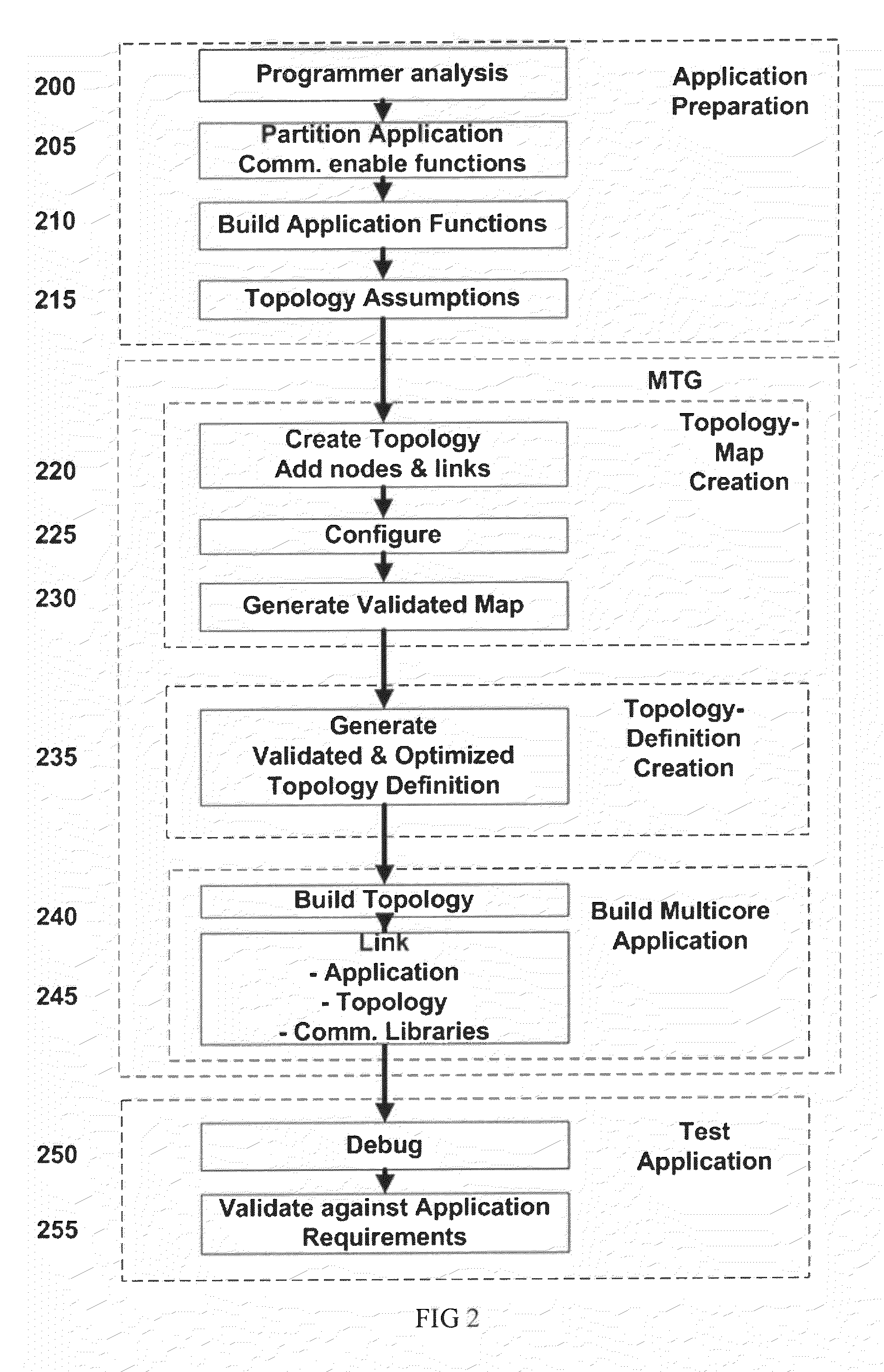

Apparatus & associated methodology of generating a multi-core communications topology

ActiveUS20100235847A1Multiprogramming arrangementsInput/output processes for data processingParallel computingDocument handling

An apparatus and associated method of generating a multi-core communication topology. The topology corresponding to a predetermined number of cores of a multi-core computer, is generated with an application programming device. A number of nodes are described for mapping to the predetermined number of available cores of the multi-core communication topology. Properties of each of the number of nodes are specified. Communication between each of the nodes of the multi-core communication topology is specified using a dedicated multi-core communication library of an electronic memory of the application programming device. A validated output file is generated for the multi-core topology at the application programming device. The output file to is processed to generate a multi-core communication capable executable application program interface (API) for the multi-core computer.

Owner:POLYCORE SOFTWARE

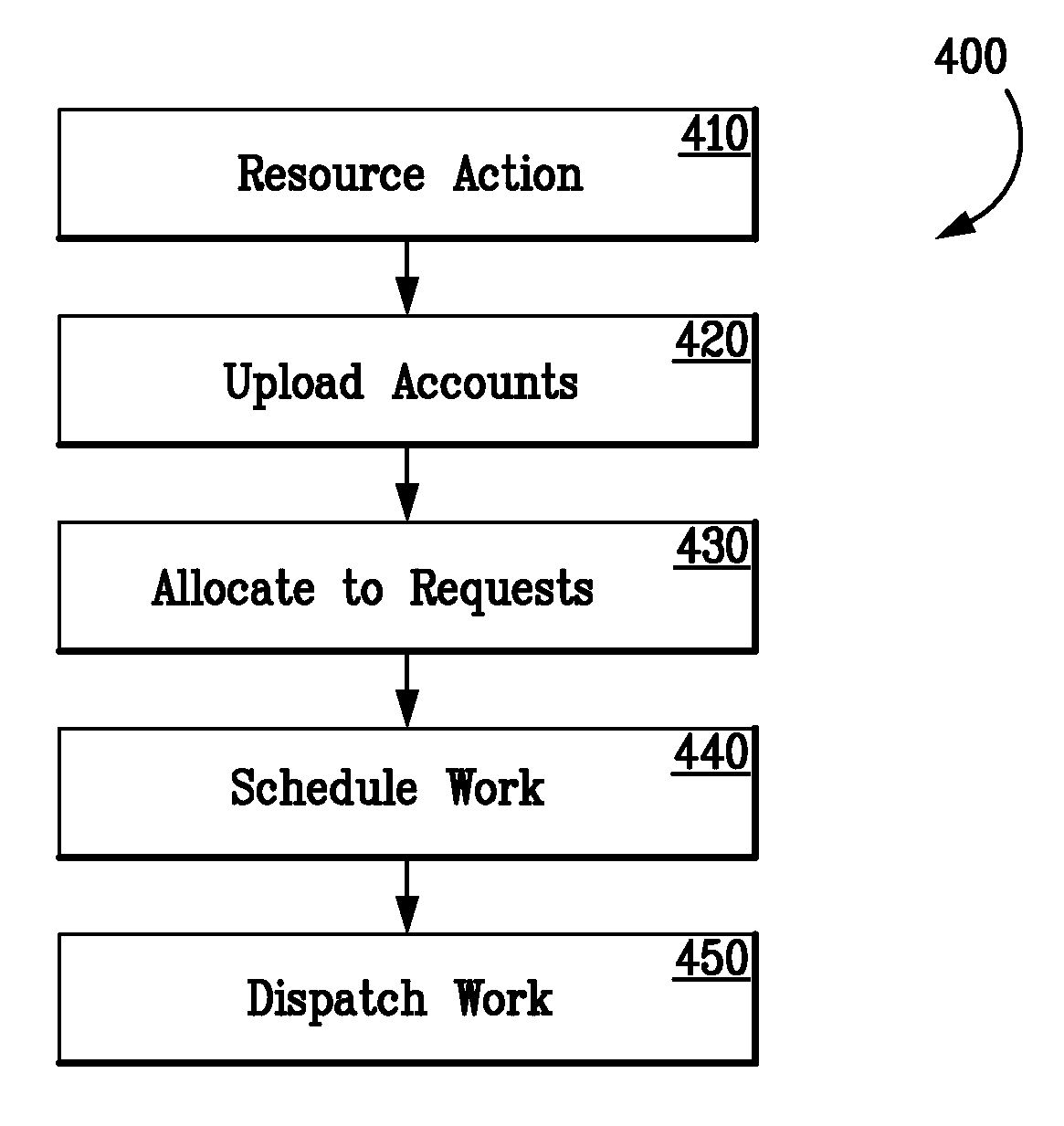

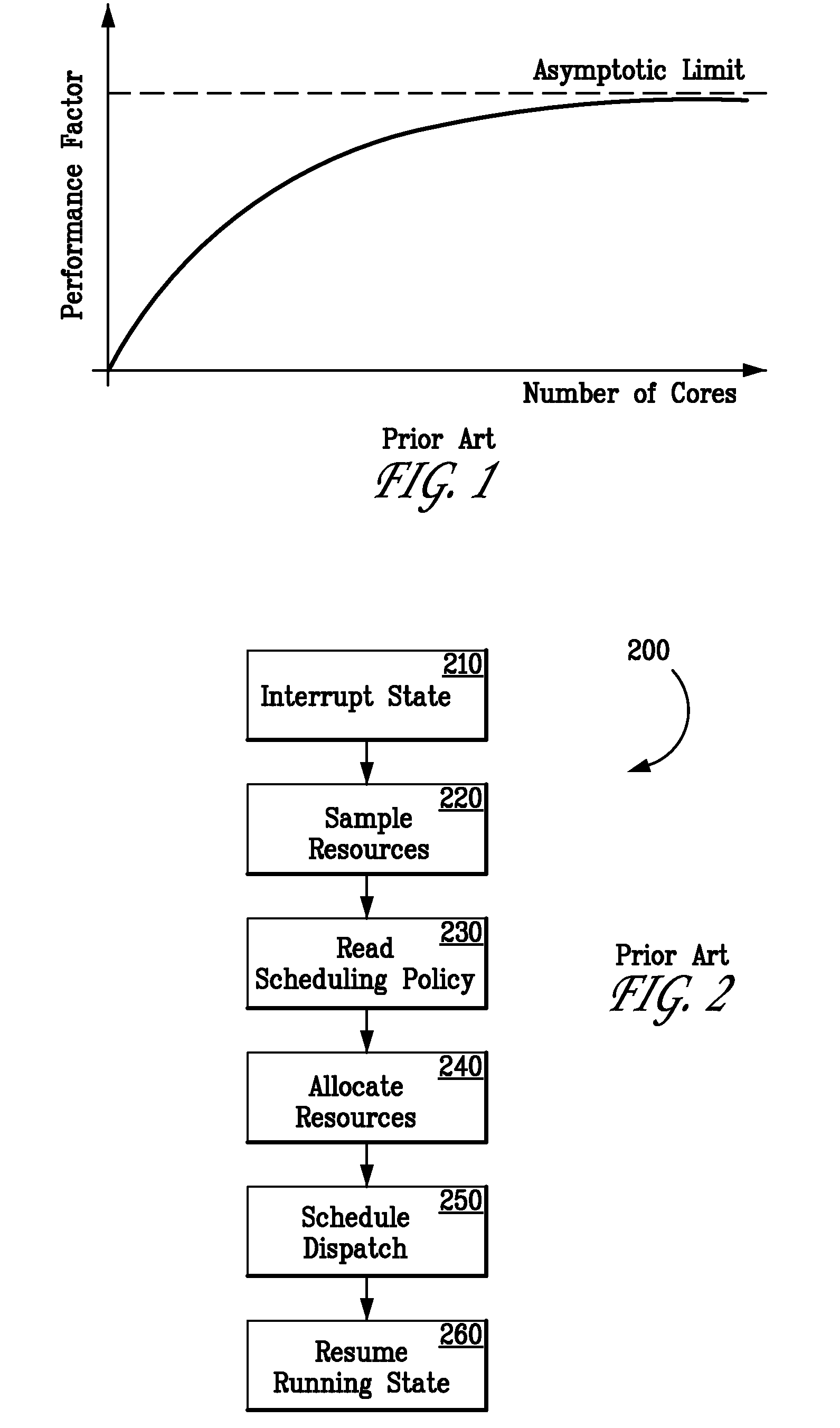

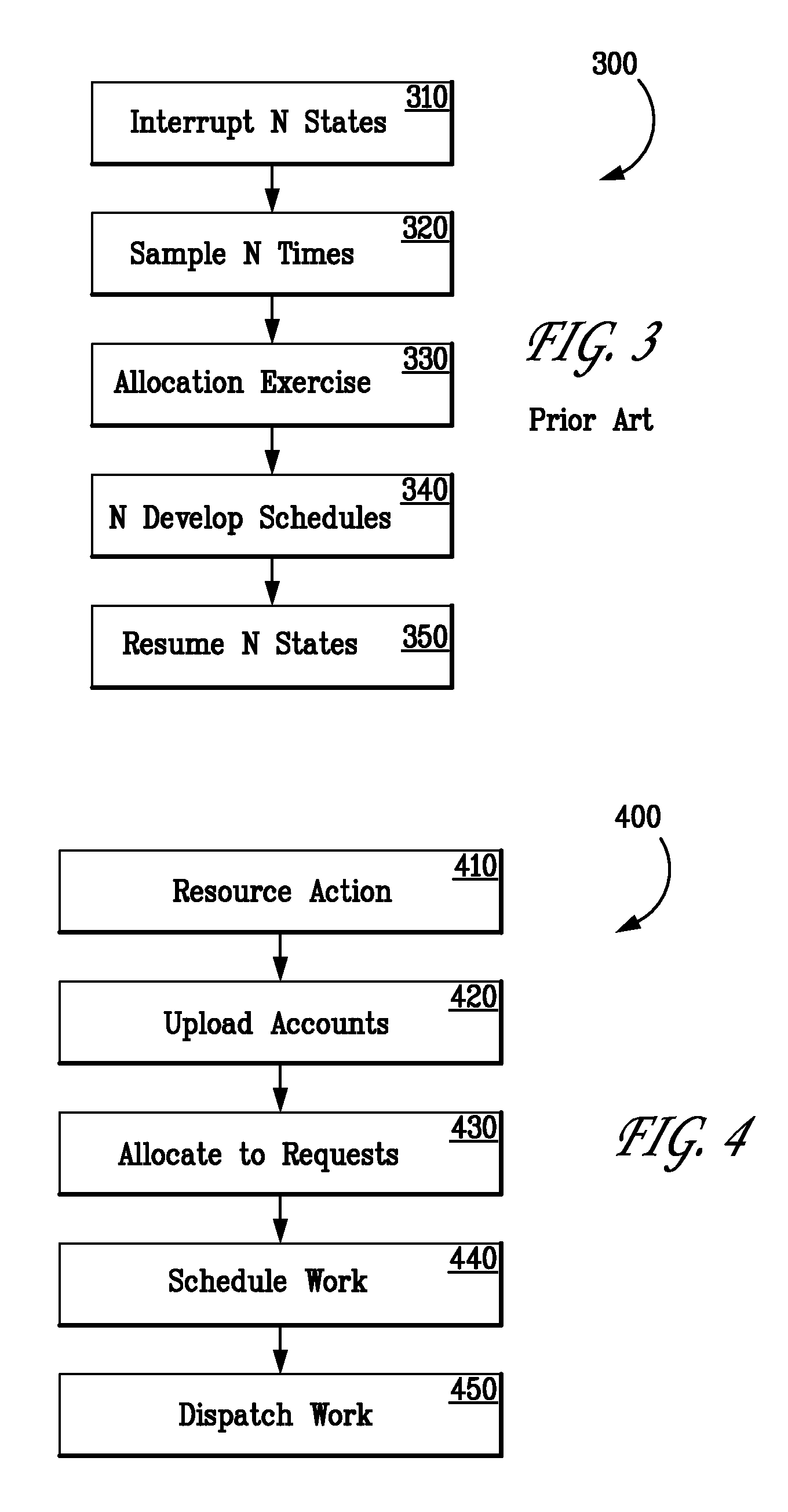

Scalable Work Load Management on Multi-Core Computer Systems

InactiveUS20100043008A1Minimize impactIncrease the number ofMultiprogramming arrangementsMemory systemsProcessing coreAmdahl's law

Embodiments of the presently claimed invention minimize the effect of Amdahl's Law with respect to multi-core processor technologies. This scheme is asynchronous across all of the cores of a processing system and is completely independent of other cores and other work units running on those cores. This scheme occurs on an as needed and just in time basis. As a result, the constraints of Amdahl's Law do not apply to a scheduling algorithm and the design is linearly scalable with the number of processing cores with no degradation due to the effects of serialization.

Owner:EXLUDUS TECH

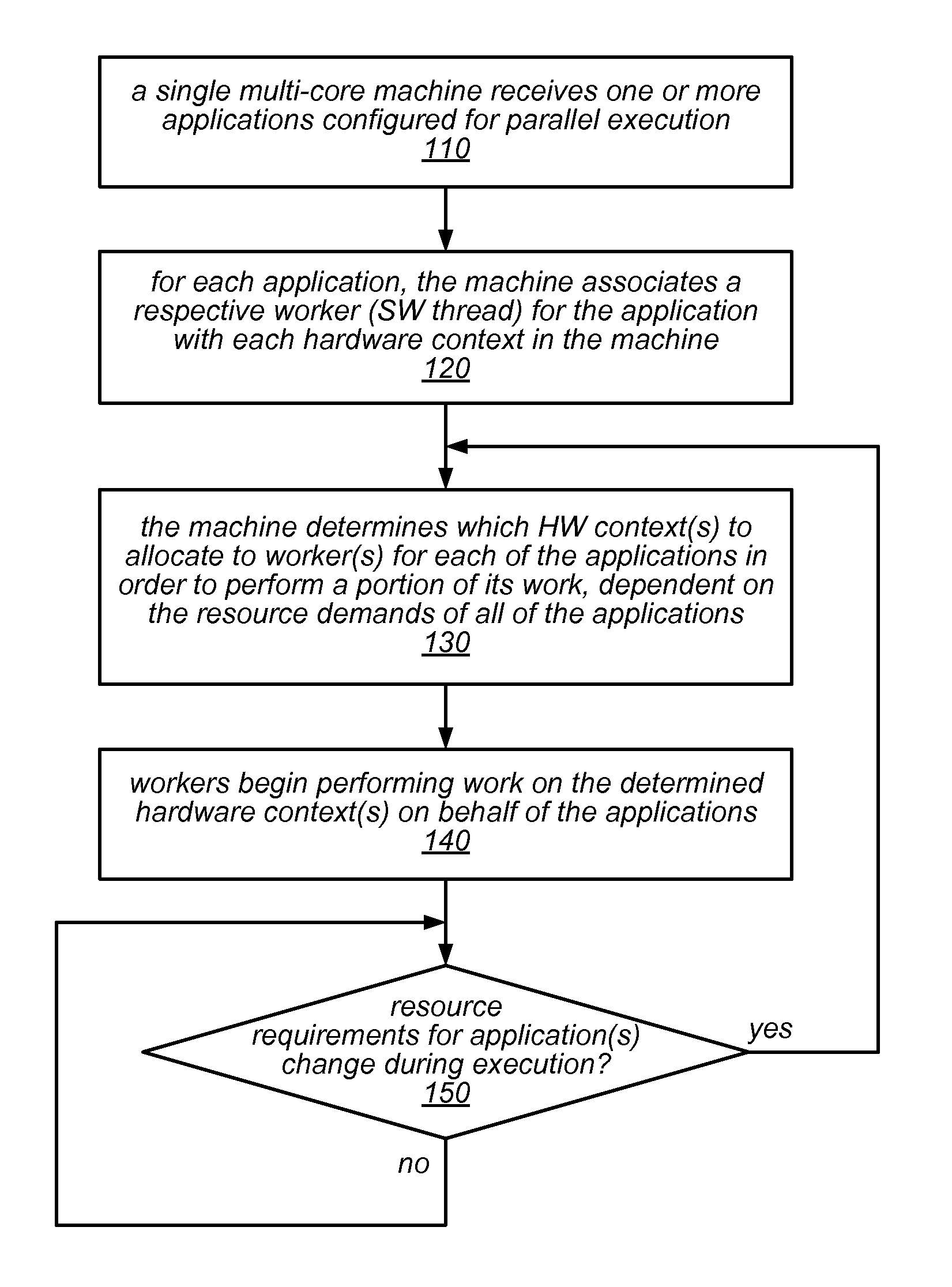

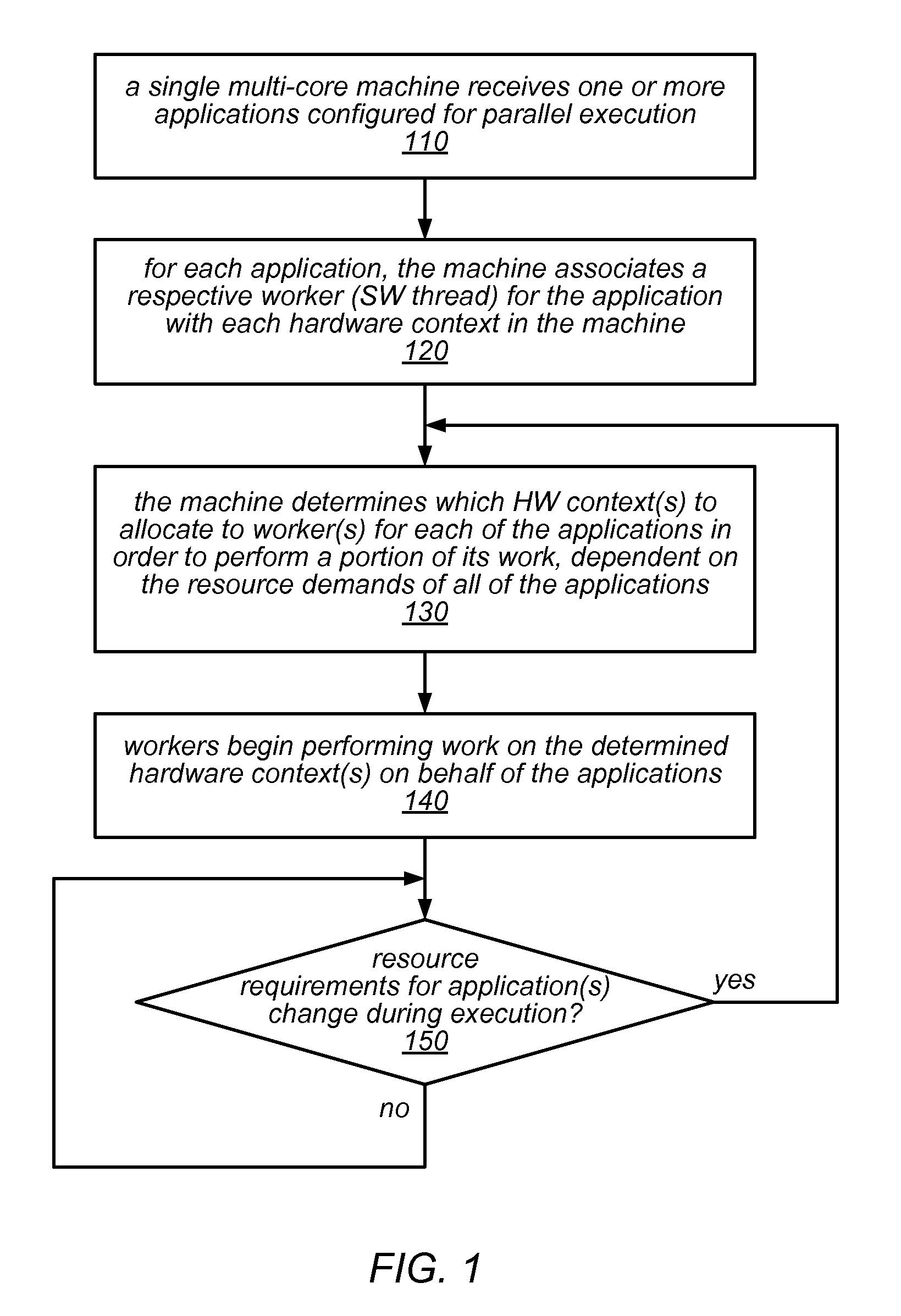

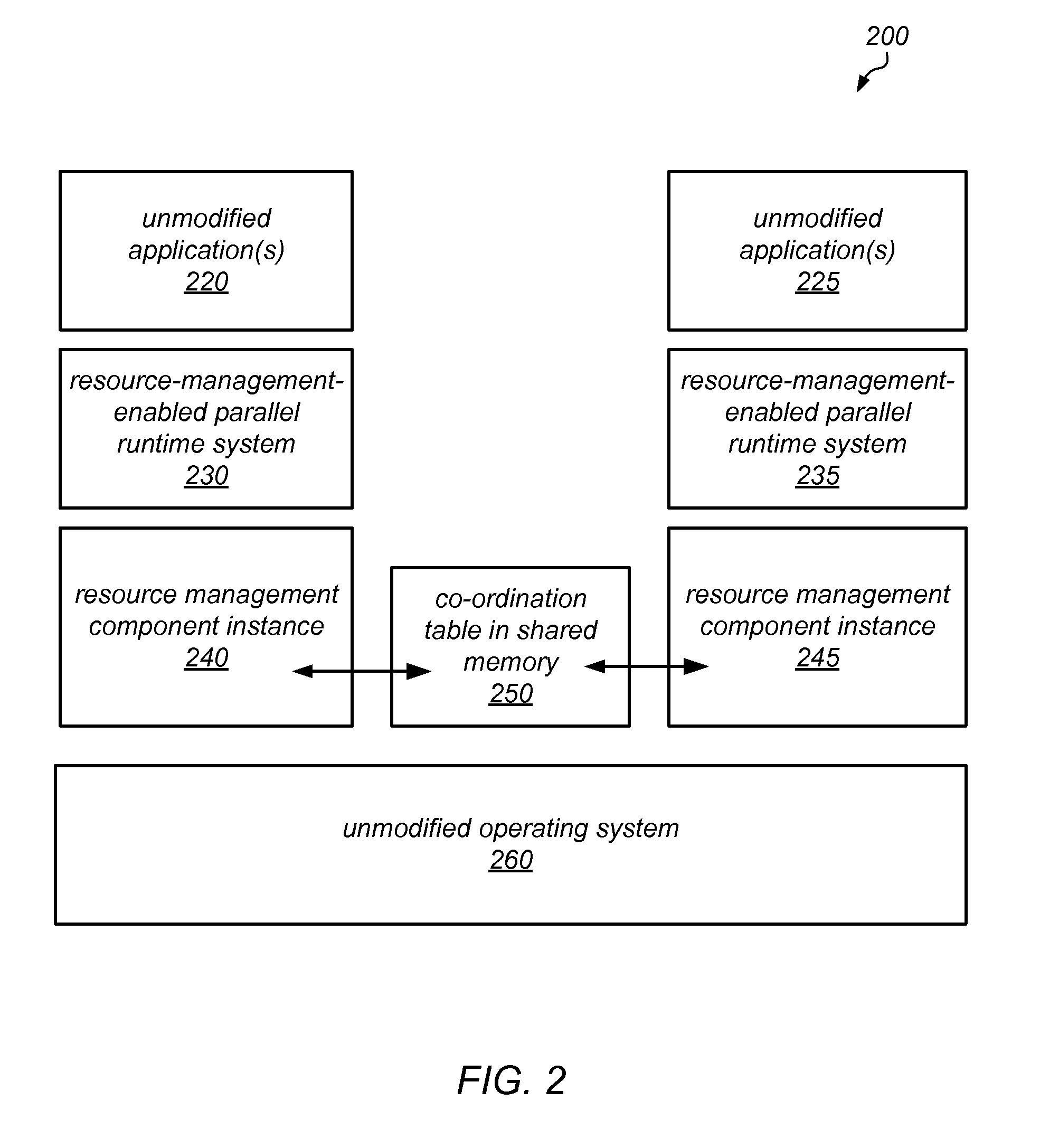

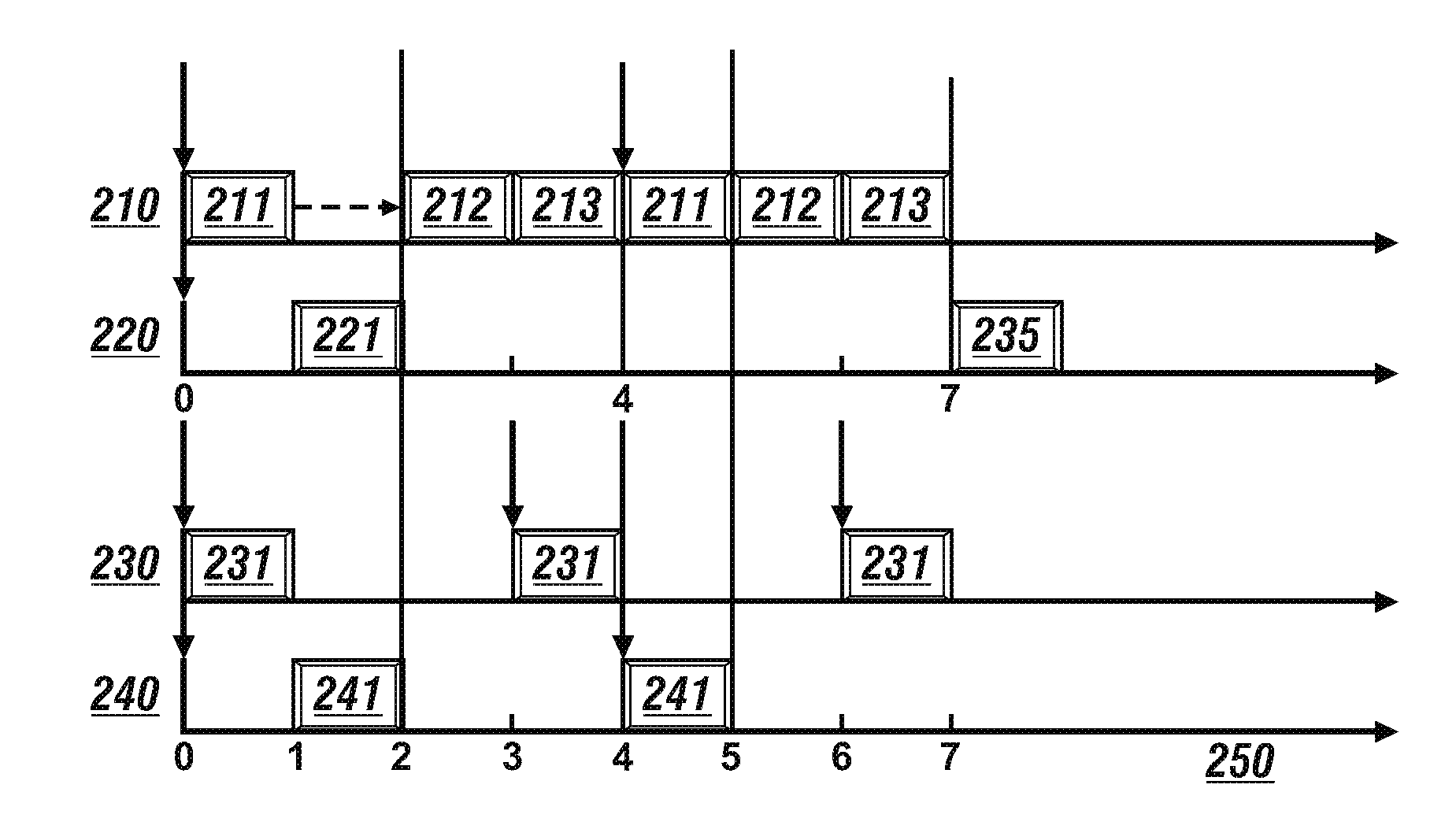

Dynamic Co-Scheduling of Hardware Contexts for Parallel Runtime Systems on Shared Machines

ActiveUS20150339158A1Reduce load imbalanceEasy to useProgram initiation/switchingResource allocationOperational systemResource management

Multi-core computers may implement a resource management layer between the operating system and resource-management-enabled parallel runtime systems. The resource management components and runtime systems may collectively implement dynamic co-scheduling of hardware contexts when executing multiple parallel applications, using a spatial scheduling policy that grants high priority to one application per hardware context and a temporal scheduling policy for re-allocating unused hardware contexts. The runtime systems may receive resources on a varying number of hardware contexts as demands of the applications change over time, and the resource management components may co-ordinate to leave one runnable software thread for each hardware context. Periodic check-in operations may be used to determine (at times convenient to the applications) when hardware contexts should be re-allocated. Over-subscription of worker threads may reduce load imbalances between applications. A co-ordination table may store per-hardware-context information about resource demands and allocations.

Owner:ORACLE INT CORP

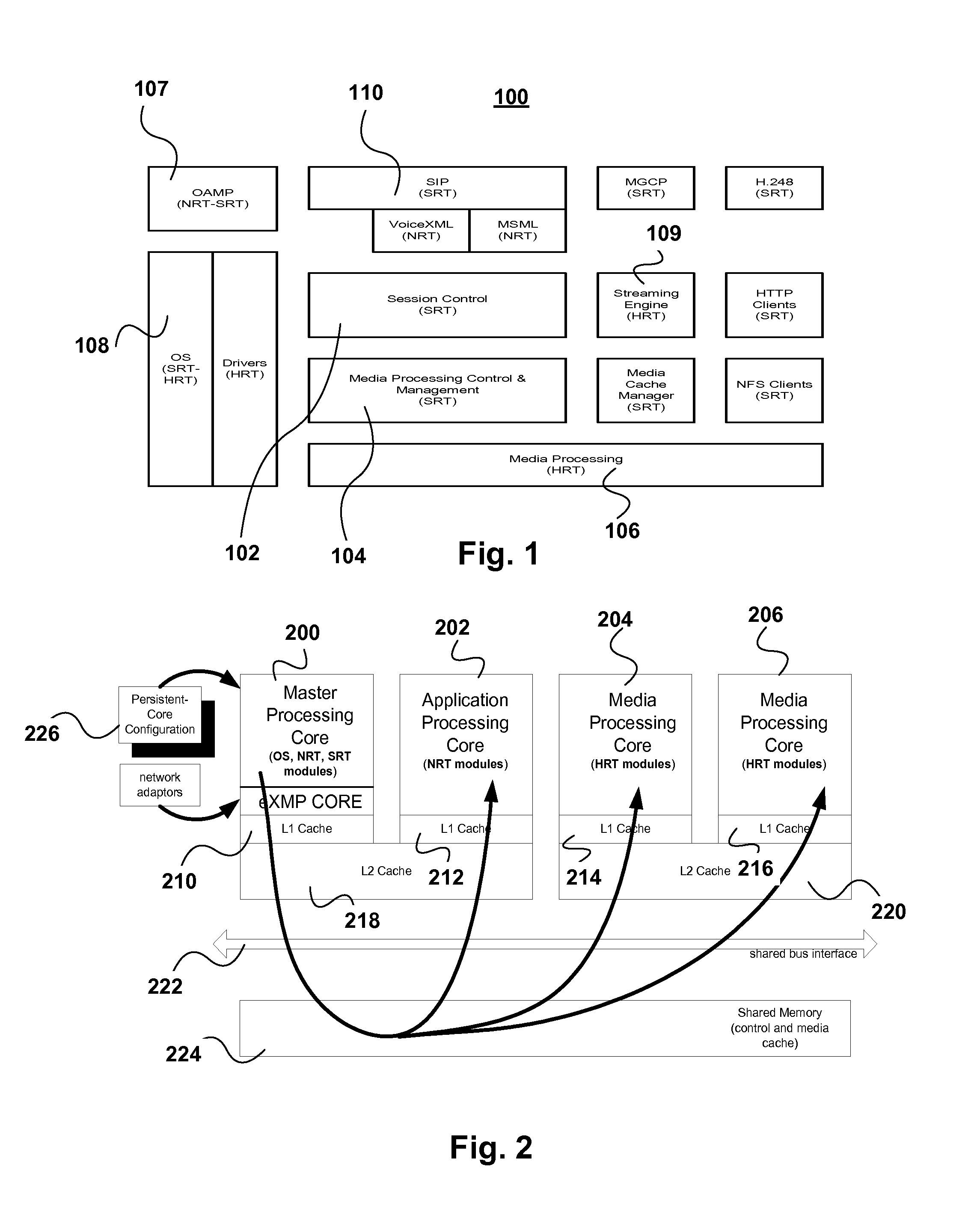

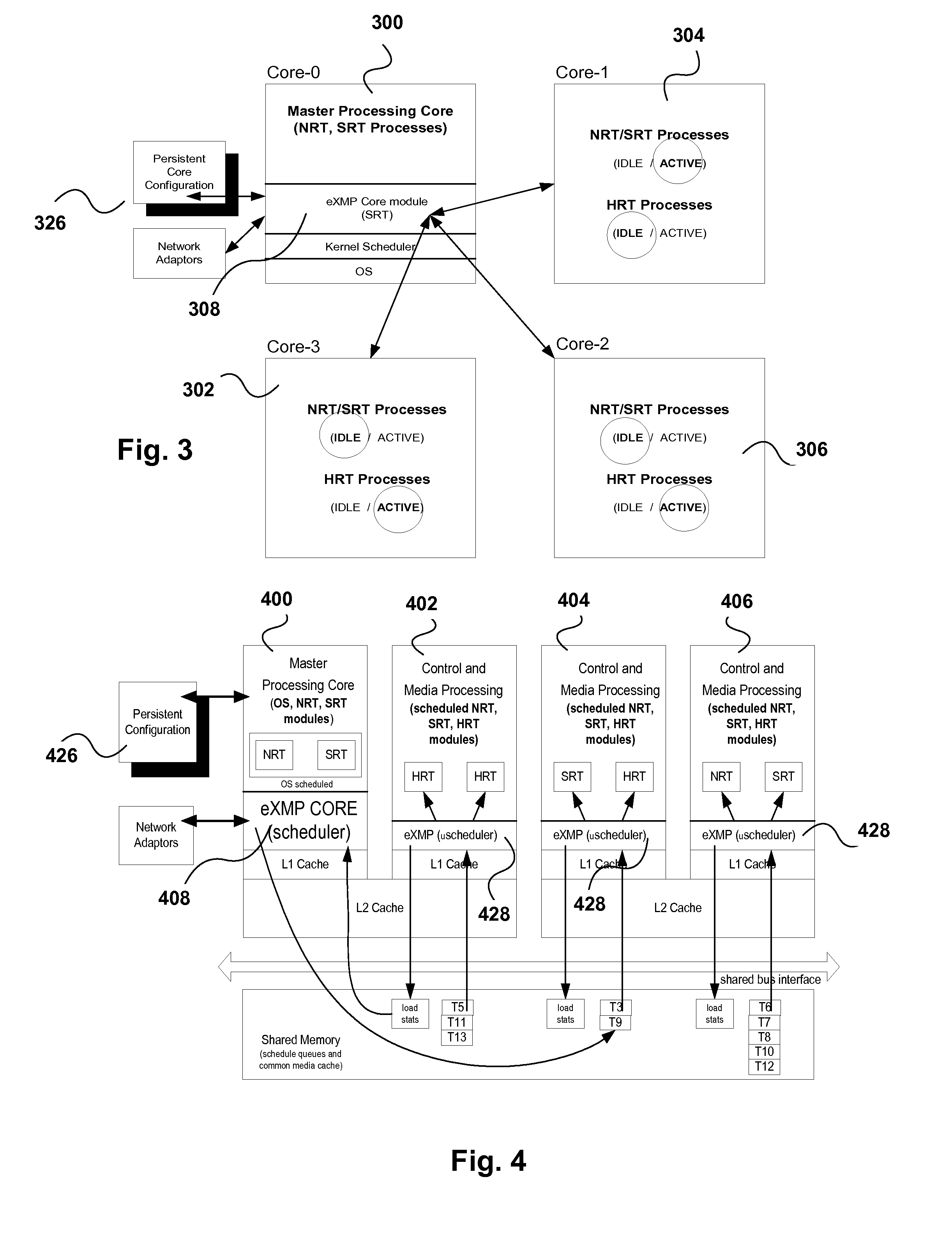

Multimedia processing in parallel multi-core computation architectures

ActiveUS20090083516A1Program control using wired connectionsMultiple digital computer combinationsTime responseMedia server

In a media server for processing data packets, media server functions are implemented by a plurality of modules categorized by real-time response requirements.

Owner:RADISYS CORP

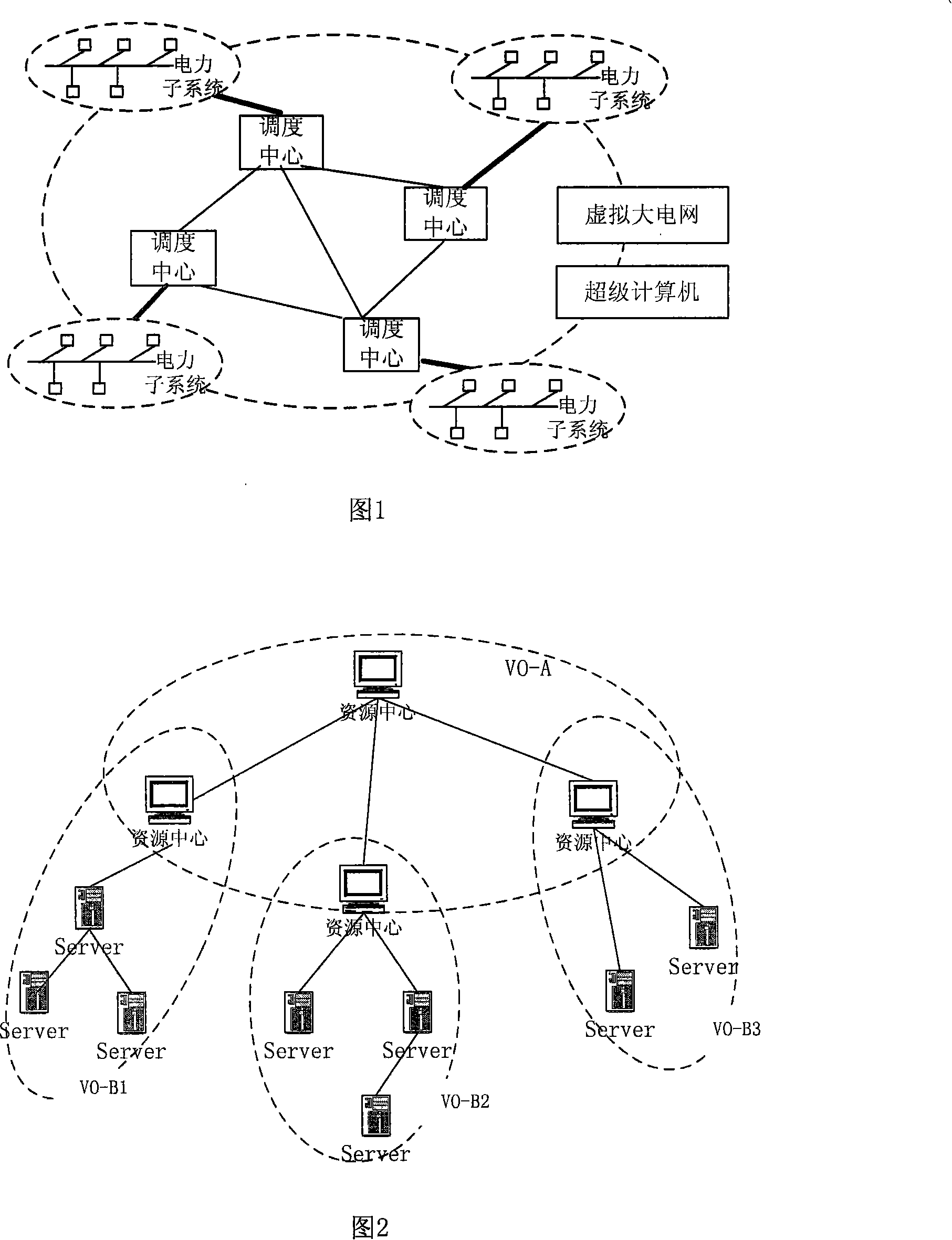

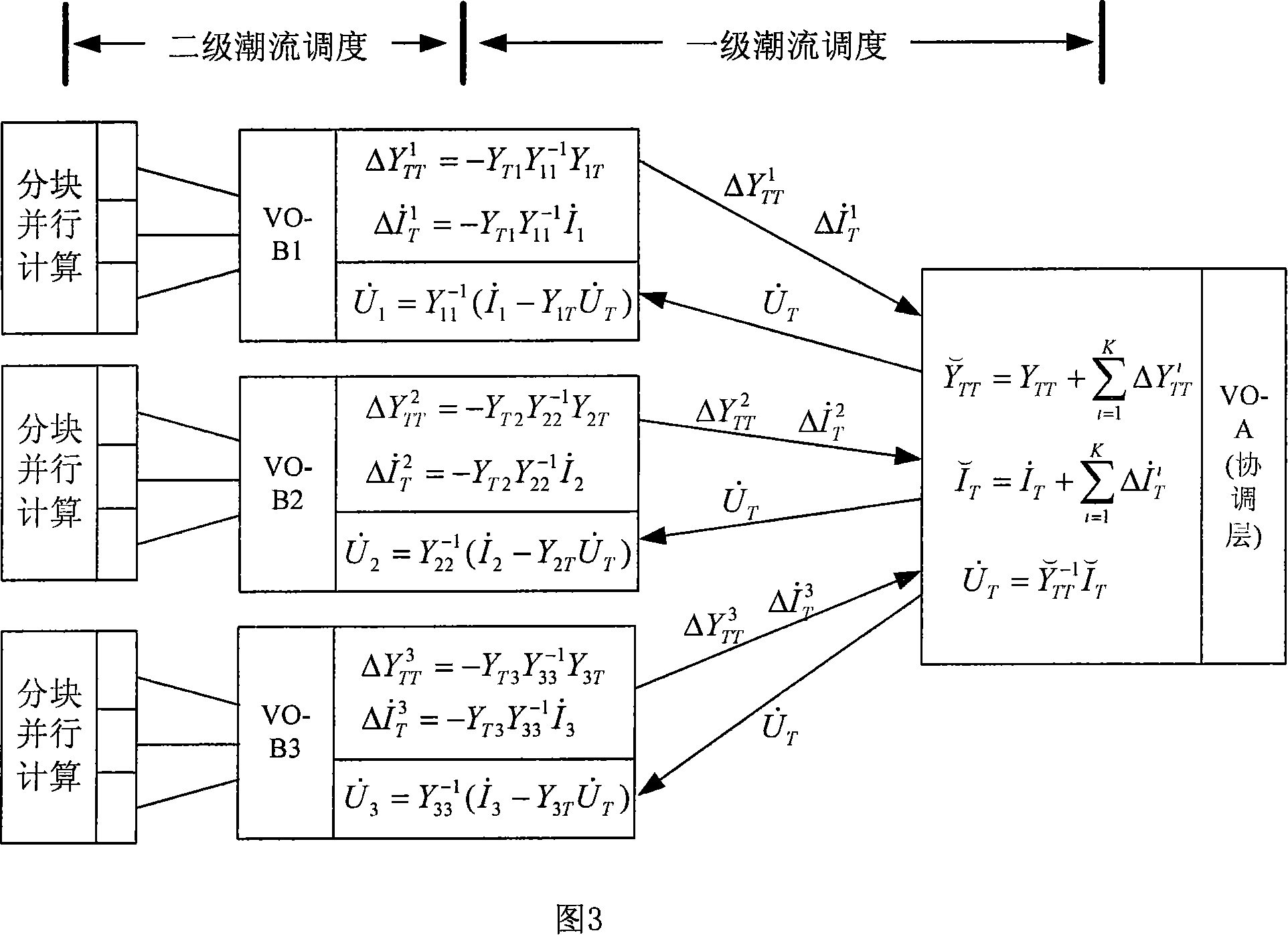

Method for implementing parallel power flow calculation based on multi-core computer in electric grid

The invention discloses a method for realizing parallel load flow computation based on a multi-core computer in power grid. The method comprises two-stage scheduling, wherein the first-stage scheduling realizes division and cooperation of load flow computation task, and the second-stage scheduling performs fine division to the computation task, in the multi-core computer, subtasks can be parallelly calculated, and after several iterative convergences, the computation results are collected and outputted by a coordination layer. The invention adopts the parallel computation and maximally utilizes the computation resource in virtual organizations, so that the computation speed is faster and the cost is lower.

Owner:NANJING UNIV

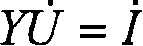

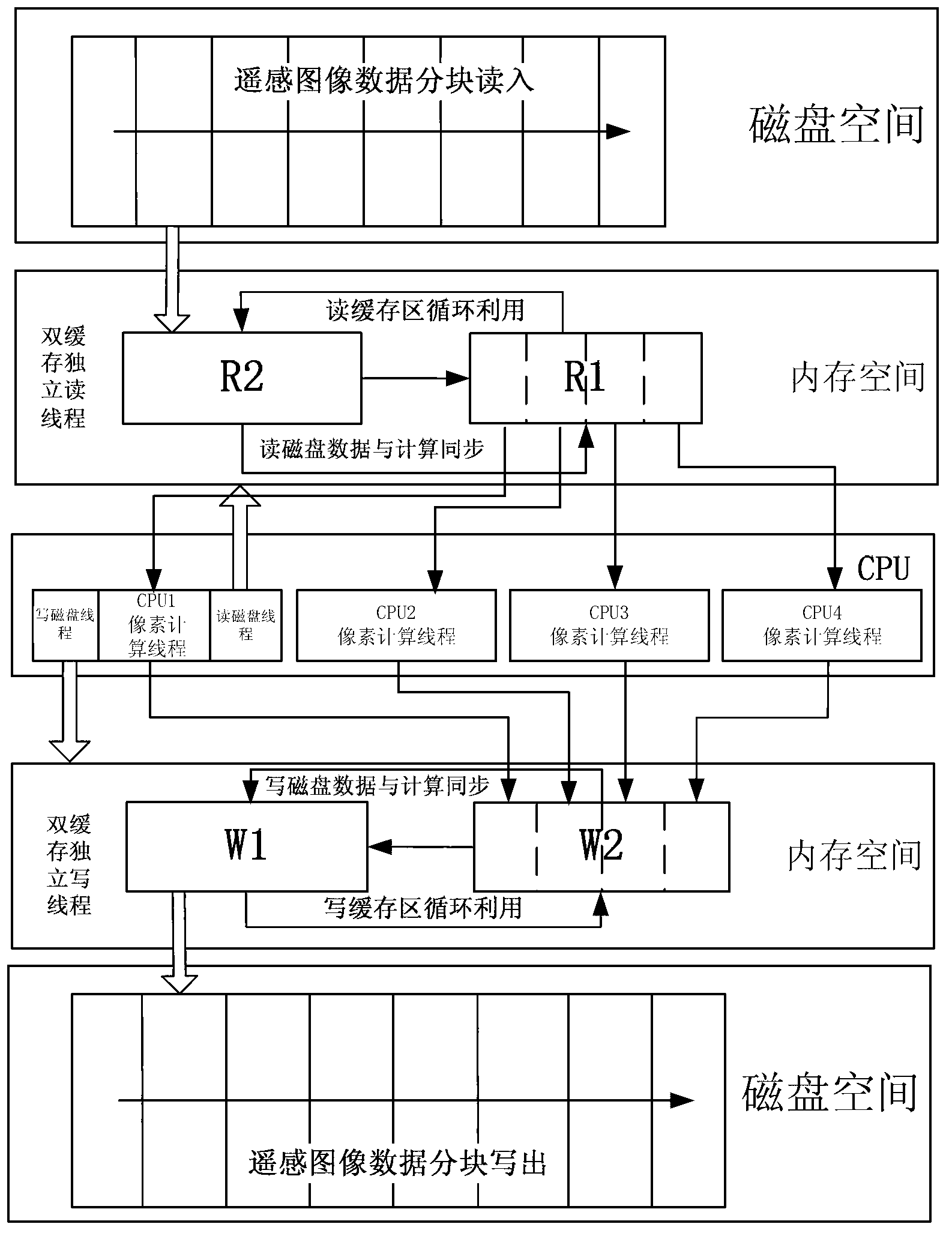

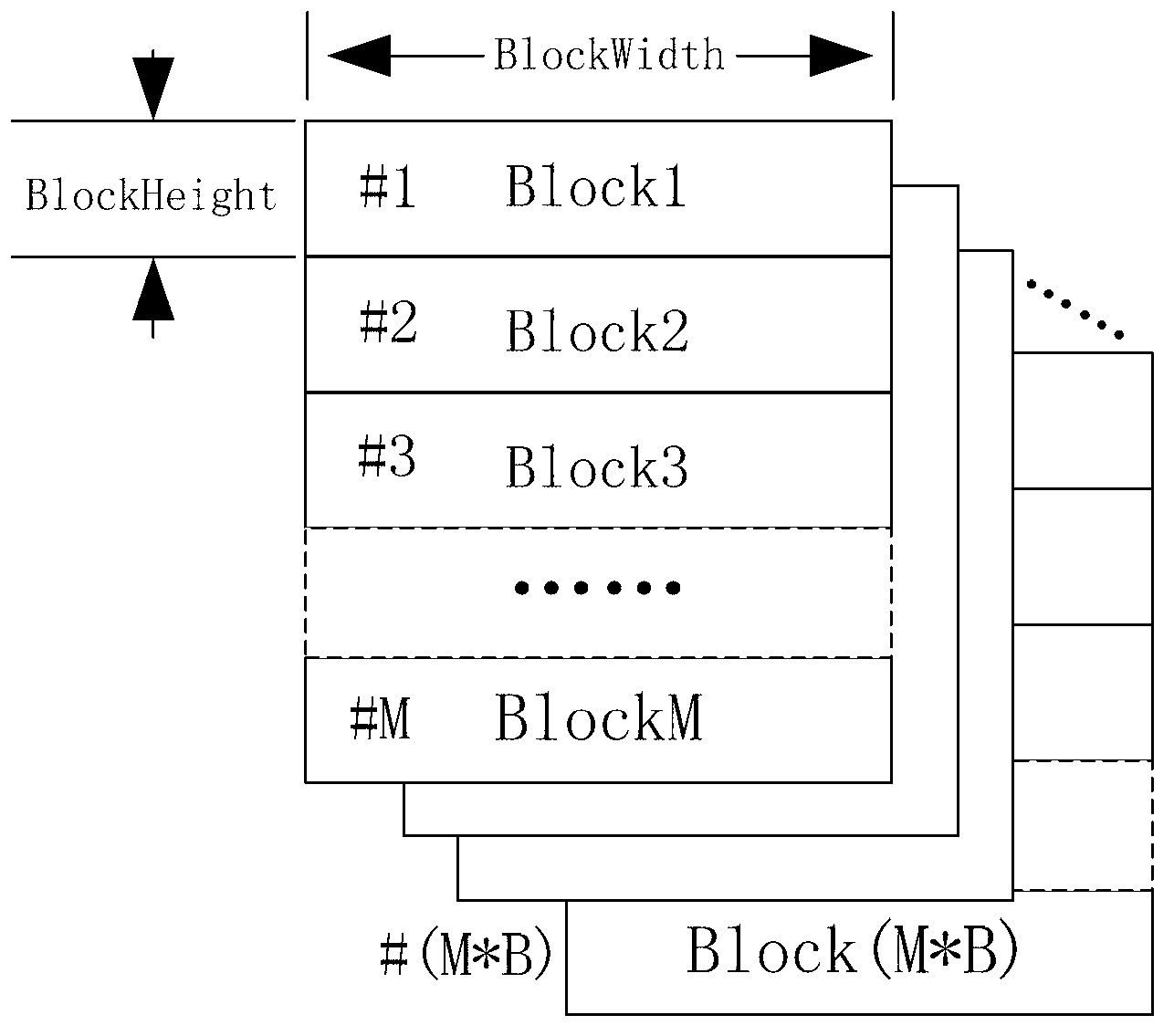

IO (Input Output) double-buffer interactive multicore processing method for remote sensing image

ActiveCN103218174AGuaranteed execution efficiencyImprove resource utilizationInput/output to record carriersConcurrent instruction executionSensing dataResource utilization

The invention discloses an IO (Input Output) double-buffer interactive multicore processing method for a remote sensing image. The method comprises the following steps of determining the quantity of multicore computing threads according to the quantity of CPU (Central Processing Unit) cores of a processing system; determining various data segmentation strategies according to various remote sensing image processing algorithms; starting each remote sensing image processing computing thread, starting to execute the remote sensing image processing algorithms and sending a data access request and an output request during the period; reading or writing in a data request according to the computing threads, starting a reading-writing data thread, reading image data into buffer memories R1 and R2 in order according to a predetermined reading segmentation strategy, and writing processed result data into writing buffers W2 and W1 in order; and destructing the reading-writing double-buffer and ending the reading-writing thread and each computing thread till the completion of the computing process according to the processing algorithms and the stopping of data reading-writing visit. With the adoption of the IO double-buffer interactive multicore processing method for the remote sensing image, the resource utilization rate of a multicore CPU and the efficiency of disk IO visit are improved, and a contradiction between limited memory space and mass remote sensing data processing is solved.

Owner:SPACE STAR TECH CO LTD

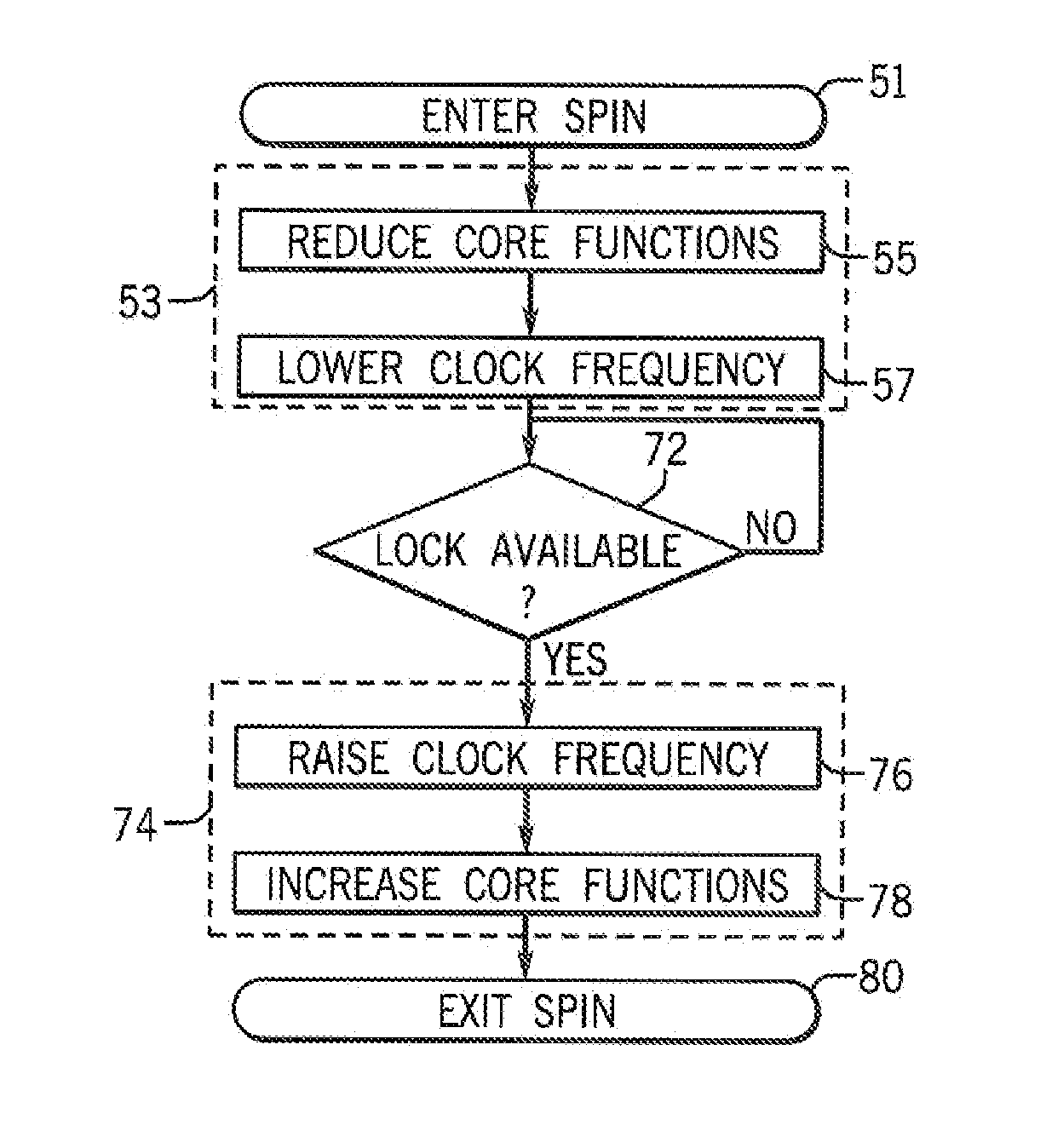

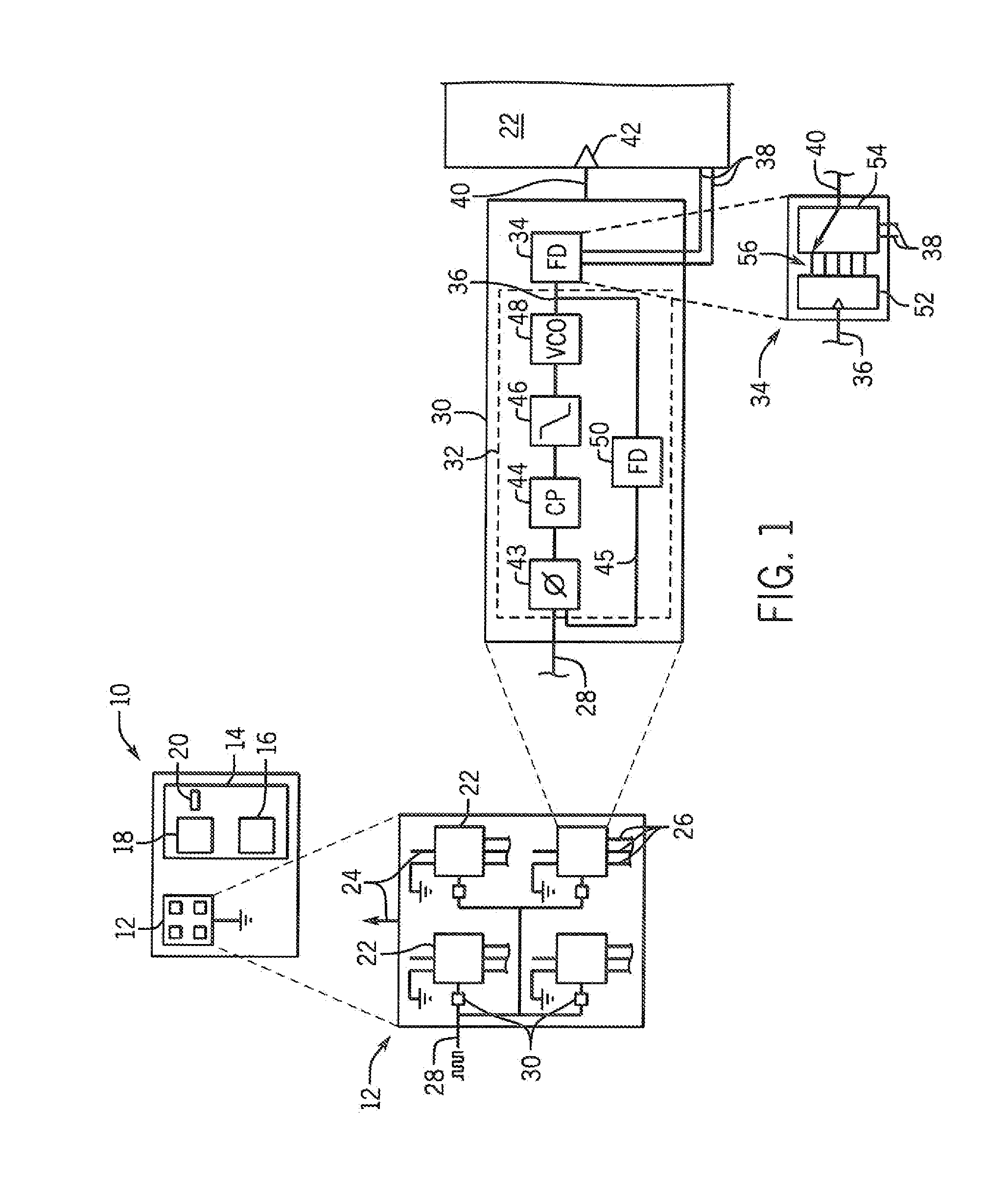

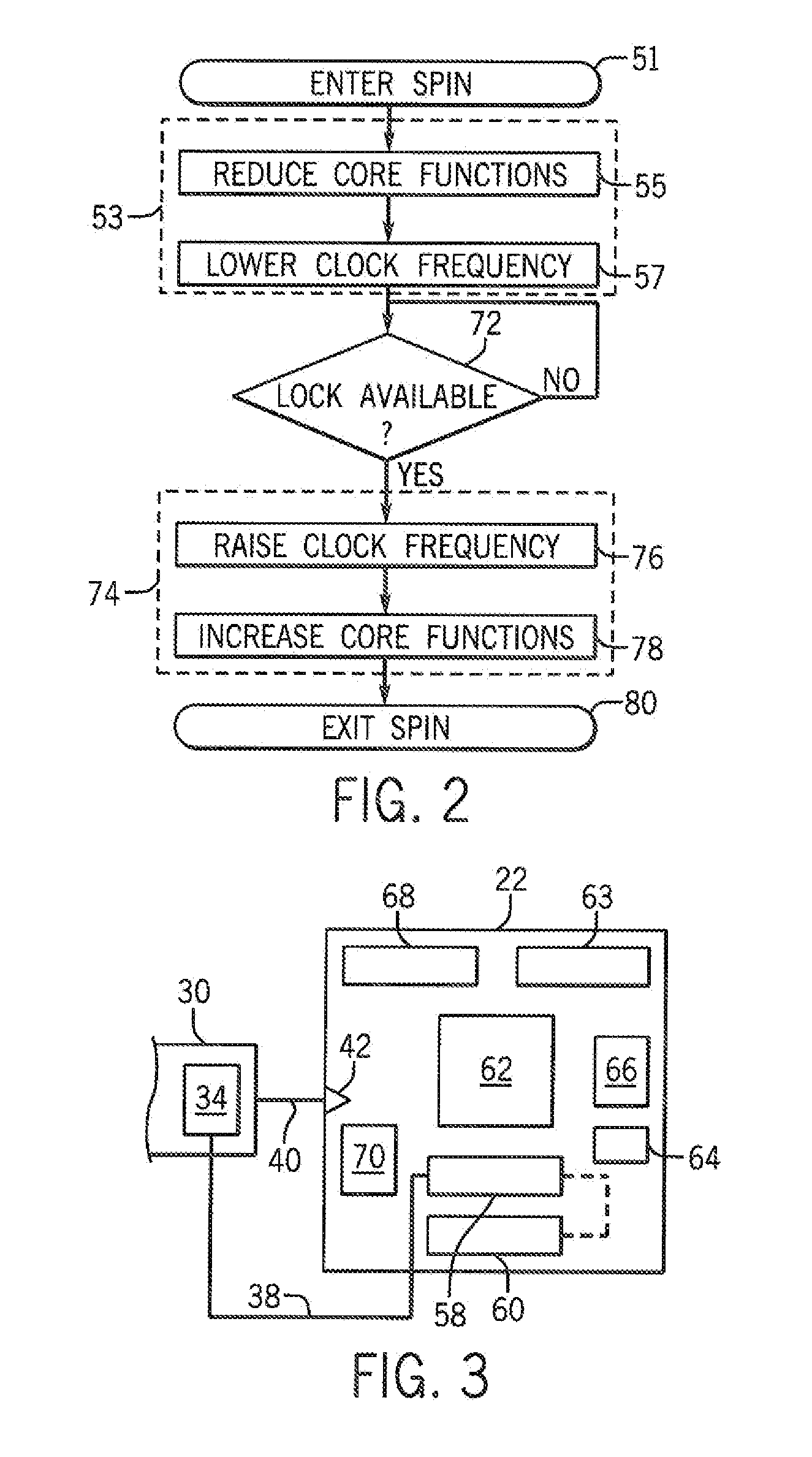

Energy-efficient multicore processor architecture for parallel processing

ActiveUS20150113304A1Reduce functionImprove executionPower supply for data processingEnergy efficient computingMulticore computingParallel processing

A multicore computer architecture provides for clock dividers on each core, the clock dividers capable of providing rapid changes in the clock frequency of the core. The clock dividers are used to reduce the clock frequency of individual cores spinning while waiting for a synchronization instruction resolution such as a lock variable. Core power demands may be decreased before and after change in dock speed to reduce power bus disruption.

Owner:WISCONSIN ALUMNI RES FOUND

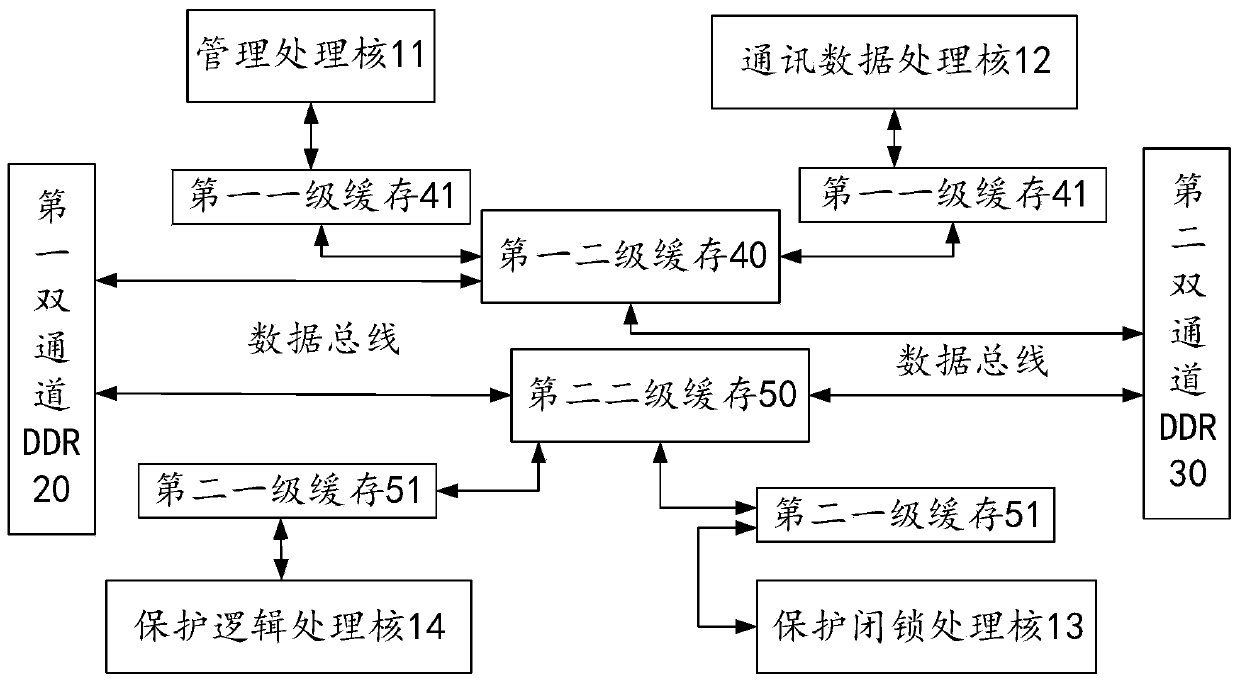

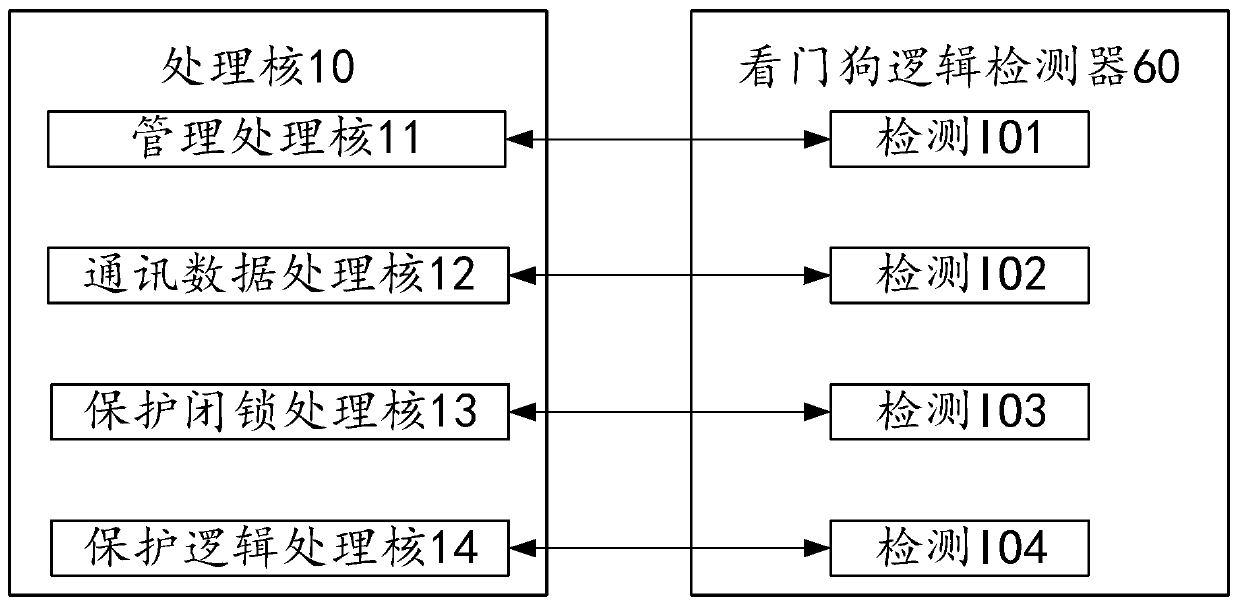

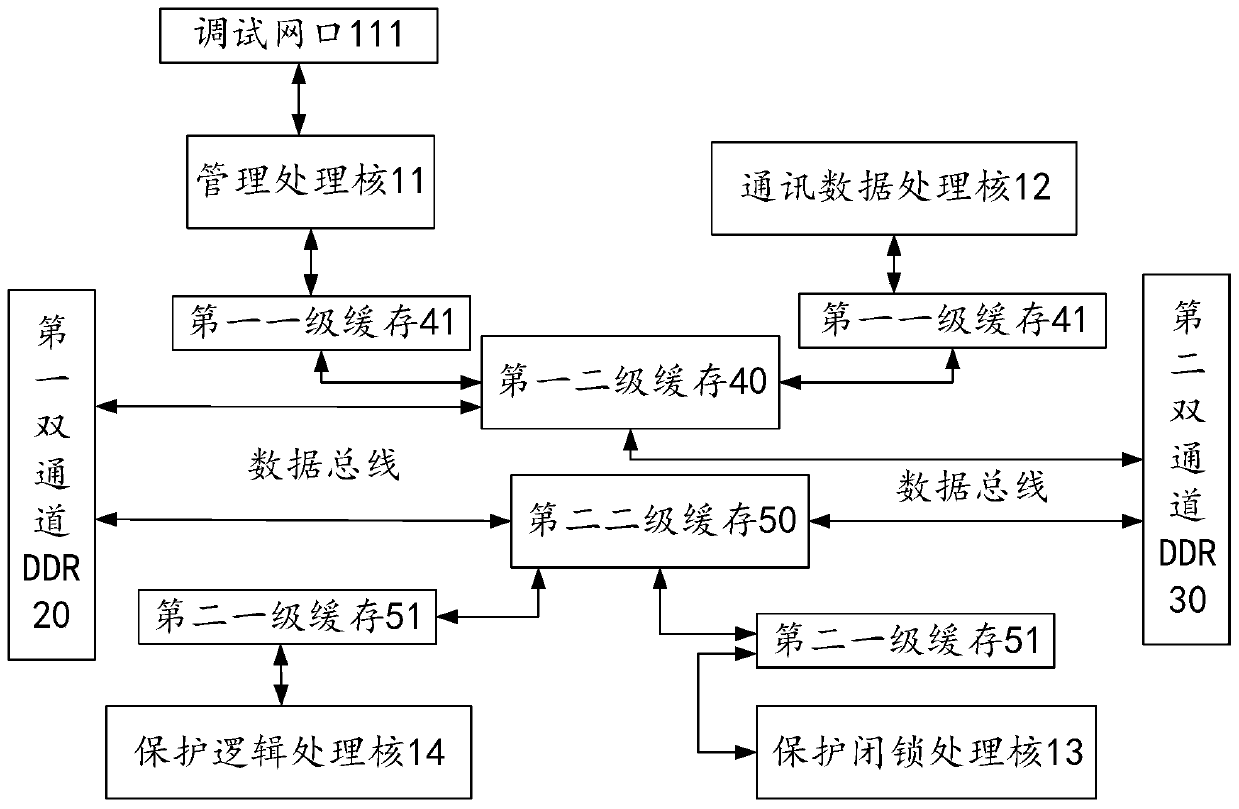

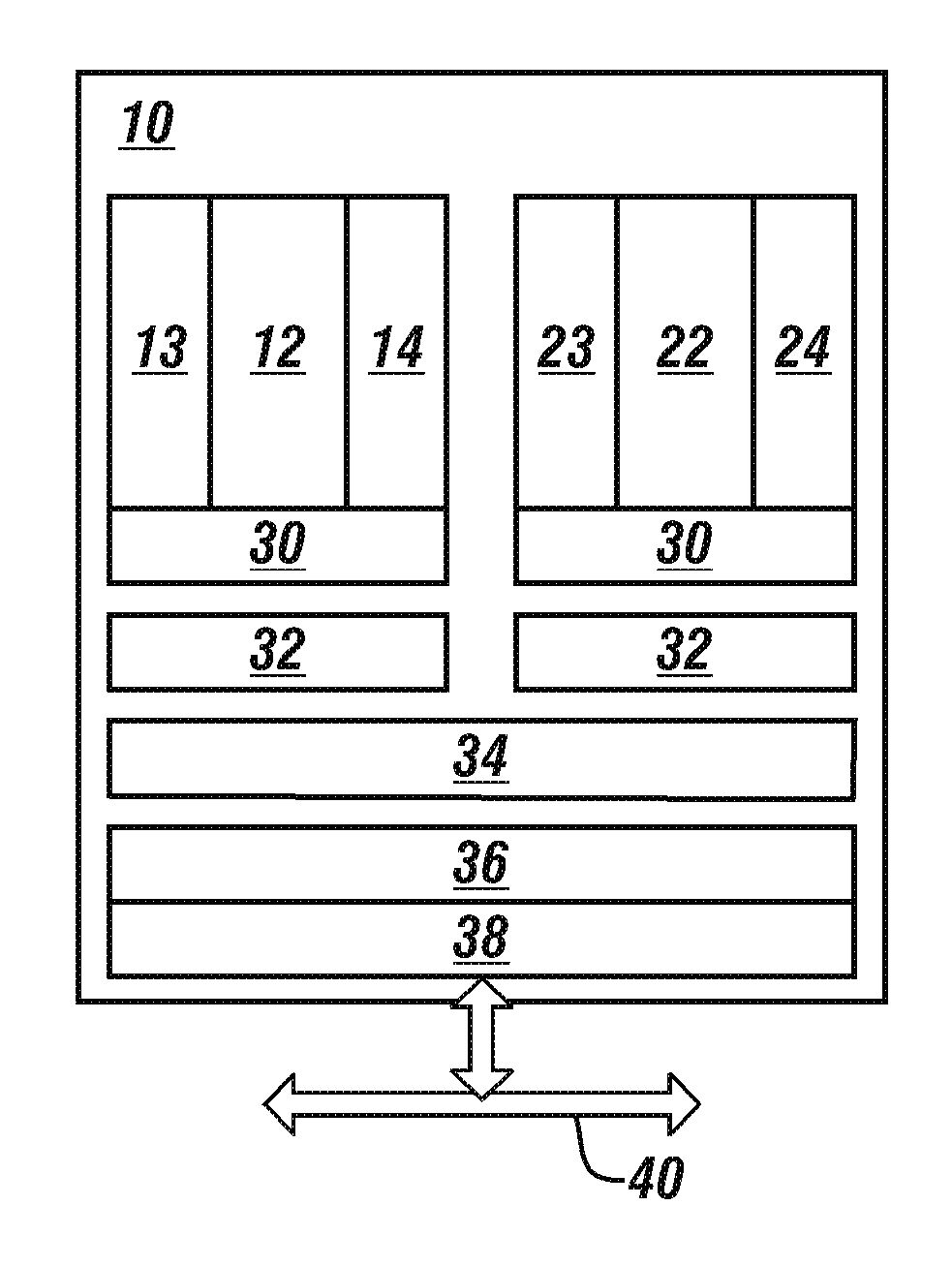

Relay protection system and special multi-core Soc chip architecture thereof

InactiveCN111427840AReduced operational reliabilityReduced operational stabilityFault responseArchitecture with single central processing unitComputer architectureProcessing core

The embodiment of the invention relates to a relay protection system and a special multi-core Soc chip architecture thereof. The special multi-core Soc chip architecture comprises a first dual-channelDDR, a second dual-channel DDR, a management processing core, a communication data processing core, a protection locking processing core, a protection logic processing core, a first secondary cache and a second secondary cache which are integrated on a chip. According to the special multi-core Soc chip architecture for the relay protection system, the four processing cores, the first dual-channelDDR, the second dual-channel DDR, the first secondary cache and the second secondary cache are integrally arranged on the chip, so that the original complex multi-chip hardware architecture is simplified; and low operation reliability and stability of the relay protection system caused by unstable connection of a multi-chip hardware structure are also avoided, and the operation reliability and stability of the relay protection system are improved. The technical problem that the operation stability and reliability of a relay protection product are influenced due to the fact that an existing relay protection multi-chip framework adopts a framework that a plurality of chips adopt a plurality of clamping plates and the multi-chip framework is complex is solved.

Owner:CHINA SOUTHERN POWER GRID DIGITAL GRID RES INST CO LTD

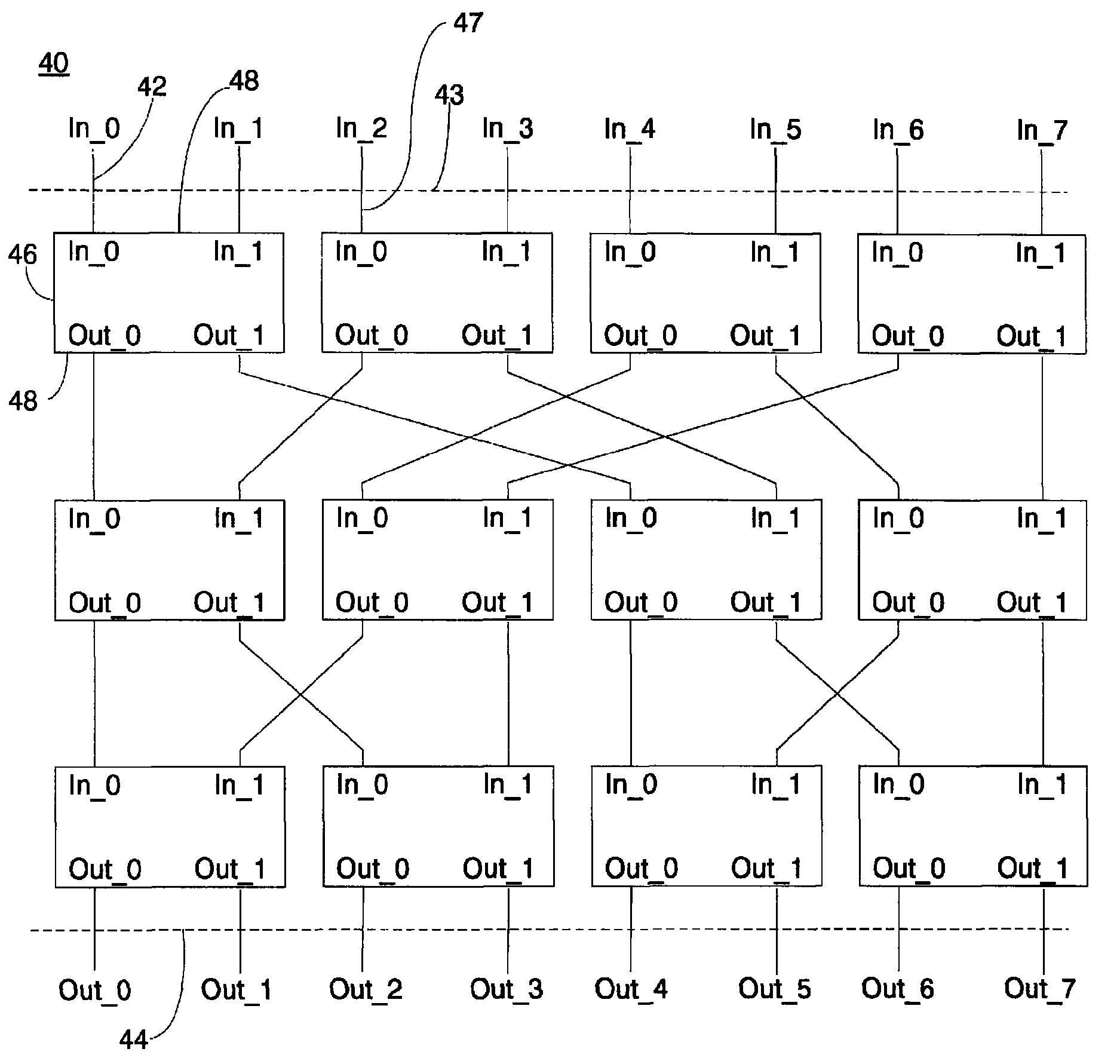

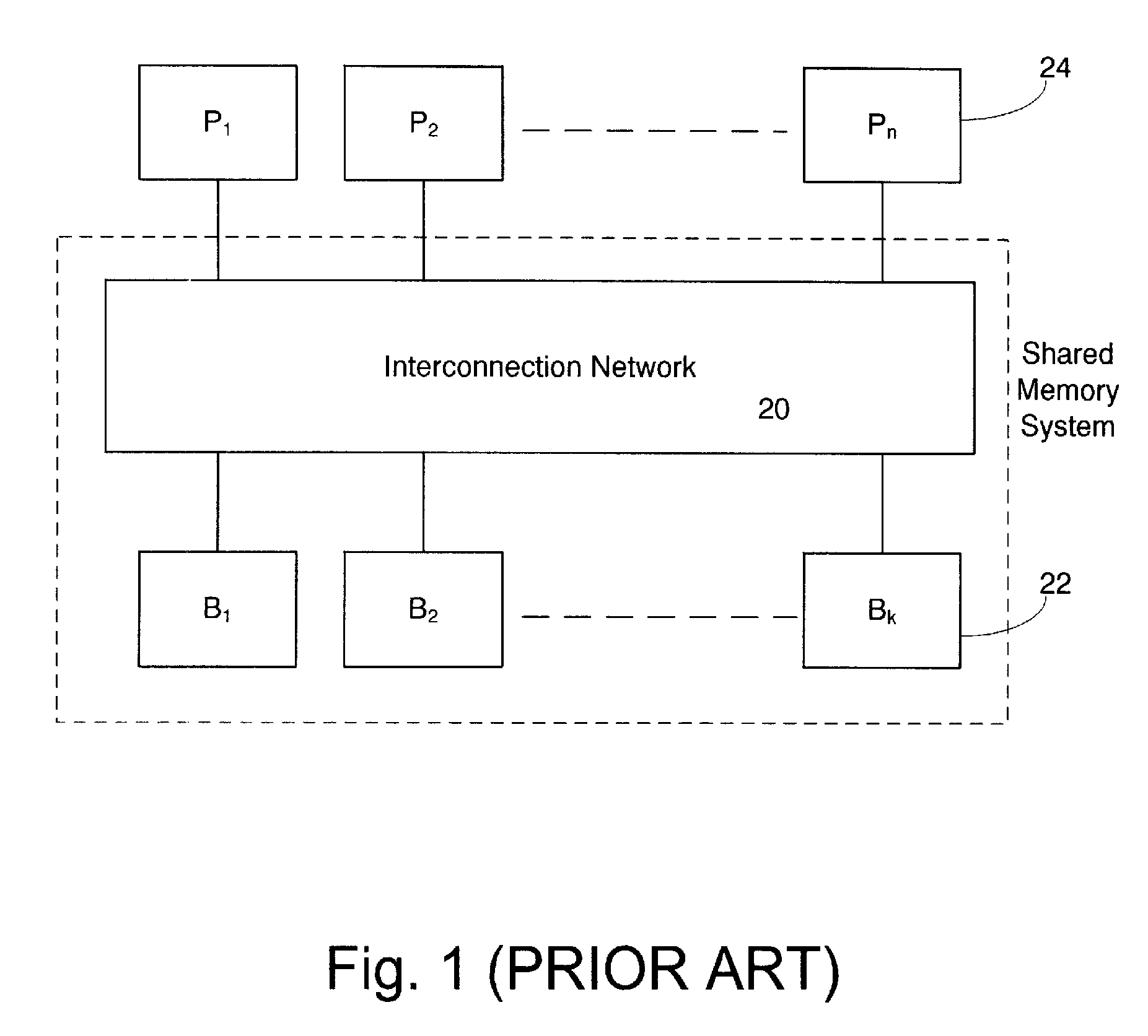

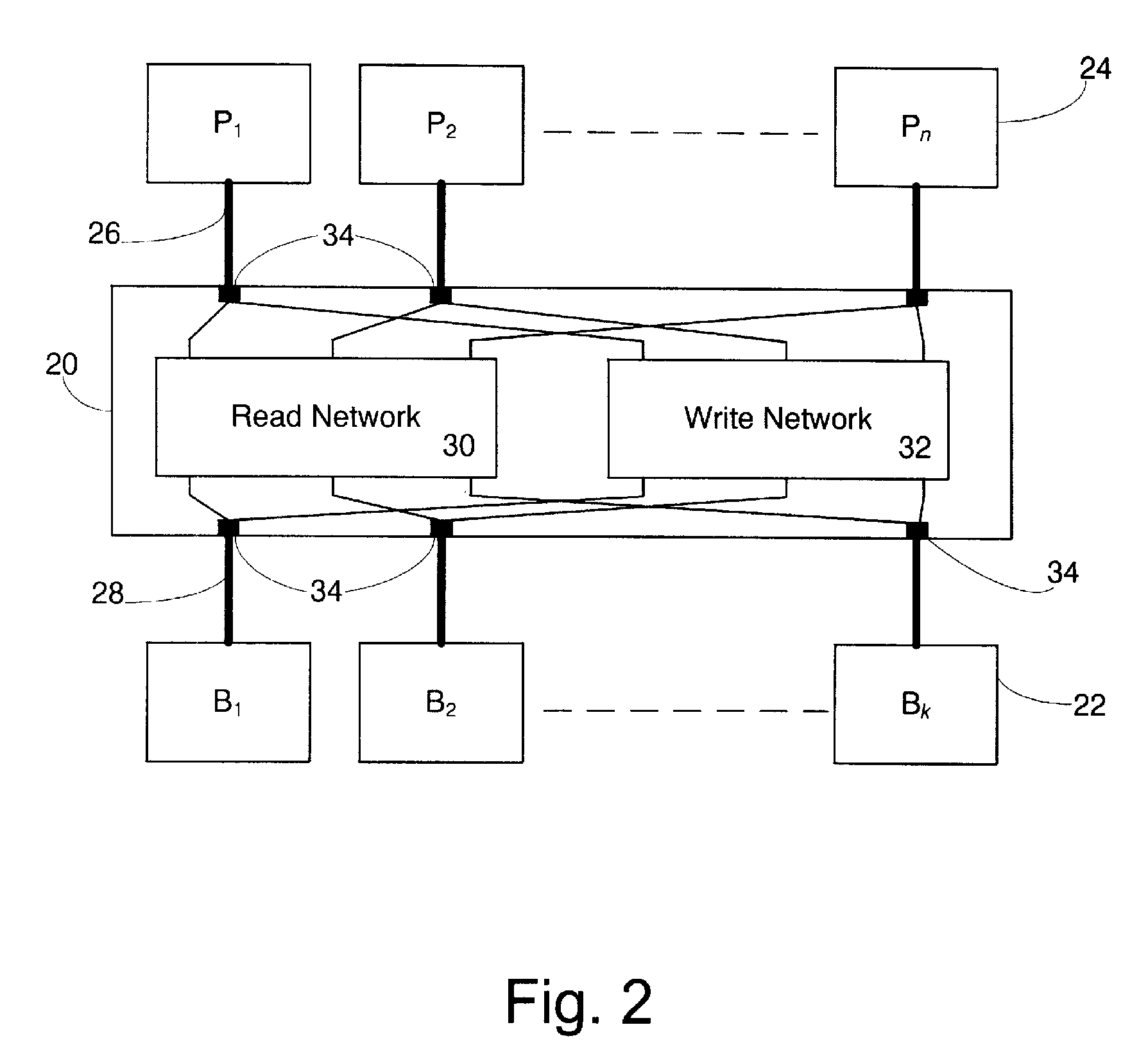

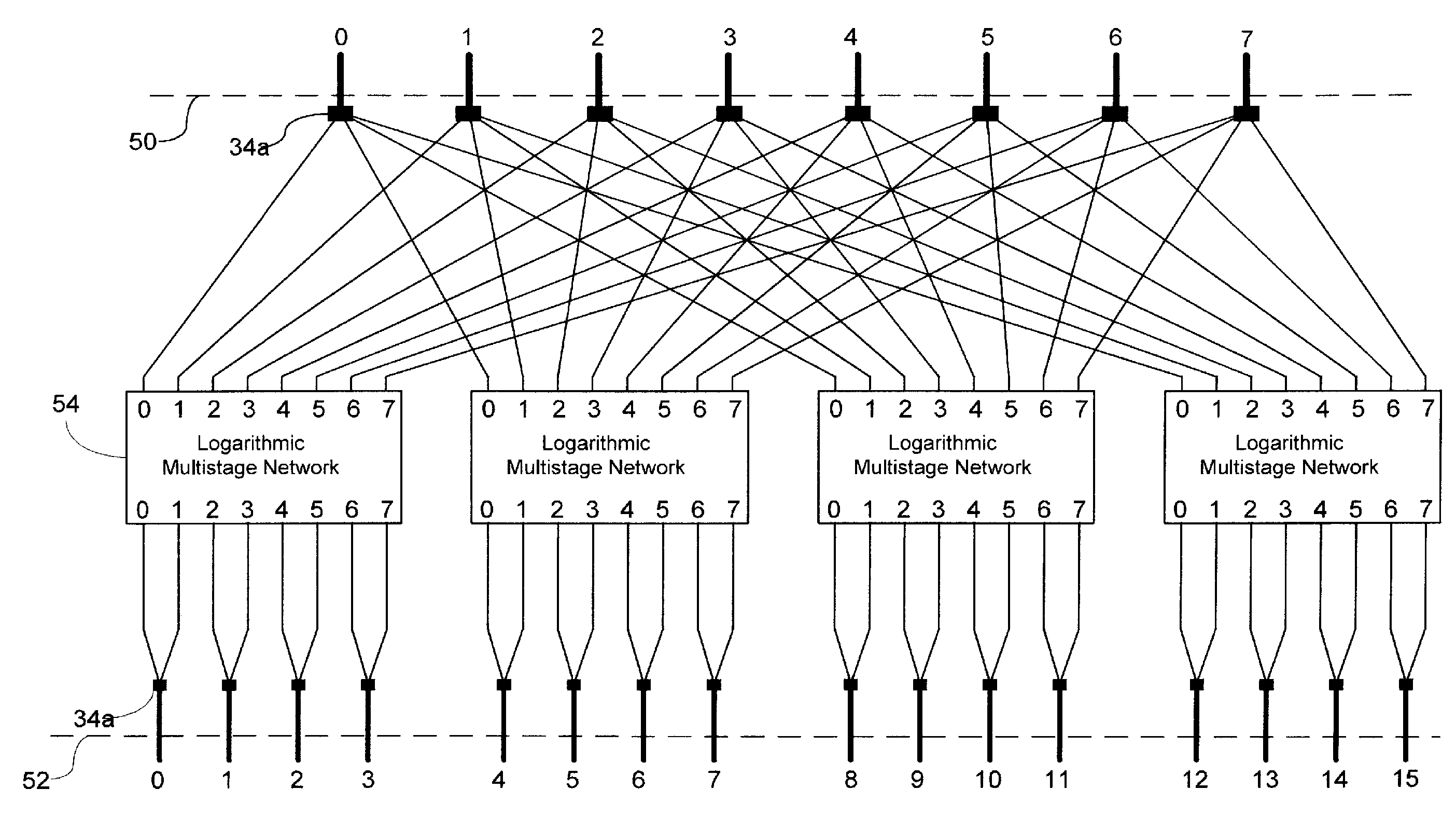

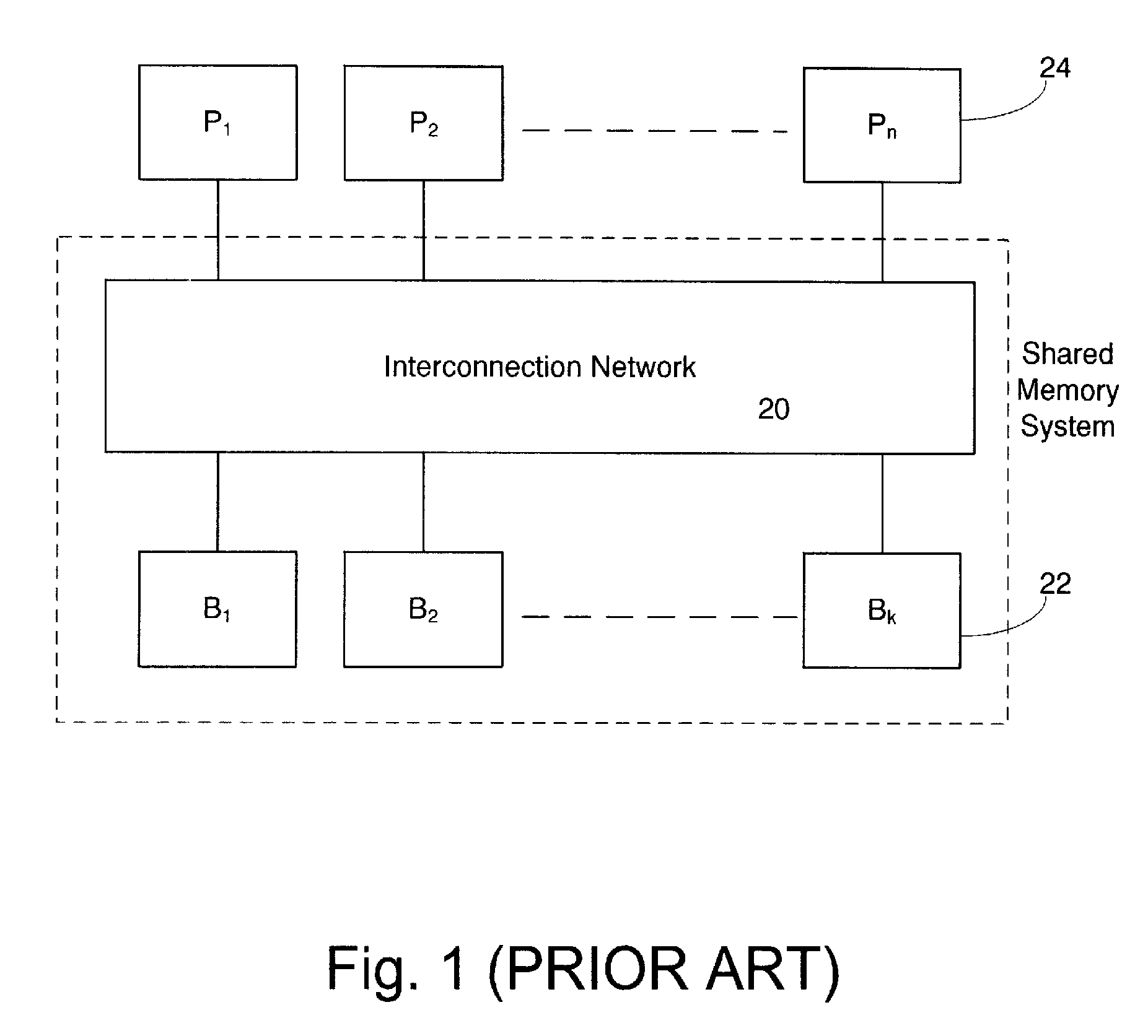

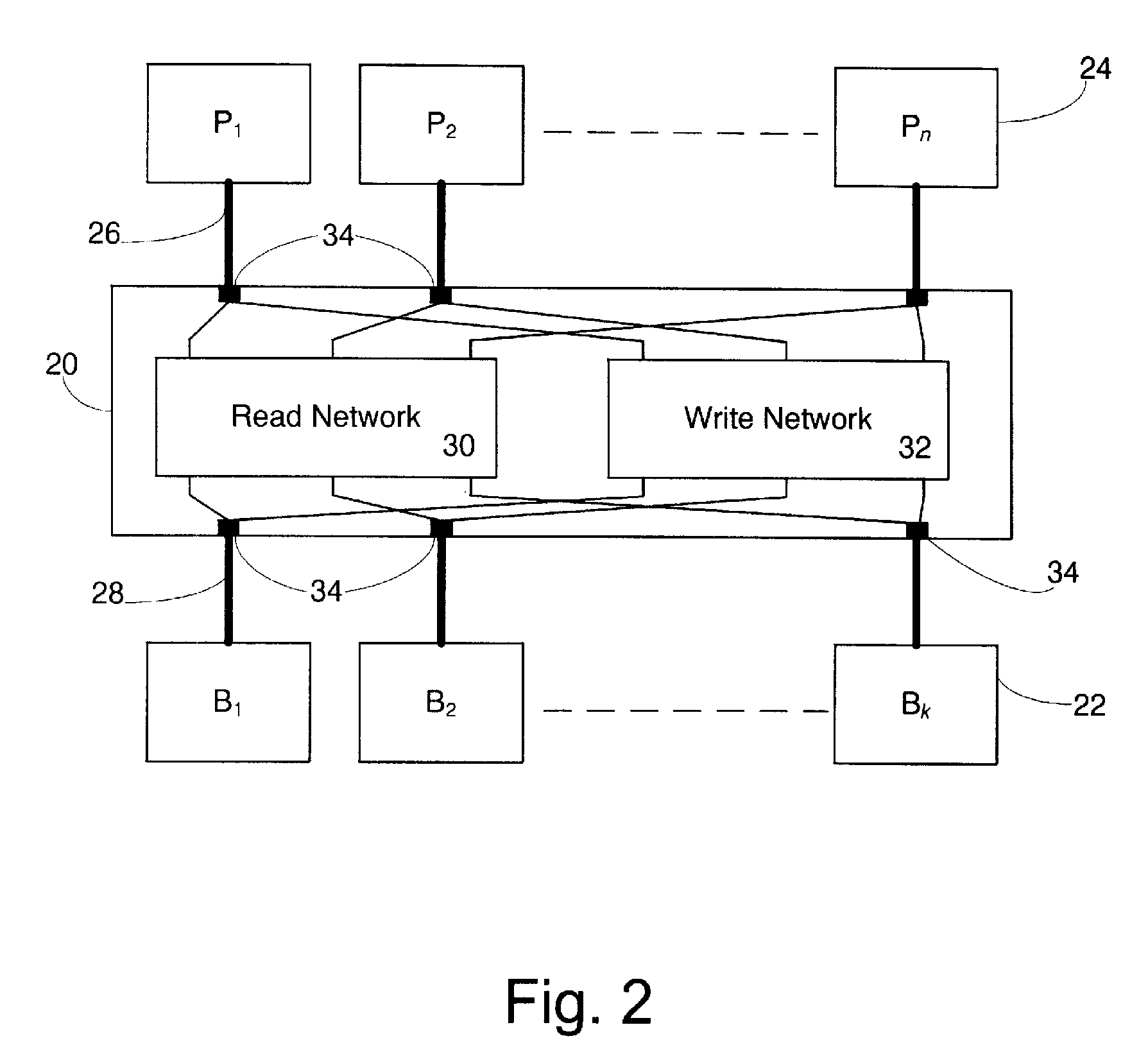

Shared memory system for a tightly-coupled multiprocessor

ActiveUS8099561B2Efficiently support massively parallel and finely grained computationDense and intensive cooperationDigital computer detailsMemory systemsProcessing coreMulti processor

A shared memory system for a multicore computer system utilizing an interconnection network that furnishes tens of processing cores or more with the ability to refer concurrently to random addresses in a shared memory space with efficiency comparable to the typical efficiency achieved when referring to private memories. The network is essentially a lean and light-weight combinational circuit, although it may also contain non-deep pipelining. The network is generally composed of a sub-network for writing and a separate multicasting sub-network for reading, whose topologies are based on multiple logarithmic multistage networks, e.g. Baseline Networks, connected in parallel. The shared memory system computes paths between processing cores and memory banks anew at every clock cycle, without rearrangement. It returns an approval reply to every core whose initiative of accessing memory leads to the successful establishment of a path and is fulfilled, or a rejection reply to every core whose initiative is not fulfilled.

Owner:N B PLURAL LTD

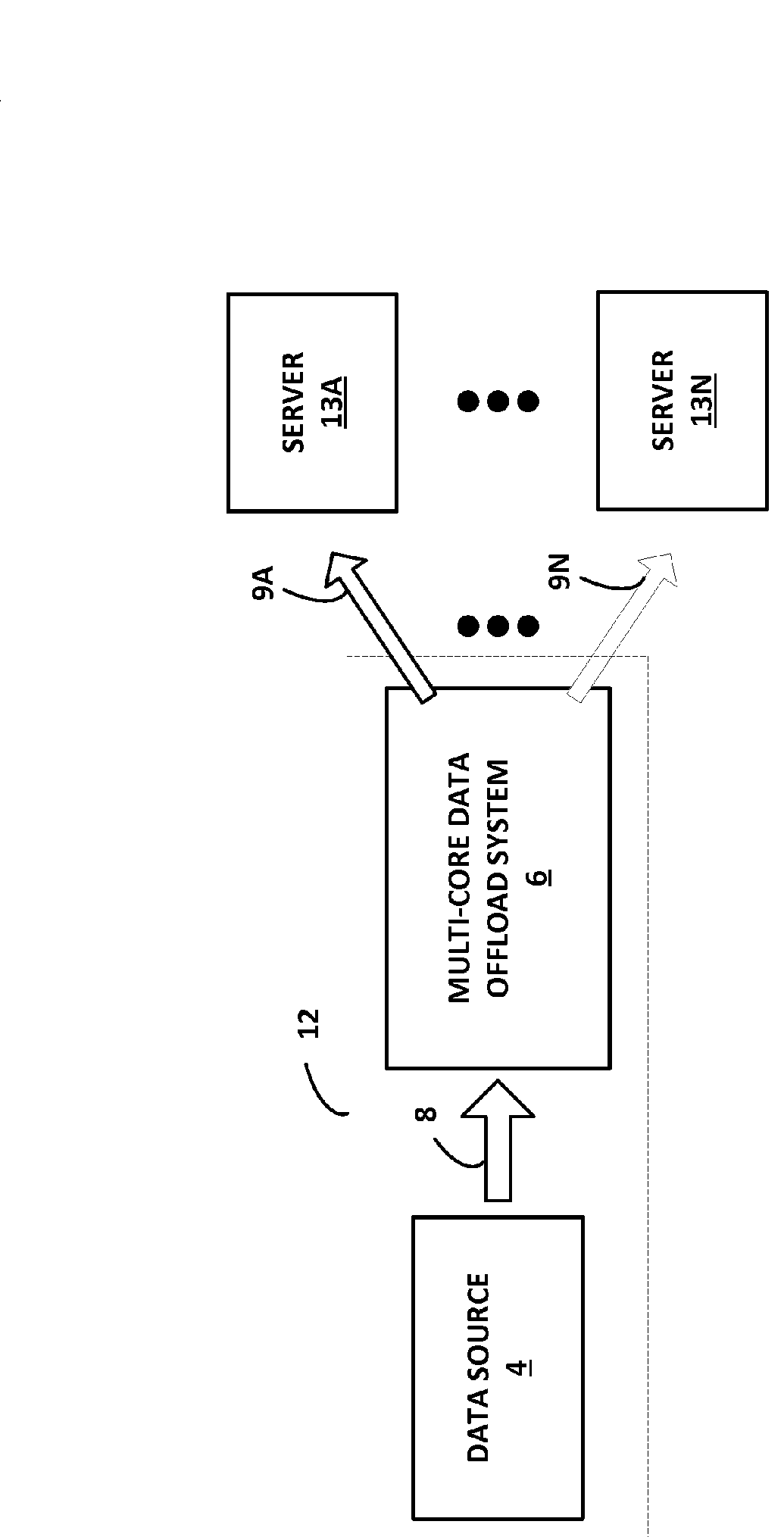

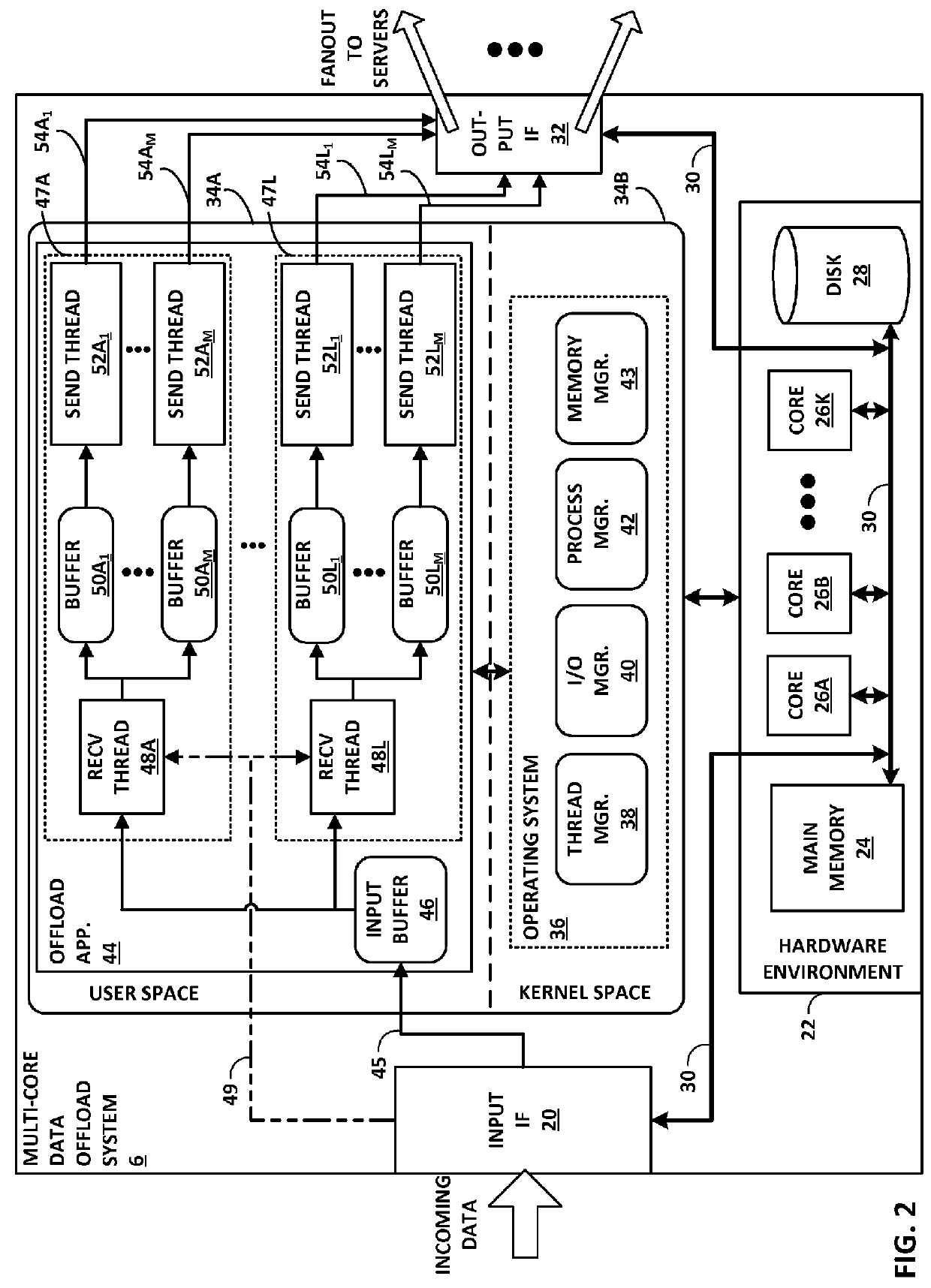

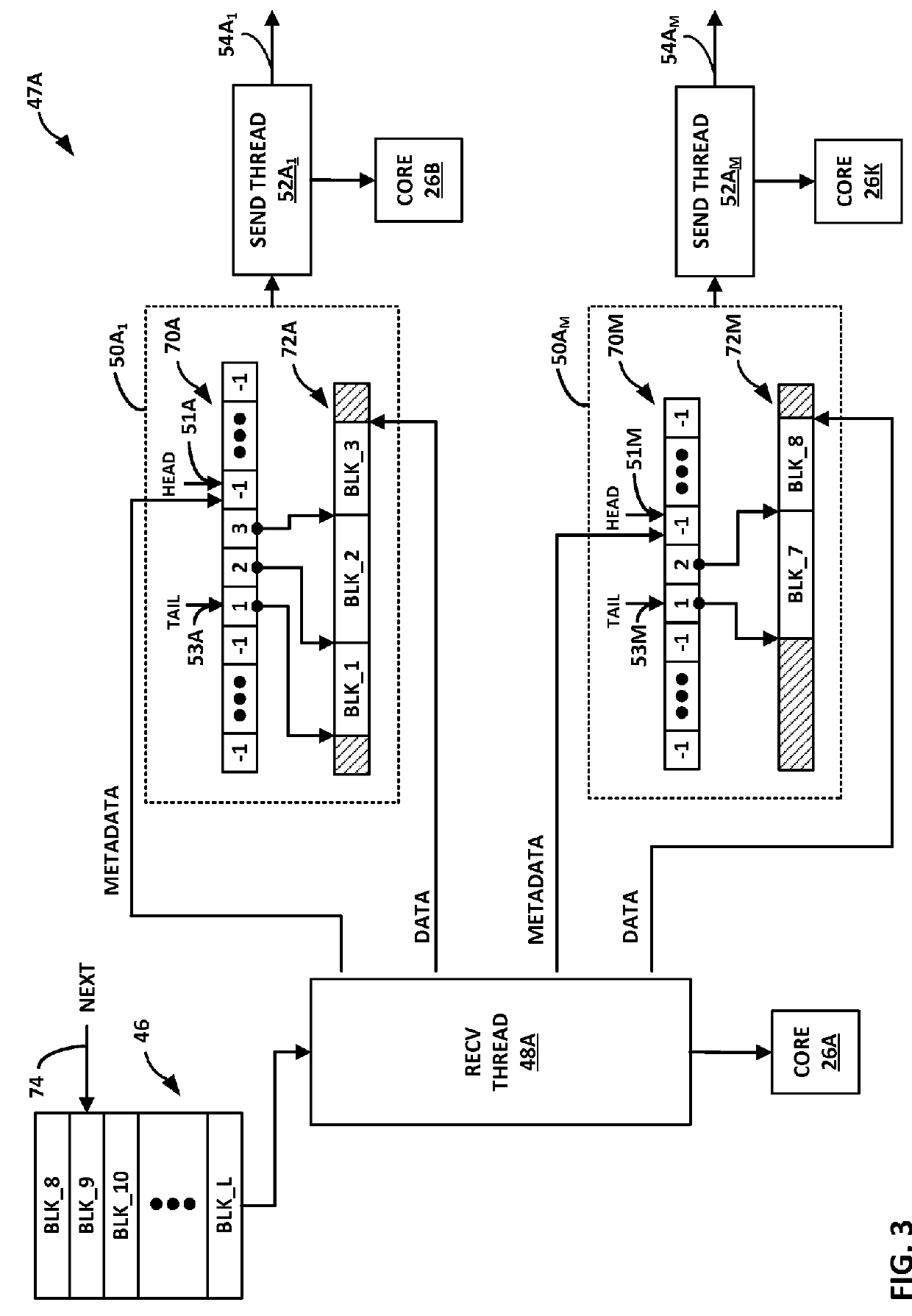

Multi-threaded, lockless data parallelization

ActiveUS9378059B2Reduce needReduce resource requirementsDigital data information retrievalResource allocationData streamCircular buffer

In general, techniques are described for parallelizing a high-volume data stream using a data structure that enables lockless access by a multi-threaded application. In some examples, a multi-core computing system includes an application that concurrently executes multiple threads on cores of the system. The multiple threads include one or more send threads each associated with a different lockless data structure that each includes both a circular buffer and a queue. One or more receive threads serially retrieve incoming data from a data stream or input buffer, copy data blocks to one of the circular buffers, and push metadata for the copied data blocks to the queue. Each of the various send threads, concurrent to the operation of the receive threads, dequeues the next metadata from its associated queue, reads respective blocks of data from its associated circular buffers based on metadata information, and offloads the block to a server.

Owner:ARGYLE DATA

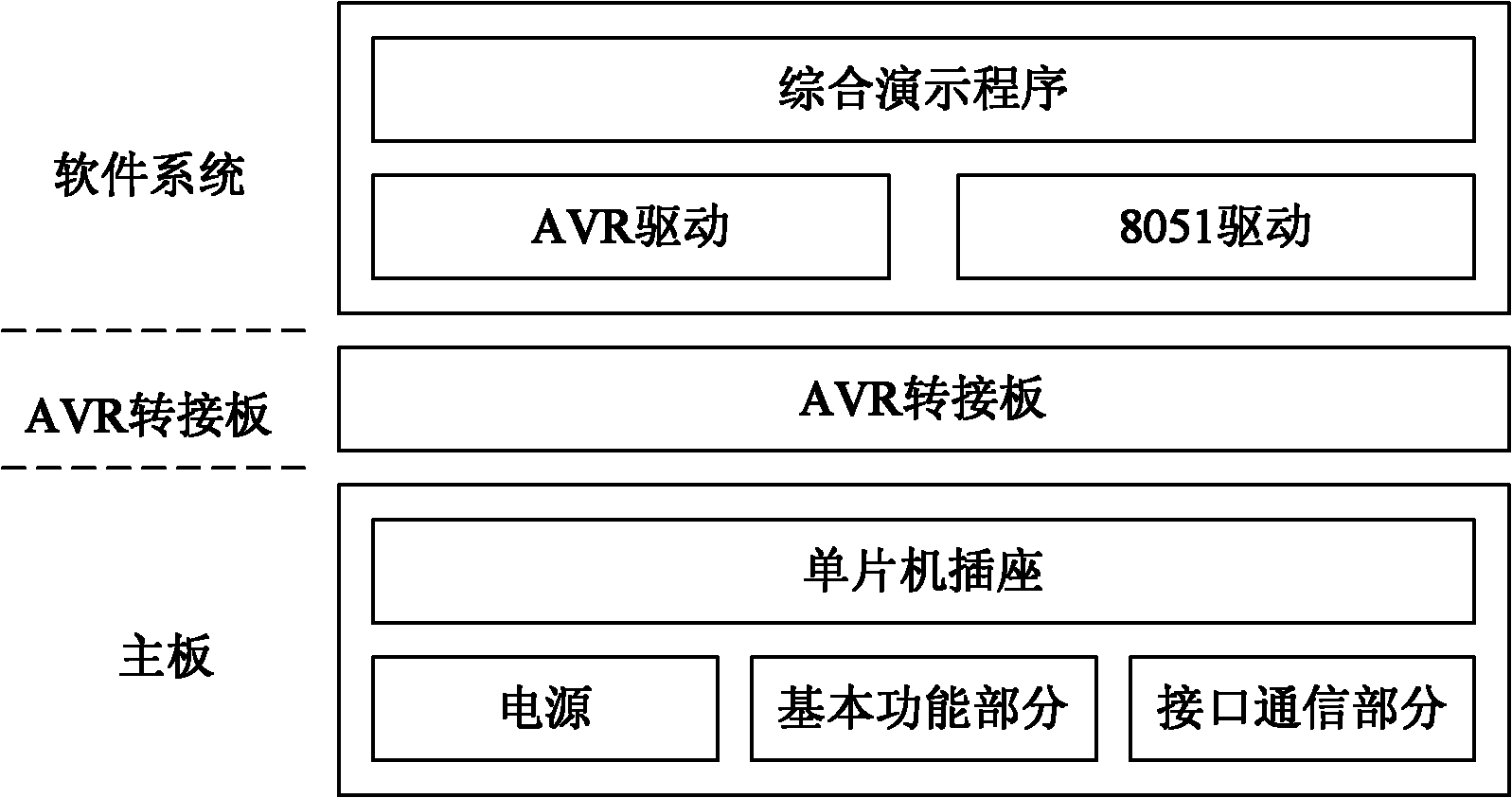

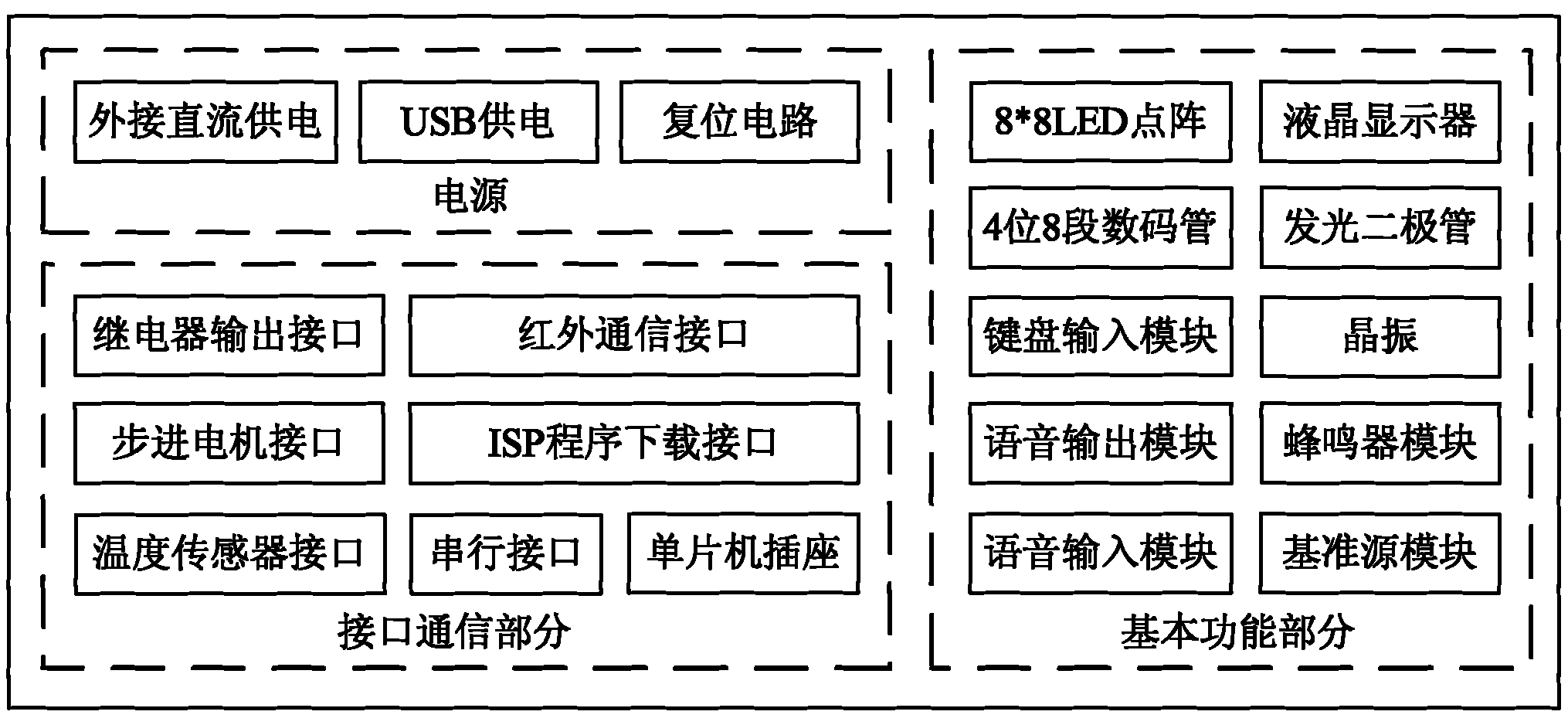

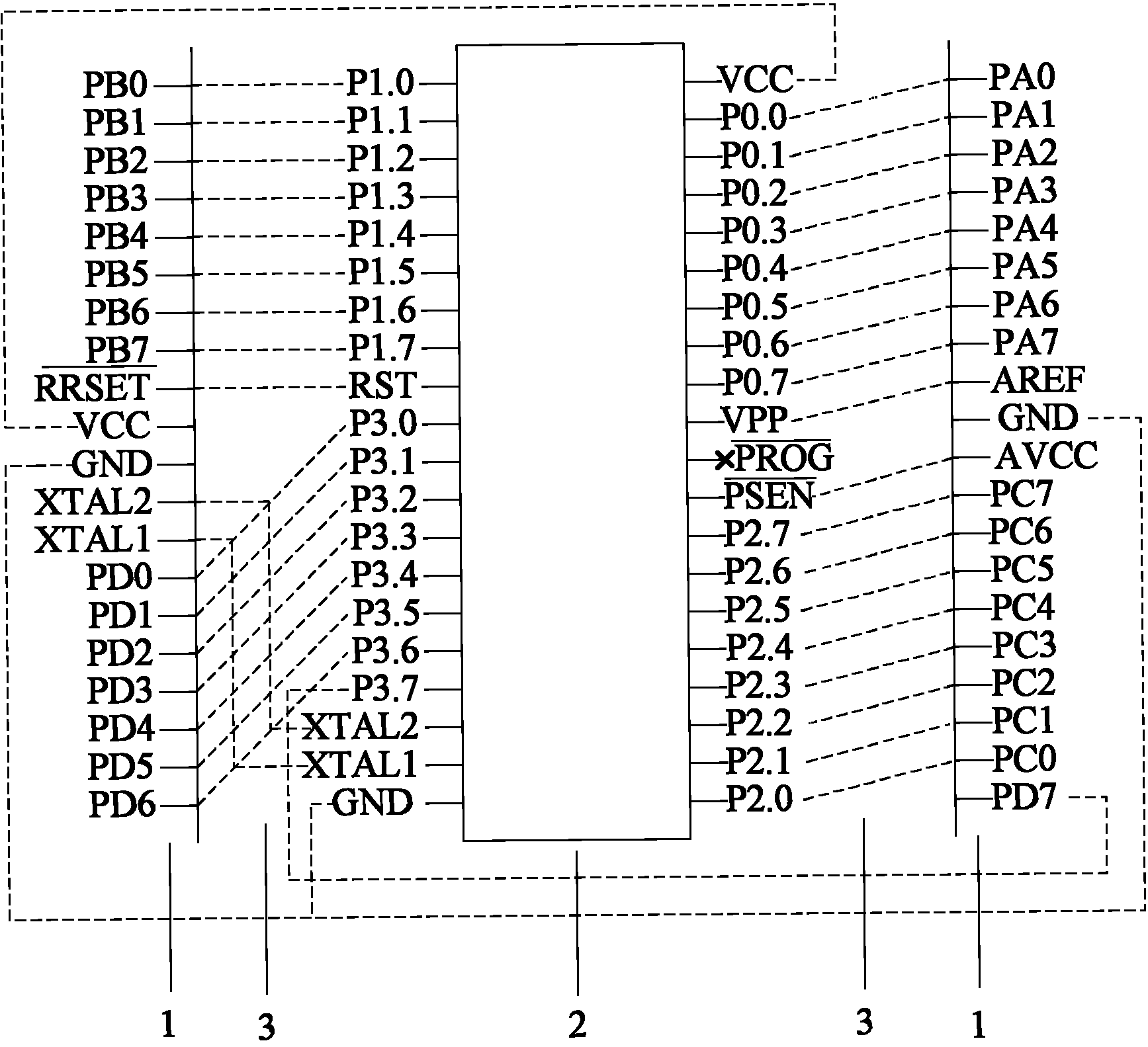

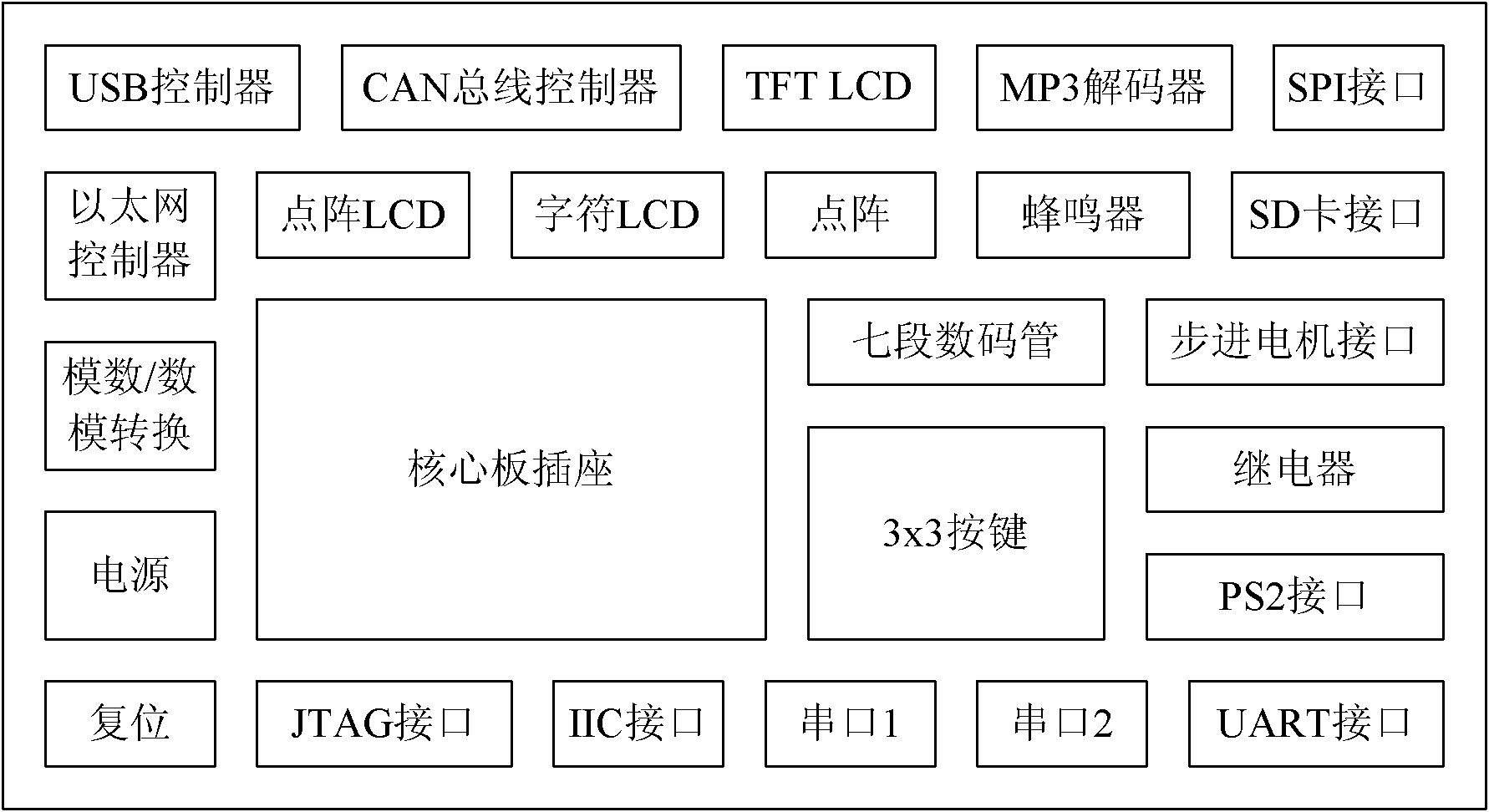

8051-or-AVR-based multi-core singlechip teaching experimental platform

InactiveCN102194351AReduce purchase costLower teacher training feesTeaching apparatusMicrocontrollerSoftware system

The invention discloses an 8051-or-AVR-based multi-core singlechip teaching experimental platform, and belongs to the field of embedded computers. The hardware of the platform comprises a mainboard, and two circuit boards of an AVR adapter plate; an 8051 singlechip adopts AT89S52; an AVR singlechip adopts ATMEGA32; AT89S52 can be directly inserted into the mainboard for work and at the moment, the platform works in an 8051 mode; ATMEGA32 can be inserted into the mainboard for work through the AVR adapter plate, the AVR adapter plate transforms ATMEGA32 pin encapsulation form into AT89S52 pin encapsulation form and at the moment, the platform works in an AVR mode. The mainboard consists of a power supply, a basic functional part and an interface communication part. A platform software system is divided into two layers, namely a driving layer and an application layer; the driving layer finishes the encapsulation of hardware resources of two singlechips; the application layer is a comprehensive demonstration program having 14 experiments, runs with support of the driving layer, and is irrelevant with hardware.

Owner:DALIAN UNIV OF TECH

Shared memory system for a tightly-coupled multiprocessor

ActiveUS20090125685A1Efficiently support massively parallel and finely grained computationDense and intensive cooperationDigital computer detailsMemory systemsProcessing coreMulti processor

A shared memory system for a multicore computer system utilizing an interconnection network that furnishes tens of processing cores or more with the ability to refer concurrently to random addresses in a shared memory space with efficiency comparable to the typical efficiency achieved when referring to private memories. The network is essentially a lean and light-weight combinational circuit, although it may also contain non-deep pipelining. The network is generally composed of a sub-network for writing and a separate multicasting sub-network for reading, whose topologies are based on multiple logarithmic multistage networks, e.g. Baseline Networks, connected in parallel. The shared memory system computes paths between processing cores and memory banks anew at every clock cycle, without rearrangement. It returns an approval reply to every core whose initiative of accessing memory leads to the successful establishment of a path and is fulfilled, or a rejection reply to every core whose initiative is not fulfilled.

Owner:N B PLURAL LTD

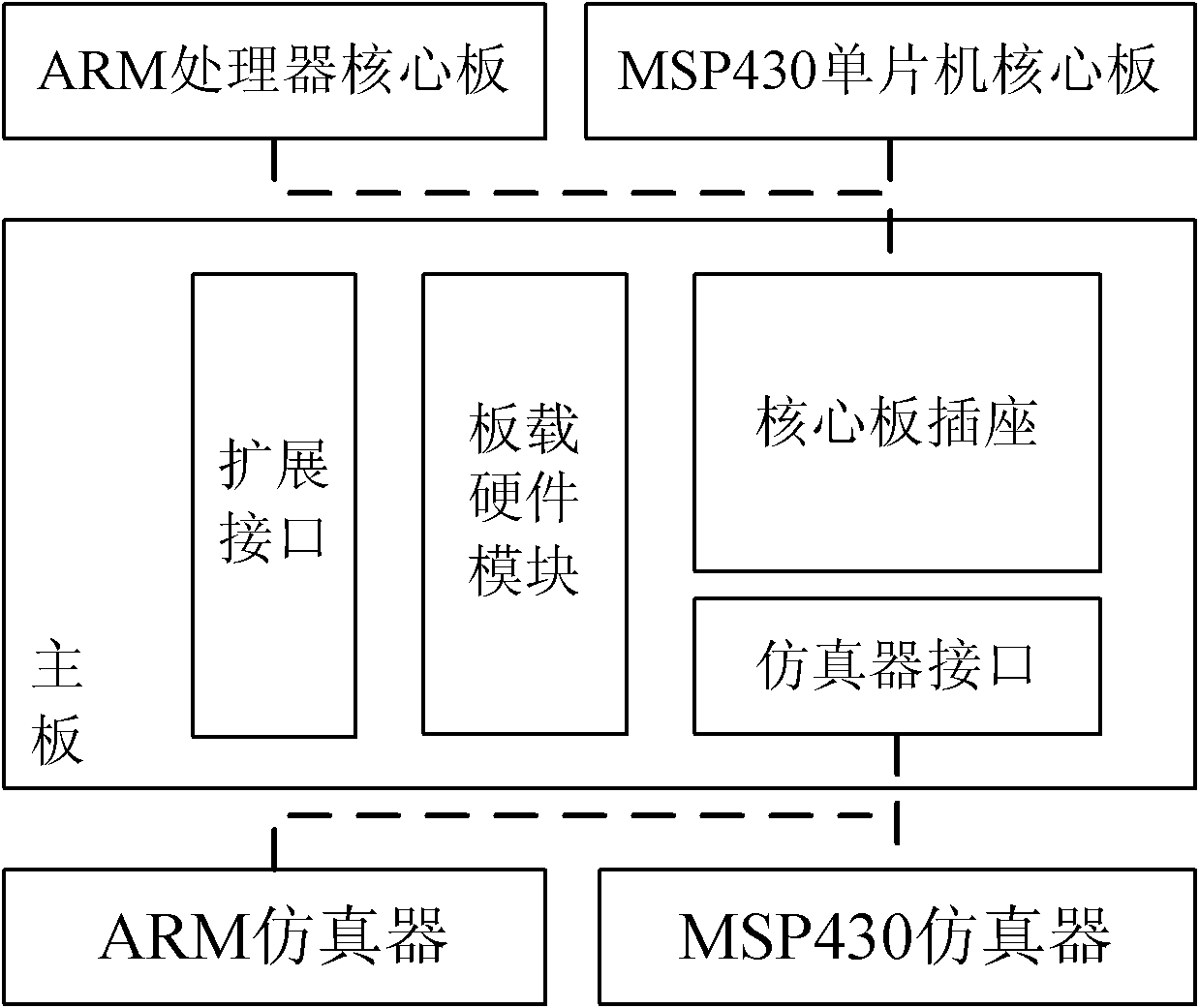

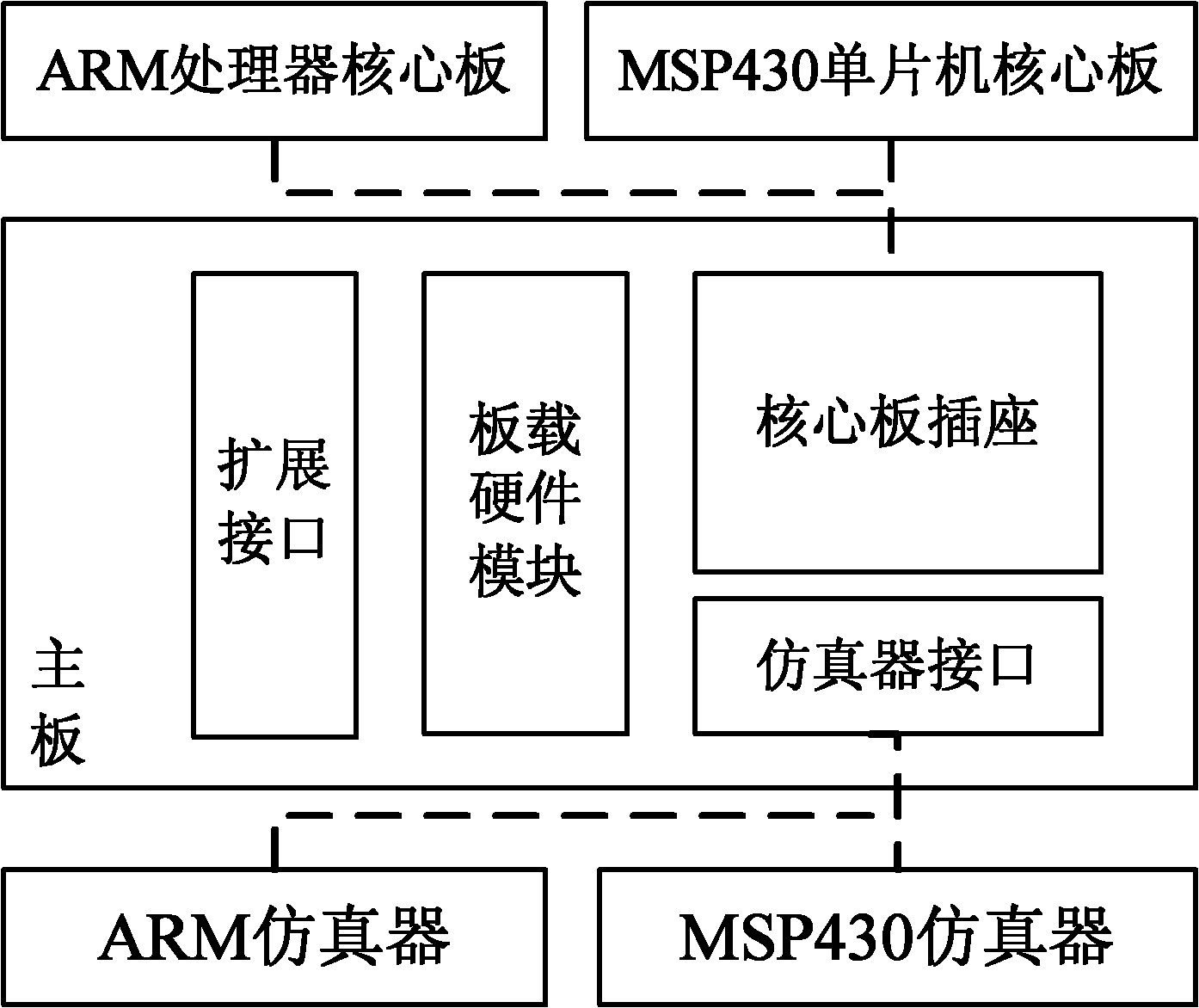

Multi-core embedded type teaching and scientific research platform

The invention discloses a multi-core embedded type teaching and scientific research platform, belonging to the field of an embedded type computer. The platform comprises 5 circuit boards, i.e. a mainboard, an MSP430 single chip microcomputer core board, an MSP430 simulator, an advanced RISC machine (ARM) processor core board and an ARM simulator; the platform has two working modes through different combinations of the five parts, i.e. a single chip microcomputer mode and an ARM mode; the core plate interface of the mainboard of the platform is a socket with 70 needles and provides multiple power supplies, a joint test action group (JTAG) interface and a general input output (IO) interface; the mainboard adopts an 8-bite simulating bus to connect multiple onboard hardware resources; the processor IO interface wires of the two core boards of the platform are connected to the socket through jumpers so as to control the mainboard hardware resources; and the processor IO interface wire resources can be led after the jumpers are broken off. The platform can be suitable for different occasions, gives the consideration to teaching and scientific research requirements, and reduces the cost of the equipment through the characteristics.

Owner:DALIAN UNIV OF TECH

Dynamic co-scheduling of hardware contexts for parallel runtime systems on shared machines

ActiveUS9542221B2Reduce load imbalanceEasy to useOperational speed enhancementProgram initiation/switchingOperational systemResource management

Multi-core computers may implement a resource management layer between the operating system and resource-management-enabled parallel runtime systems. The resource management components and runtime systems may collectively implement dynamic co-scheduling of hardware contexts when executing multiple parallel applications, using a spatial scheduling policy that grants high priority to one application per hardware context and a temporal scheduling policy for re-allocating unused hardware contexts. The runtime systems may receive resources on a varying number of hardware contexts as demands of the applications change over time, and the resource management components may co-ordinate to leave one runnable software thread for each hardware context. Periodic check-in operations may be used to determine (at times convenient to the applications) when hardware contexts should be re-allocated. Over-subscription of worker threads may reduce load imbalances between applications. A co-ordination table may store per-hardware-context information about resource demands and allocations.

Owner:ORACLE INT CORP

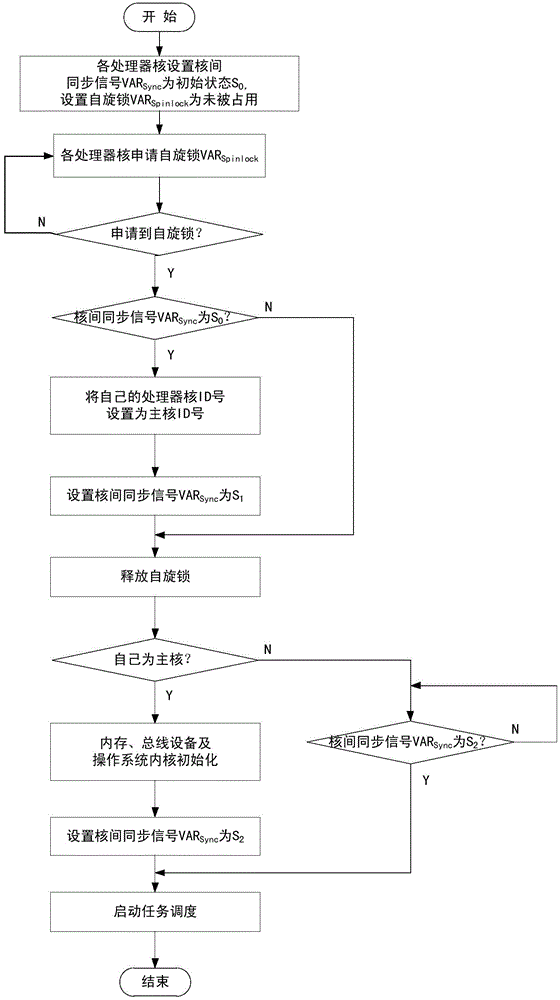

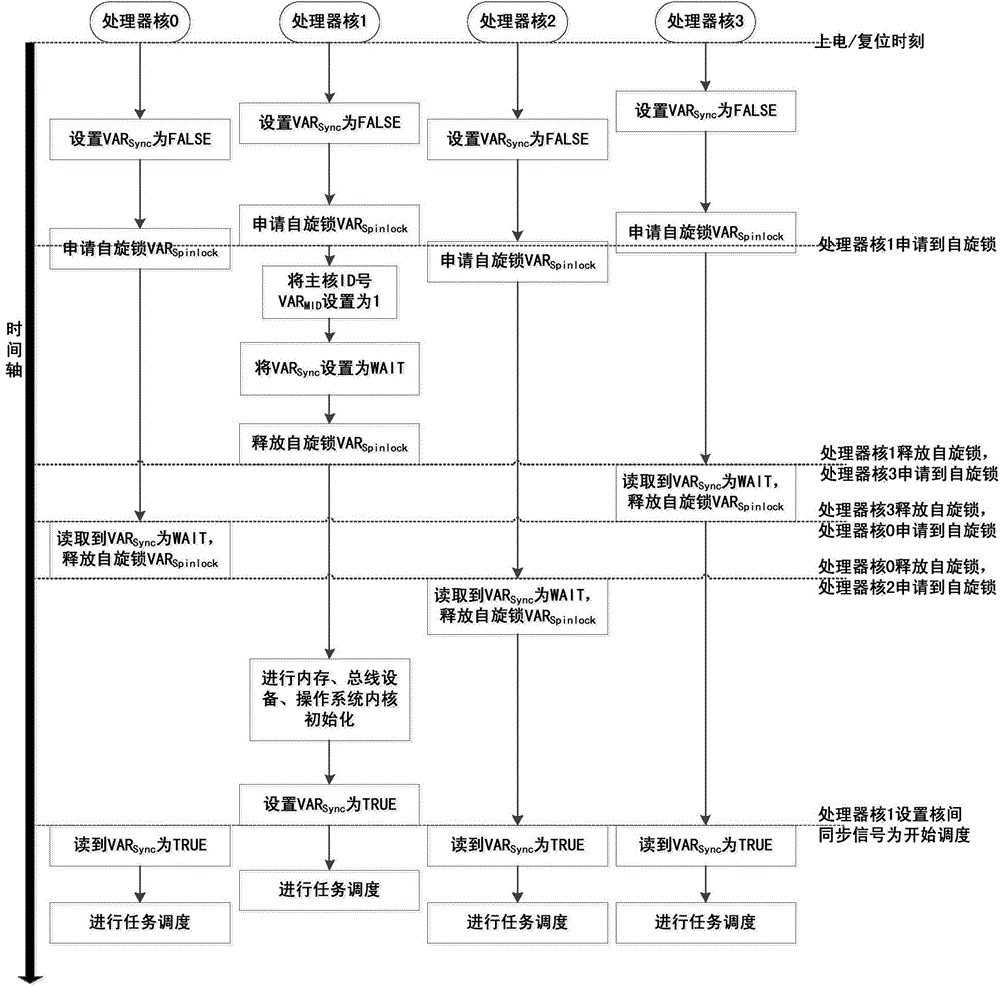

Reconfigurable fault-tolerant starting method for multicore operating system

ActiveCN104063295ASolve the problem that the fault cannot start the slave coreImprove reliabilityProgram loading/initiatingRedundant hardware error correctionOperational systemParallel computing

The invention discloses a reconfigurable fault-tolerant starting method for a multicore operating system. The reconfigurable fault-tolerant starting method for the multicore operating system comprises the following steps that a synchronizing signal is set as initial state; a spin lock is set to be unoccupied; after each processor core finishes initialization, the spin lock is applied; the processor core which successfully applies for the spin lock enters an inter-core mutual exclusion critical zone, and the rest processor cores are blocked on the spin lock; a self processor core ID (identity) is set as a main core ID number by the processor core which successfully applies for the spin lock first, the synchronizing signal is set, and then the spin lock is released; the processor cores which subsequently successfully apply for the spin lock are known as slave cores by a read value, the processor core corresponding to a main core ID is a main core, and the spin lock is released; after the main core finishes the initialization of a memory, bus equipment and the inner core of the operating system, an inter-core synchronizing signal is set to start the slave cores, and therefore the main core and the slave core simultaneously begin to schedule tasks. According to the reconfigurable fault-tolerant starting method for the multicore operating system, which is disclosed by the invention, other processor cores still can be normally started to operate when the main core fails, and the reliability of a multi-core computer is improved.

Owner:BEIJING INST OF CONTROL ENG

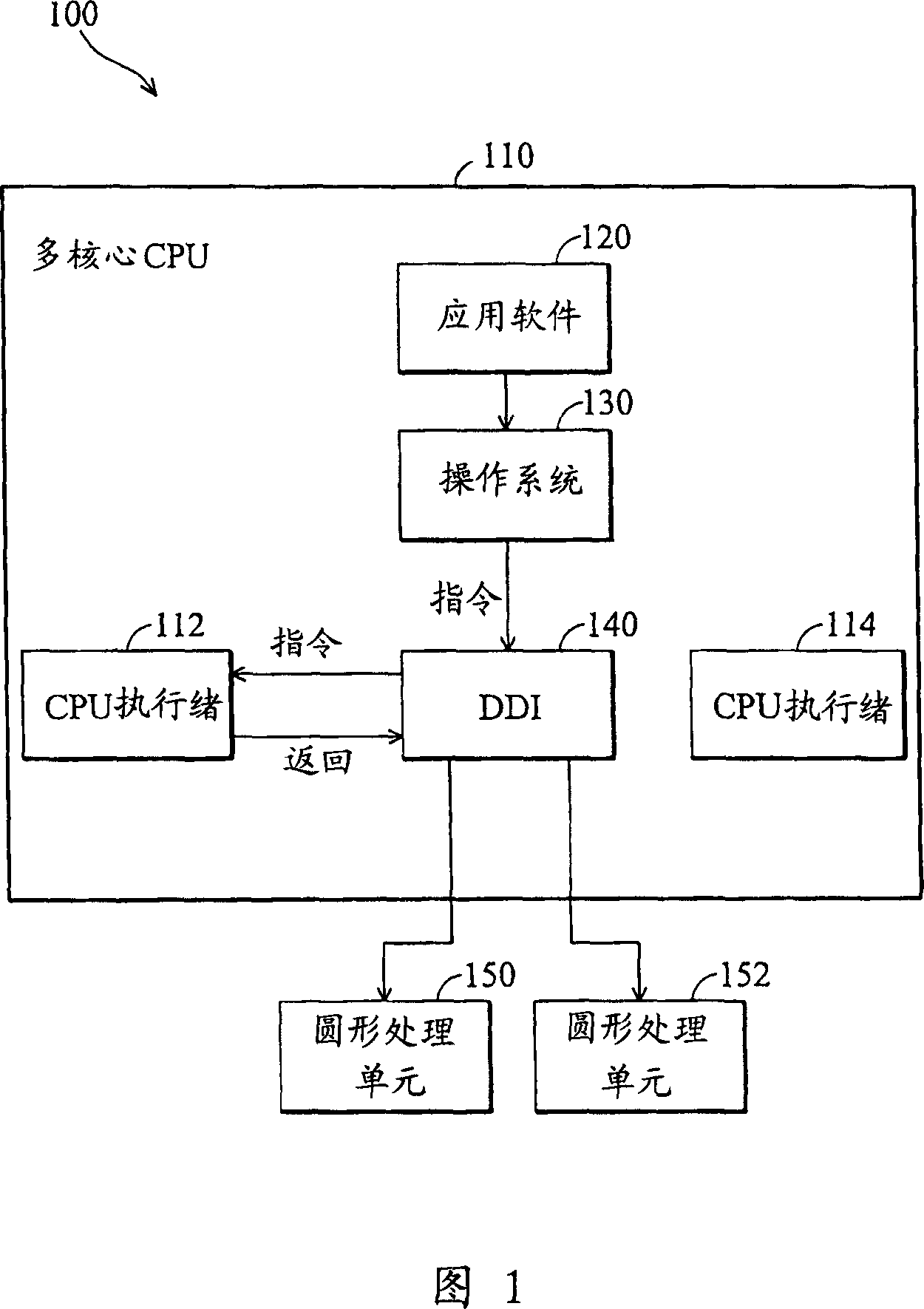

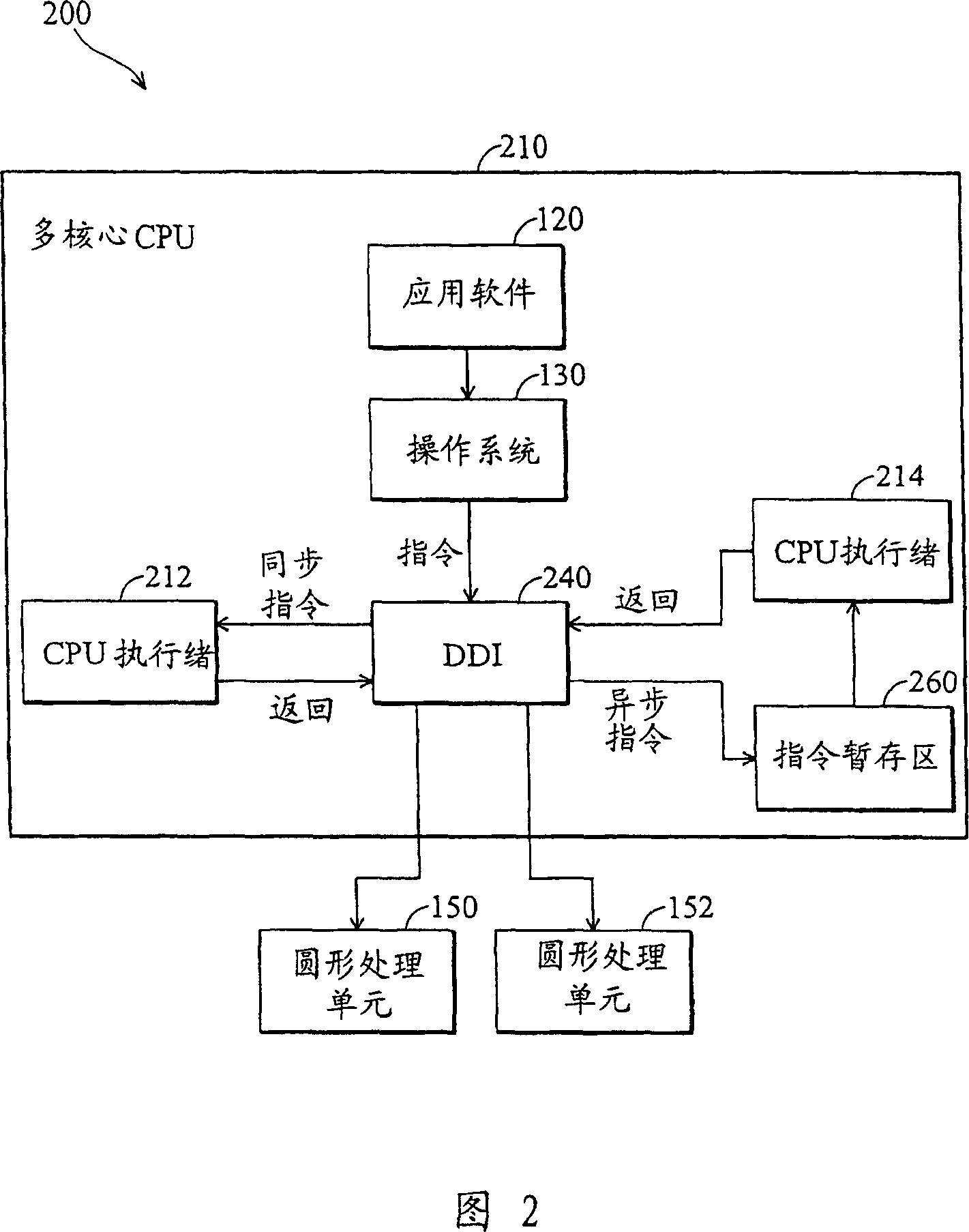

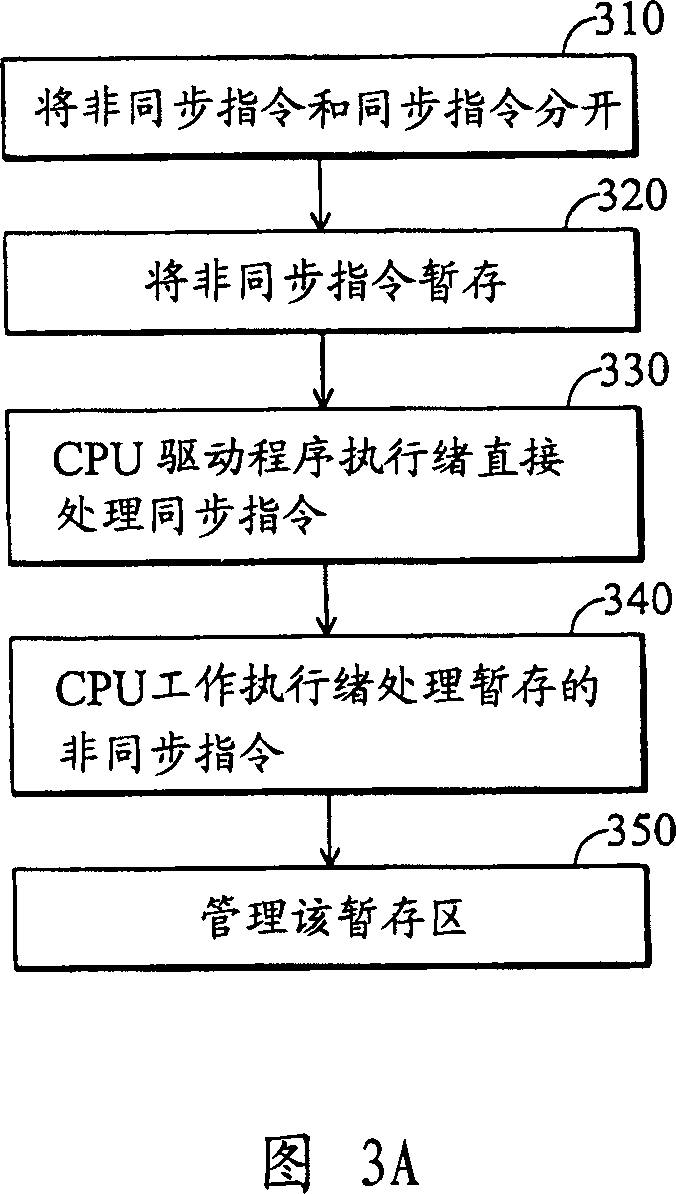

Method for supporting multi-threaded instruction implementation of multi-core computer system drive program

This invention discloses a method for assisting multi-threaded command execution by a driver in a multi-core, computer system, the method comprising distinguishing asynchronous commands from synchronous commands, buffering the asynchronous commands in a buffer, processing the synchronous commands directly in a CPU driver thread, processing the asynchronous commands from the buffer by one or more CPU work threads, wherein multiple threads of the multi-core computer system can be utilized at the same time; and managing the buffer after the buffer is processed by the CPU work thread, wherein the command executions appear to be just like single-threaded to application software.

Owner:VIA TECH INC

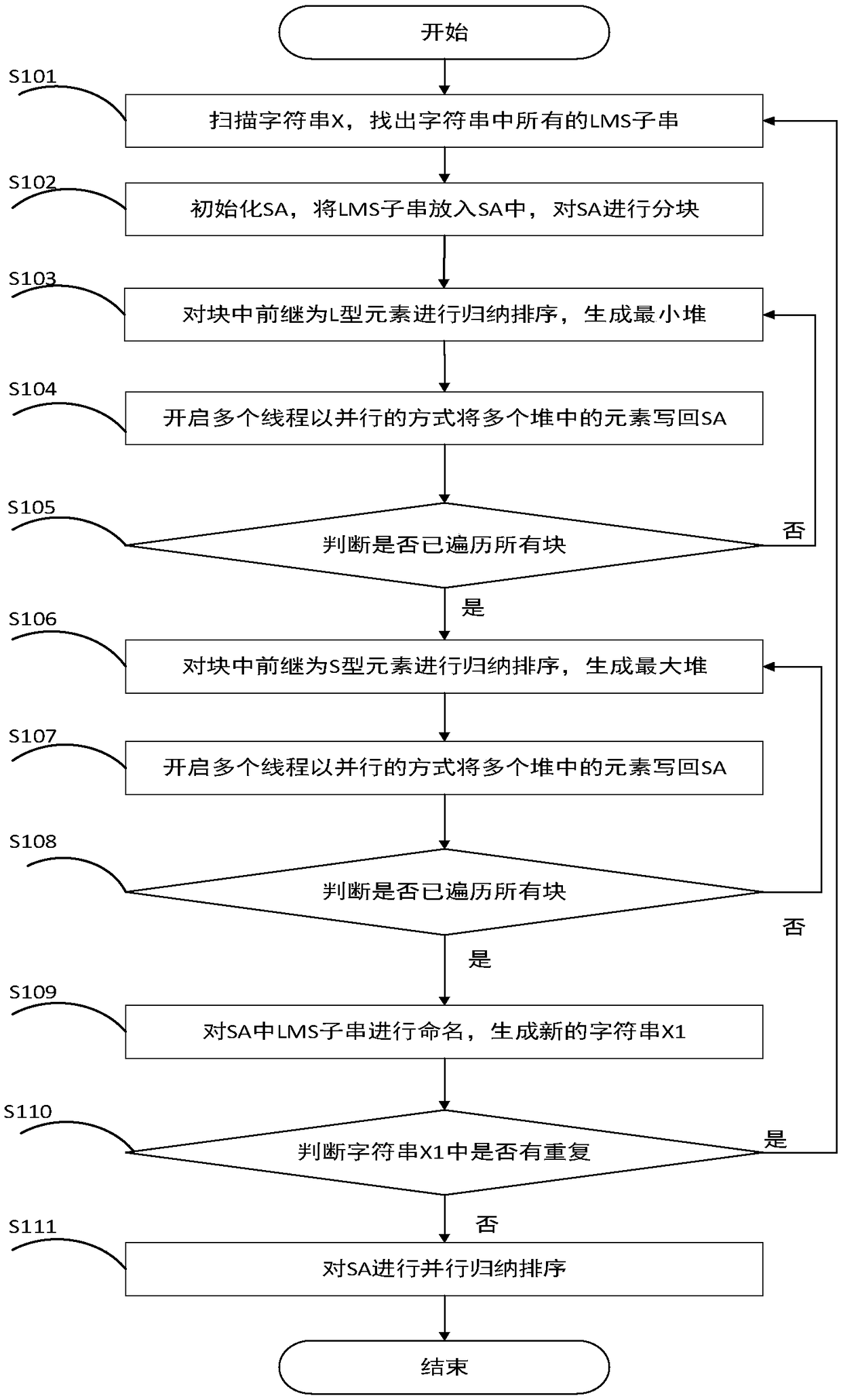

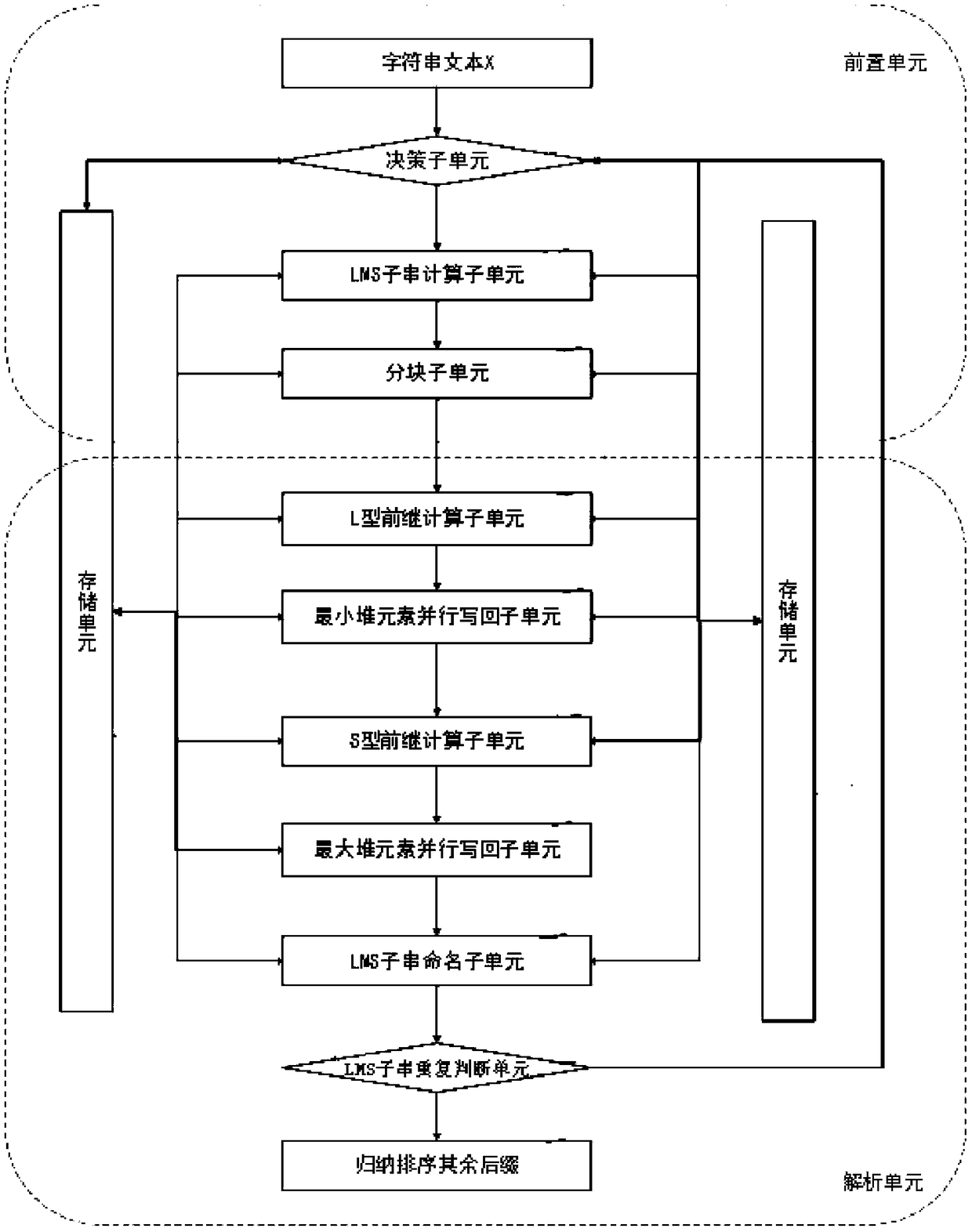

A parallel suffix sorting method and system

ActiveCN109375989ARun fastHigh speedupDigital data information retrievalMultiprogramming arrangementsInteraction timeSuffix sorting

The invention relates to a parallel suffix sorting method and system. For the string X of length n, when its size is much larger than the size of the computer Cache, the method of dividing SA into blocks is used to increase the hit rate of the Cache, reduce the interaction times between the Cache and the memory, and thus greatly reduce the sorting time of the string. The invention utilizes the parallel computing resources of the modern multi-core computer to parallelize the data access operation in the sorting process by using multi-threads, effectively improves the running speed of the algorithm, induces the parallelism of the sorting process to be high, the system can obtain a higher acceleration ratio, and greatly improves the work efficiency.

Owner:SUN YAT SEN UNIV

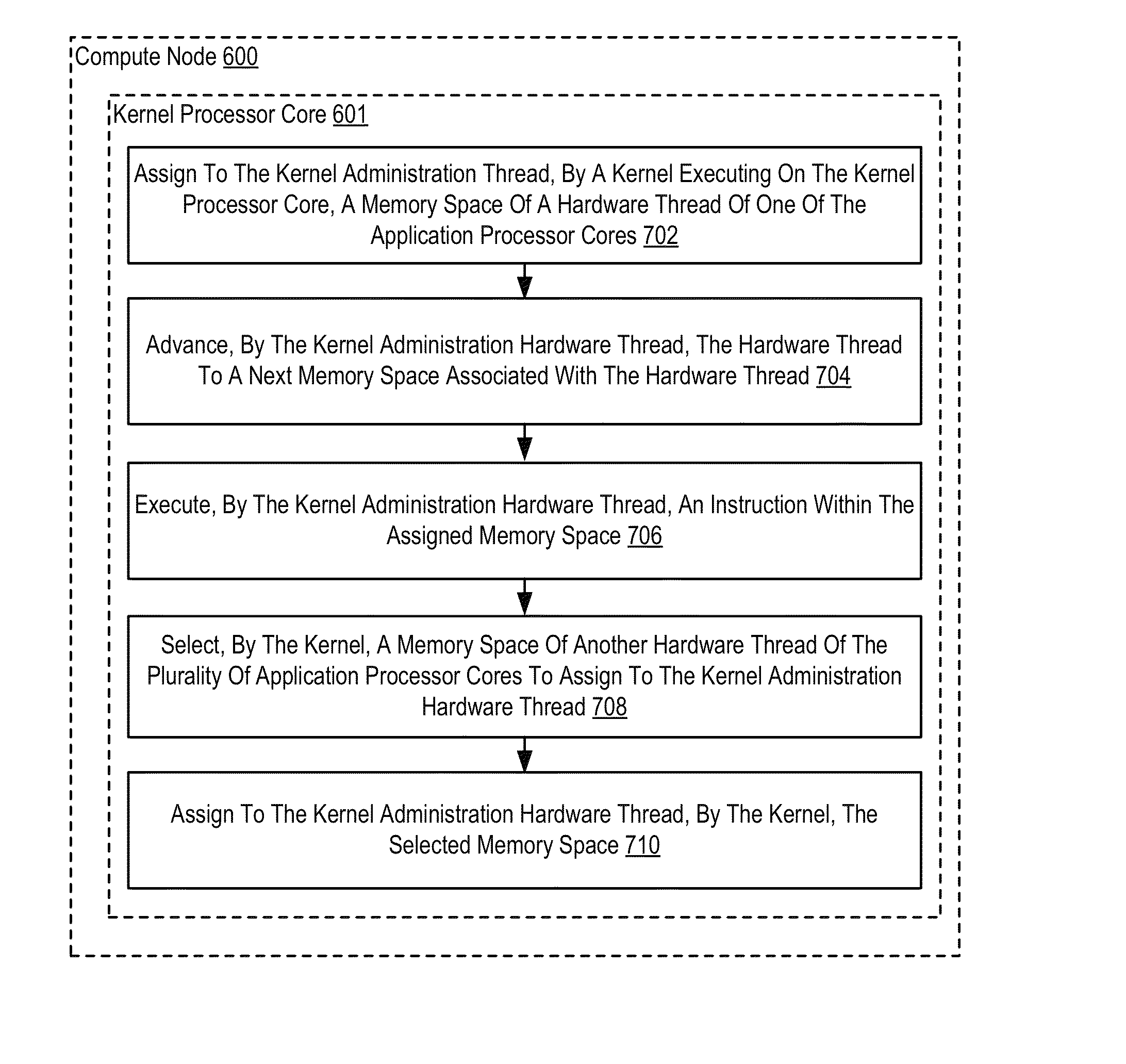

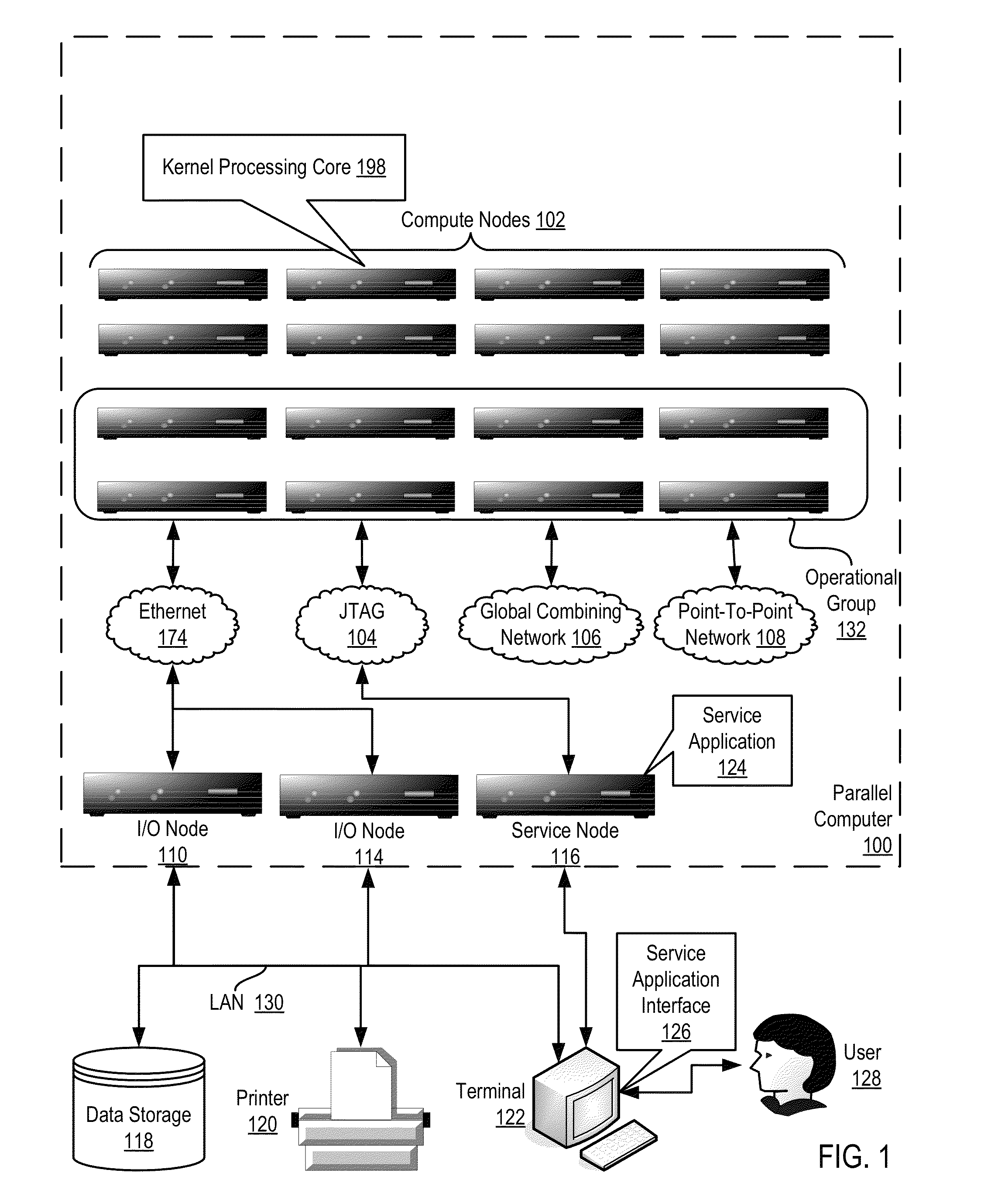

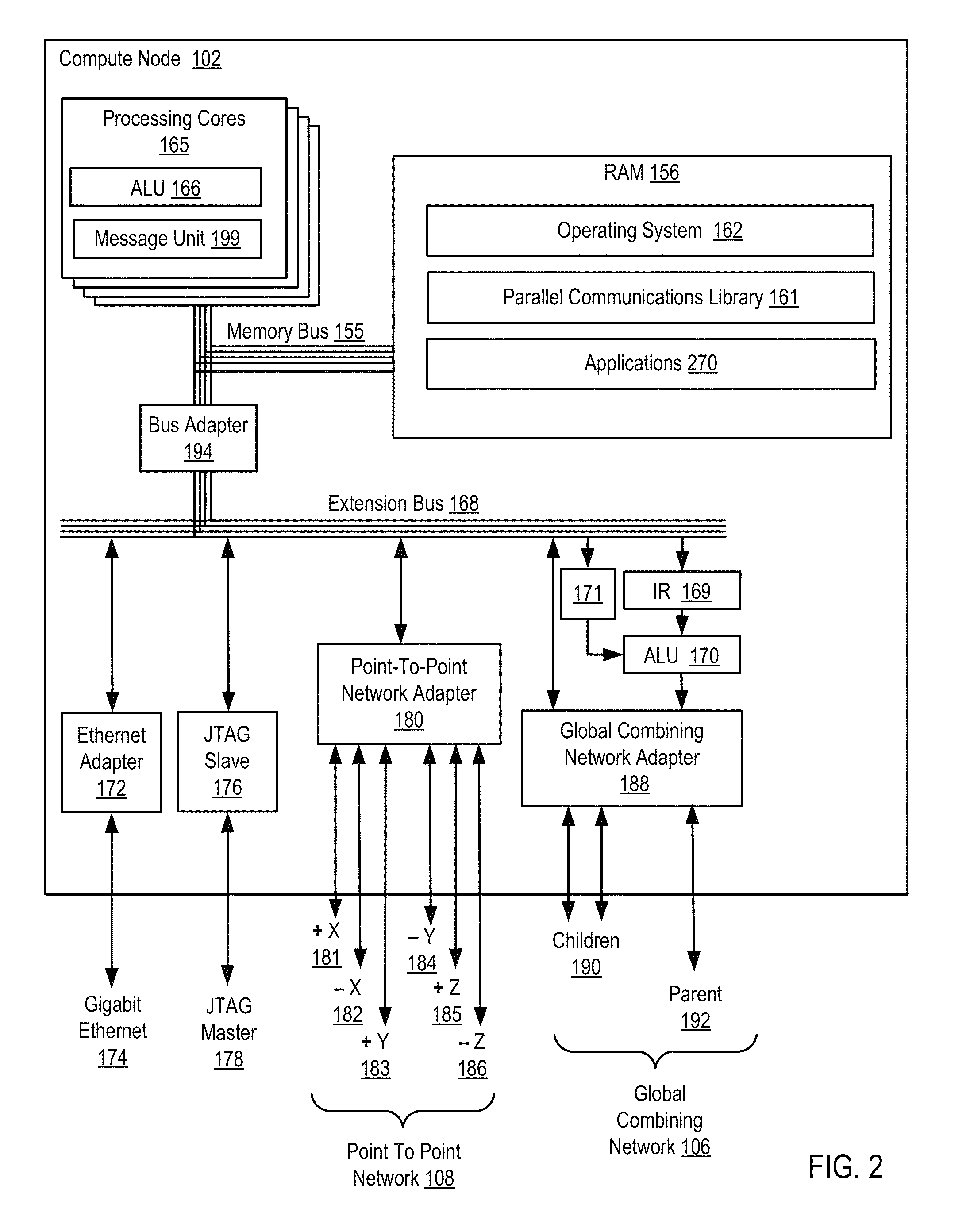

Utilizing a kernel administration hardware thread of a multi-threaded, multi-core compute node of a parallel computer

Methods, apparatuses, and computer program products for utilizing a kernel administration hardware thread of a multi-threaded, multi-core compute node of a parallel computer are provided. Embodiments include a kernel assigning a memory space of a hardware thread of an application processing core to a kernel administration hardware thread of a kernel processing core. A kernel administration hardware thread is configured to advance the hardware thread to a next memory space associated with the hardware thread in response to the assignment of the kernel administration hardware thread to the memory space of the hardware thread. Embodiments also include the kernel administration hardware thread executing an instruction within the assigned memory space.

Owner:INT BUSINESS MASCH CORP

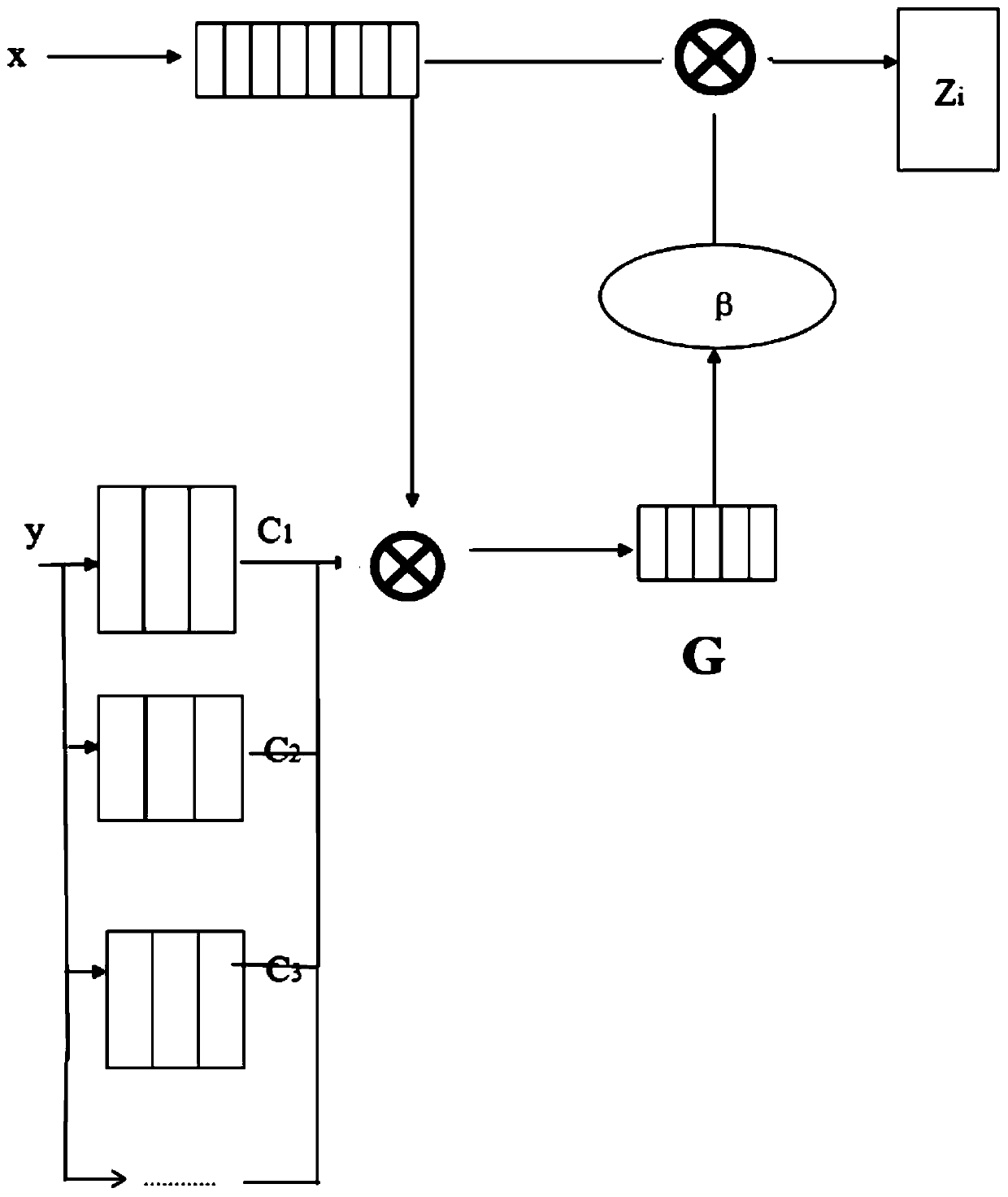

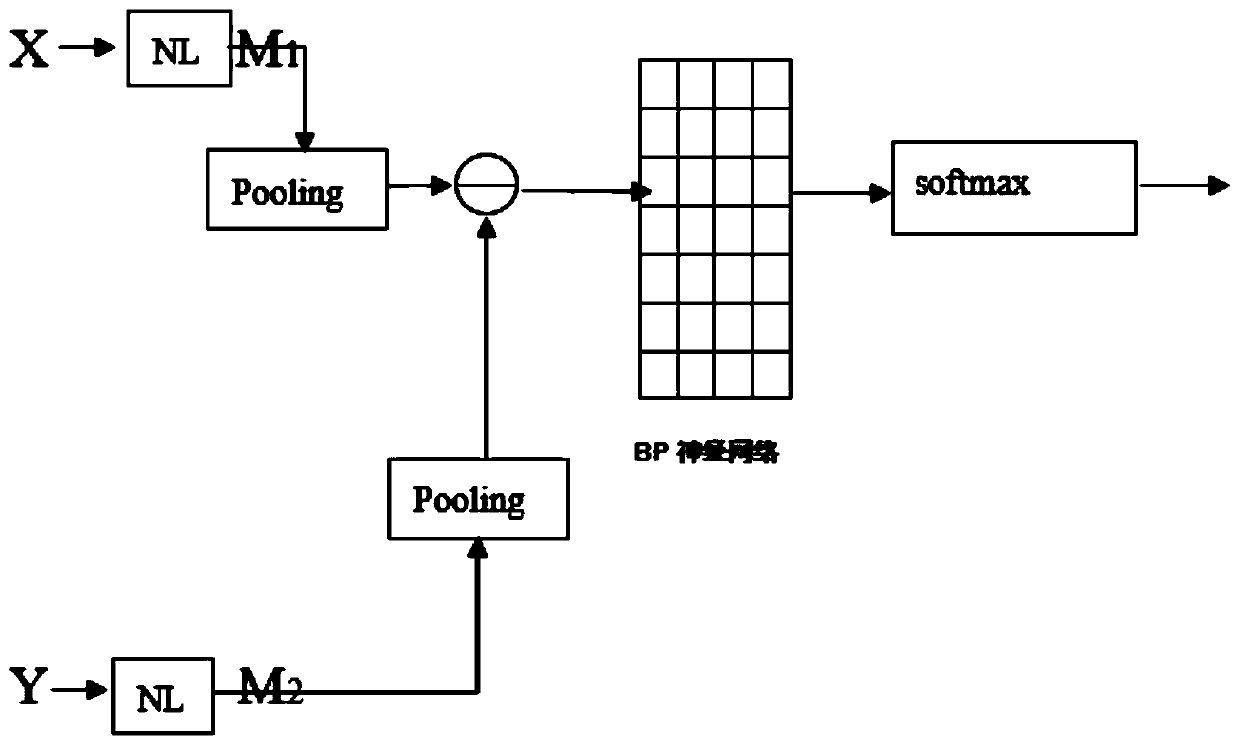

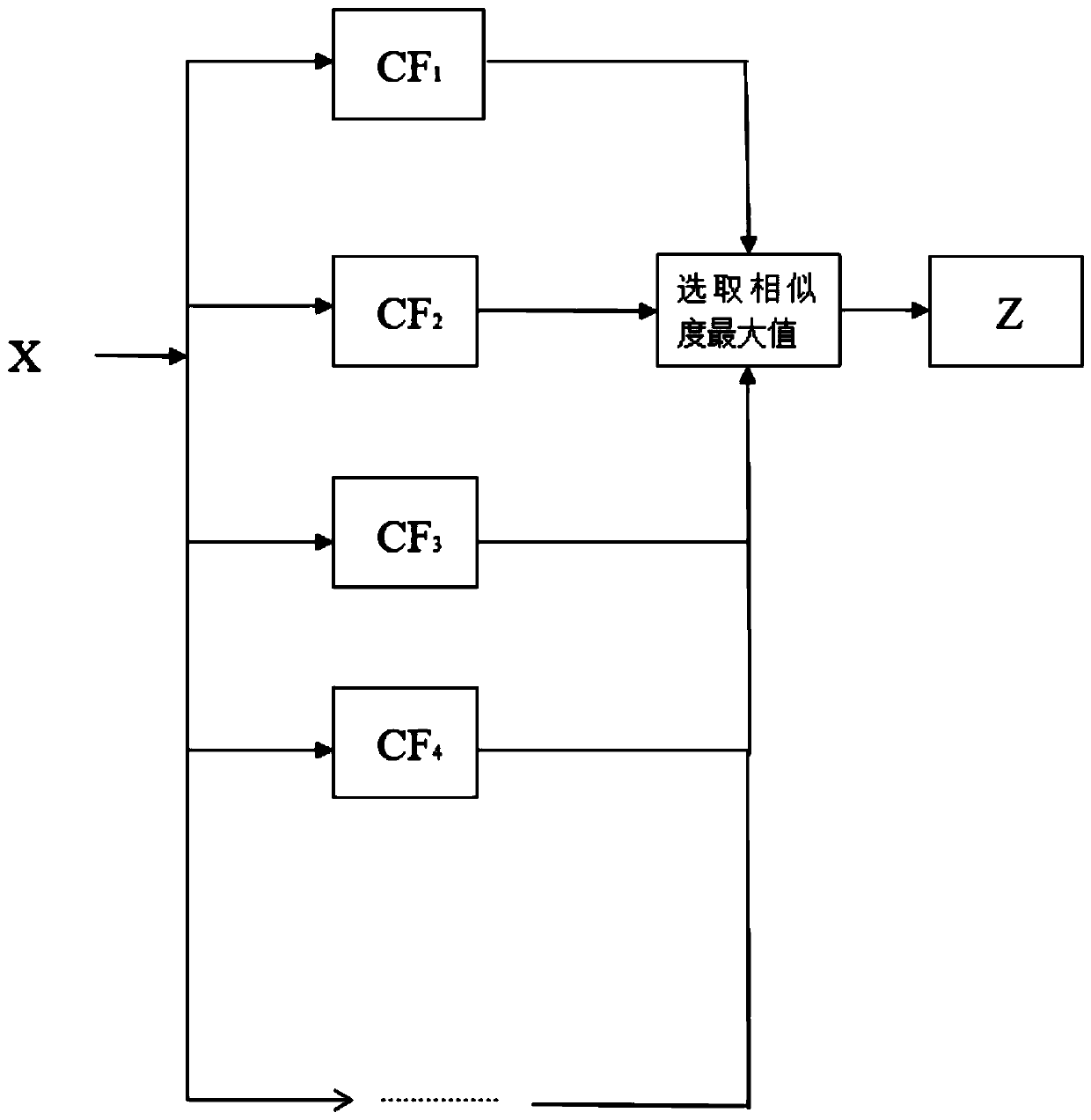

Chinese text difficulty assessment method based on siamese network and multi-core LEAM architecture

ActiveCN111090985AReduce the problem of underfittingImprove accuracyNatural language data processingEnergy efficient computingData setEngineering

The invention discloses a Chinese text difficulty assessment method based on a siamese network and a multi-core LEAM architecture. The method comprises the following steps: determining a classification basis and concluding different labes; correctly dividing different types of article data sets according to the classification basis; adopting an LEAM structure to allocate the weight of the action by using the distance between the spatial domain distribution of all the labes and the Embedded code of each word; embedding the label into an Embedded space of the Chinese text to obtain a multi-dimensional vector representation of the label; for each category, manually selecting an article which can best represent the category, and encoding the article to serve as an input of the Siamese network;obtaining a difference value between the obtained text code and a reference, and then sending the difference value to softmax classification; and finally obtaining a classification result according to the similarity with different types of texts. The label of the text and the words in the text are subjected to Embedded together, and the label is embedded into the space for multiple times at the same time, so that the boundaries of different labels are not simply coupled together, the problem of underfitting is greatly reduced, and the classification accuracy is improved.

Owner:HUAZHONG NORMAL UNIV

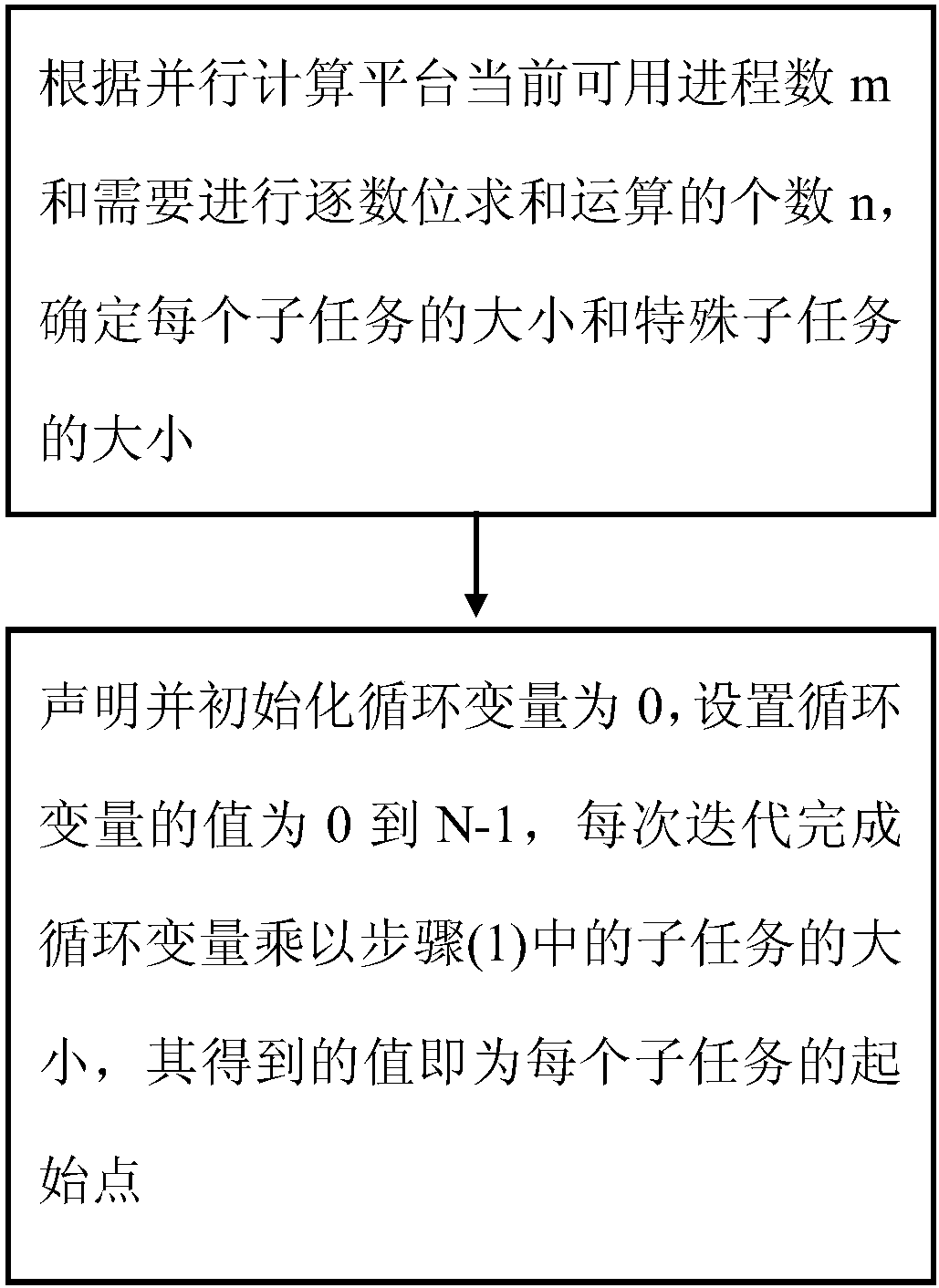

Big data-based cloud data distributing and dispatching method

The invention provides a big data-based cloud data distributing and dispatching method. The method comprises the following steps of: determining a size of each sub-task and a size of a special sub-task according the number m of current available processes and a number n of digit-by-digit summation operations of a parallel calculation platform; and declaring and initializing an iteration variable to be 0, setting a value of the iteration variable to be 0-N-1, and after each iteration is completed, respectively multiplying the iteration variable by the sizes of the sub-tasks in the step (1) so as to obtain values which are initial points of the sub-tasks, wherein N is a number of terms of a cache queue. According to the big data-based cloud data distributing and dispatching method, the operation speed can be improved by sufficiently utilizing a distributed parallel environment on the basis of a multicore calculation platform.

Owner:成都博睿德科技有限公司

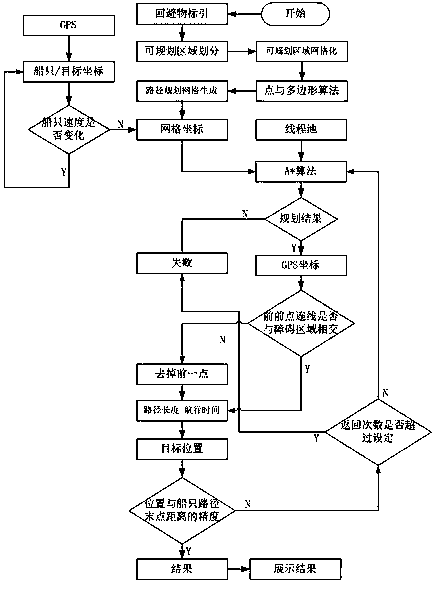

Multi-ship path planning algorithm for maritime pursuit or rescue

InactiveCN111506060ASolve full useSolve the problem that the path is not smoothPosition/course control in two dimensionsArea networkAlgorithm

The invention relates to path planning, in particular, a multi-ship path planning algorithm for marine pursuit or rescue. The algorithm comprises 15 steps, such as avoidance object indexing, planeablearea division, planeable area gridding, point and polygon algorithm execution, path planning grid generation, thread pool creation, GPS mapping-based grid coordinate generation, A* path planning algorithm execution. Compared with the prior art, the method solves the problems of unsmooth paths in the path planning of a moving target, the blockage of a main thread in a path planning calculation process, and the fully utilization of a modern multi-core processor by multi-ship simultaneous path planning.

Owner:YANTAI JIERUI NETWORK TRADING

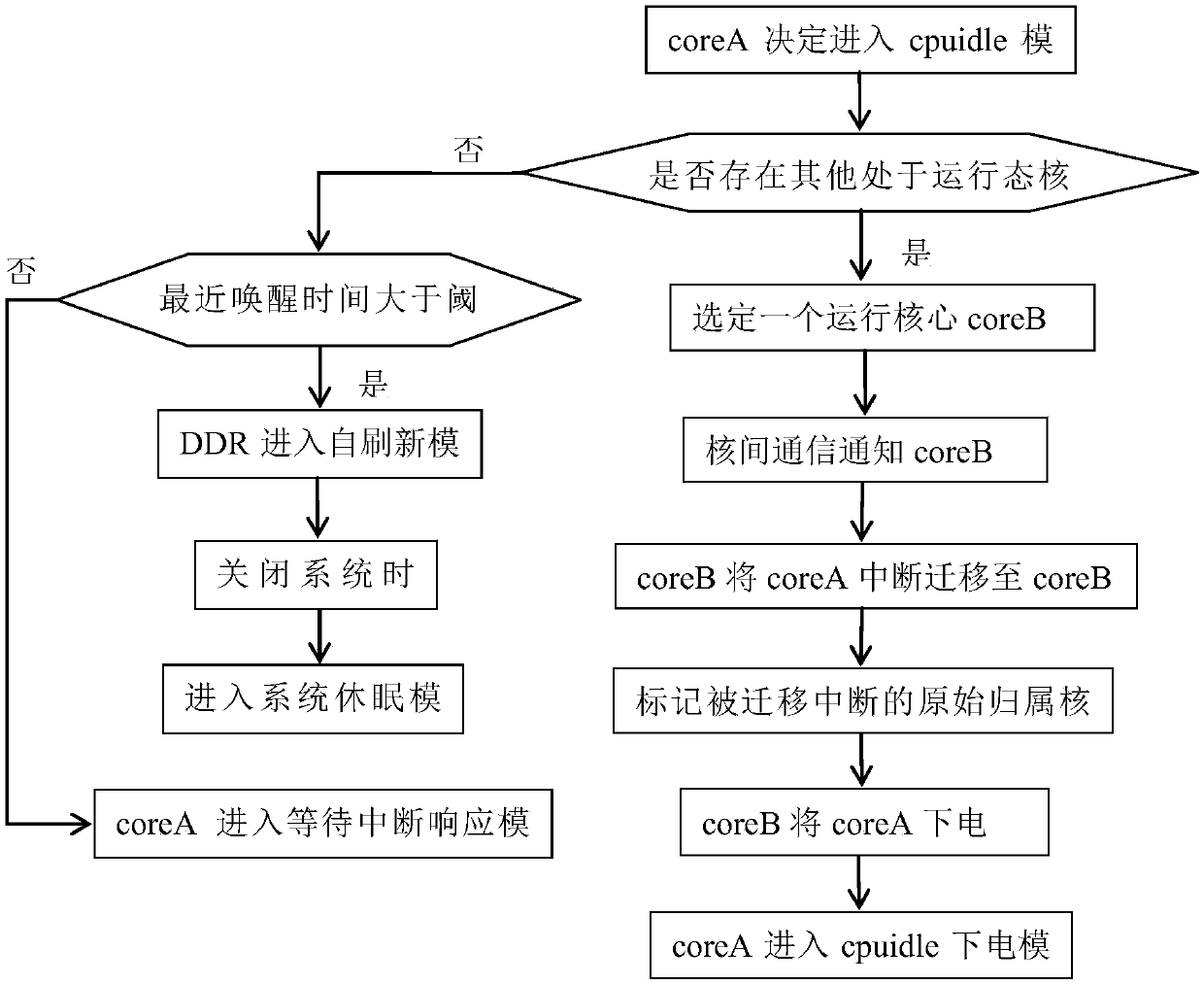

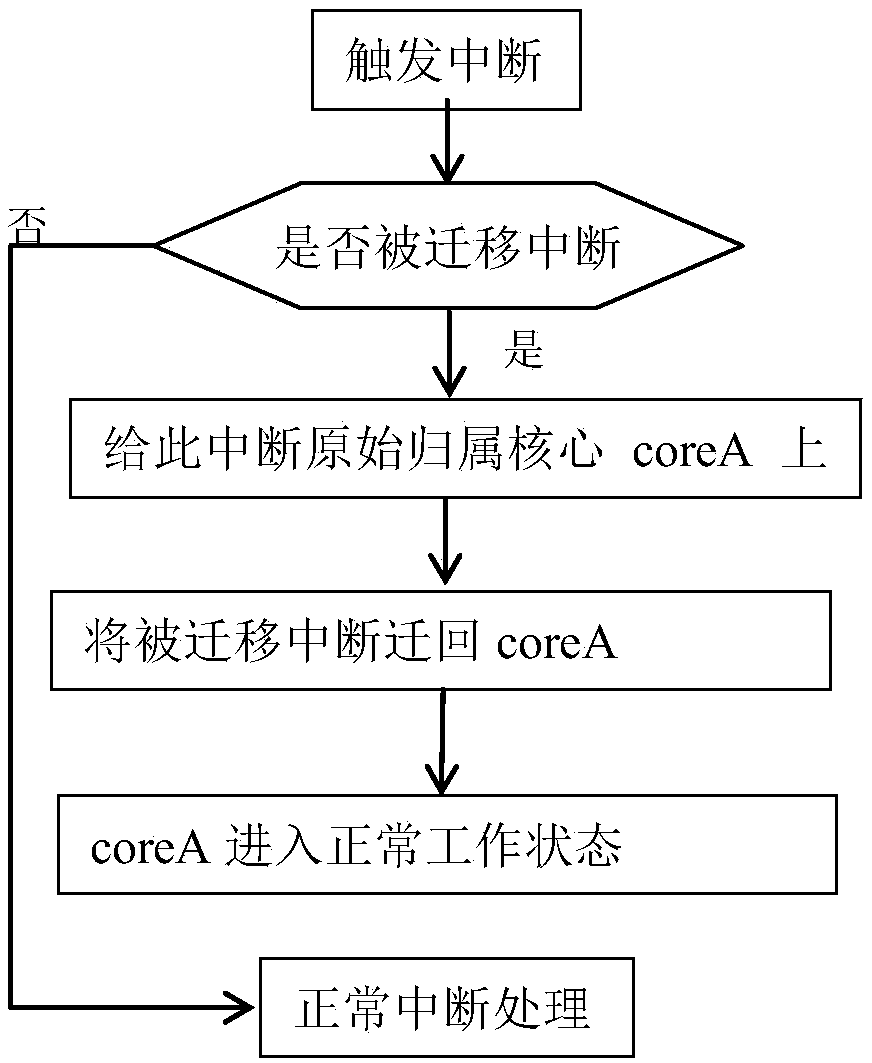

Idle state low-power-consumption mode implementation method of multi-core processor and processor

The invention discloses an idle-state low-power-consumption mode implementation method of a multi-core processor and a processor, which are used for at least solving the problems of higher power consumption, poorer performance and response lag in low-power-consumption management of the multi-core processor. The method comprises the steps that a first core in multiple cores in an idle state selectsa second core in a running state from the multiple cores, and the second core is triggered to execute power-off processing on the first core; the first core and the second core are different cores.

Owner:ALLWINNER TECH CO LTD

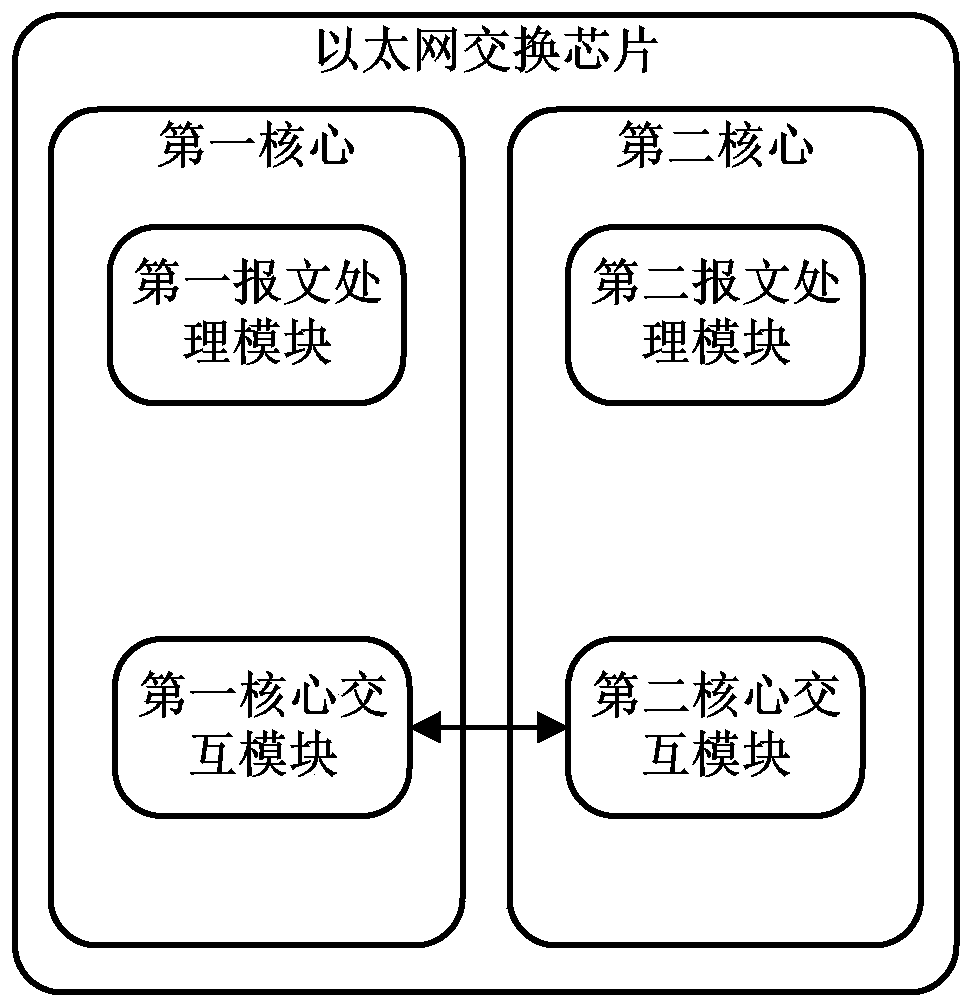

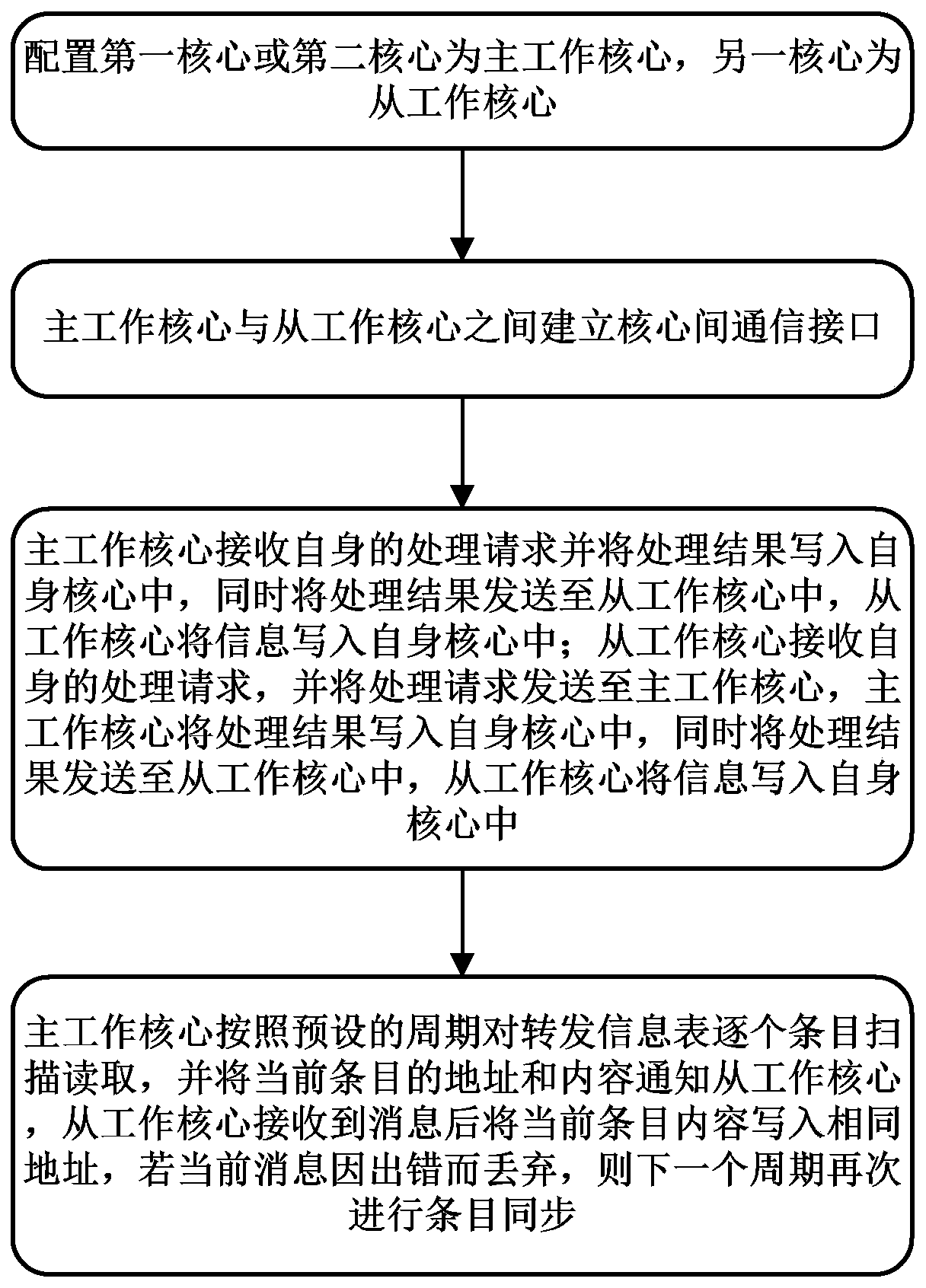

Method and device for synchronizing forwarding table of ultra-bandwidth multi-core Ethernet switch chip

ActiveCN111464447ASolving Interoperability IssuesLow costData switching networksCommunication interfaceHigh bandwidth

The invention discloses a method and a device for synchronizing a forwarding table of an ultrahigh-bandwidth multi-core Ethernet switch chip. The method comprises the following steps of: configuring amaster working core and a slave working core; establishing an inter-core communication interface between the master working core and the slave working core; enabling the master working core to receive the processing request of the master working core and writes a processing result into the master working core, meanwhile, sending the processing result to the auxiliary working core, and enabling the auxiliary working core to write information into the master working core; enabling the slave working core to receive the processing request of the slave working core and send the processing requestto the master working core, enabling the master working core to write a processing result into the slave working core and sends the processing result to the slave working core, and the slave working core writes information into the slave working core; and enabling the master working core to perform entry synchronization according to a preset period. According to the invention, the interoperation problem of two cores on one package is effectively solved, so that the external system behavior of the multi-core Ethernet switch chip is the same as that of a single core.

Owner:SUZHOU CENTEC COMM CO LTD

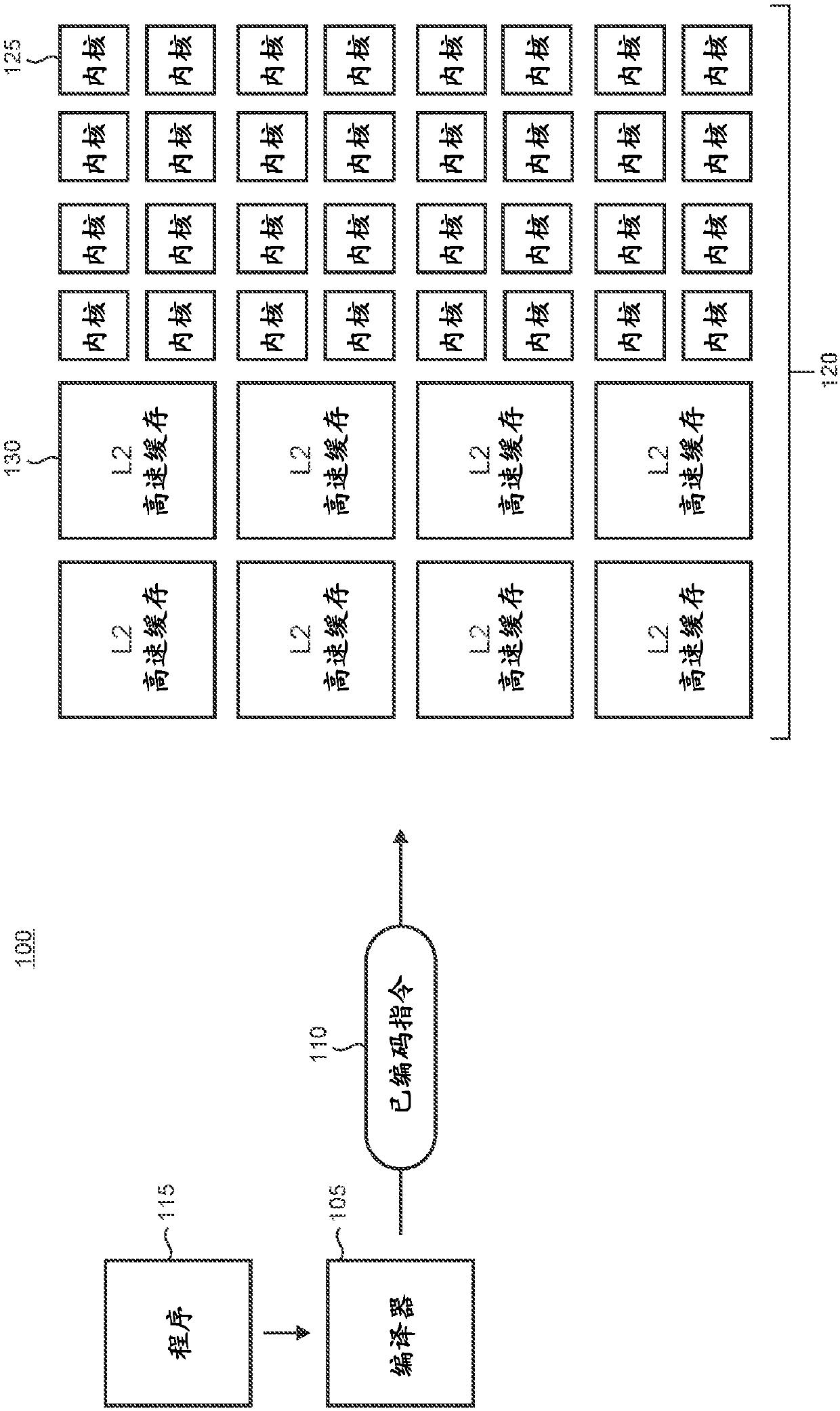

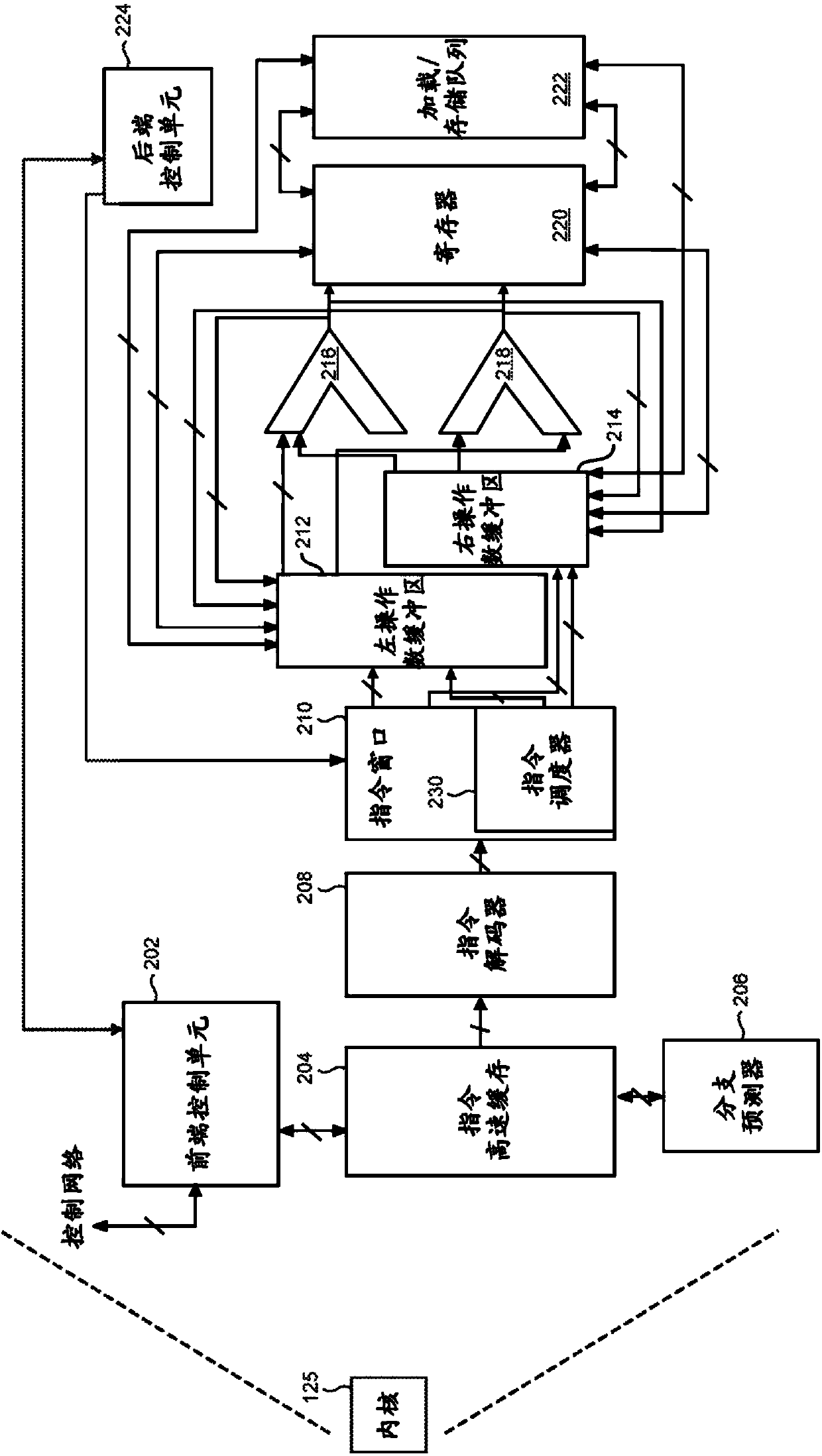

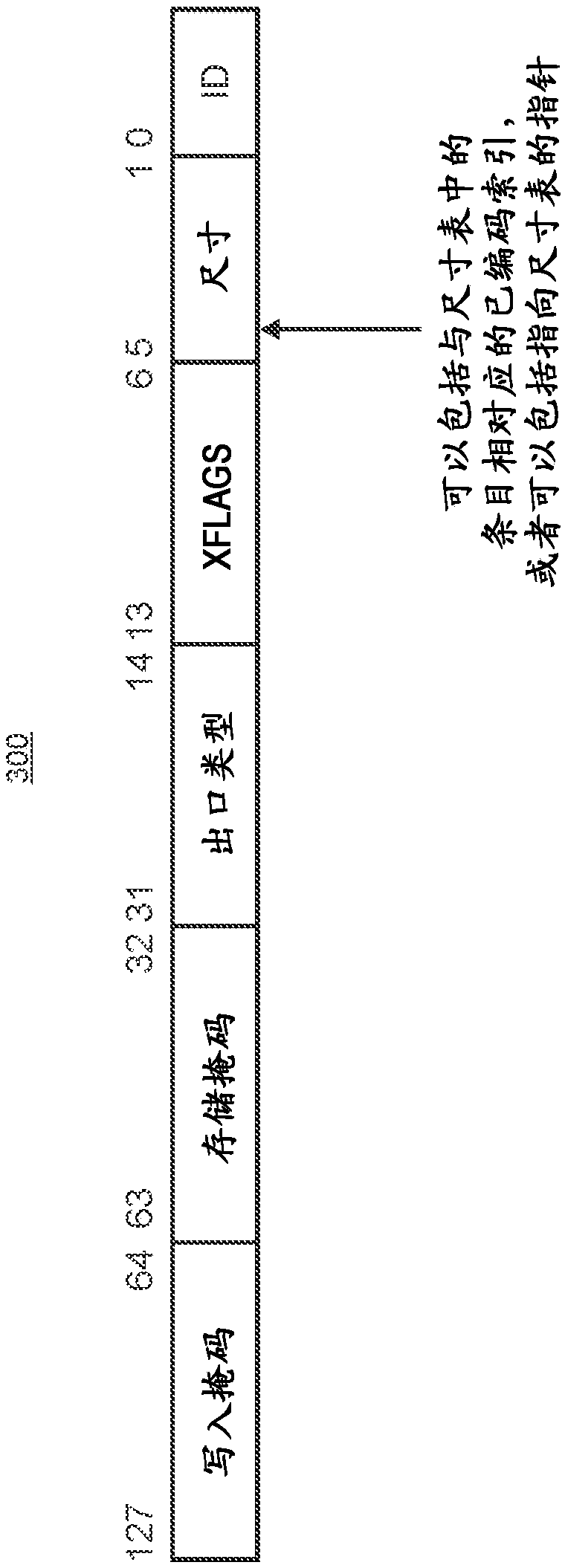

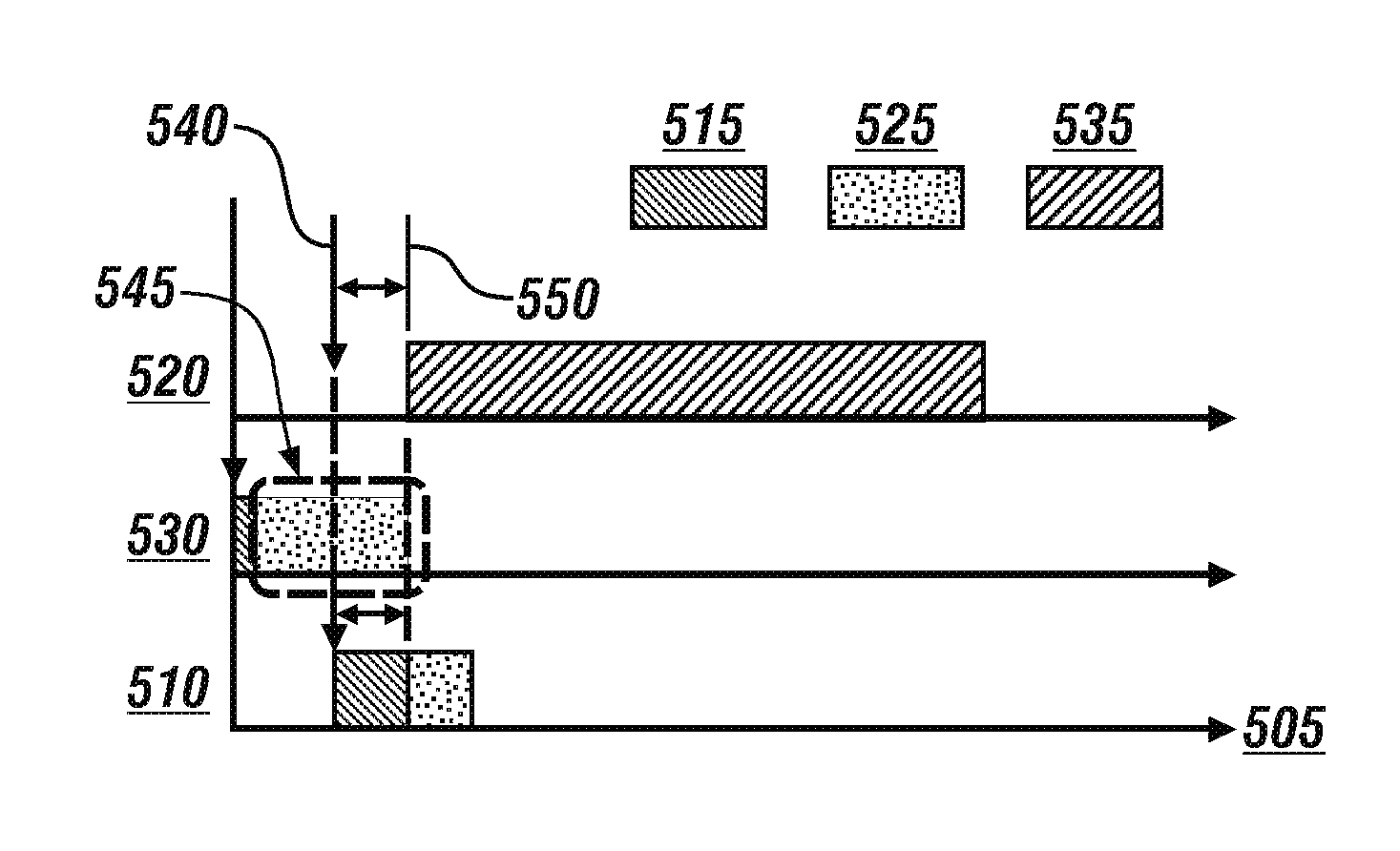

Decoupled processor instruction window and operand buffer

ActiveCN107810476AMemory architecture accessing/allocationInstruction analysisInstruction windowEngineering

A processor core in an instruction block-based microarchitecture is configured so that an instruction window and operand buffers are decoupled for independent operation in which instructions in the block are not tied to resources such as control bits and operands that are maintained in the operand buffers. Instead, pointers are established among instructions in the block and the resources so thatcontrol state can be established for a refreshed instruction block (i.e., an instruction block that is reused without re-fetching it from an instruction cache) by following the pointers. Such decoupling of the instruction window from the operand space can provide greater processor efficiency, particularly in multiple core arrays where refreshing is utilized (for example when executing program codethat uses tight loops), because the operands and control bits are pre-validated.

Owner:MICROSOFT TECH LICENSING LLC

Method and apparatus for improving processing performance of a multi-core processor

ActiveCN103577376AMultiprogramming arrangementsMultiple digital computer combinationsComputer architectureProcessing core

A method for managing task execution in a multi-core processor includes employing a spinlock to effect a dynamically enforceable mutual exclusion constraint and employing a multi-processor priority ceiling protocol to effect the dynamically enforceable mutual exclusion constraint to synchronize a plurality of tasks executing in the first and second processing cores of the multi-core processor.

Owner:GM GLOBAL TECH OPERATIONS LLC +1

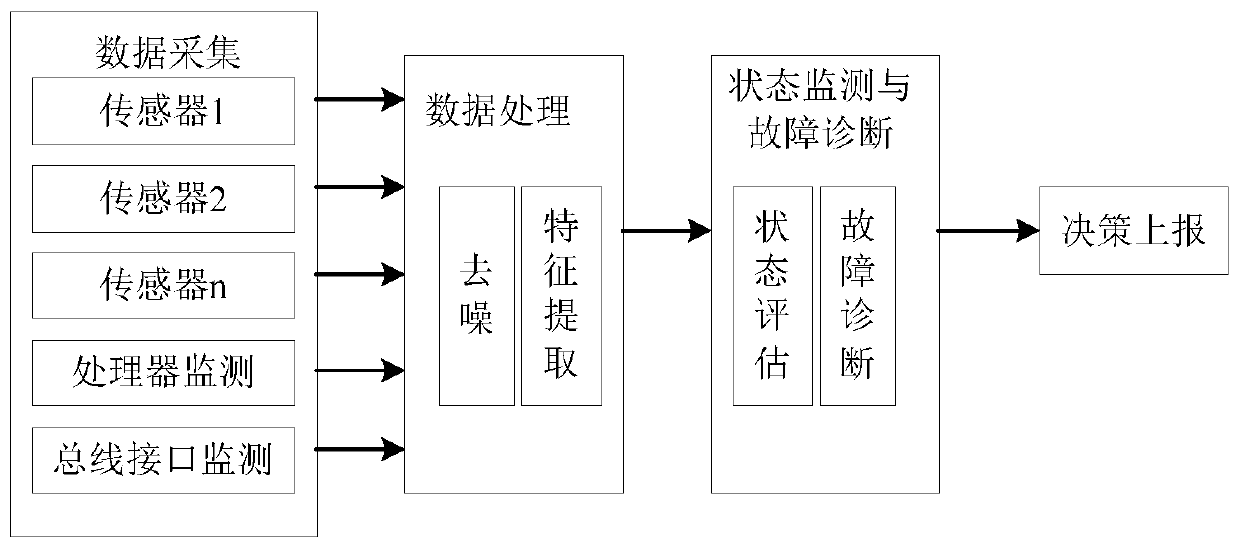

Fault detection and health management method for multiprocessor computer

PendingCN110989427AImplement fault detectionResolve detectionProgramme controlComputer controlFeature extractionMulti processor

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

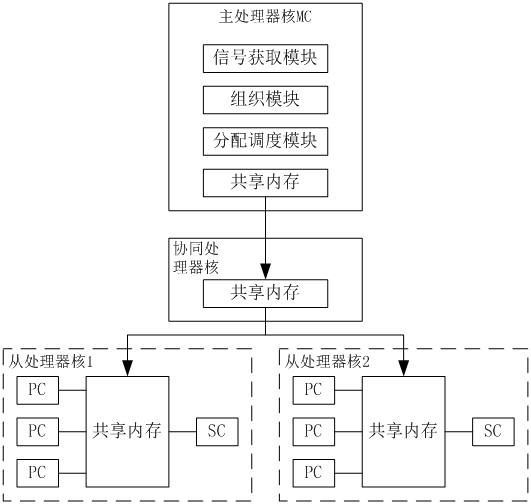

Multi-core security chip processor based on logic expansion and processing method thereof

ActiveCN112527514ALoad balancingImprove performanceResource allocationDigital computer detailsComputer architectureControl signal

The invention provides a multi-core security chip processor based on logic expansion and a processing method thereof. The processor comprises a master processor core and a plurality of slave processorcores, and the master processor core comprises a signal acquisition module, an organization module and a distribution scheduling module; the signal acquisition module is used for acquiring externallytransmitted control signals in real time, and the organization module is used for performing dynamic logic organization on the plurality of slave processor cores according to the security operation logic to form a dynamic execution architecture matched with the security operation logic; the distribution scheduling module is used for decomposing the security operation into a plurality of operationtasks according to the security operation logic, distributing the operation tasks to the corresponding slave processor cores under the dynamic execution architecture, and cooperatively scheduling theoperation tasks among the plurality of slave processor cores; and the plurality of slave processor cores are respectively used for running the operation tasks allocated and scheduled by the master processor core. The method has the advantages of being high in safety operation efficiency, accurate in operation result, balanced in inter-core load, capable of improving the performance of the multi-core processor and the like.

Owner:ZHEJIANG GEOFORCECHIP TECH CO LTD

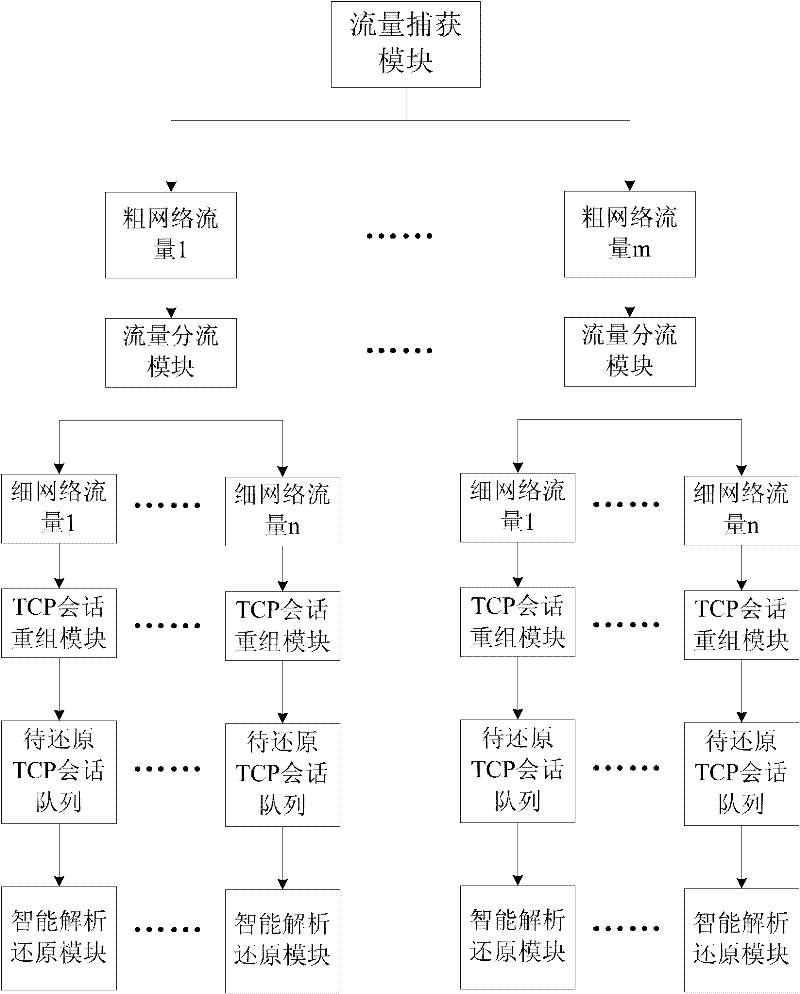

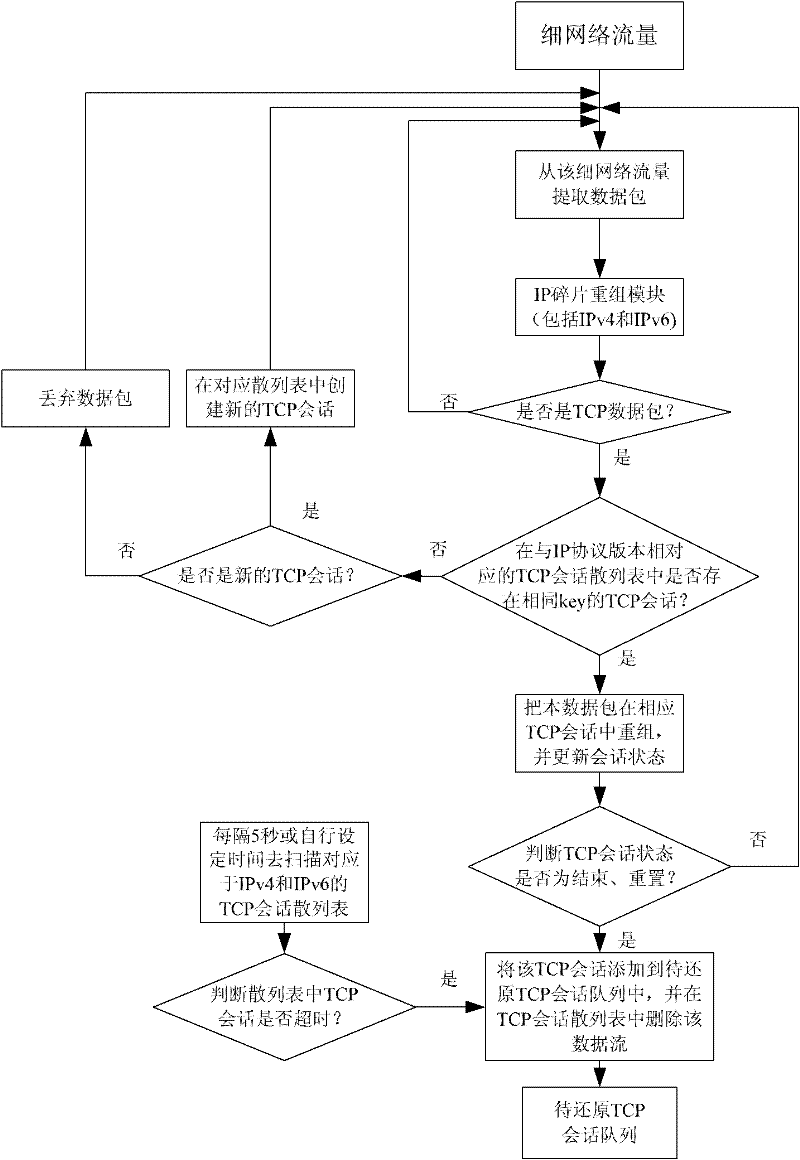

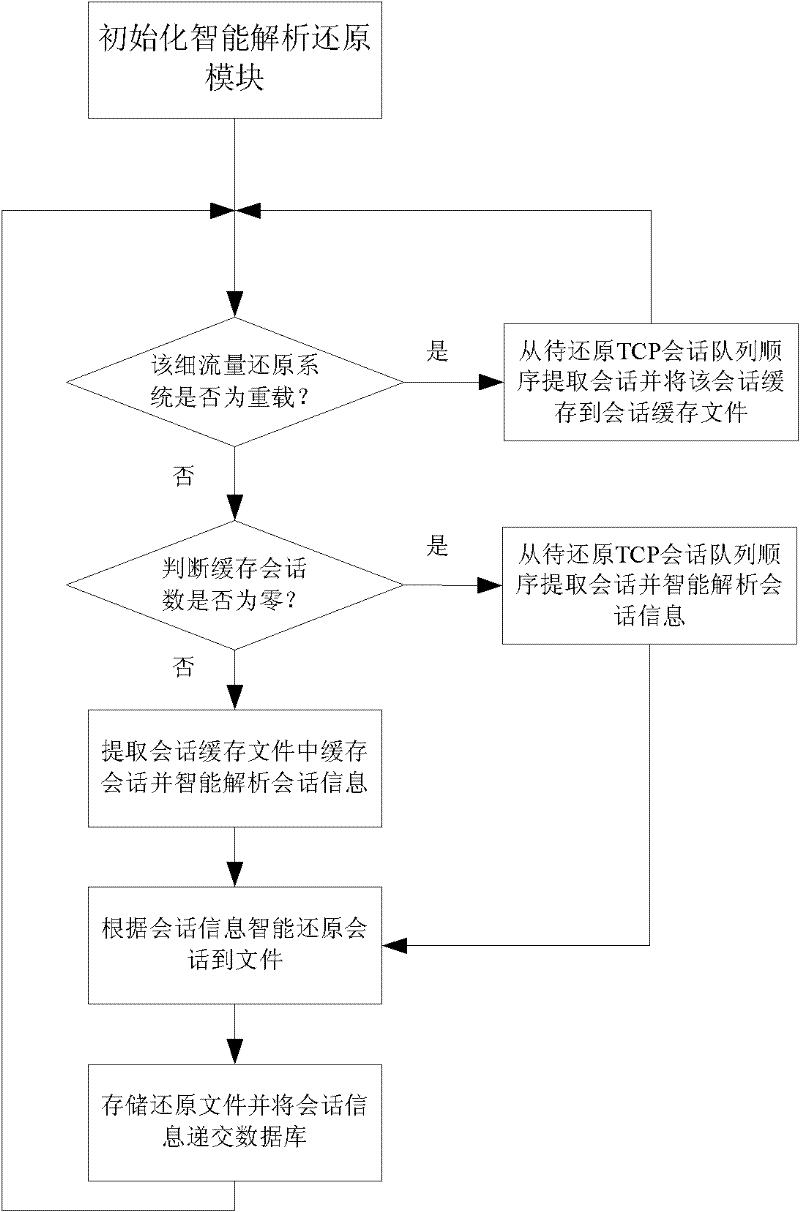

Network flow recovery method

The invention relates to a network flow recovery method, which belongs to the technical field of Internet and discloses a method for recovering network flow to a file. The method adopts a two-stage parallel strategy method to fully make the best of the processing efficiency of a multi-core computer, which comprises the following steps: firstly acquiring high-speed flow, adopting a Mac address xorand IP address xor method to split flow twice, and resolving the acquired initial flow into a plurality of thin flows to realize the two-stage parallel resolution of the flow; then adopting a 'producer-consumer model' loose coupling multithreading framework between working modules with data transfer in a thin flow recovery flow path to realize parallel on a threading level. In addition, the method realizes load balancing on each thin flow, and supports IPv4 and IPv6 protocols simultaneously. The invention aims to solve the problem of converting 'invisible' network flow into information which can be directly processed by a computer under high-speed network bandwidth, and provides technical support for identifying and blocking illegal network information transmission.

Owner:XI AN JIAOTONG UNIV