Idle state low-power-consumption mode implementation method of multi-core processor and processor

A low-power mode and idle state technology, applied in the computer field, can solve the problems of high power consumption, poor performance, and response lag of multi-core processors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

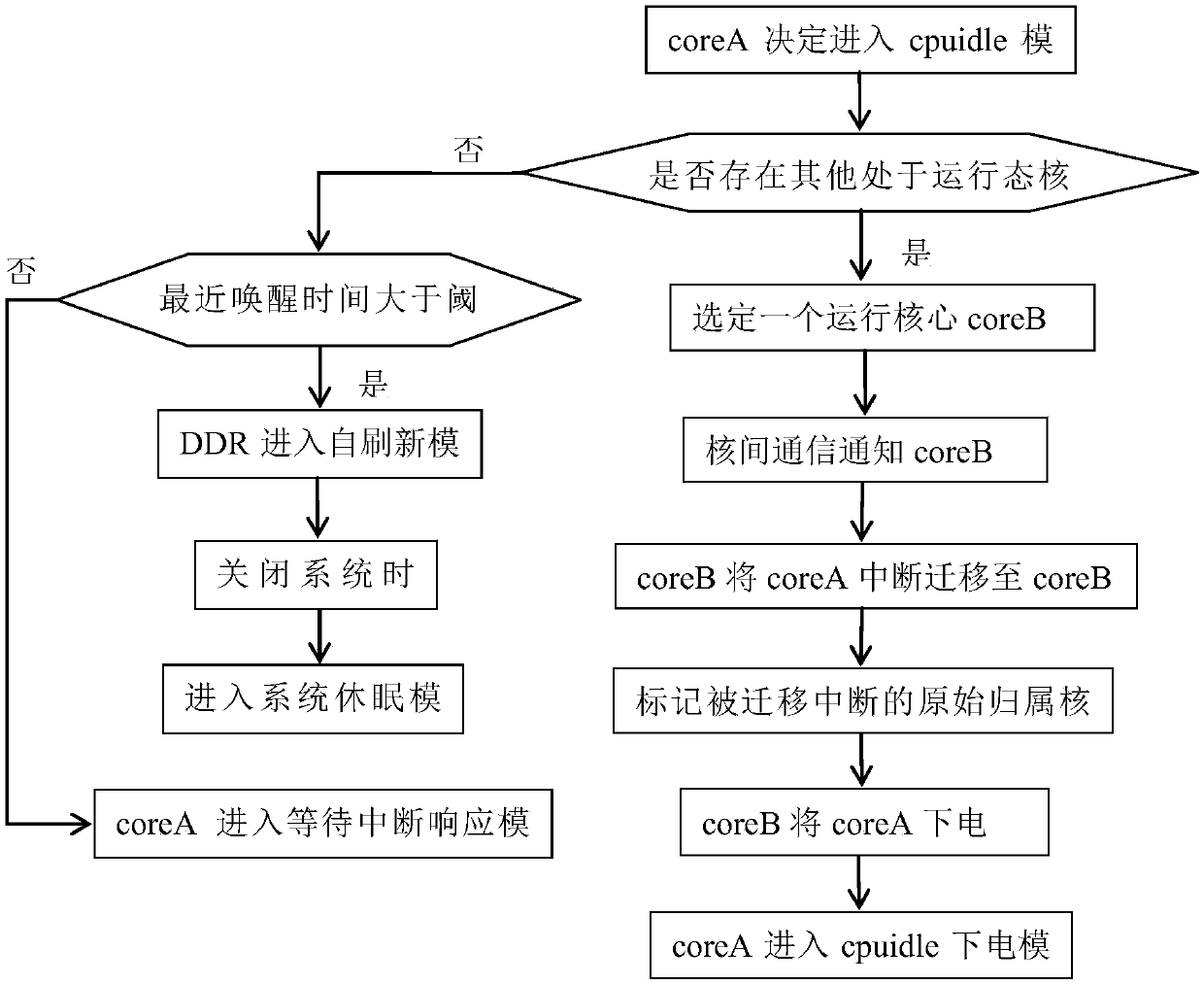

[0035] An embodiment of the present invention provides a method for implementing an idle state low-power CPUidle mode of a multi-core processor, the method comprising:

[0036] The first core in the multi-core in the idle state selects the second core in the running state from the multi-core, and triggers the second core to perform power-off processing on the first core; the first core and all The second core is a different core.

[0037] In the embodiment of the present invention, when the core has nothing to do (that is, it is in an idle state), it actively shuts down the core, wakes up the core in real time to perform task processing when the core interrupt comes, and performs power-off processing on the first core through the second core, thereby cleverly Various defects in the prior art are avoided, and the problems of high power consumption, poor performance and lagging response in low power consumption management of multi-core processors are effectively solved.

[0038...

Embodiment 2

[0076] An embodiment of the present invention provides a processor, where the processor includes multiple cores connected to each other;

[0077] The first core among the multi-cores in the idle state is configured to select a second core in the running state from the multi-cores, and trigger the second core to perform power-off processing on the first core; the first The core and the second core are different cores.

[0078] Wherein, the first core may be specifically configured to send inter-core communication information to the second core, where the inter-core communication information is used to instruct the second core to perform power-off processing on the first core;

[0079] The second core is configured to power off the first core when receiving the inter-core communication.

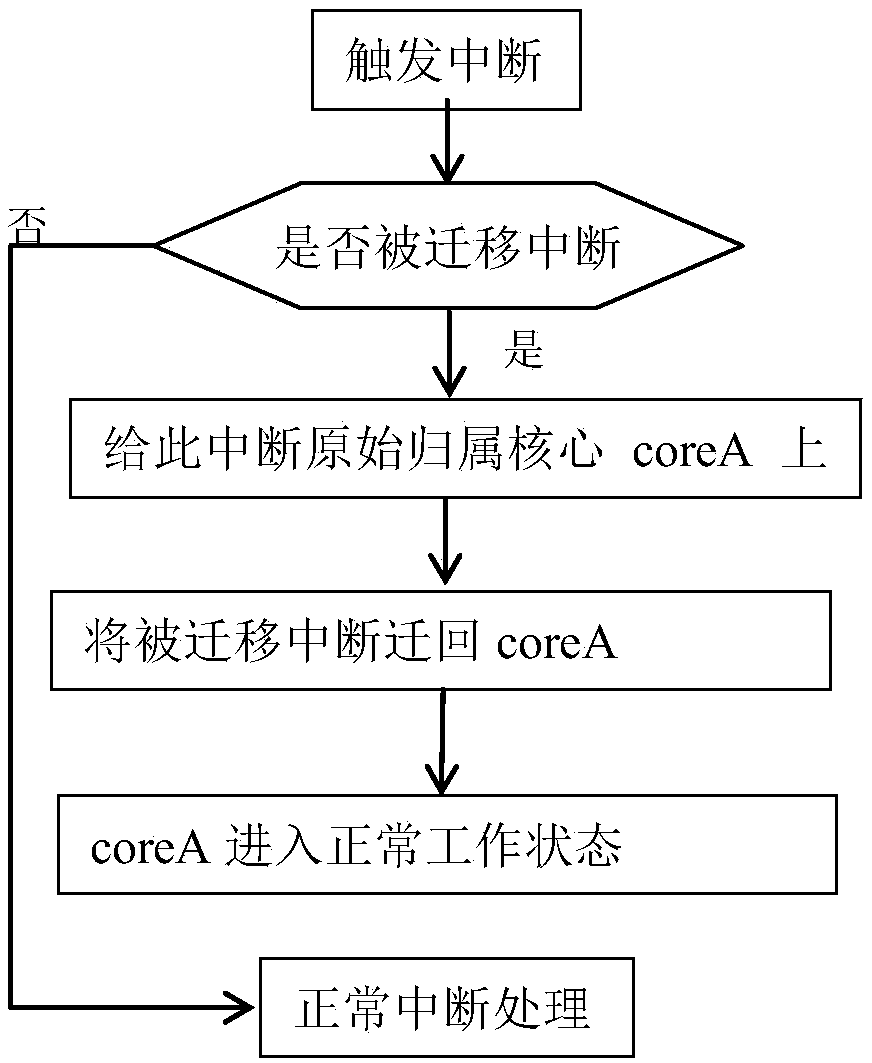

[0080] Wherein, when the second core receives the inter-core communication, before powering off the first core, it may also be used to migrate the first interrupt source that the first core is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More