Programmable 50%-duty cycle frequency divider

A frequency divider and ratio technology, applied in the field of programmable frequency divider with 50% duty ratio, can solve the problem of increasing the difficulty of counter design, limiting the working frequency of frequency divider, reducing the adjustment range of frequency division coefficient of programmable frequency divider, etc. problem, to achieve the effect of increasing the maximum operating frequency, improving the clock duty cycle, and simple structure

Active Publication Date: 2011-04-27

CHANGSHA JINGJIA MICROELECTRONICS

View PDF3 Cites 18 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

For the digital method, it is necessary to design a decimal counter with 0.5 cycles, which limits the operating frequency of the frequency divider and increases the difficulty of counter design. For the programmable frequency divider, it will inevitably reduce the adjustment of the frequency division coefficient of the programmable frequency divider scope

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

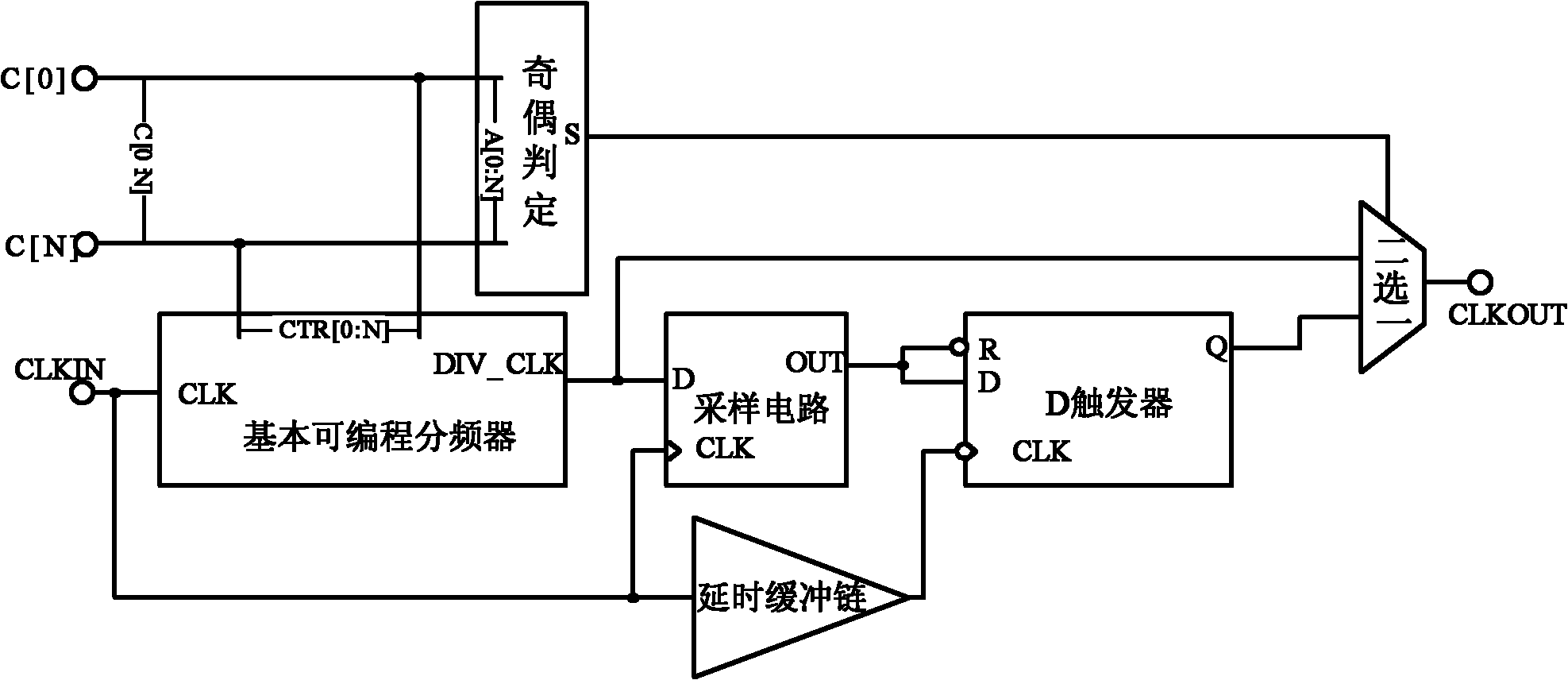

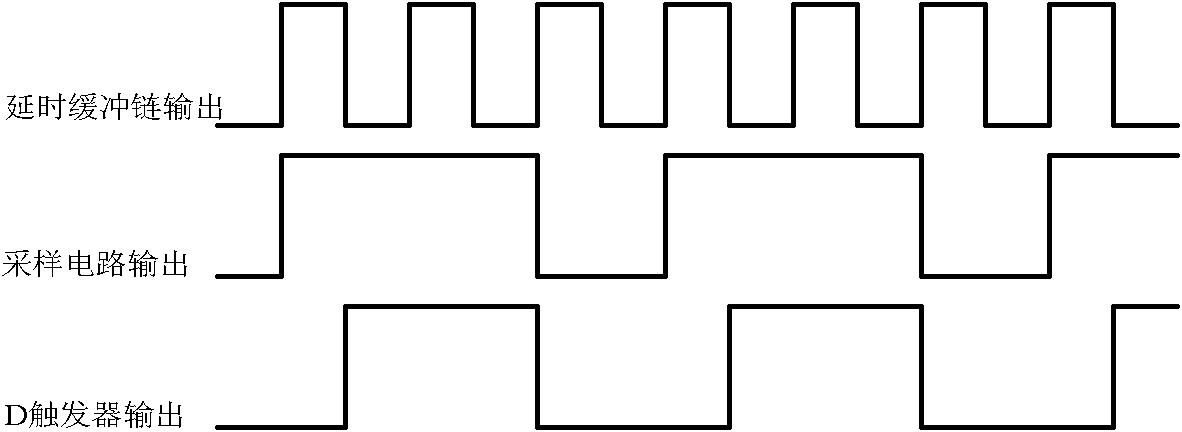

The invention discloses a programmable 50%-duty cycle frequency divider which comprises a basic programmable frequency divider, a sampling circuit, a D (DICE (Dual Interlocked Cell)) trigger, a delay buffer chain, an odd-even decision circuit and an alternative multi-path selector. Aiming at the duty cycle problem of clock output of a programmable frequency divider during the odd frequency division of the programmable frequency divider, the basic programmable frequency divider is adopted to perform frequency division for an original clock; a clock with 50% duty cycle is output during even frequency division; a clock, the difference of a high level and a low level of which is one original clock period, is output during odd frequency division; and then, a half original clock period is respectively added to and subtracted from a high level and a lower level of the odd frequency division clock to generate an odd frequency division clock with 50% duty cycle; and thus, the programmable frequency divider can output an 50%-duty cycle clock in any frequency division ratio.

Description

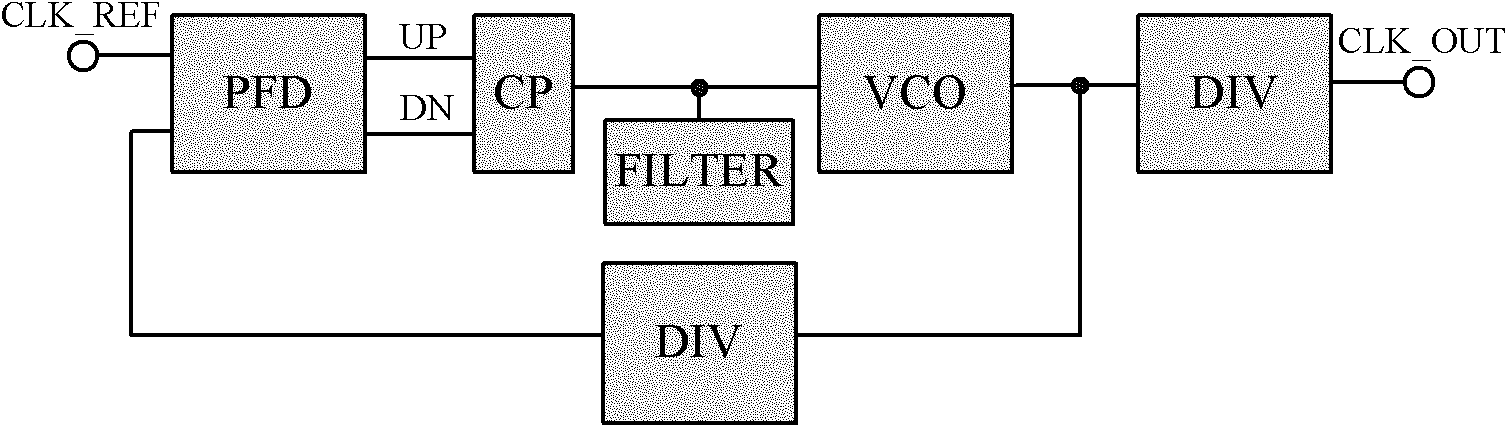

technical field [0001] The invention mainly relates to the field of integrated circuit design that needs frequency division processing of a clock, such as a phase-locked loop, and particularly refers to a programmable frequency divider with a duty ratio of 50%. Background technique [0002] Programmable frequency divider is widely used in integrated circuits for clock frequency division, and is one of the key modules in the frequency synthesis phase-locked loop. like figure 1 As shown, in the frequency synthesis phase-locked loop, the frequency of the clock signal output by the voltage-controlled oscillator (VCO) is divided, and then the frequency and phase detection are carried out with the reference signal, so that the frequency and phase of the frequency-divided clock and the reference clock are It is fully aligned to realize the functions of frequency synthesis and phase locking. Generally, the output clock of the phase-locked loop needs to be multiplied by a fractiona...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): H03K23/50

Inventor 李俊丰陈怒兴陈宝民蒋仁杰石大勇郭斌谭晓强

Owner CHANGSHA JINGJIA MICROELECTRONICS