Clock dynamic switching circuit

A technology for switching circuits and clocks, applied in electrical components, pulse processing, generating/distributing signals, etc., can solve problems such as circuit abnormalities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

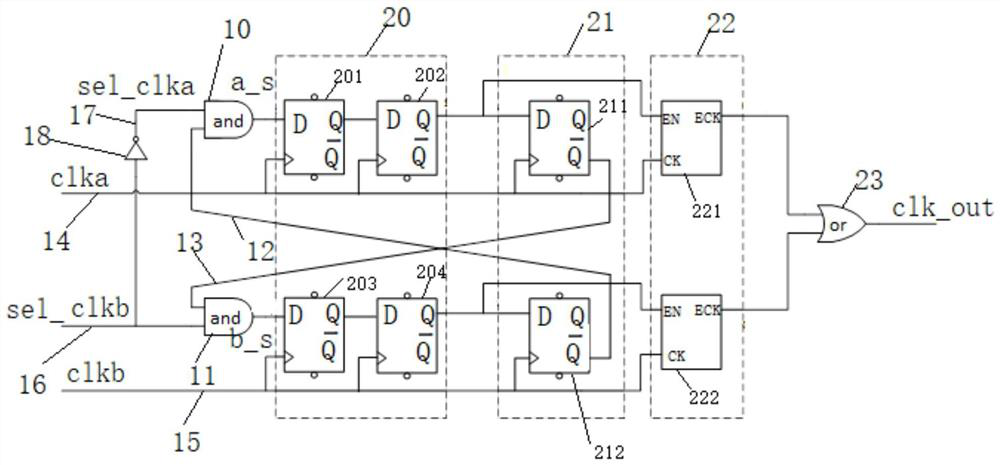

[0031] Please refer to figure 1 , This embodiment provides a clock dynamic switching circuit, which includes: a first AND gate 10, a second AND gate 11, a first clock signal line 14, a second clock signal line 15, a first clock enable signal line 17, The second clock enable signal line 16 , the first feedback signal line 13 , the second feedback signal line 12 , the level synchronization circuit 20 , the clock gating circuit 21 and the OR gate circuit 23 . Wherein, the level synchronization circuit 20 includes a first level synchronization unit and a second level synchronization unit, such as figure 1 The upper half of the mid-level synchronization circuit 20 is a first level synchronization unit, and the lower half is a second level synchronization unit; the output end of the second feedback signal line 12 and the first clock enable signal line 17 are respectively connected to the first level synchronization unit. An input terminal of an AND gate 10 is connected, the output ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More