Arithmetic logic unit using asynchronous circuit to implement

An arithmetic logic unit, asynchronous circuit technology, applied in computing, electrical digital data processing, program control design, etc., can solve problems such as clock skew, complex condition control logic, etc., to achieve small circuit area, high performance, low The effect of power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

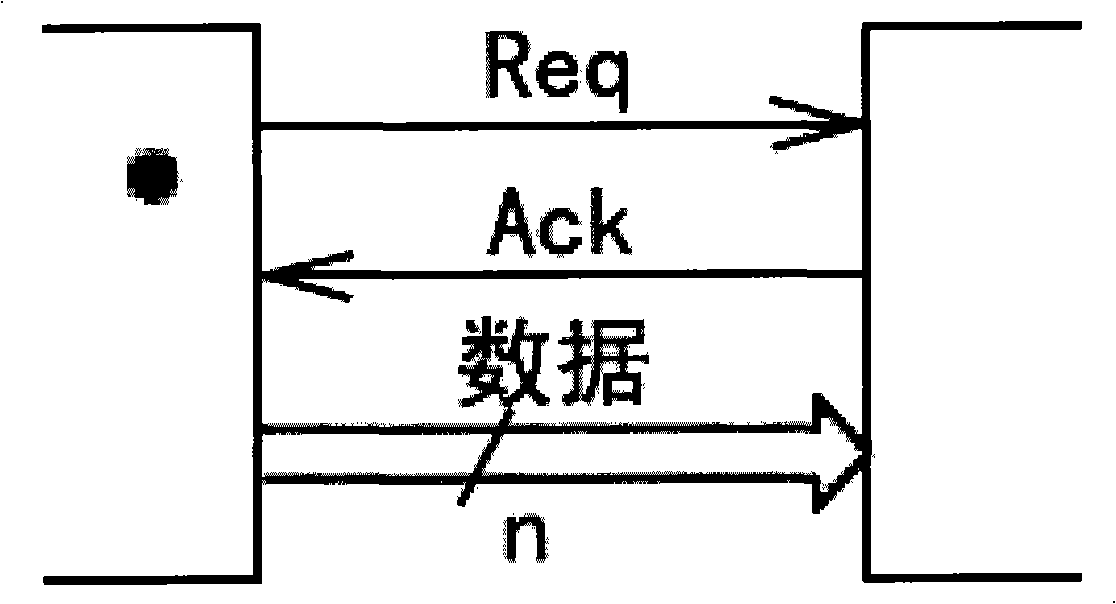

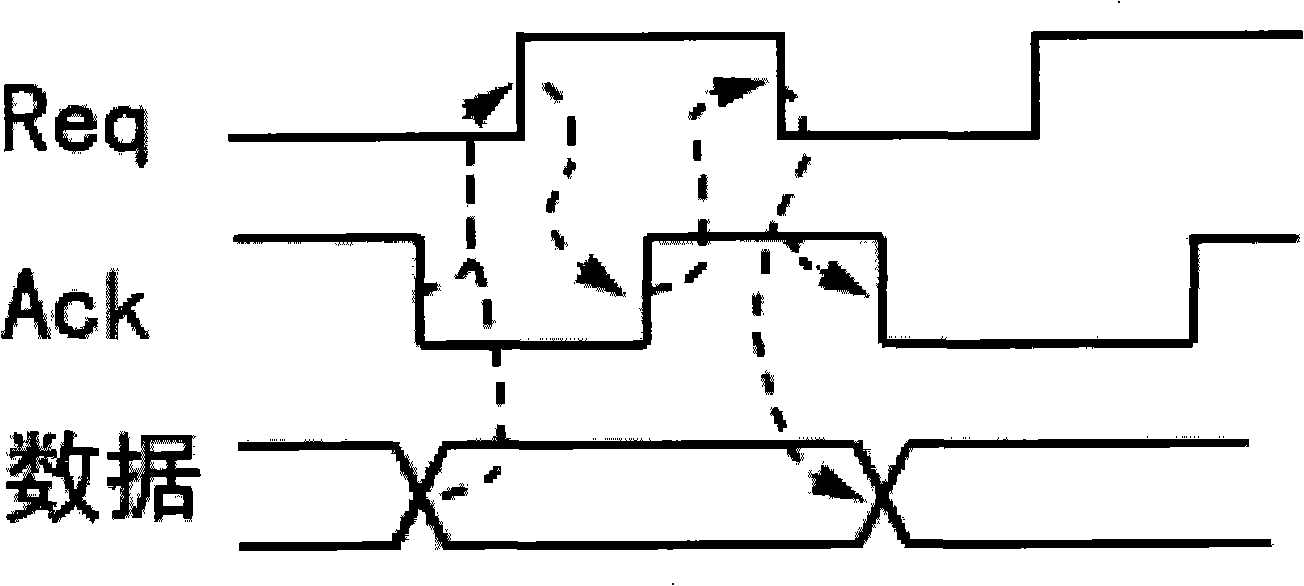

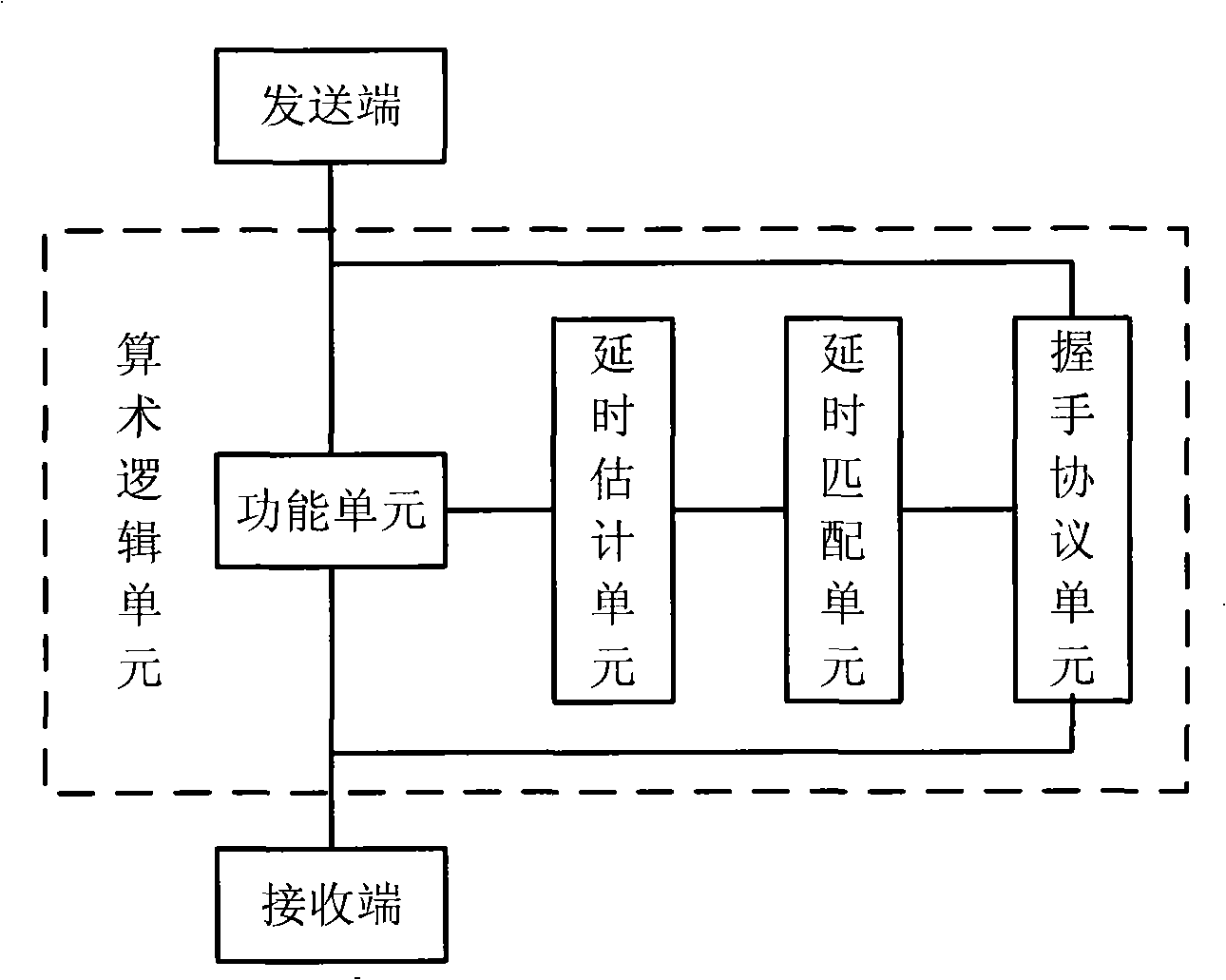

[0039] as attached image 3 Shown is the structural diagram of the asynchronous arithmetic and logic unit of the present invention, including: a functional unit, receiving the operation control instruction and input data of the sending end, and executing the arithmetic logic operation of the input data according to the operation control instruction; a delay estimation unit, based on the input data received by the function unit The type of operation control instruction and the input specific data perform delay estimation; the delay matching unit selects the operation delay matching the functional unit according to the delay estimated by the delay estimation unit; the handshake protocol unit sends the input data at the sending end At the same time, a request signal is generated at the sending end to synchronize the input, and after the operation delay, the receiving end is notified to take away the output data of the functional unit, and a response signal is generated at the rece...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More