Patents

Literature

66results about How to "Ease of hardware implementation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

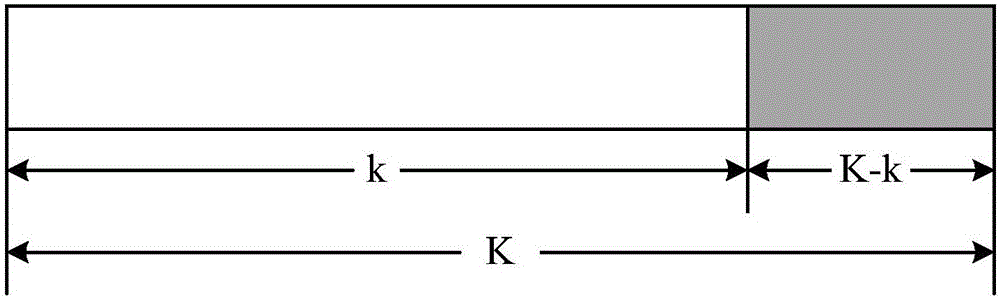

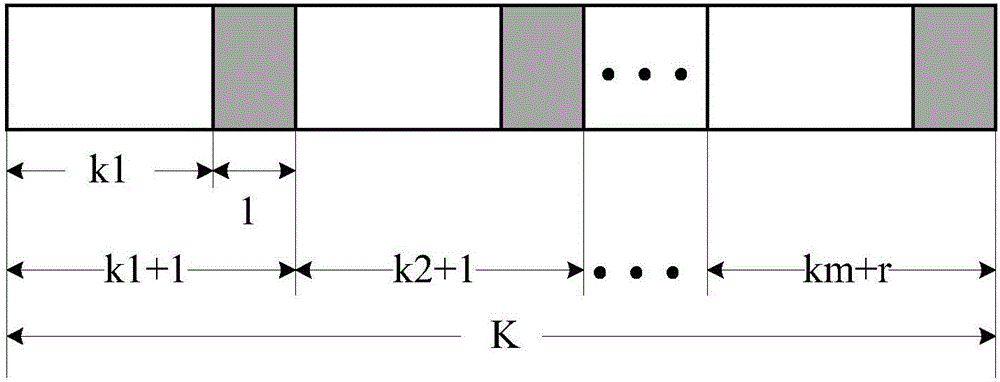

Optimized FFT/IFFT module

ActiveUS20050058059A1Ease of hardware implementationMinimize the numberAmplitude-modulated carrier systemsRadio transmissionTheoretical computer scienceComputer module

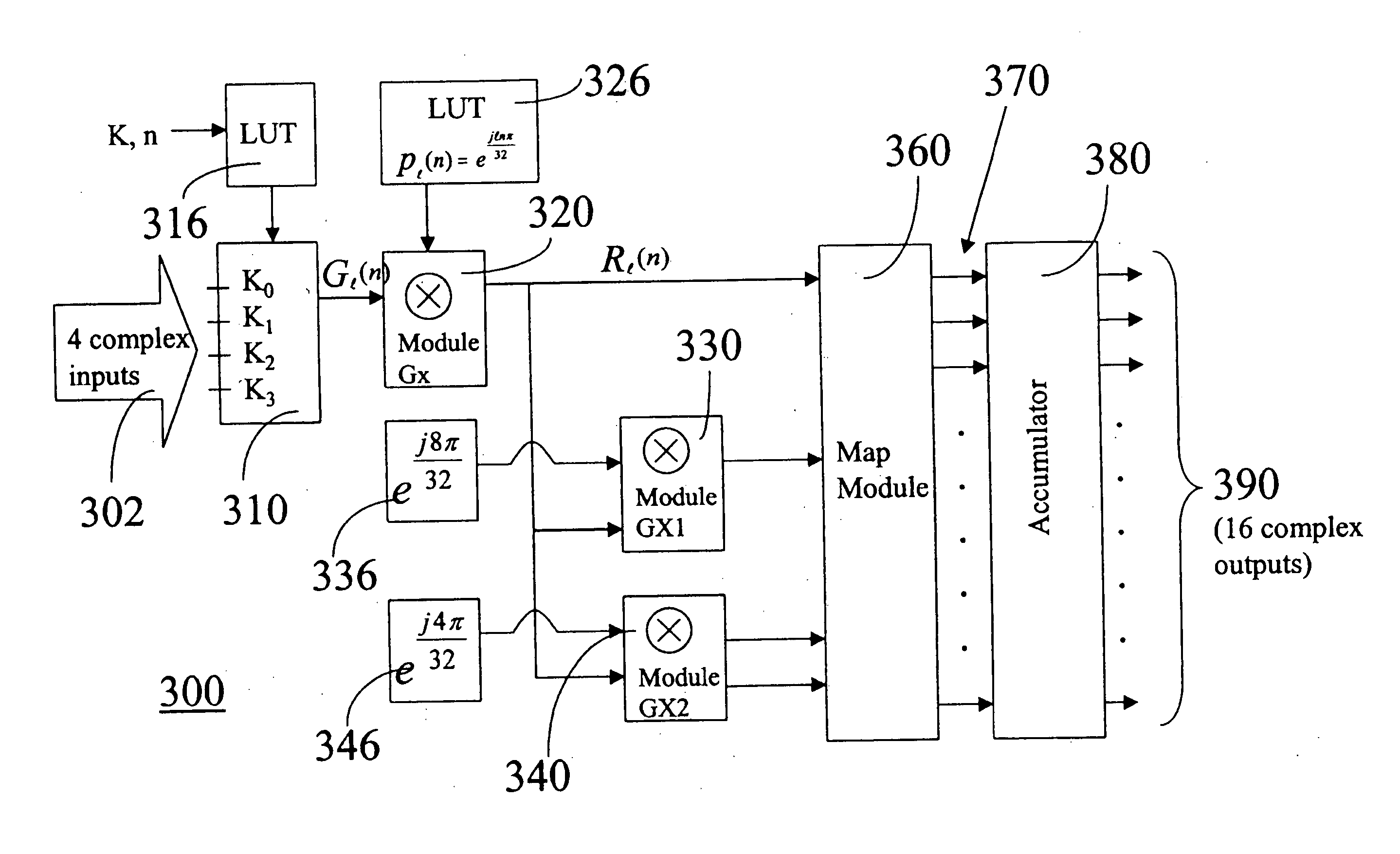

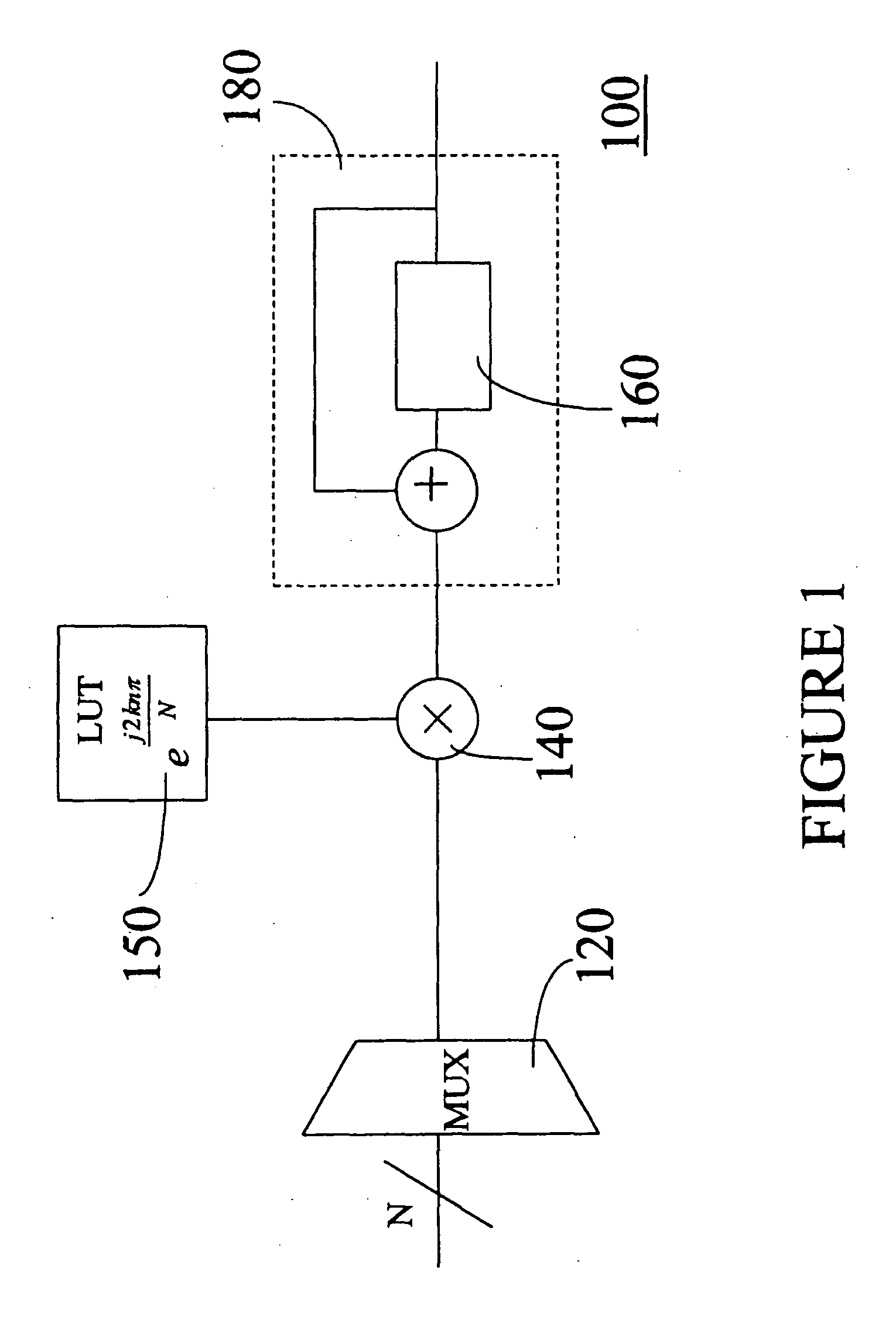

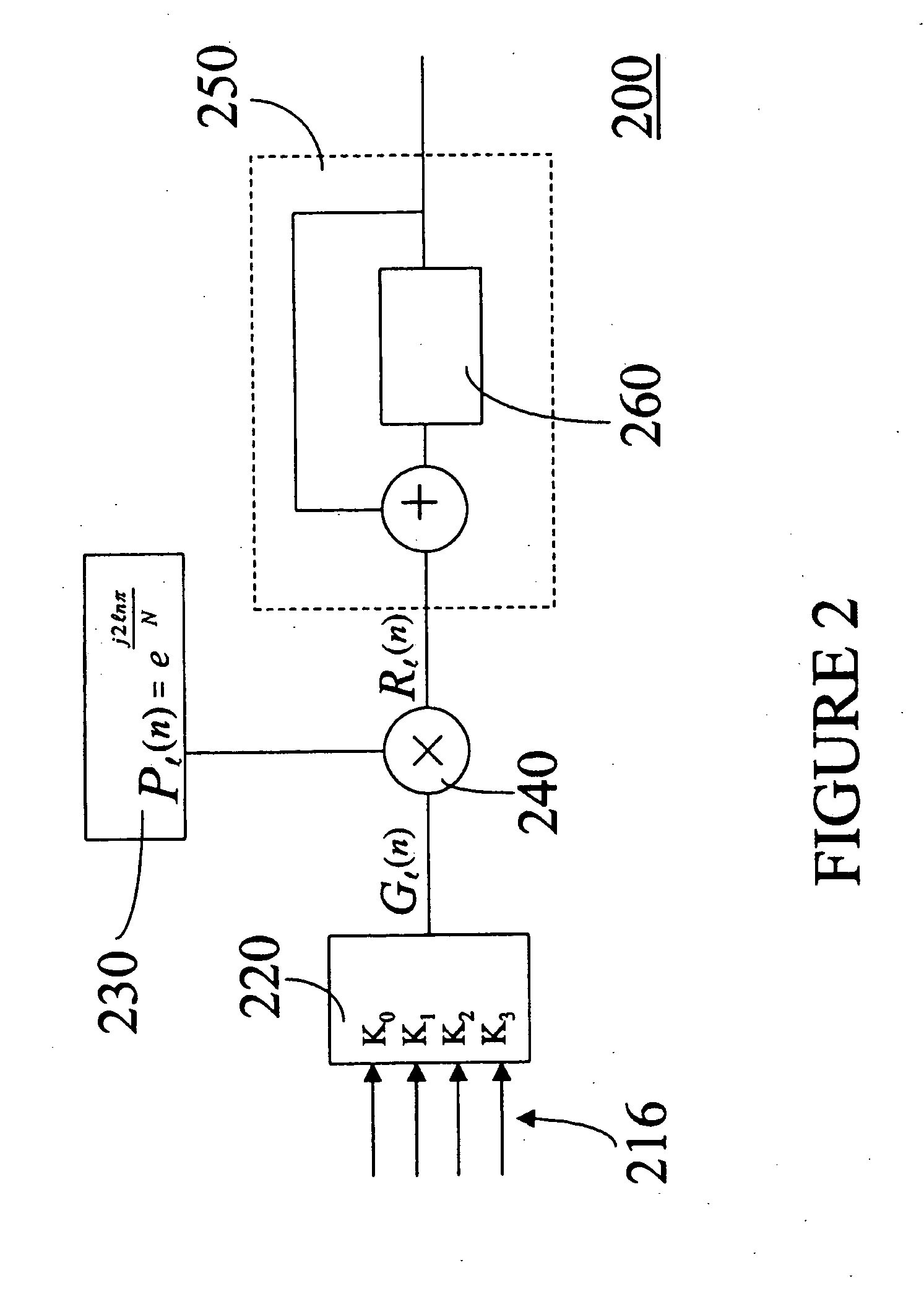

The present invention discloses an optimal hardware implementation of the FFT / IFFT operation that minimizes the number of clock cycles required to compute the FFT / IFFT while at the same time minimizing the number of complex multipliers needed. For performing an N-point FFT / IFFT operation in N clock cycles, the optimal hardware implementation consists of several modules. An input module receives a plurality of inputs in parallel and combines the inputs after applying a multiplication factor to each of the inputs. At least one multiplicand generator is used to provide multiplicands to the system. At least two complex multiplier modules for performing complex multiplications are required with at least one of the complex multiplier modules receiving an output from the input module. Each of the complex multiplier modules receives multiplicands from the at least one multiplicand generator. Furthermore, at least one of the complex multiplier modules receives an output of another complex multiplier module. A map module is provided for receiving outputs of the at least two complex multiplier modules, the map module selecting and applying a multiplication factor to each of the outputs received to generate multiple outputs. Finally, an accumulation module receives and performs an accumulation task on each of the multiple outputs of the map module thereby generating a corresponding number of multiple outputs. In a preferred embodiment, the N-point FFT / IFFT operation is performed in N clock cycles using (N32+1)complex multipliers. In a specific implementation, a system comprising 3 complex multipliers is used to compute a 64-point FFT / IFFT operation in 64 clock cycles. Advantageously, the total number of clock cycles required to complete the FFT / IFFT operation is minimized while at the same time minimizing the number of complex multipliers needed.

Owner:ZARBANA DIGITAL FUND

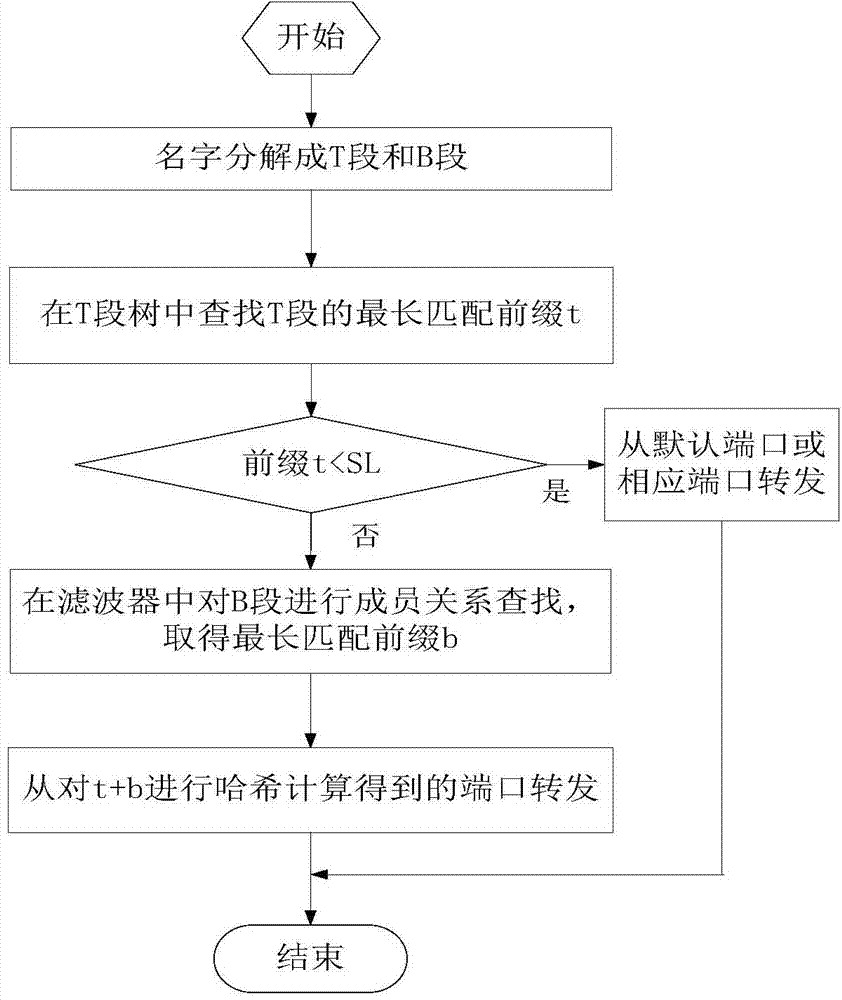

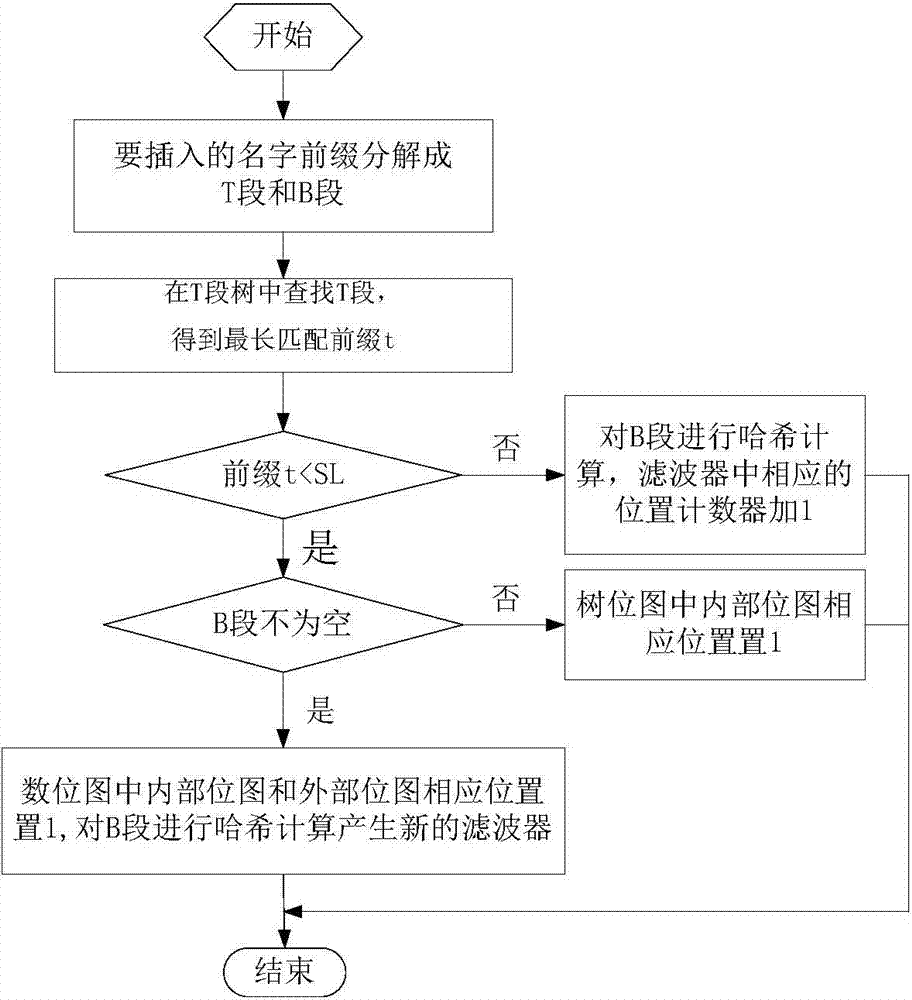

Name routing fast matching search method and device

ActiveCN103873371AControl depthReduce the numberData switching networksSpecial data processing applicationsLongest prefix matchBitmap

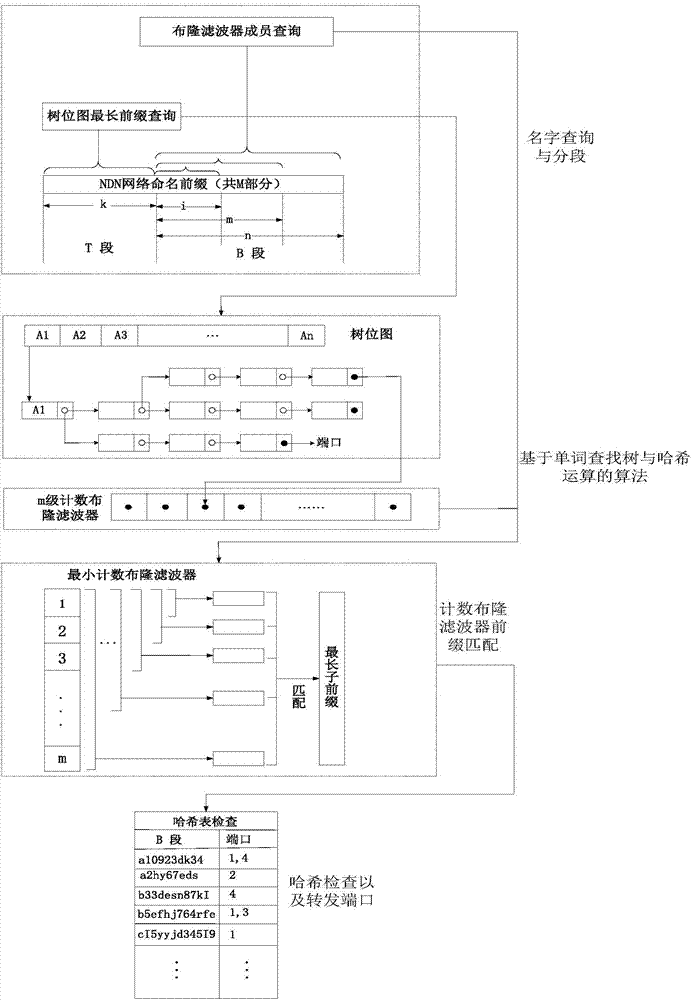

The invention discloses a name routing fast matching search method and device. The device mainly comprises a tree-bitmap and a Blond filter. The tree-bitmap is used for storing the first m layers of name routing, and performing fast longest prefix matching on the first m layers of request content name reaching a router; the Blond filter is used for storing the rest of the prefix of the name routing, and performing longest prefix matching on the rest of the request content name reaching the router. According to the different prefix length of the name routing to be updated, the tree-bitmap and the Blond filter can be updated respectively or simultaneously by the method. According to the invention, the characteristics of fast searching, little required storing of the tree-bitmap and the characteristics of high time efficiency and spatial efficiency are utilized, the routing addressing problem based on the content name in the novel network system is solved, and the requirements of little occupied memory, fast matching speed and fast updating speed of the future network routing are met.

Owner:BEIJING UNIV OF POSTS & TELECOMM

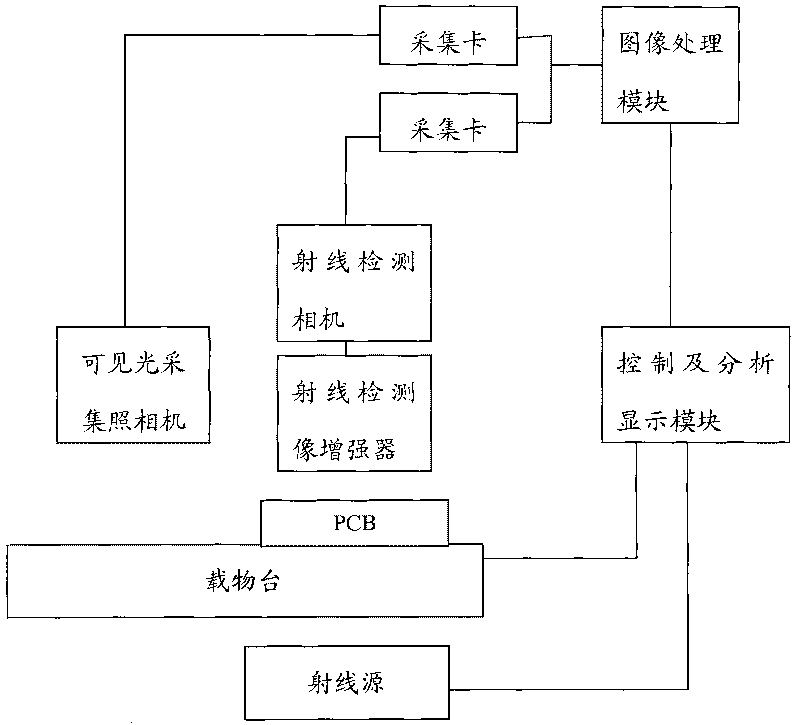

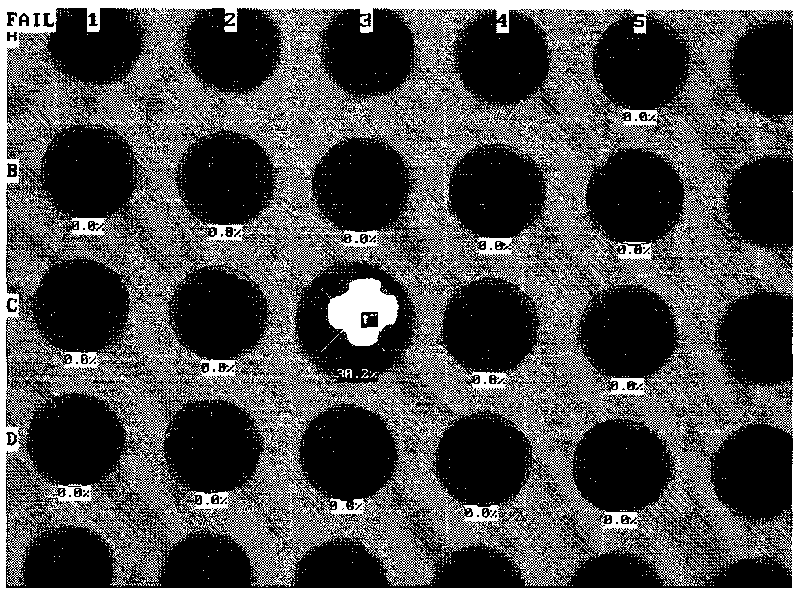

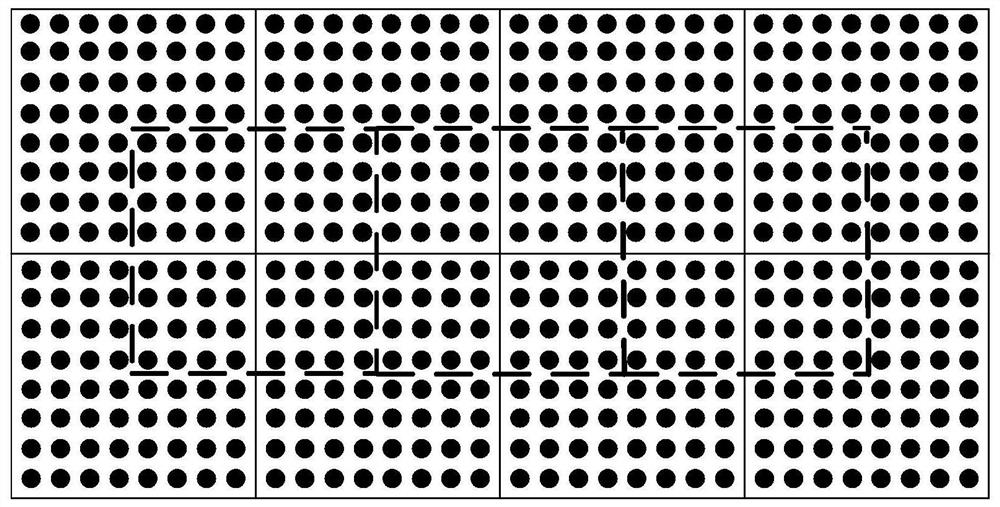

Automatic detection system and detection method of high resolution printed circuit board

InactiveCN101706458AReduce blurReduce volumeMaterial analysis by optical meansMaterial analysis by transmitting radiationPrinted circuit boardHigh resolution

Owner:ZHONGBEI UNIV

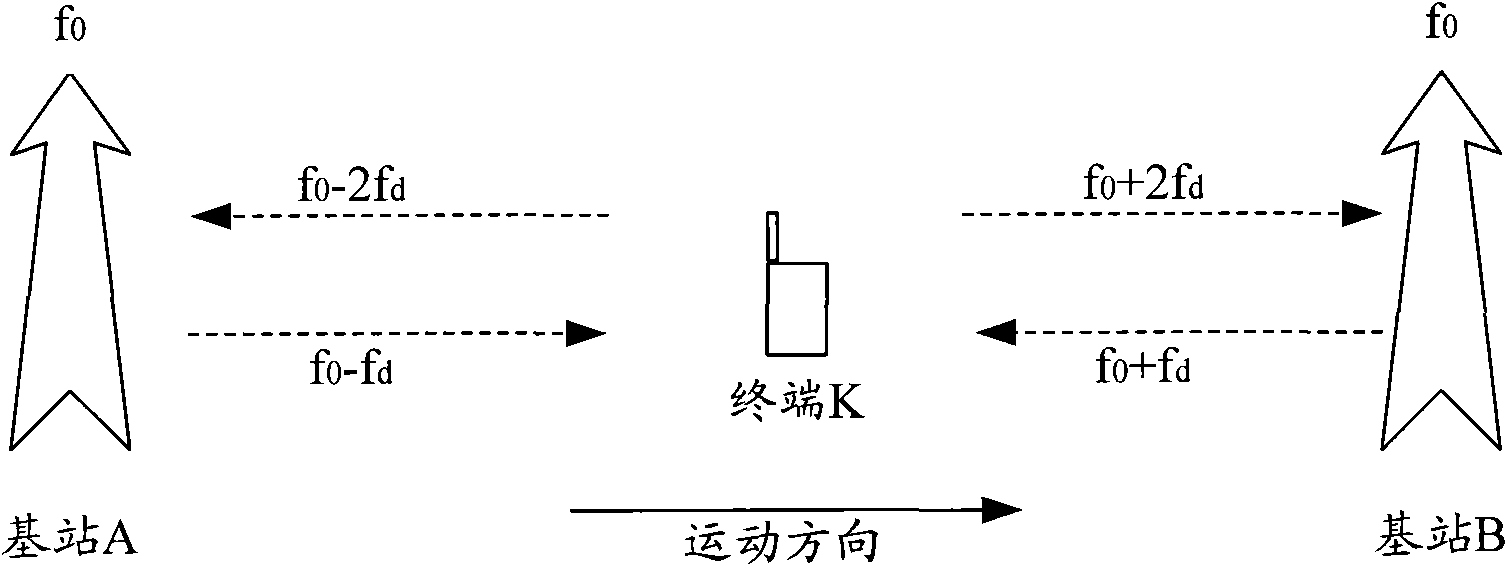

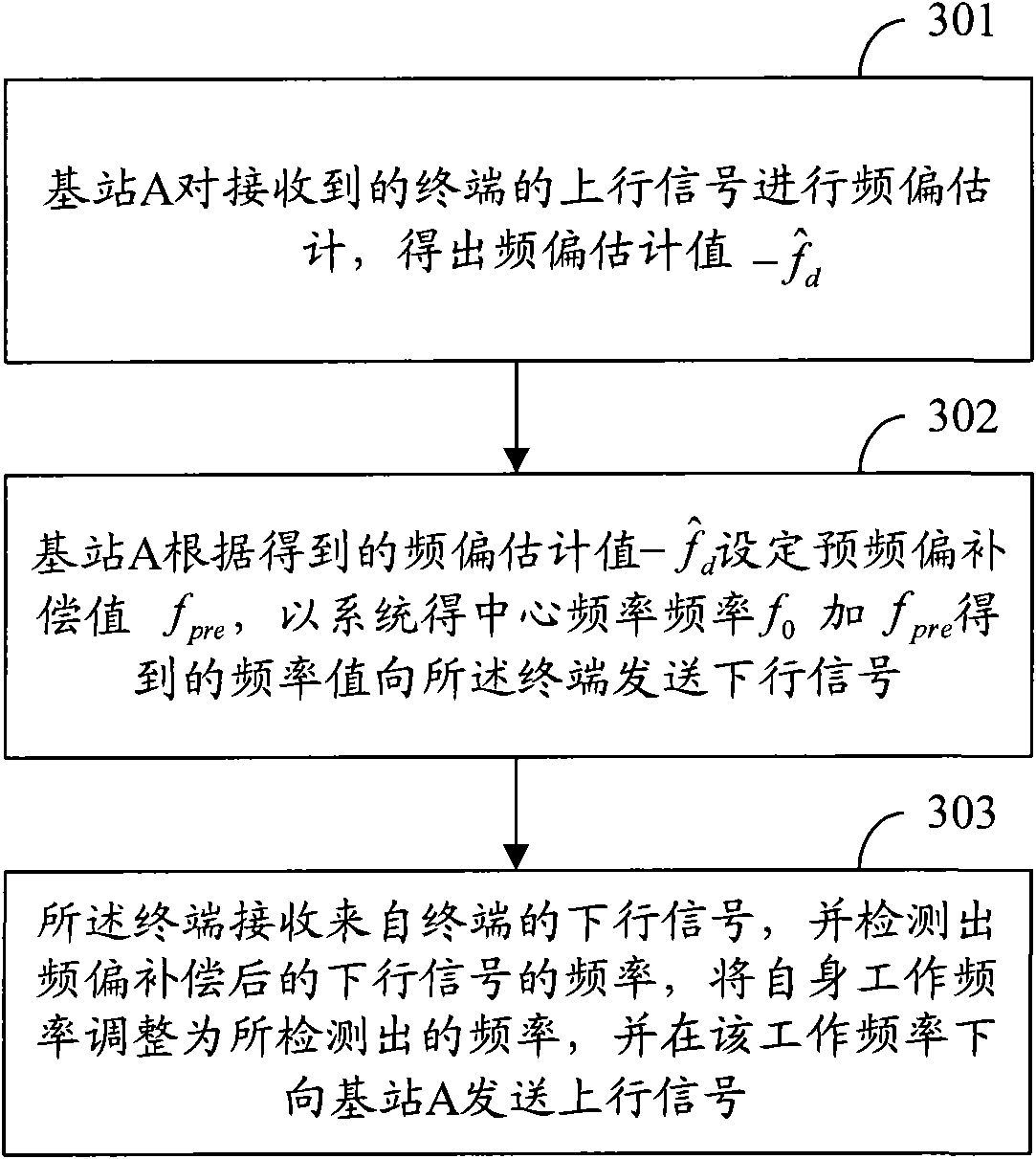

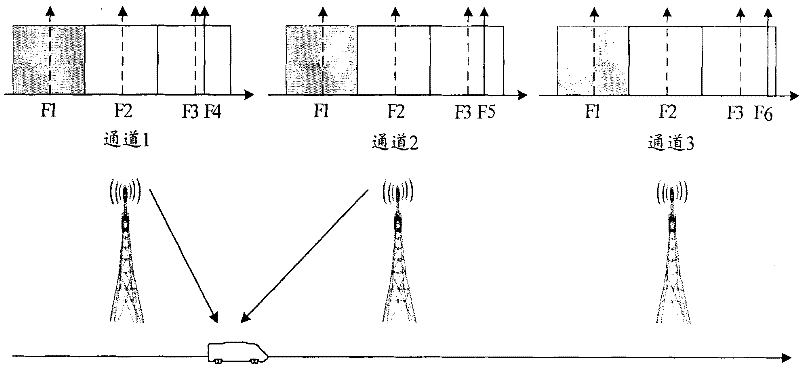

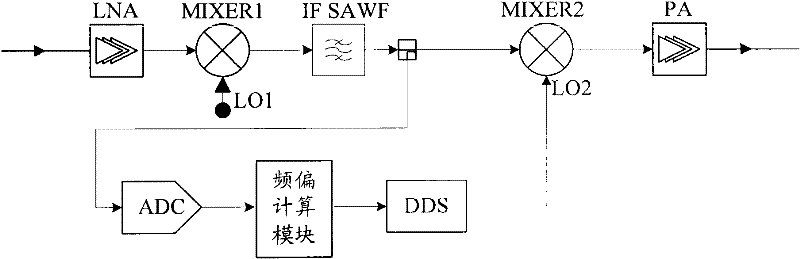

Frequency offset compensation method and device

ActiveCN101567708ATake the Stress Out of Frequency CorrectionCommunication service quality is reliableTransmitter/receiver shaping networksSignal frequencyEngineering

The invention discloses a frequency offset compensation method, which comprises the following steps that: a base station performs frequency offset estimation on received uplink signals to obtain a frequency offset estimation result, and pre frequency offset compensation is performed on downlink signals according to the frequency offset estimation result; a terminal detects the frequency of the received downlink signals after the frequency offset compensation, the emission frequency of the uplink signals is determined according to the detected frequency of the downlink signals, and the uplink signals are emitted in the determined frequency; and a terminal side performs the pre frequency offset compensation by the same method. The invention also discloses a frequency offset compensation device, which comprises a frequency offset estimation module, a pre frequency offset compensation module and a frequency detection and frequency modulation module. The method and the device can effectively reduce the frequency offset of uplinks and downlinks, perform the frequency offset compensation of the uplinks and the downlinks, and not only reduce the relative frequency offset between the base station and the terminal, but also reduce frequency jump variable when the terminal switches between the base stations, so that both the base station and the terminal can correctly correct the receivedsignals to ensure communication quality.

Owner:ZTE CORP

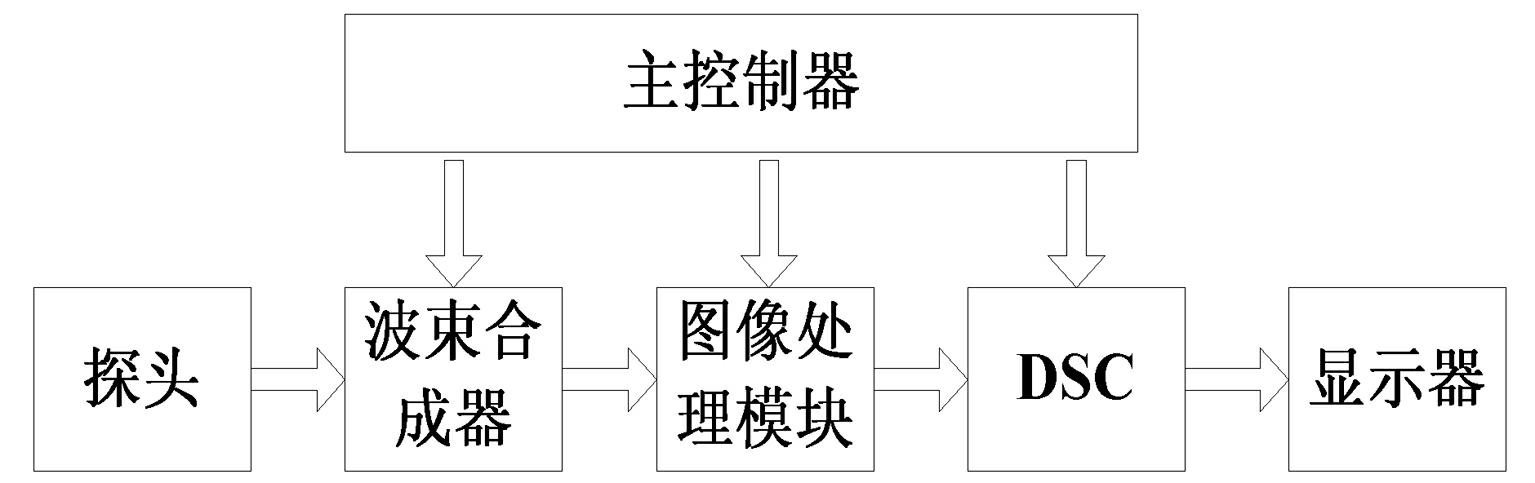

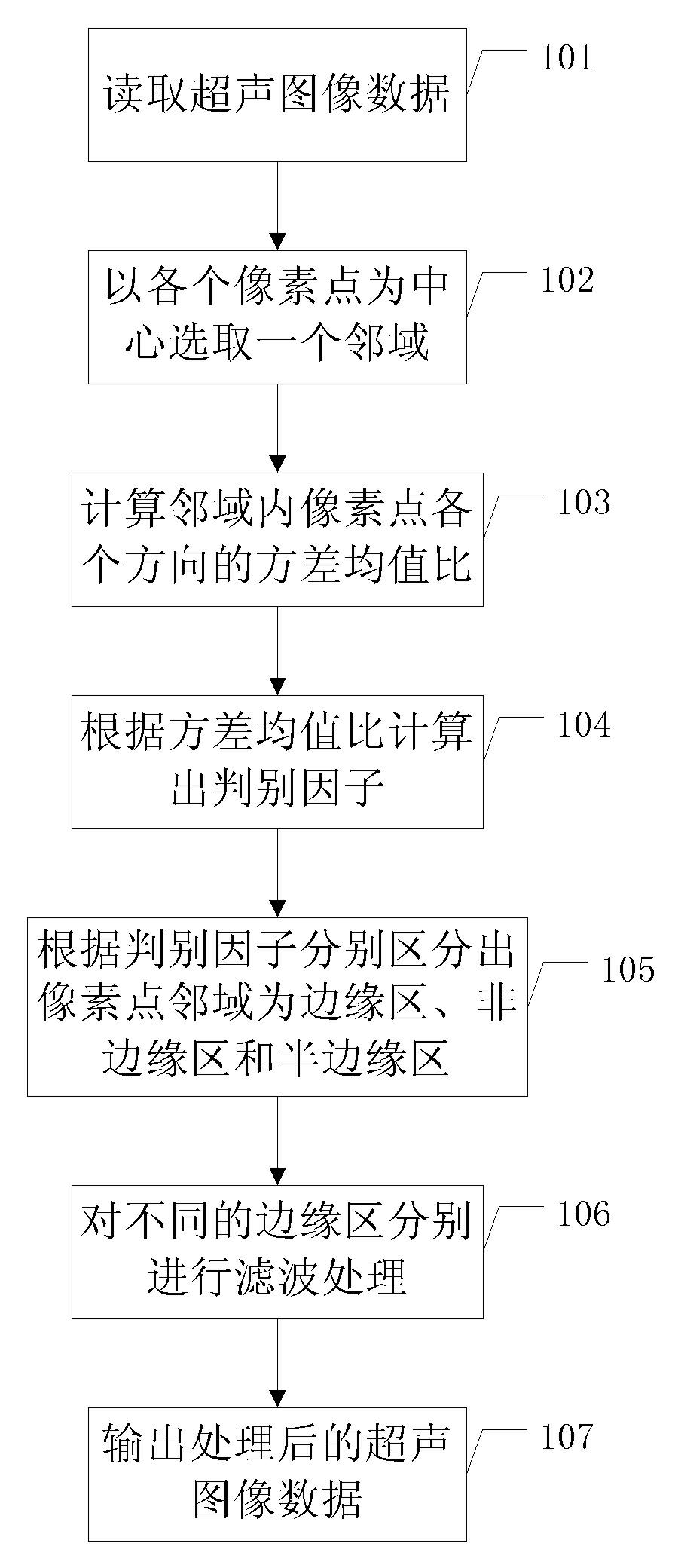

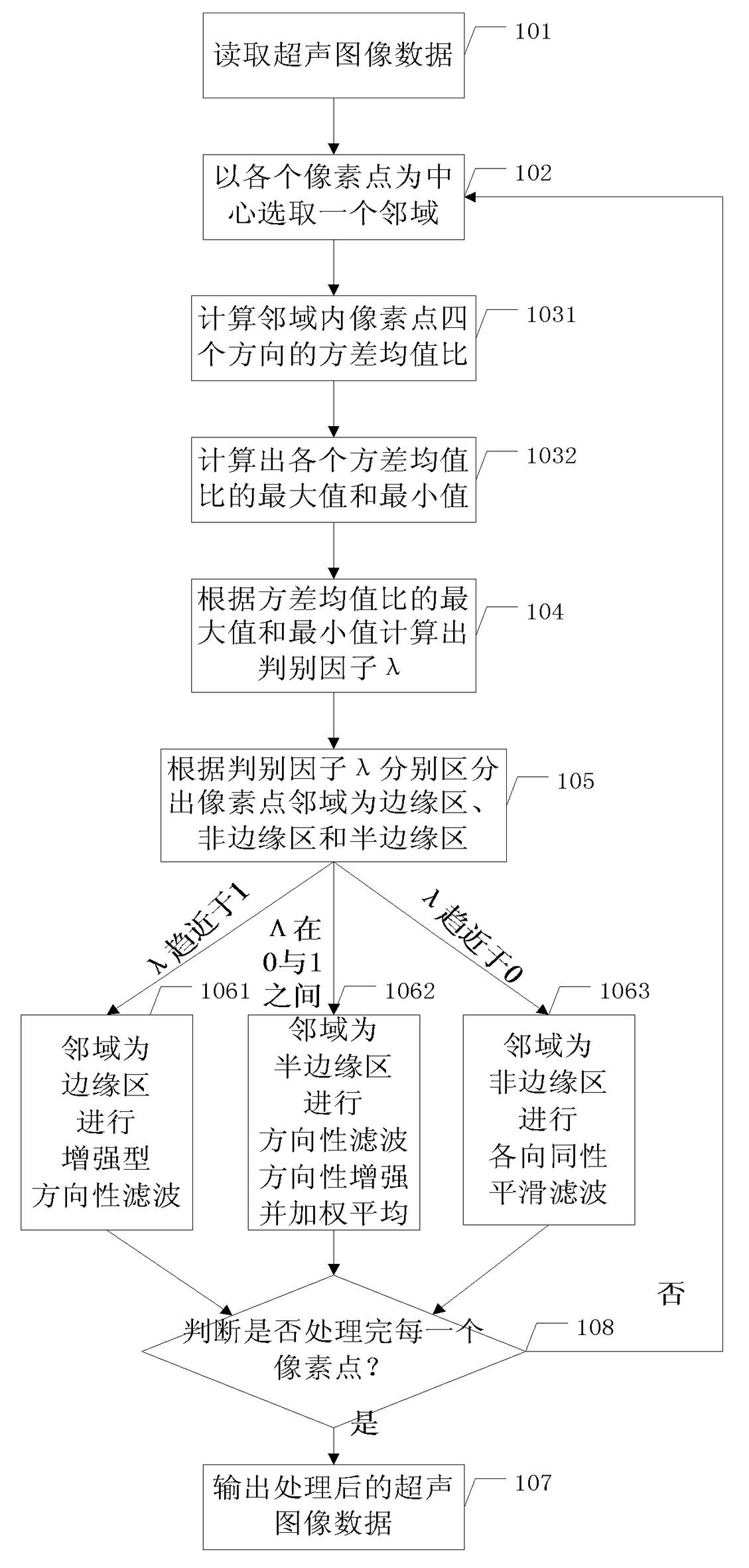

Method and device for reducing noise in ultrasound image

ActiveCN102306377ASimple algorithmEase of hardware implementationImage enhancementUltrasound imageEdge region

The invention relates to an image processing technique, particularly relates to an image data processing technique in an ultrasound image, and more particularly to a method and a device for reducing noise in the ultrasound image. The method provided by the invention comprises the following steps: reading ultrasound image data; selecting an adjacent region with each pixel point as a center; computing the variance mean value ratio of the pixel points in each direction in the adjacent regions; computing discrimination factors according to the variance mean value ratio; respectively distinguishing the adjacent regions of the pixel points as an edge region, a non-edge region and a semi-edge region according to the discrimination factors; respectively carrying out filtering processing on the different edge regions; and outputting the processed ultrasound image data. According to the technical scheme provided by the invention, the edge enhancement and spot suppression of images can be simultaneously realized; and the method provided by the invention has the advantages of simple algorithm, self adaptation, strong practicality and the like, is easy to achieve by hardware, and can be conducted in real time.

Owner:EDAN INSTR

Polar code coding/decoding method

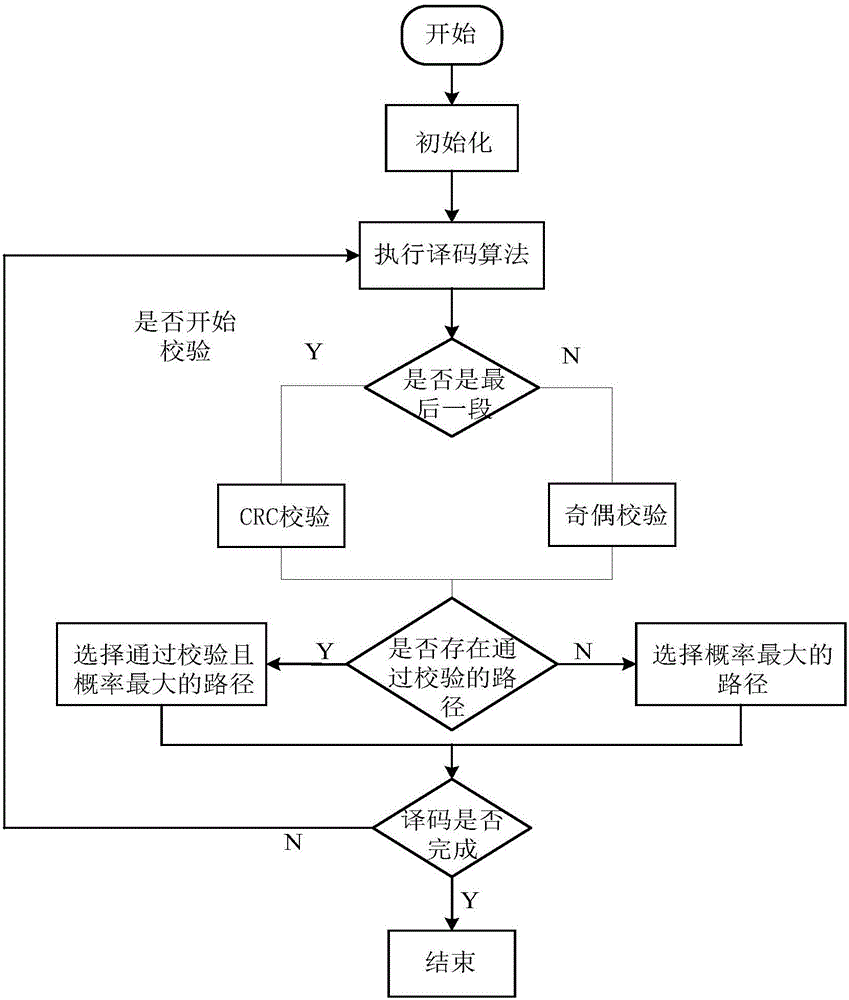

ActiveCN106788456ASave register storage spaceEase of hardware implementationError detection onlyDirect feedbackCyclic redundancy check

The invention belongs to the field of channel coding and specifically relates to a polar code coding / decoding method. According to the method, on the basis of a traditional CRC (Cyclic Redundancy Check) assisted SCL decoding method for a polar code and a segmented CRC assisted polar code coding / decoding structure, a segmented odd-even check and CRC jointly assisted polar code coding / decoding method is provided. According to the method, coding is carried out by employing a segmented odd-even check and CRC assisted information check structure at a coding side, thereby generating codons; a corresponding segmented odd-even check and CRC assisted polar code decoding method is designed at a decoding side; the segmented decoding check is carried out on the received codons; and under the condition that the performance loss is very little, the storage space of a decoder is greatly saved, thereby facilitating hardware realization of the polar code. According to the method, if the odd-even check or CRC check is failed after a first layer or a plurality of former layers of decoding is finished, direct feedback and retransmission can be carried out, and the retransmission does not need to be carried out after all decoding is finished, so the decoding delay can be reduced, thereby facilitating the application of the polar code in real-time communication.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Method for improving structure of convolution code encoder

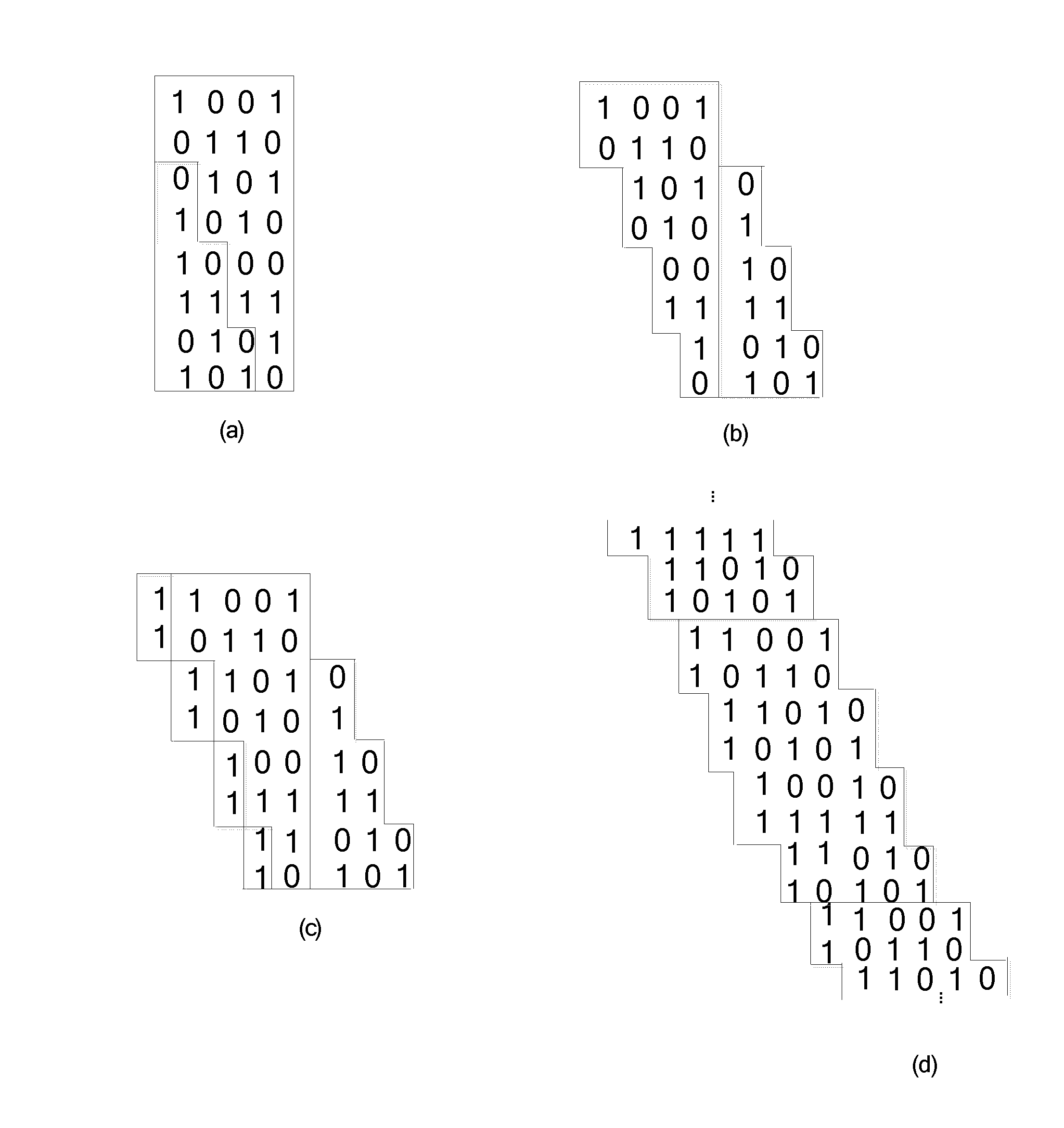

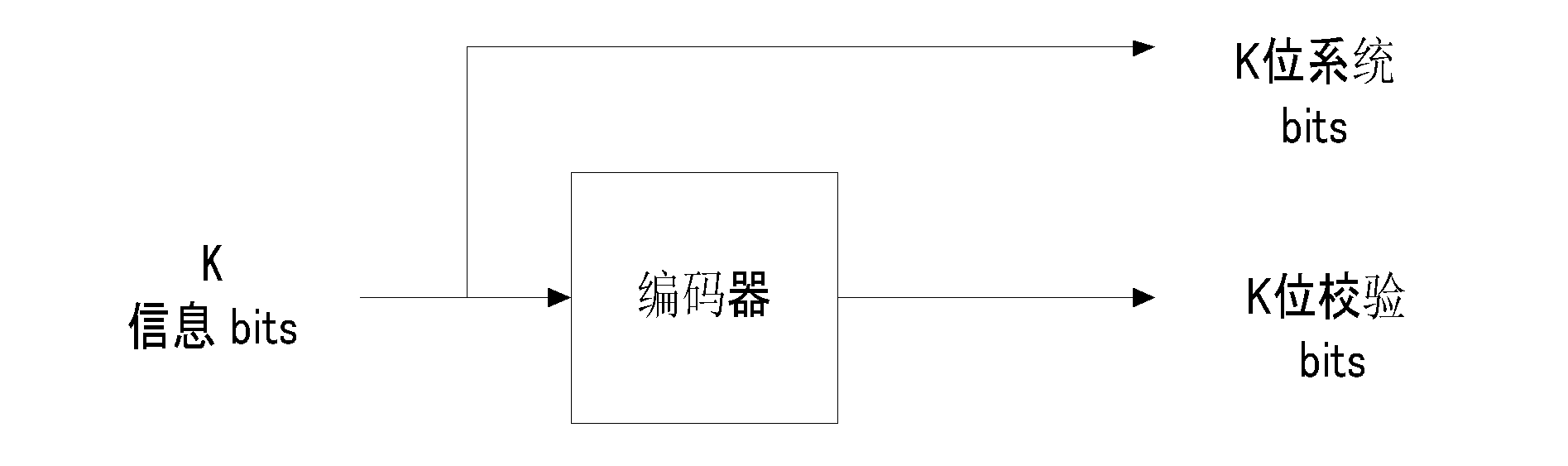

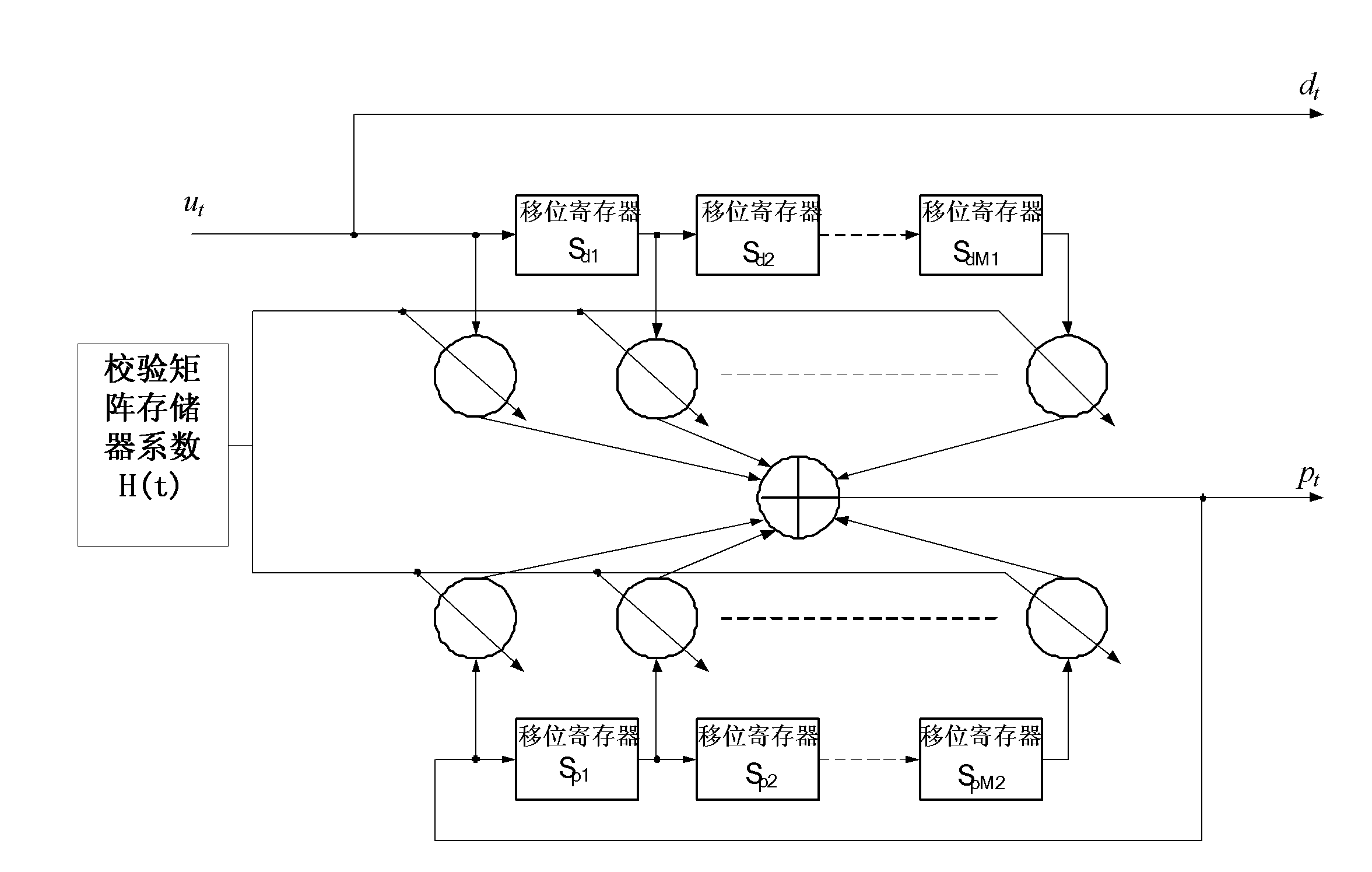

InactiveCN102437858AReduce coding complexityEase of hardware implementationError correction/detection using convolutional codesLdpc convolutional codesFrequency spectrum

The invention relates to a method for improving a structure of a convolution code encoder, particularly relates to a method which is applied to wireless local area network (WLAN) and long time evolution (LTE) relevant standard systems and used for improving the structure of the convolution code encoder, and belongs to the technical field of wireless mobile communication. By designing parameters of the encoder for a low density parity check (LDPC) convolution code and a check matrix H (t) of the LDPC convolution code and improving the encoding structure of the convolution code, the high performance and low error rate are realized. The LDPC convolution code integrates the advantages of both an LDPC code and the convolution code; due to the regular structure, the convolution code encoder has high-speed encoding capability; and the hardware of the encoder is simplified; the encoding complexity of the LDPC convolution code is reduced, and the parallel iterative decoding can be performed to realize low time delay; under the condition of rate compatibility, during forward error correction control (FEC) of IEEE 802.16m, the LDPC convolution code be used for realizing hybrid automatic repeat request (HARQ) which supports an IR type; therefore, the spectrum efficiency and the system throughput are improved.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

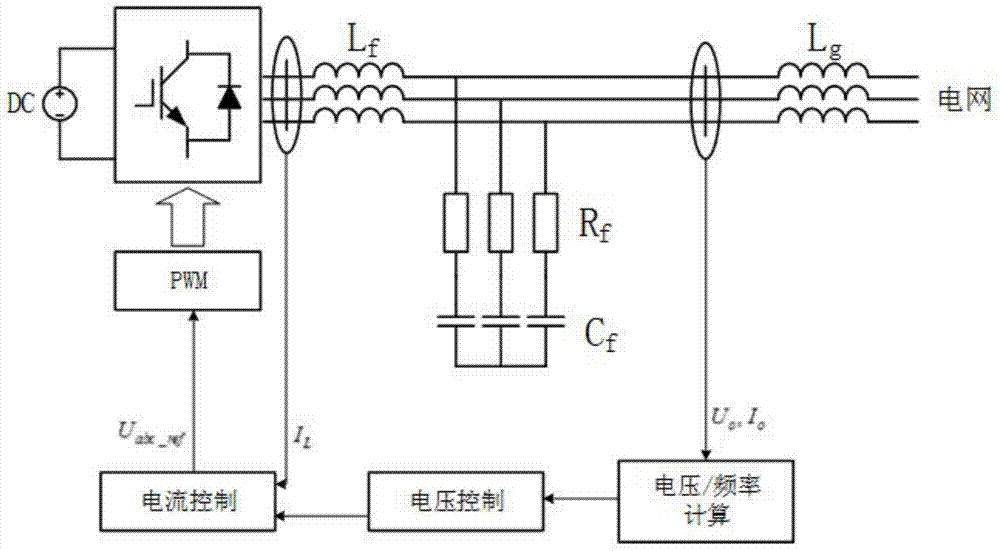

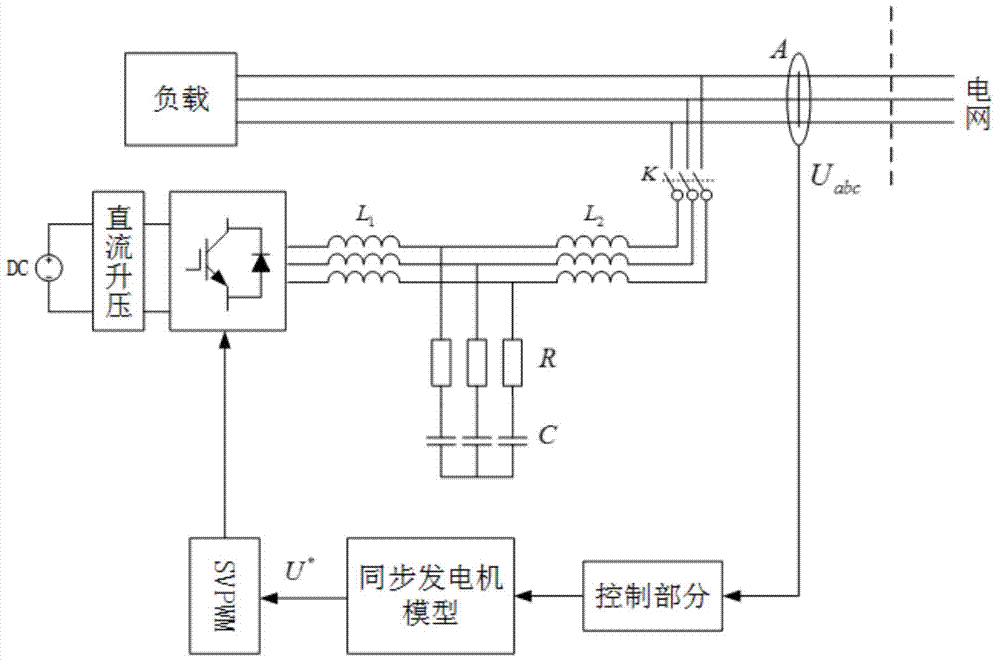

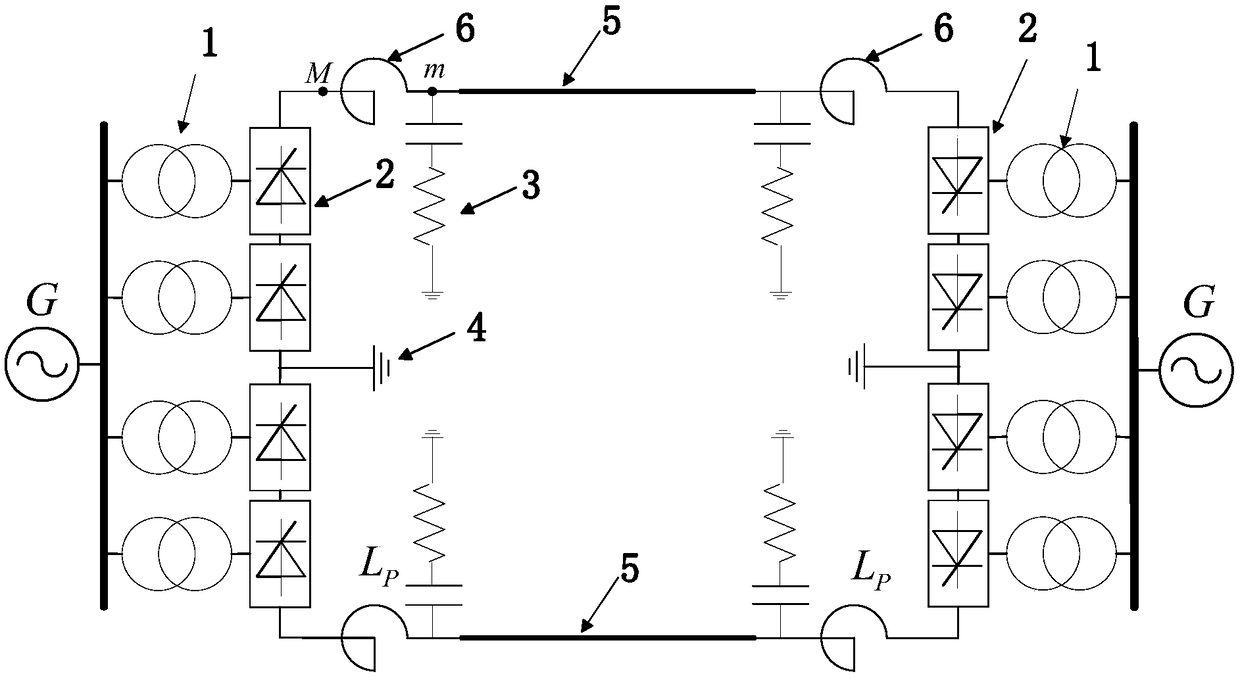

Household grid-connected inverter control strategy based on virtual synchronous generator

InactiveCN104767219AActively participate in coordinated controlEasy to implementSingle network parallel feeding arrangementsVirtual synchronous generatorIslanding

The invention relates to the technical field of power generation systems, in particular to a household grid-connected inverter control strategy based on a virtual synchronous generator. A mathematic model of the virtual synchronous generator is introduced into a grid-connected inverter, a control method of the synchronous generator is added to a control link of the grid-connected inverter, the grid-connected inverter is used for island detection, and when the power grid side breaks down, the grid-connected inverter can be quickly switched to an off-grid operation state. By the adoption of the control strategy, the household medium-small-generated output grid-connected inverter is equivalent to the synchronous generator from the aspects of input and output characteristics, and the inverter can actively participate in coordination control over the voltage and the frequency of a power system.

Owner:STATE GRID CORP OF CHINA +3

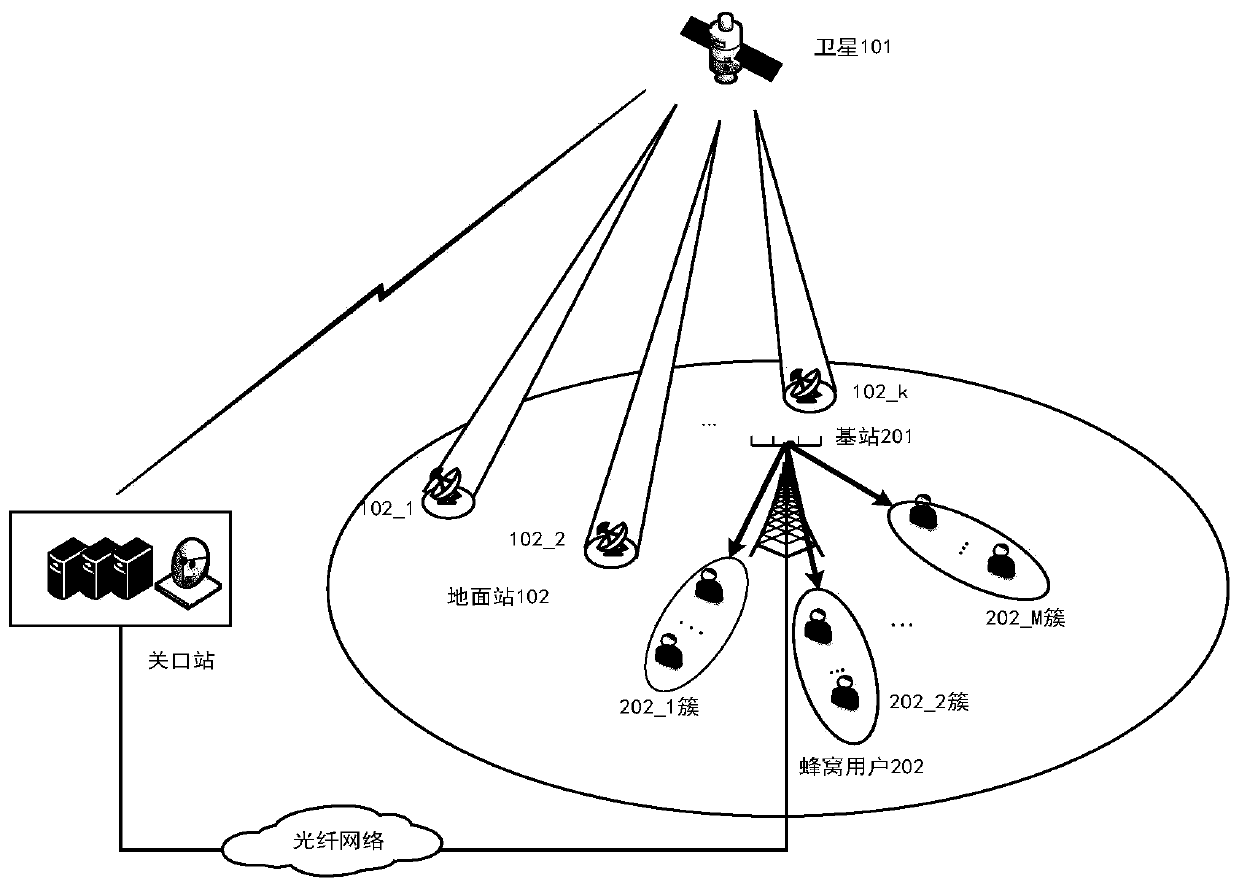

Satellite-ground joint beam forming and power distribution method based on non-orthogonal multiple access technology

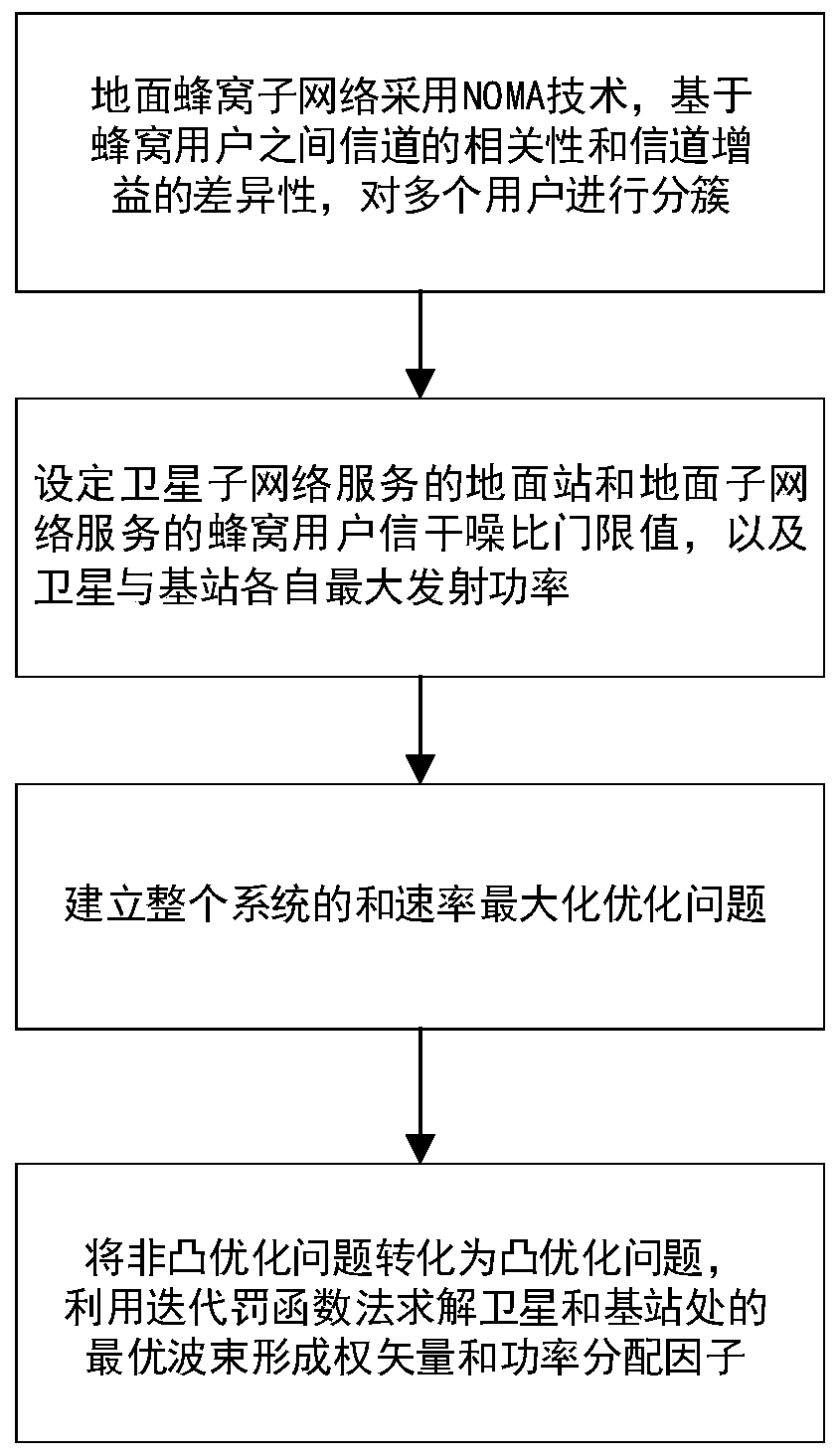

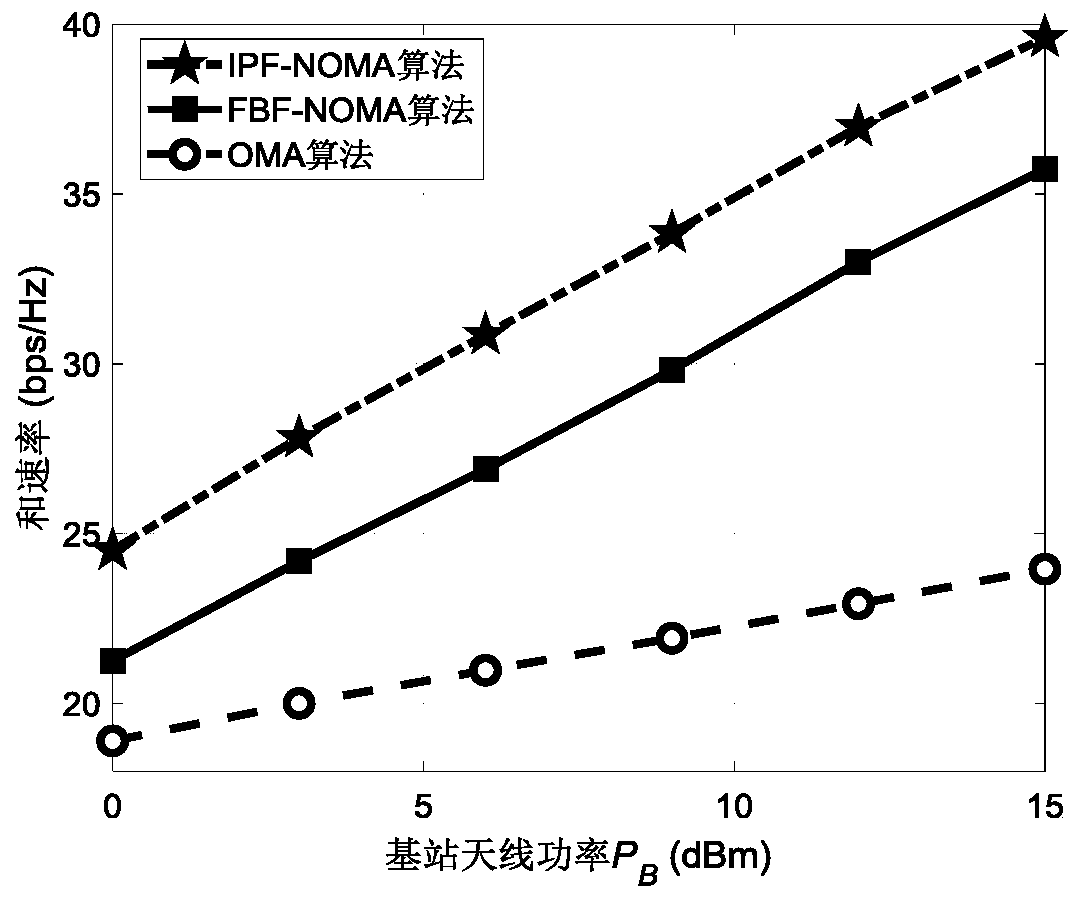

PendingCN111447631ALow hardware requirementsSimple additionPower managementRadio transmissionQuality of serviceTransmitted power

The invention discloses a satellite-ground joint beam forming and power distribution method based on a non-orthogonal multiple access technology (NOMA), and the method comprises the steps that a satellite communication sub-network serves a plurality of ground stations, a ground cellular sub-network serves a plurality of cellular users, and two sub-networks achieve the spectrum sharing; firstly, anNOMA technology is adopted in the ground cellular sub-network, and a multi-user clustering method is provided based on the correlation of channels among cellular users and the difference of channel gains; secondly, under the conditions that the user service quality is guaranteed and the transmitting power of a satellite and a base station is limited, the optimization problem of sum rate maximization of the whole system is established; and, the non-convex problem is converted into a convex optimization problem by adopting an S-Procedure and Taylor expansion method, and further the optimal beamforming weight vector and the power distribution factor of the satellite and the base station are obtained by utilizing an iterative penalty function method. According to the method, the beam formingtechnology and the non-orthogonal multiple access technology are combined, and a technical scheme is provided for improving the effectiveness of satellite-ground fusion network information transmission.

Owner:NANJING UNIV OF POSTS & TELECOMM

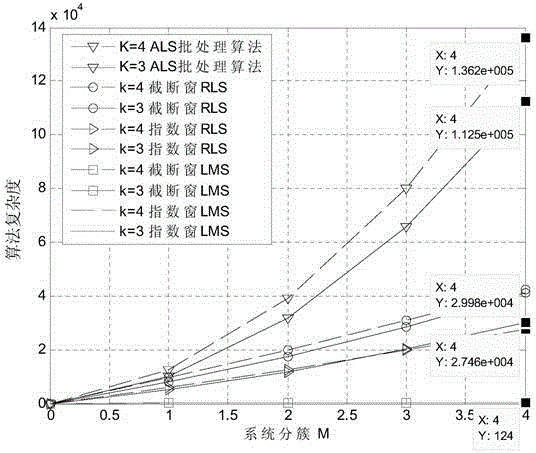

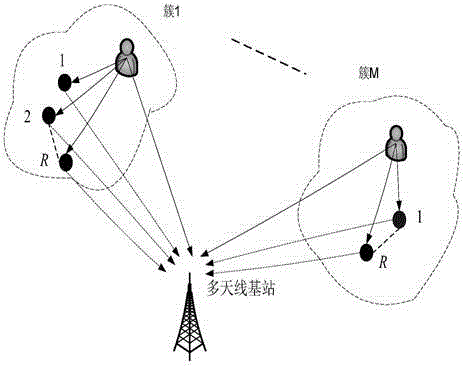

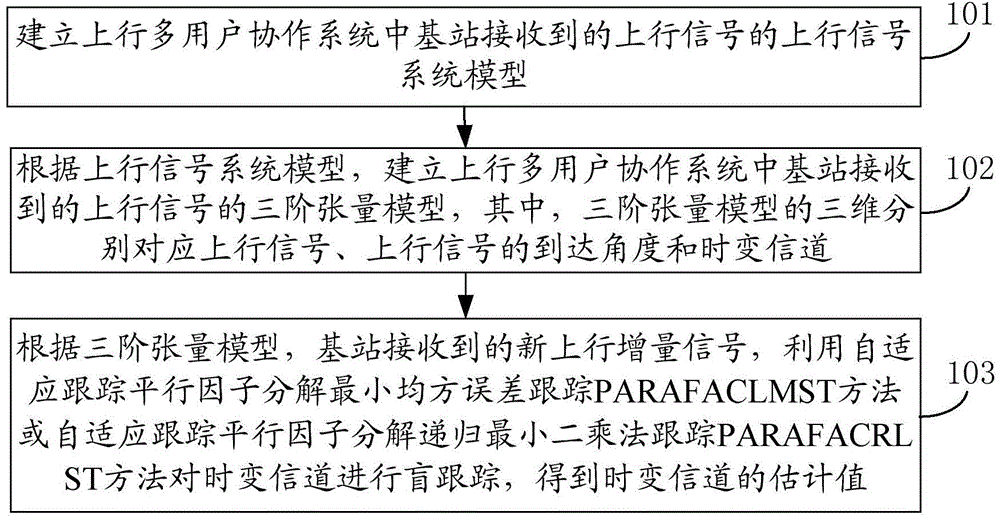

Tensor model based channel estimation method and device

ActiveCN104601498AFast convergenceEasy to implementBaseband system detailsCommunications systemEstimation methods

The invention relates to the technical field of communication, and provides tensor model based channel estimation method and device. The method comprises the steps of creating a three-order tensor model of an uplink signal received by a base station in an uplink multi-user coordination system according to the created uplink signal system model, wherein the three dimensions of the three-order tensor model are respectively corresponding to the uplink signal, an arrival angle and a time-varying channel of the uplink signal; performing blind tracking for the time-varying channel by the PARAFAC-LMST method or the PARAFAC-RLST method according to the three-order tensor model and the new uplink increase signal received by the base station to obtain the estimation value of the time-varying channel. The device comprises a first creating module, a second creating module and a channel estimation module. The device is applicable to a coordinative communication system of a slow-varying channel as well as the coordinative channel system of a rapid fading channel.

Owner:BEIJING UNIV OF POSTS & TELECOMM

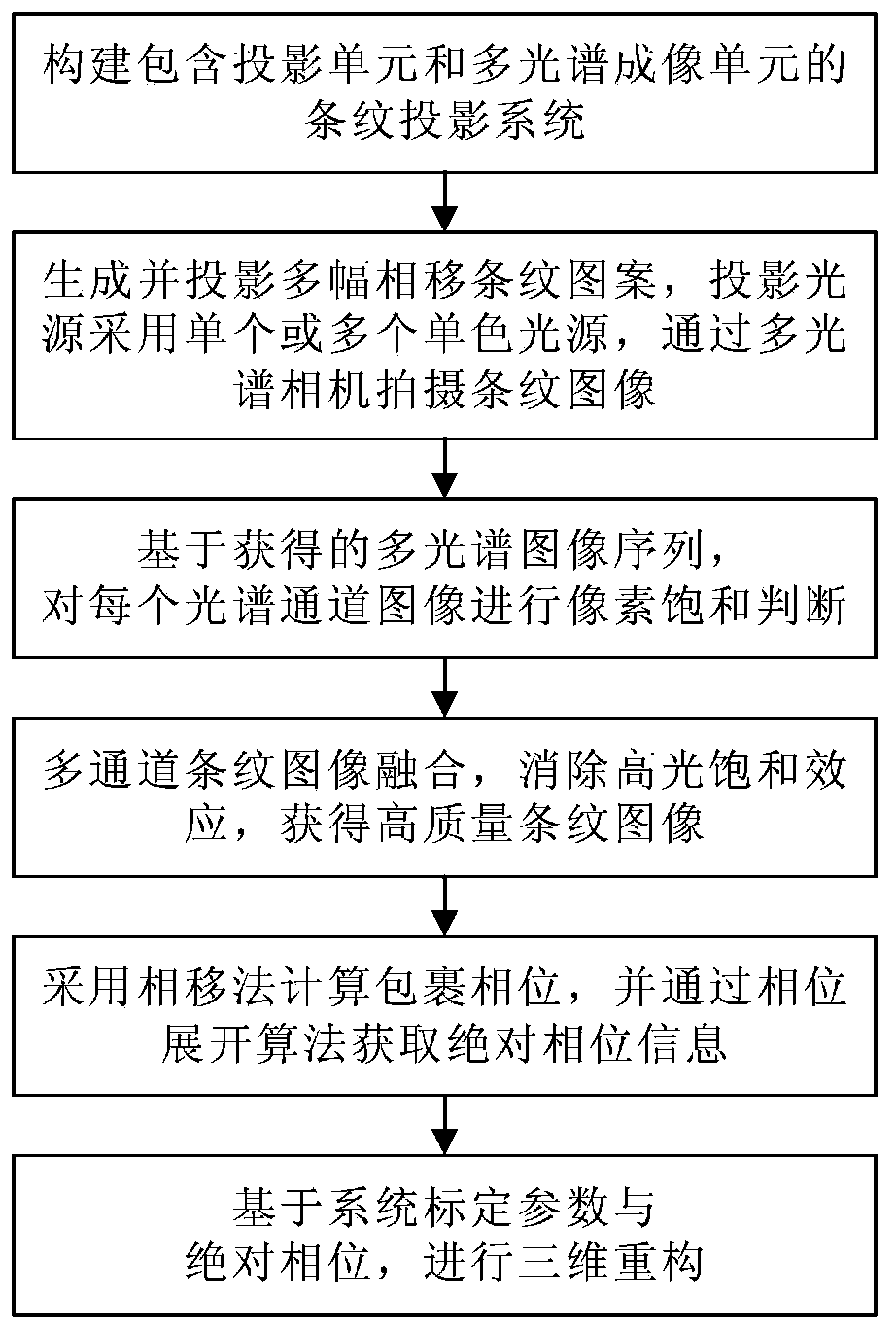

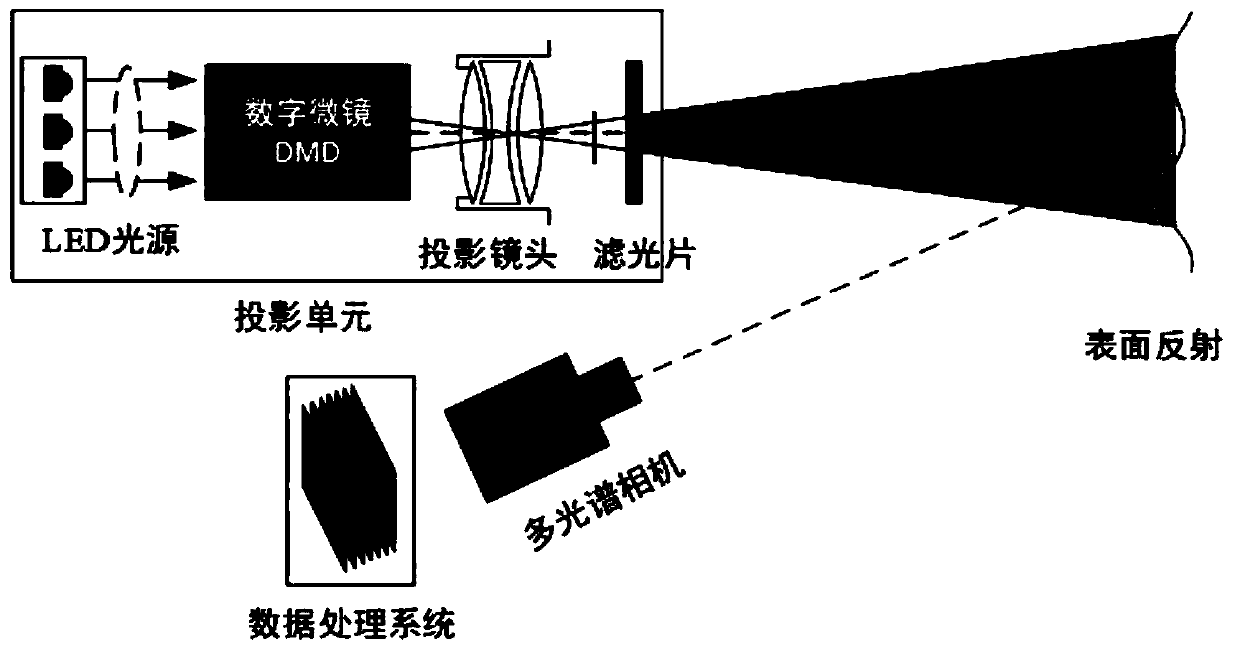

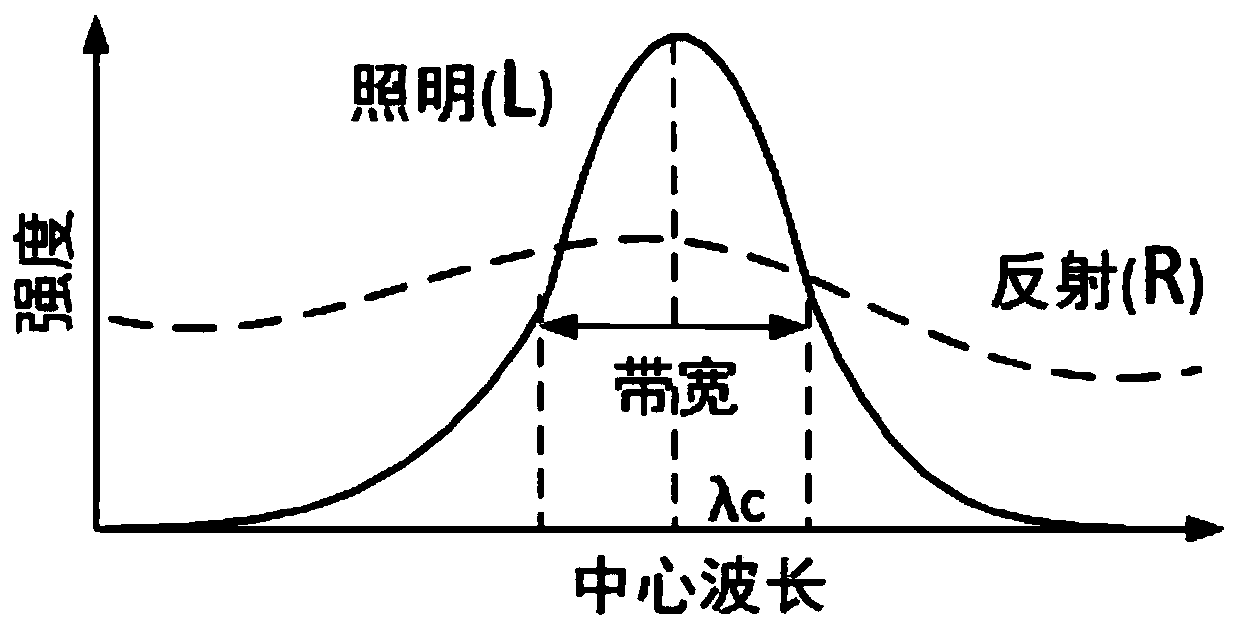

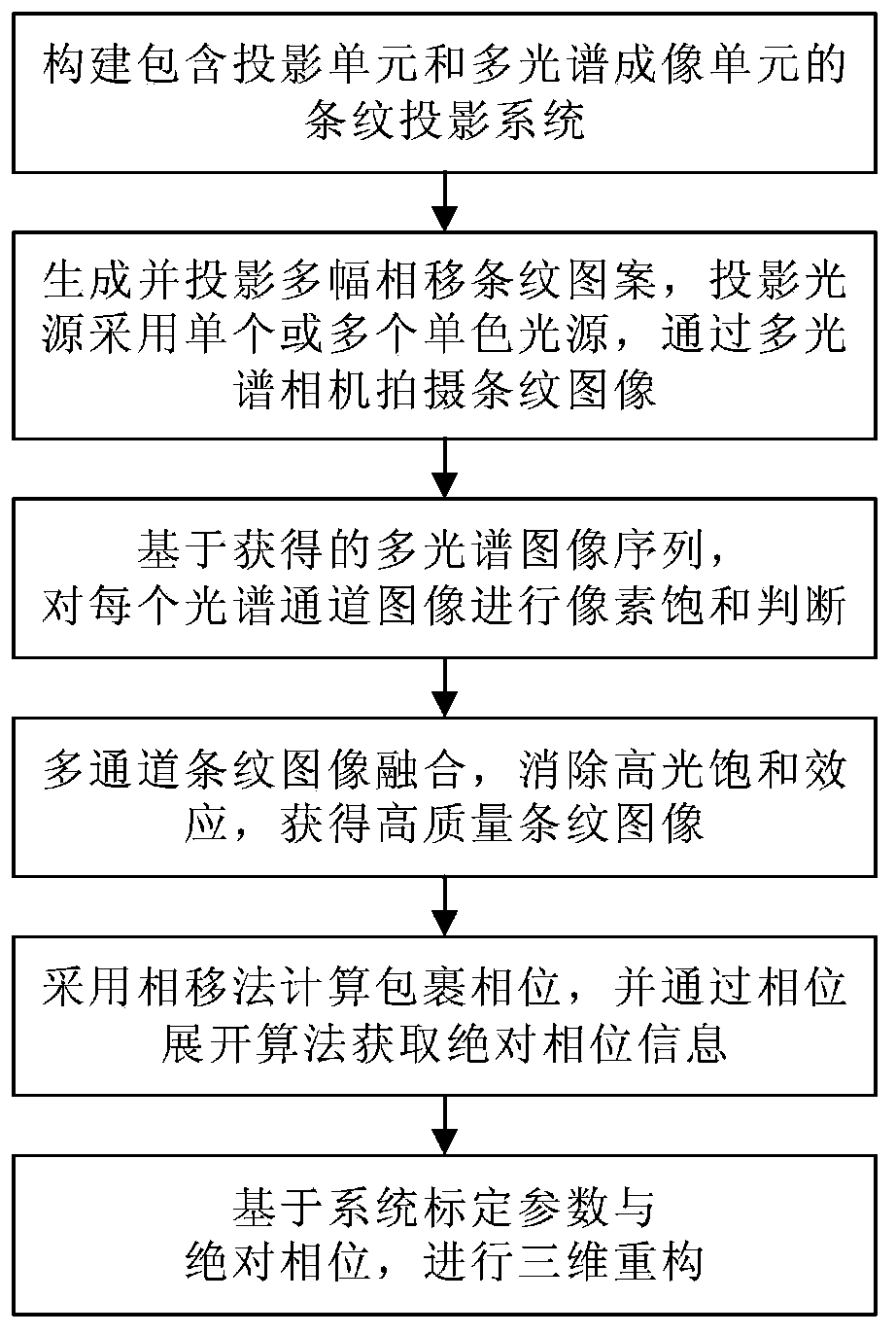

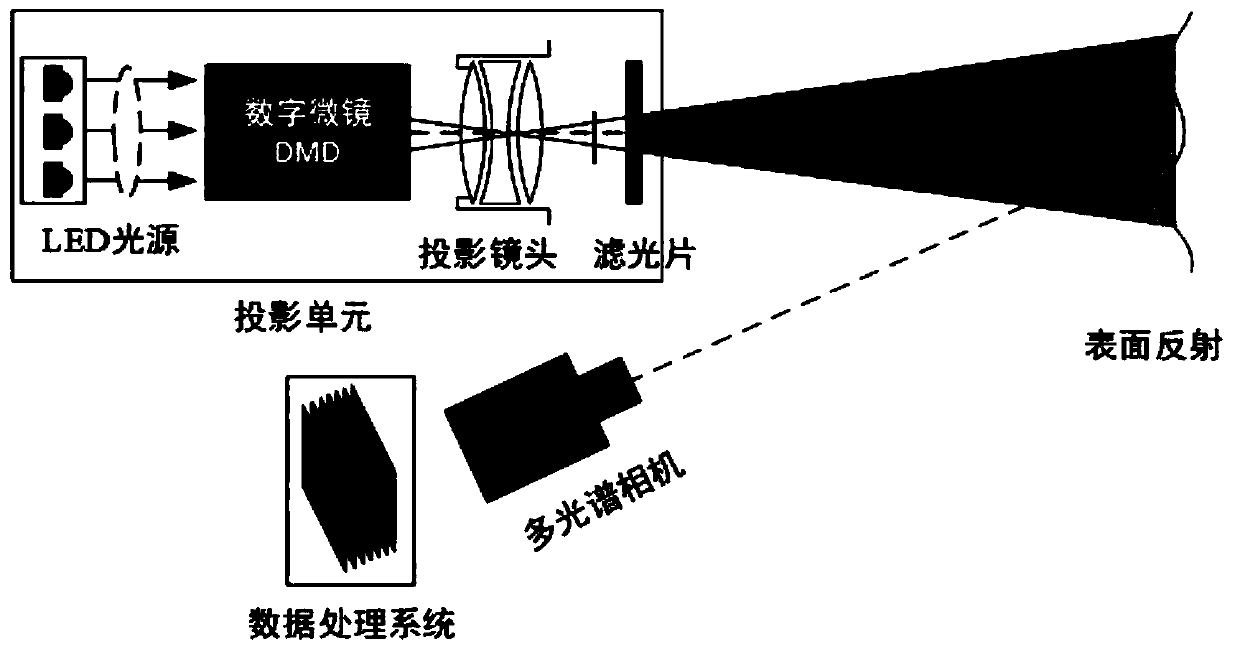

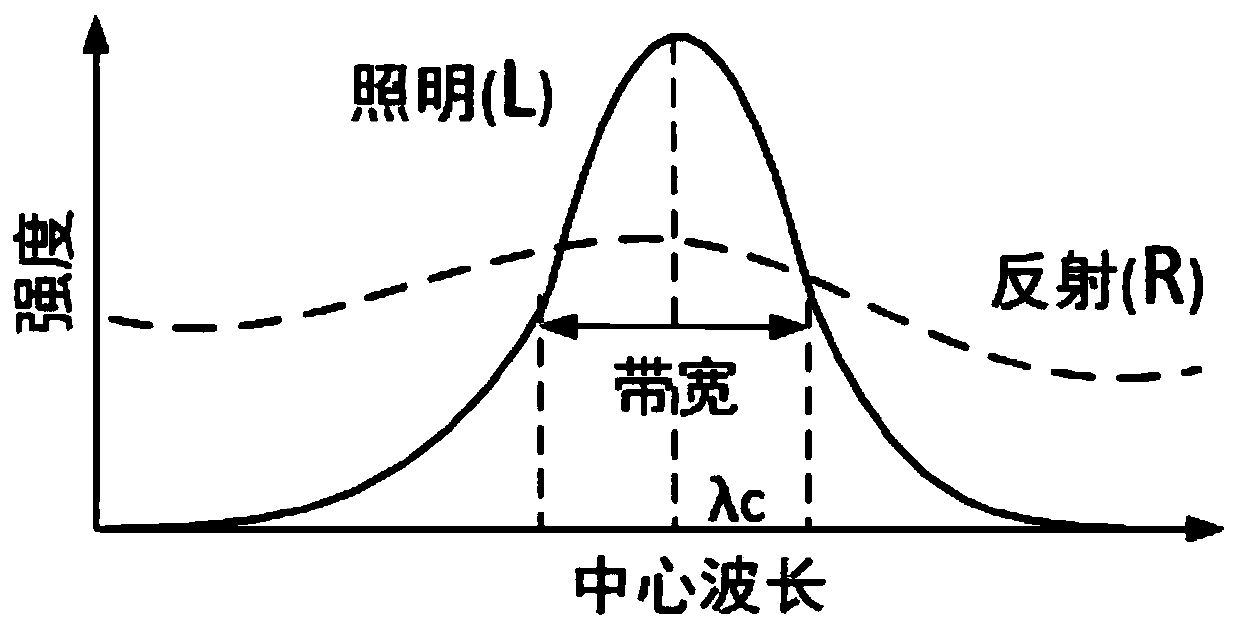

High-dynamic-range three-dimensional measurement method based on spectrum modulation and multispectral imaging

ActiveCN109916336AAvoid multiple shotsConvenient 3D measurementUsing optical meansObject basedThree dimensional measurement

The invention discloses a high-dynamic-range three-dimensional measurement method based on spectrum modulation and multispectral imaging, which comprises the following steps: constructing a fringe projection system comprising a projection unit and an imaging unit, and obtaining system parameters through system calibration; the projection unit generating and projecting a plurality of phase shift stripe patterns to the surface of an object to be measured, and the imaging unit acquiring a multispectral stripe image sequence reflected by the object; on the basis of the multispectral stripe image sequence, making a pixel saturation judgment on each spectral channel image; performing multi-channel fringe image fusion based on a saturation judgment result, to obtain a fused fringe image sequence;calculating a wrapping phase based on the fused fringe image sequence, and obtaining absolute phase information through a phase unwrapping algorithm; and recovering the three-dimensional shape of themeasured object based on the system parameters and the absolute phase. By adopting the method, stripe imaging and three-dimensional measurement within a high dynamic range can be rapidly achieved under single exposure, repeated shooting of a traditional multi-exposure method is avoided, and the measurement efficiency is improved.

Owner:武汉斌果科技有限公司

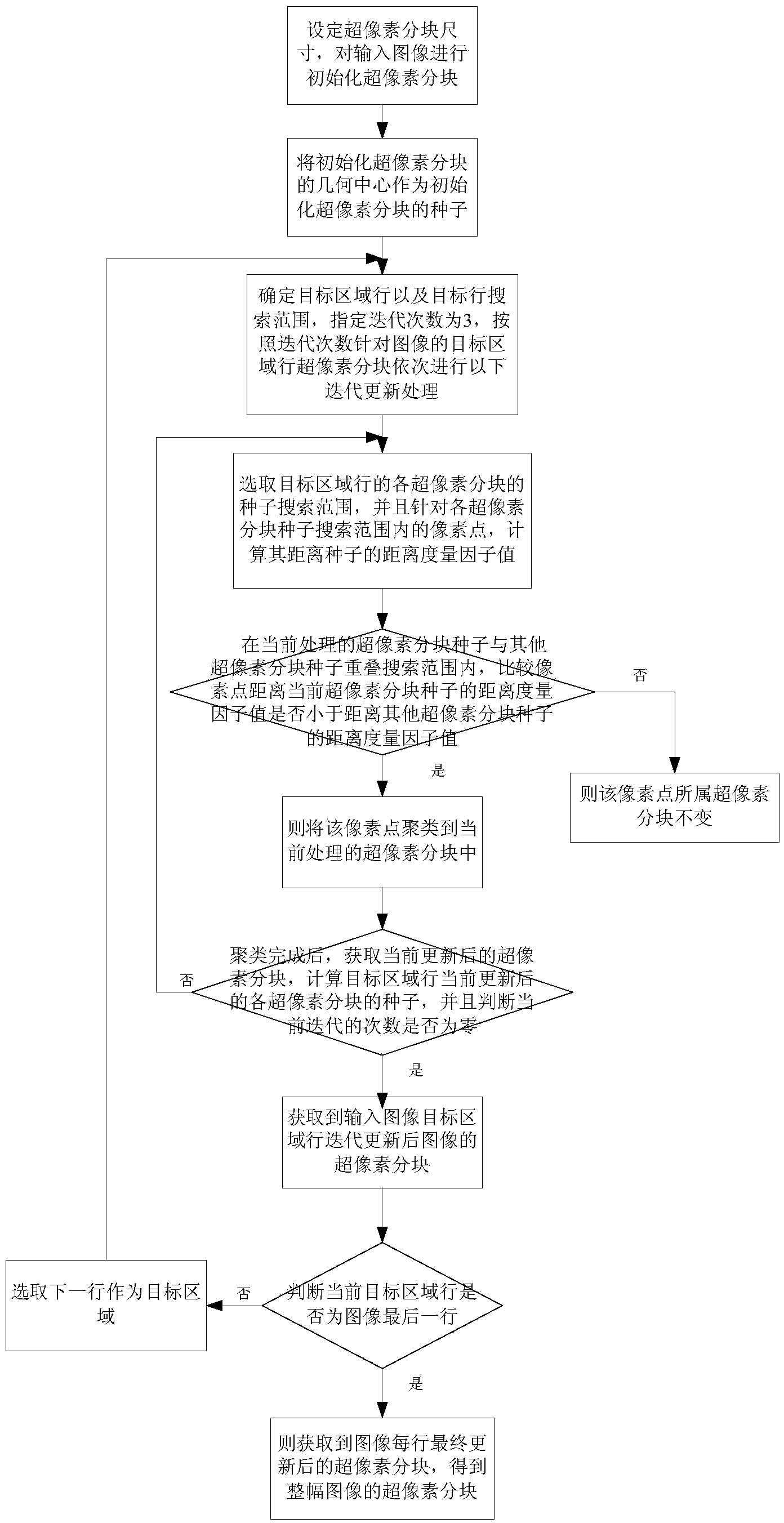

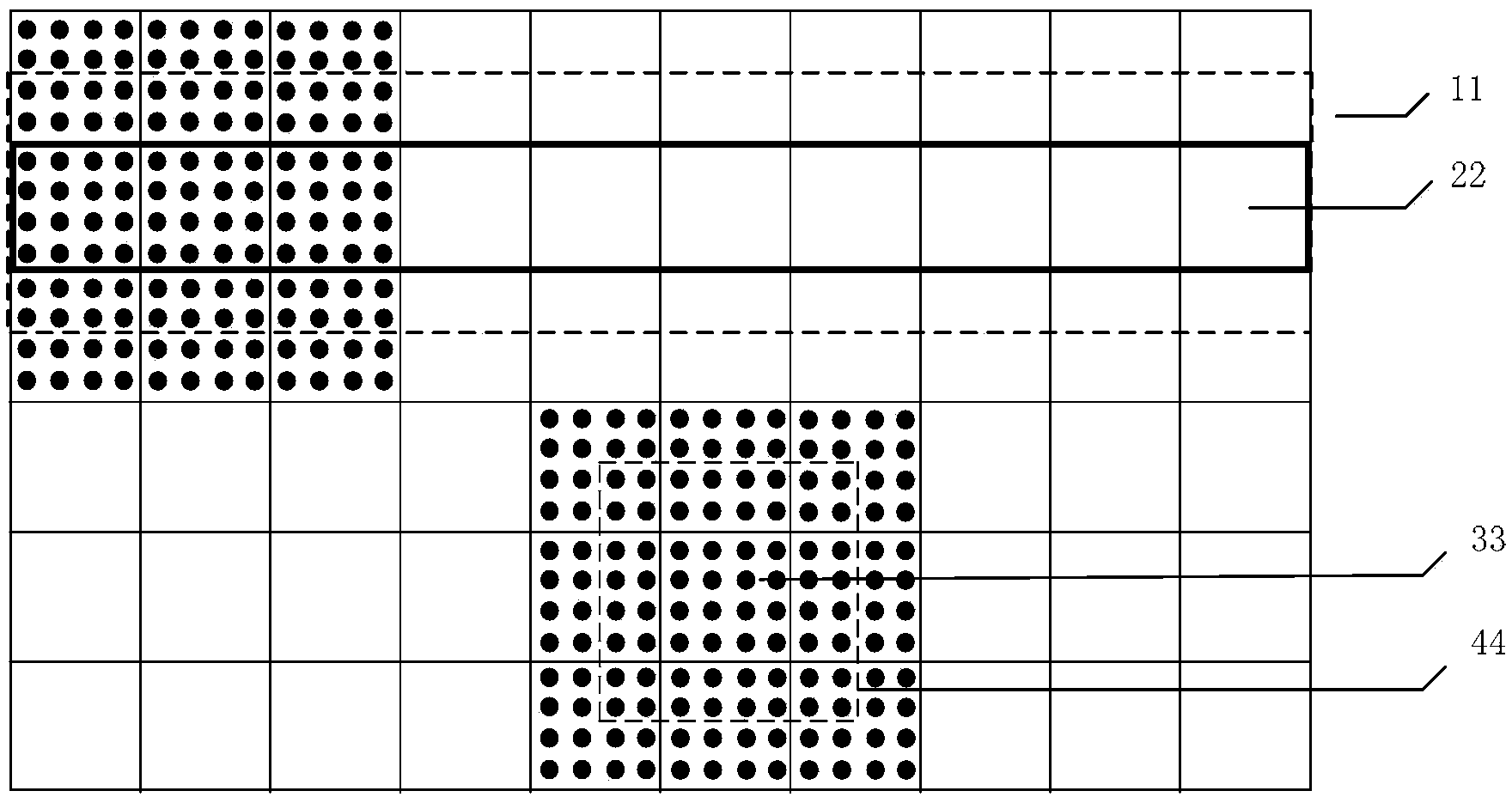

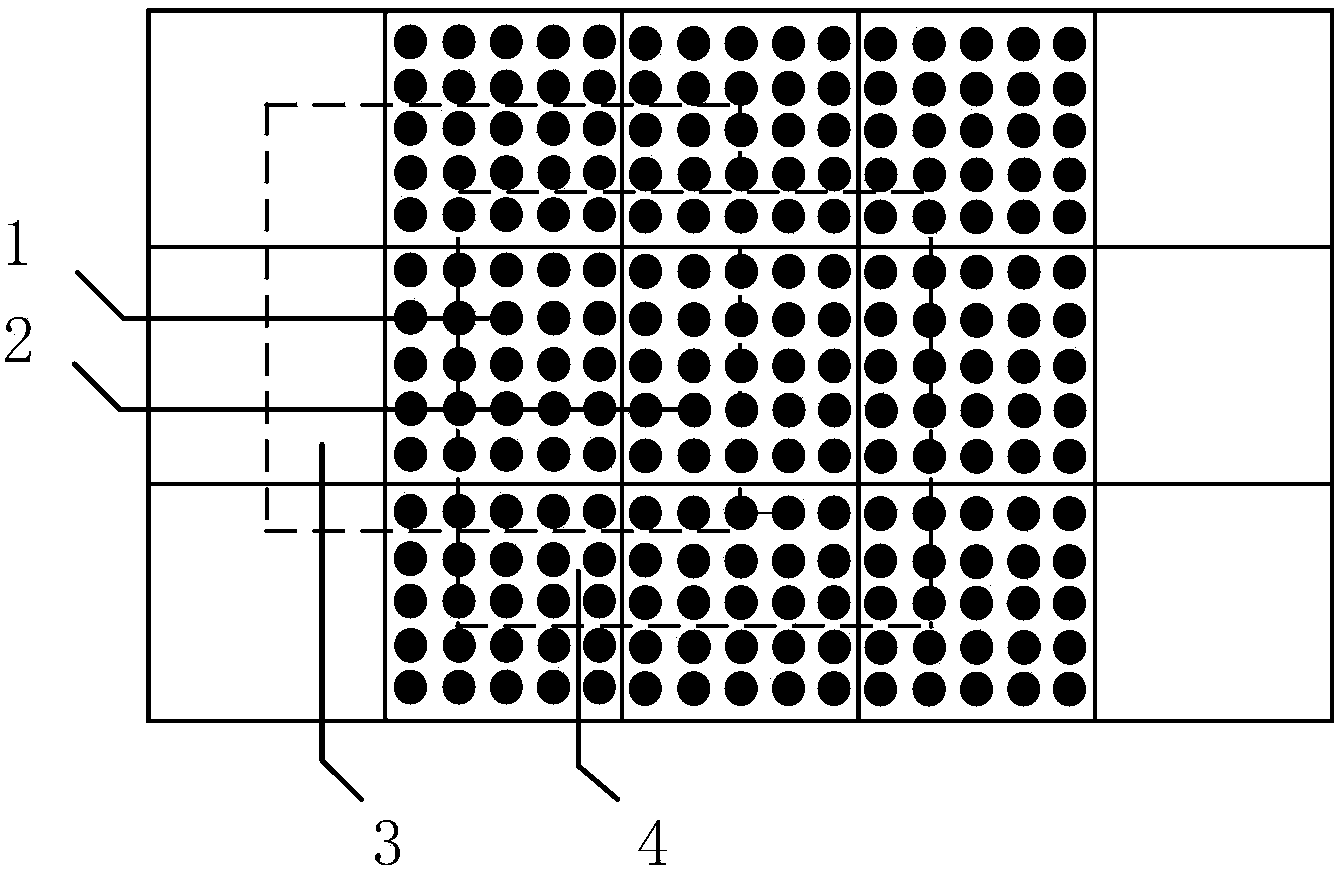

SLIC super-pixel block optimizing method

InactiveCN104143186AReduce storage requirementsReduce the amount of calculationImage analysisTheoretical computer scienceTarget line

The invention discloses an SLIC super-pixel block optimizing method. The method includes the steps that (1) initialized super-pixel blocks are obtained; (2) initialized super-pixel block seeds are obtained; (3) the super-pixel blocks on each line serve as target zones, a search range is determined, the number of iteration times is designated, and update processing is conducted, wherein (3-1) the search range is selected according to target line seeds and pixel point distance measuring factor values are calculated; (3-2) in the overlapped search range of the current super-pixel block seeds and other super-pixel block seeds, the pixel point distance measuring factor values are compared, and pixel points closer to the current super-pixel block seeds are clustered into the current super-pixel blocks; (3-3) the updated super-pixel blocks are obtained, updated super-pixel block seeds on target lines are calculated, whether the number of iteration times is zero or not is judged, if not, the step (3-1) is executed again according to the updated target lines, and if yes, the finally-updated super-pixel blocks are obtained. The method has the advantages of being small in calculated amount and convenient to conduct through hardware.

Owner:SOUTH CHINA UNIV OF TECH

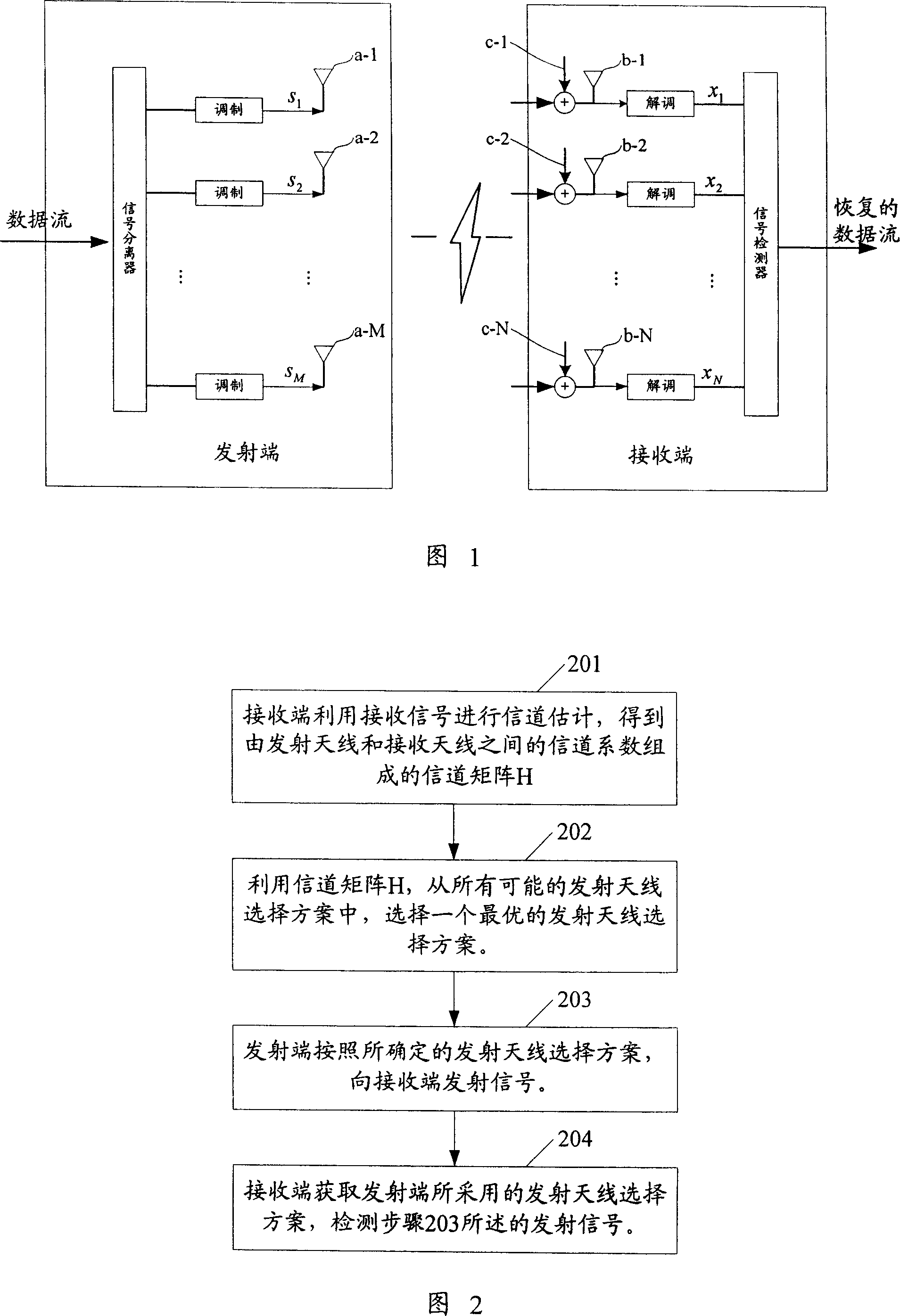

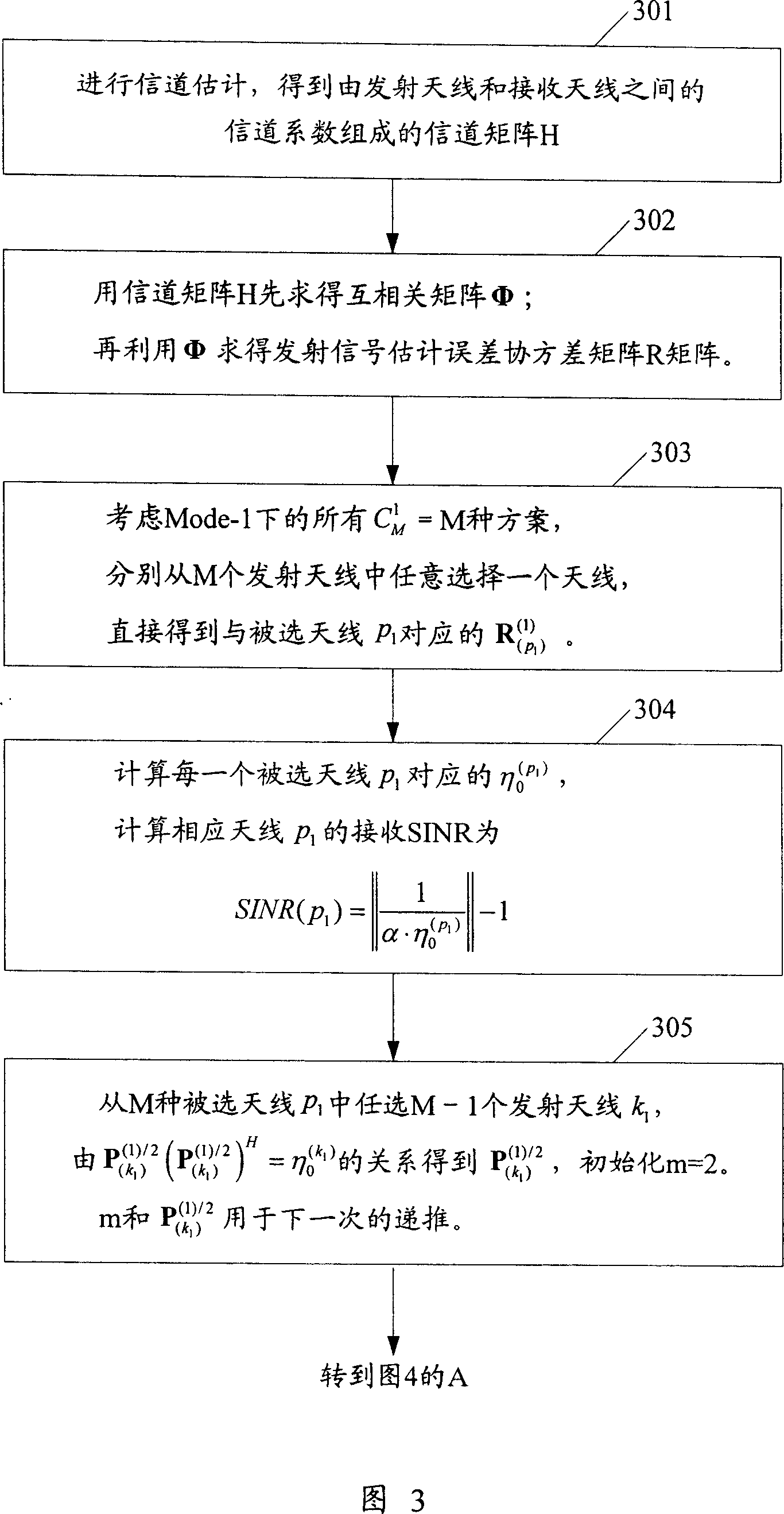

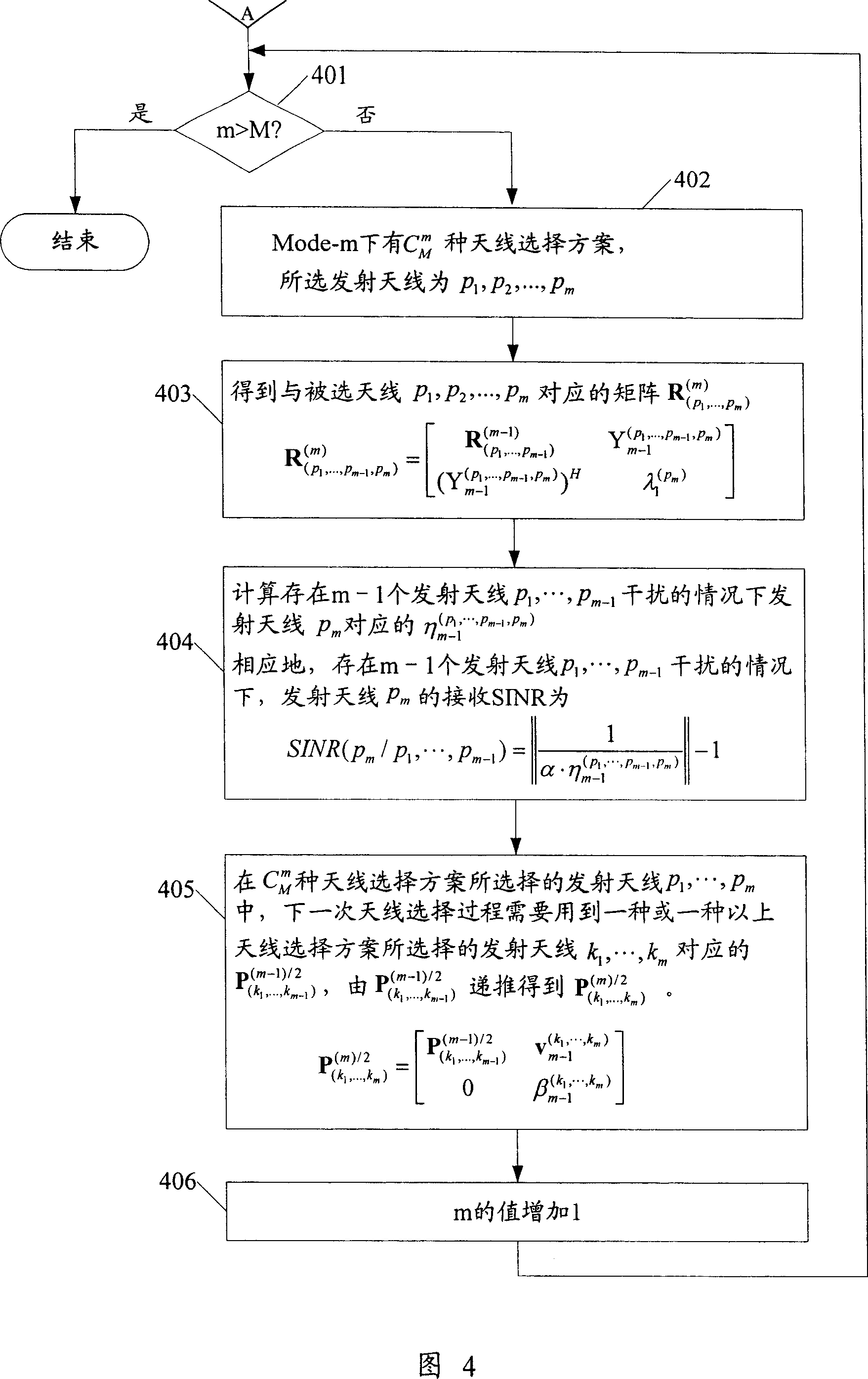

The method for antenna selection scheme and signal detection in the multi-antenna communication system

InactiveCN101009509AReduce computational complexityEase of hardware implementationSpatial transmit diversityError prevention/detection by diversity receptionDecompositionIntermediate variable

The invention discloses a method for determining the selection project of antenna on the multi antenna communication system, the method includes: using the decomposition gene matrix of estimating error covariance matrix of little emission antenna recurs the middle variables of decomposition gene matrix of few emission antennas, and uses the middle variables to compare the receiving signal and disturbance signal SINR of all emission antennas chosen by the all selection projects of antennas, and determines the selection project according to the comparing SINR result. The invention also provides a detection method in the multi antenna communication system, the method includes: using the decomposition gene matrix of estimating error covariance matrix which are got by the SINR, or using the middle variables of decomposition gene matrix and relative with the decomposition gene matrix to recur the decomposition gene matrix which is need by the detection signal, calculate the zero vector of every detected emission antennas, and use the zero vector to detect the signal of emission antenna.

Owner:HUAWEI TECH CO LTD

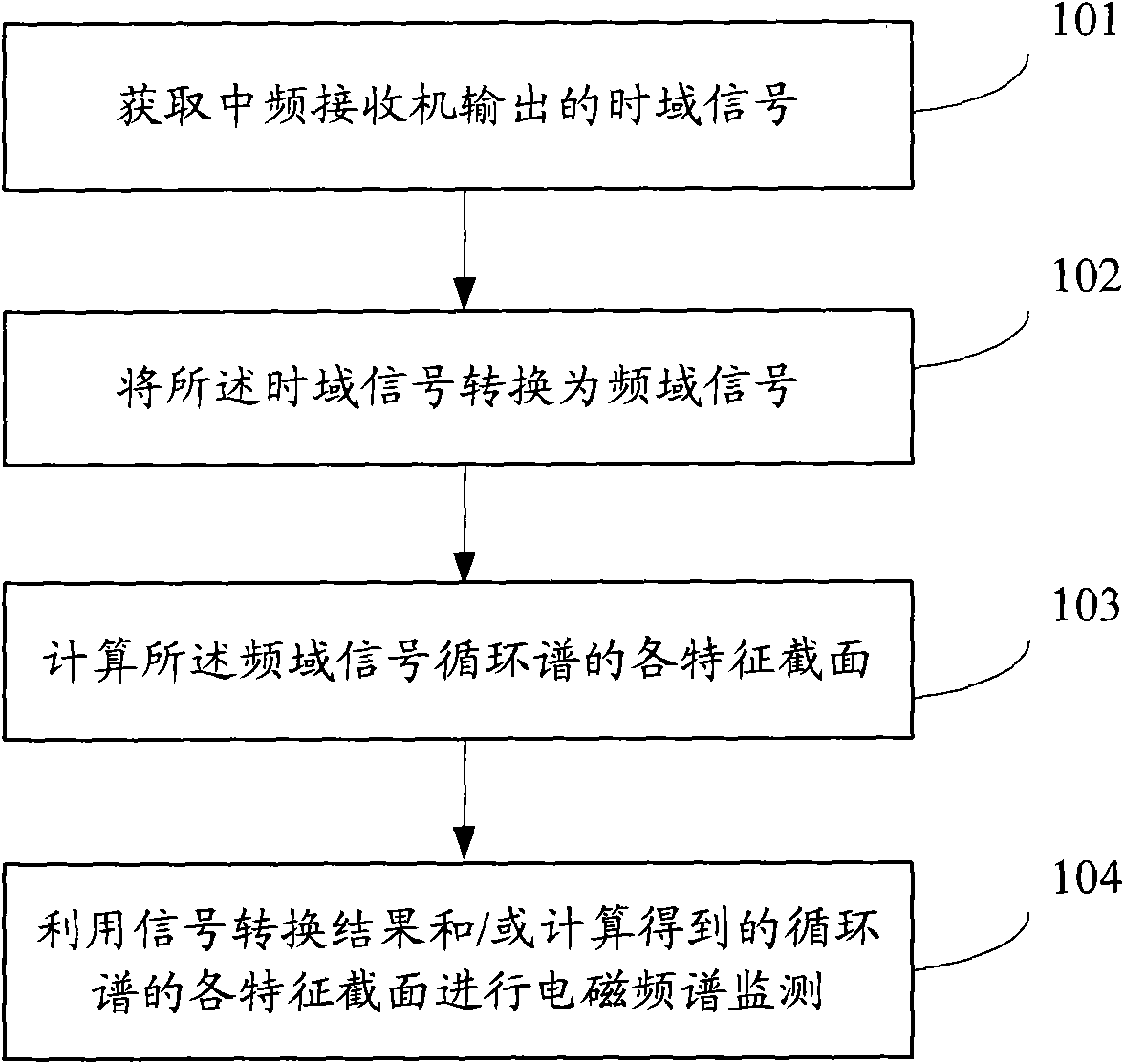

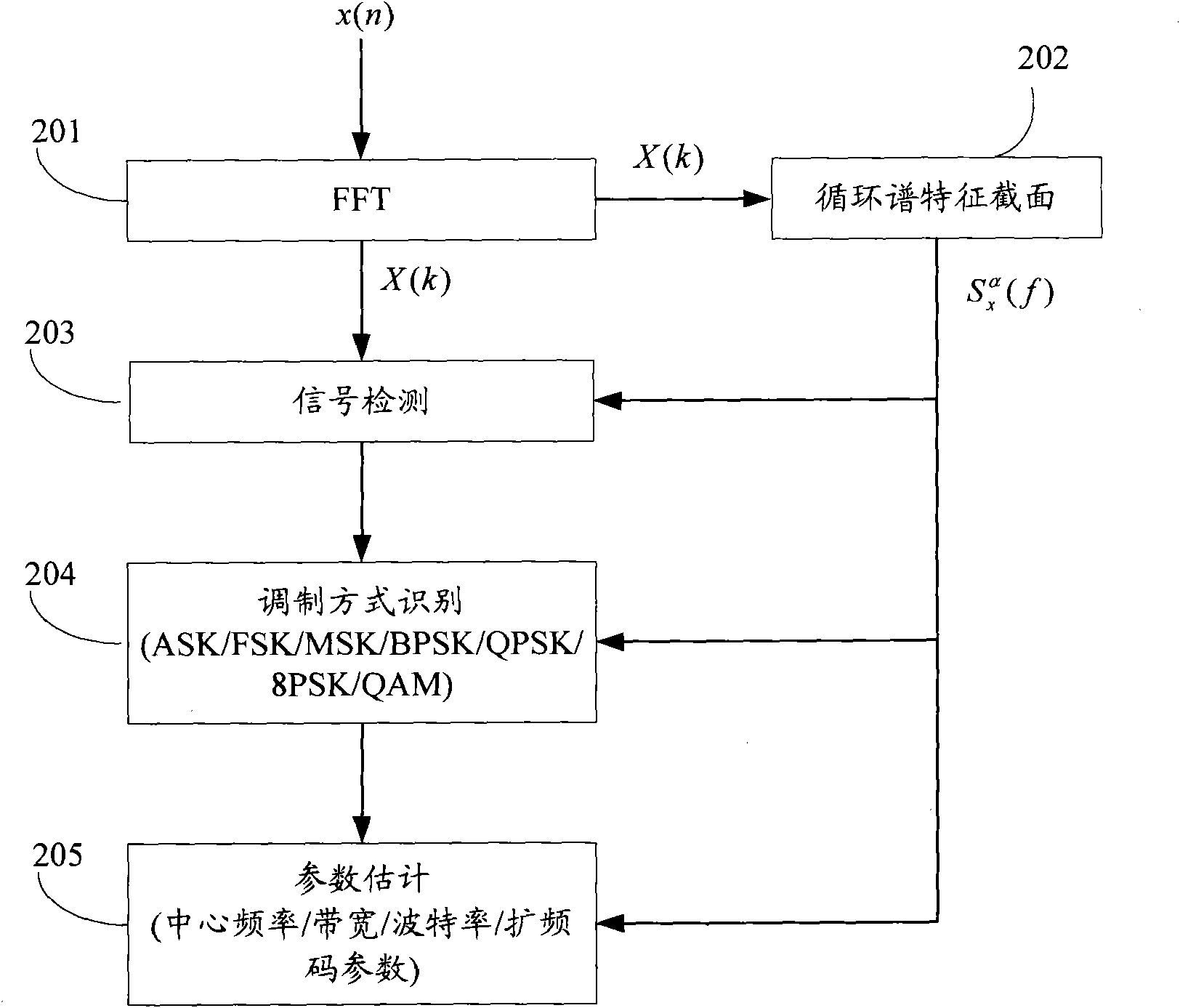

Method and system for monitoring electromagnetic spectrum

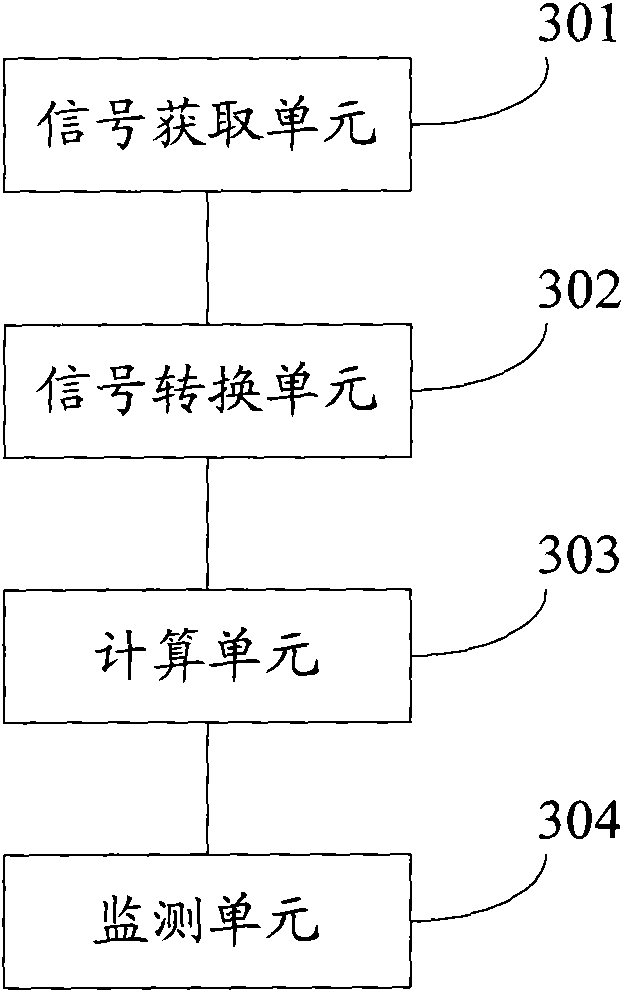

InactiveCN101977091ASimplify complexityFlexible loadabilityTransmission monitoringTime domainFrequency spectrum

The invention discloses a method and system for monitoring an electromagnetic spectrum, wherein the method comprises the following steps of: obtaining a time-domain signal output by an intermediate-frequency receiver; and converting the time-domain signal into a frequency-domain signal; computing each characteristic cross section of the cyclic spectrum of the frequency-domain signal; and monitoring the electromagnetic spectrum by utilizing the conversion result of the signal and / or each characteristic cross section of the cyclic spectrum obtained through computation. The invention can be utilized for completely realizing the monitoring processing for the electromagnetic spectrum in a frequency domain and can be simply and effectively applied to sensor nodes.

Owner:THE PLA INFORMATION ENG UNIV

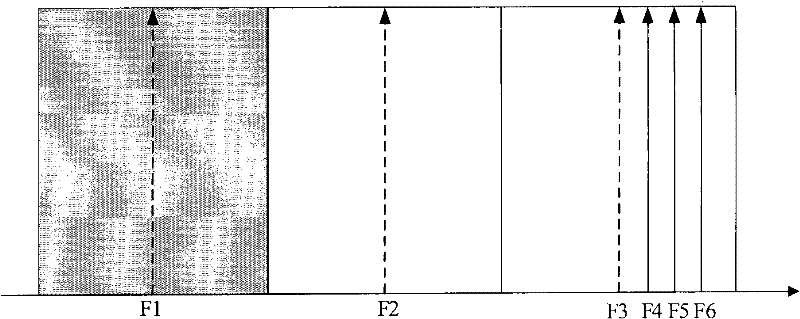

Downlink frequency offset compensation method and repeater used for performing downlink frequency offset compensation

InactiveCN102164109ASimple hardwareEase of hardware implementationActive radio relay systemsMulti-frequency code systemsEmission channelingSignal on

The invention discloses a downlink frequency offset compensation method which comprises: in a to-be-compensated downlink time slot, a base station inserts a specific signal on a pre-appointed assistant carrier of each RRU (radio remote unit); a repeater receives a signal, and compares the frequency of the received signal with the frequency of the specific signal, thereby acquiring a frequency error between the two frequencies; and the repeater compensates the frequency error to an emission channel. The invention also discloses a repeater used for performing downlink frequency offset compensation. By using the method and repeater provided by the invention, the downlink frequency offset compensation can be performed on a common signal channel and the channels of other BBU (base band unit) which are not compensated with frequency.

Owner:TD TECH COMM TECH LTD

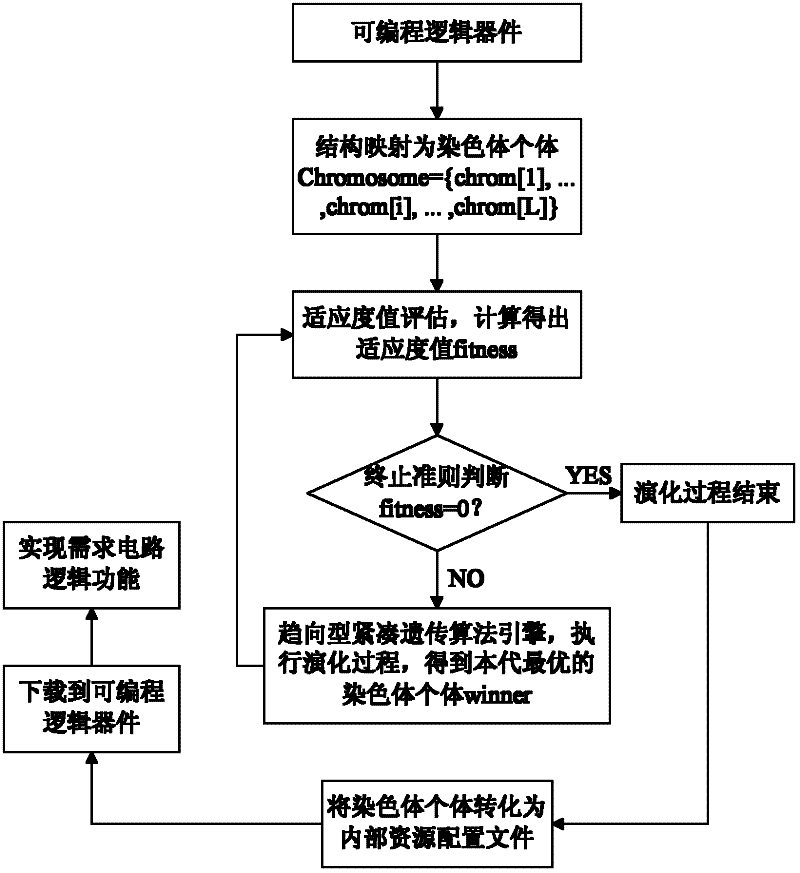

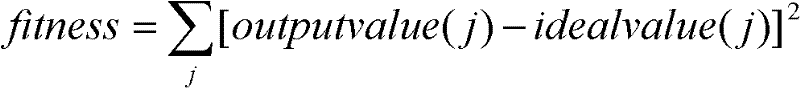

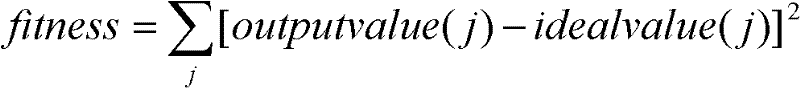

Evolvable hardware implementation method based on trend-type compact genetic algorithm

ActiveCN102254225AProvide real-timeEase of hardware implementationPhysical realisationEvolvable hardwareProgrammable logic device

The invention relates to an evolvable hardware implementation method based on a trend-type compact genetic algorithm, and the method comprises the following steps of: 1) obtaining configuration parameters of an actual programmable logic device; 2) mapping the configuration parameters of the actual programmable logic device and forming into chromosome individuals; 3) calculating the fitness of thecurrent chromosome individuals; and 4) identifying whether to terminate the evolvement according to the situation of the fitness. The evolvable hardware implementation method based on the trend-type compact genetic algorithm can be used for enhancing the search capability of a hardware configuration bit string, increasing the diversity of a candidacy solution space, obtaining high-quality and optimal hardware configuration structure bit string more fast, greatly increasing the convergence speed, reducing the time required by obtaining an optimal hardware circuit structure and enhancing the real-time performance of the actual evolvable hardware.

Owner:XI'AN INST OF OPTICS & FINE MECHANICS - CHINESE ACAD OF SCI

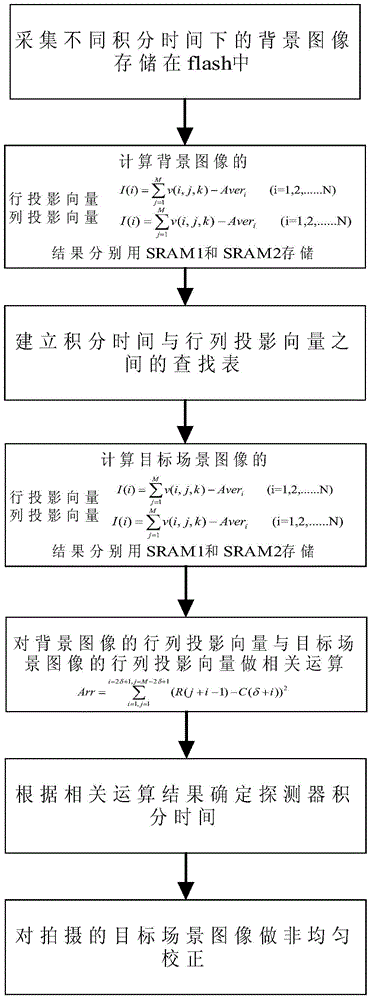

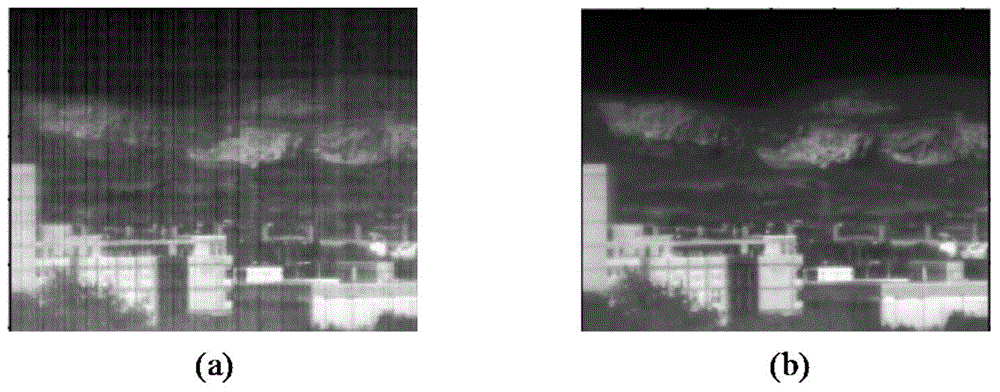

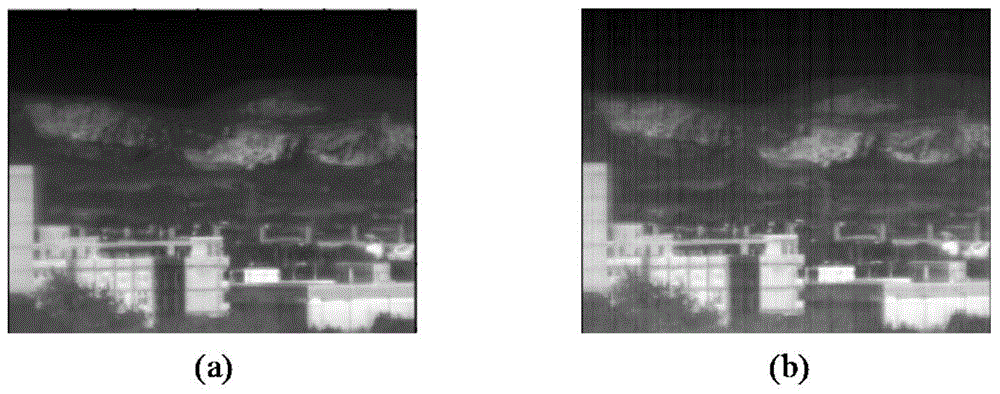

Variable integral time non-uniformity correction method based on scenes

InactiveCN105092043ABest integration timeImprove registration accuracyRadiation pyrometryImage analysisLookup tableBackground image

The invention discloses a variable integral time non-uniformity correction method based on scenes. The method comprises calculating row projection vectors and column projection vectors of background images of a detector under different integral conditions firstly, storing the background row and column projection vectors, and then forming a lookup table. When the detector shoot an image at the different scenes, in order to determine best integral time of the detector, the row and column projection vectors of the image are calculated firstly, related operation respectively between the row and column projection vectors and the background row and column vectors in the lookup table are performed, the most relevant background of the image is found, and the best integral time of the detector is determined through the background. Innovation points of the method are in that the best integral time of the detector in the different scenes can be found, the image obtained under the best integral condition is in favor of subsequent image registration, registration precision is improved, and then the method has the good non-uniformity correction effect.

Owner:NANJING UNIV OF SCI & TECH

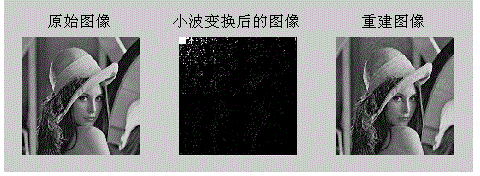

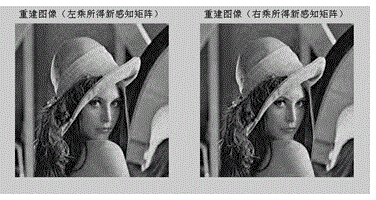

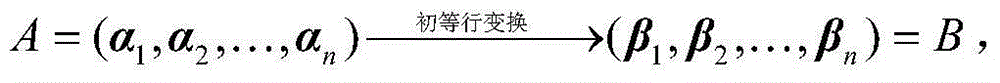

Generation method of sensing matrix for signal compressive sensing

ActiveCN104660269AGood application effectEase of hardware implementationCode conversionDiagonal matrixSignal reconstruction

The invention discloses a generation method of a sensing matrix for signal compressive sensing (CS). The generation method comprises the following steps: firstly, selecting a determinated sensing matrix or generating a random sensing matrix; then performing left multiplication on a specific reversible matrix or right multiplication on a specific reversible diagonal matrix or full permutation of lines / rows of the specific reversible diagonal matrix to obtain a matrix product which is the required novel sensing matrix. Based on conventional sensing matrixes, the structures or elements are adjusted to generate the sensing matrix with certain regularity, and meanwhile, the CS attribute is unchanged. Particularly for the determinated sensing matrix, the invention provides a very convenient generation or extension new way. The sensing matrix with certain regularity on structure or element facilitates improvement of a CS measurement system in the aspects of compressive sampling frequency, signal reconstruction speed, implementation cost and the like.

Owner:CENT SOUTH UNIV

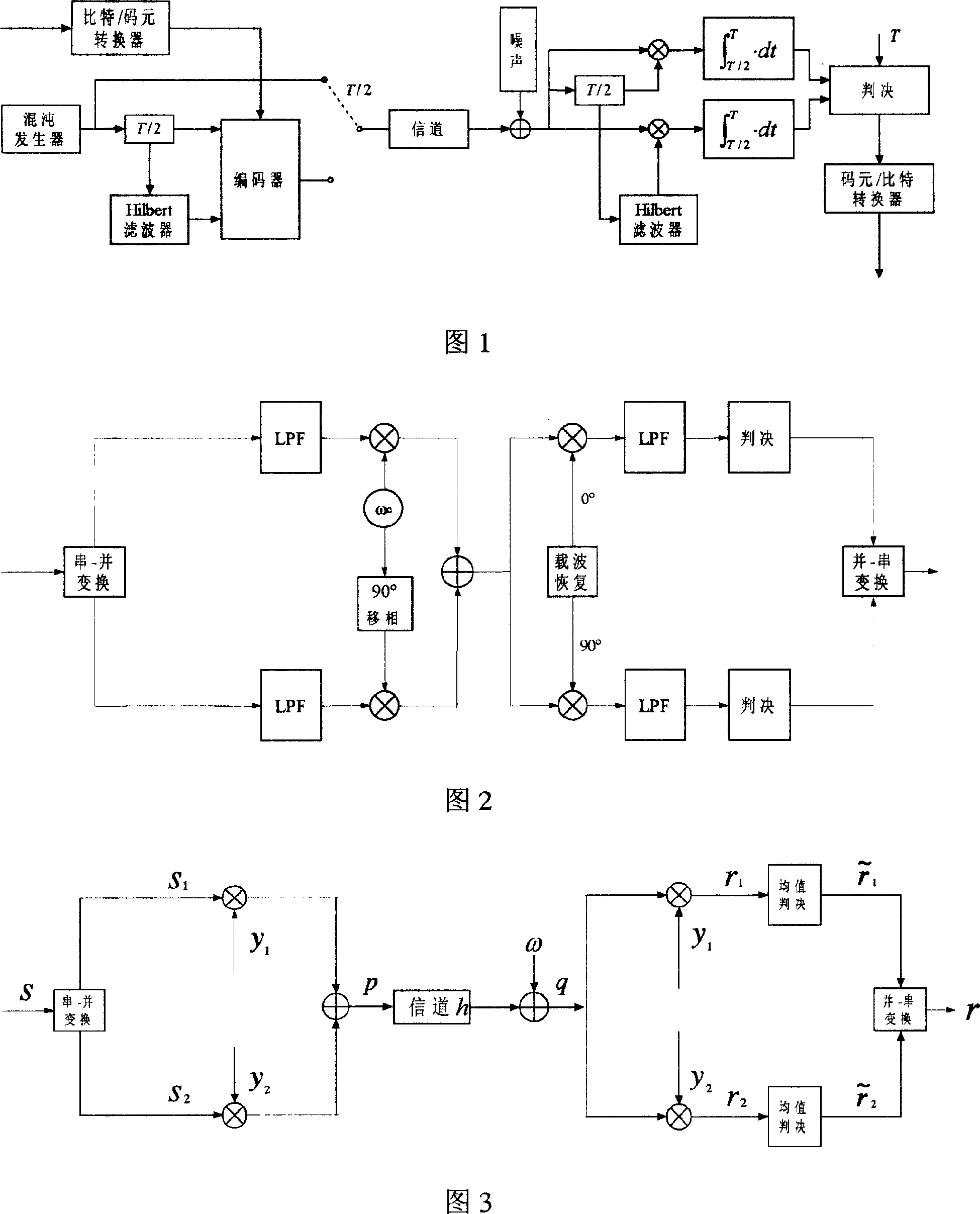

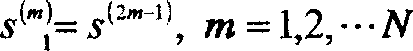

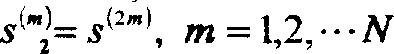

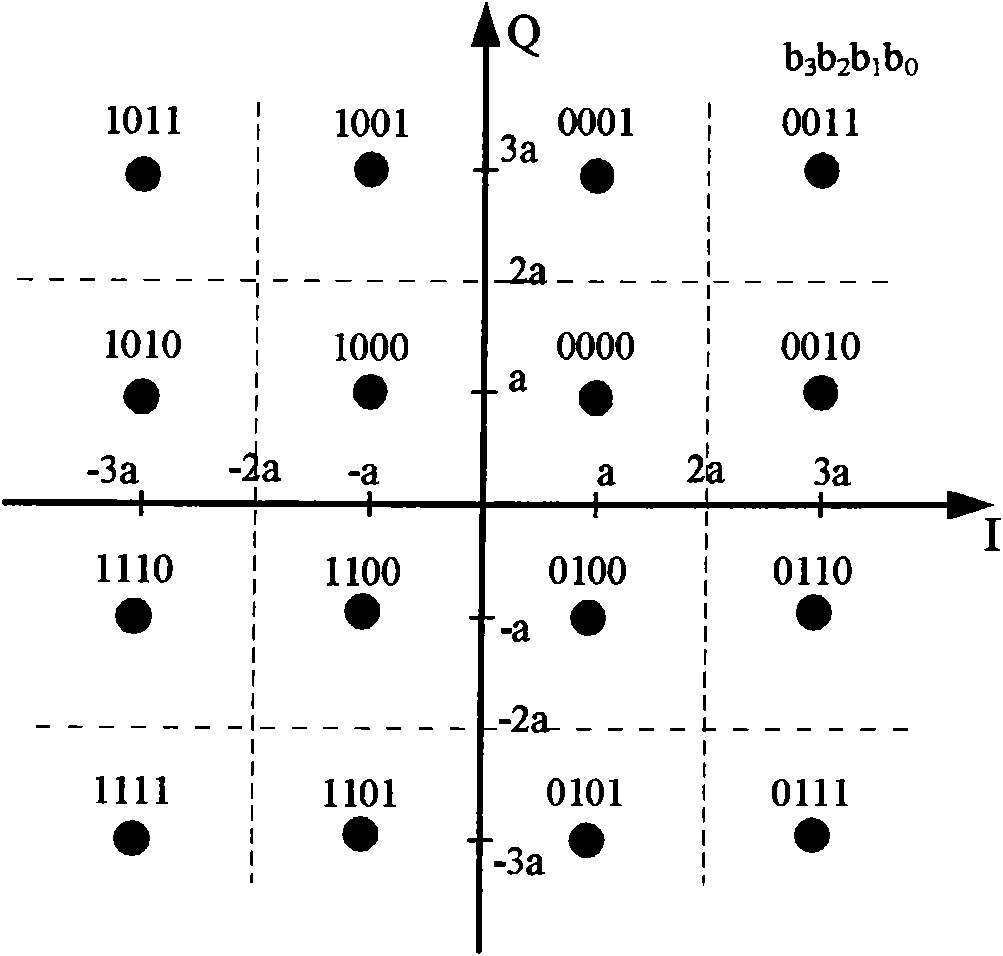

Orthogonal modulated chaos communication method

InactiveCN101026602ASimple system structureEase of hardware implementationMultiple carrier systemsCarrier signalSystem structure

Using Schimidt orthogonalization for chaos sequence set. The method generates a series of orthogonal basis functions as carrier waves. Then, using orthogonal amplitude modulation carries out modulation / demodulation. Features are: simple system structure, easy of realization through hardware, and higher interference killing feature than that of QCSK scheme.

Owner:SOUTH CHINA UNIV OF TECH

Hardware implementation system and method for high-performance elliptic curve digital signature and signature verification

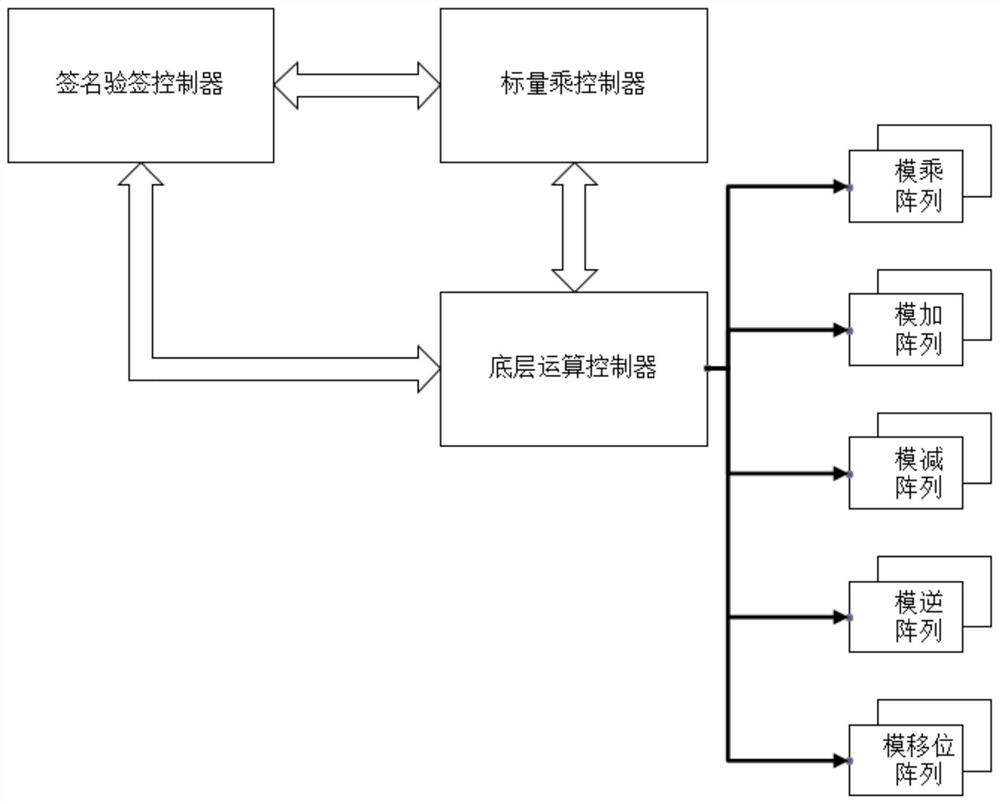

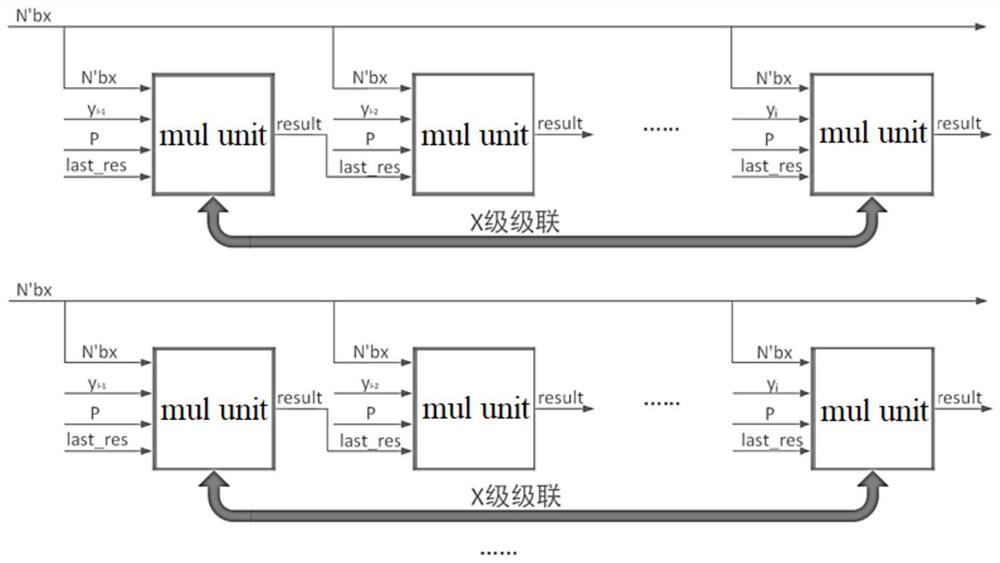

PendingCN113794572AReduce hardware circuit overheadEase of hardware implementationUser identity/authority verificationHardware accelerationAlgorithm complexity

The invention discloses a hardware implementation system and a method for high-performance elliptic curve digital signature and signature verification, and belongs to the technical field of information security. In order to solve the problems that in the prior art, an ECDSA algorithm is high in complexity, long in calculation time consumption and large in hardware acceleration difficulty, the system comprises a signature verification controller, a scalar multiplication controller, a bottom layer operation controller and an operation array for achieving various modular operations, and a novel modular multiplication array structure is provided in the operation array. The scheduling of point doubling and point adding calculation is facilitated, and the performance is high in unit area. According to the invention, point doubling, point addition, modular multiplication operation, modular addition operation, modular subtraction operation, modular inverse operation, modular shift operation and other underlying operations are integrated together, resource sharing of a calculation path is realized to the greatest extent, and high-performance implementation of modular multiplication is combined, so that a high-performance elliptic curve digital signature and signature verification algorithm is realized under relatively low hardware overhead.

Owner:南京宁麒智能计算芯片研究院有限公司

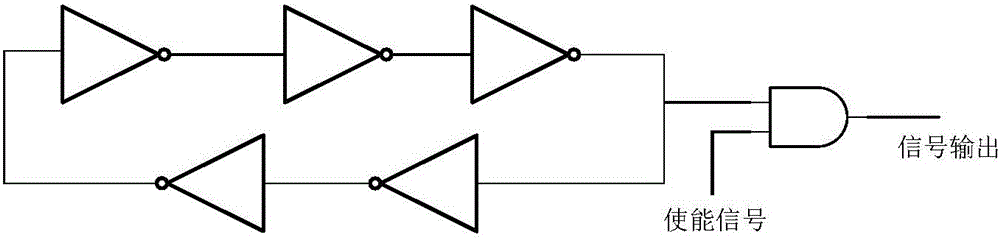

MOS tube parameter degradation detection circuit

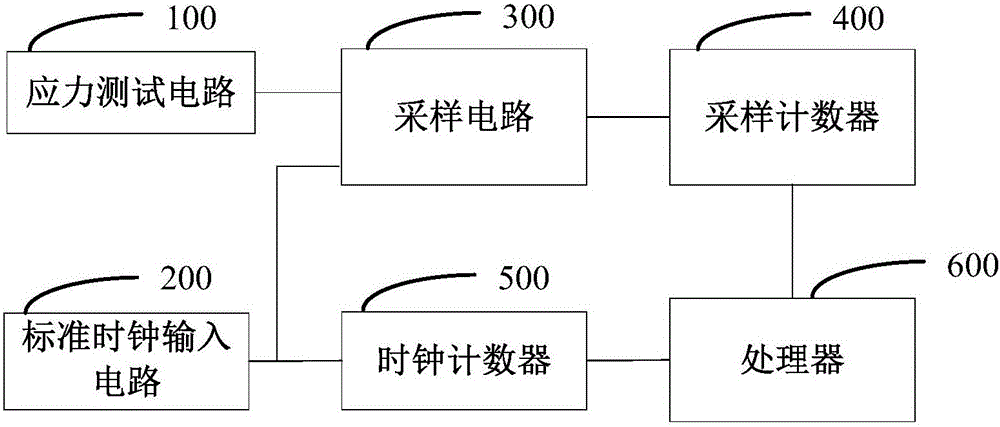

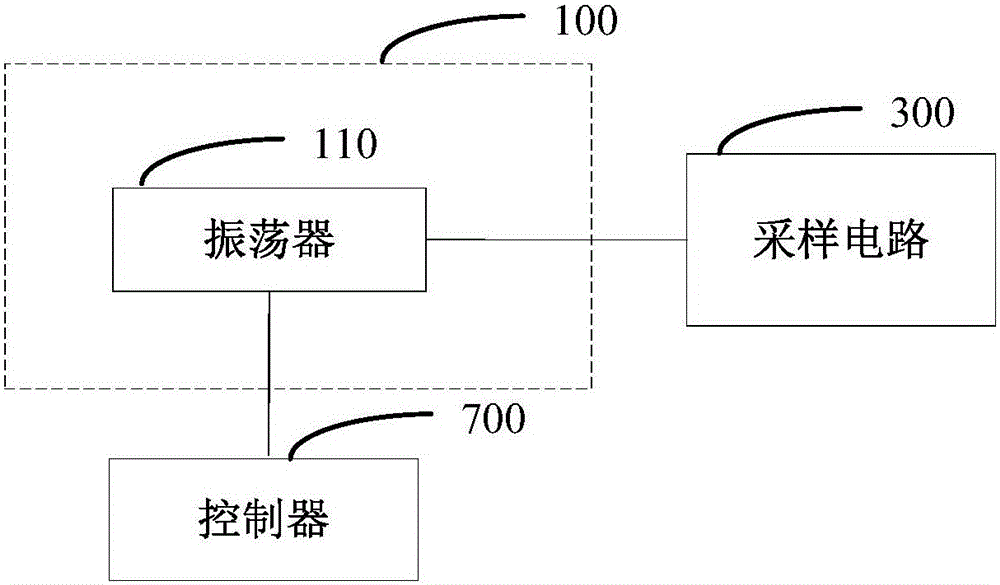

ActiveCN105759190AEasy to transplantMeet the requirements of online monitoringIndividual semiconductor device testingSampling circuitsClock signal

The invention relates to an MOS tube parameter degradation detection circuit comprising a stress test circuit, a standard clock input circuit, a sampling circuit, a sampling counter, a clock counter, a controller, and a processor. In the MOS tube parameter degradation detection circuit, the stress test circuit outputs a test signal characterizing the parameters of an MOS tube in the stress test circuit, the sampling circuit acquires sampling data according to the test signal, the sampling counter carries out counting according to the sampling data, the standard clock input circuit provides clock signals for the sampling circuit and the clock counter, the clock counter counts the clock signals, and the processor carries out calculation according to the count value of the sampling data and the count value of the clock signals to get the detection value of MOS tube parameter degradation. The detection circuit can complete detection of related values of MOS tube parameter degradation according to the composition thereof without the need for external equipment, the application scope of the detection circuit is improved effectively, and the requirement of online monitoring is satisfied.

Owner:FIFTH ELECTRONICS RES INST OF MINIST OF IND & INFORMATION TECH

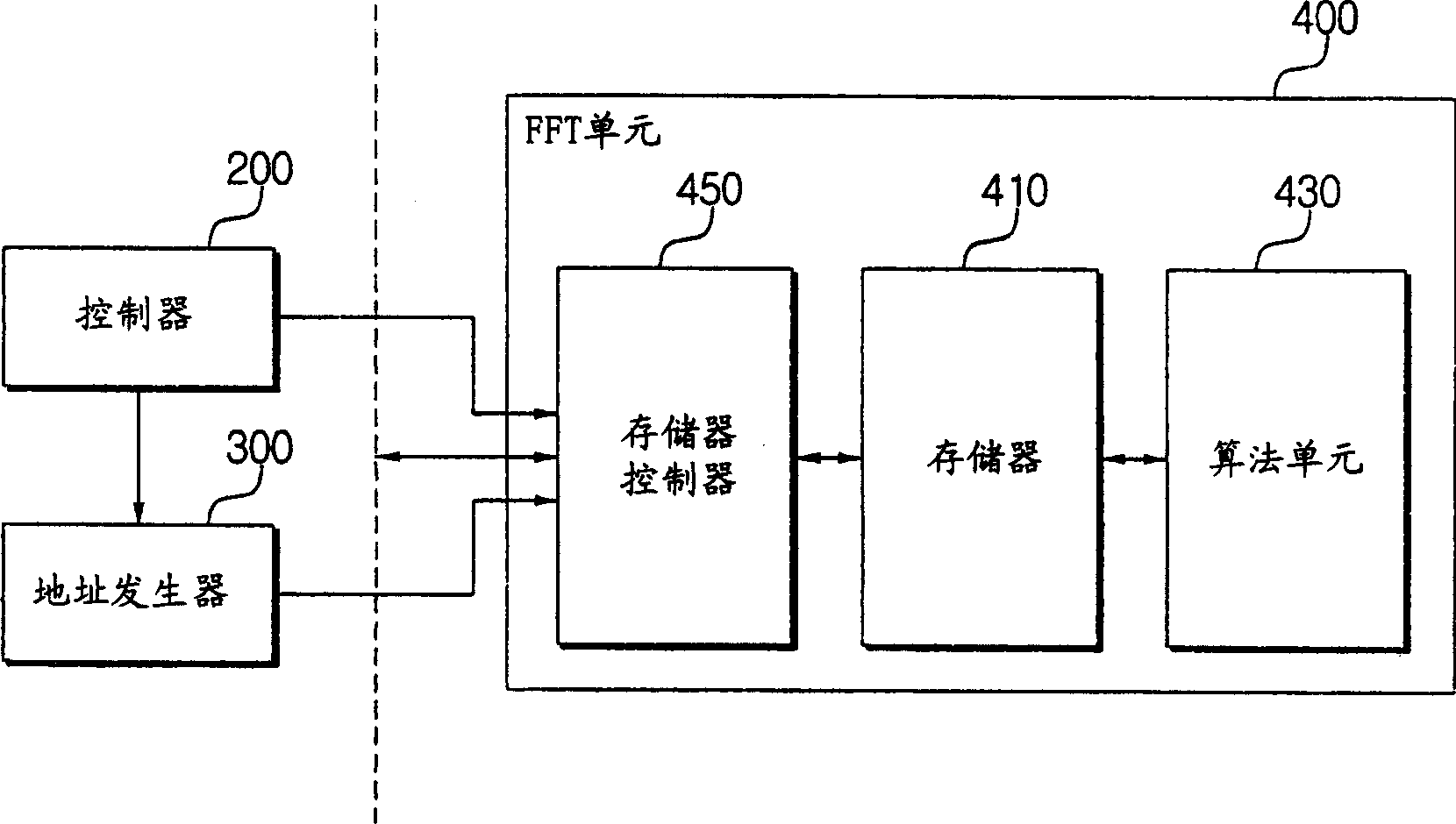

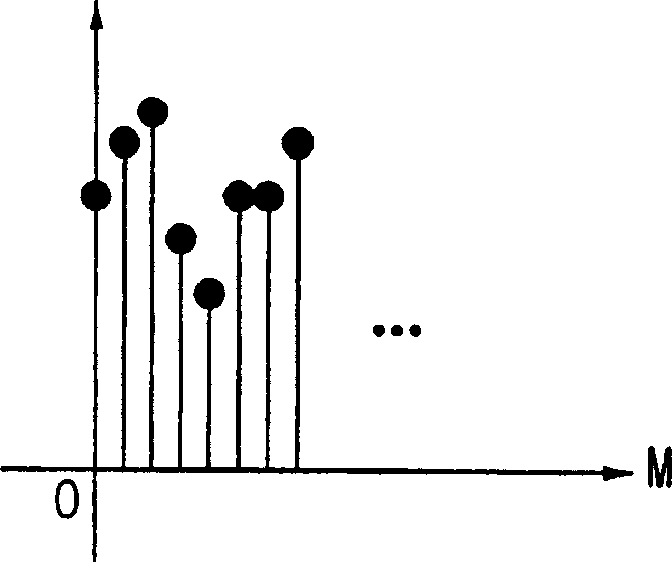

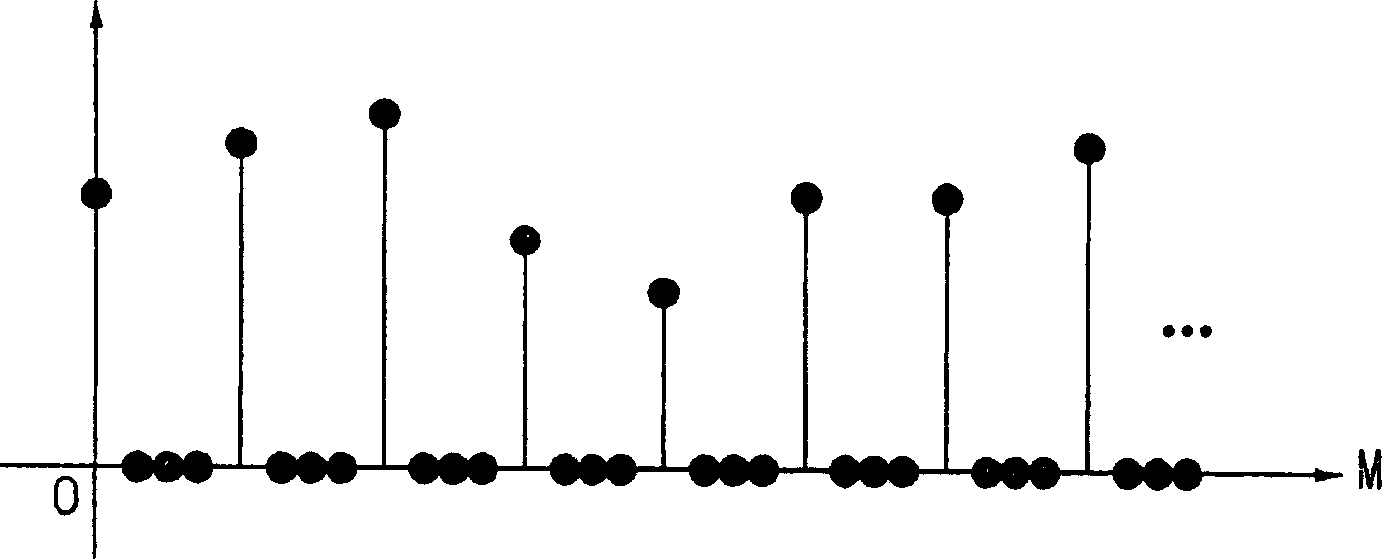

Digital audio broadcast receiver having simply implementable FFT processor

InactiveCN1520071ASimplified operation controlEase of hardware implementationBroadcast transmission systemsDigital audio broadcastingFast Fourier transformAddress generator

Disclosed is a European digital audio broadcast receiver having a simply implementable fast Fourier transform processor and an operation method therefor. A digital audio broadcast receiver having diverse fast Fourier transform (FFT) modes based on sizes of transmitted data has an address generator for generating a predetermined number of write addresses and read addresses, a fast Fourier transform (FFT) processor for repeating data of FFT modes to generate a predetermined number of data and implementing a fast Fourier transform (FFT) by using the predetermined number of data, and a controller for controlling the address generator to the write addresses and the read addresses according to operations of the FFT processor.

Owner:SAMSUNG ELECTRONICS CO LTD

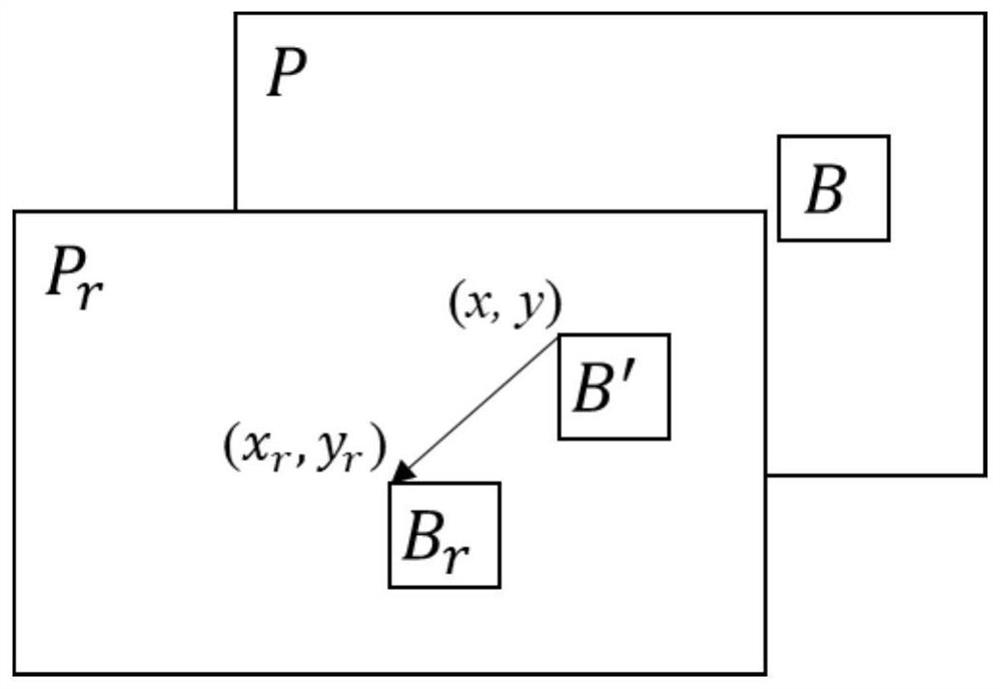

Method for obtaining image reference block in a code of mode of fixed reference frame number

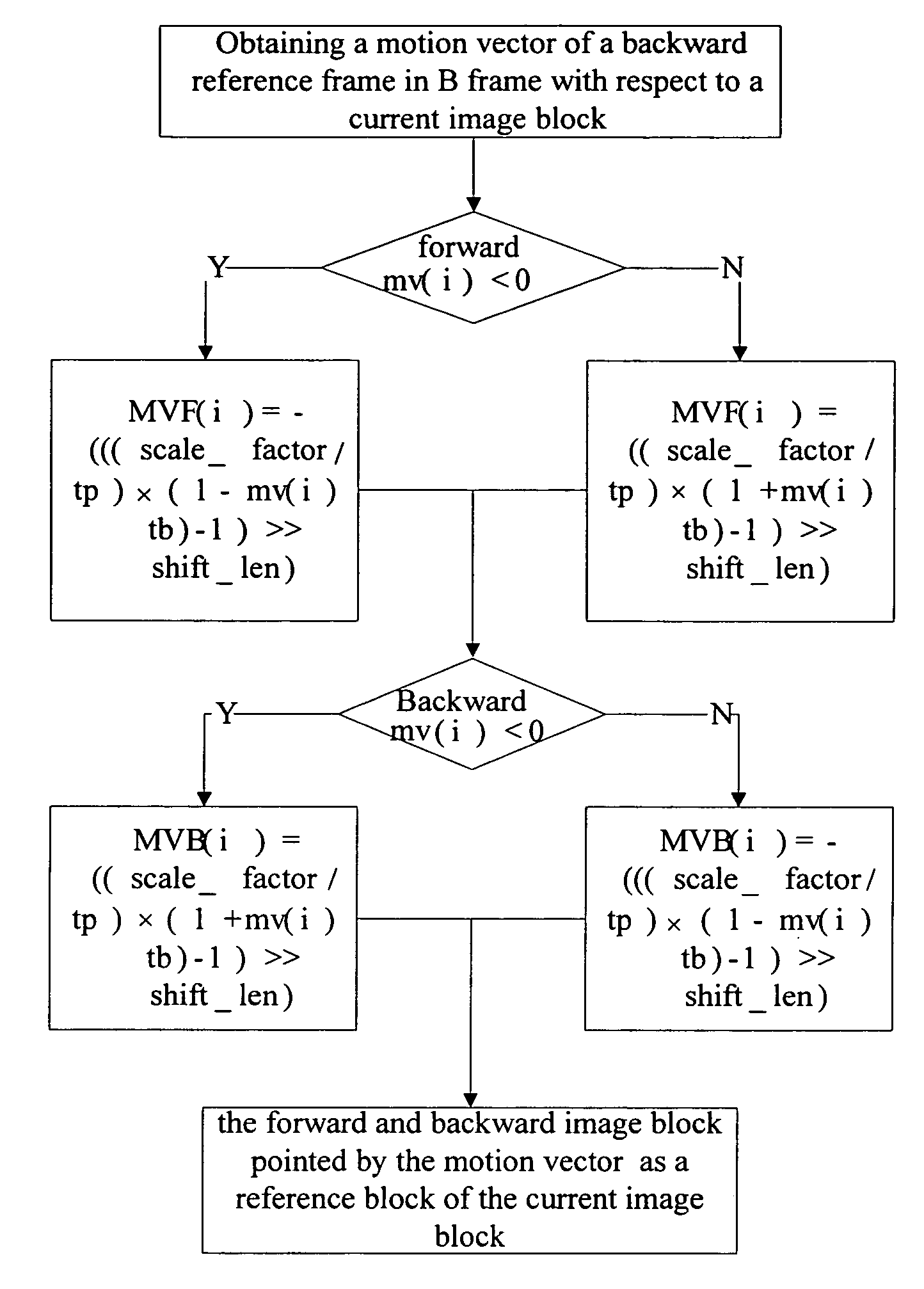

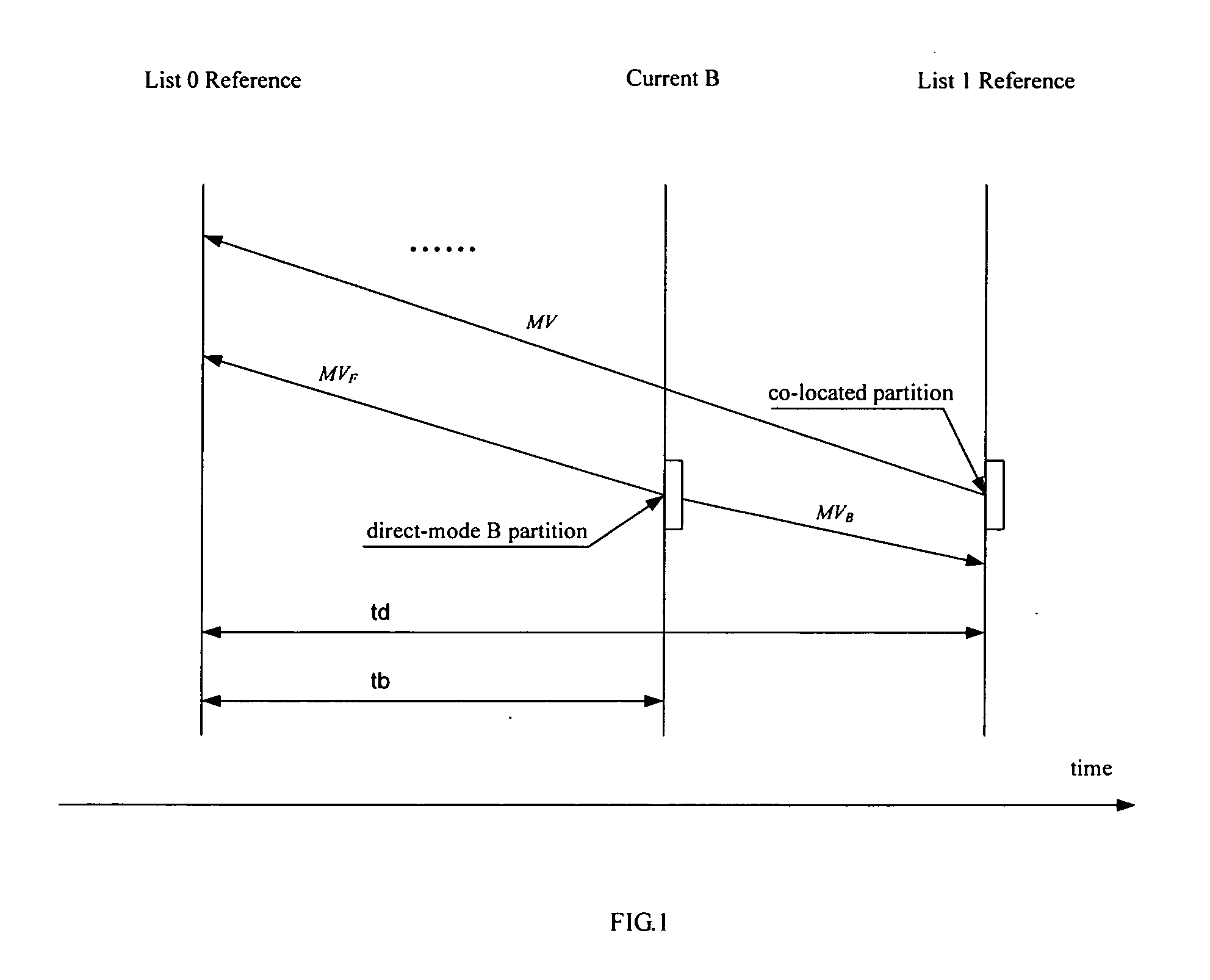

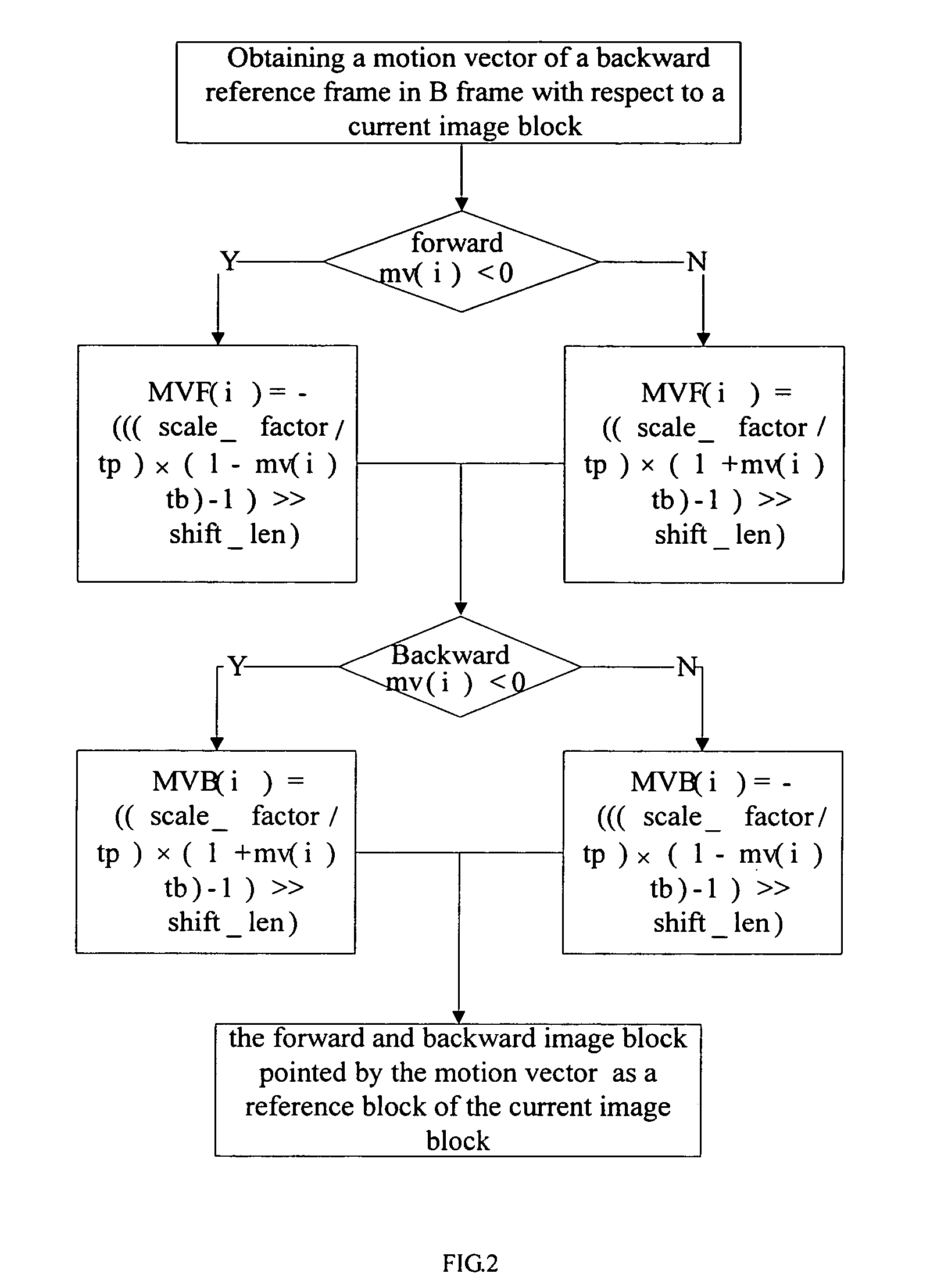

ActiveUS20090304083A1Improve coding efficiencyHigh precisionColor television with pulse code modulationPulse modulation television signal transmissionMotion vectorComputer science

The present invention discloses a “rounding to zero” method which can maintain the exact motion vector and can also be achieved by the method without division so as to improve the precision of calculating the motion vector, embody the motion of the object in video more factually, and obtain the more accurate motion vector prediction. Combining with the forward prediction coding and the backward prediction coding, the present invention realizes a new prediction coding mode, which can guarantee the high efficiency of coding in direct mode as well as is convenient for hardware realization, and gains the same effect as the conventional B frame coding.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

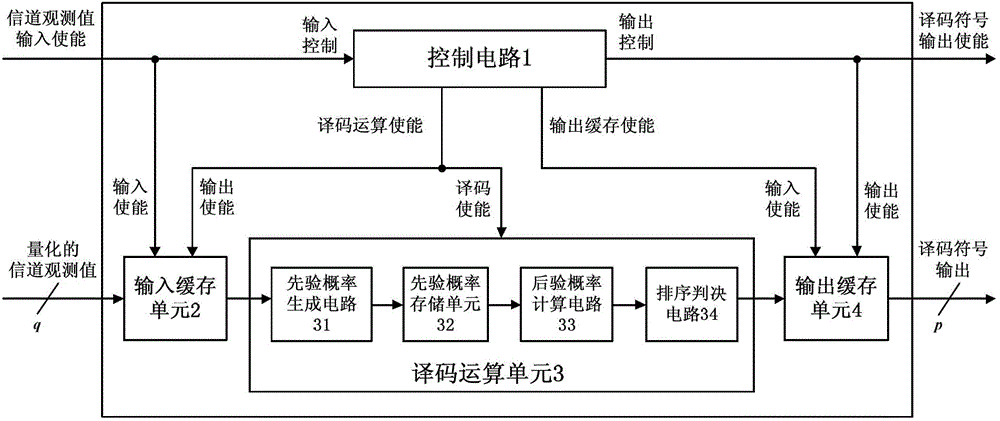

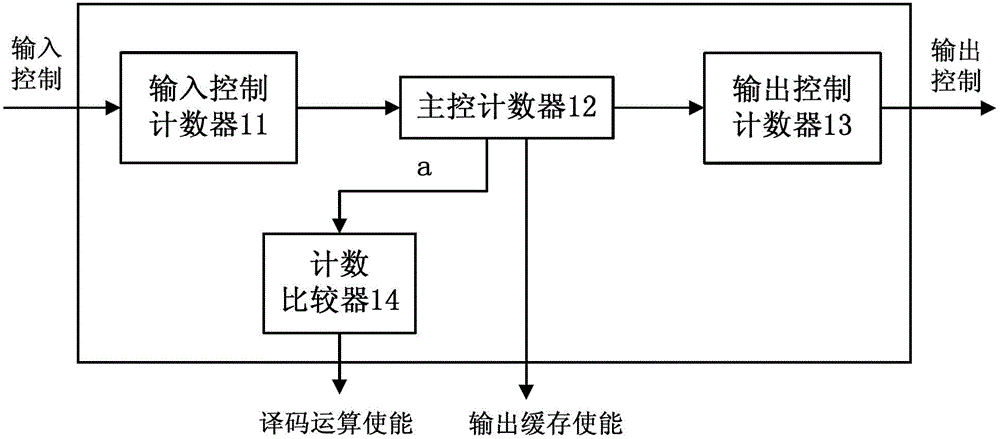

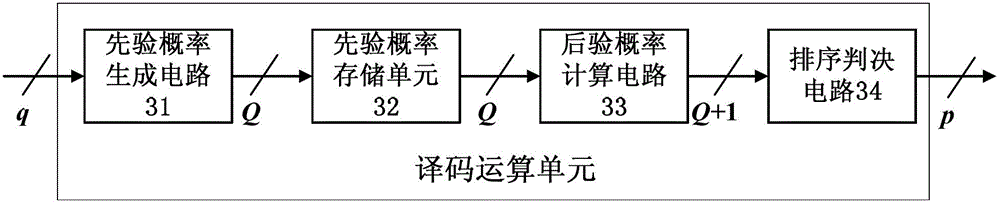

Short code length block code decoder device based on two finite group symbols

InactiveCN102751994AEase of hardware implementationReduce complexityError correction/detection using multiple parity bitsBlock codeLow complexity

The invention discloses a short code length block code decoder device based on two finite group symbols, and belongs to the error control coding field of digital communications. The decoder device disclosed by the invention comprises a control circuit, an input buffer unit, an output buffer unit and a decoding calculation unit, wherein the decoding calculation unit is the core part of the decoder and comprises a prior probability generation circuit, a prior probability storage unit, a posterior probability calculation circuit and a sequencing decision circuit which are connected in sequence. The prior probability generation circuit uses a plurality of basic units which are connected in sequence, has a regular structure, and is convenient for the circuit realization; the prior probability storage unit realizes data interleaving through a read-write address and is relatively low in complexity; and both the posterior probability calculation circuit and the sequencing decision circuit use a realizing method which is relatively low in complexity. In conclusion, the short code length block code decoder device based on two finite group symbols is realized, the complexity of the hardware is relatively low, and the performance is good.

Owner:TIANJIN UNIV

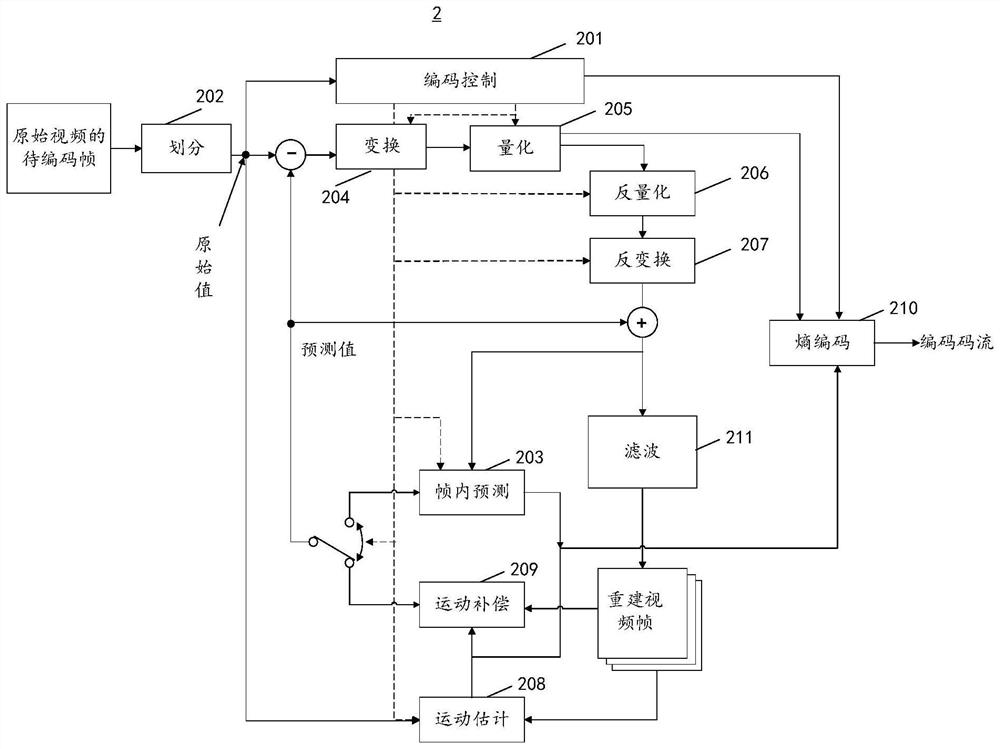

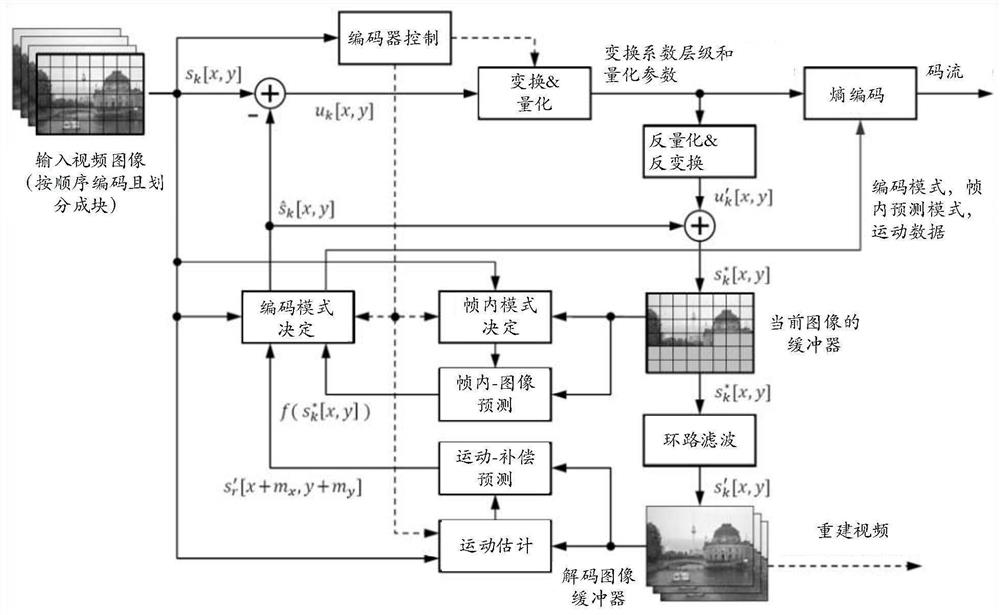

Video encoding method and apparatus

ActiveCN112514390AGuaranteed coding qualitySimplify Design ComplexityDigital video signal modificationPattern recognitionComputer graphics (images)

The invention provides a video encoding method and apparatus, comprising: receiving, with a first processor, first encoding parameter information and first reconstructed pixels of a first boundary image block in an image to be encoded, the first boundary image block being encoded by a second processor; receiving, by the first processor, second encoding parameter information and second reconstructed pixels of a second boundary image block in the image to be encoded, the second boundary image block being encoded by a third processor, the image to be encoded comprising a first image and a secondimage adjacent to each other, wherein the first boundary image block is a boundary image block in the first image, the second boundary image block is a boundary image block in the second image, and the second boundary image block is adjacent to the first boundary image block; and filtering, using the first processor, adjacent boundaries between the first image and the second image based on the first encoding parameter information, the second encoding parameter information, the first reconstructed pixel and the second reconstructed pixel.

Owner:SZ DJI TECH CO LTD

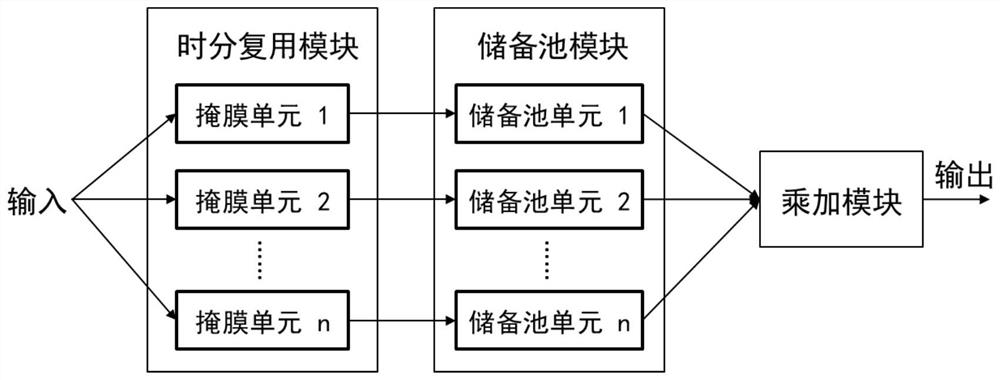

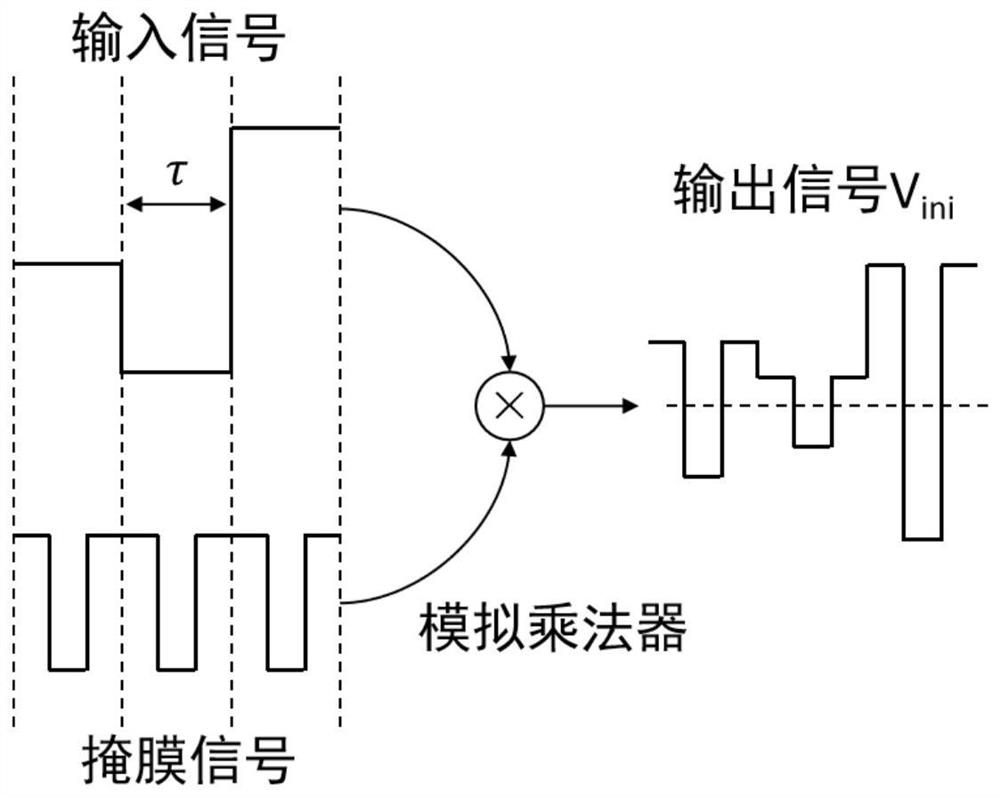

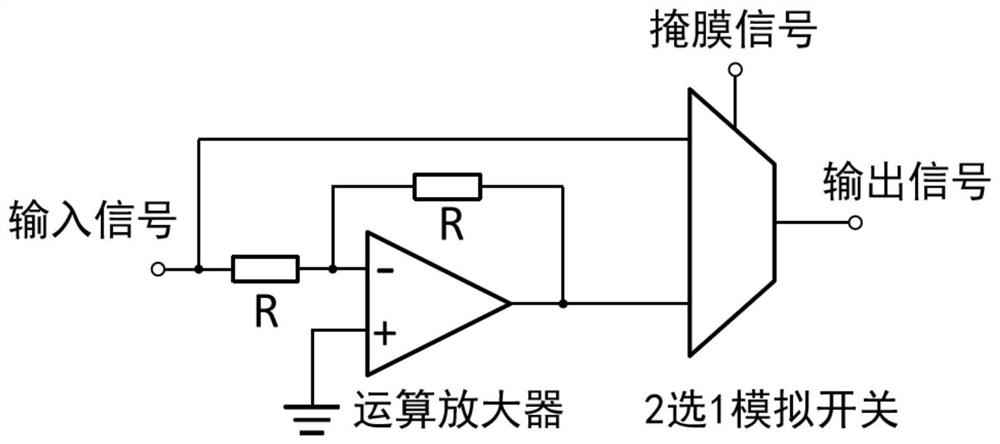

Reserve pool computing system based on dynamic memristor

InactiveCN112488308AImprove performanceImprove operational efficiencyPhysical realisationCarrier signalTime-division multiplexing

The invention provides a reservoir calculation system based on a dynamic memristor, and the system comprises a time division multiplexing module which comprises a plurality of parallel mask units, andmodulates the amplitude of an input signal according to different mask signals through employing each mask signal as a carrier wave, and obtains a plurality of voltage signals with different amplitudes; a reserve pool module which comprises a plurality of reserve pool units, each reserve pool unit comprises a dynamic memristor and a load resistor which are connected with each other, the dynamic memristors are used for carrying out nonlinear transformation on the voltage signals from the mask units to obtain current signals, and the load resistors are used for converting the current signals into voltage signals and then outputting the voltage signals; and a multiply-add module which adopts a non-volatile memristor array, multiply-add operation is carried out on the plurality of voltage signals from the storage battery module and the conductance values of the non-volatile memristors to obtain a plurality of corresponding current signals, then the current signals are output, and the conductance values of the non-volatile memristors correspond to the weight values output by the storage battery system. The working efficiency of the reserve battery system is improved, and the power consumption is reduced.

Owner:TSINGHUA UNIV

High Dynamic Range 3D Measurement Method Based on Spectral Modulation and Multispectral Imaging

ActiveCN109916336BAvoid multiple shotsConvenient 3D measurementUsing optical meansObject basedThree dimensional shape

Owner:武汉斌果科技有限公司

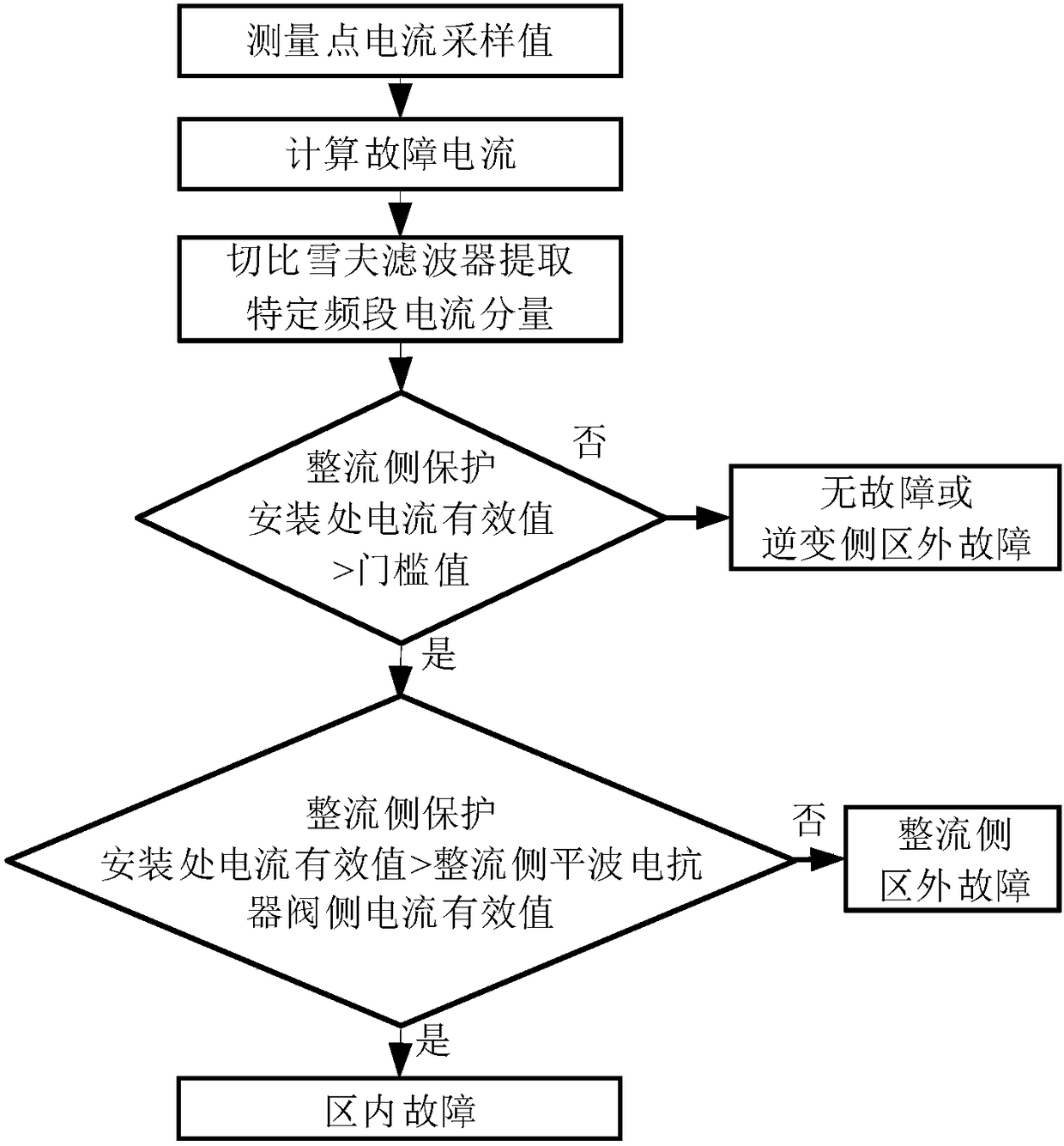

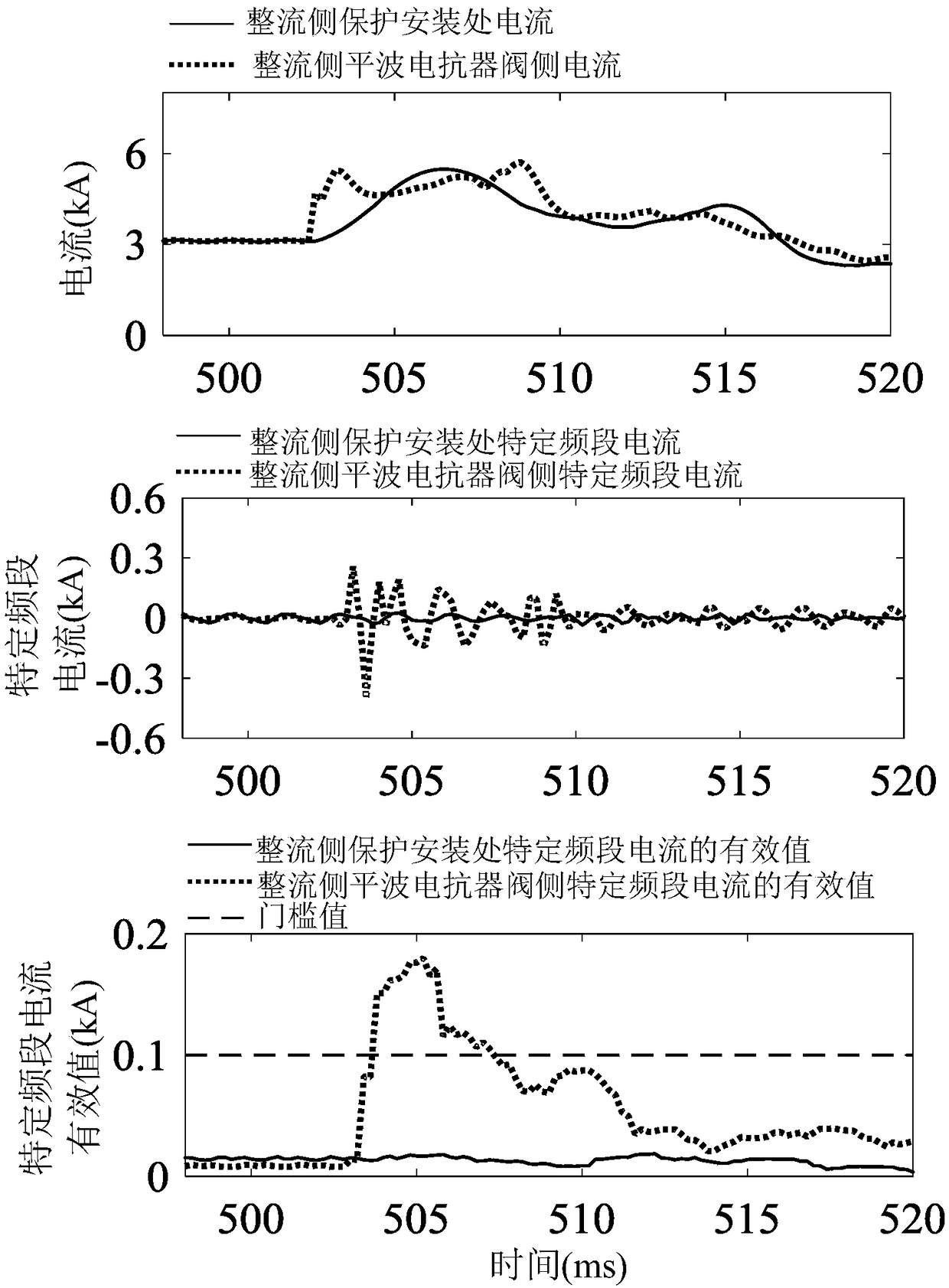

Ultrahigh-voltage DC line protection method based on specific frequency band current

ActiveCN108321776ALow sampling rate requirementsEase of hardware implementationEmergency protective circuit arrangementsFrequency bandVoltage

The invention relates to an ultrahigh-voltage DC line protection method based on specific frequency band current, which comprises the steps of firstly extracting real-time current values measured by current dividers at a rectification-side protection installation part and a rectification-side smoothing reactor valve side; calculating fault current of the protection installation part and the smoothing reactor valve side, namely, the difference between the real-time current and steady-state current of an ultrahigh-voltage DC system in normal operation; extracting a specific frequency band current component of the fault current by a filter; performing comparative judgment on a specific frequency band current effective value at the rectification-side protection installation part, a specific frequency band current effective value at the rectification-side smoothing reactor valve side and a protection threshold to obtain whether the DC line has a fault or not; and then obtaining the type ofthe fault. According to the invention, fault judgment is performed by only using the single-end specific frequency band current, data synchronization is not required to be performed, requirements forthe sampling rate is low, and various DC line faults can be recognized quickly and accurately.

Owner:SHANGHAI JIAO TONG UNIV

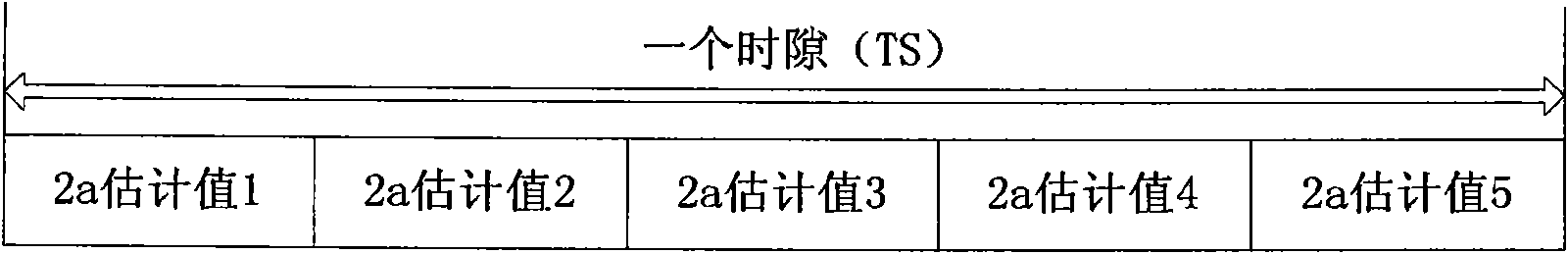

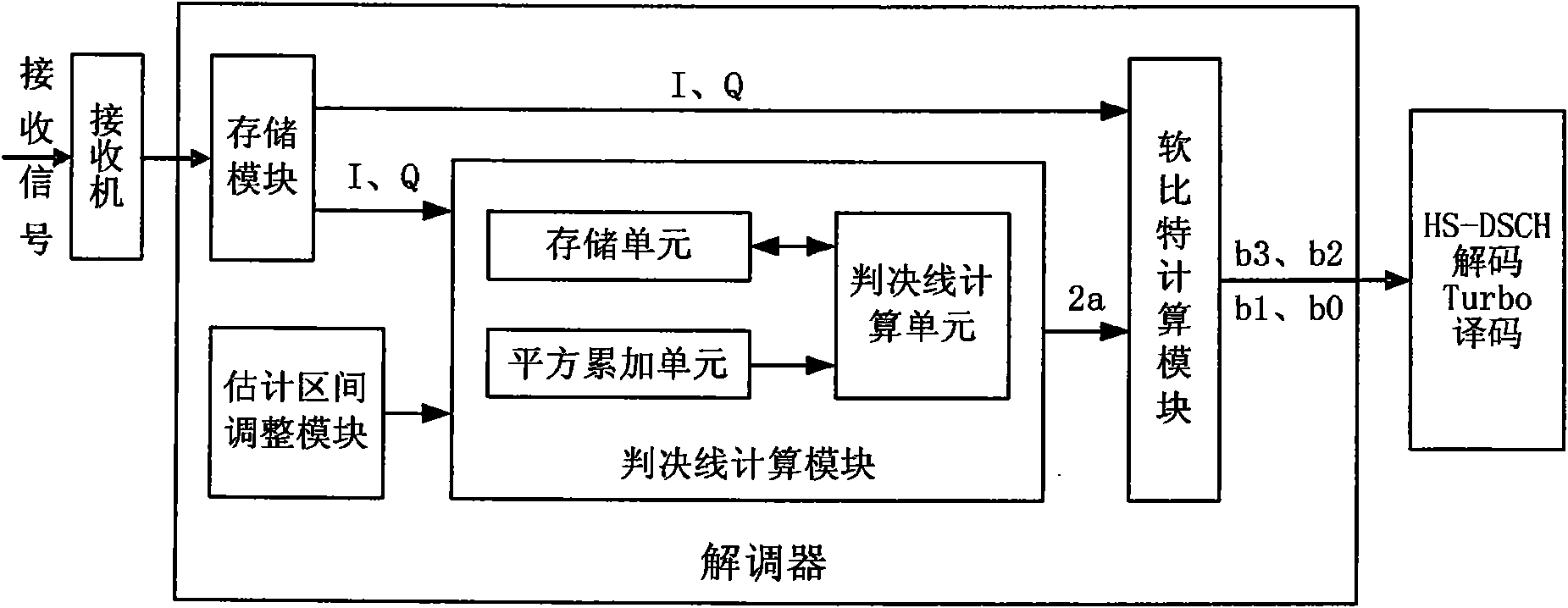

Demodulator and demodulating method for high-speed data packet access system

ActiveCN101626361AImprove demodulation performanceEase of hardware implementationMultiple carrier systemsMulti codeDemodulation

Owner:SANECHIPS TECH CO LTD

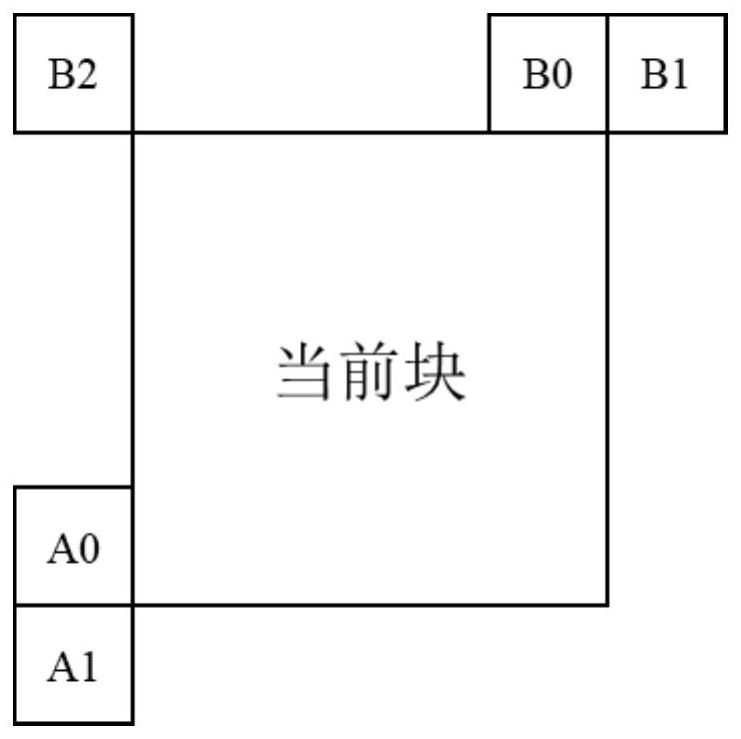

Video encoding method, video decoding method and related equipment

ActiveCN112532988AEasy to implementEase of hardware implementationDigital video signal modificationCoding blockVideo encoding

The invention provides a video encoding method, a video decoding method and related equipment. The video encoding method comprises the steps of: acquiring a current image, wherein the current image comprises a maximum coding unit, the maximum coding unit comprises a current maximum coding unit and a coded maximum coding unit, the current maximum coding unit comprises a current coding block, and the current coding block comprises a current string; storing pixels in the current coding block by using a first part of a storage space with the size of M*W, and storing at least part of coded blocks in the coded maximum coding unit and the current maximum coding unit by using a second part of the storage space, wherein M is a positive integer greater than or equal to W; and searching a reference string of the current string in the second part to obtain a predicted value of the current string according to the reference string, and encoding the current string.

Owner:TENCENT TECH (SHENZHEN) CO LTD