NAND Flash-based data recording method and recording controller

A data recording and controller technology, applied in the direction of input/output to record carrier, memory address/allocation/relocation, etc., can solve problems such as rewriting, writing bandwidth is difficult to continue to improve, and heat generation is large

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

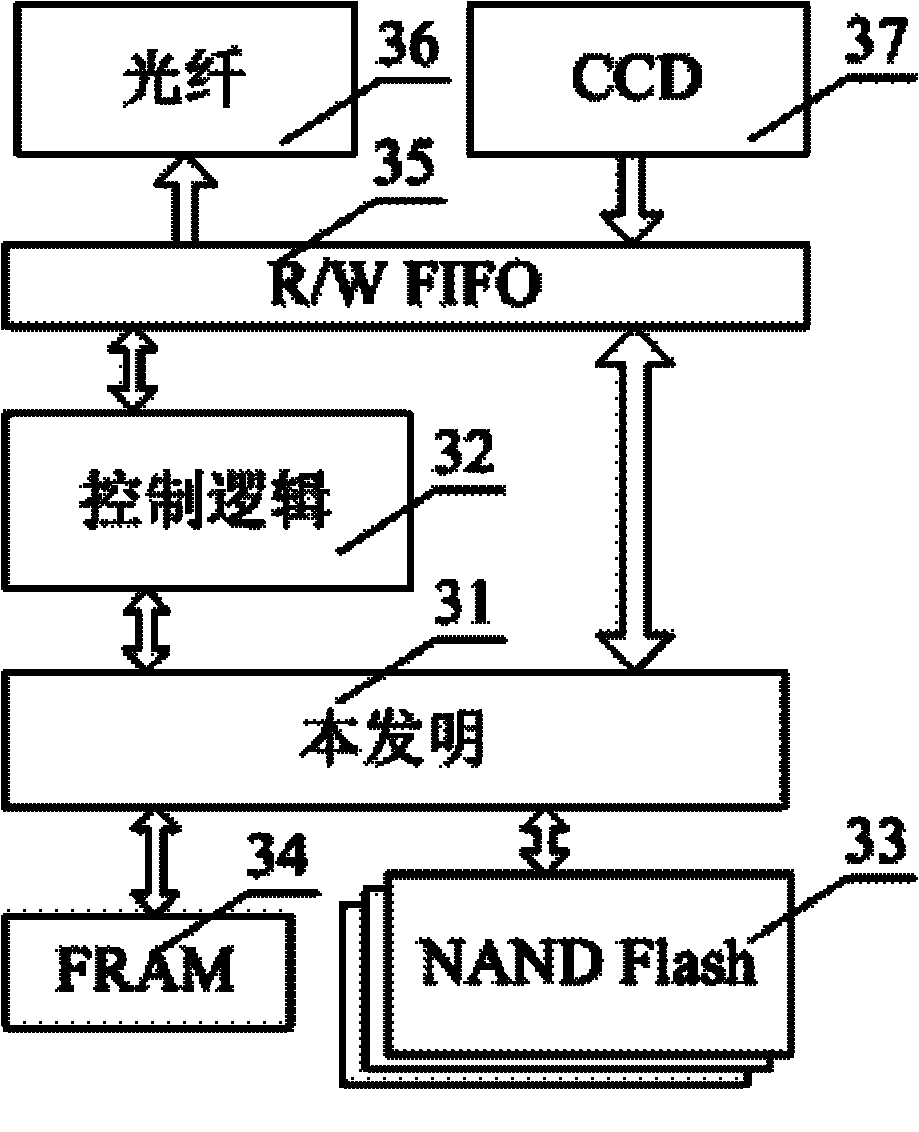

[0158] This example takes a non-embedded application as an example. The image data of the CCD camera is recorded in the NAND Flash array, and the recorded data is read out through the optical fiber interface, and then the erase operation is performed. The technical scenario is: the system connects 42 Samsung K9WBG08U1MSLC NAND flash chips in parallel, each 4GB, including 16384 blocks, each block has 64 pages, and each page (4K+128)B. The total system capacity is 168GB, the reserved capacity for bad block management is 8GB, and the effective image storage capacity of the system is 160GB. The FRAM uses Ramtron's FM20L08 ferroelectric memory with a capacity of 128KB. FPGA adopts Xilinx VIRTEX-5 XC5VFX70T chip. The image comes from a Pantera SA 2M30 high-definition CCD camera with a frame rate of 120frame / s, a resolution of 1600×1200pixels, and a grayscale of 10bits. Peripheral modules in the example are designed with Verilog hardware language.

[0159] Attached below image 3...

Embodiment 2

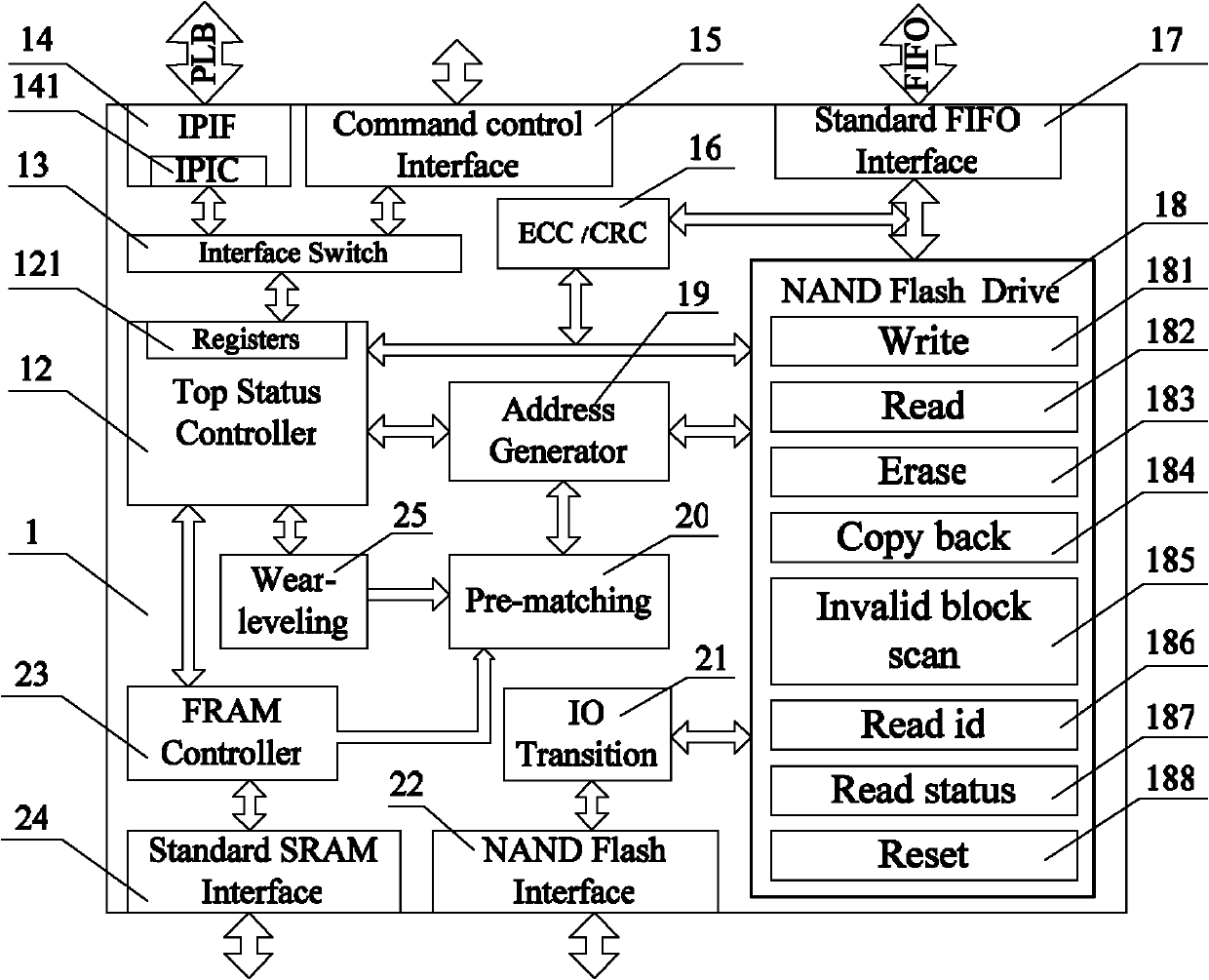

[0187] In this embodiment, the present invention is applied in an embedded design to record the image data of a CCD camera in a NAND Flash array, and read out the recorded data through a Gigabit network. The technical scenario is: the system uses 42 Samsung K9WBG08U1M SLCNAND flash chips connected in parallel, each 4GB, including 16384 blocks, each block 64 pages, each page (4K+128)B. The total system capacity is 168GB, the reserved capacity for bad block management is 8GB, and the effective image storage capacity of the system is 160GB. The FRAM uses Ramtron's FM20L08 ferroelectric memory with a capacity of 128KB. The image comes from a Pantera SA 2M30 high-definition CCD camera with a frame rate of 120frame / s, a resolution of 1600×1200pixels, and a grayscale of 10bits. FPGA adopts XilinxVIRTEX-5XC5VFX70T chip. The embedded CPU adopts the PPC440 hard core 1,01A version in the FPGA, the working frequency is 400MHz, and the PLB bus working frequency is 100MHz. The memory con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More