Patents

Literature

163results about How to "Improve parallel processing capabilities" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

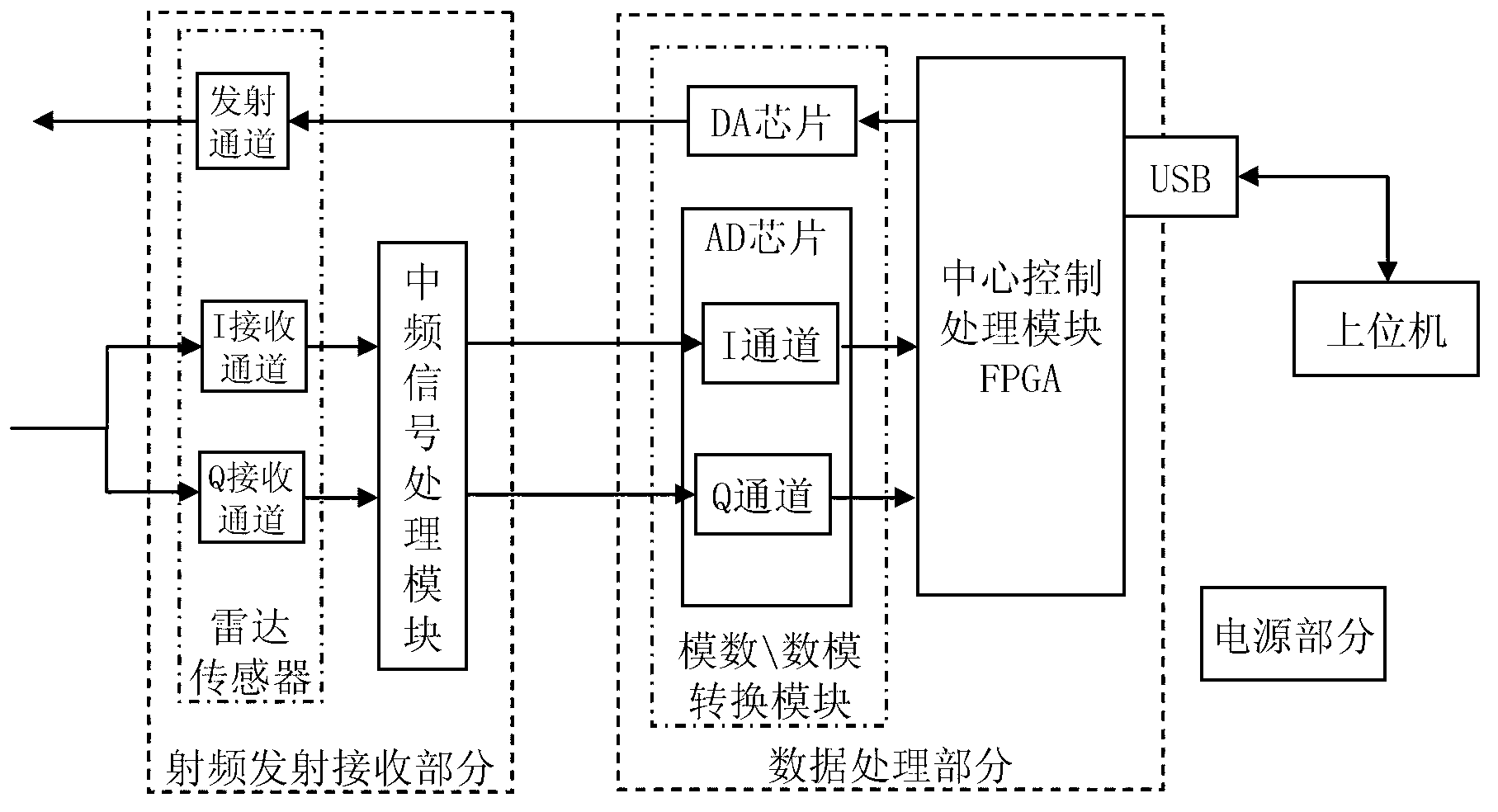

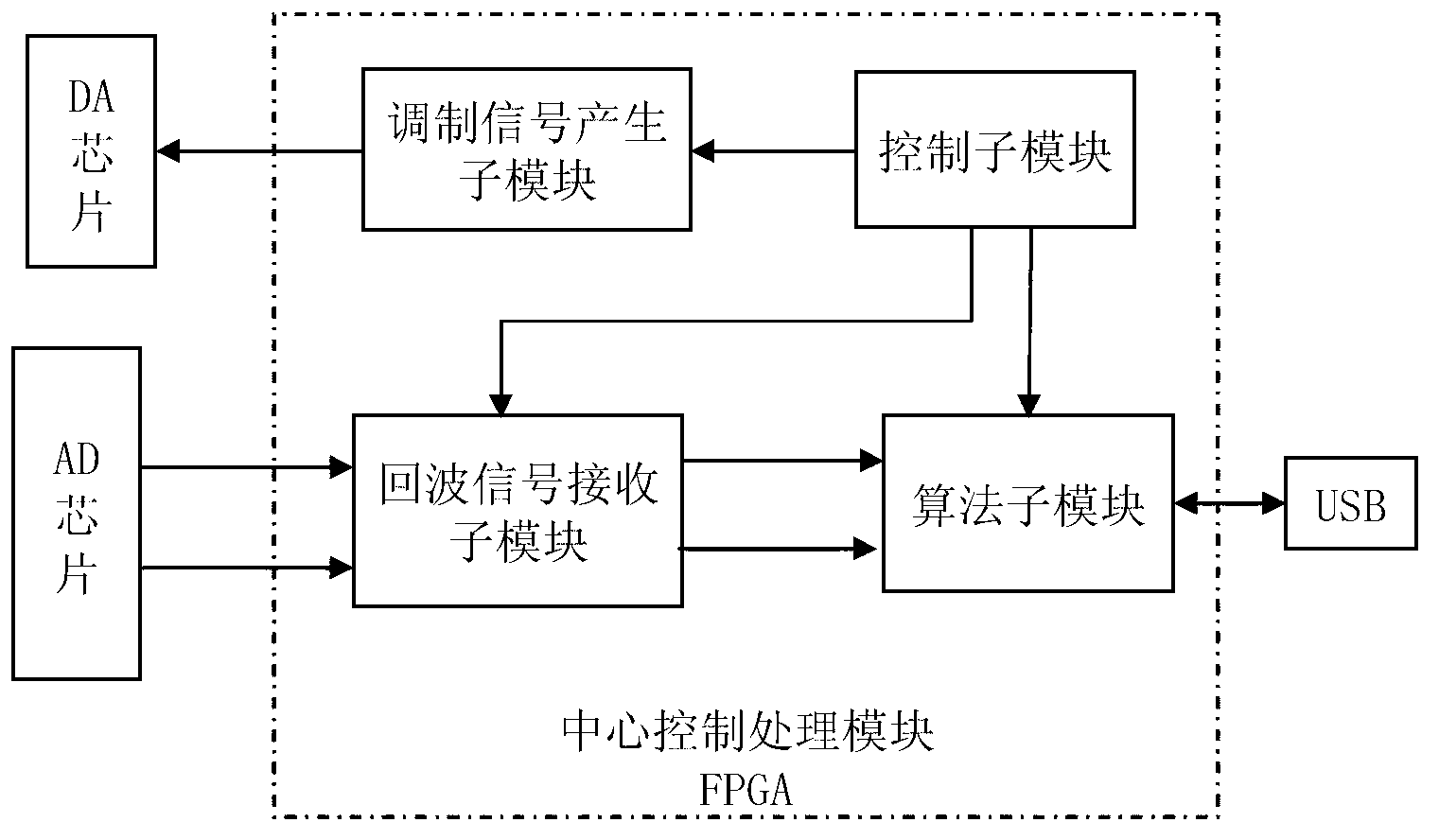

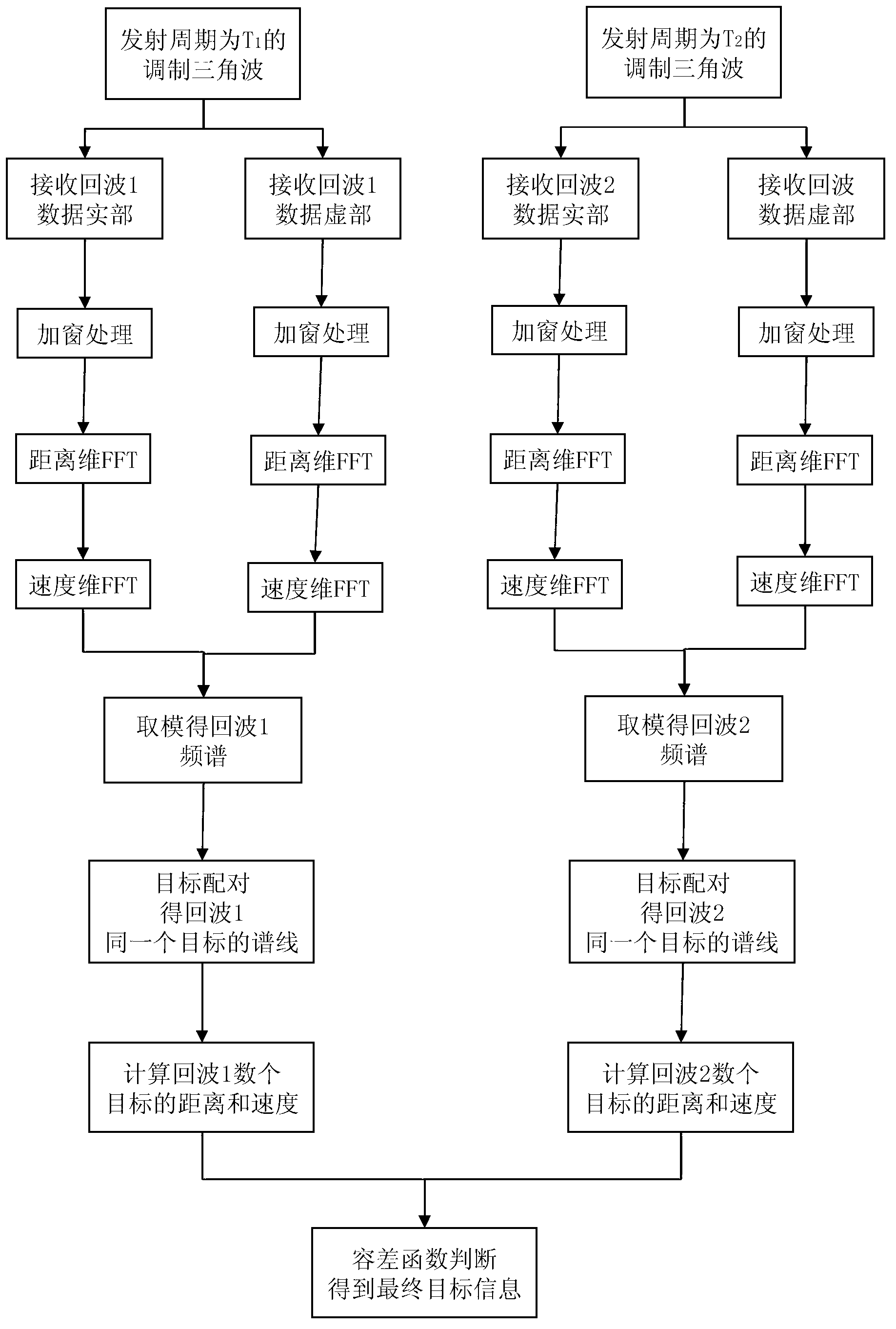

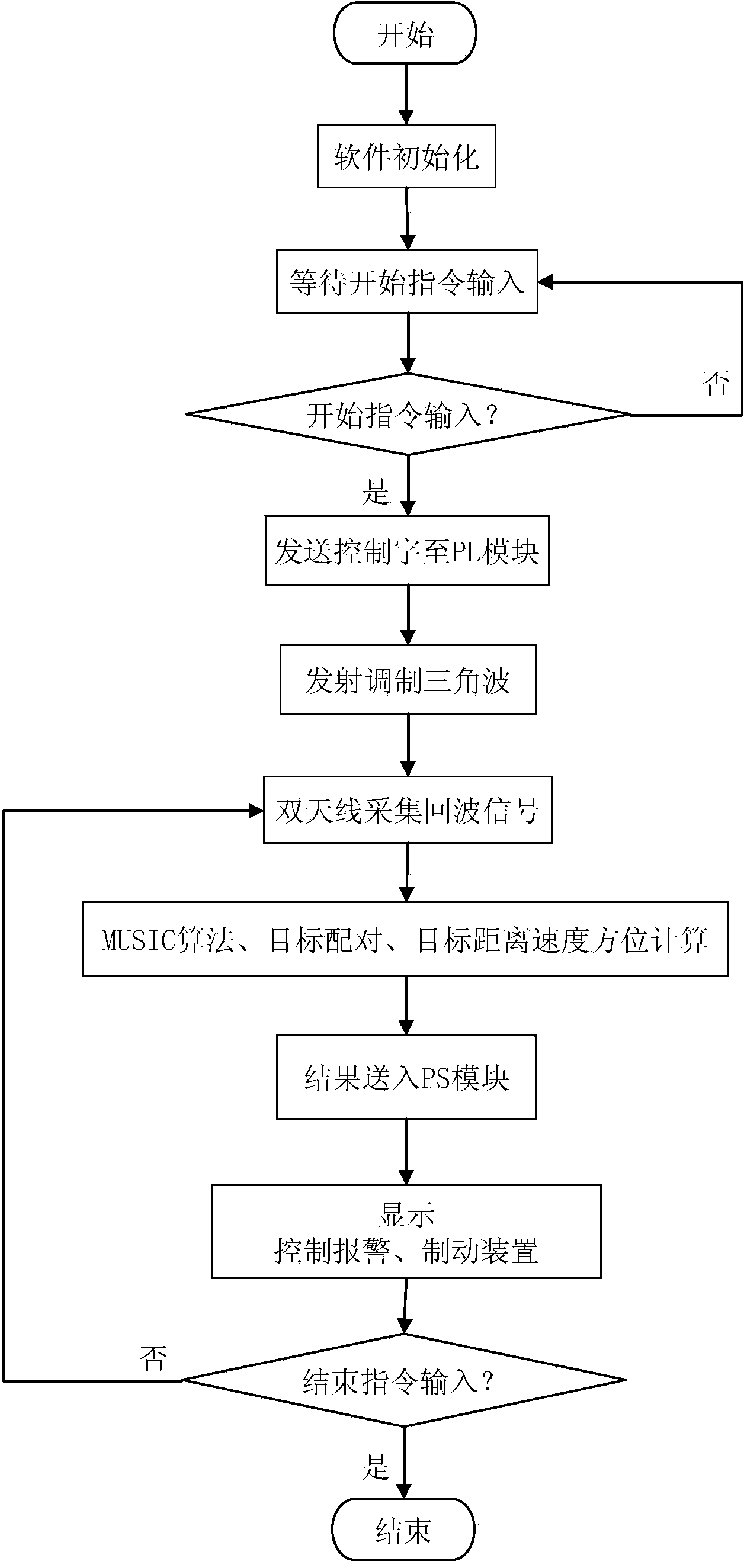

Automotive anti-collision radar multi-target detecting method and system

InactiveCN103257346AResolve echoResolve interferenceRadio wave reradiation/reflectionFrequency spectrumIntermediate frequency

Owner:GUILIN UNIV OF ELECTRONIC TECH

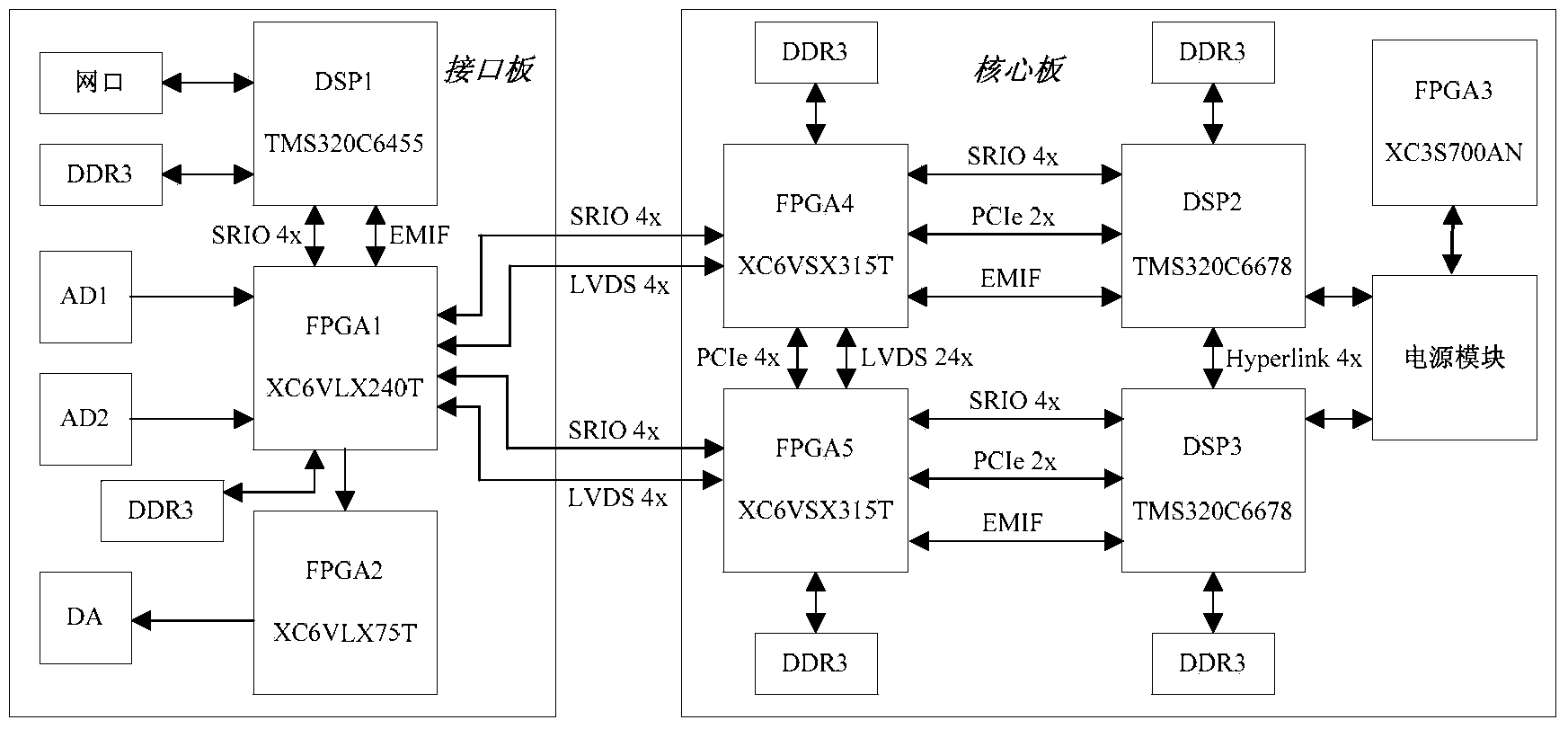

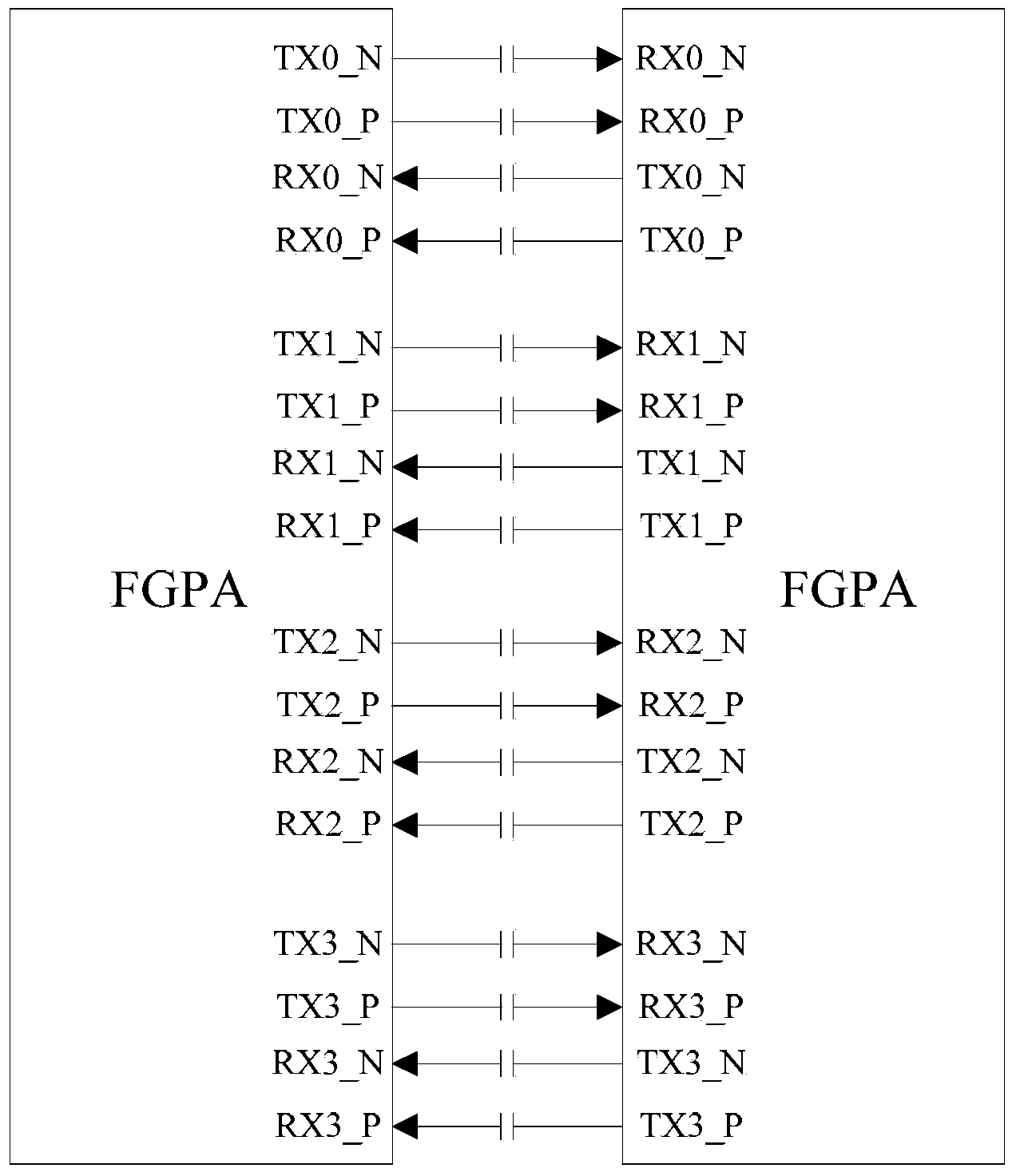

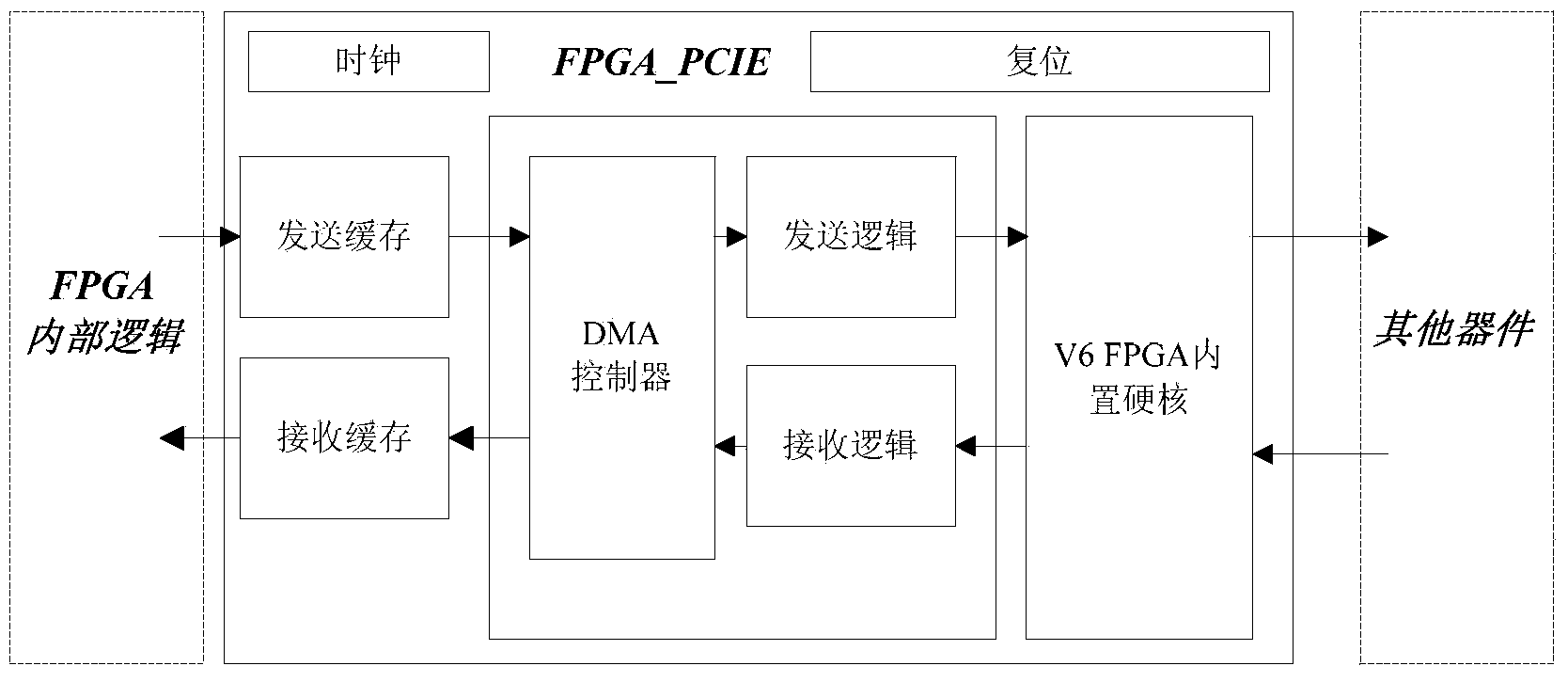

Multi-DSP and multi-FPGA parallel processing system and implement method

ActiveCN103885919AStrong interface capabilityImprove parallel processing capabilitiesElectric digital data processingHyperlinkExtensibility

The invention discloses a multi-DSP and multi-FPGA parallel processing system which comprises FPGAs, DSPs, ADs, a DA, DDR3s and power supply chips. An implement method of the multi-DSP and multi-FPGA parallel processing system includes the following five steps: (1) achieving PCIe interconnection between the FPGAs, (2) achieving PCIe interconnection between the FPGAs and the DSPs, (3) achieving SRIO interconnection between the FPGAs, (4) achieving SRIO interconnection between the FPGAs and the DSPs, and (5) achieving Hyperlink interconnection between the DSPs. The multi-DSP and multi-FPGA parallel processing system is high in parallel processing capacity, abundant in function and high in flexibility and extensibility, data transmission bottlenecks between processor chips are broken, and the multi-DSP and multi-FPGA parallel processing system is high in transportability and have the good practical value in the digital signal processing field.

Owner:杭州雷世科技有限公司

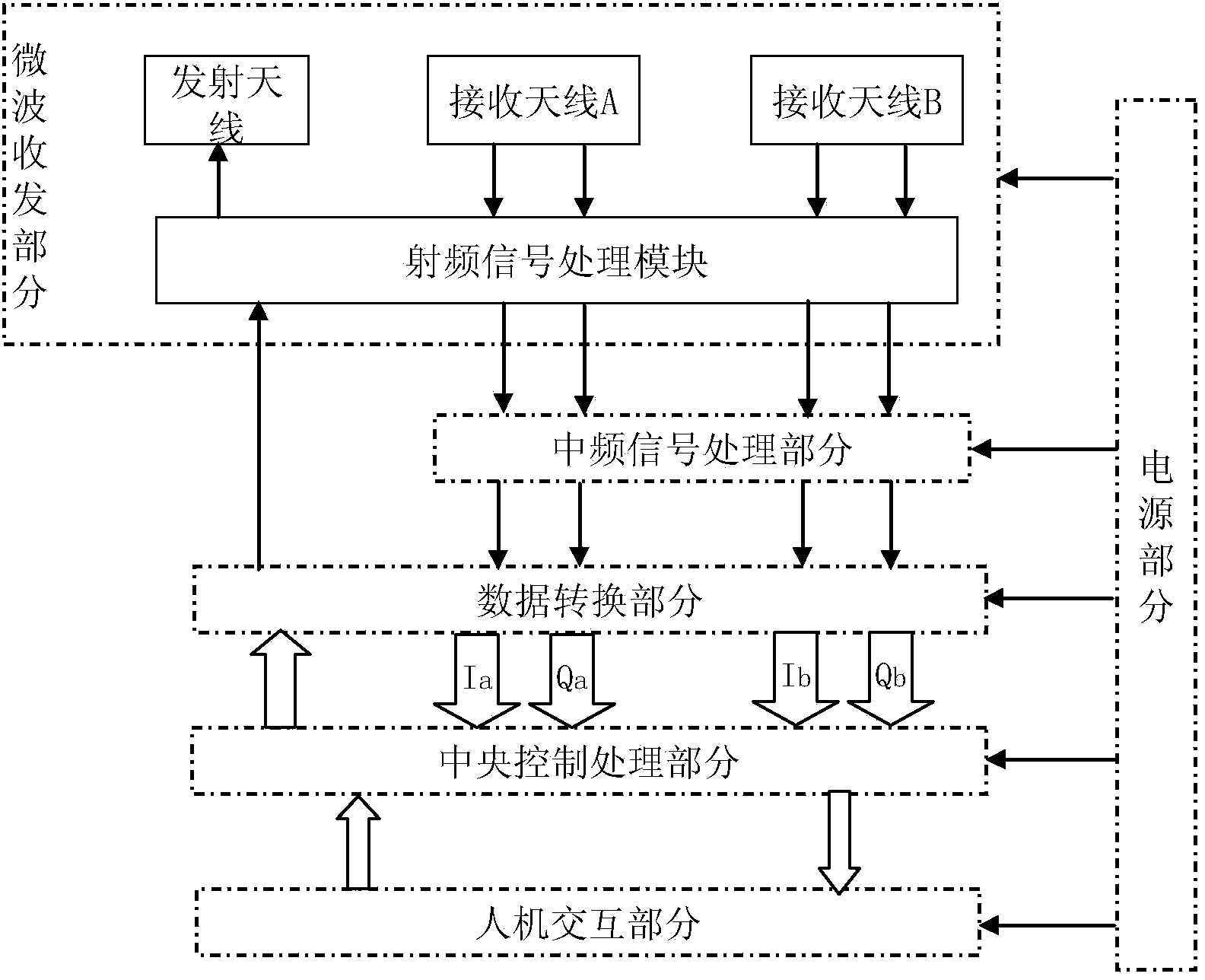

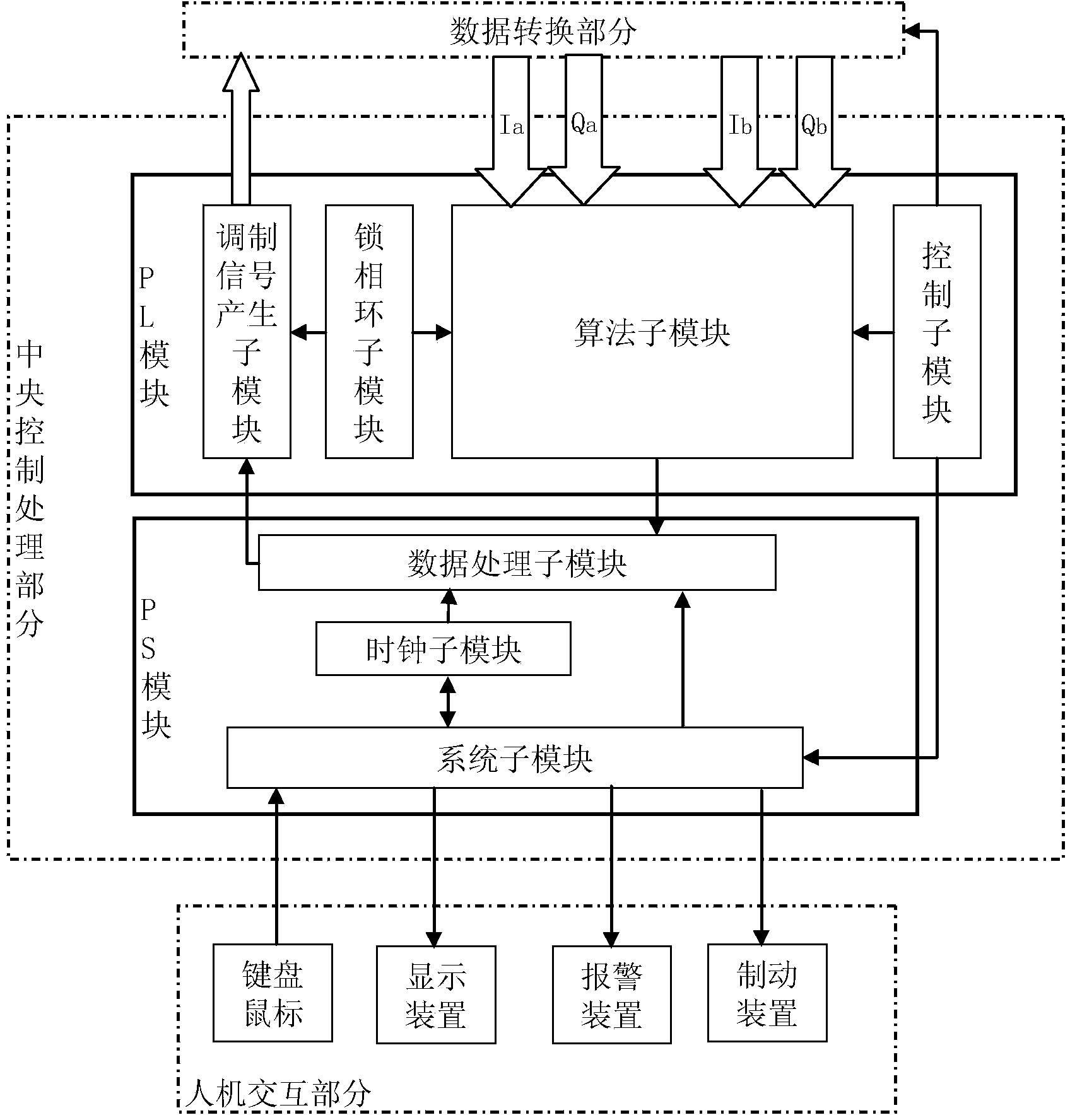

Automotive anti-collision radar system with two receiving antennas and operating method

ActiveCN103913742AProcessing speedImprove multi-target judgment abilityRadio wave reradiation/reflectionEcho signalData processing

Owner:GUILIN UNIV OF ELECTRONIC TECH

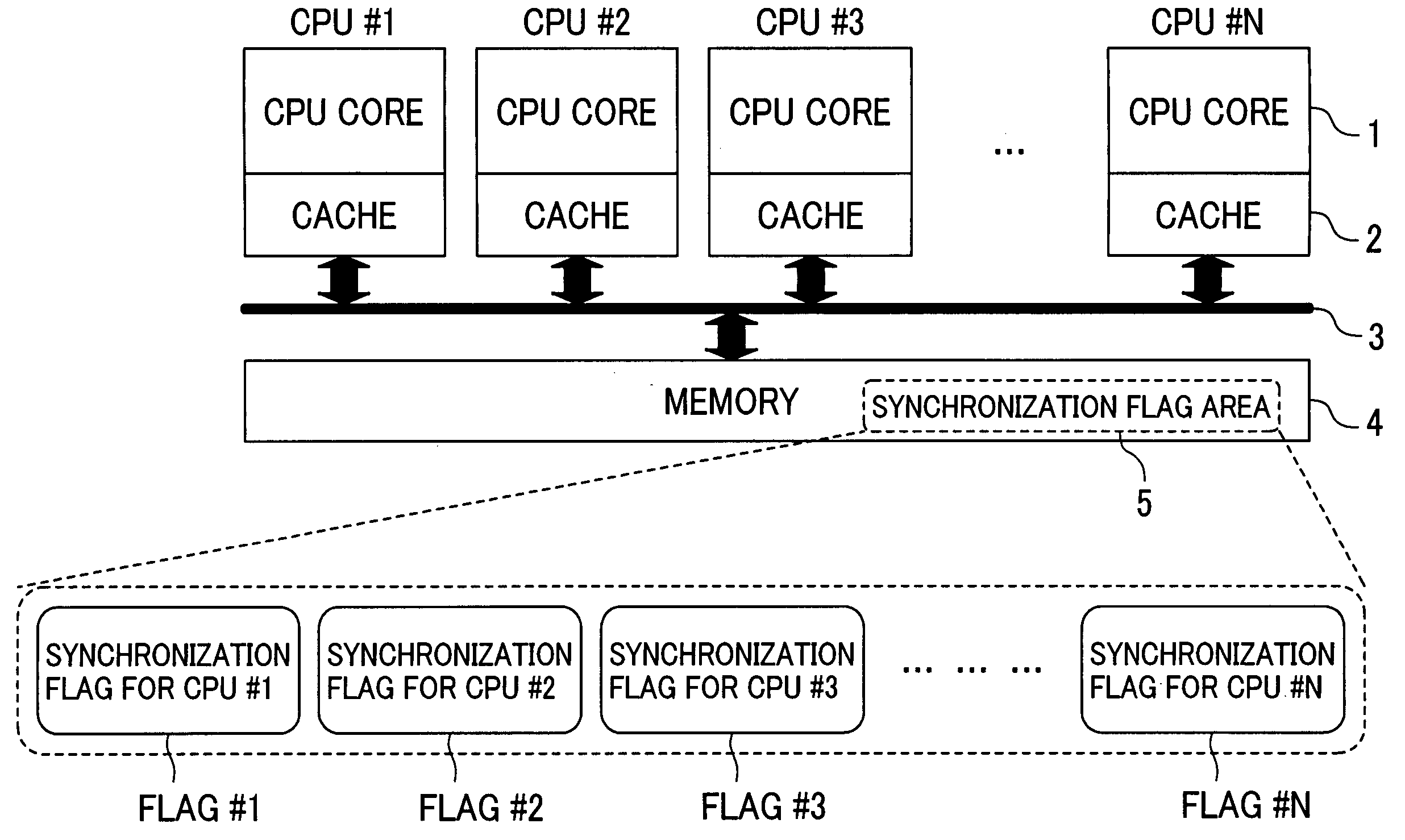

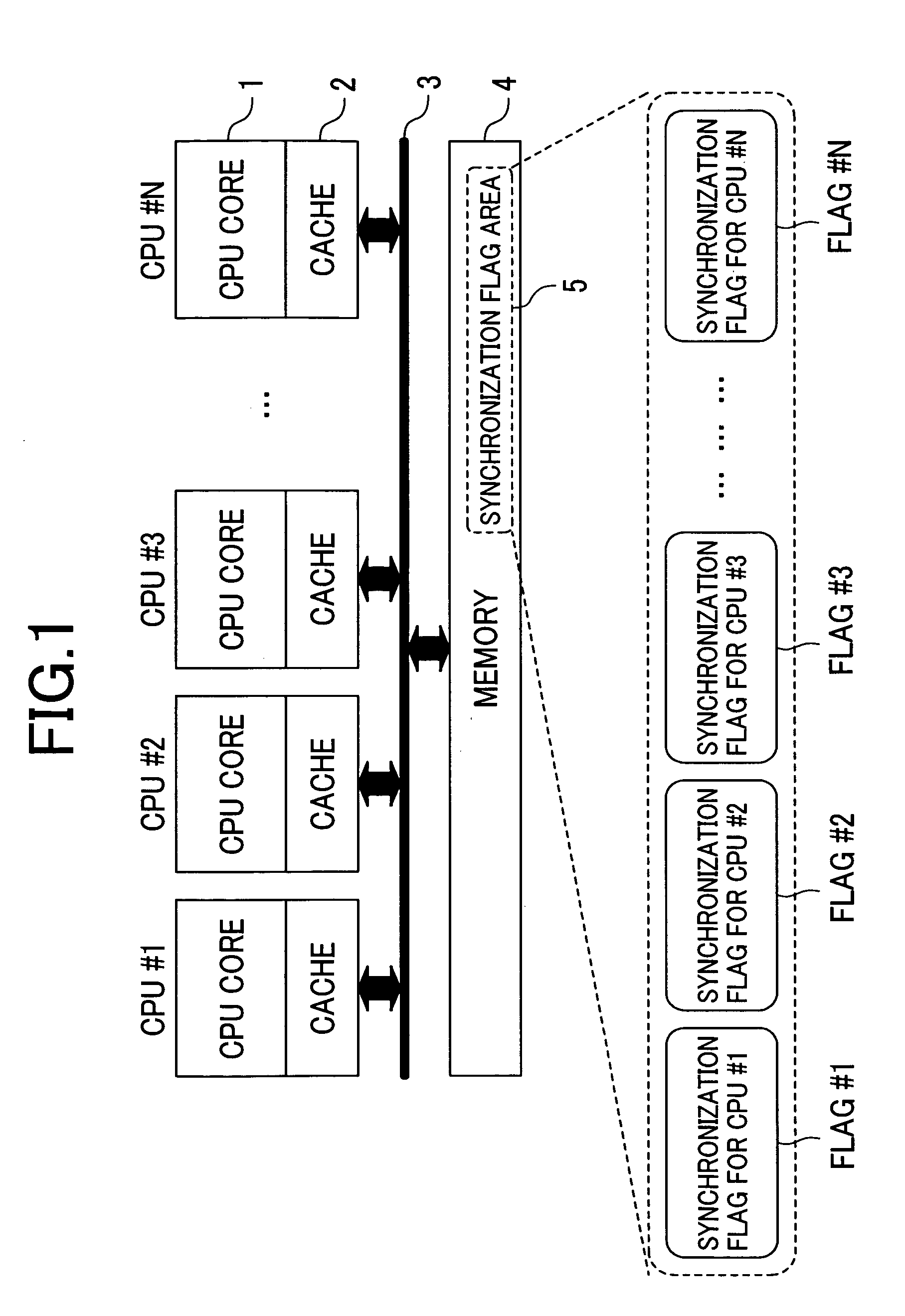

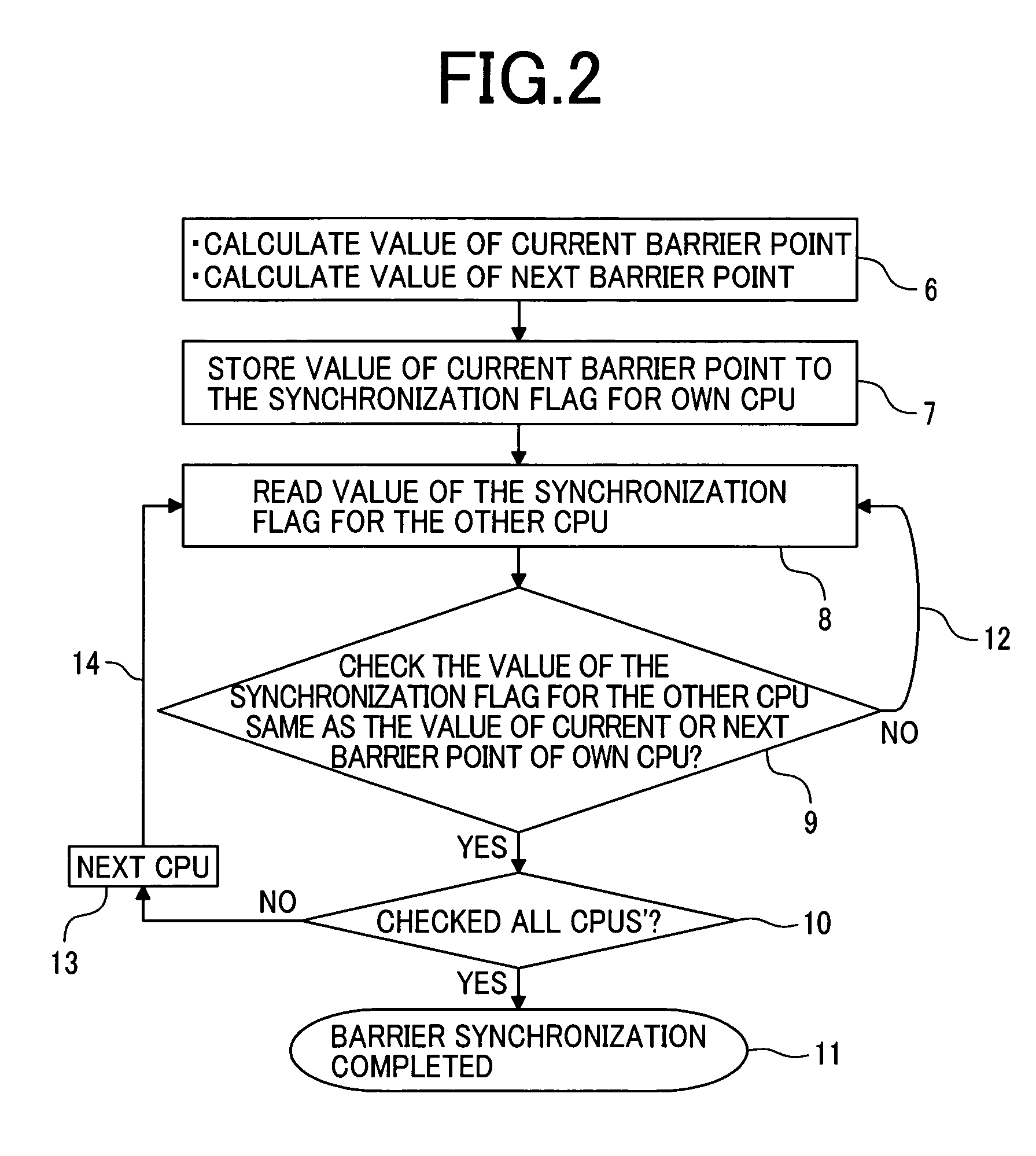

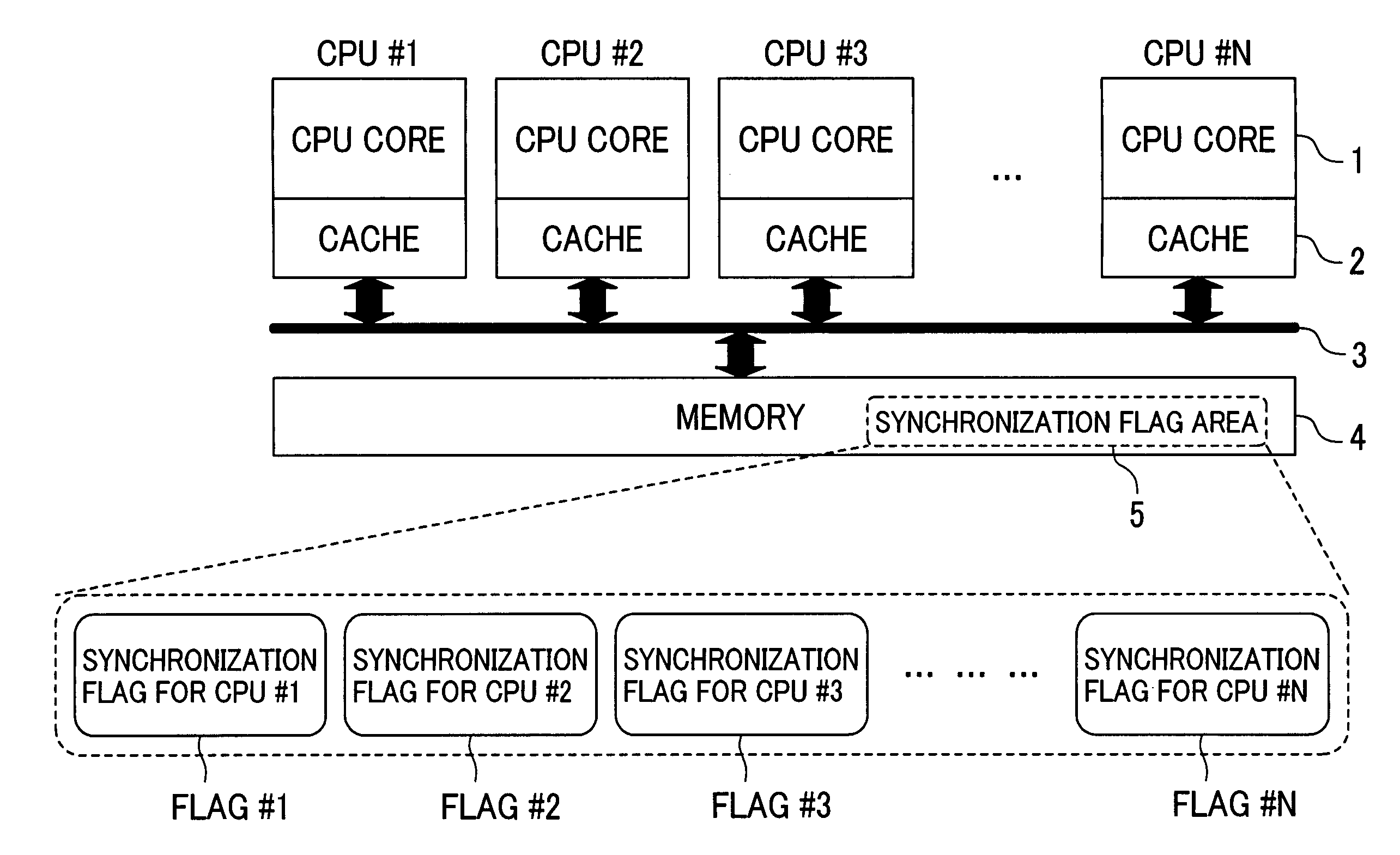

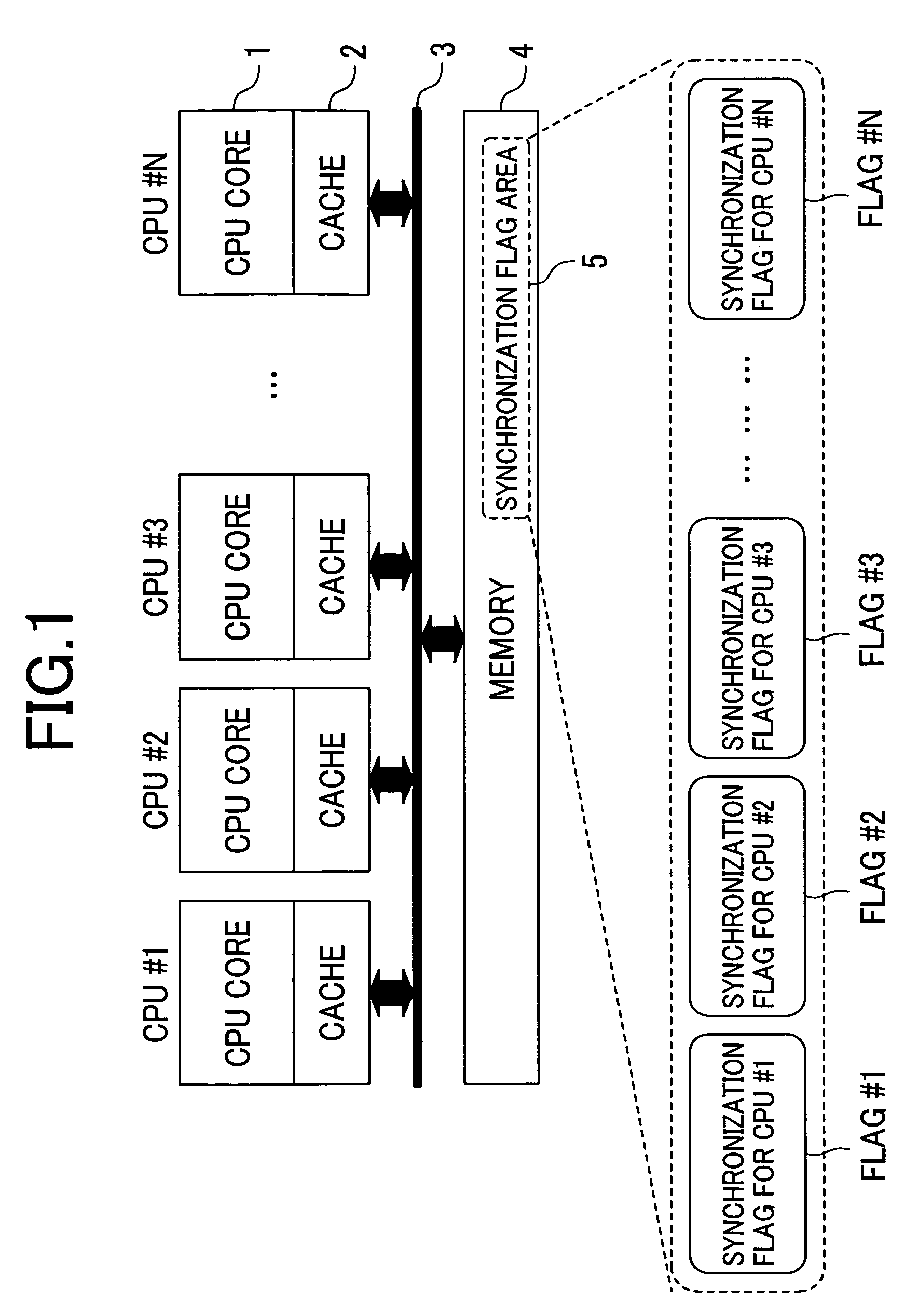

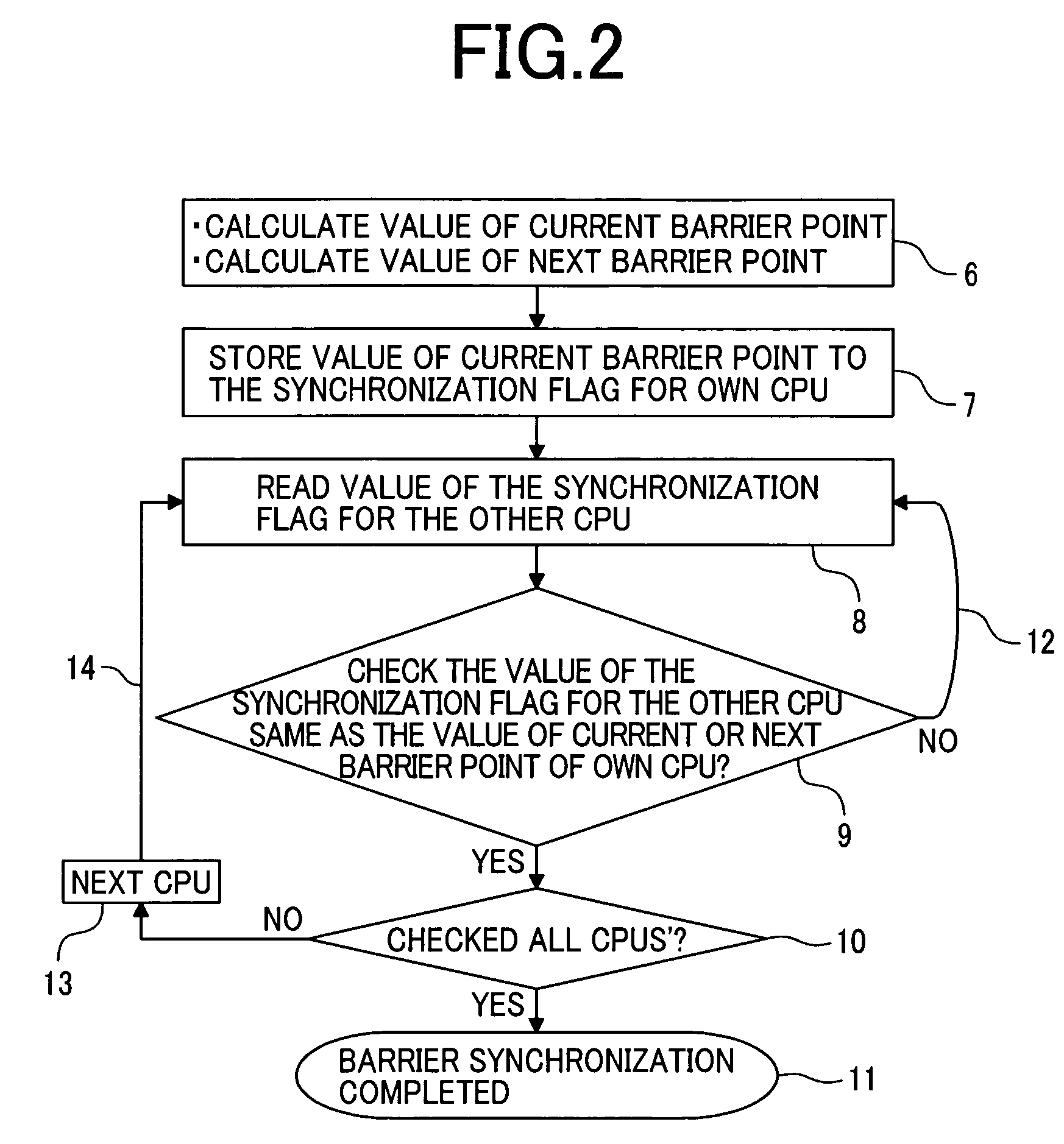

Method for synchronizing processors in a multiprocessor system

InactiveUS20050050374A1Improve parallel processing capabilitiesProgram synchronisationMemory adressing/allocation/relocationMulti processorSoftware update

The high-speed barrier synchronization is completed among multiprocessors by saving overhead for parallel process without addition of a particular hardware mechanism. That is, the barrier synchronization process is performed by allocating the synchronization flag area, on the shared memory, indicating the synchronization point where the execution of each processor for completing the barrier synchronization is completed, updating the synchronization flag area with the software in accordance with the executing condition, and comparing, with each processor, the synchronization flag area of the other processors which takes part in the barrier synchronization.

Owner:HITACHI LTD

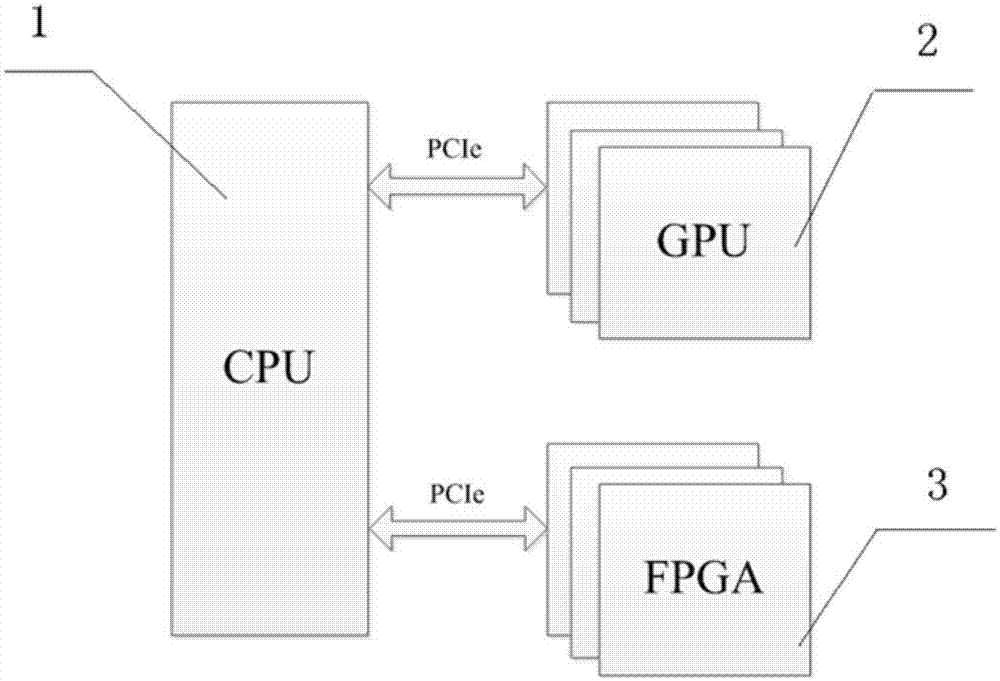

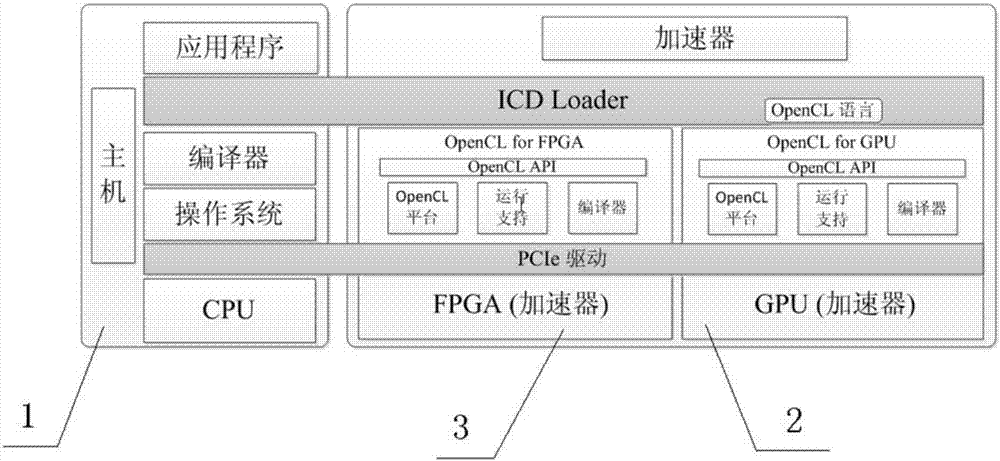

Heterogeneous computing system and method based on CPU+GPU+FPGA architecture

InactiveCN107273331AGive full play to the advantages of management and controlTake full advantage of parallel processingArchitecture with single central processing unitEnergy efficient computingFpga architectureResource management

The invention provides a heterogeneous computing system based on CPU+GPU+FPGA architecture. The system comprises a CPU host unit, one or more GPU heterogeneous acceleration units and one or more FPGA heterogeneous acceleration units. The CPU host unit is in communication connection with the GPU heterogeneous acceleration units and the FPGA heterogeneous acceleration units. The CPU host unit is used for managing resources and allocating processing tasks to the GPU heterogeneous acceleration units and / or the FPGA heterogeneous acceleration units. The GPU heterogeneous acceleration units are used for carrying out parallel processing on tasks from the CPU host unit. The FPGA heterogeneous acceleration units are used for carrying out serial or parallel processing on the tasks from the CPU host unit. According to the heterogeneous computing system provided by the invention, the control advantages of the CPU, the parallel processing advantages of the GPU, the performance and power consumption ratio and flexible configuration advantages of the FPGA can be exerted fully, the heterogeneous computing system can adapt to different application scenes and can satisfy different kinds of task demands. The invention also provides a heterogeneous computing method based on the CPU+GPU+FPGA architecture.

Owner:SHANDONG CHAOYUE DATA CONTROL ELECTRONICS CO LTD

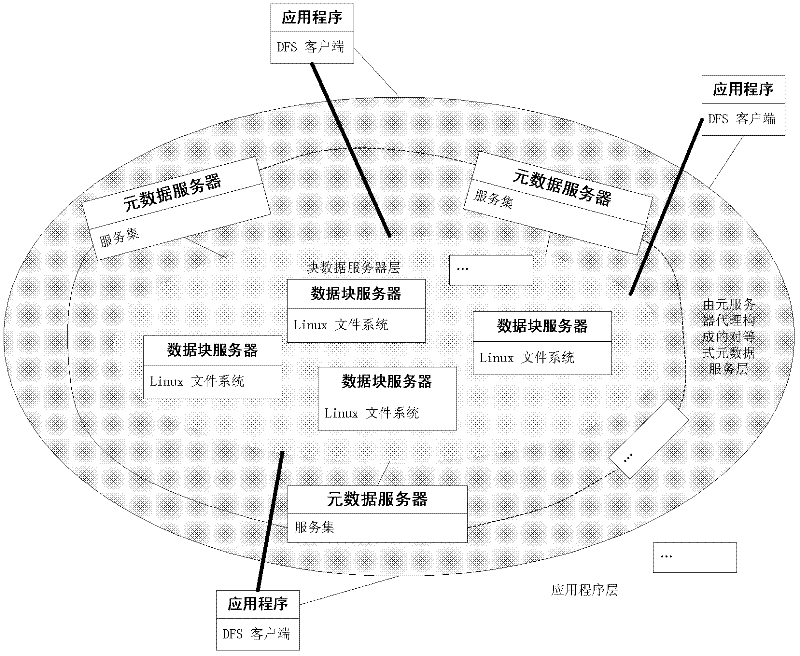

Distributed file system facing to cloud storage

InactiveCN102420854AImprove parallel processing performanceOvercoming high load problemsTransmissionSpecial data processing applicationsSingle pointMetadata service

The invention provides a distributed file system facing to cloud storage, mainly aiming at solving the problem that the existing cloud storage system is low in performance and reliability, high in load and invalid in a single point. The system comprises a block data service layer, a metadata service layer and an application client layer, wherein the metadata service layer replaces single metadata server in a global file system (GFS) by a plurality of agent servers, and forms into peer-to-peer type service network by adopting peer-to-peer P2P network configuration; the interaction among three layers of the system comprises the following steps: the application client layer requests to write to the metadata service layer, and the metadata service layer returns block data server information; and the client layer writes the file into the block data service layer and performs the redundancy backups according to a returned result, and the metadata service layer generates metadata according to a backups result and updates local metadata and a vector clock. Therefore, the performance and the business support capacity of the existing cloud storage system can be enhanced, and the system can be used for designing and optimizing the high-performance and high-reliability cloud storage system.

Owner:XIDIAN UNIV

Systems and methods for coalescing memory accesses of parallel threads

ActiveUS20090240895A1Improve efficiencyImprove parallel processing capabilitiesProgram controlMemory systemsMemory interfaceParallel computing

One embodiment of the present invention sets forth a technique for efficiently and flexibly performing coalesced memory accesses for a thread group. For each read application request that services a thread group, the core interface generates one pending request table (PRT) entry and one or more memory access requests. The core interface determines the number of memory access requests and the size of each memory access request based on the spread of the memory access addresses in the application request. Each memory access request specifies the particular threads that the memory access request services. The PRT entry tracks the number of pending memory access requests. As the memory interface completes each memory access request, the core interface uses information in the memory access request and the corresponding PRT entry to route the returned data. When all the memory access requests associated with a particular PRT entry are complete, the core interface satisfies the corresponding application request and frees the PRT entry.

Owner:NVIDIA CORP

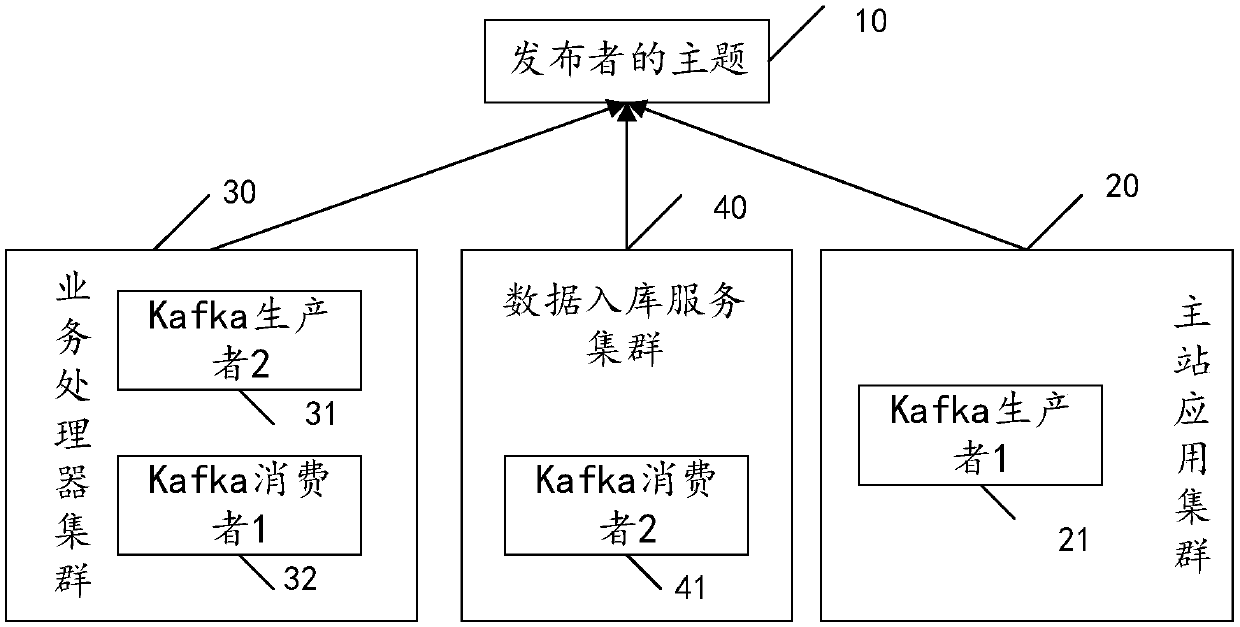

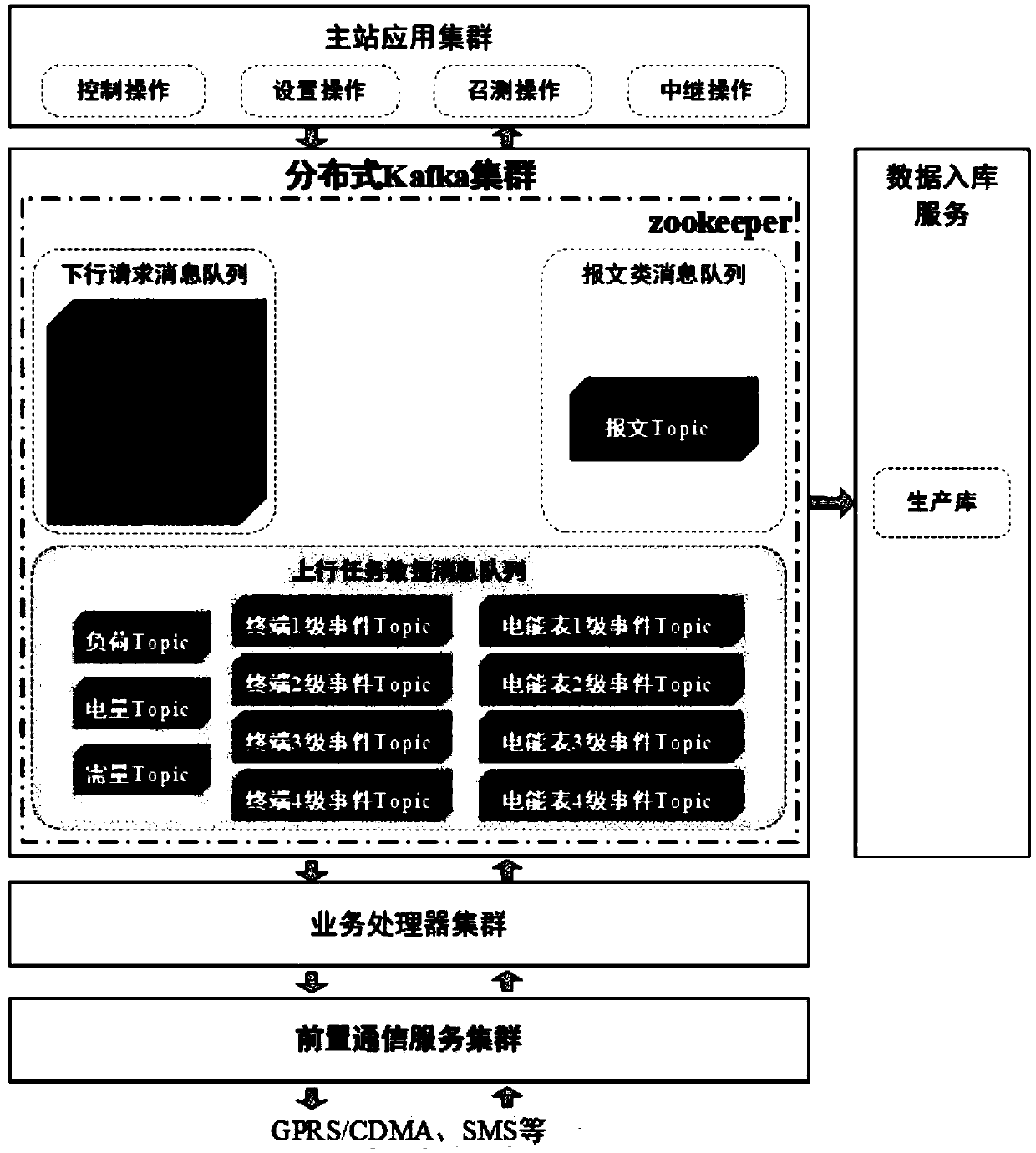

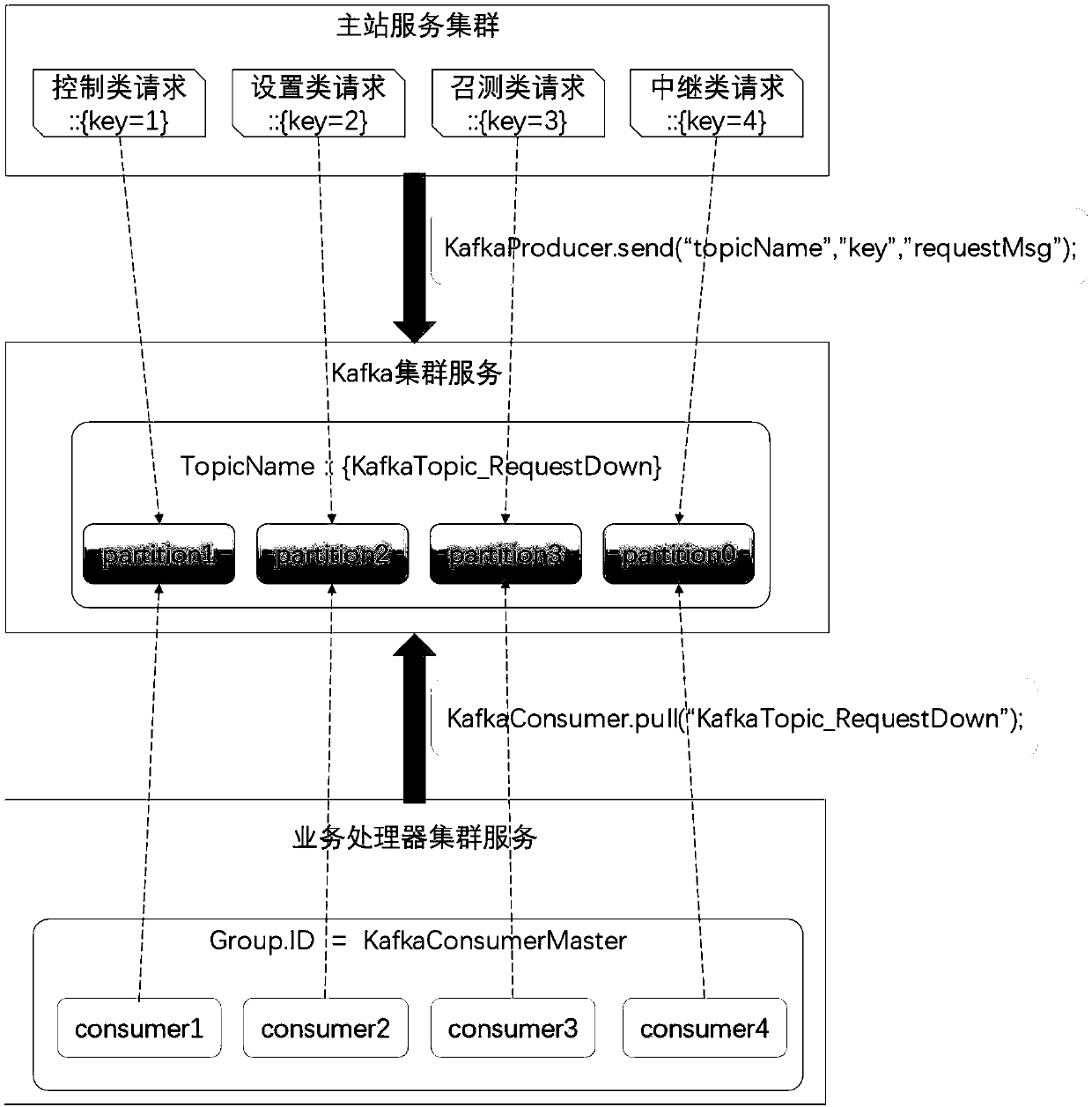

Message caching system and message caching method based on Kafka

InactiveCN109451072AImprove parallel processing capabilitiesImprove throughputTransmissionMessage queueData warehouse

The application discloses a message caching system and a message caching method based on Kafka. The system comprises: a service processor cluster, a main station application cluster and a data warehousing service cluster, which are all associated with a publisher's theme, wherein the main station application cluster comprises a first Kafka production for transmitting downlink request data to the service processor cluster to a downlink theme of the Kafka message queue; a first Kafka consumer of the service processor cluster sends the downlink data to the terminal, and a second Kafka producer sends the uplink data to an uplink theme of the Kafka message queue; and the data warehousing service cluster comprises a second Kafka consumer that receives the uplink theme and message theme of the Kafka message queue and bulks the warehousing. The message caching system and message caching method based on Kafka provided by the application can implement unified management of receiving / transmittinguplink and downlink data.

Owner:GUANGDONG POWER GRID CO LTD +1

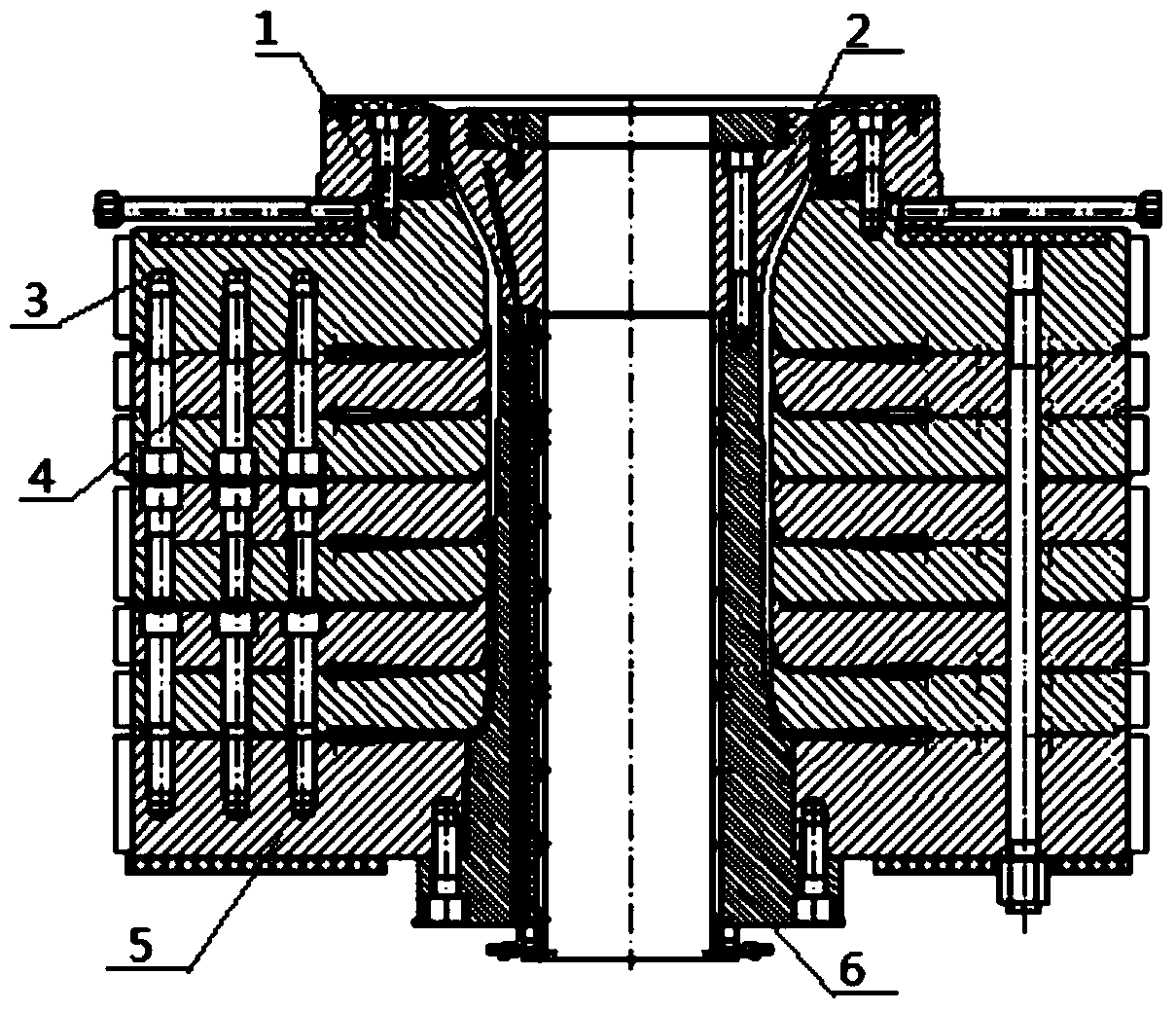

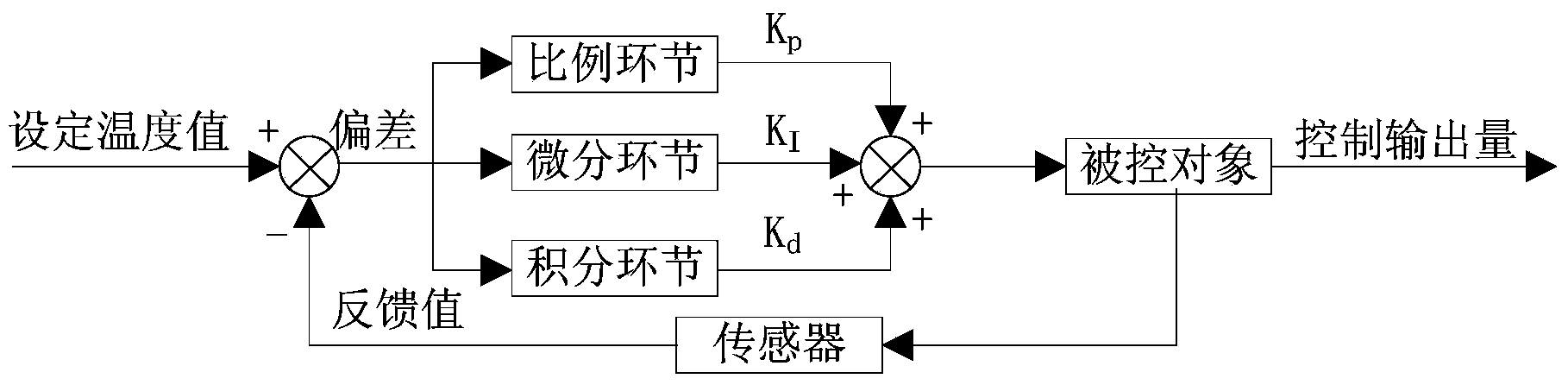

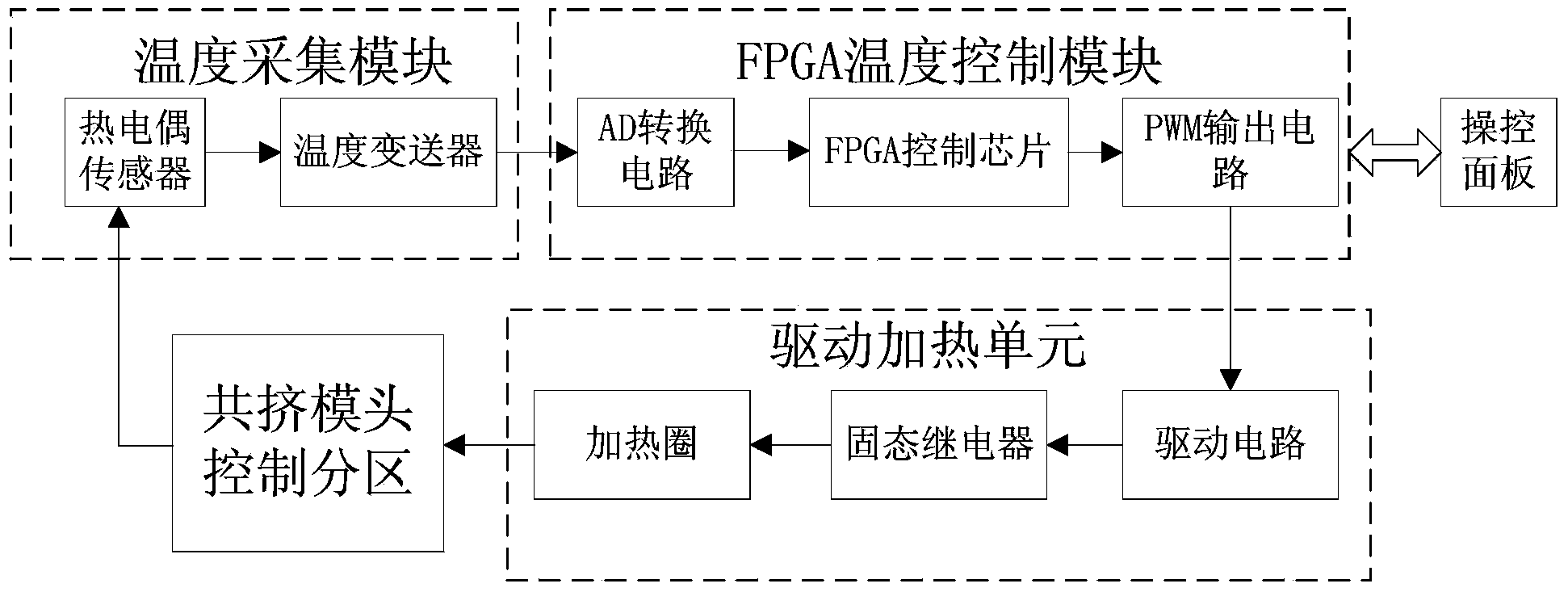

Multi-layer co-extrusion die head intelligent temperature control system and control method thereof

The invention relates to a multi-layer co-extrusion die head intelligent temperature control system including a temperature acquisition module, an FPGA temperature control module, a drive heating module and a control panel. The temperature acquisition module includes N temperature acquisition units; the FPGA temperature control module includes an AD switching circuit, an FPGA control chip for realizing a fuzzy PID control algorithm, and a PWM output circuit; the drive heating module includes N drive heating units corresponding to heaters in a control partition; temperature signals of the control partition are acquired by the temperature acquisition units and are inputted into the FPGA temperature control module, and after treatment, N paths of PWM control variables are outputted and are respectively outputted to the drive heating units by the PWM output circuit in a single path mode. According to the control method, double-parameter input of a deviation e and a deviation change rate e[c] is adopted, correction values of a PID parameter value obtained by fuzzy inference are corrected, final PID input parameter values are obtained, and thus heating coil temperature intelligent control is realized.

Owner:XI AN JIAOTONG UNIV

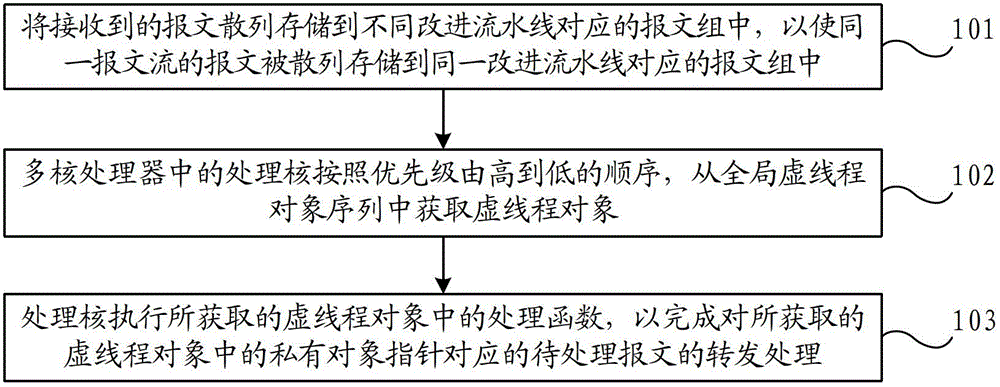

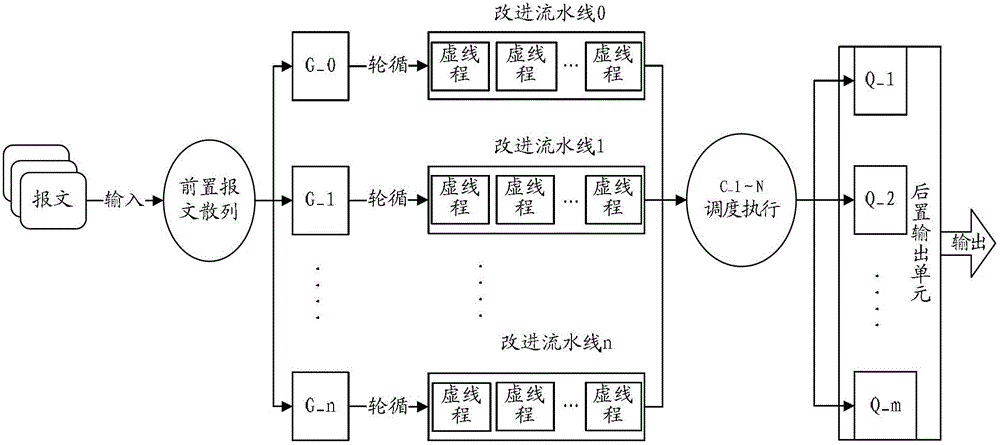

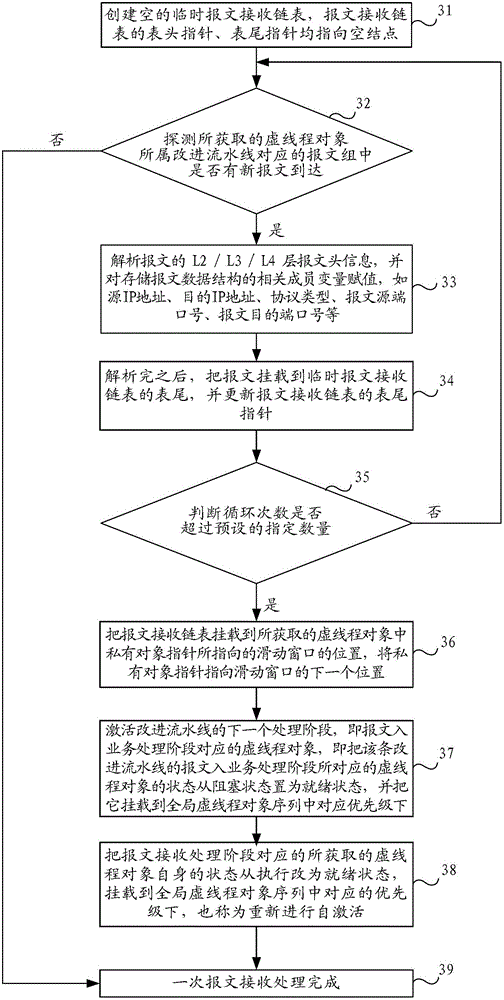

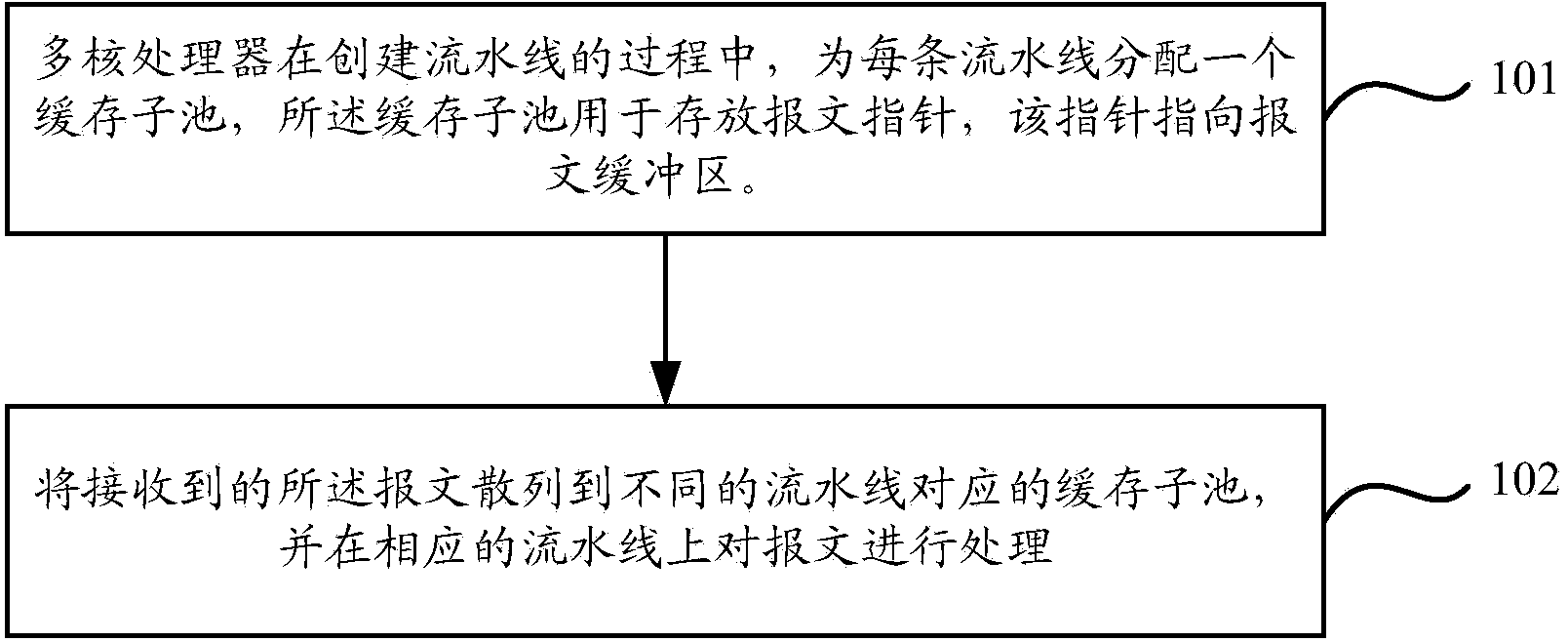

Multi-core message forwarding method, multi-core processor and network equipment

ActiveCN102752198AImprove parallel processing capabilitiesSolve idle problemsNetworks interconnectionMulti-core processorMessage flow

The invention provides a multi-core message forwarding method, a multi-core processor and network equipment. The method comprises the following steps of: storing received messages into message groups corresponding to different improvement pipelines in a hash way so that the messages of the same message flow are stored in the message group corresponding to the same improvement pipeline in the hash way; acquiring virtual thread objects from a global virtual thread object sequence by using a processing core in the multi-core processor according to the order of the priority levels from high to low, wherein the global virtual thread object sequence stores the virtual thread objects in a ready state at each priority level, and the virtual thread objects in the ready state at the same priority level are stored in the global virtual thread object sequence according to a first-in first-out order; and executing a processing function in the acquired virtual thread object to finish forwarding a message to be processed corresponding to a private object pointer in the acquired virtual thread objects by using the processing core. By using the technical scheme provided by the invention, the parallel processing capacity of the multi-core processor is improved.

Owner:BEIJING XINWANG RUIJIE NETWORK TECH CO LTD

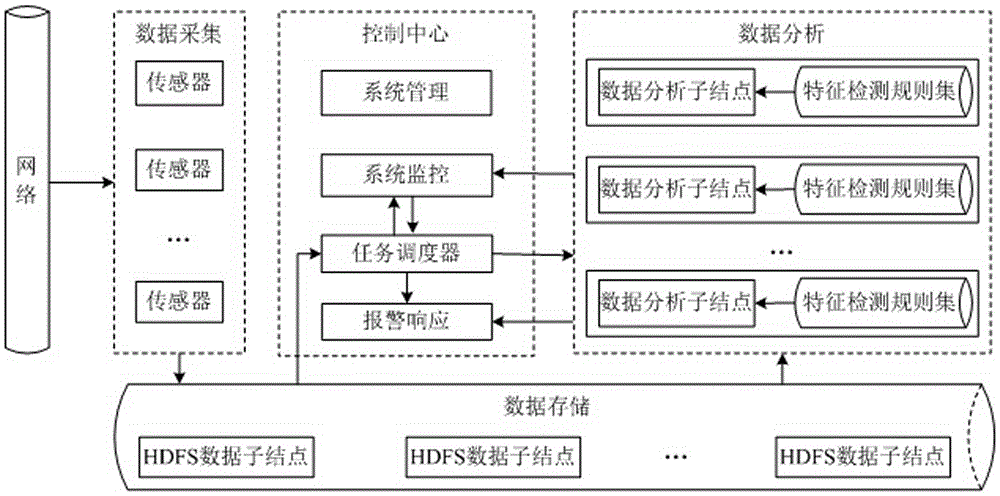

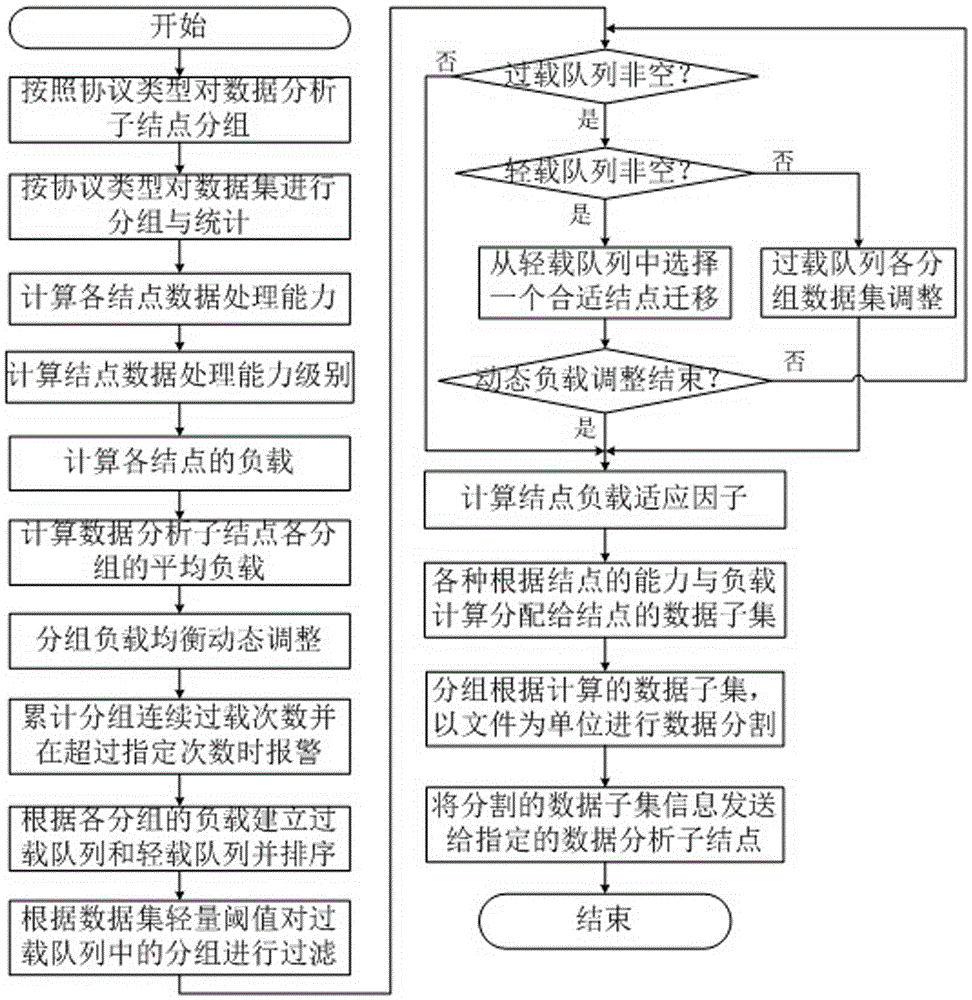

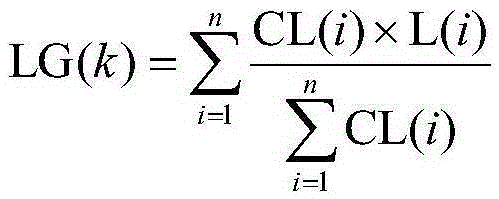

Hadoop-based distributed intrusion detection system

ActiveCN105391742AStrong interoperabilityReduce false negative rateTransmissionSpecial data processing applicationsData processingData analysis

The invention discloses a Hadoop-based distributed intrusion detection system which comprises a data acquisition module, a data storage module, a control center and a data analysis module, wherein the control center comprises a system management module, a system monitor module, a task scheduling module and an alarm response module. By utilizing a Hadoop-based distributed computation framework, the system is allowed to have good interoperability, and the system reliability is improved; the system carries out data parallel acquisition through a distributed mode, thereby improving data acquisition capability and reducing packet loss probability; in an algorithm adopted in the system, data is allocated according to capacity and load of nodes, and adjustment is carried out by utilizing a dynamic load balancing strategy, so that data processing capacity of the nodes is given effective play to, and load balancing of the system is maintained; and through the algorithm, the case of distributing the data comprising the same attack to two or more detection nodes for processing separately, which damages integrity of the data, is prevented, and detection efficiency is improved effectively.

Owner:GUILIN UNIV OF ELECTRONIC TECH

Method and device for processing traffic information in real time

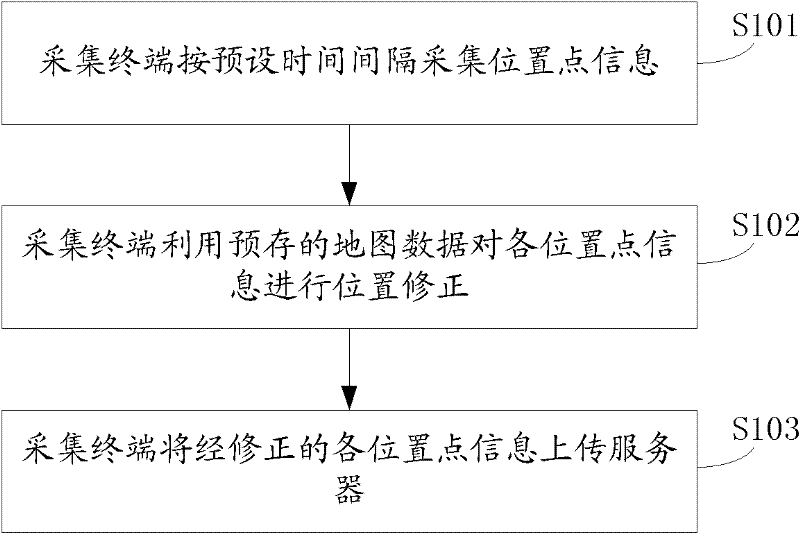

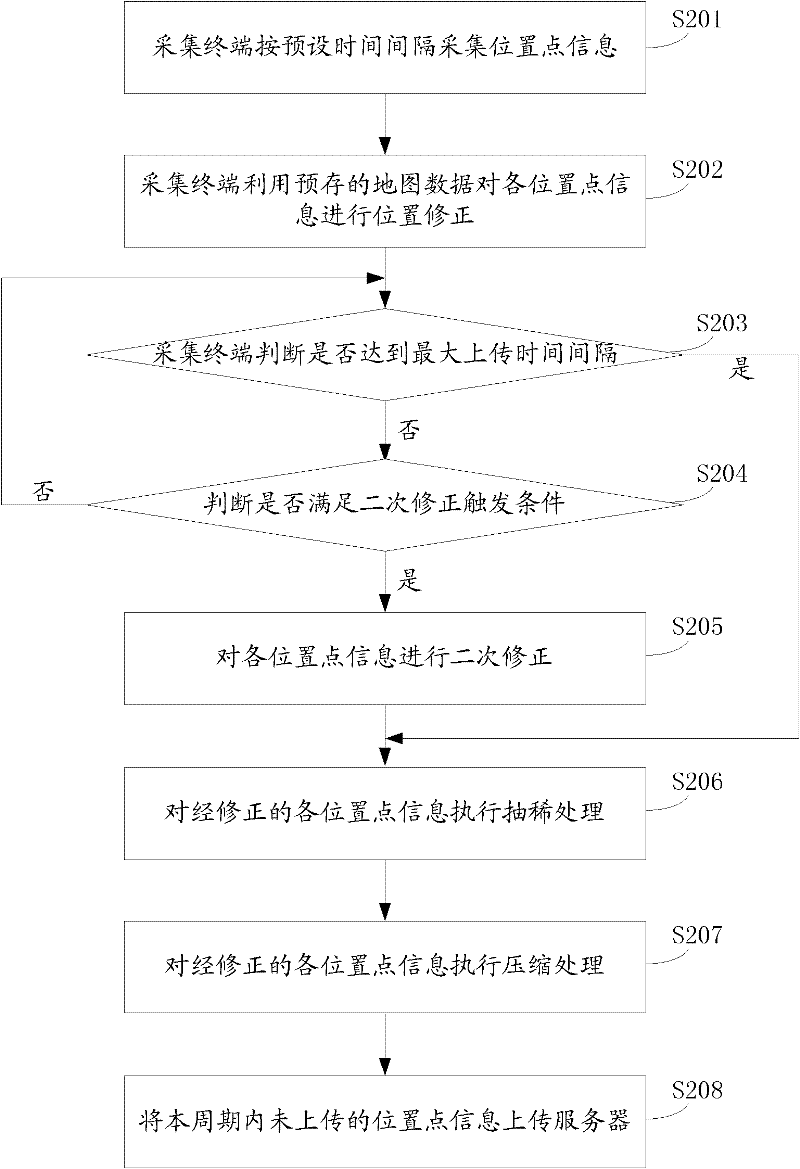

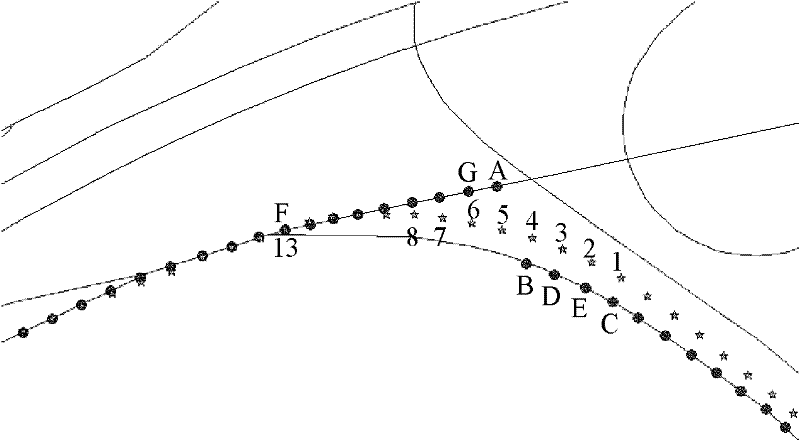

ActiveCN102682590AReduce computing pressureImprove parallel processing capabilitiesDetection of traffic movementOperational costsComputer terminal

The invention discloses a method and a device for processing traffic information in real time and relates to the field of navigation. The method comprises the following steps: collecting information of a position point by a collecting terminal according to a preset time interval; correcting the information of each position point by utilizing pre-stored map data; and uploading the corrected information of the position point to a server. The device comprises a collection module, a position correction module and an uploading module. In the embodiment of the invention, the position of an original position point is corrected at the collecting terminal, and the corrected information of the position point is uploaded to the server, so that the calculating pressure of the server is effectively reduced, thereby the parallel processing capability of the server is greatly increased and the operation cost of the server is sharply reduced.

Owner:ALIBABA (CHINA) CO LTD

Method for synchronizing processors in a multiprocessor system

InactiveUS7191294B2Improve parallel processing capabilitiesProgram synchronisationMemory adressing/allocation/relocationMulti processorSoftware update

The high-speed barrier synchronization is completed among multiprocessors by saving overhead for parallel process without addition of a particular hardware mechanism. That is, the barrier synchronization process is performed by allocating the synchronization flag area, on the shared memory, indicating the synchronization point where the execution of each processor for completing the barrier synchronization is completed, updating the synchronization flag area with the software in accordance with the executing condition, and comparing, with each processor, the synchronization flag area of the other processors which takes part in the barrier synchronization.

Owner:HITACHI LTD

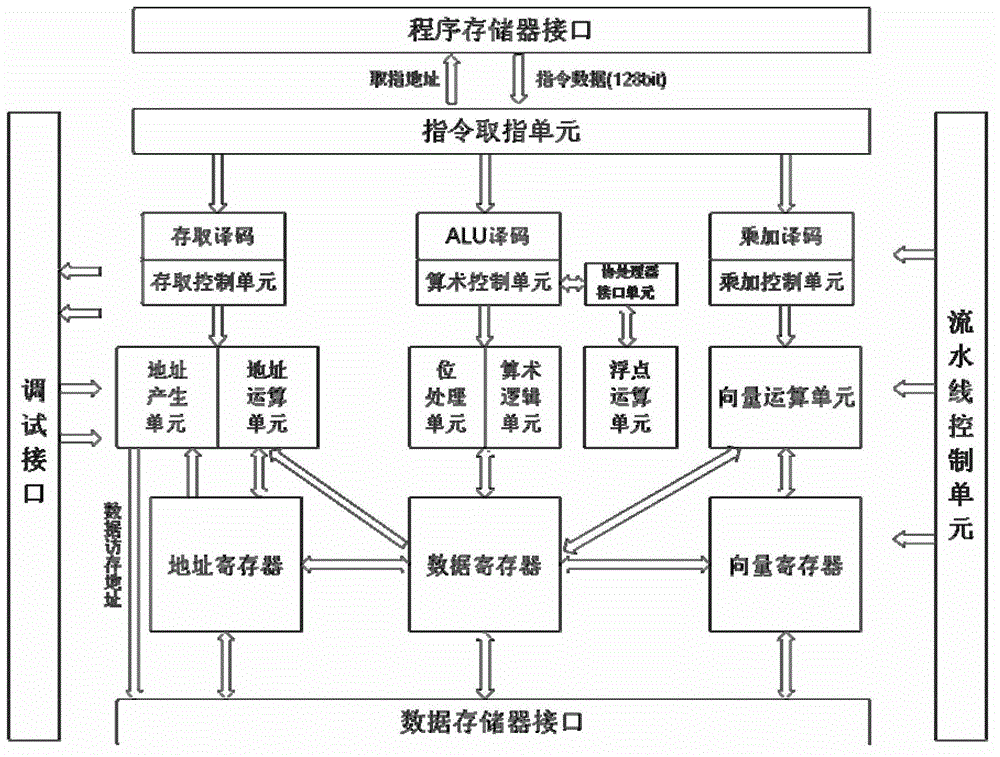

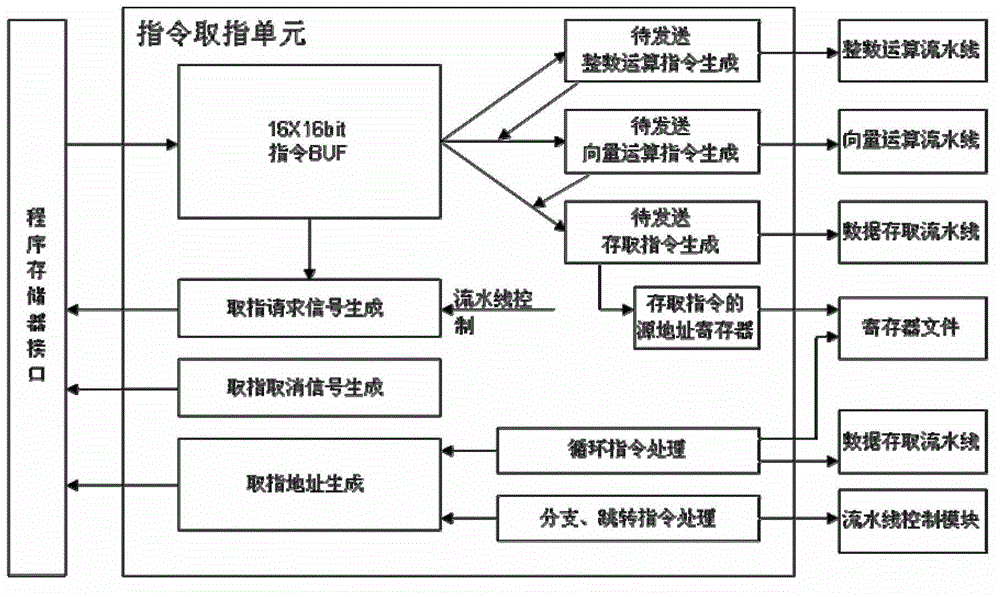

32-Bit triple-emission digital signal processor supporting SIMD

ActiveCN102750133ASupport operationReduce power consumptionConcurrent instruction executionMemory interfaceData access

The invention discloses a 32-bit triple-emission digital signal processor supporting SIMD (Single Instruction Multiple Data), comprising three flow lines in parallel emission: a data access flow line, an integer arithmetic flow line and a vector arithmetic flow line, wherein each flow line is provided with an independent decoding and execution unit and supports SIMD operation. The 32-bit triple-emission digital signal processor supporting SIMD is mainly composed of a program memory interface unit, a data memory interface unit, an instruction fetch unit, a flow line control unit, a system bus, a data access flow line unit, an integer arithmetic flow line unit, a vector arithmetic flow line unit, a data register, an address register, a vector register, a coprocessor interface unit and a floating point arithmetic unit, all of which are connected together through a circuit. The 32-bit triple-emission digital signal processor supporting SIMD supports parallel execution of three flow lines so that the parallel processing capability of a DSP (Digital Signal Processor) is improved; besides, the 32-bit triple-emission digital signal processor supports parallel execution four groups of 16-bit multiplying and adding operations in a single cycle, and supports simultaneous execution of the operation of five groups of data and the access operation of one group of data; therefore, the data processing capability of the DSP is enhanced.

Owner:58TH RES INST OF CETC

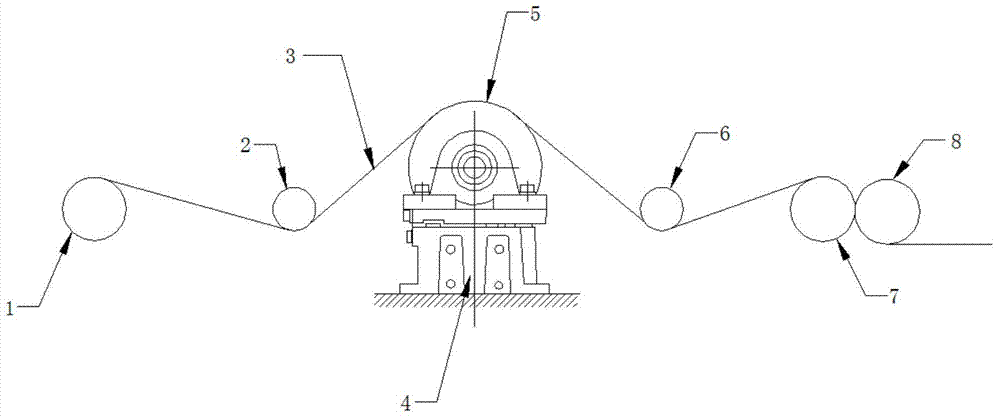

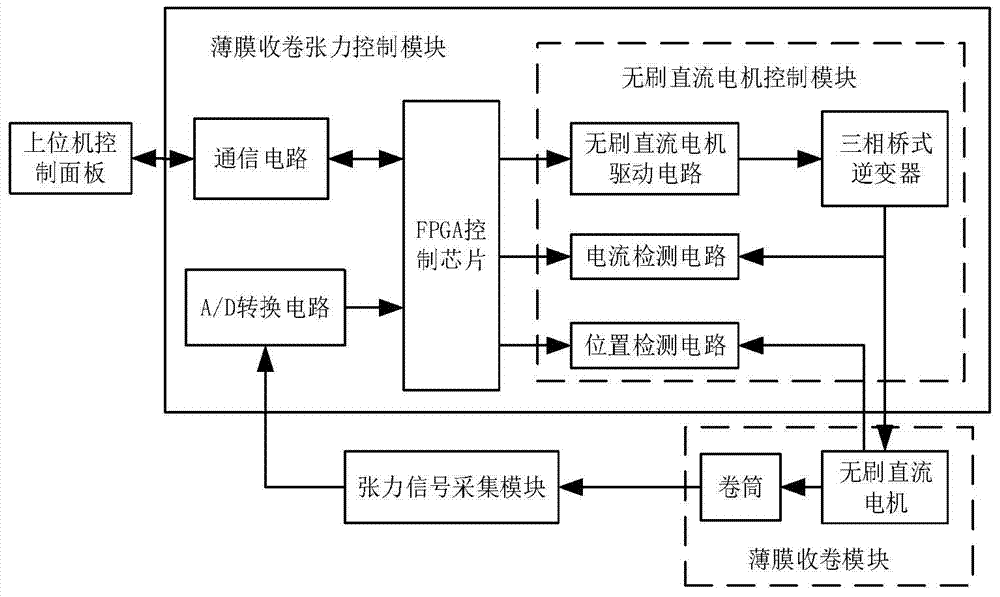

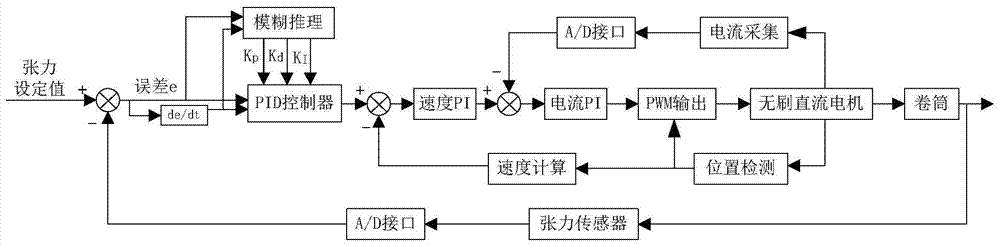

FPGA-based thin film rolling tension control system and method

InactiveCN104709748AImprove stabilityImprove parallel processing capabilitiesWebs handlingControl signalProgrammable logic device

The invention discloses an FPGA-based thin film rolling tension control system and method. The system comprises a tension signal collection module, a thin film rolling tension control module, a thin film rolling module and an upper computer operation panel. A programmable logic device FPGA controls a chip to achieve a fuzzy PID control algorithm, the speed controlled quantity of a brushless direct current motor is obtained, a double closed-loop control algorithm of the brushless direct current motor is combined, then signals are controlled to be correspondingly changed and adjusted when tension changes in the rolling process of a thin film, and constant control over the tension in the rolling process of the thin film can be achieved through real-time collection of tension of the thin film by utilization of the fuzzy PID control algorithm; the development cost is low, the integration level of the system is high, the steady state performance is good, the response speed is high, the control precision is high, and adaptability is high.

Owner:XI AN JIAOTONG UNIV

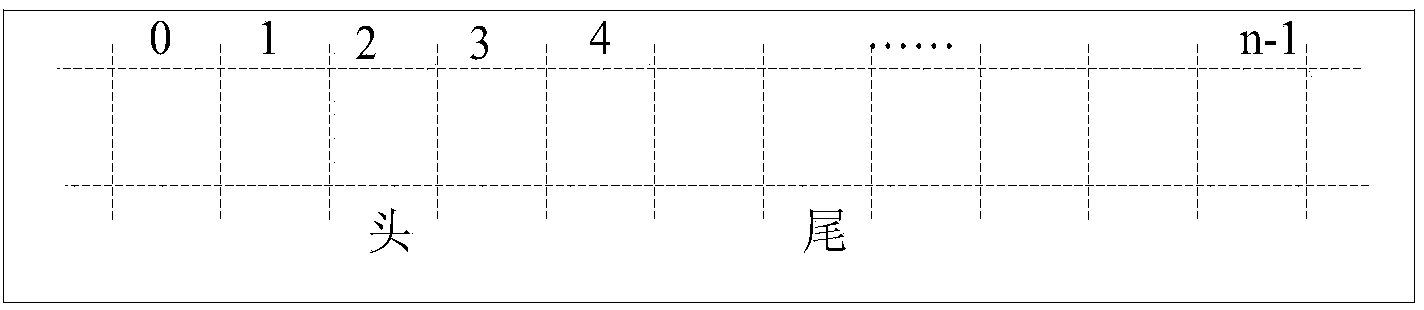

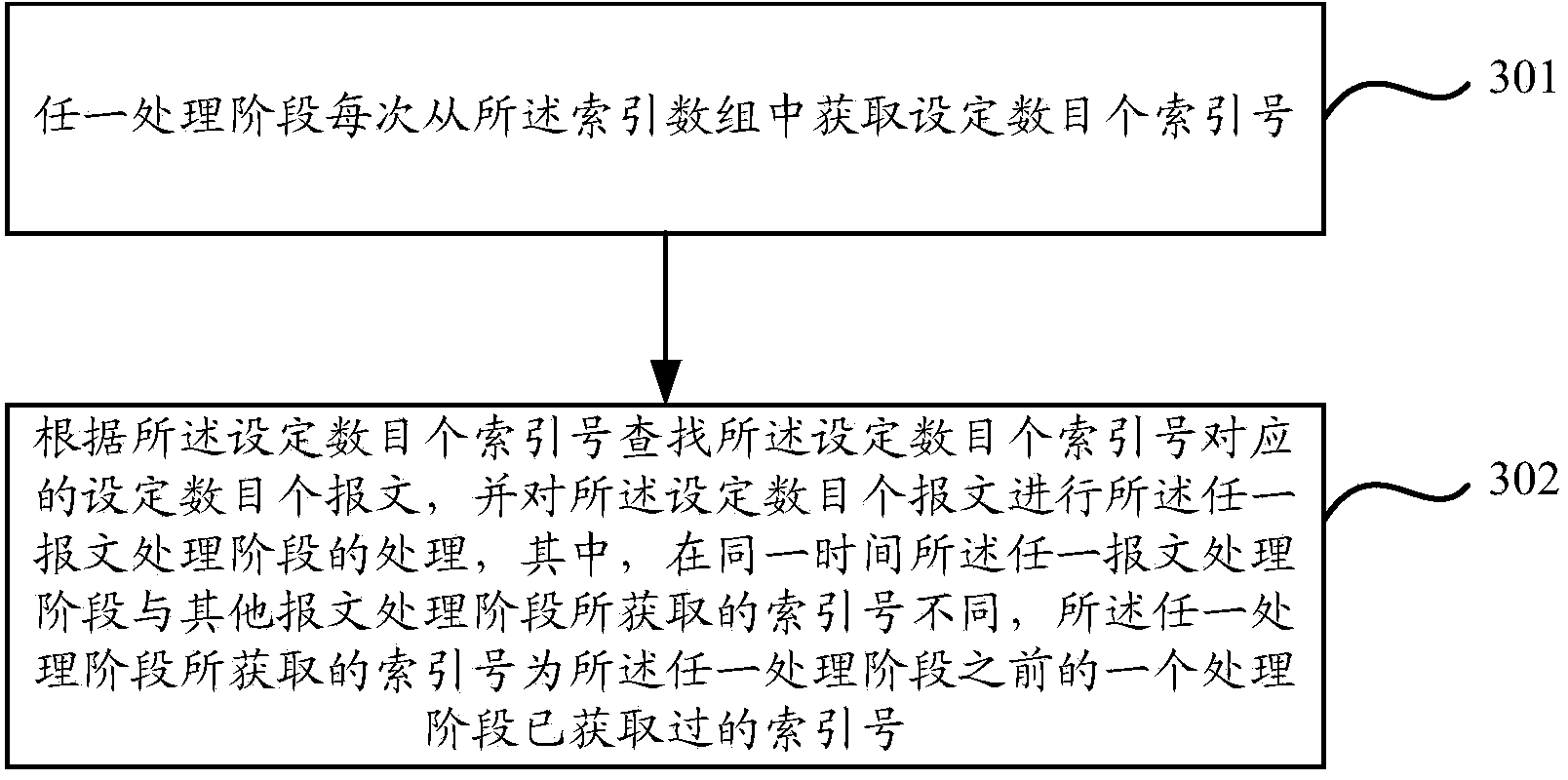

Multi-core processor based message processing method and multi-core processor

ActiveCN104394096AAvoid lock conflictsImprove parallel processing capabilitiesData switching networksMessage processingAssembly line

The invention provides a multi-core processor based message processing method and a multi-core processor. The method comprises steps as follows: the multi-core processor distributes one buffer subpool to each assembly line in a flow line establishing process, and the buffer subpool is used for storing a message pointer which points to a message buffer; and the received messages are scattered to the buffer subpools corresponding to different flow lines and processed on the corresponding flow lines. According to the multi-core processor based message processing method and the multi-core processor, one buffer subpool is provided for each flow line, and resources are directly acquired from the corresponding buffer subpools when required to be acquired for the flow lines, so that the lock confliction phenomenon among the flow lines in the prior art is avoided, lockless message retransmission is realized, and the parallel processing capability of the multi-core processor is improved to a certain degree.

Owner:RUIJIE NETWORKS CO LTD

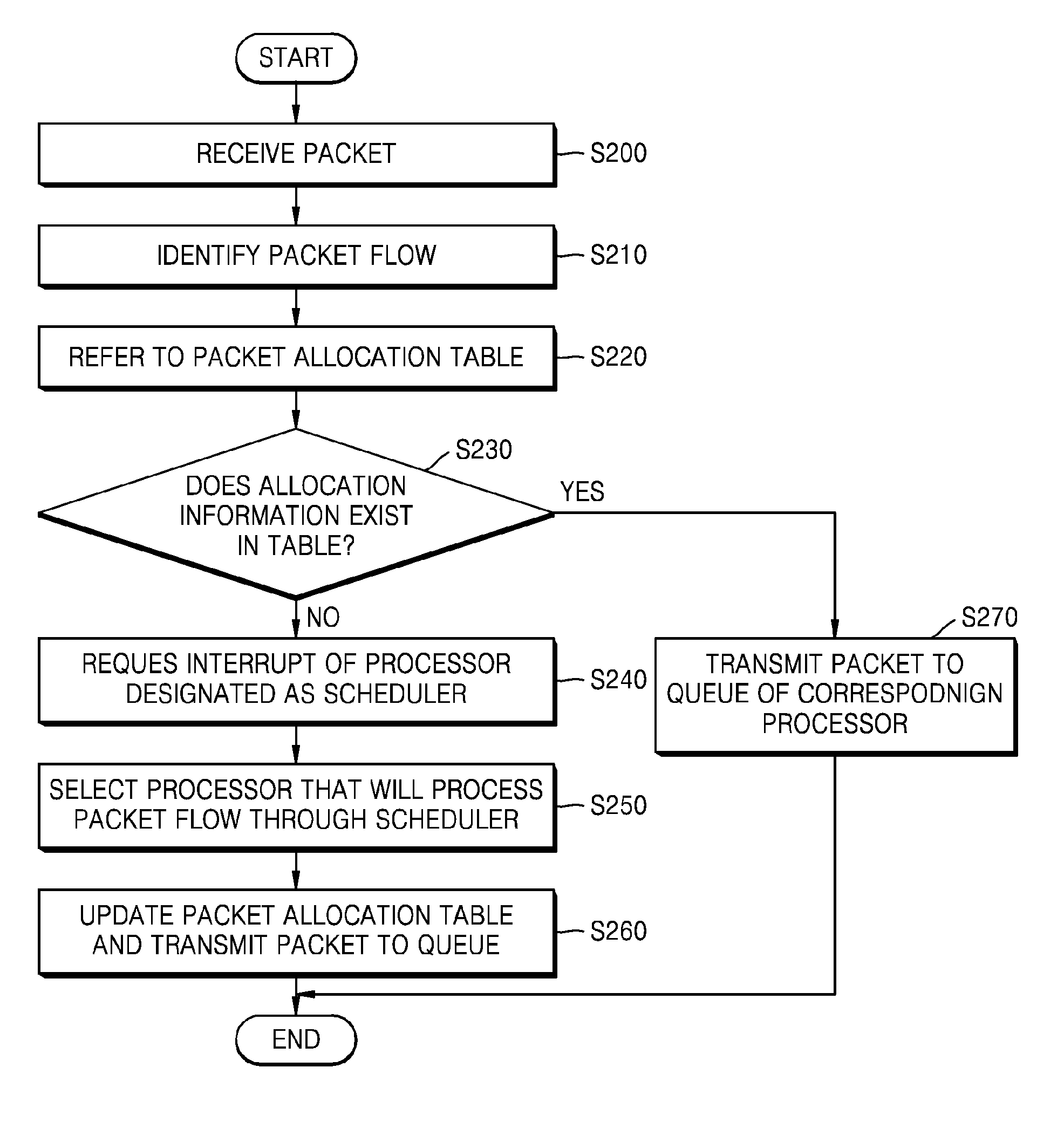

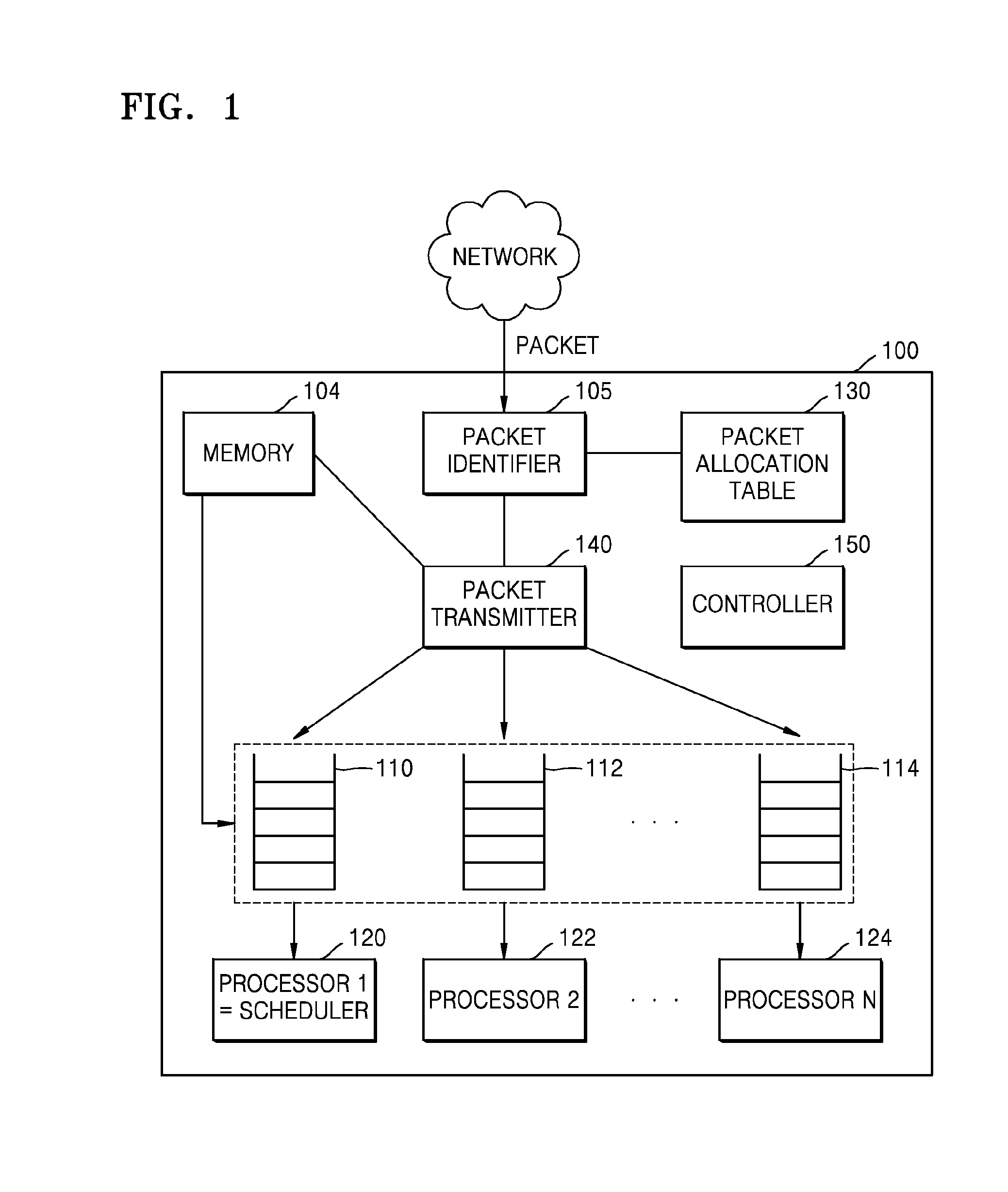

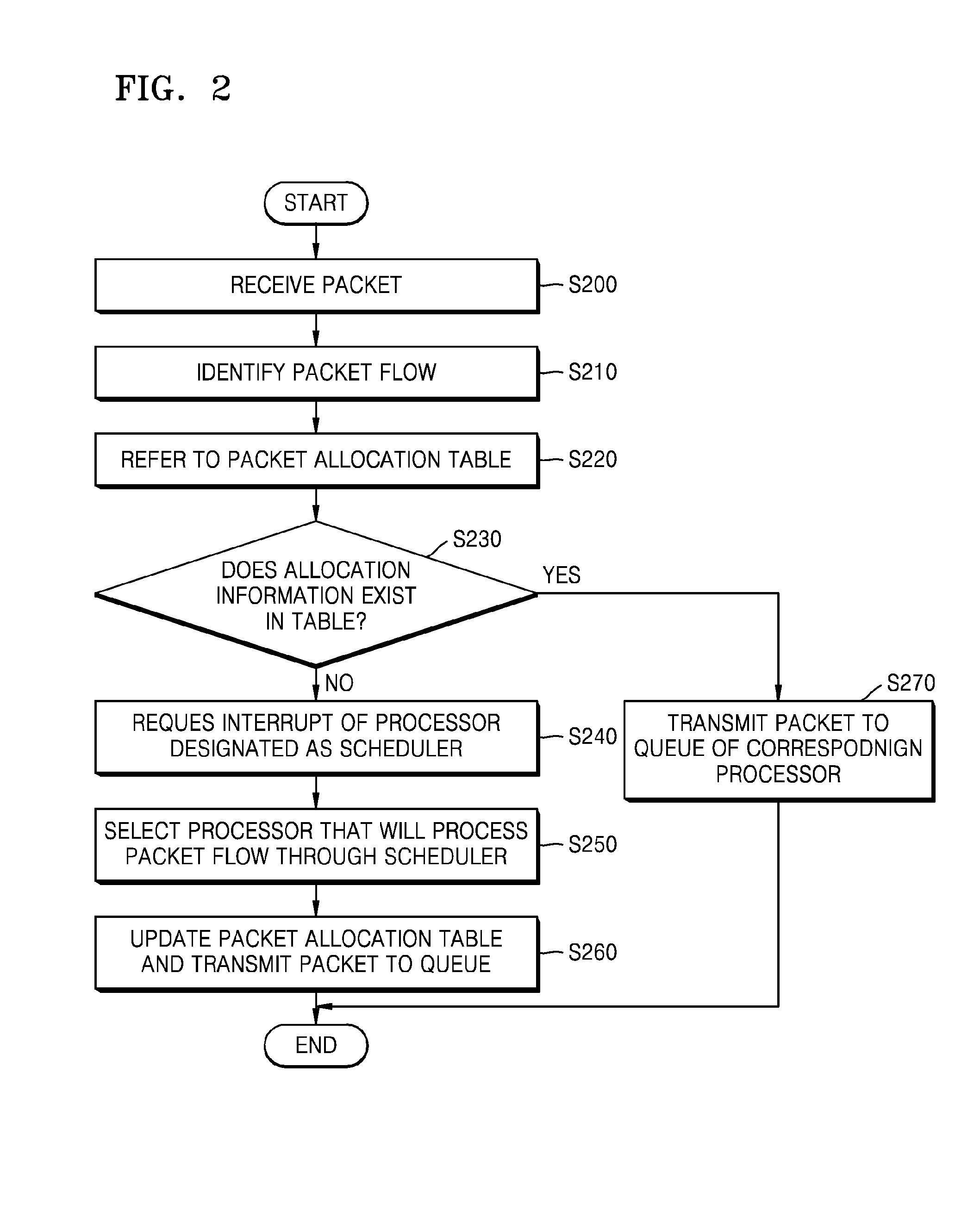

Scheduling method and apparatus in multiprocessing environment

ActiveUS20160283283A1Improve parallel processing performanceReduce latencyProgram initiation/switchingResource allocationNetwork interfaceNetwork packet

A network interface unit for processing a packet and a method thereof are provided. The network interface unit includes a plurality of queues, if a packet is received through a physical network, identifies a flow of the packet, stores the packet in a plurality of queues in the unit of flow, and processes the packet in parallel through a multiprocessor.

Owner:GUBERNET

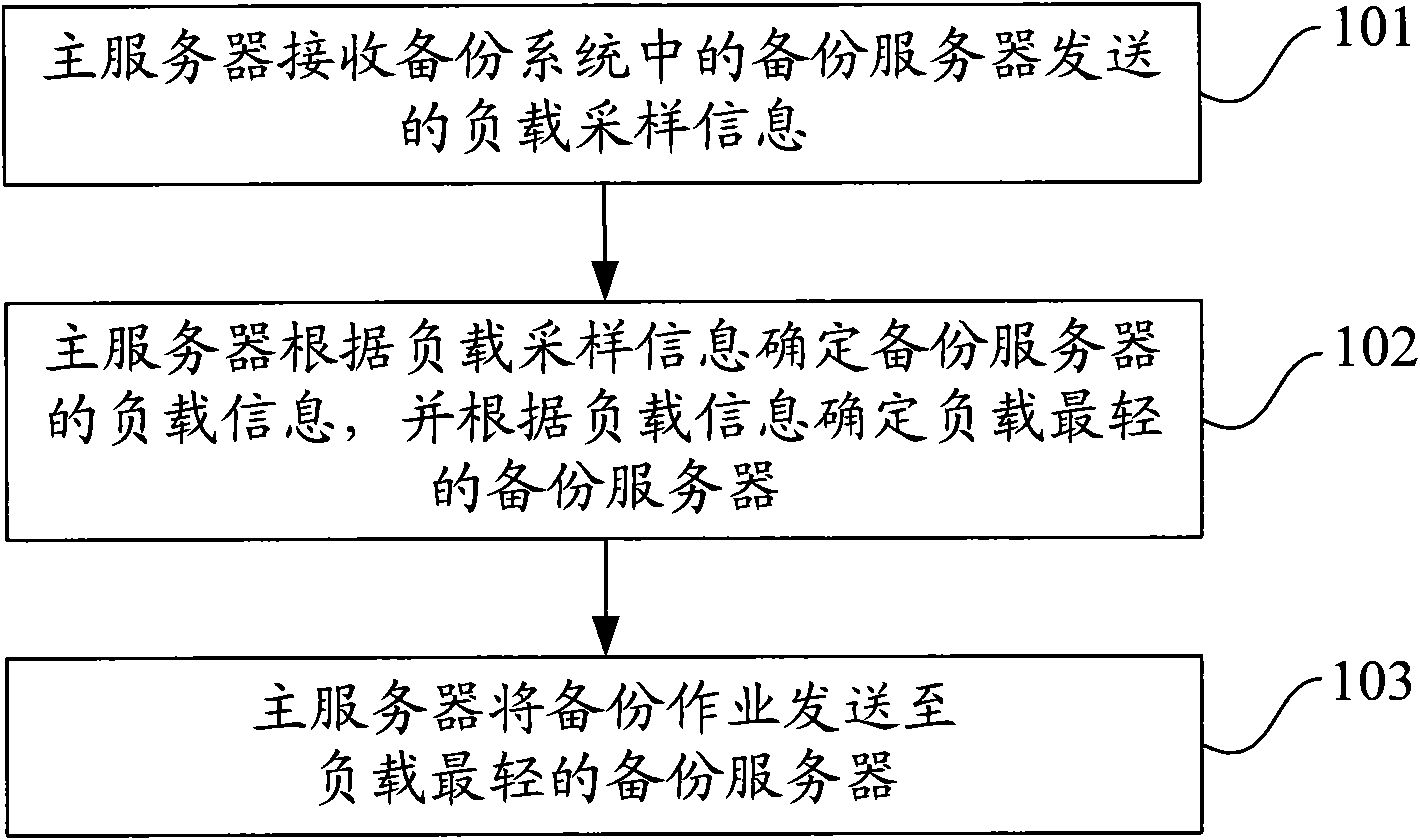

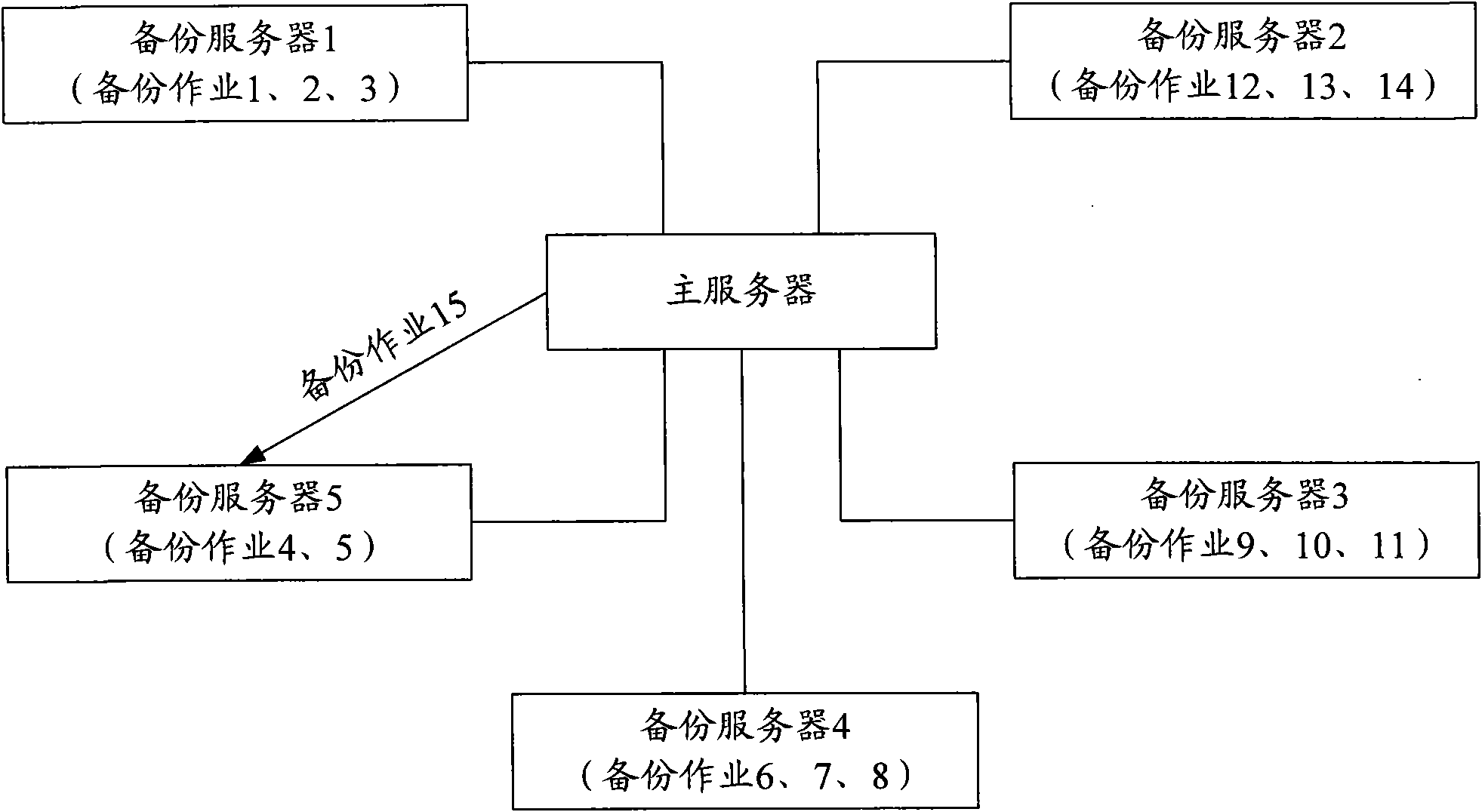

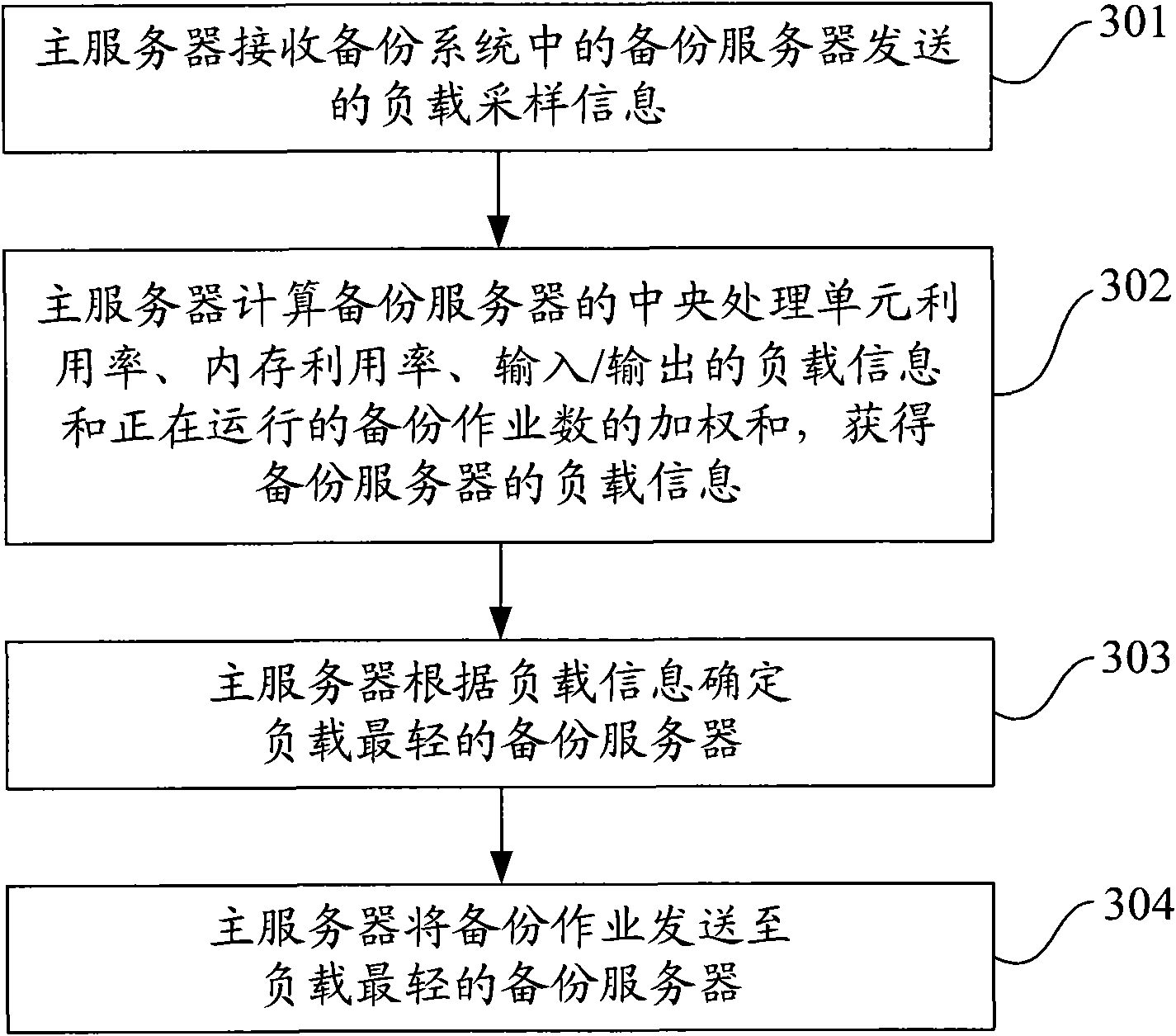

Backup method, master server, backup servers and backup system

ActiveCN101662495AImprove parallel processing performanceAvoid overloadingData switching networksOperating systemUtilization rate

The embodiment of the invention discloses a backup method, a master server, backup servers and a backup system. The method includes the following steps: receiving load sampling information sent by thebackup server in the backup system that comprises at least two backup servers; according to the load sampling information, determining the load information of the backup server and according to the load information, determining the backup server with lightest load in the backup system; and sending backup operation to the backup server with lightest load so that the backup server with lightest load stores the backup data stream corresponding to the backup operation in a storage array. In LAN-Free framework, the embodiment of the invention improves the utilization rate of SAN bandwidth resources and the whole backup performance of the backup system, shortens a backup window, makes up the defect that the treatment of backup operation fails when the backup server goes wrong and improves the robustness of the backup system.

Owner:CHENGDU HUAWEI TECH

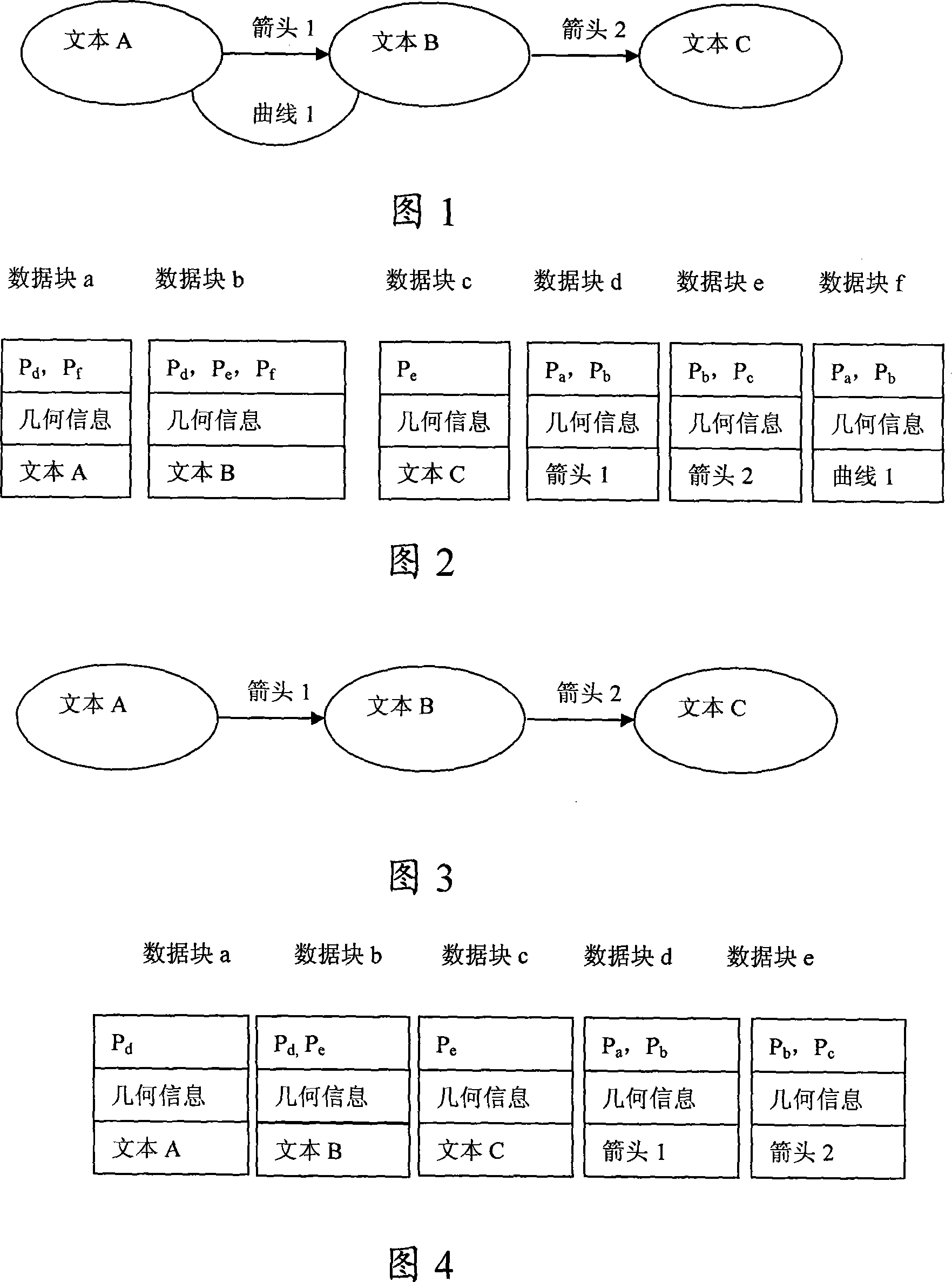

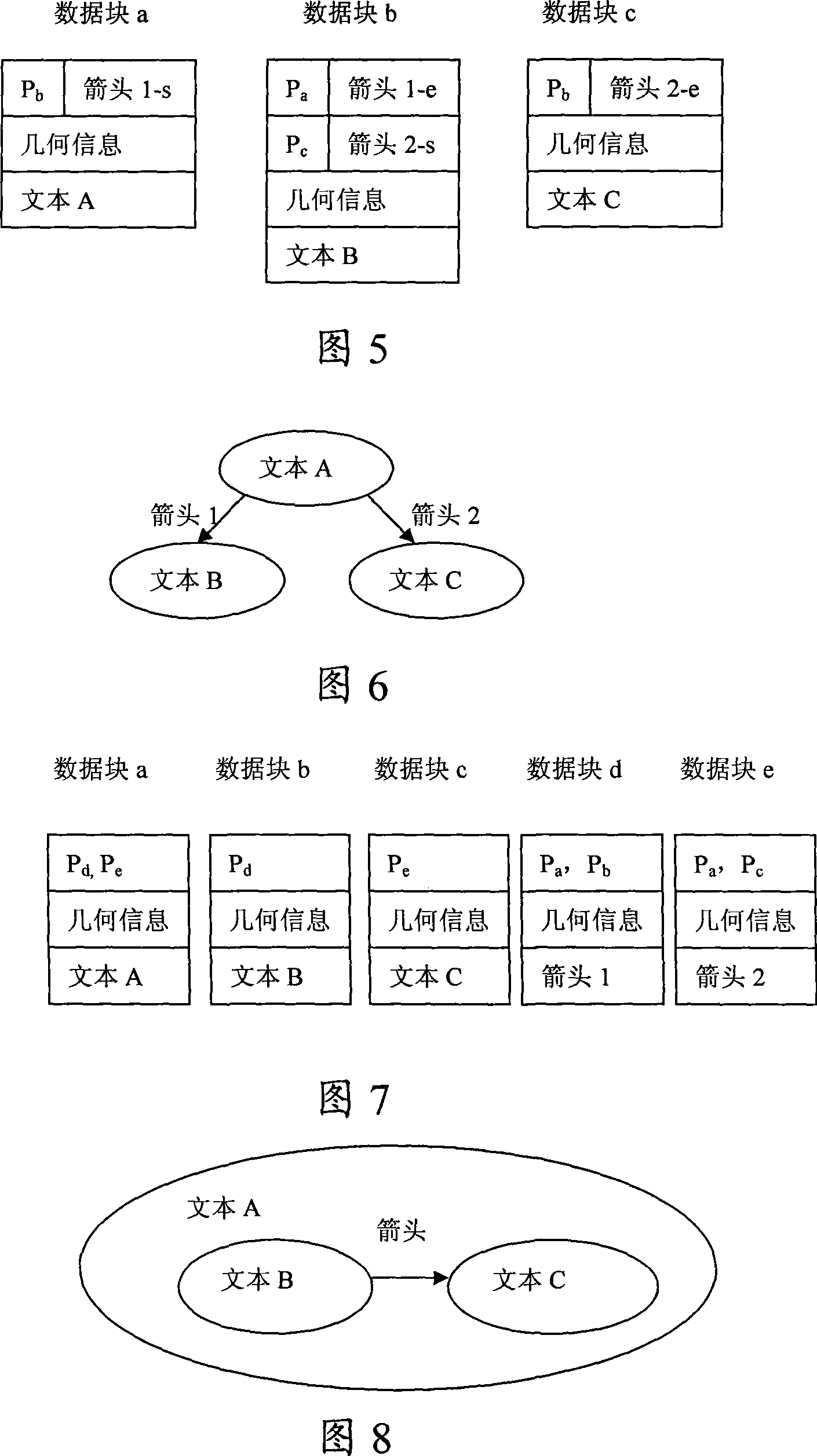

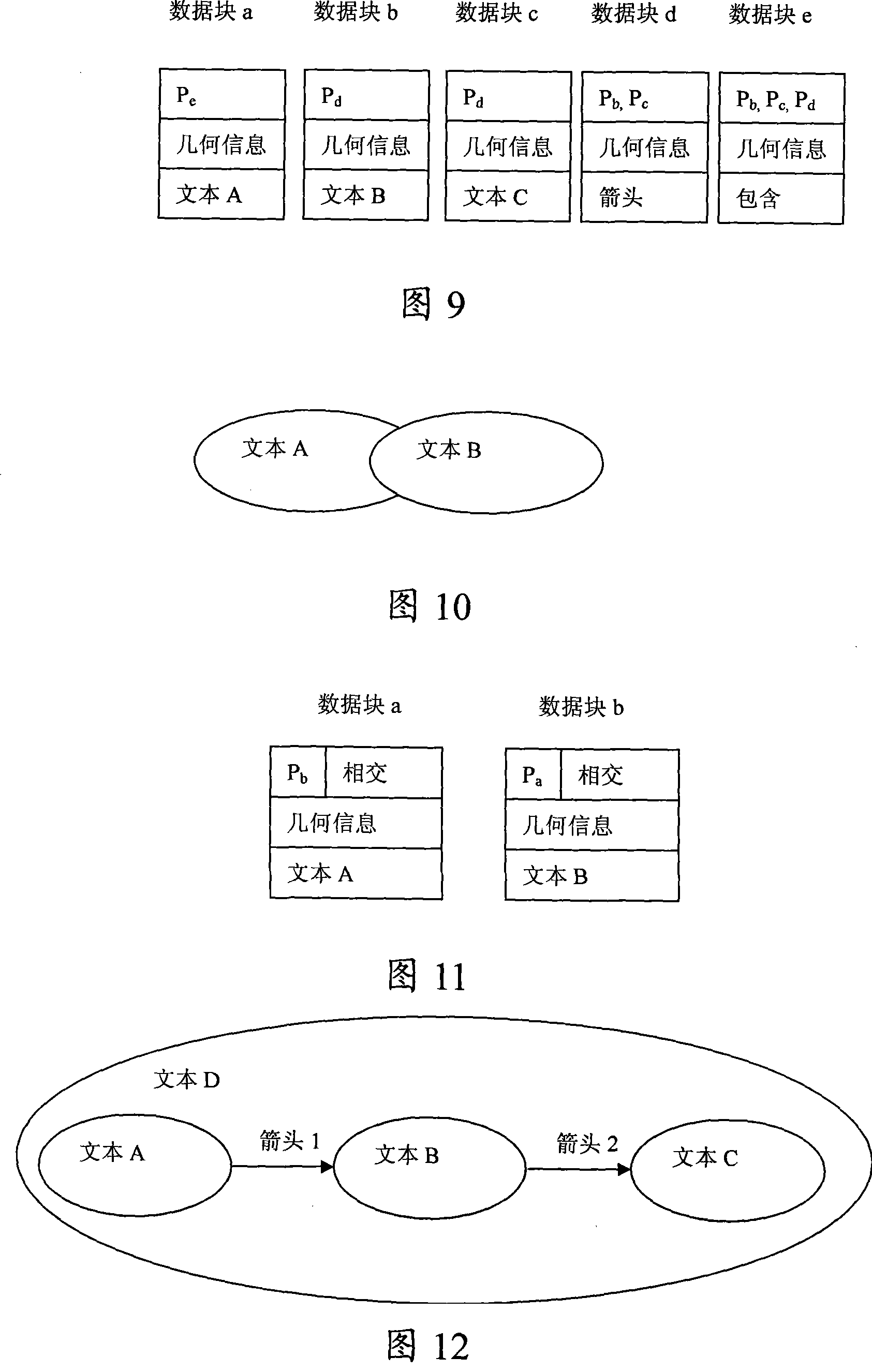

Index, search, storage and display control information systems for associated data

InactiveCN101178733AAccurate storageThe data blocks stored to record accurateDigital data information retrievalSpecial data processing applicationsUser inputIndex system

The invention discloses an information system relating to the index, searches, storage and control displaying of the related data. The invention index system at least comprises two data blocks with relating relationship, each data block consists of position information blocks and content information blocks, the content information blocks are the other data besides the position information blocks in the data blocks, the position information blocks record the position information of the other data blocks related to the data blocks and generate index data according to the prescribed steps; the index method is that: the method generates data block aggregation according to the information input by the users, uses the method of generating key words by corresponding index system to generate index words, and then proceeds index to the index words and displays the result. The invention proceeds the displaying control based on the data blocks and the geometrical relationships in the existing displaying district. The invention is utilized to directly index the relating information in the related data, so as to conveniently realize the concurrent processing of multi-users and commonly share the information which is managed.

Owner:彭海杰

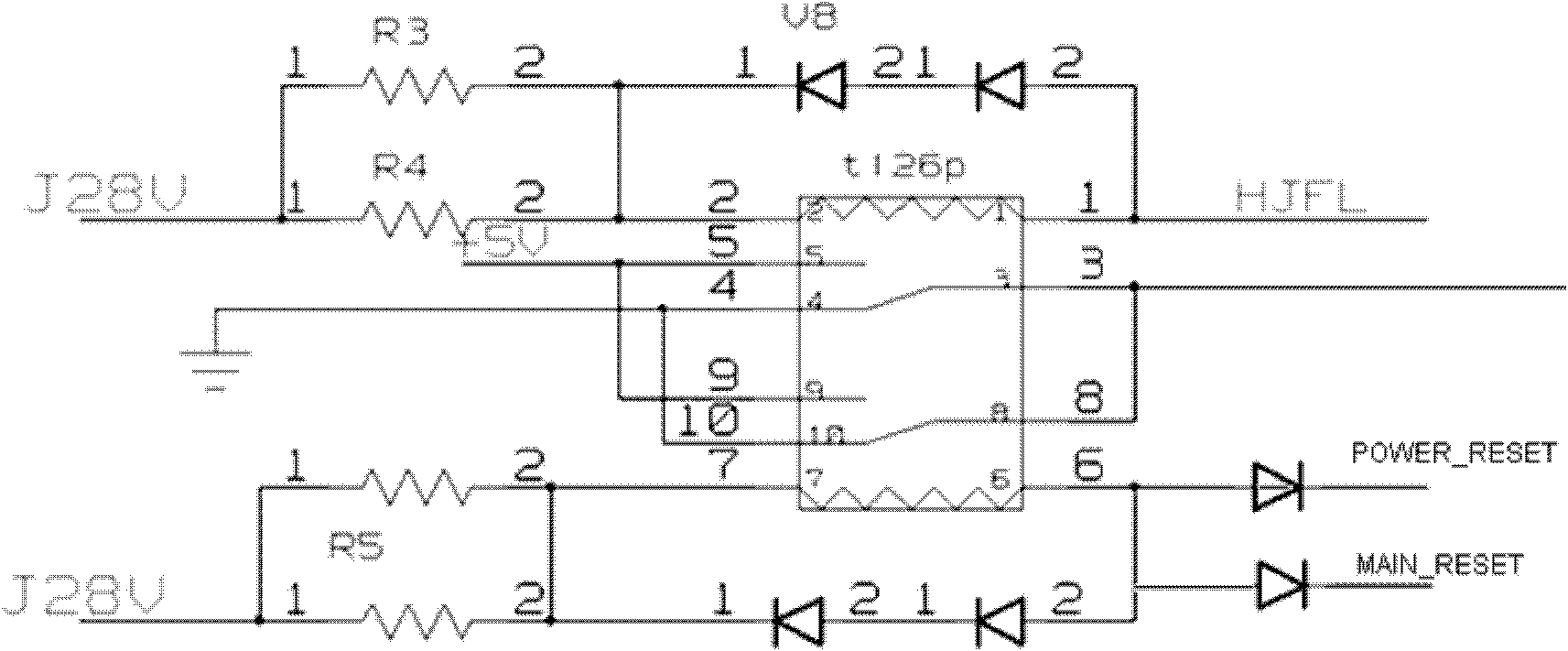

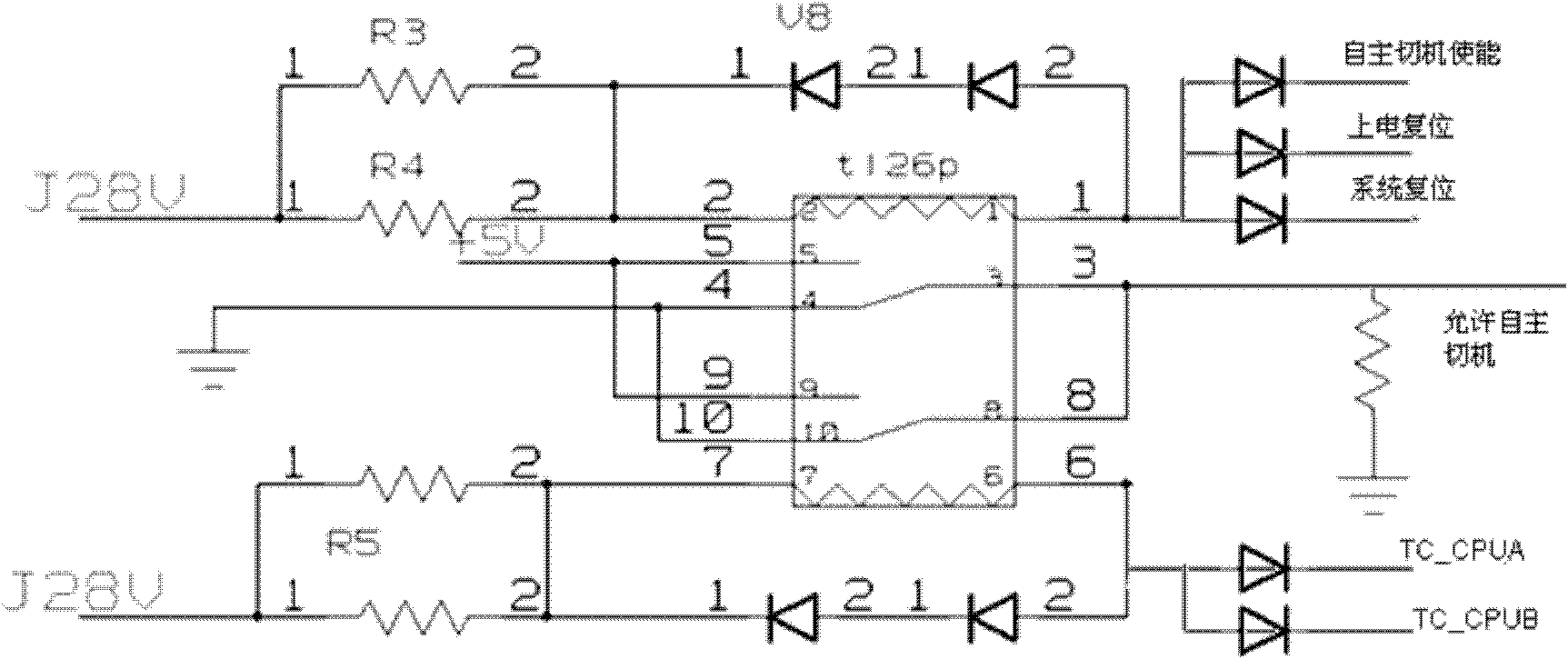

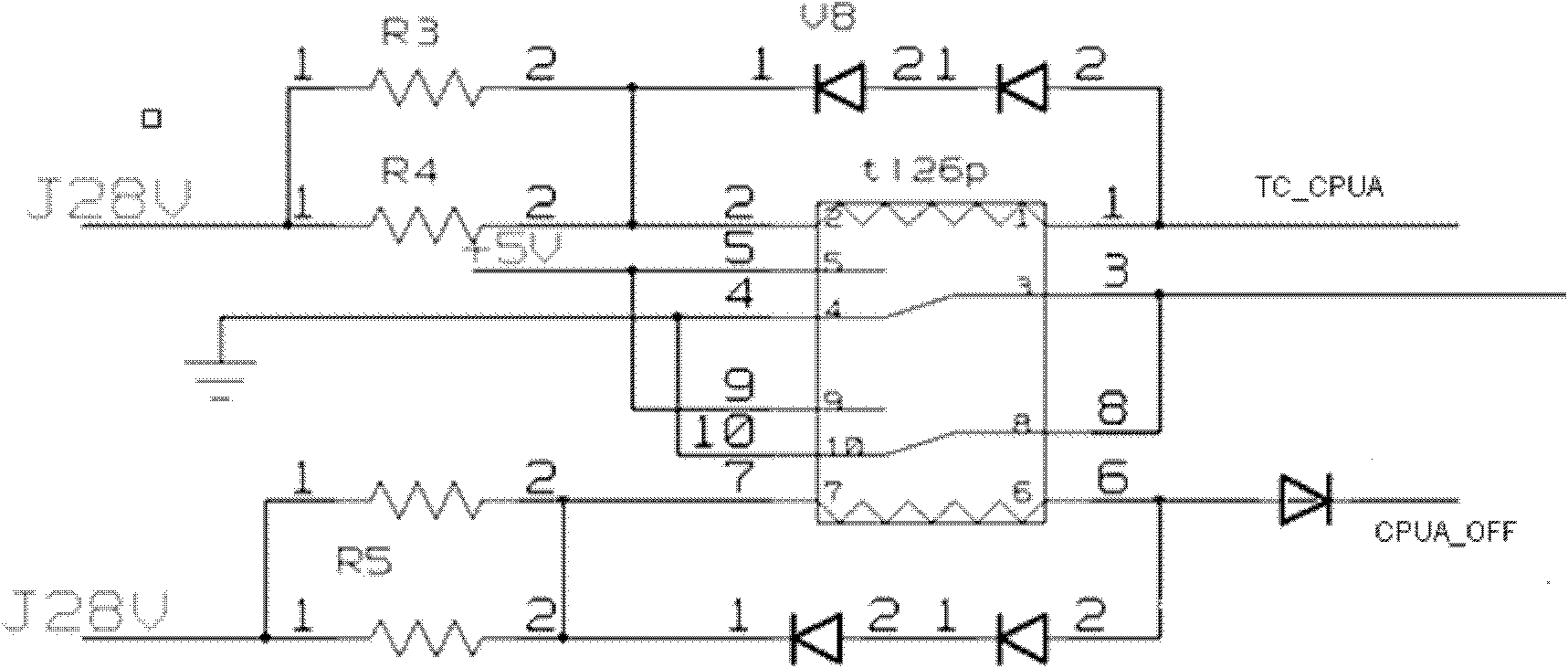

Double-processor borne computer

InactiveCN102122276AGuarantee the function of the cutting machineGuaranteed stabilityArchitecture with multiple processing unitsRemote controlComputer module

The invention discloses a double-processor borne computer which relates to a double-processor technology applied in the aerospace field. The double-processor borne computer solves the problem that ping pong switch and ping-pong right robbing are difficult to avoid in the arbitration method in a borne computer of the traditional double-processor borne computer. A master computer, a slave computer,a power supply, an arbitration module and an IO module of the double-processor borne computer are all fixed on a base plate and connected mutually through data address buses, signal wires and power wires on the base plate, wherein the logical relation of the arbitration module is that: the working condition of the master computer is that an star arrow separation signal is ineffective, an output enable signal of the slave computer is ineffective, and a ready signal of the master computer is effective, or a remote control switch master computer signal is effective; and the working condition of the slave computer is that: an output enable signal of the master computer is ineffective, a generator tripping enable flag is effective, a ready signal of the master computer is ineffective, and a ready signal of the master computer is effective; or an automatic generator tripping signal of the master computer is effective, and the generator tripping enable flag is effective; or a remote control switch slave computer signal is effective.

Owner:HARBIN INST OF TECH

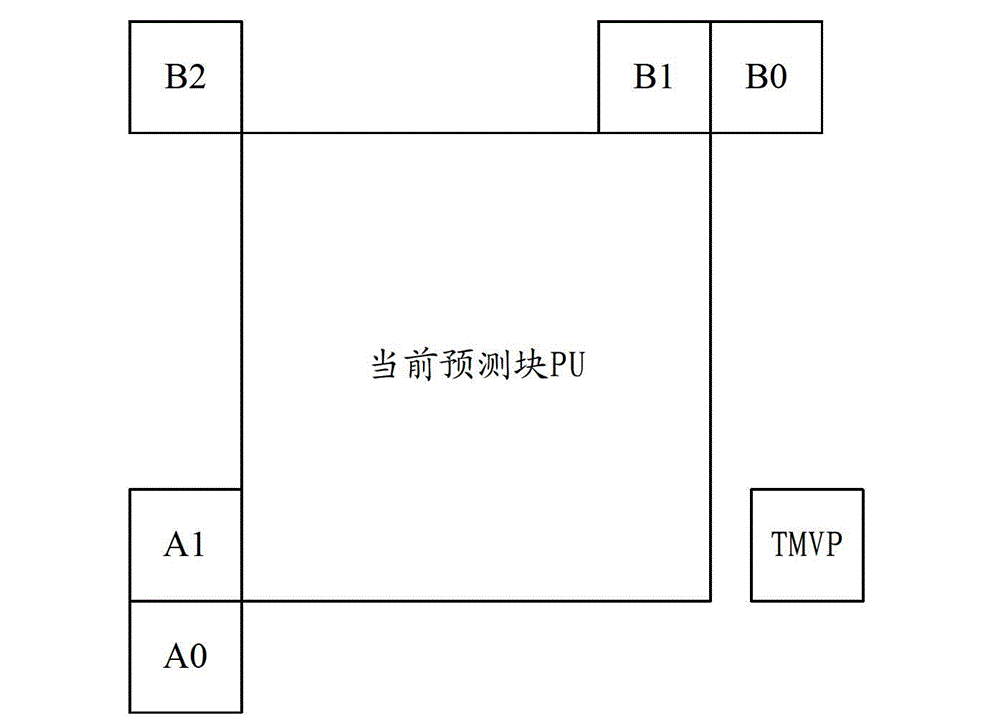

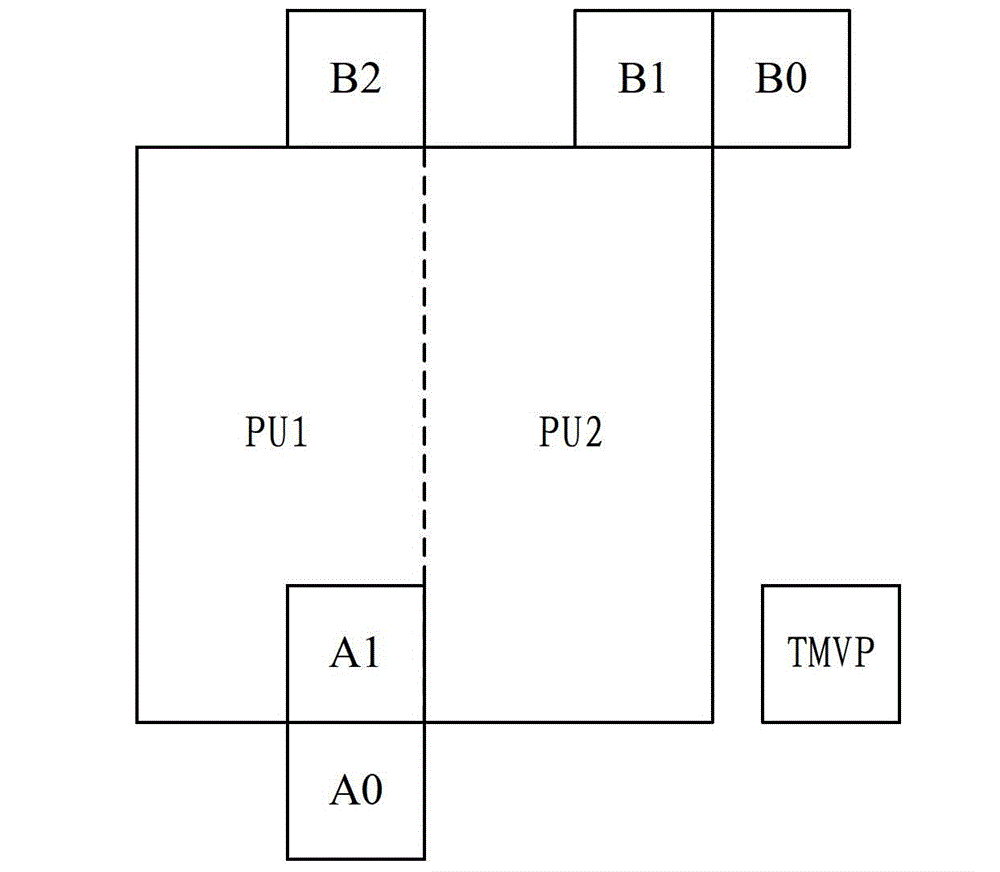

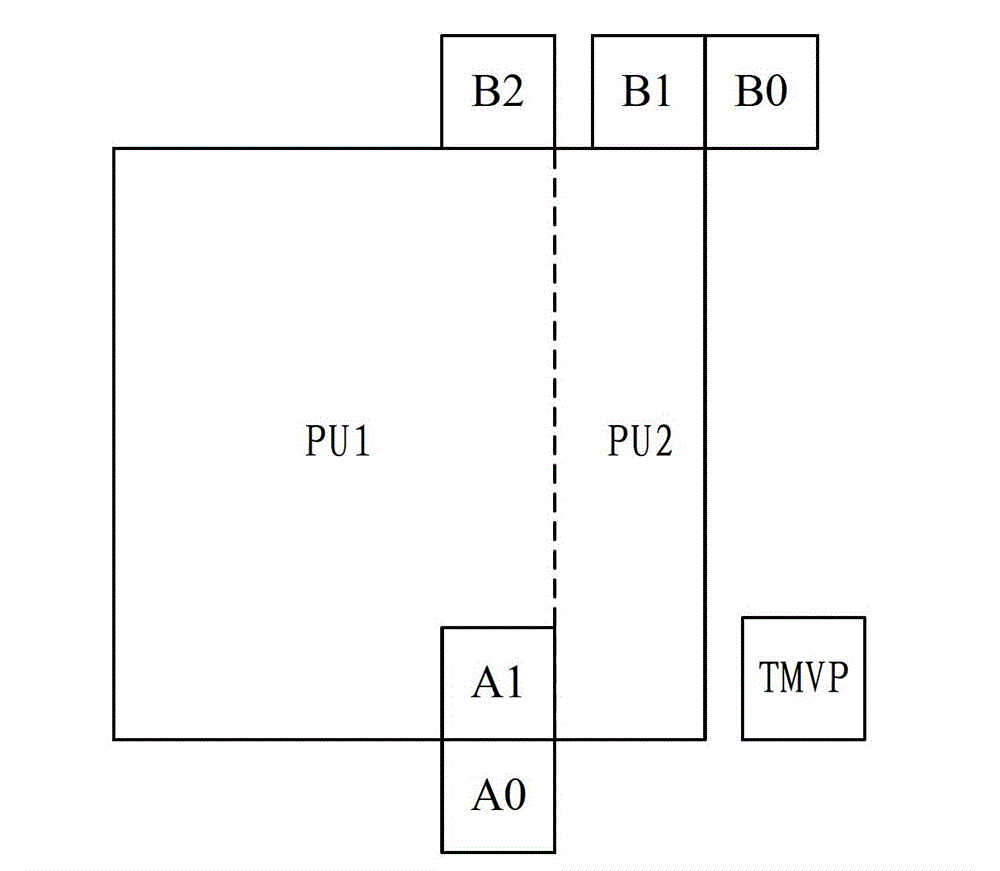

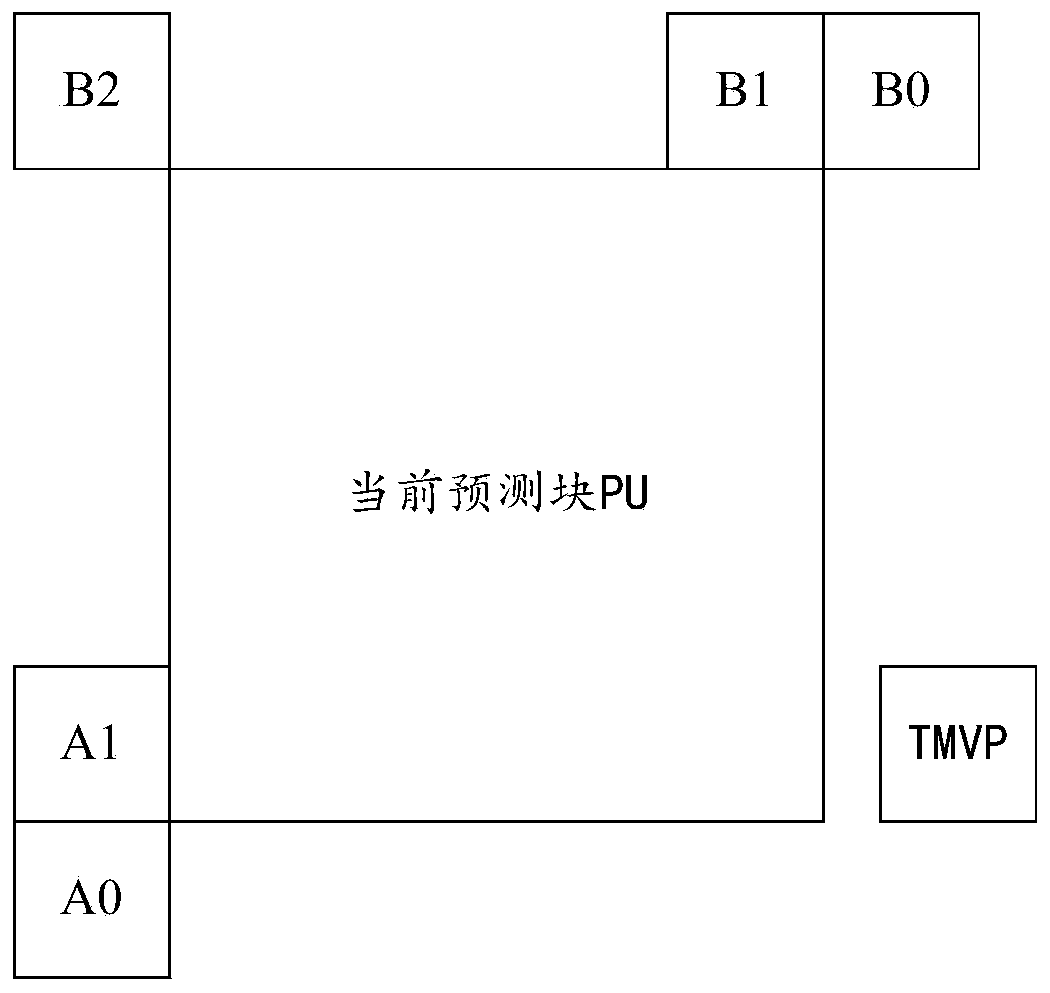

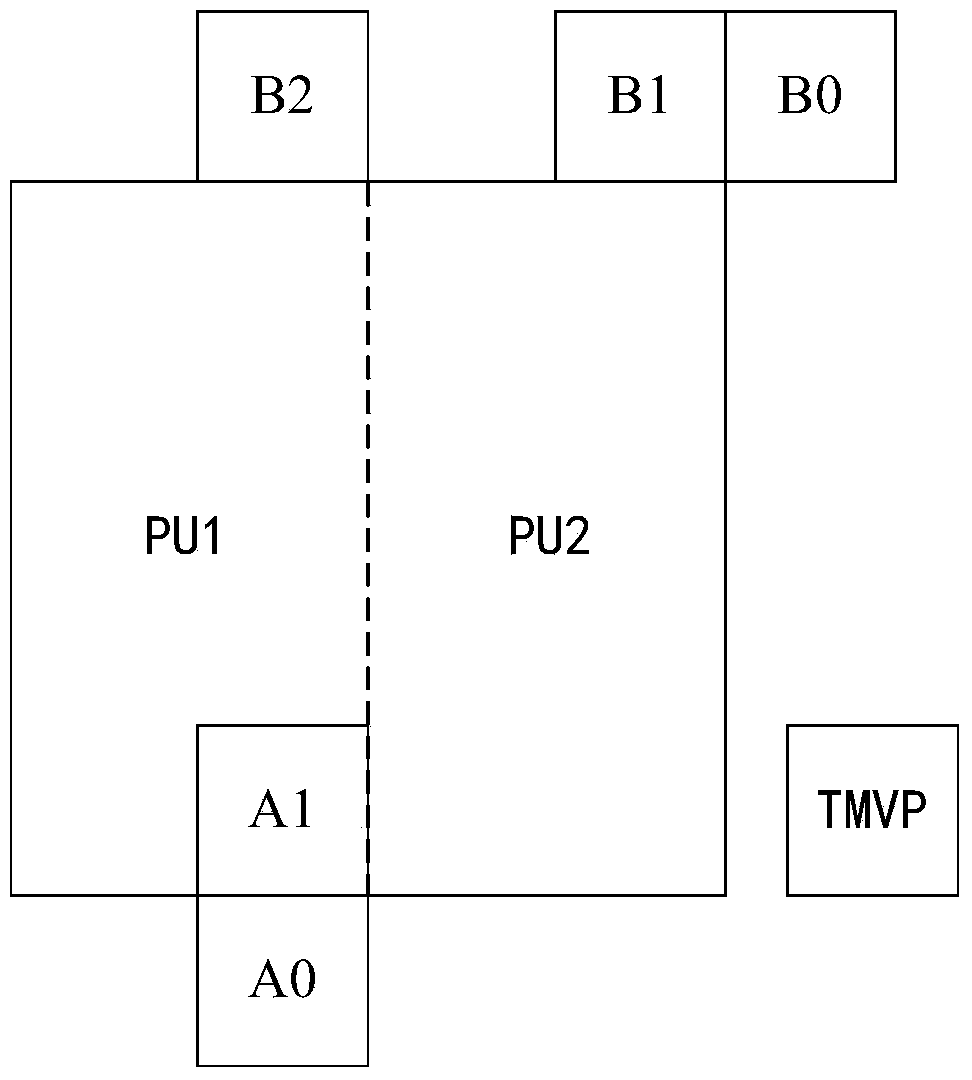

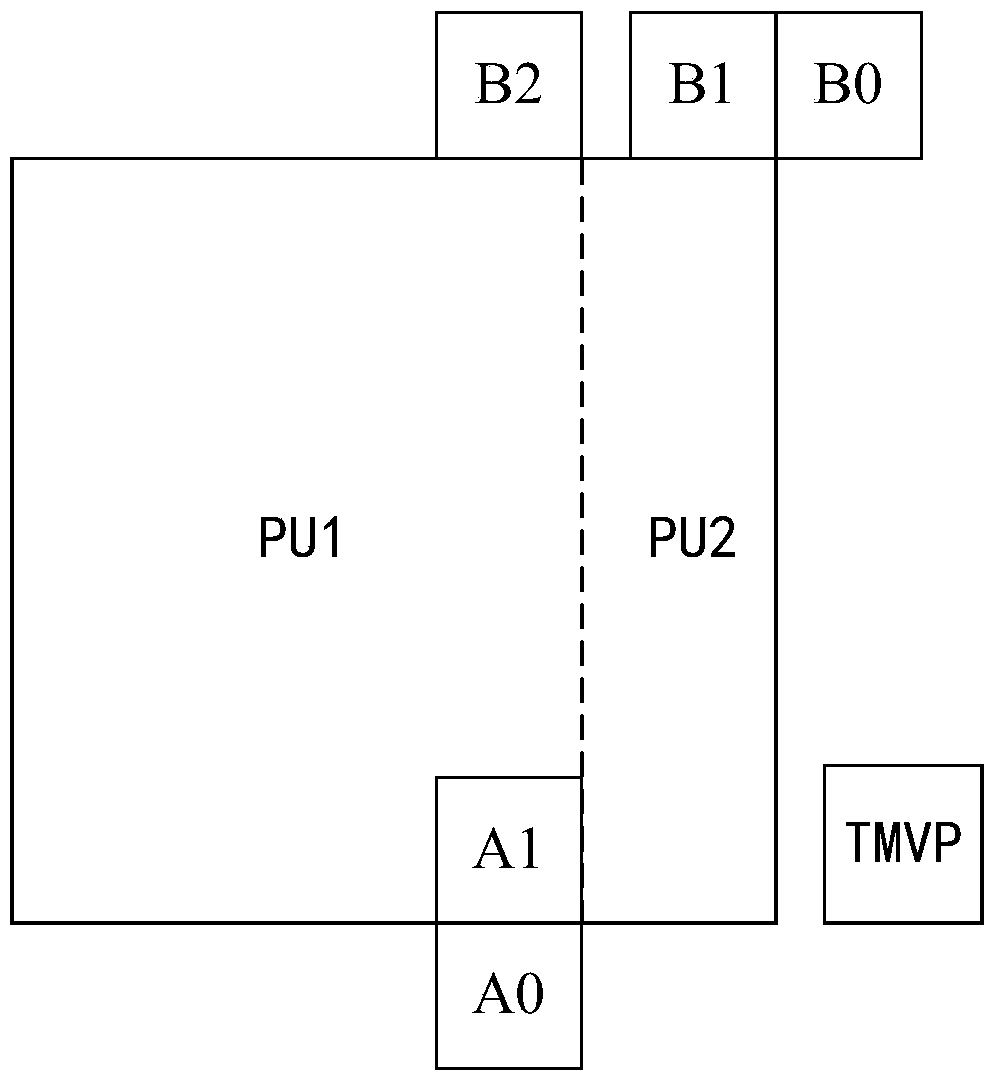

Method and device for building motion vector lists for prediction of motion vectors

ActiveCN102883163AHigh speedImprove parallel processing capabilitiesTelevision systemsDigital video signal modificationPhysical unitMotion vector

The invention provides a method and a device for building motion vector lists for prediction of motion vectors and relates to the field of video coding. The method and the device resolve the problem of adopting the serial mode to build motion vector lists of at least two physical units (PU) in one coding unit and improve parallel mode processing capability. The method and the device specifically include acquiring adjacent blocks on a current prediction block airspace, enabling a current prediction block to be located in a current coding unit, determining a proper adjacent block of the current prediction block according to the dividing mode of the current coding unit, enabling the proper adjacent block to be located outside the current coding unit, acquiring motion vector prediction value from the proper adjacent block according to the motion vector prediction value of the proper adjacent block and according to the preset sequence and adding the acquired motion vector prediction value into the motion vector lists. The method and the device can be used for building the motion vector lists.

Owner:HUAWEI TECH CO LTD

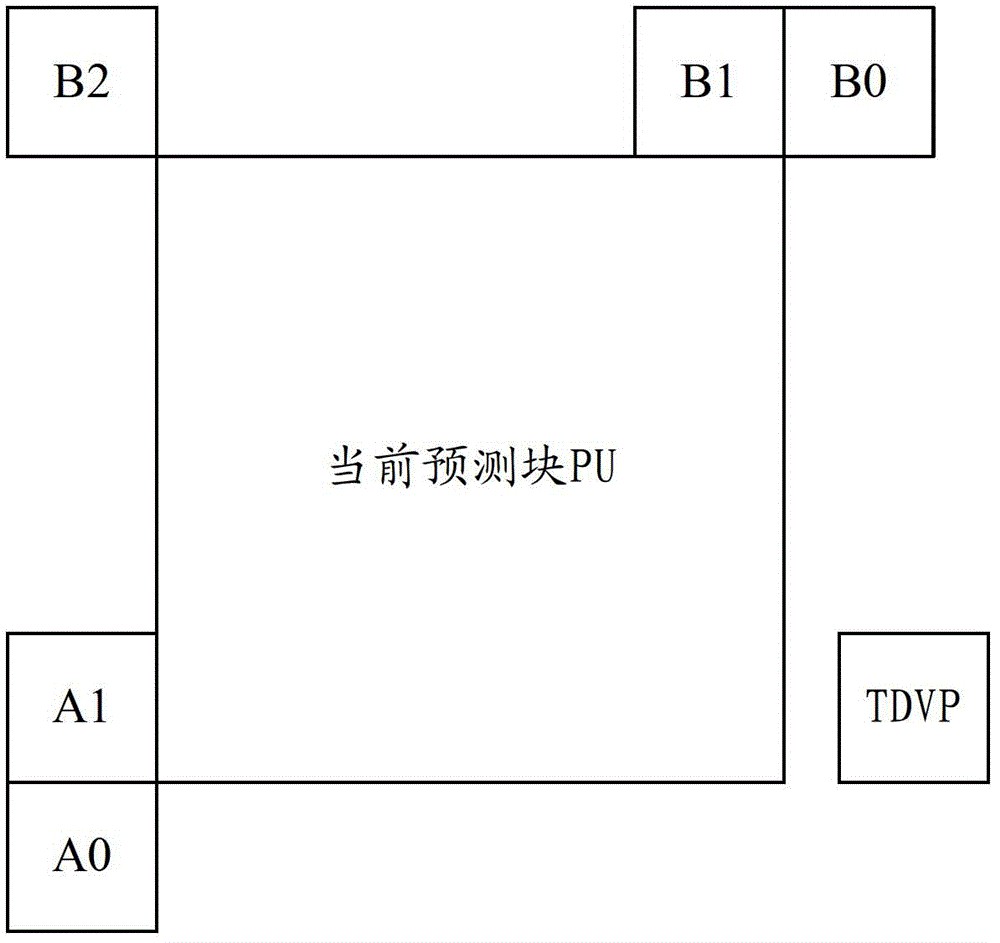

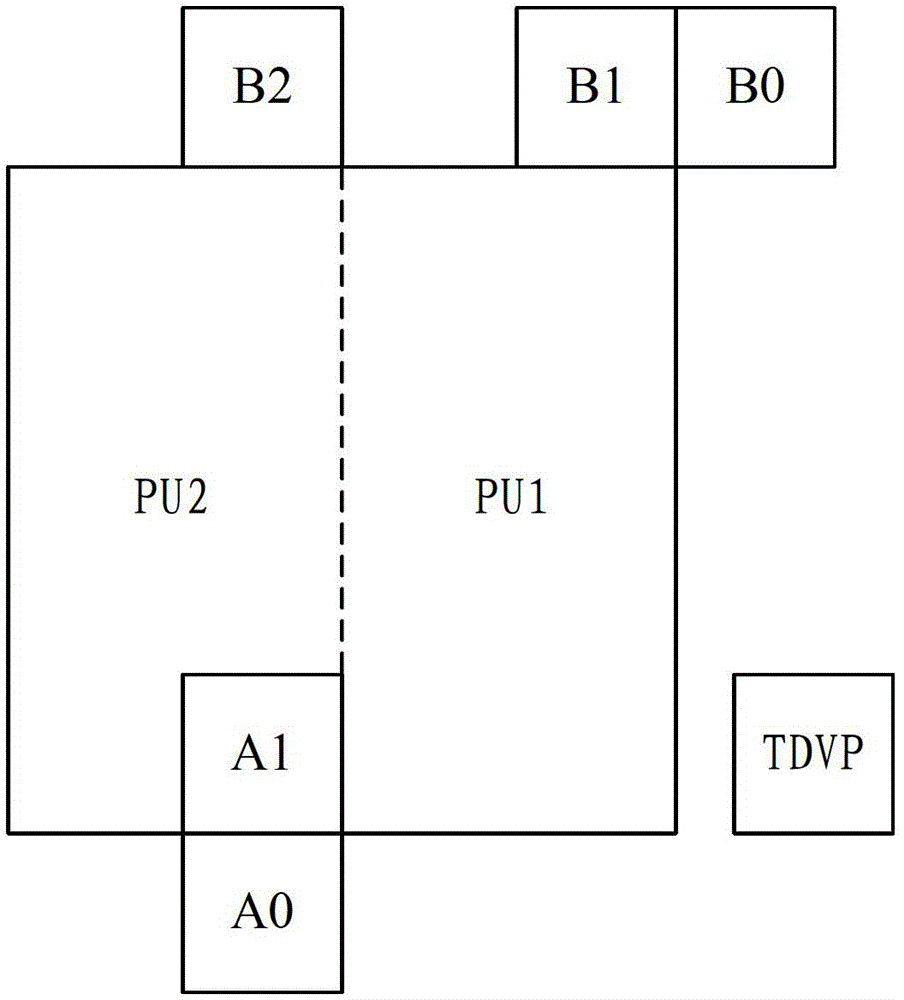

Method and device for obtaining disparity vector predictors of prediction units

InactiveCN102946535AHigh speedImprove parallel processing capabilitiesTelevision systemsDigital video signal modificationParallaxAlgorithm

The invention provides a method and a device for obtaining disparity vector (DV) predictors of prediction units (PUs), relates to the field of video coding, and achieves the effect of obtaining the DV predictors of at least two PUs in the same one coding unit (CU) by serial mode, to improve the parallel processing capability. Specifically, the method comprises the following steps: obtaining adjacent units on the current prediction unit air space; according to the division mode of the current CU, the positions of the current PUs in the current CU and the positions of the adjacent units, determining whether the adjacent units are located in the current CU; and obtaining DV predictors from the adjacent units which are not in the current CU in a preset order and stopping until a DV predictor is obtained. The method and the device can be applied to obtain disparity vector (DV) predictors.

Owner:HUAWEI TECH CO LTD

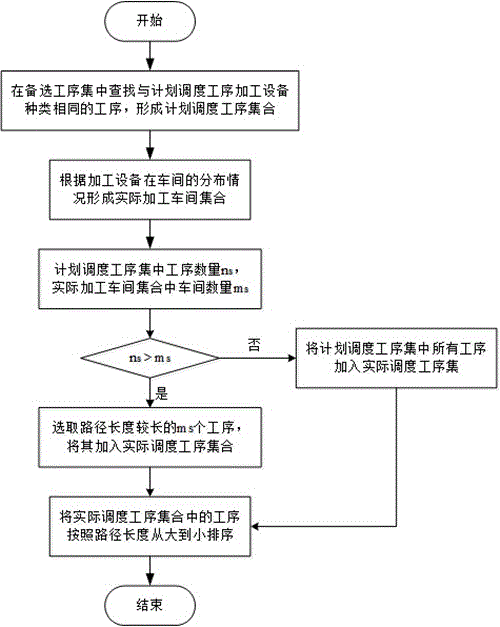

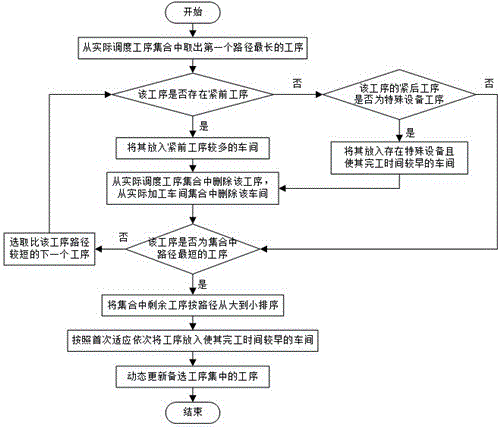

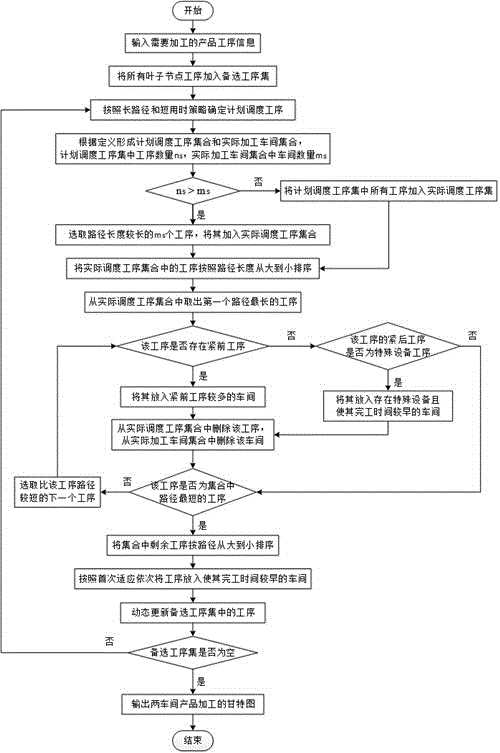

Asymmetric multi-workshop integrated dispatching method with consideration of same-kind-of-equipment process

PendingCN106651139ALoad balancingImprove parallelismResourcesTotal factory controlPath lengthAlternative process

The invention relates to an asymmetric multi-workshop integrated dispatching method with consideration of a same-kind-of-equipment process. The method comprises: all leaf nodes are added to an alternative process set; a planned dispatching process is determined from the alternative process set according to a method of selecting a long-path process and a short-time process preferably; a processing equipment type of the planned dispatching process is determined; a process identical with the processing equipment of the planned dispatching process is searched in the alternative process set; a planned dispatching process set is formed by a same-equipment process; a practical dispatching process set is determined based on a method of same-kind-of-equipment process long-path optimization method; and then according to a multi-workshop process group dispatching balancing method, processes in the practical dispatching process set are distributed to proper processing workshops, the processes in the practical dispatching process set are dispatched successively according to a descending path length order, and the process is placed into a workshop enabling a transferring frequency to be reduced preferably, so that the workshop parallelism and balancing can be improved. Therefore, the method can be applied to integrated asymmetric multi-workshop dispatching of single complex products.

Owner:HARBIN UNIV OF SCI & TECH

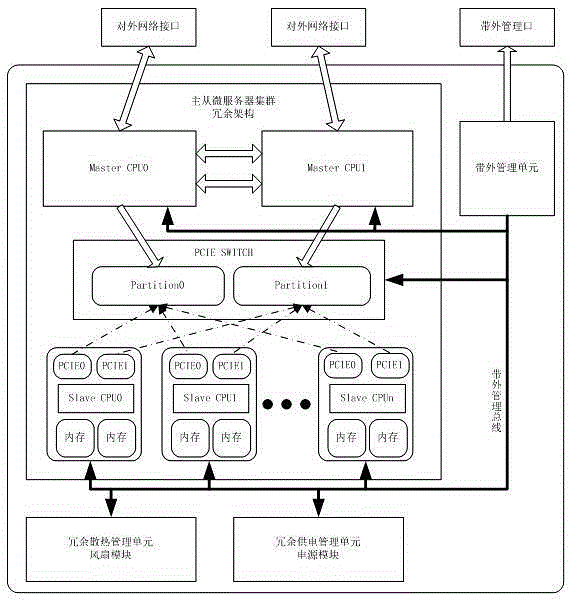

Micro server cluster system based on master-slave architecture

InactiveCN105335330AImprove latencyReduce utilizationDigital computer detailsElectric digital data processingComputer architectureEngineering

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

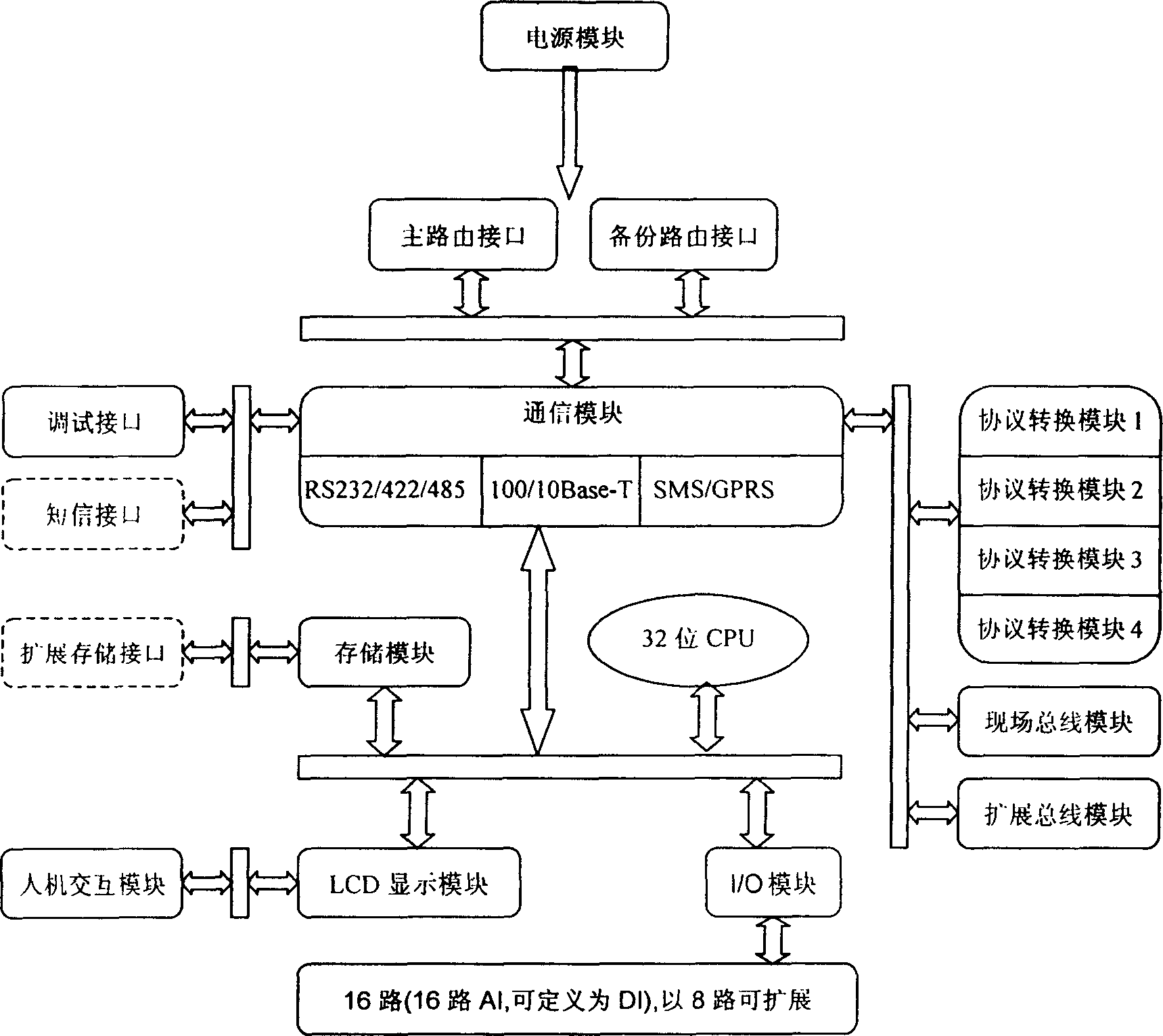

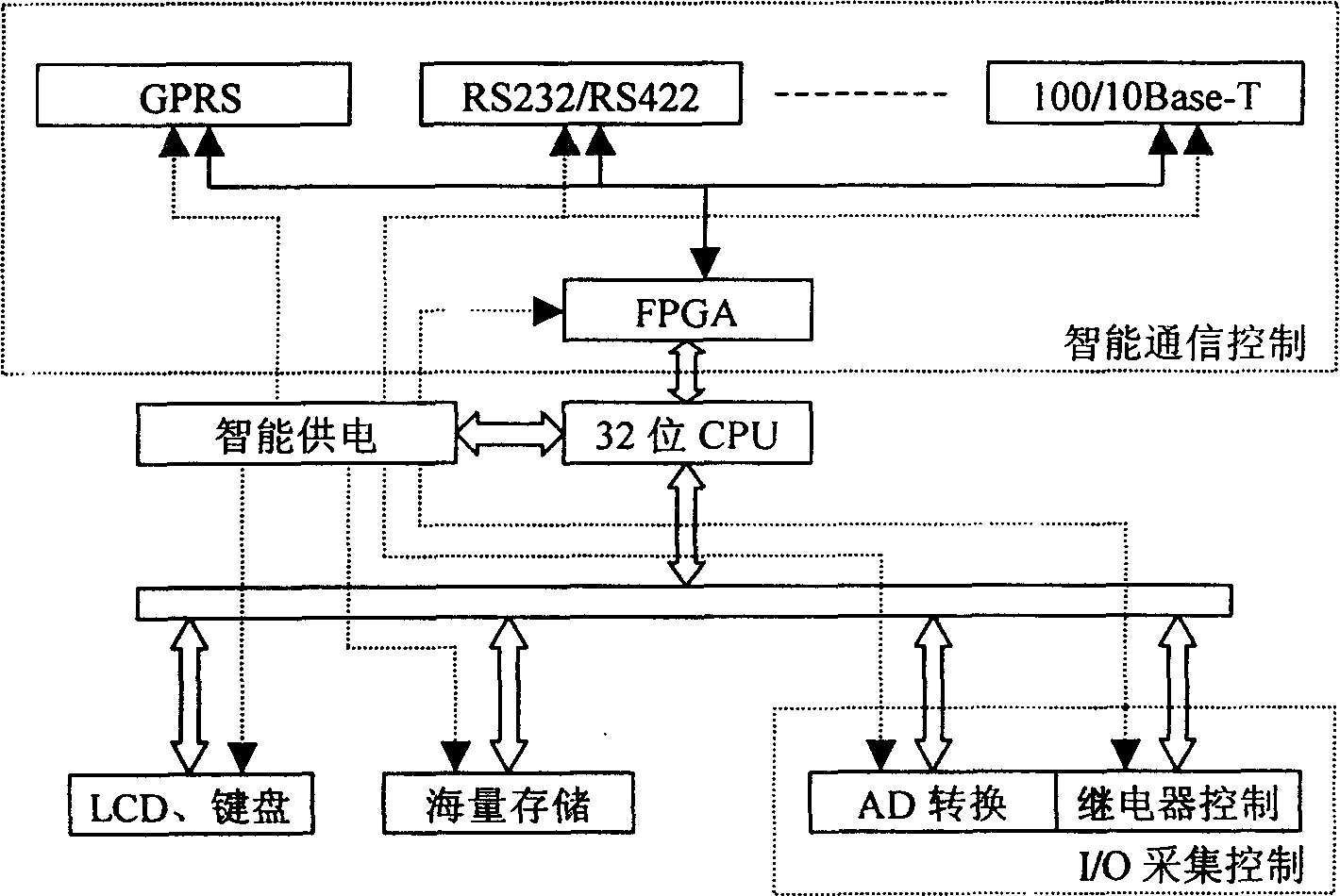

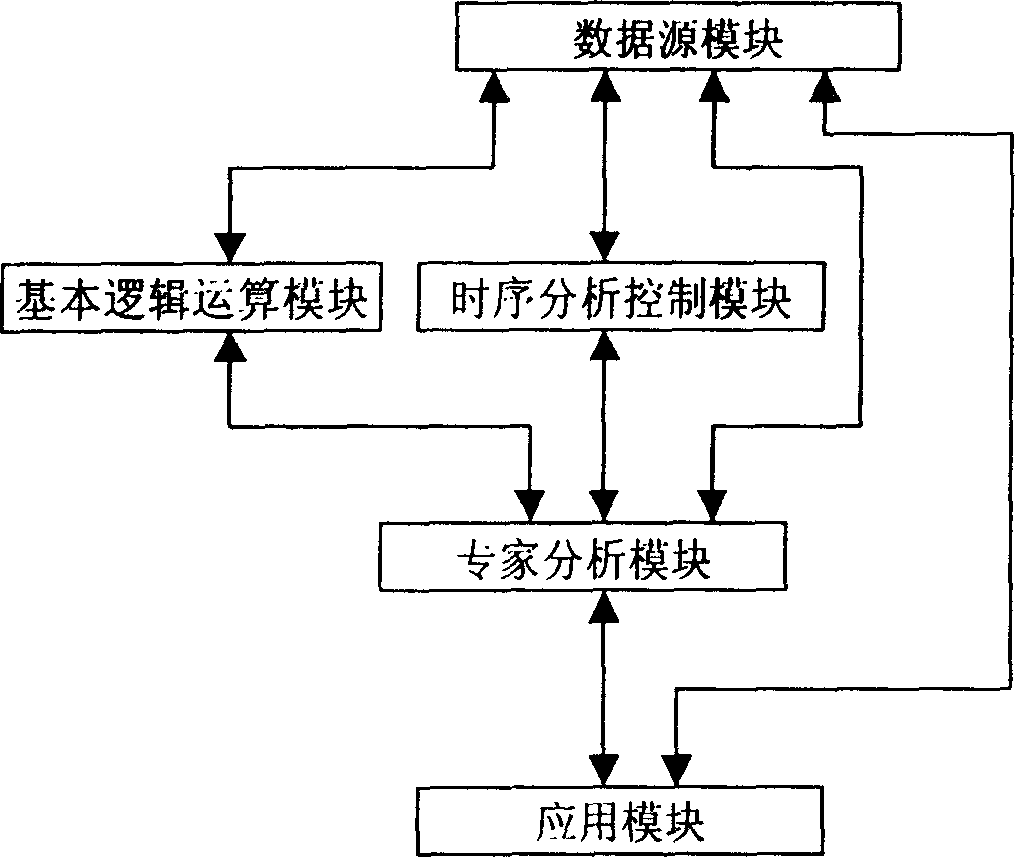

Power and environment concentrated monitoring management system

InactiveCN1889468AWill not affect normal workTo achieve the purpose of energy savingData switching networksLiquid-crystal displayModularity

A centralized monitoring and managing system of power or environment comprises display window with LCD; structure of input keyboard; modularized electronic circuit board being set in structure and being set with bus module, communication module, protocol conversion module, LCD display module, storage module, multipath I / O module and power supply module. It is featured as integrating communication, protocol conversion, I / O collection, bus convergence and liquid crystal display in a unified body for saving energy and resource.

Owner:上海集成通信设备有限公司

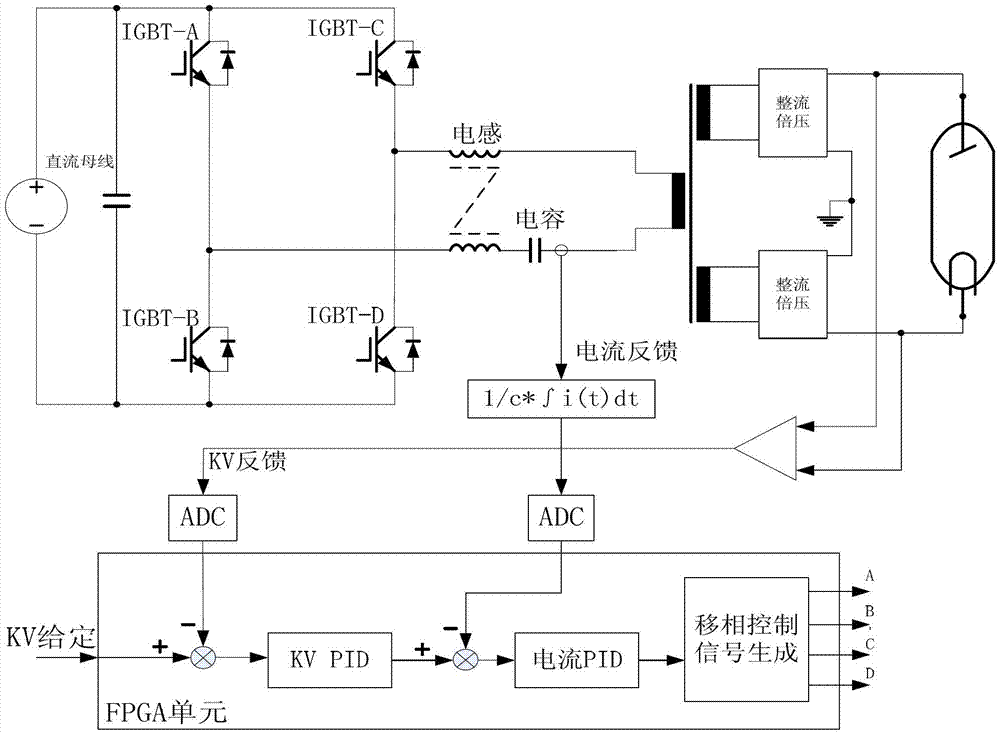

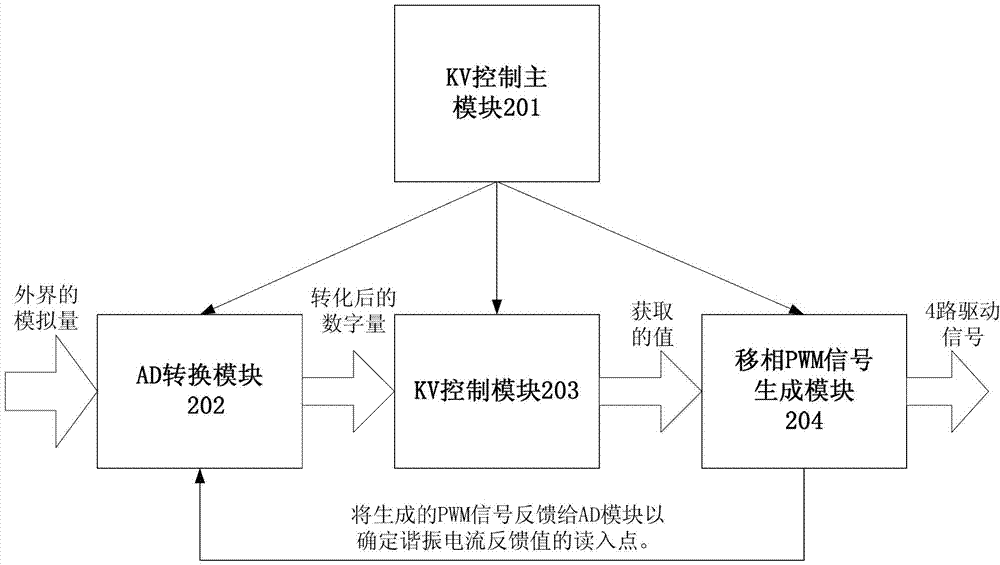

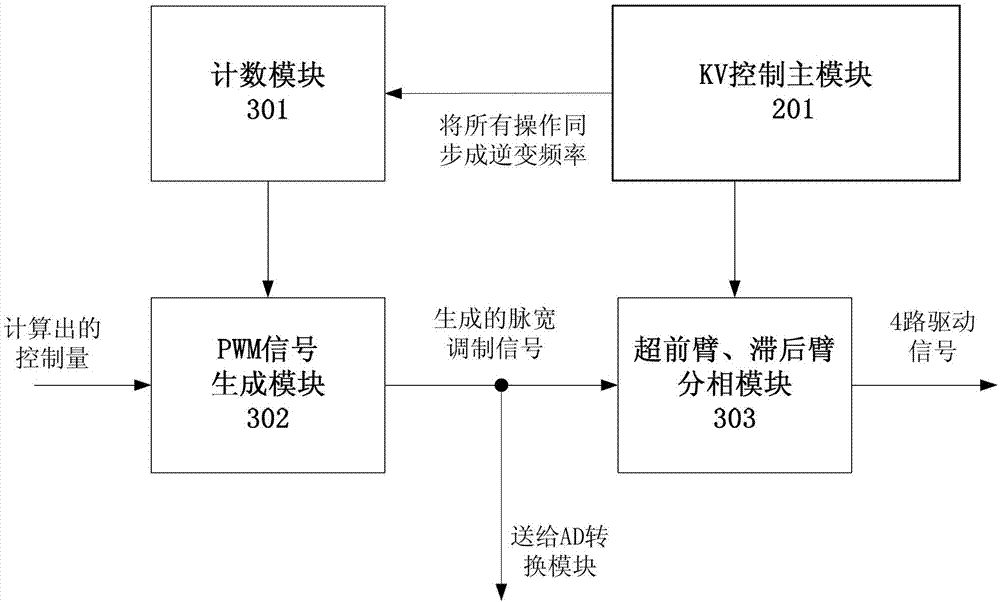

Kilovolt (KV) control method and system adopting digital technique

InactiveCN103208924AAbundant hardware resourcesImprove parallel processing capabilitiesDc-dc conversionElectric variable regulationLoop controlControl manner

The invention provides a kilovolt (KV) control method and system adopting a digital technique. The KV control system comprises a KV closed-loop control system and a phase-shifting pulse-width modulation (PWM) signal generation module. The KV closed-loop control system comprises an outer ring and an inner ring, wherein the outer ring adopts KV closed-loop control, and the inner ring adopts inversion current effective value closed-loop control. The KV closed-loop control system and the phase-shifting PWM signal generation module are achieved through a field programmable gate array (FPGA) unit. The FPGA unit comprises a KV control main program module, an analog-to-digital (AD) conversion module, a KV control unit and a phase-shifting PWM signal generation module, wherein the four modules achieve KV double closed-loop control together. The KV closed-loop control mode includes: reading KV feedback values and inversion current effective values for once in each PWM period, and obtaining the pulse width values to be output in the next PWM period by adopting a proportional integral derivative (PID) control flow according to the deviation between KV reference values and the KV feedback values and the inversion current effective values. By means of the KV control method and system, the problem existed in a KV control circuit of a high voltage power supply simulation technique can be solved, and the KV closed-loop control effect is ensured to be in accordance with the KV closed-loop control effect of an analog circuit under the double-loop control condition.

Owner:NEUSOFT MEDICAL SYST CO LTD +1

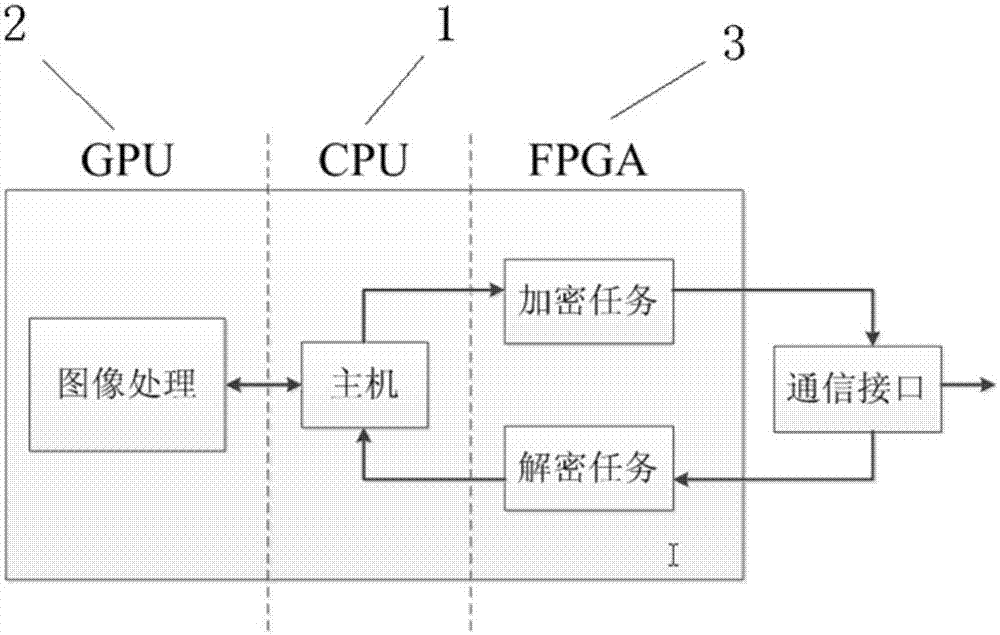

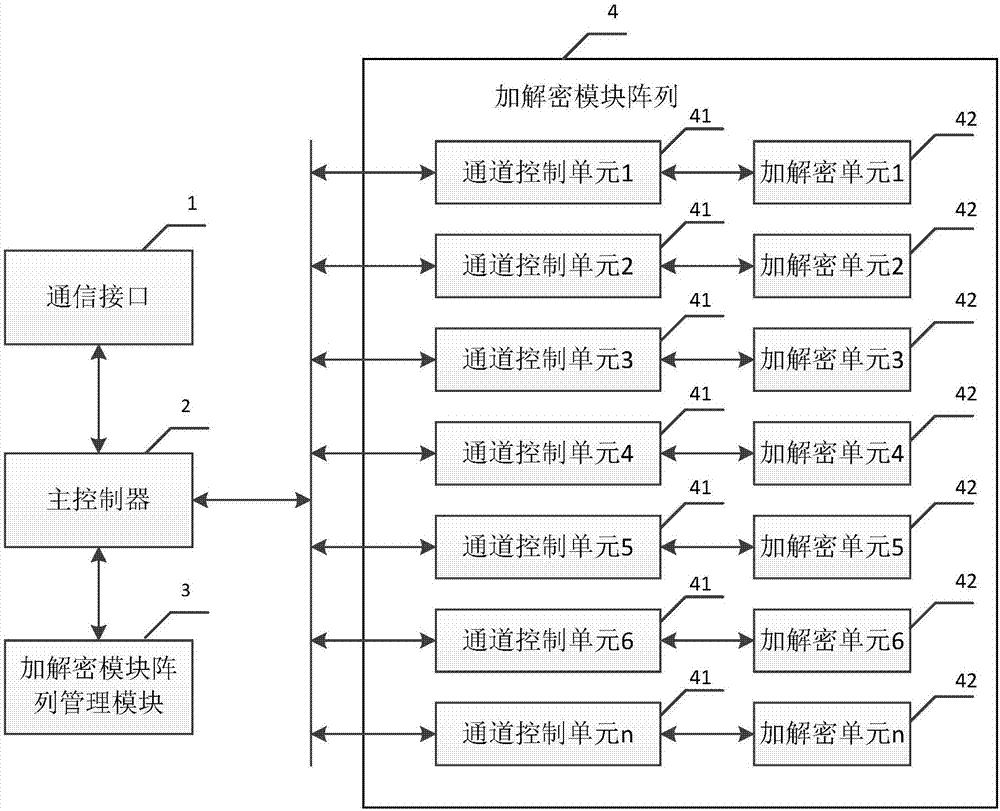

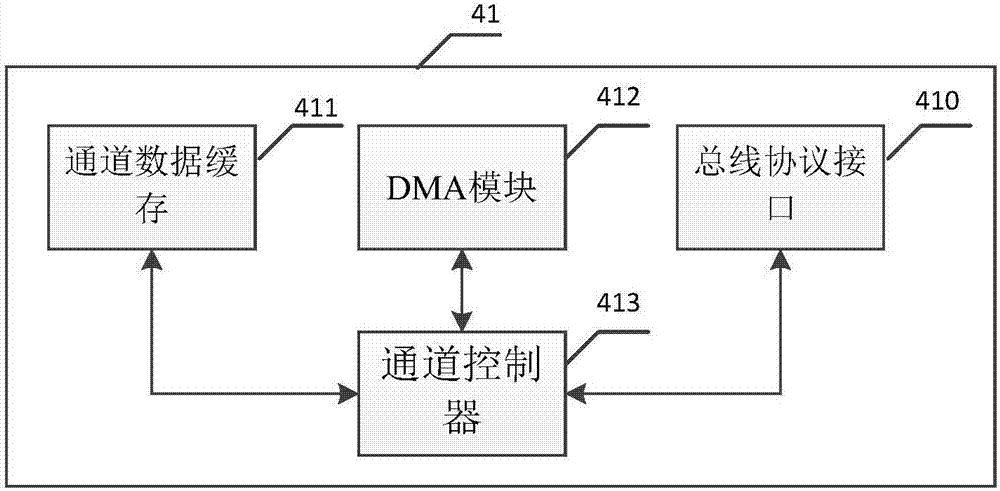

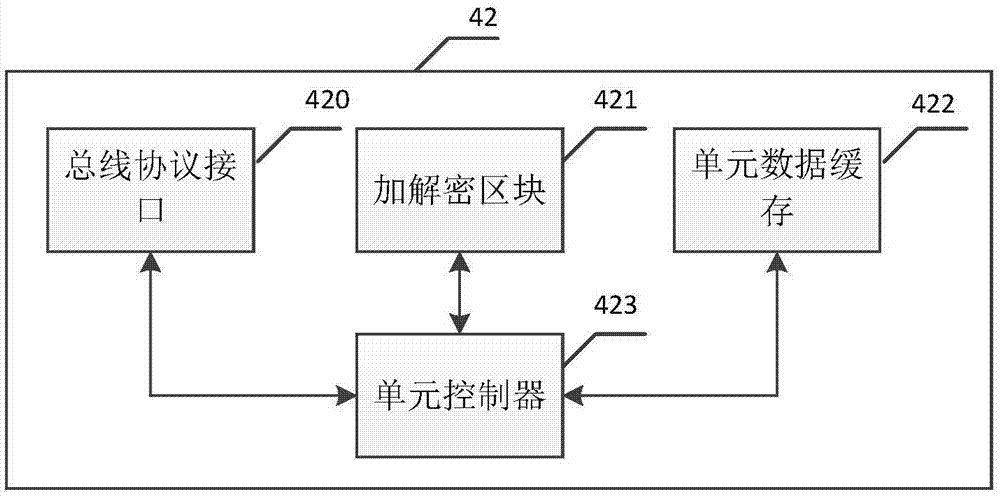

High-speed encryption and decryption device composed of encryption and decryption module array

ActiveCN107256363AIncrease the scale of operationsImprove parallel processing capabilitiesMemory architecture accessing/allocationDigital data protectionCommunication interfaceState management

The invention discloses a high-speed encryption and decryption device composed of an encryption and decryption module array. The device comprises a communication interface, an encryption and decryption array management module used for managing resource allocation and states of all encryption and decryption units in the encryption and decryption module array, a master controller and the encryption and decryption module array, wherein the master controller is used for sending an encryption and decryption instruction to corresponding channel control units according to the running states of all the encryption and decryption units and identity information carried in an input encryption and decryption instruction, outputting data subjected to encryption and decryption from the corresponding encryption and decryption units according to identity information carried in an output instruction and returning the data to a computer host; and the encryption and decryption module array comprises multiple groups of encryption and decryption modules, and each group of encryption and decryption modules comprises one channel control unit and the encryption and decryption units connected with the channel control unit in a one-to-one correspondence mode through a bus protocol interface. Through the device, the operation scale of parallel encryption and decryption is enlarged, encryption and decryption efficiency is improved, and arrangement cost is lower by the adoption of an array mode.

Owner:SAGE MICROELECTRONICS CORP

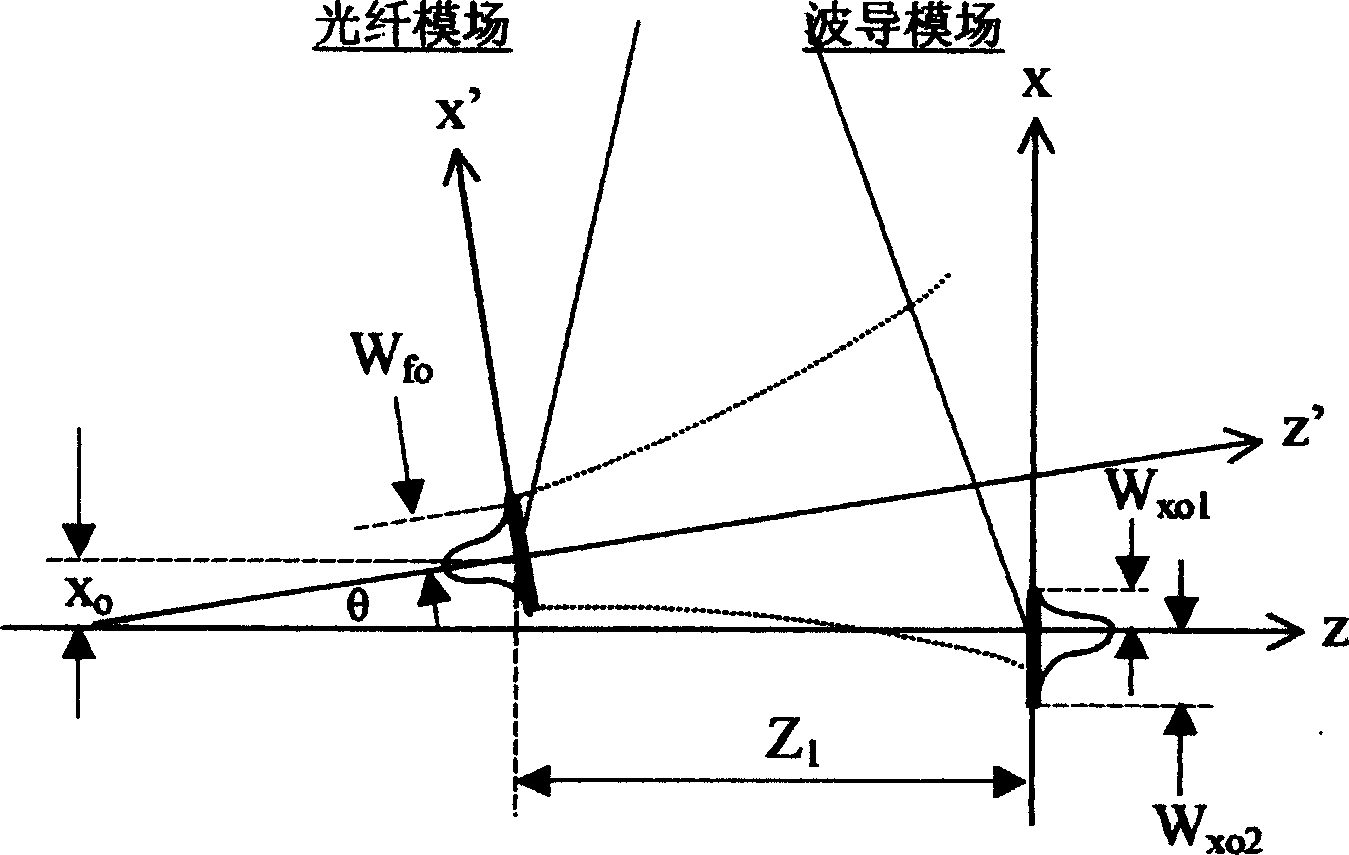

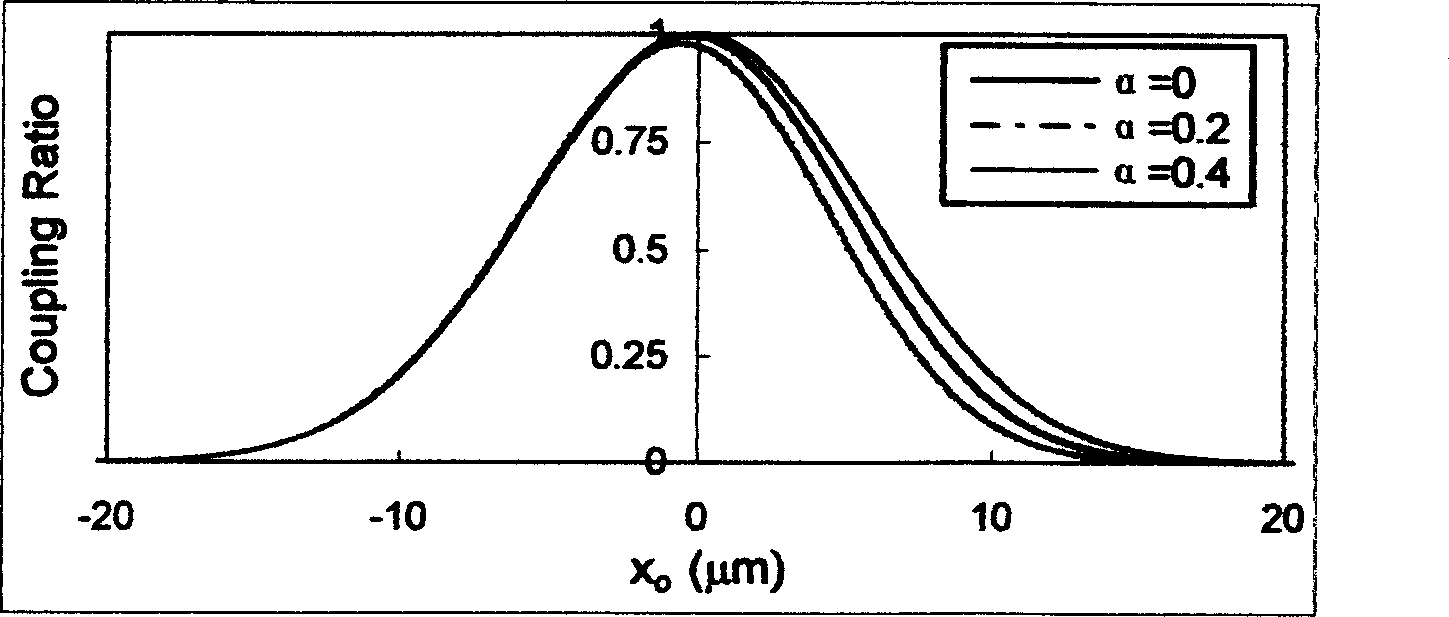

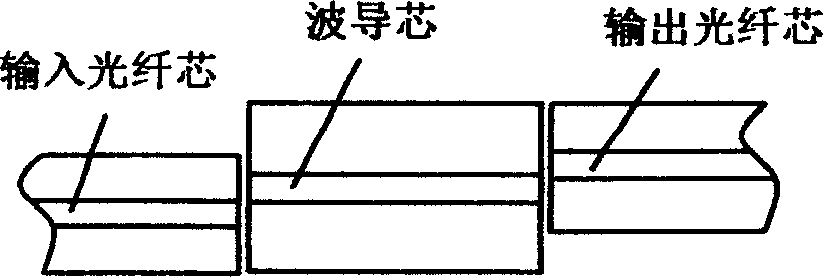

Waveguide-optical fiber automatic core adjusting method based on genetic algorithm and device thereof

InactiveCN1570687AImprove robustnessLow robustnessCoupling light guidesFibre transmissionIliofemoral ligamentOptical axis

This invention discloses a method and an apparatus for automatic regulating core with waveguide optical fiber based on genetic algorism, which is characterized by forming mapping between regulating-core physical parameter and genetic gene model, describing a certain relative place between waveguide optical axis and fibre-optical optical axis when regulating core by individual concept, taking coupling efficiency as adapting function to judge and adjusting constantly the related place between waveguide and optical fiber through generations of genetic manipulation such as selecting regeneration, cross-over, variation according to genetic principle about survival of the fittest until astringing in the optimal coupling place, and adopting up-rush method adjusting four-axis in little neighborhood when realizing the iliofemoral ligament of waveguide and optical fiber is lower than 2dB to find the optimum place between waveguide and optical fiber and finish the process

Owner:UNIV OF SHANGHAI FOR SCI & TECH

Method and device for setting up motion vector list for motion vector prediction

ActiveCN103841425AHigh speedImprove parallel processing capabilitiesDigital video signal modificationMotion vectorParallel processing

The invention provides a method and device for setting up a motion vector list for motion vector prediction, and relates to the field of video coding. The problem of how to set up the motion vector lists of at least two PUs in the same coding unit in a serial mode is solved, and the parallel processing capacity is improved. The method can specifically comprise the steps that adjacent blocks in the space domain of a current predication block are acquired, and the current predication block is located in the current coding unit; the proper adjacent block of the current predication block is determined according to the division mode of the current coding unit, and the proper adjacent block is located outside the current coding unit; a motion vector predication value is acquired from the proper adjacent block according to the motion vector predication value of the proper adjacent block and the preset sequence, and the acquired motion vector predication value is added into the motion vector list. The method and device can be used for setting up the motion vector list.

Owner:HUAWEI TECH CO LTD

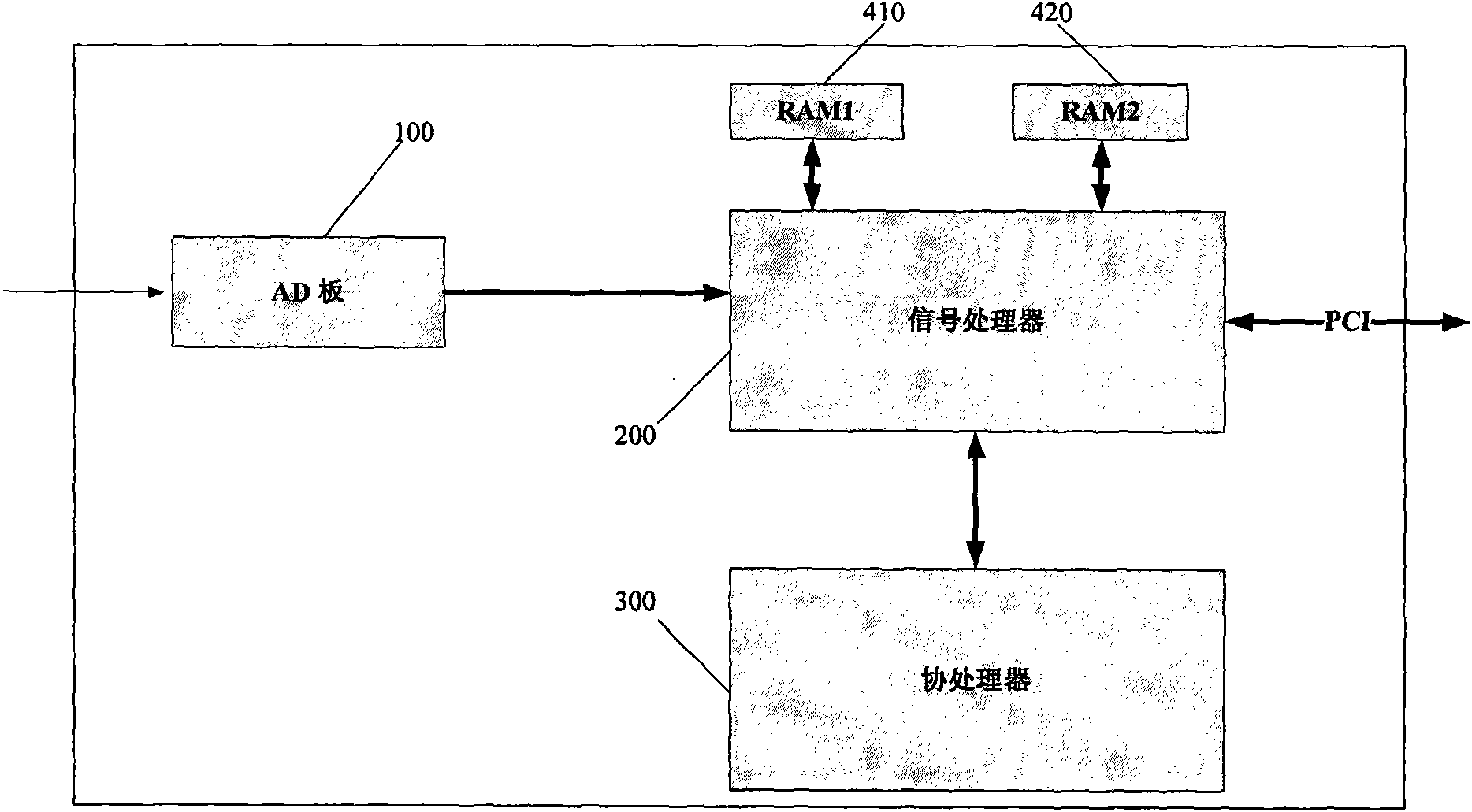

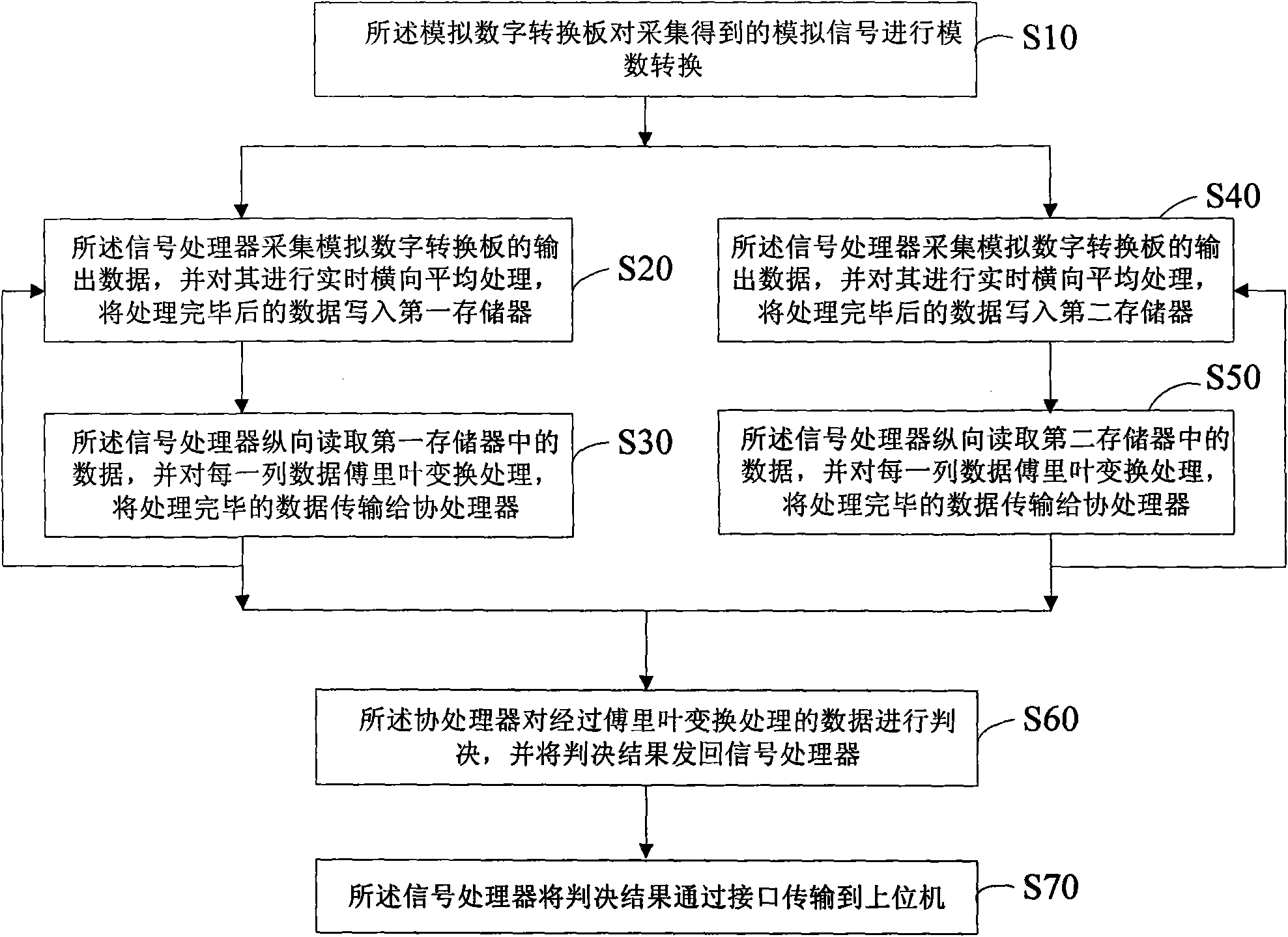

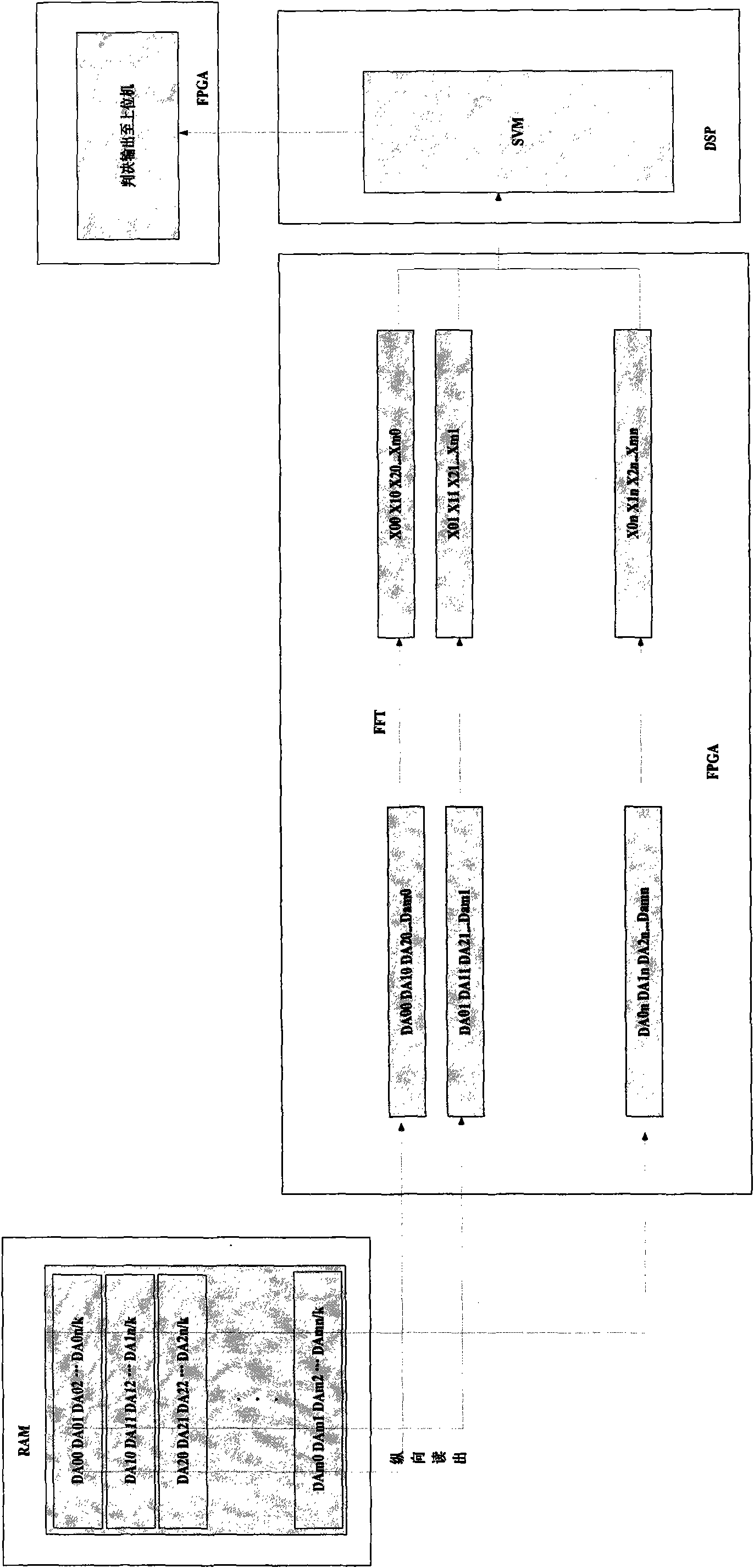

Implementation method of optical fiber vibration processor system

InactiveCN101639963AImprove parallel processing capabilitiesProcessing speedConcurrent instruction executionBurglar alarmHandling systemParallel processing

The invention provides an implementation method of an optical fiber vibration processor system, which is applied to an electronic signal processing system of a positioning type distributed vibration sensing system in the boundary security protection field and can effectively give an alarm for an intrusion event. In the invention, the large-scale and high-performance combined structure of FPGA andDSP is adopted. The scheme has the advantages that the FPGA not only has strong parallel processing capacity but also has quick processing speed (hardware processing), thus algorithms having large operating amount or rigorous speed requirements are implemented in the FPGA, and the DSP has the advantage of processing complicated algorithms (such as SVM algorithm). Thus, by combining the FPGA and the DSP, the invention can greatly improve the processing performance of the system, simultaneously meets the real-time requirement of the system and reduces the rate of missing report.

Owner:江西华神智能物联技术有限公司