Patents

Literature

899 results about "Alternative methods" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Implantation system for annuloplasty rings

InactiveUS7485142B2Good coaptation of leafletImprove hemodynamic functionSuture equipmentsSurgical needlesEffective lengthShape-memory alloy

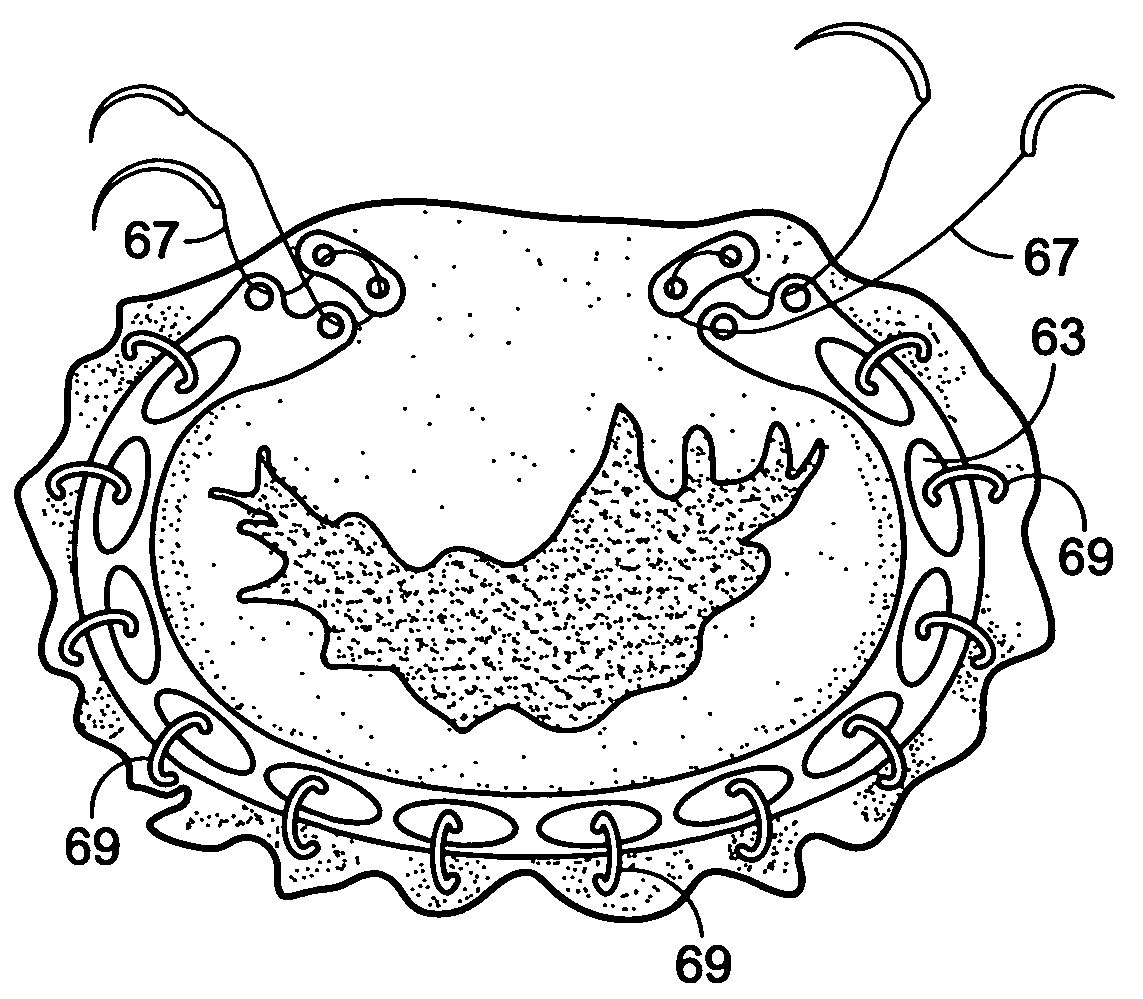

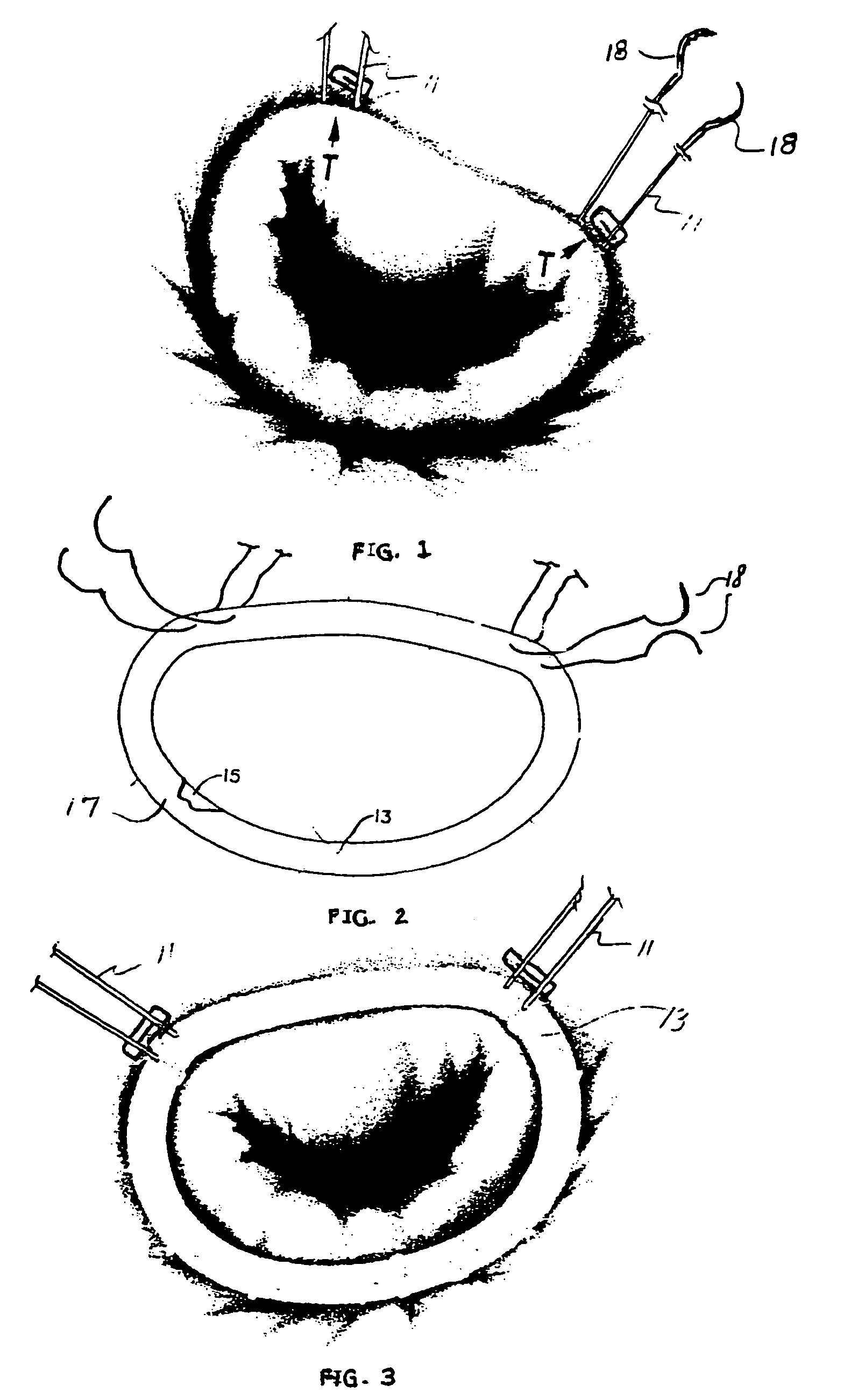

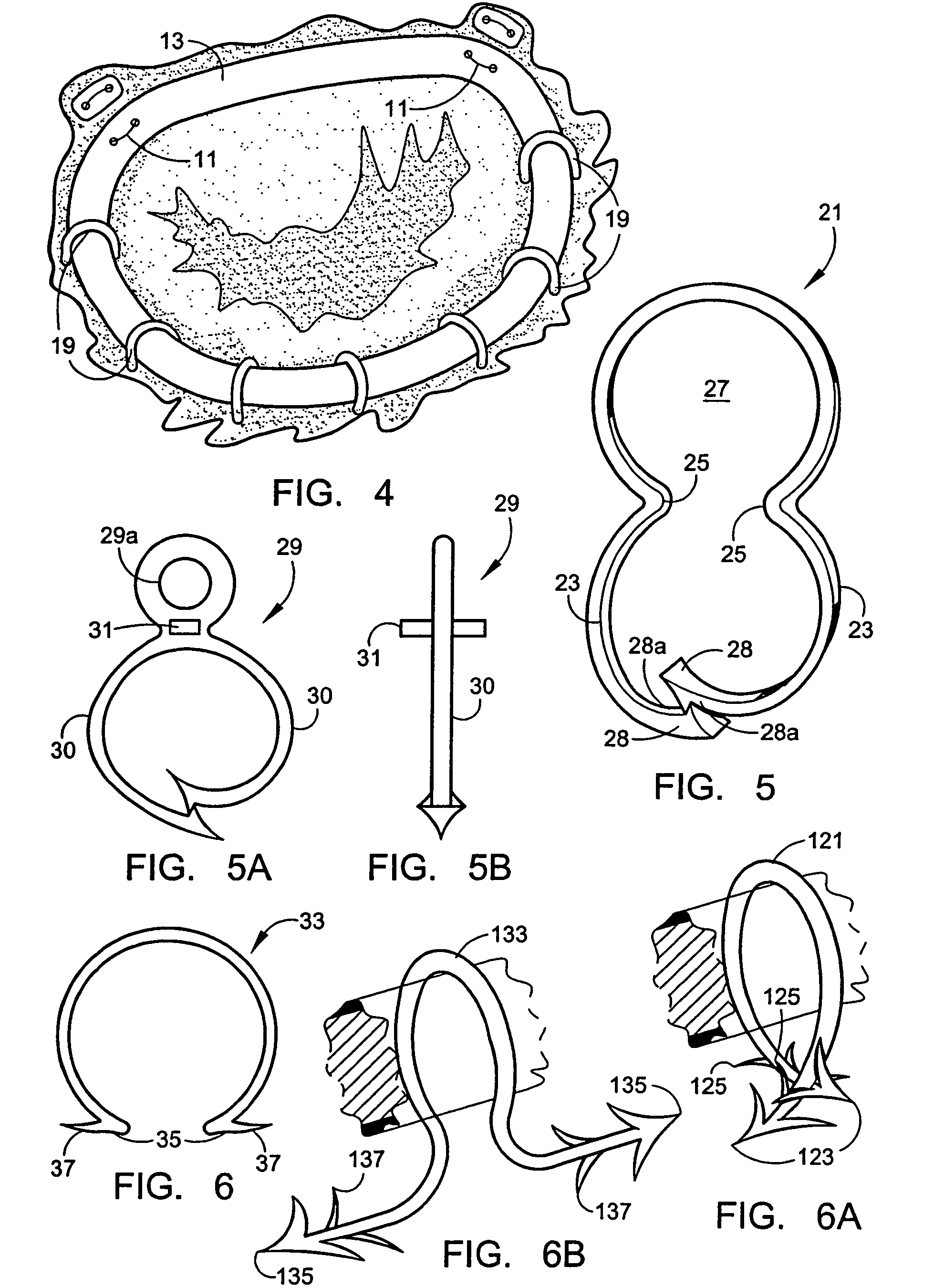

Methods for reconfiguring an atrioventricular heart valve that may use systems comprising a partial or complete annuloplasty rings proportioned to reconfigure a heart valve that has become in some way incompetent, a pair of trigonal sutures or implantable anchors, and a plurality of staples which may have pairs of legs that are sized and shaped for association with the ring at spaced locations along its length. These systems permit relative axial movement between the staples and the ring, whereby a patient's heart valve can be reconfigured in a manner that does not deter subtle shifting of the native valve components. Shape-memory alloy material staples may have legs with free ends that interlock following implantation. Annuloplasty rings may be complete or partial and may be fenestrated. One alternative method routes a flexible wire, preferably of shape-memory material, through the bights of pre-implanted staples. Other alternative systems use linkers of shape-memory material having hooked ends to interengage with staples or other implanted supports which, following implantation, decrease in effective length and pull the staples or other supports toward one another so as to create desired curvature of the reconfigured valve. These linkers may be separate from the supports or may be integral with them and may have a variety of shapes and forms. Various of these systems may be implanted non-invasively using a delivery catheter.

Owner:QUICKRING MEDICAL TECH LTD

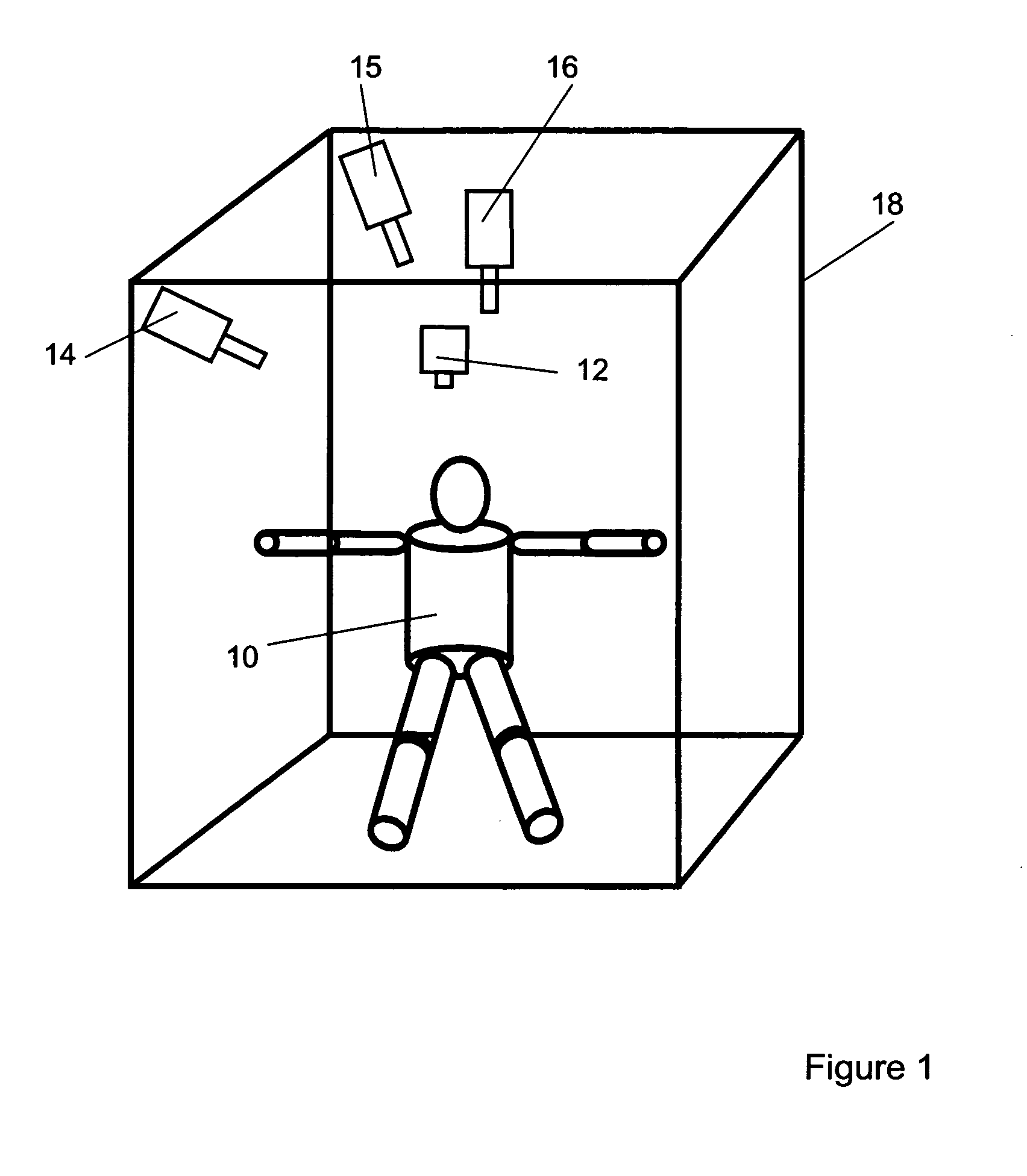

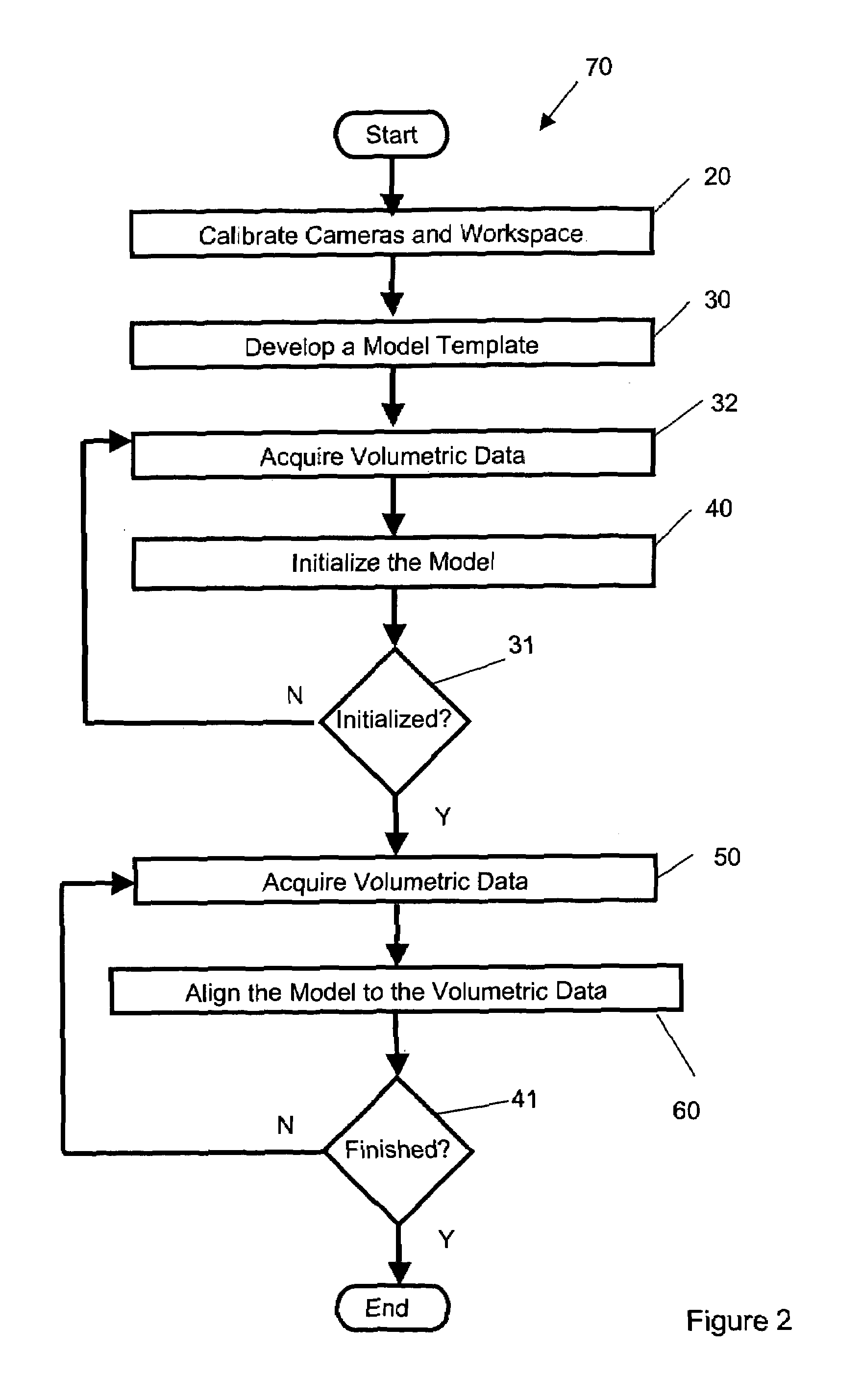

Real time markerless motion tracking using linked kinematic chains

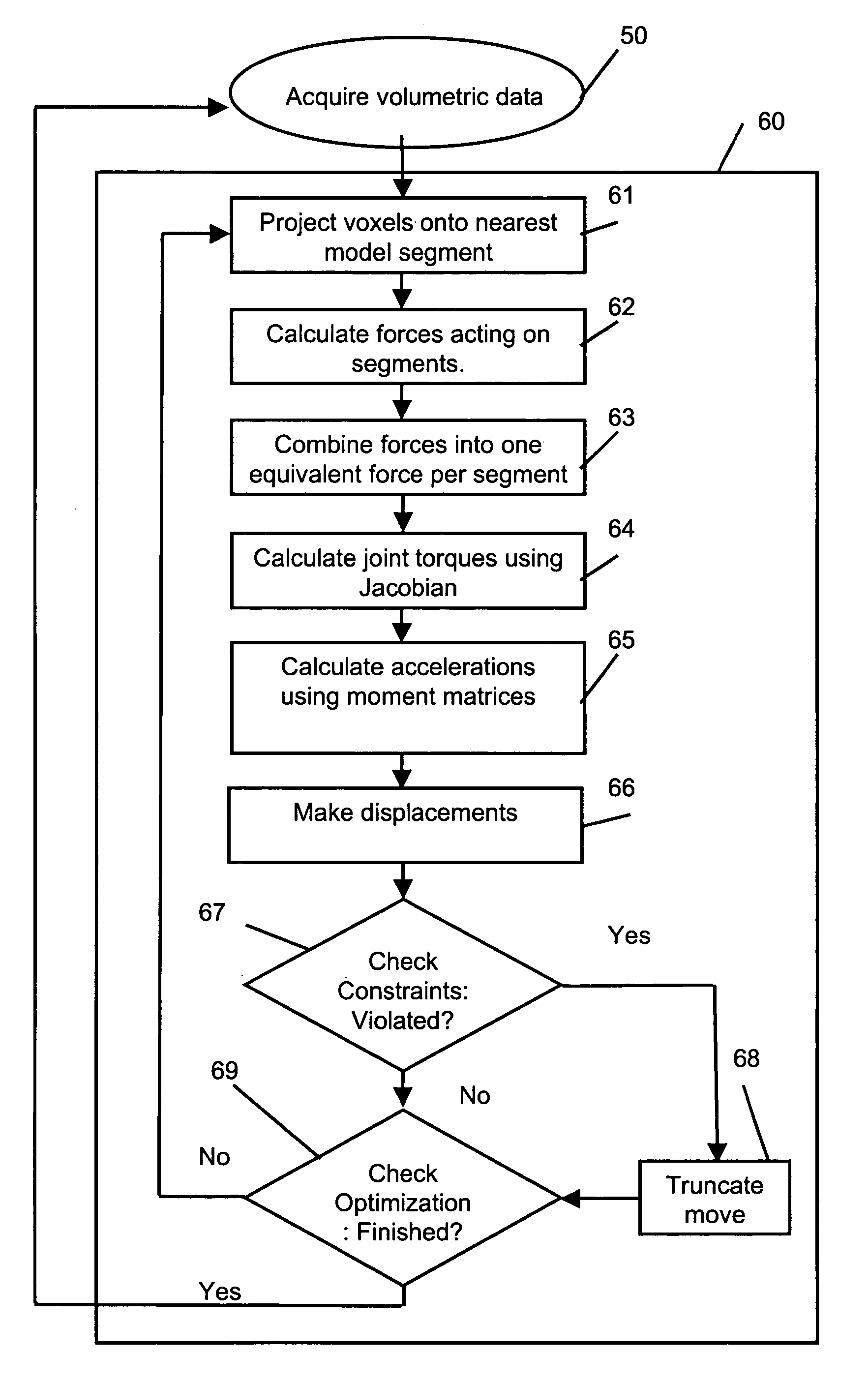

A markerless method is described for tracking the motion of subjects in a three dimensional environment using a model based on linked kinematic chains. The invention is suitable for tracking robotic, animal or human subjects in real-time using a single computer with inexpensive video equipment, and does not require the use of markers or specialized clothing. A simple model of rigid linked segments is constructed of the subject and tracked using three dimensional volumetric data collected by a multiple camera video imaging system. A physics based method is then used to compute forces to align the model with subsequent volumetric data sets in real-time. The method is able to handle occlusion of segments and accommodates joint limits, velocity constraints, and collision constraints and provides for error recovery. The method further provides for elimination of singularities in Jacobian based calculations, which has been problematic in alternative methods.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

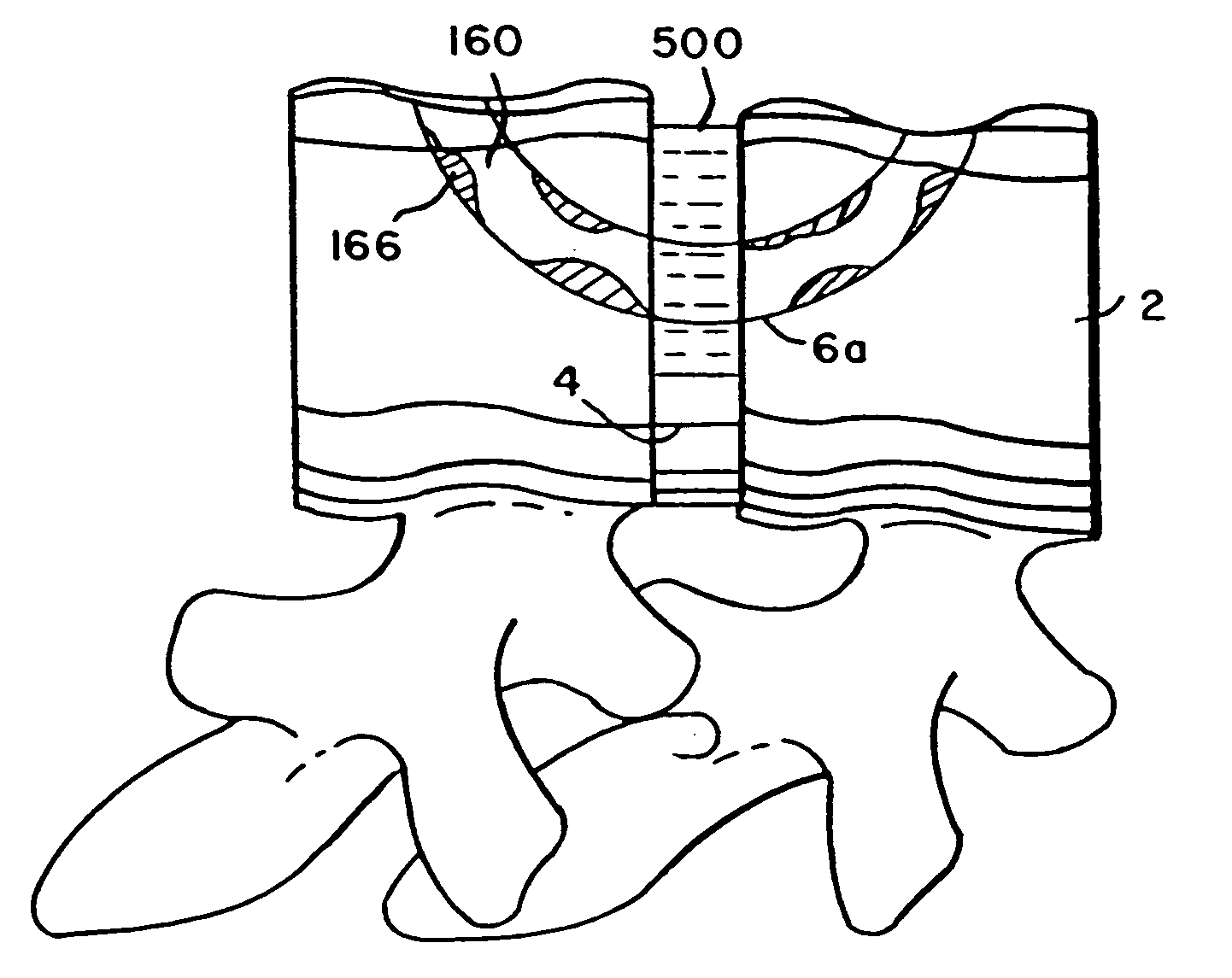

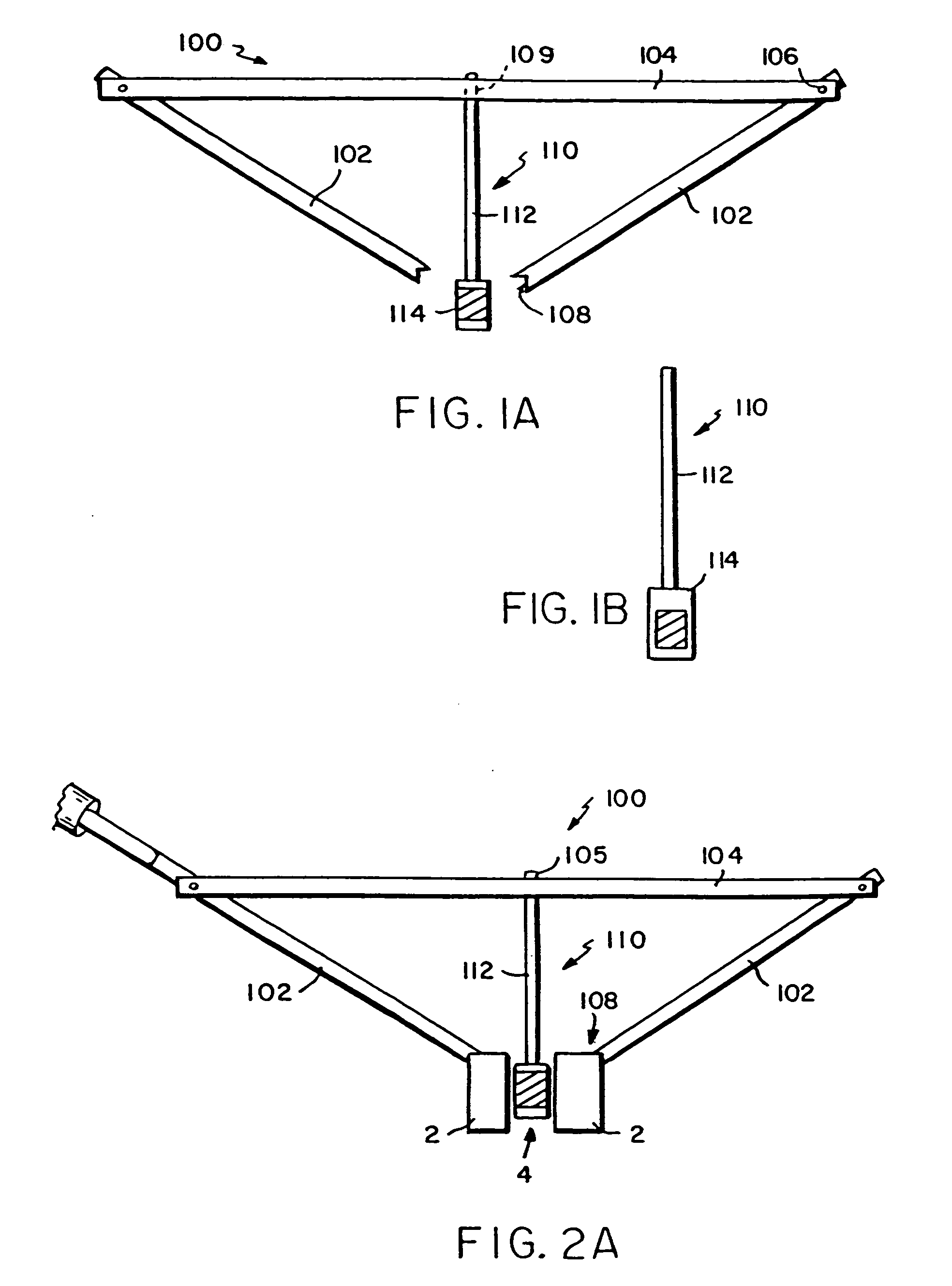

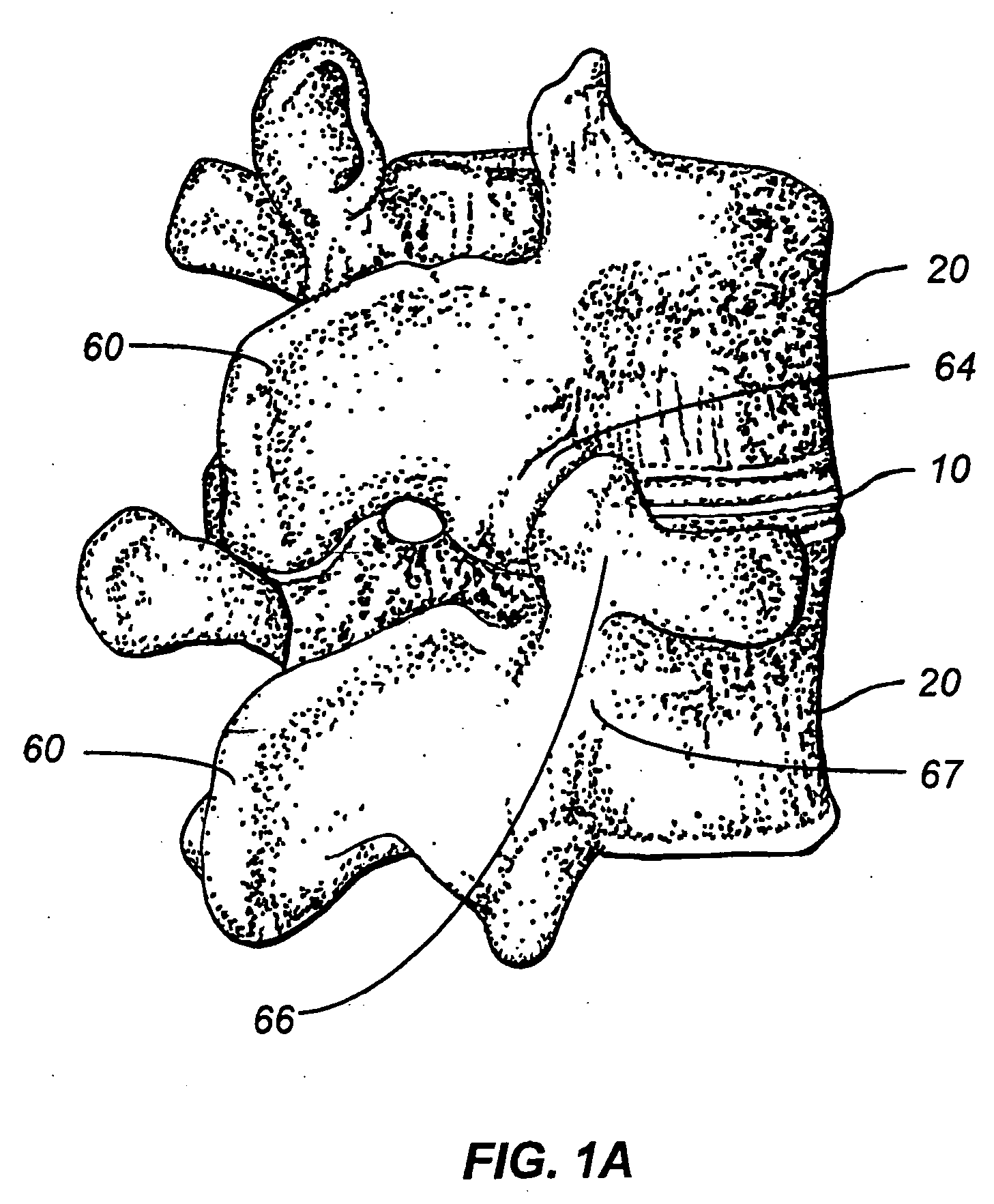

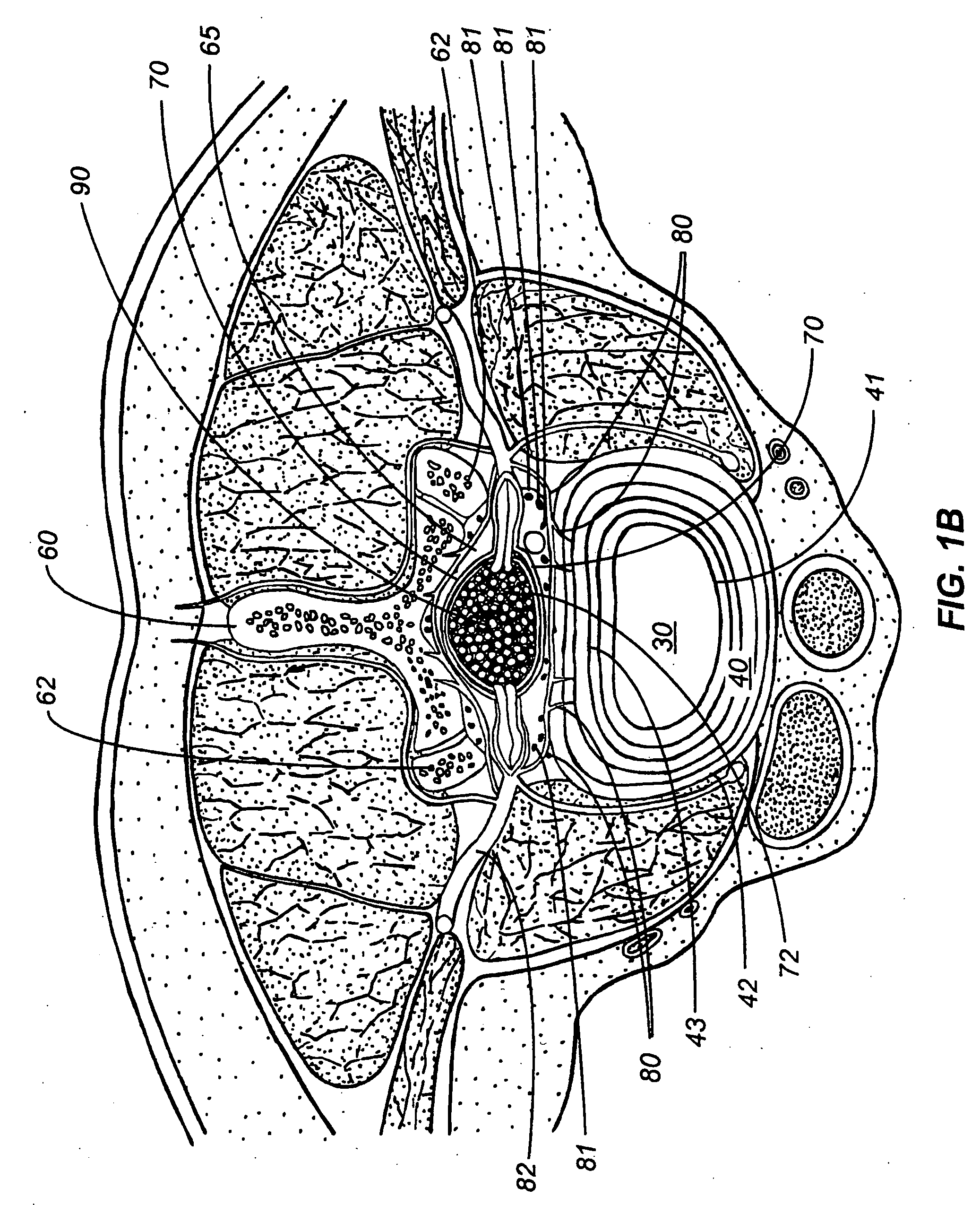

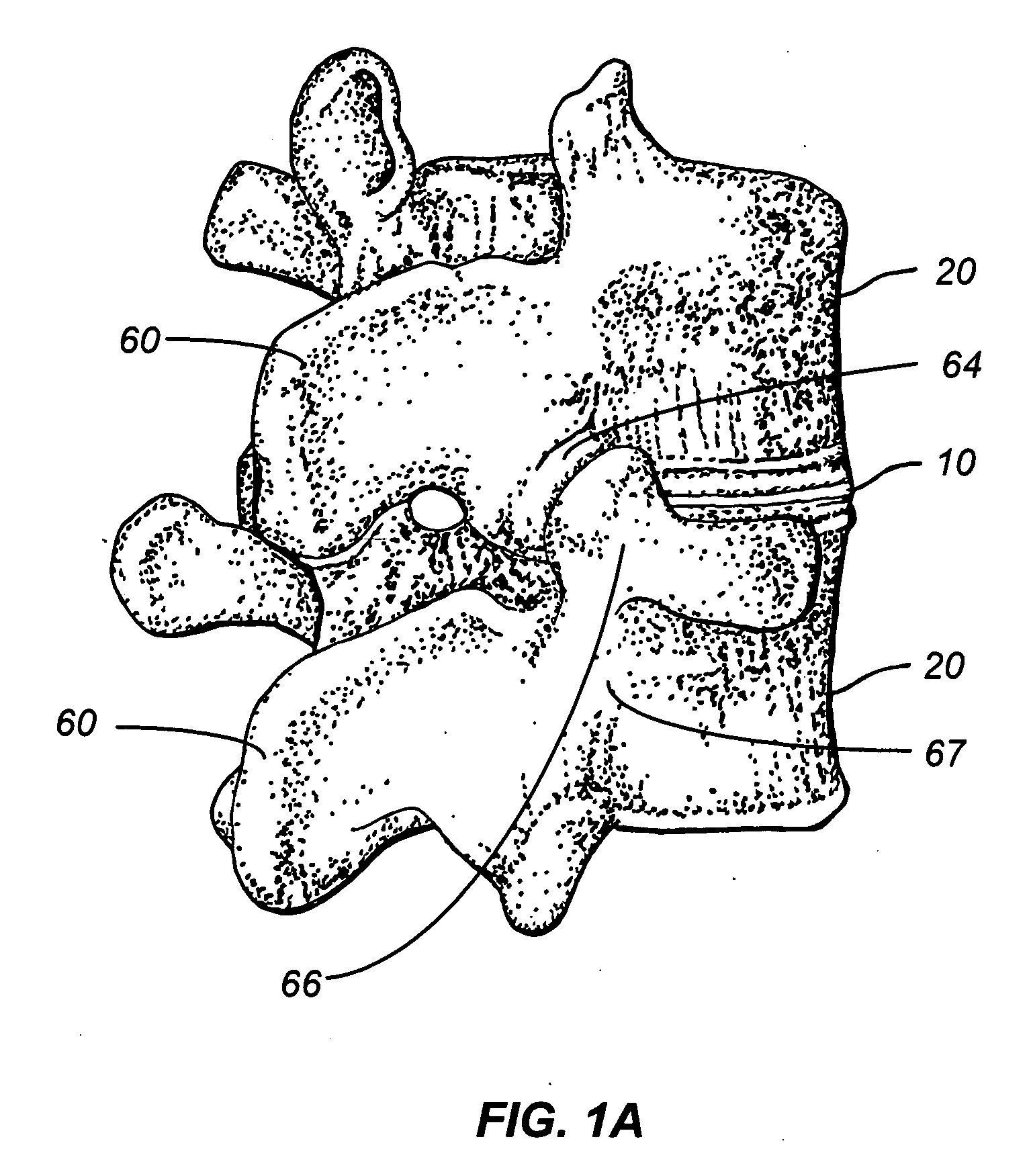

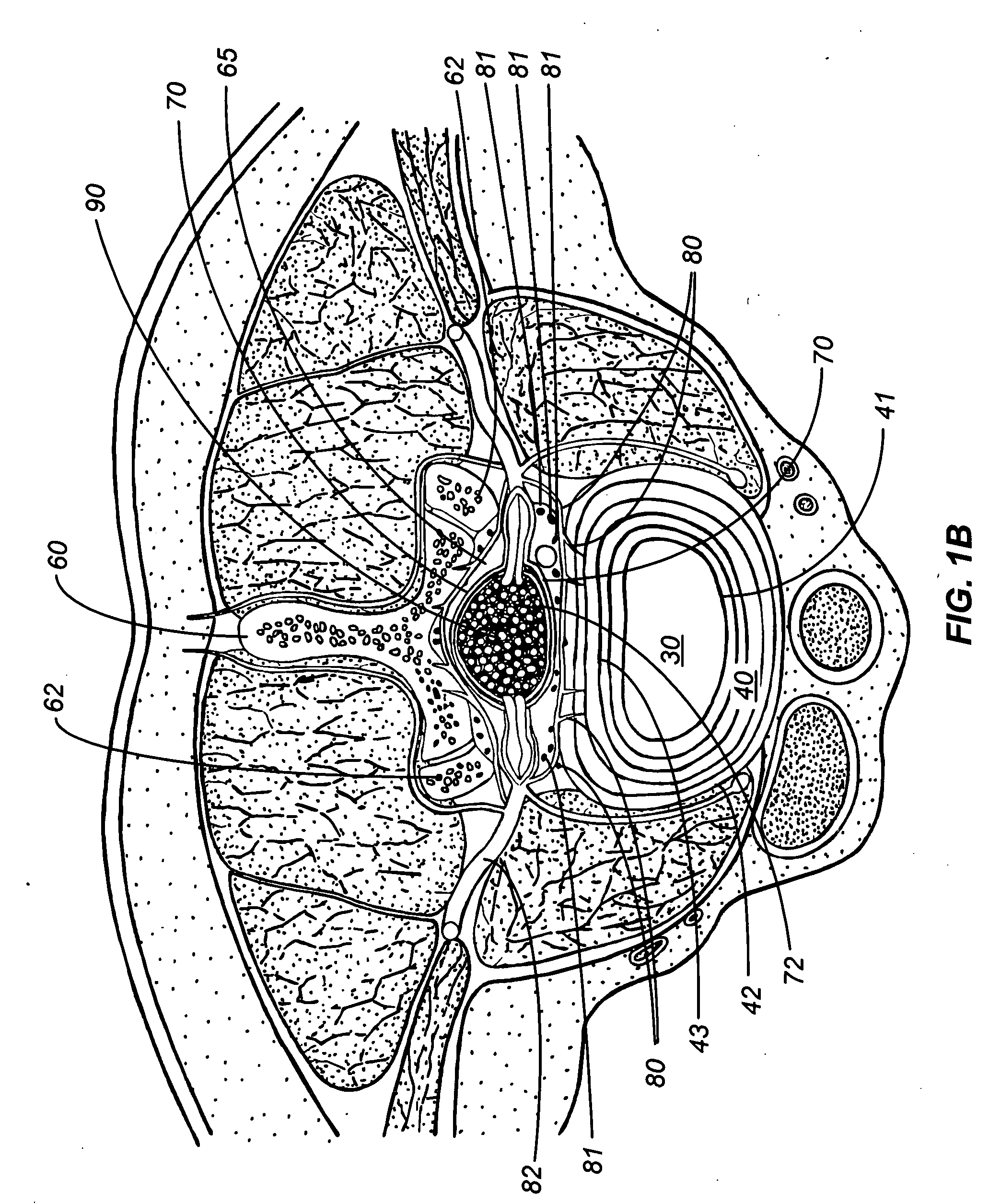

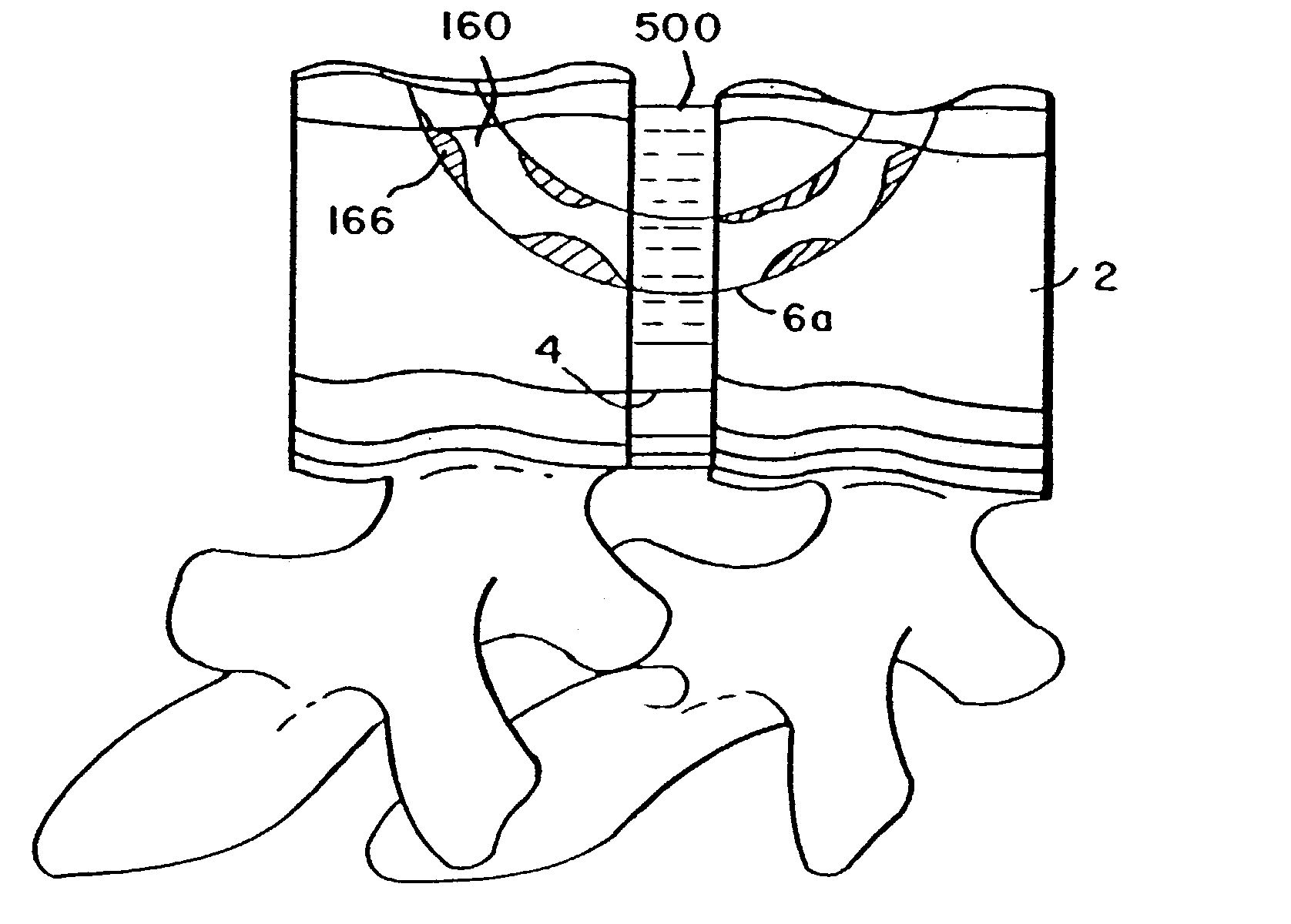

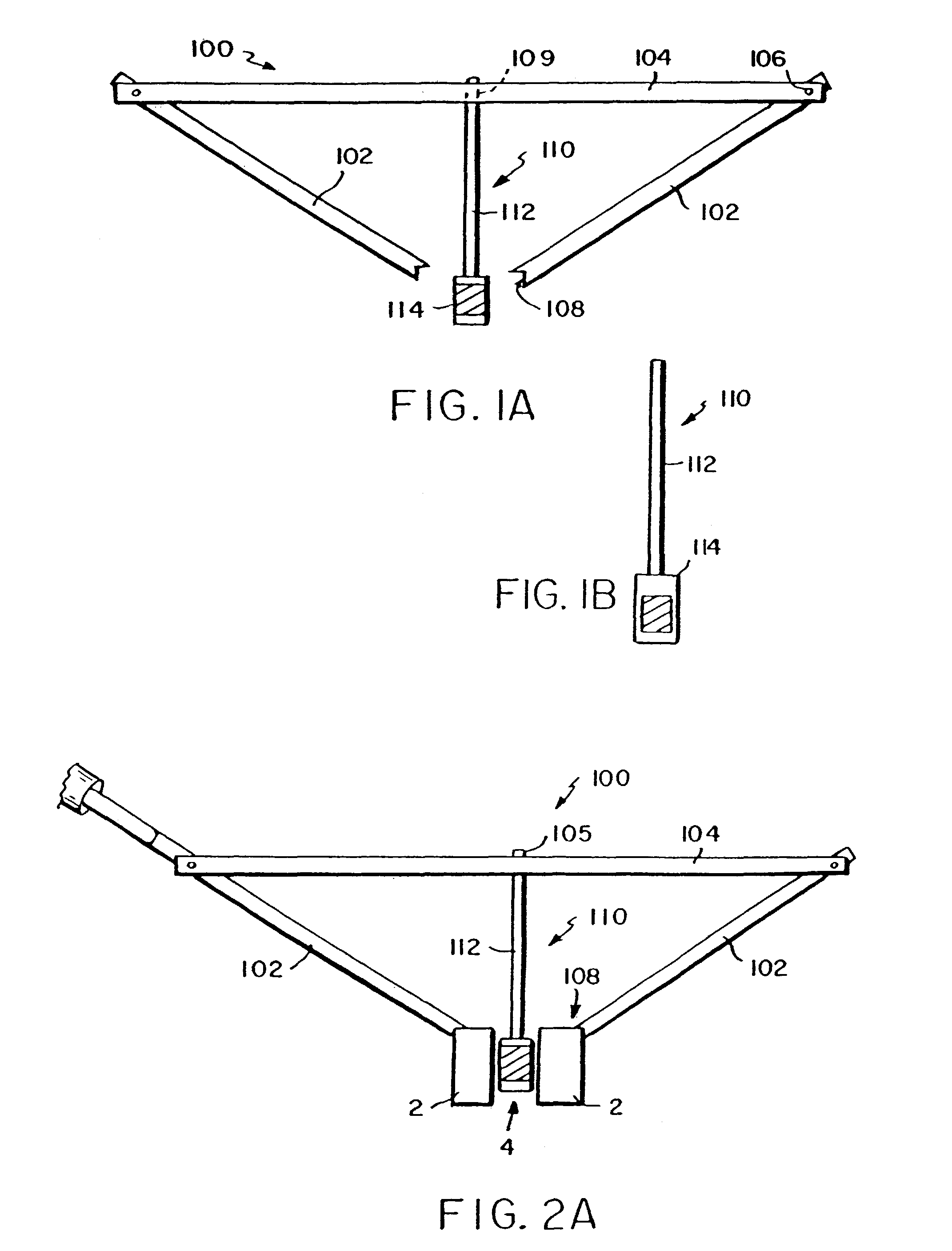

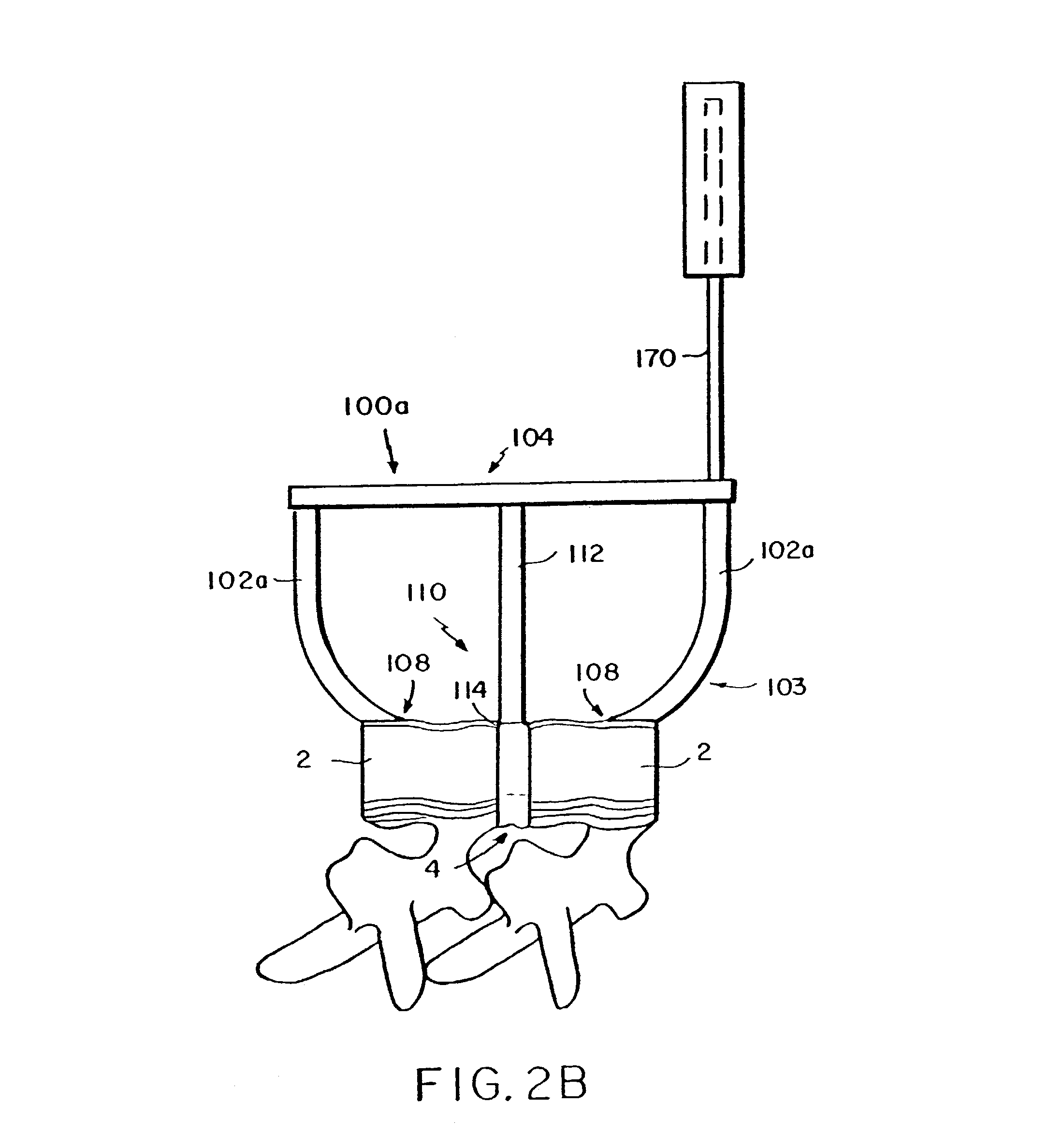

Systems and methods for spinal fixation

InactiveUS6923811B1Maintain alignmentProvide protectionInternal osteosythesisDiagnosticsScrew systemIntervertebral space

Featured are a method and apparatus for fixing adjacent vertebrate of a spine that avoids the need and associated problems with prior cage or straight rod and screw systems. Methods and apparatus of the invention utilize a new implant member, which preferably is arcuate. Preferred methods of the invention for stabilizing adjacent vertebrae of the spine, include steps of providing a positioning apparatus including two guide sleeves, each guide sleeve having a long axis and locating the two guide sleeves with respect to the adjacent vertebrae such that a vertex formed by the long axis of each guide sleeve is located in the intervertebral space for the adjacent vertebrae. The method further includes forming an aperture in each of the adjacent vertebrae using the guide sleeves and inserting an implant into the apertures formed in each of the adjacent vertebrae so that the implant extends between the adjacent vertebrae and through the intervertebral space. In an alternative method a cutting fixture including a pivot arm is secured to the adjacent vertebrae and a cutting device is secured to the pivot arm. The pivot arm and cutting device are configured and arranged so that rotation of the pivot arm about a particularly located pivot point allows the cutting device to form the aperture in each of the adjacent vertebrae. Another alternative method for fixing adjacent vertebrate of a spine includes the step of forming a common channel in and between the adjacent vertebrae and inserting a biscuit implant in the common so as to bridge between the adjacent vertebrae.

Owner:K2M

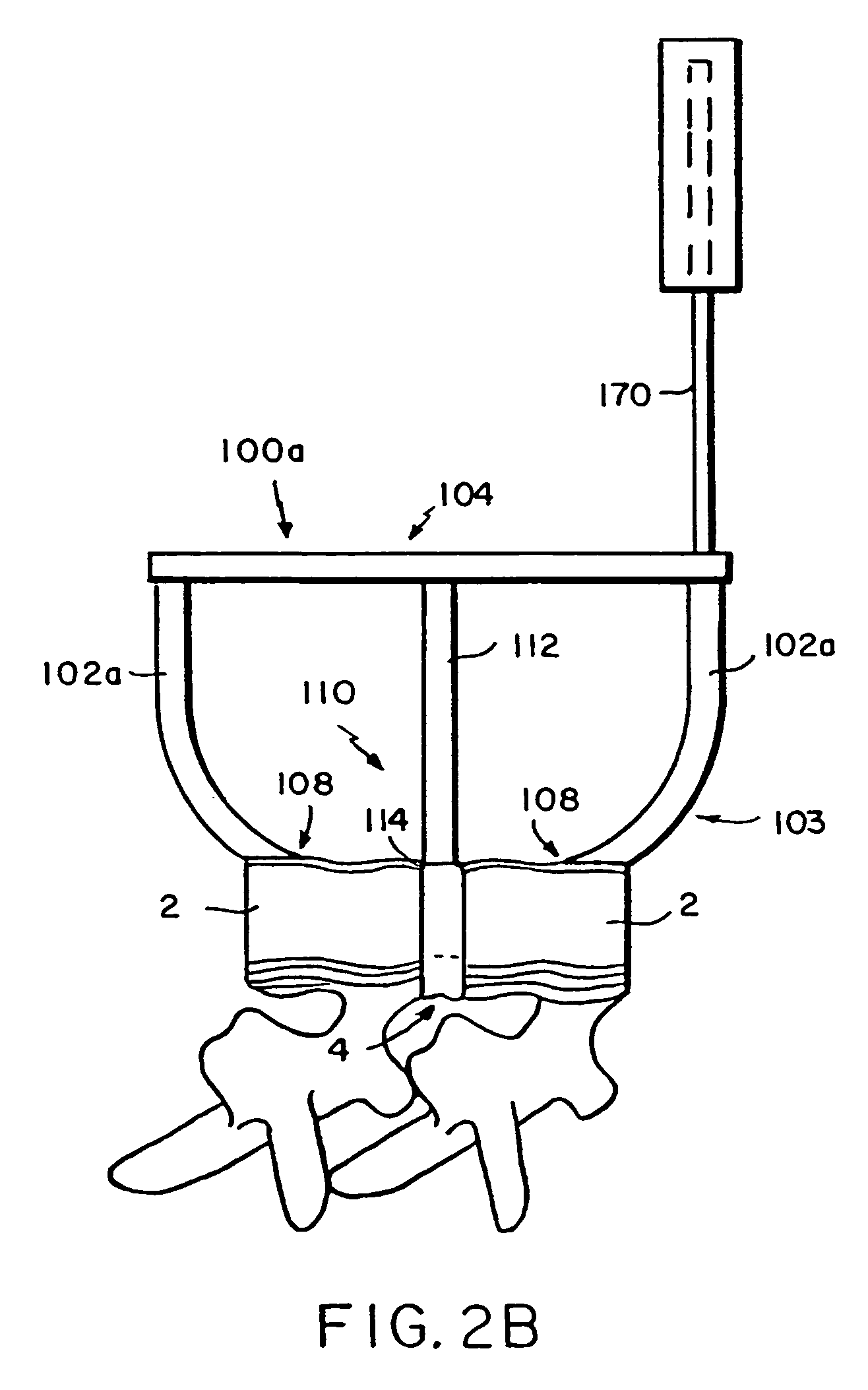

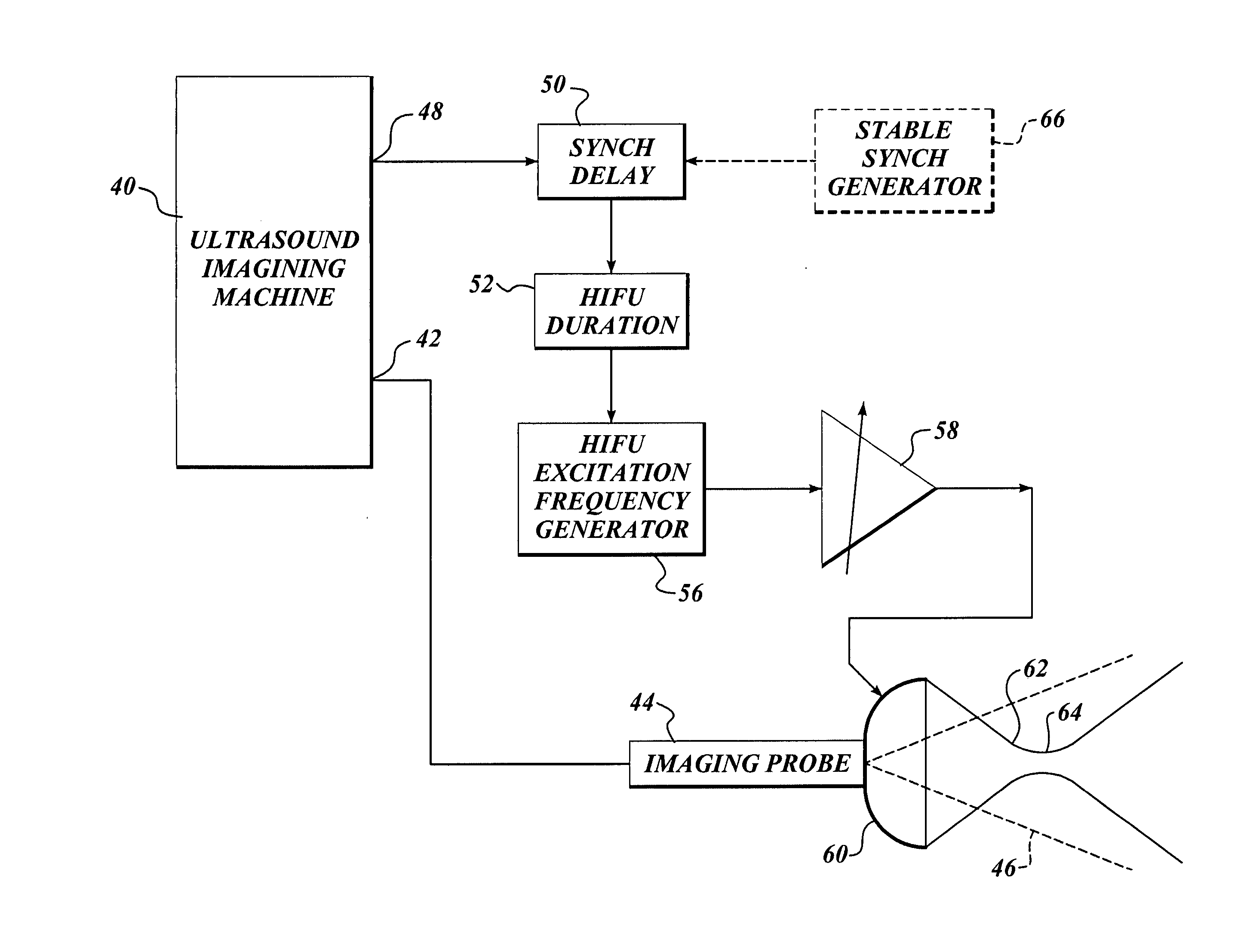

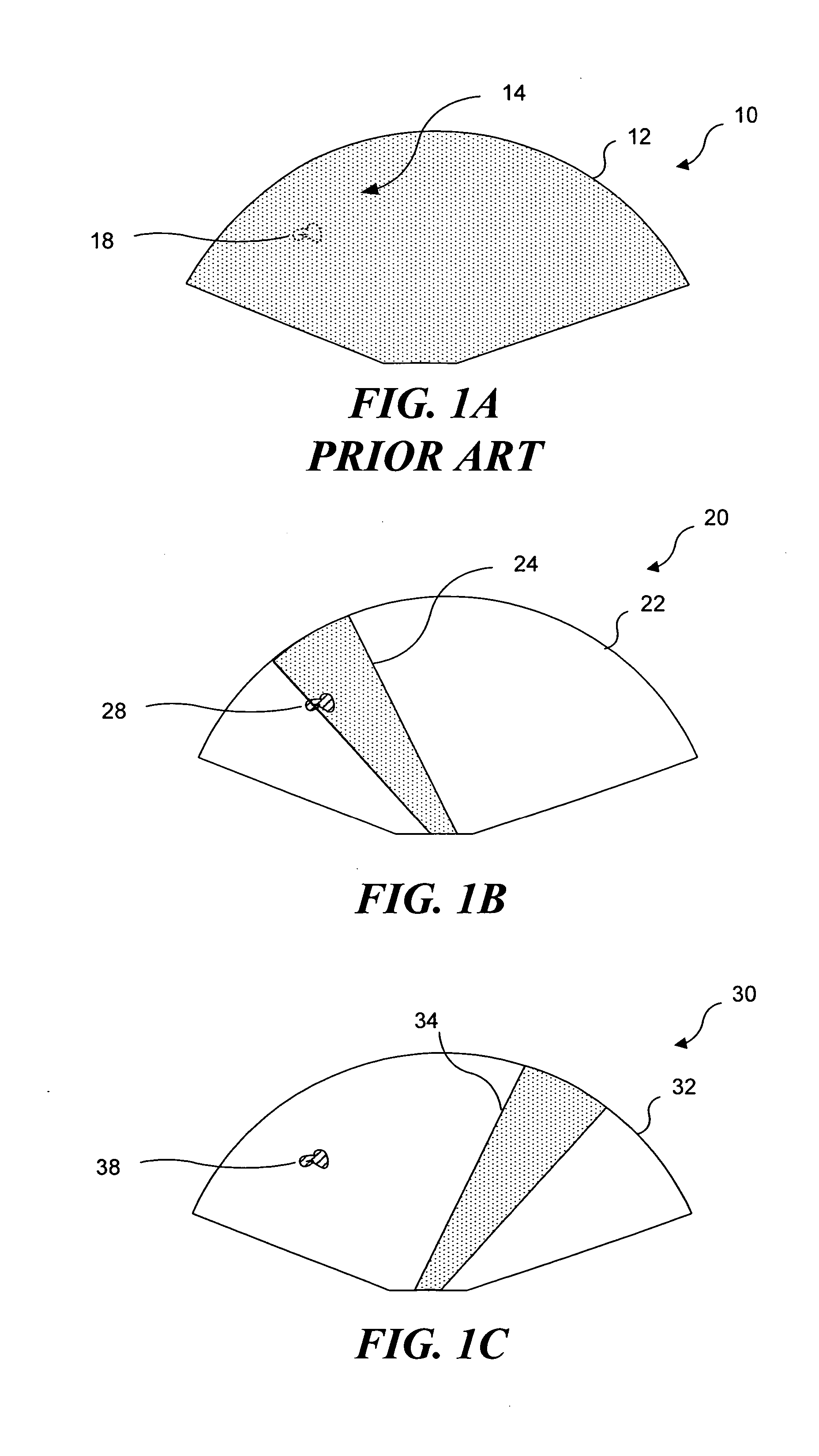

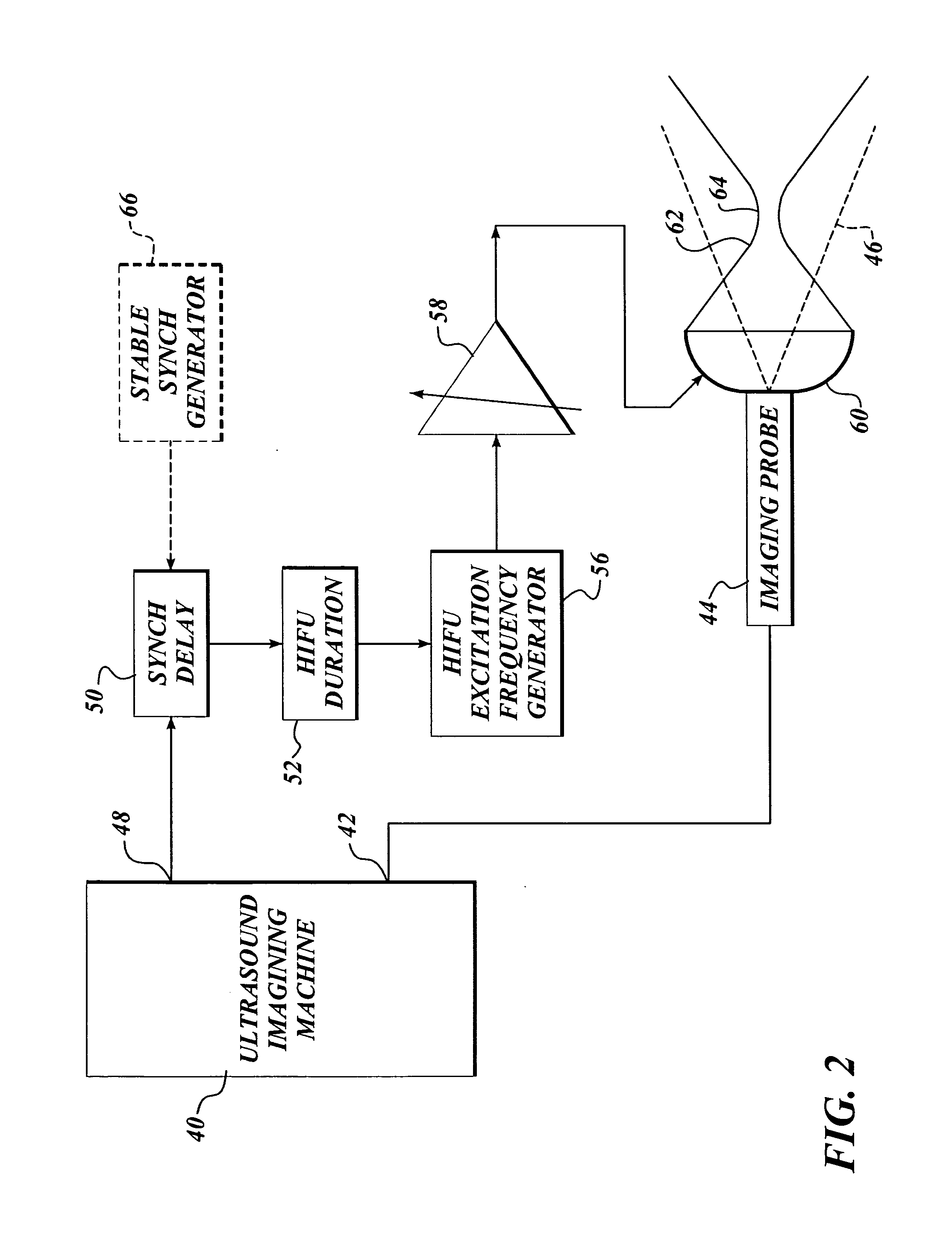

Ultrasound guided high intensity focused ultrasound treatment of nerves

InactiveUS20050240126A1Relieve painEasy procedureUltrasound therapyBlood flow measurement devicesAbnormal tissue growthHigh doses

A method for using high intensity focused ultrasound (HIFU) to treat neurological structures to achieve a desired therapeutic affect. Depending on the dosage of HIFU applied, it can have a reversible or irreversible effect on neural structures. For example, a relatively high dose of HIFU can be used to permanently block nerve function, to provide a non-invasive alternative to severing a nerve to treat severe spasticity. Relatively lower doses of HIFU can be used to reversible a block nerve function, to alleviate pain, to achieve an anesthetic effect, or to achieve a cosmetic effect. Where sensory nerves are not necessary for voluntary function, but are involved in pain associated with tumors or bone cancer, HIFU can be used to non-invasively destroy such sensory nerves to alleviate pain without drugs. Preferably, ultrasound imaging synchronized to the HIFU therapy is used to provide real-time ultrasound image guided HIFU therapy of neural structures.

Owner:UNIV OF WASHINGTON

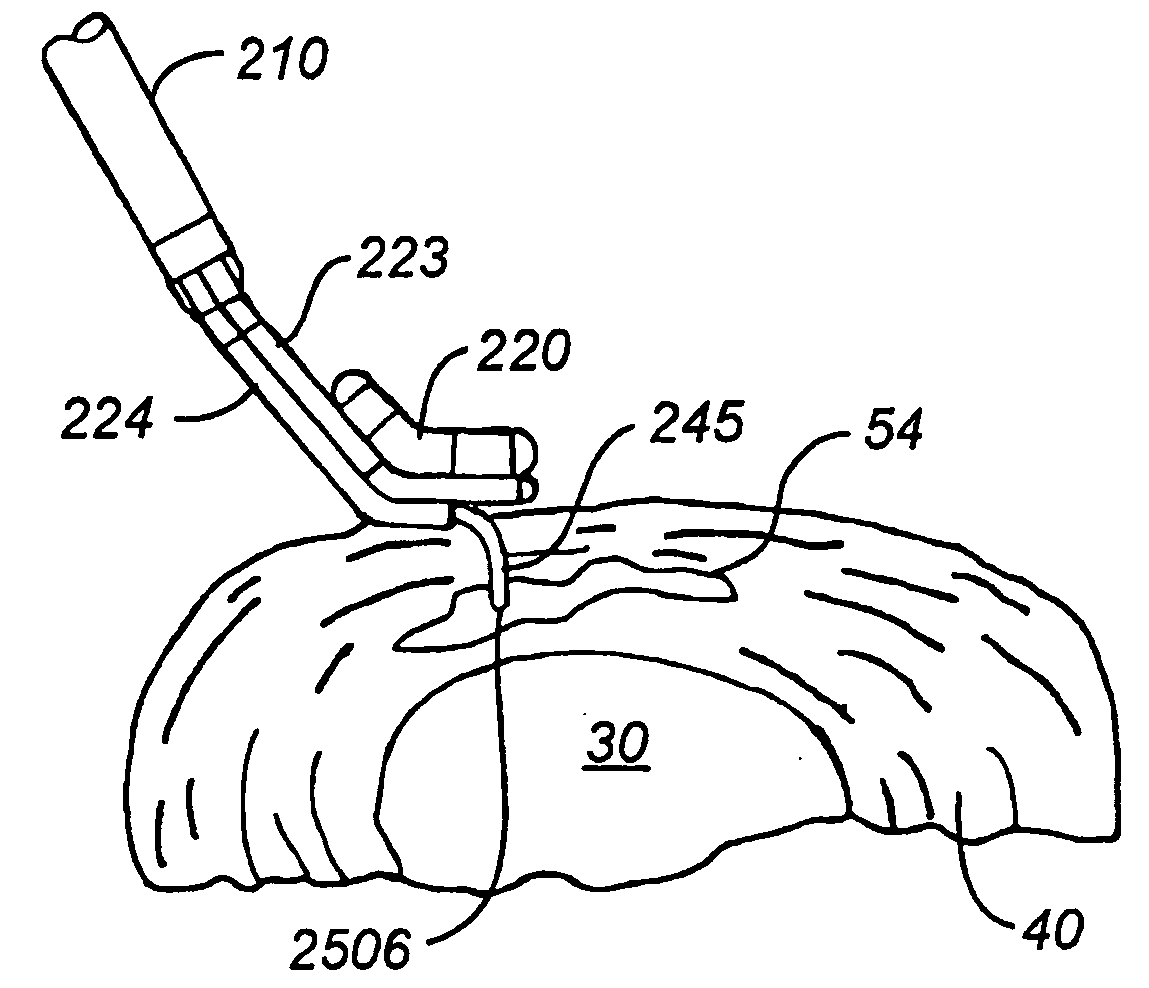

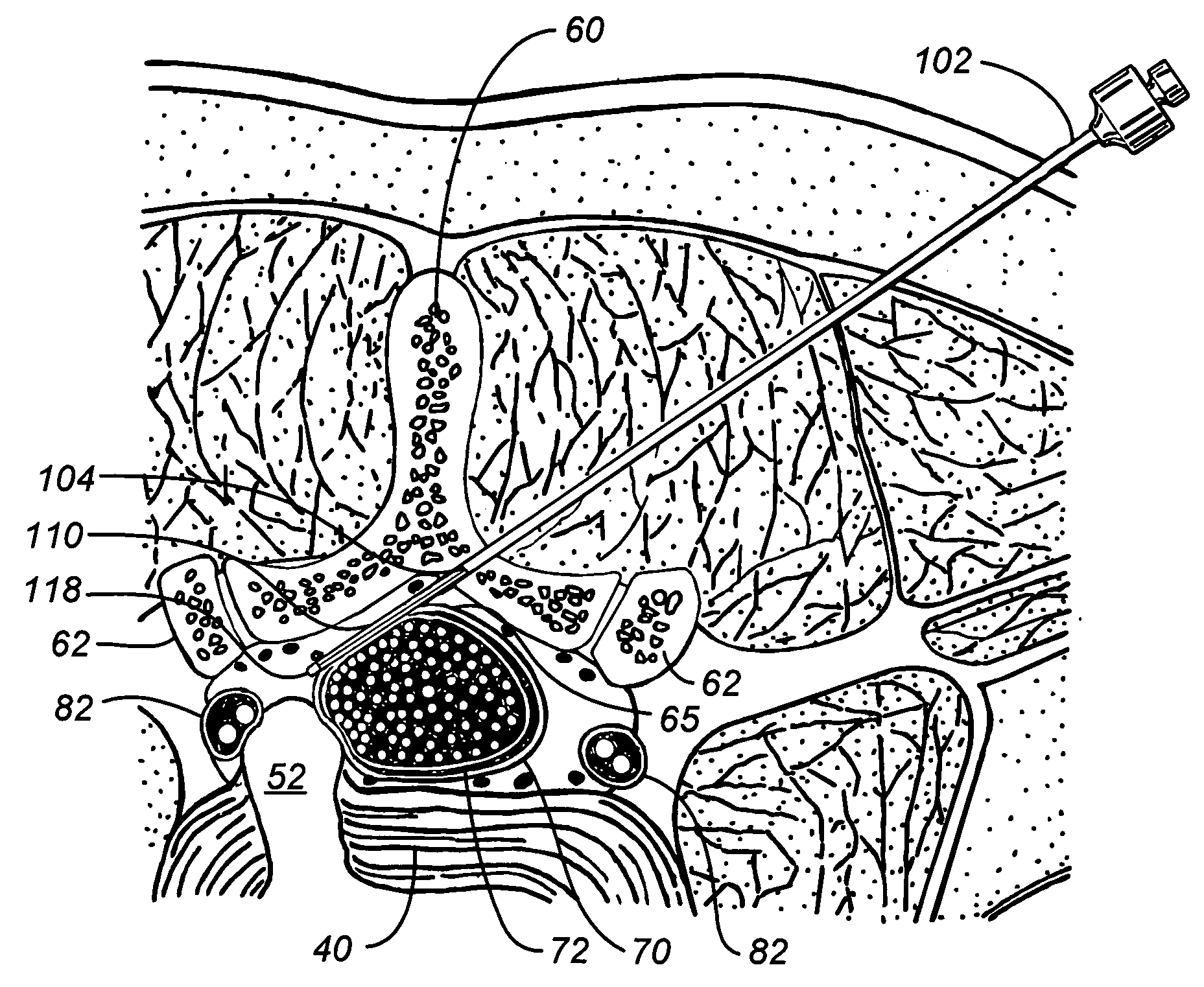

Percutaneous endoscopic access tools for the spinal epidural space and related methods of treatment

InactiveUS20060206118A1Reduce and diminish and minimize epidural neural tissue scarringIncrease spacingCannulasDiagnosticsSpinal epidural spaceAlternative methods

Several alternative spinal access devices are described. A number of alternative methods for performing therapies in the spinal region using the described spinal access devices are also described.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV +1

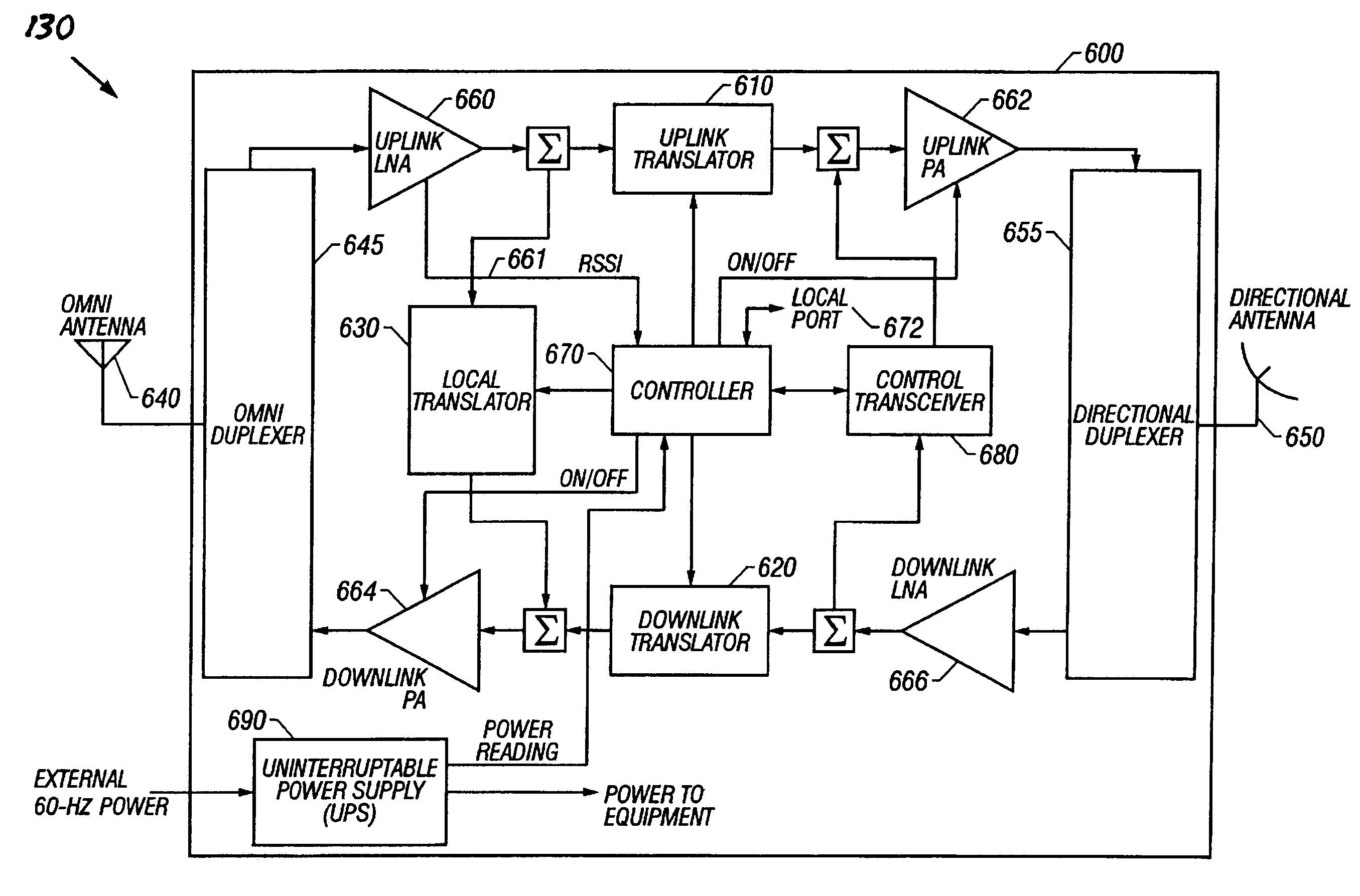

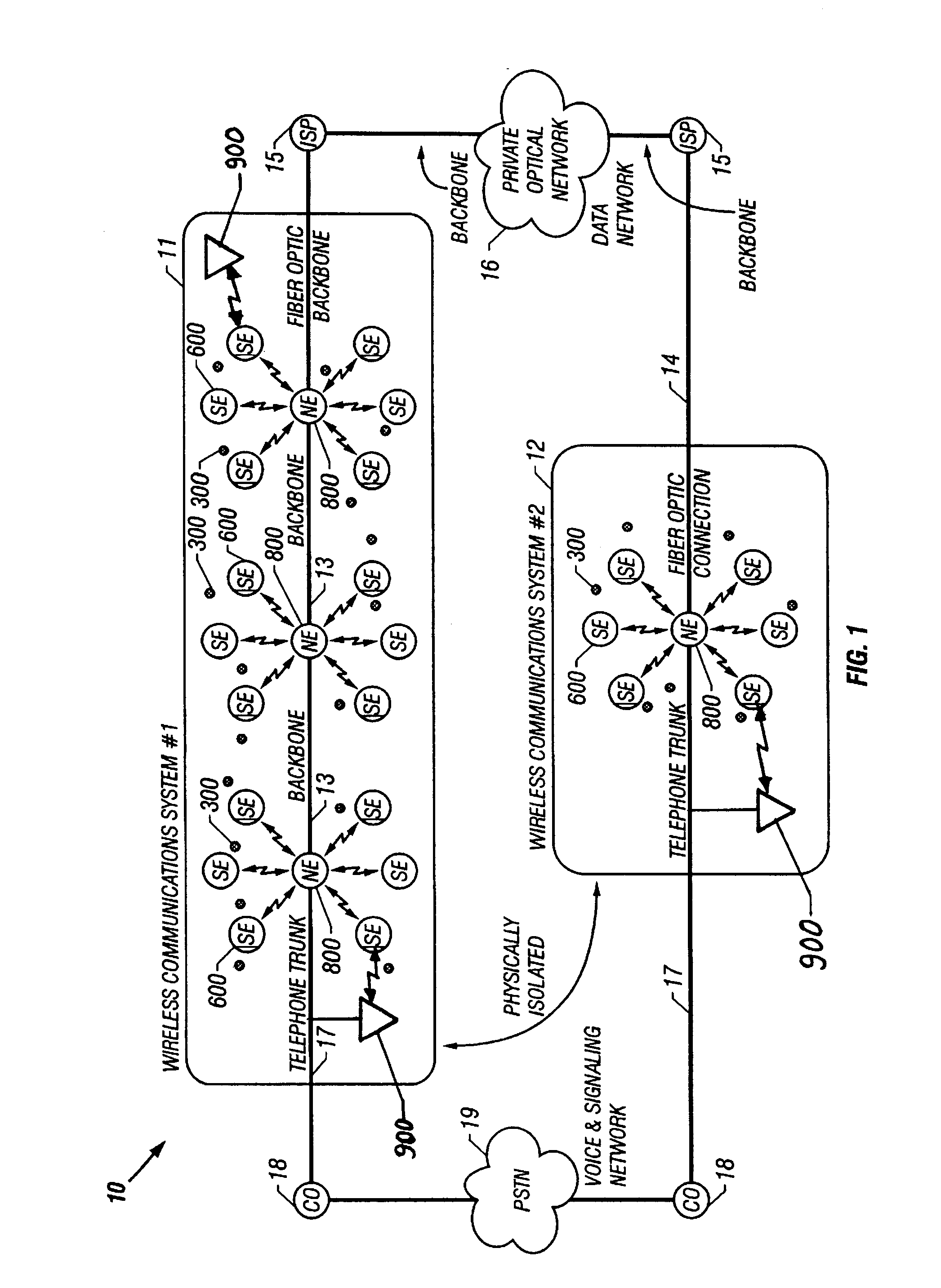

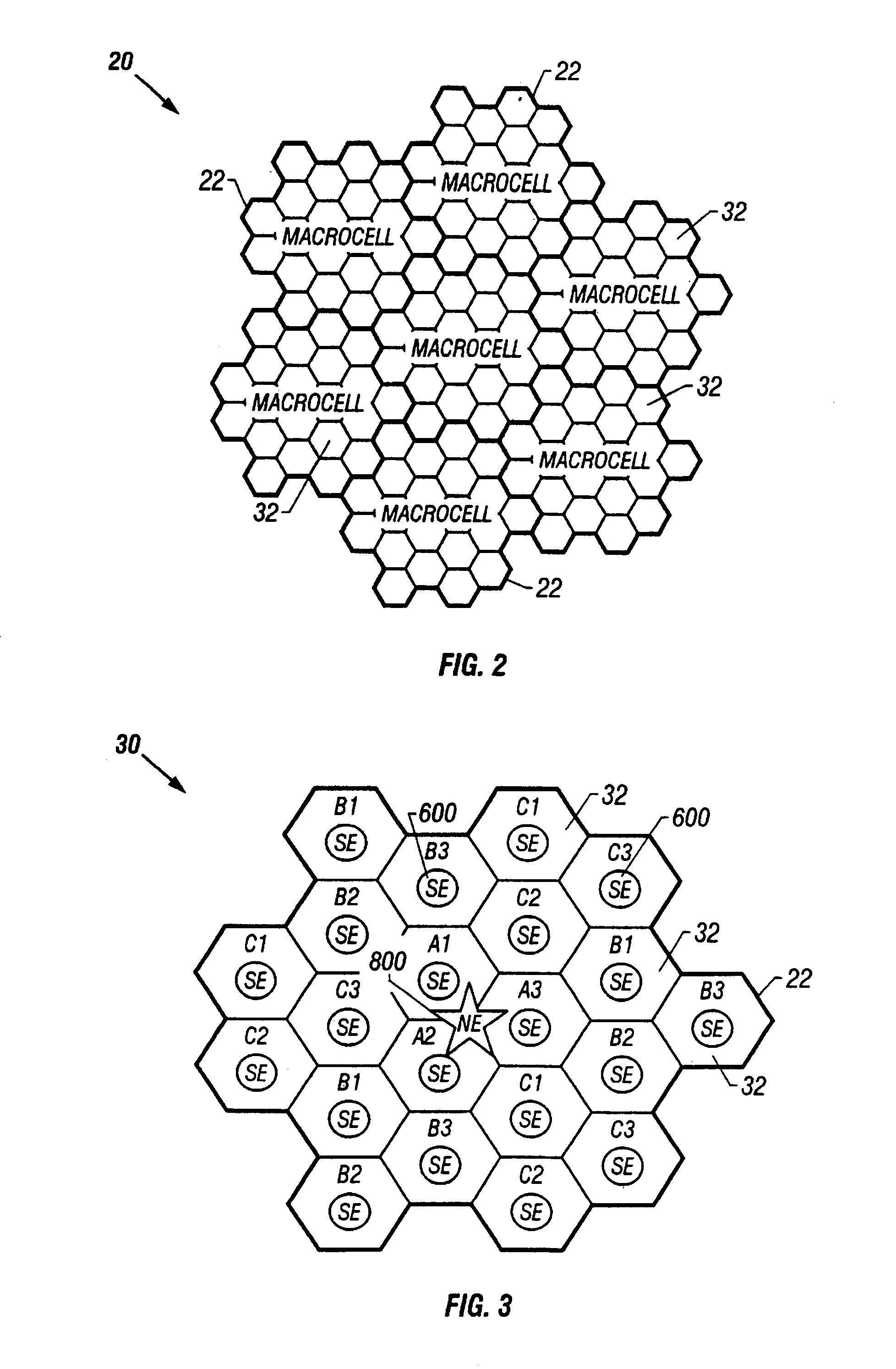

Wireless communication device with multiple external communication links

InactiveUS6842617B2Operational securityCollect revenuePower distribution line transmissionRepeater circuitsTelecommunications linkPopulation density

A decentralized asynchronous wireless communication system is disclosed for providing voice and data communication that allows flexibility of communication paths for local communication or for communication to external networks. The system makes use of communication docking bays that may communicate in a local mode with other communication docking bays or handsets within a same microcell via signal extenders. In an extended mode, a communication docking bay located in a first microcell of a first macrocell may communicate with a second communication docking bay or handset in a second microcell of the first macrocell via signal extenders and a network extender. In a remote mode, a communication docking bay located in a first microcell of a first macrocell may communicate with a second communication docking bay or handset in a second microcell of a second macrocell via signal extenders and network extenders. The communication docking bays also provide a communication path to a Public Switch Telephone Network and other communication medium. This feature provides an alternate means of connecting a mobile handset to a Public Switch Telephone Network without communicating through a network extender. The system is particularly suitable for operation in rural areas having a low population density.

Owner:WAHOO COMM CORP

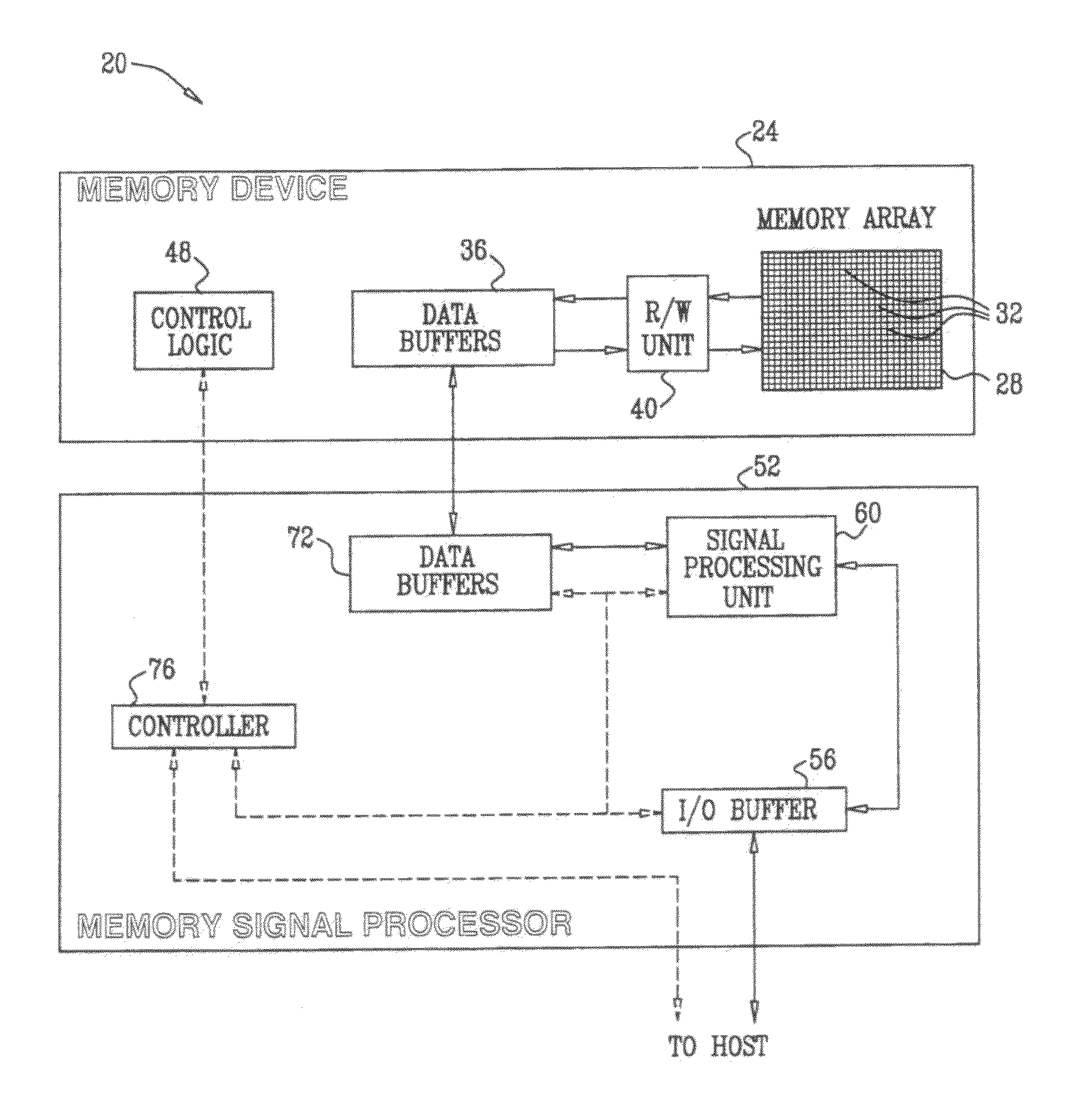

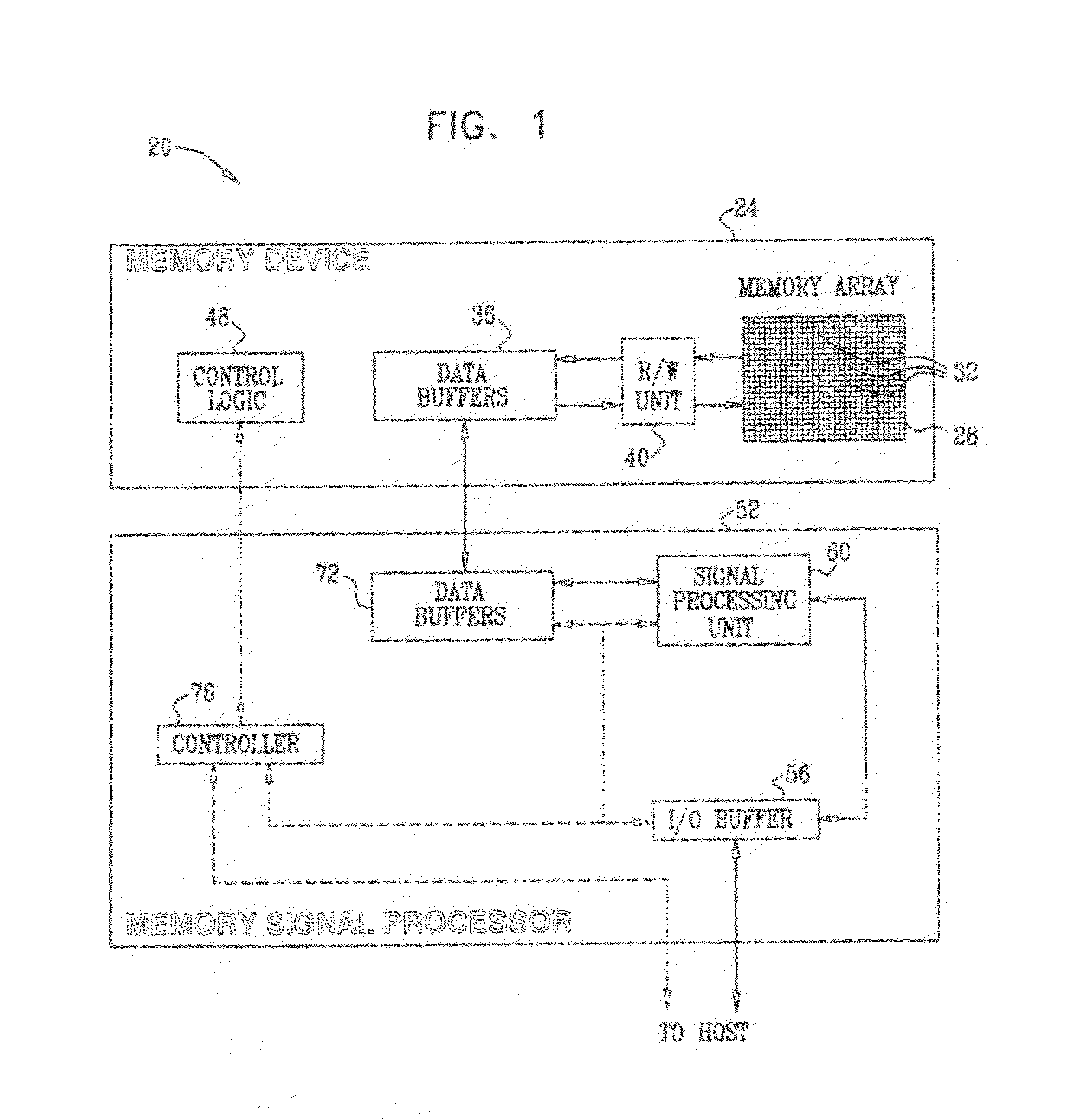

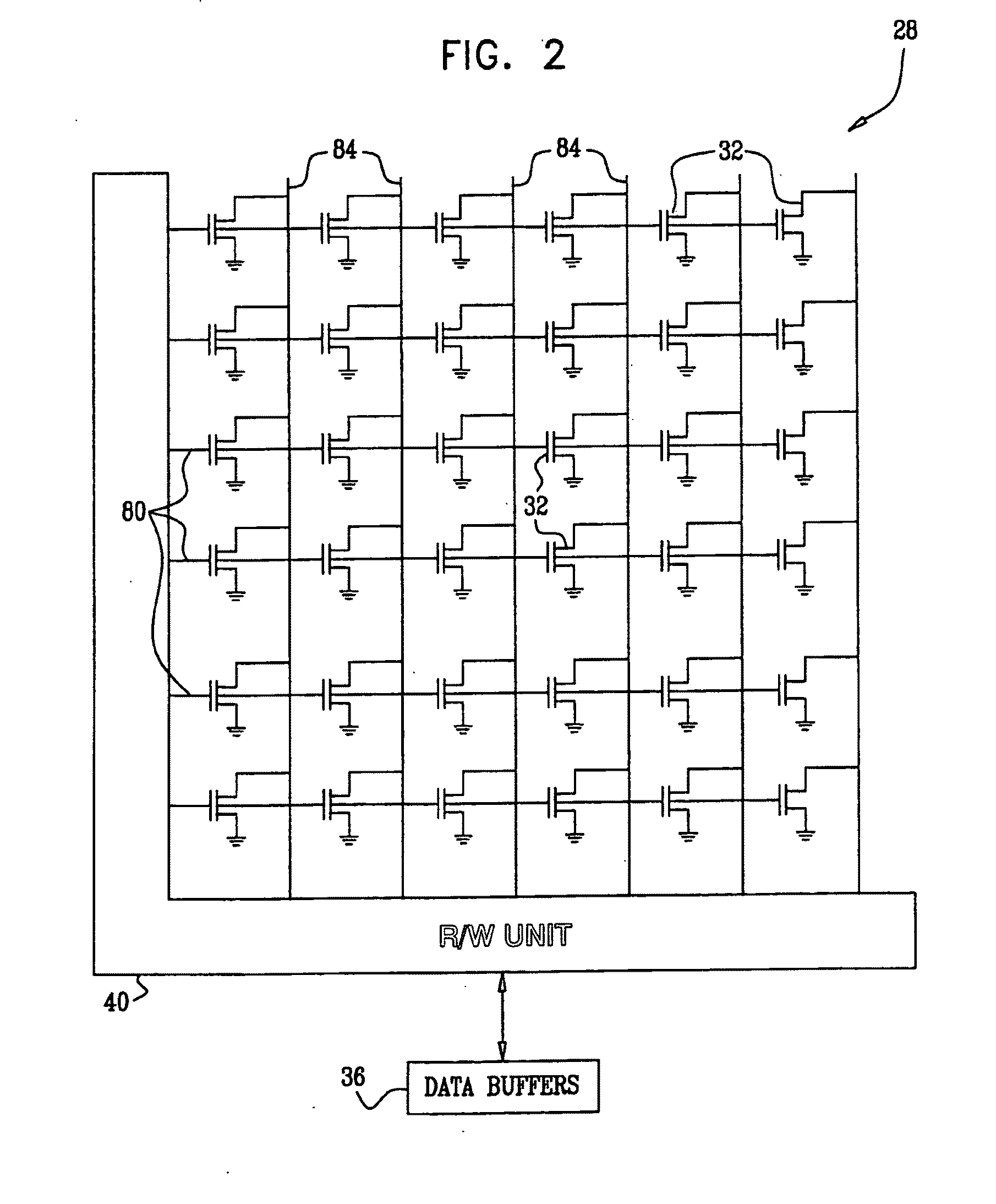

Automatic defect management in memory devices

ActiveUS20100115376A1Code conversionError correction/detection using block codesAlternative methodsComputer science

A method for storing data in a memory (28) that includes analog memory cells (32) includes identifying one or more defective memory cells in a group of the analog memory cells. An Error Correction Code (ECC) is selected responsively to a characteristic of the identified defective memory cells. The data is encoded using the selected ECC and the encoded data is stored in the group of the analog memory cells. In an alternative method, an identification of one or more defective memory cells among the analog memory cells is generated. Analog values are read from the analog memory cells in which the encoded data were stored, including at least one of the defective memory cells. The analog values are processed using an ECC decoding process responsively to the identification of the at least one of the defective memory cells, so as to reconstruct the data.

Owner:APPLE INC

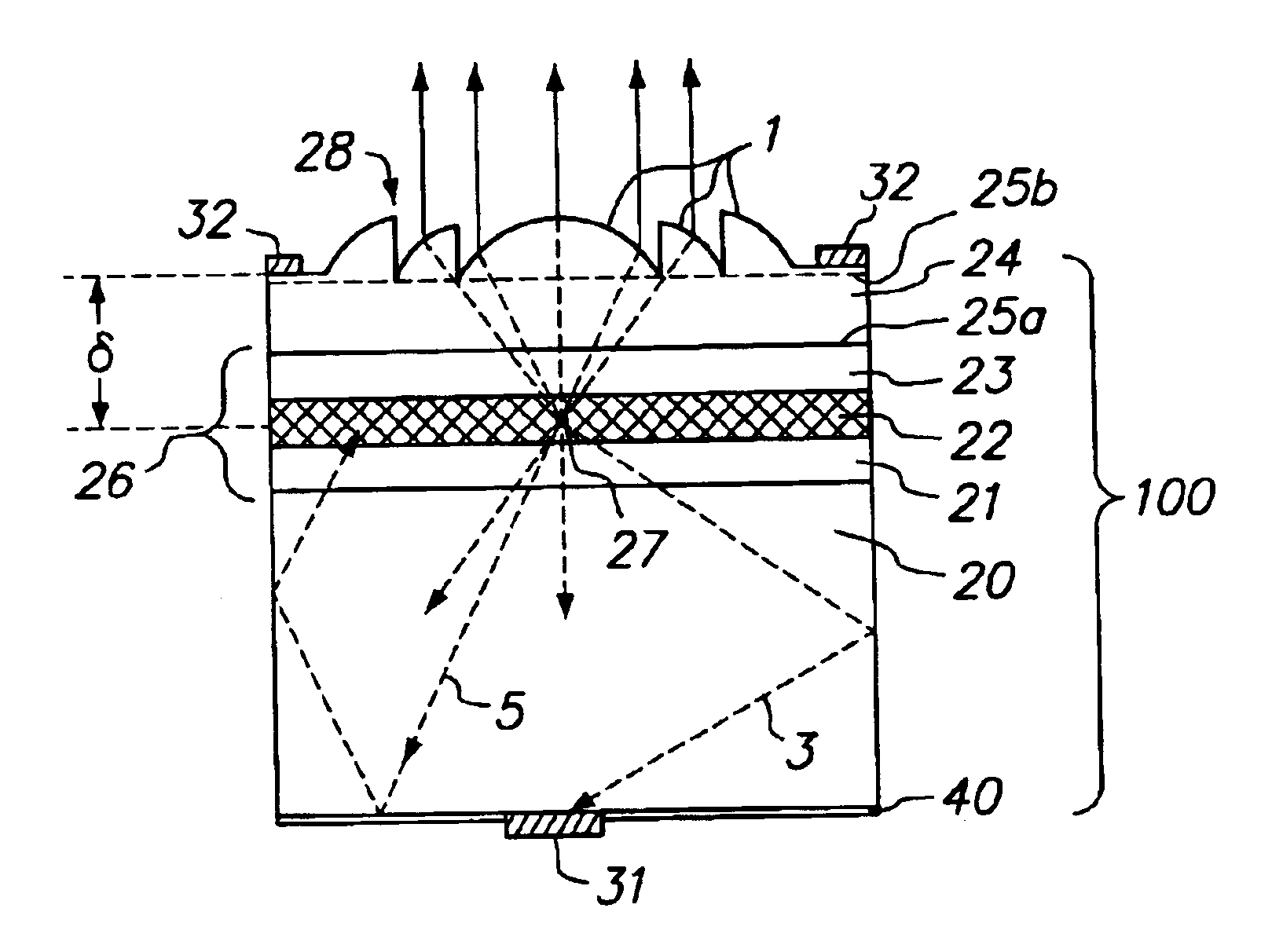

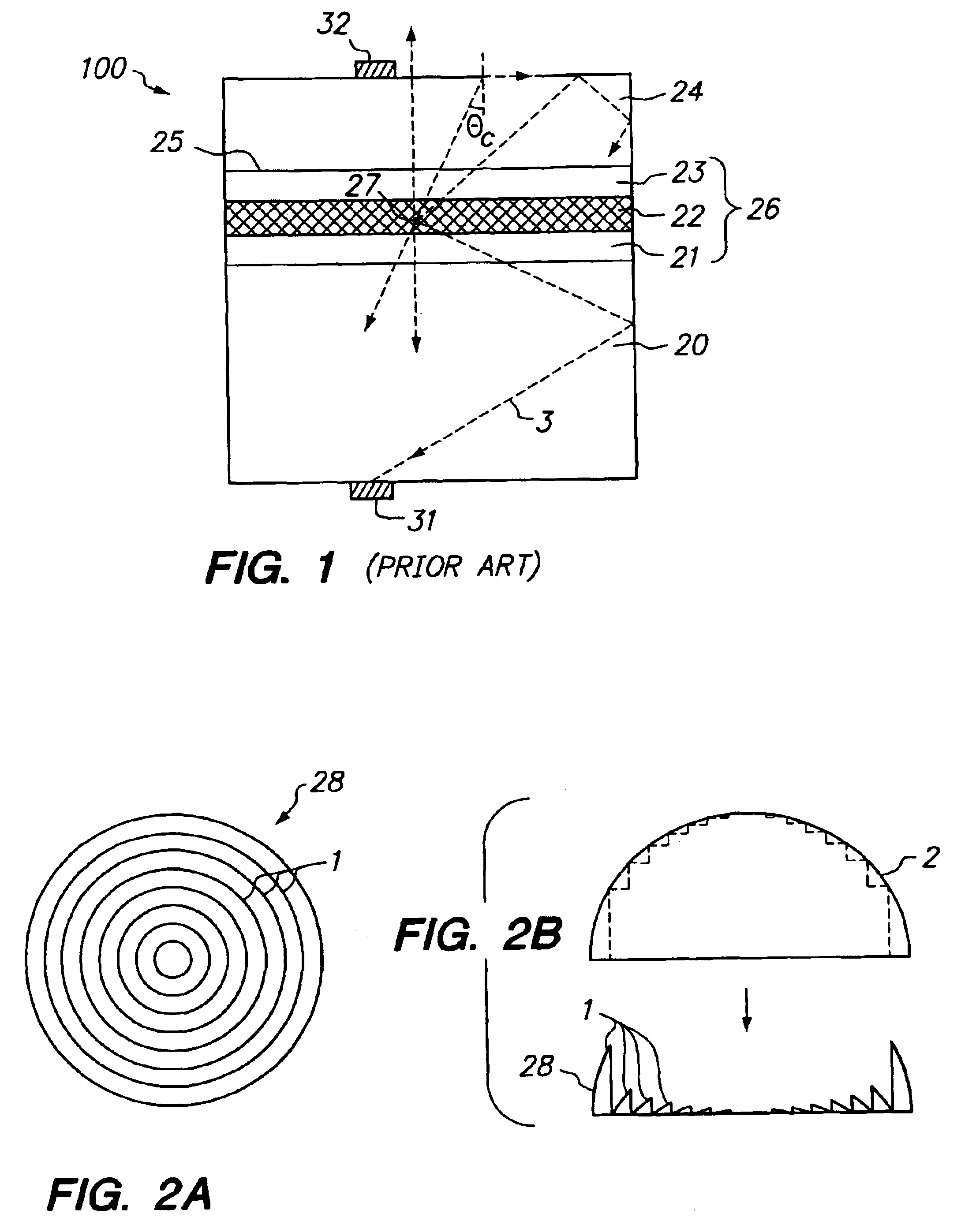

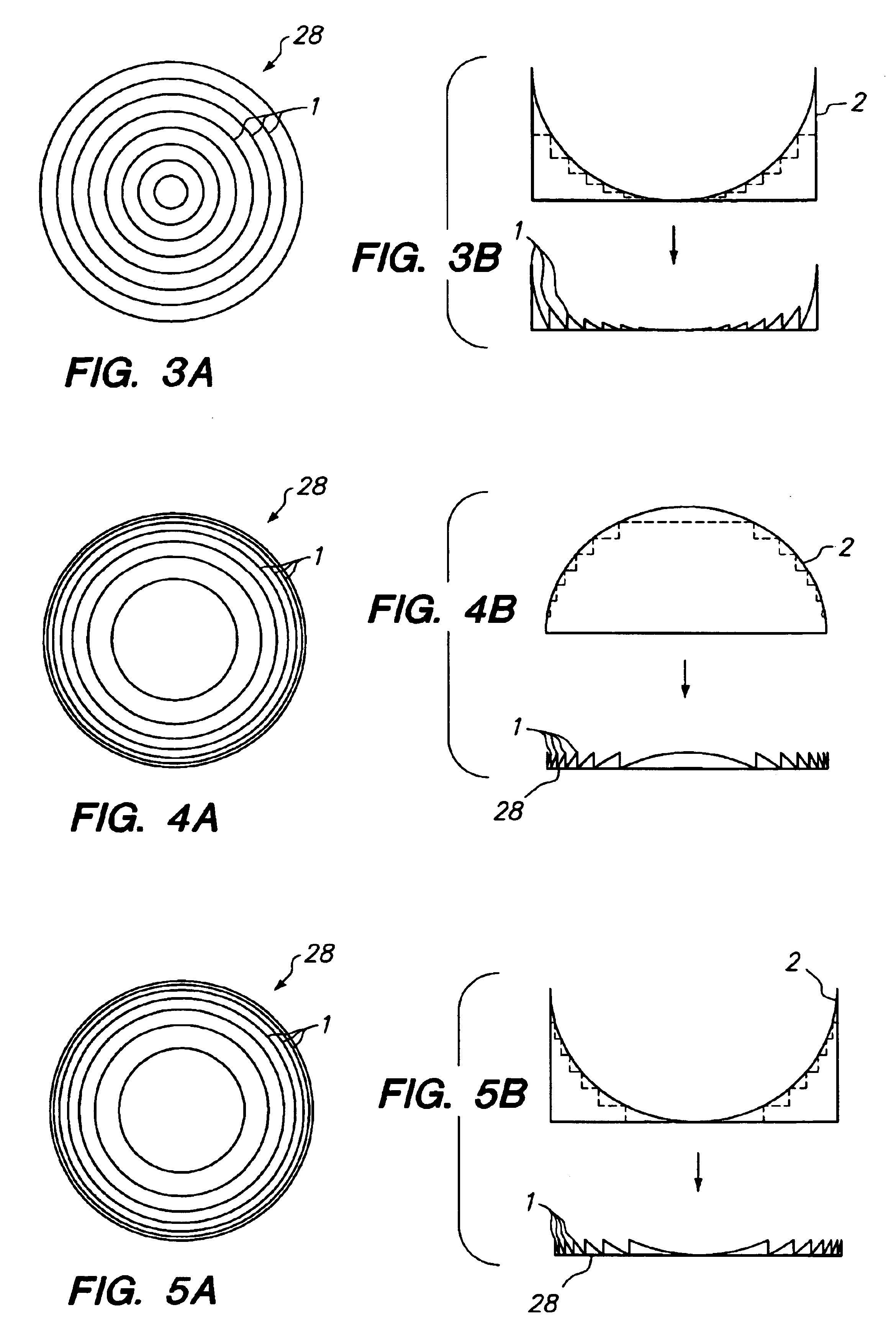

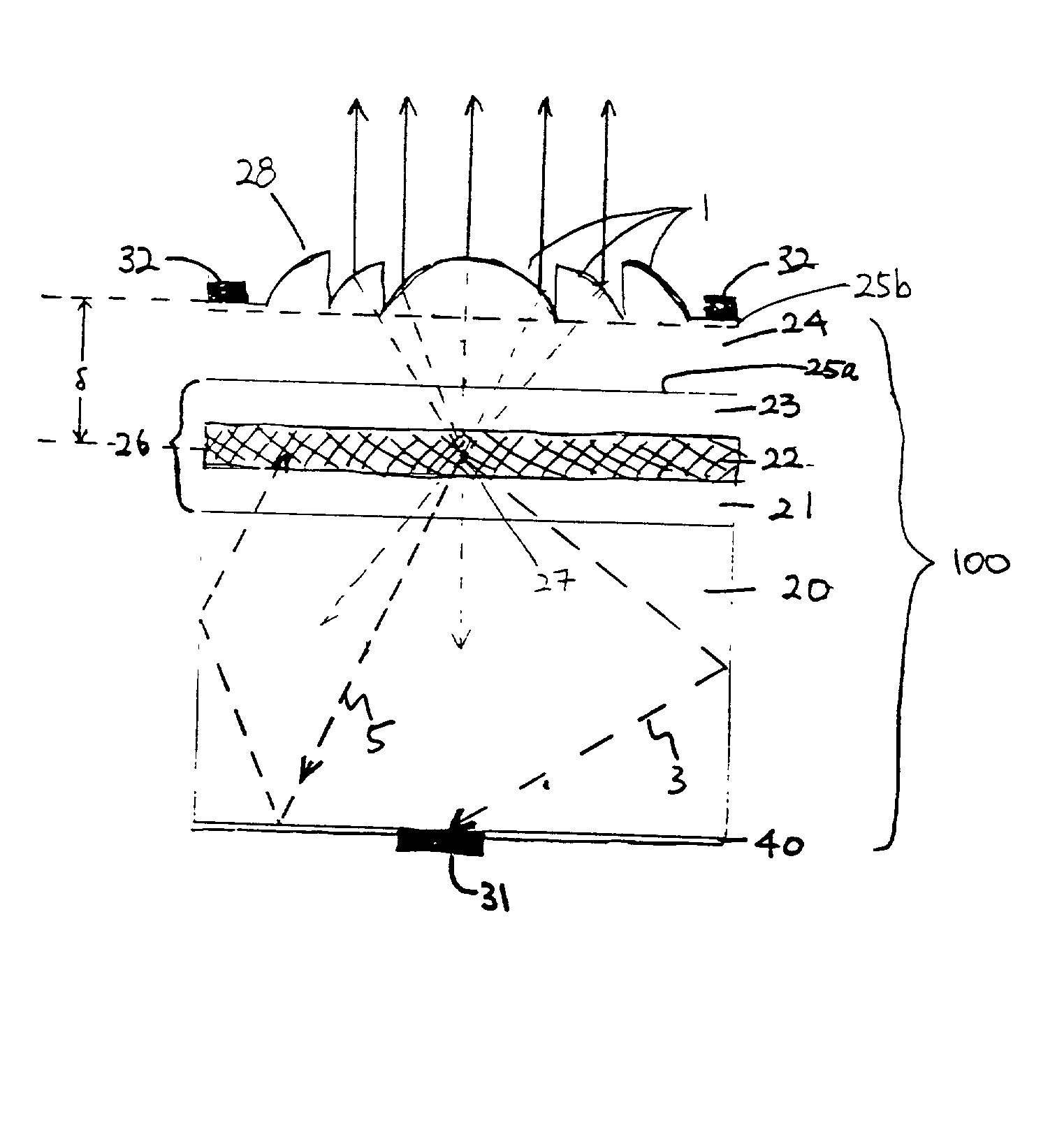

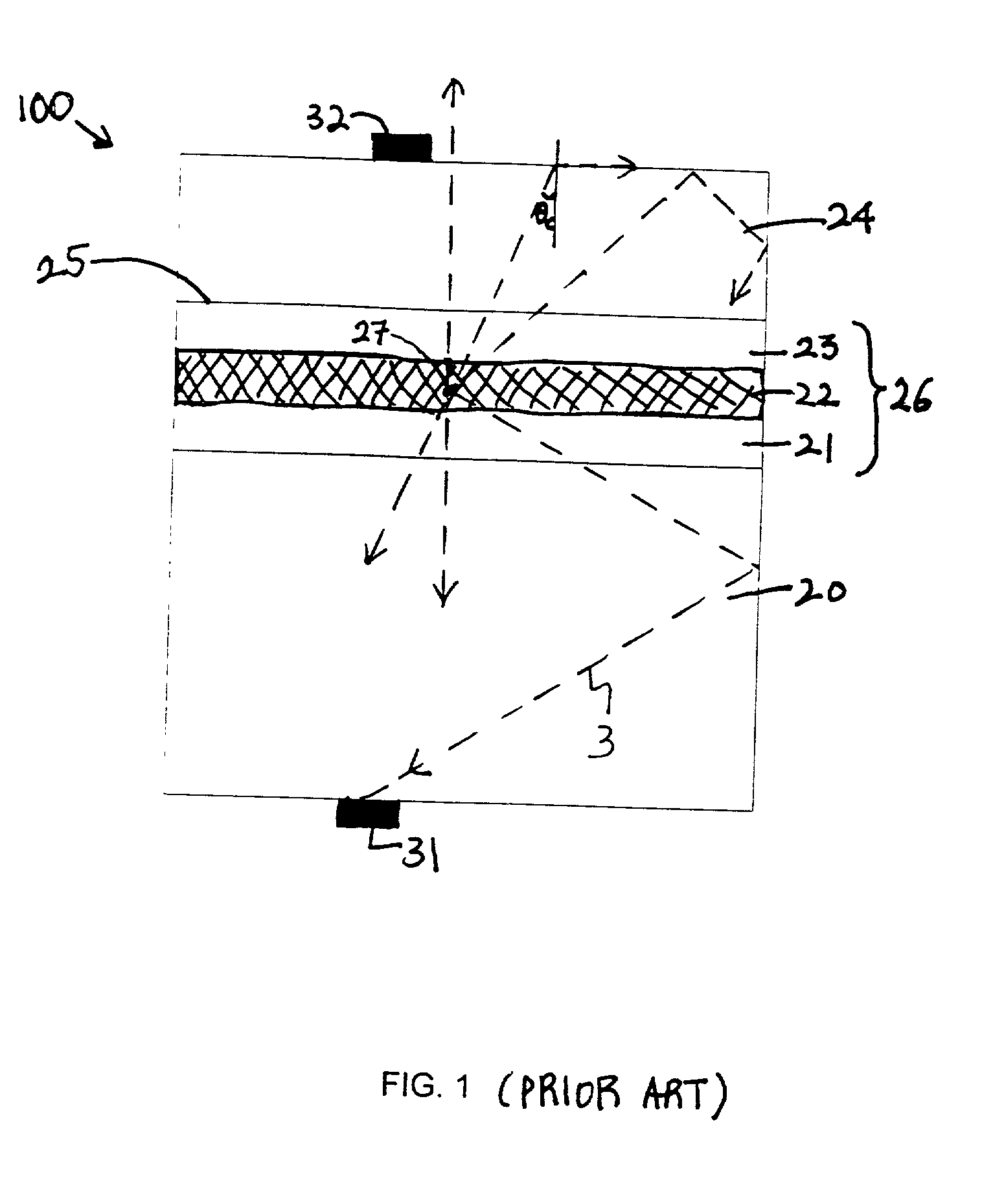

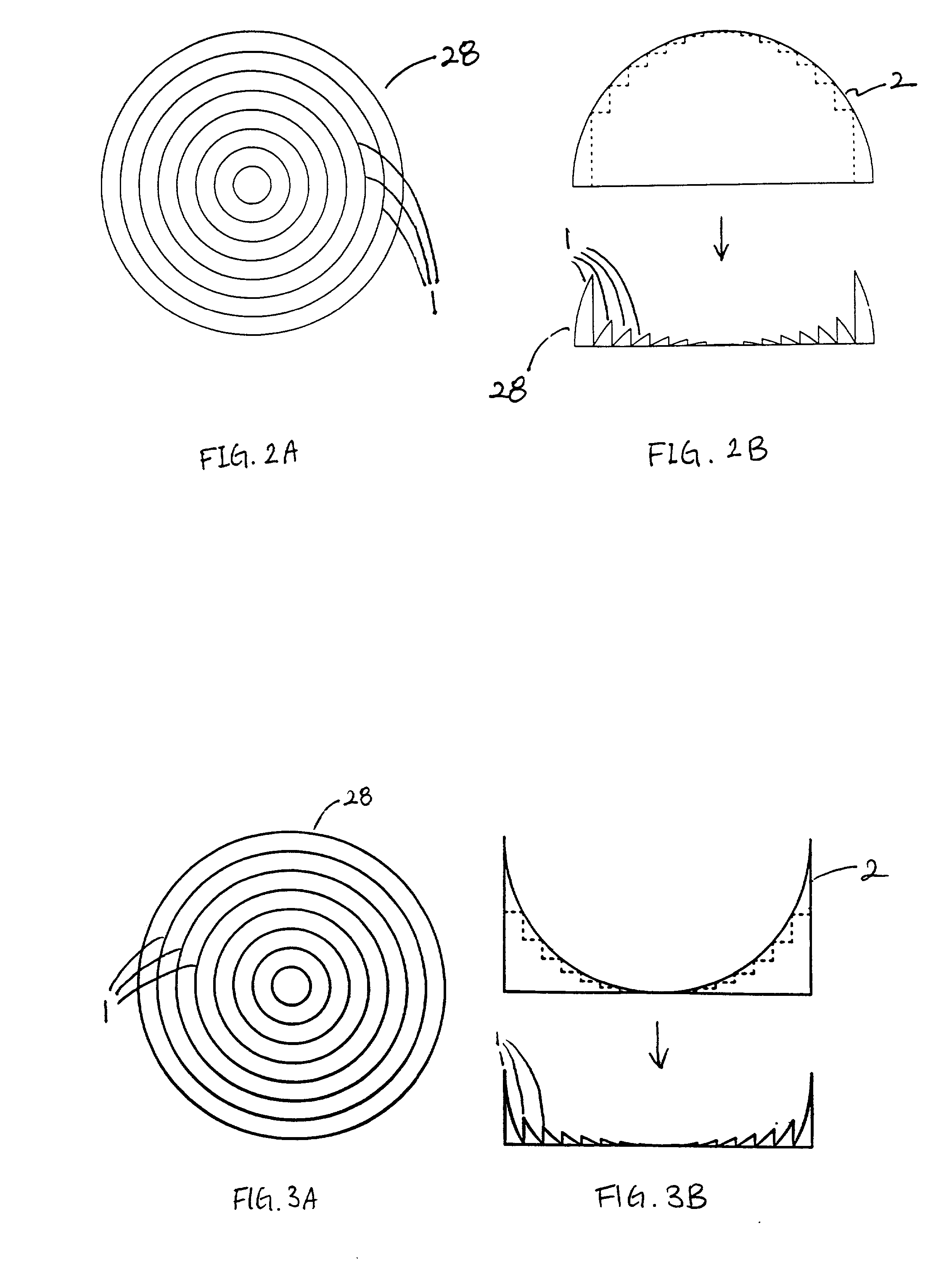

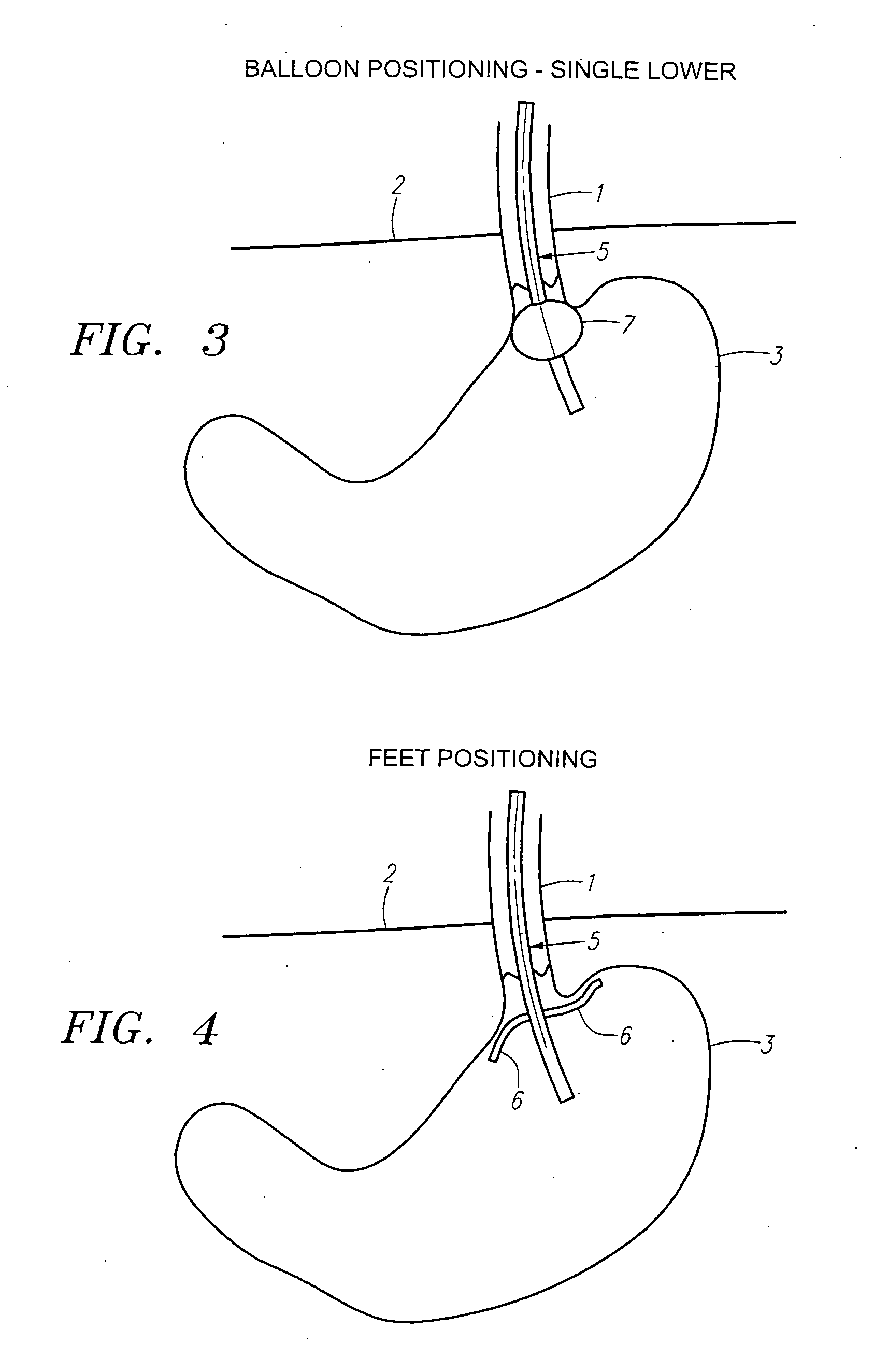

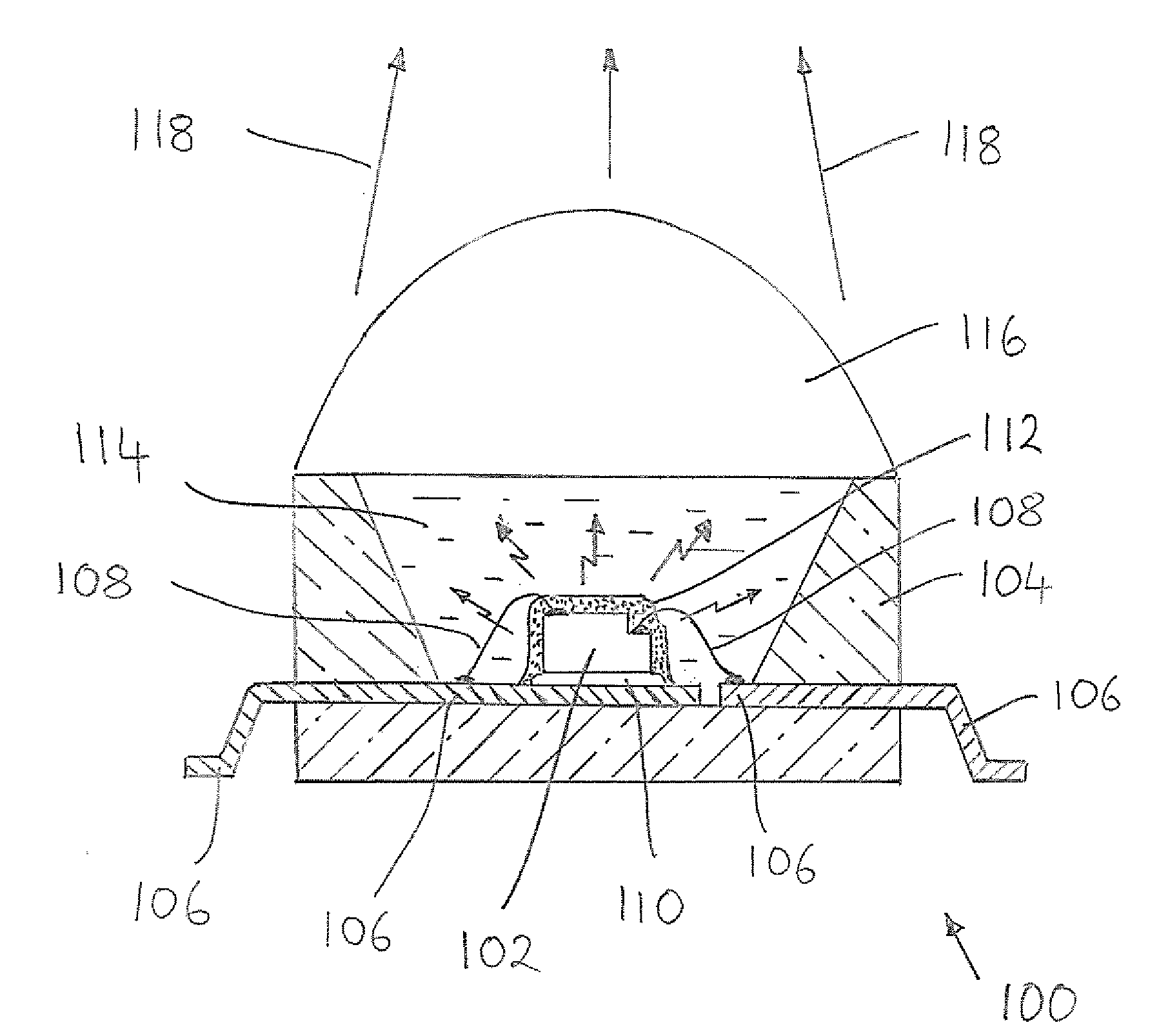

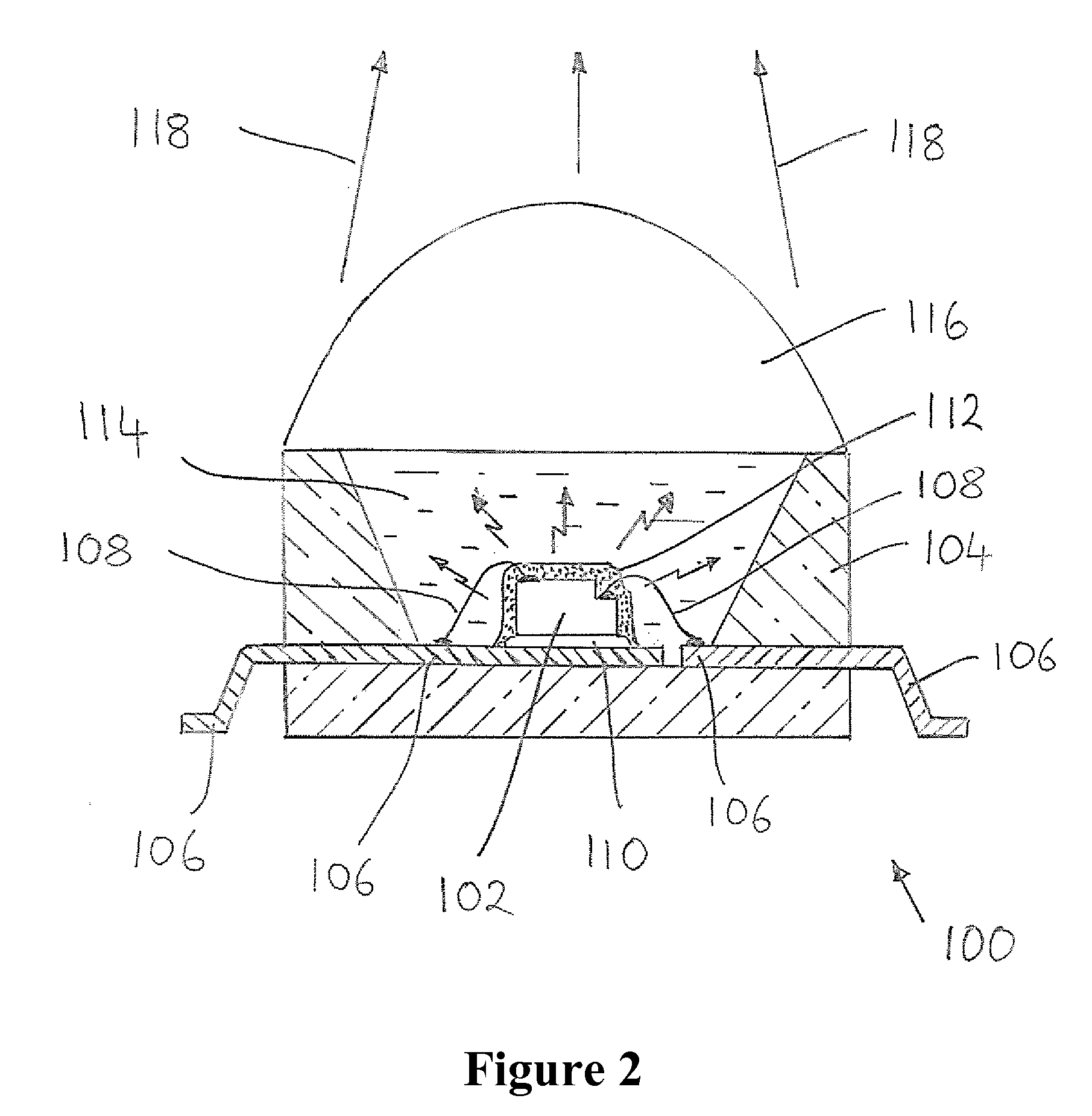

Forming an optical element on the surface of a light emitting device for improved light extraction

InactiveUS6987613B2Easy to integrateMaximize production efficiencyDiffraction gratingsSemiconductor devicesWafer bondingAlternative methods

Provided is a light emitting device including a Fresnel lens and / or a holographic diffuser formed on a surface of a semiconductor light emitter for improved light extraction, and a method for forming such light emitting device. Also provided is a light emitting device including an optical element stamped on a surface for improved light extraction and the stamping method used to form such device. An optical element formed on the surface of a semiconductor light emitter reduces reflective loss and loss due to total internal reflection, thereby improving light extraction efficiency. A Fresnel lens or a holographic diffuser may be formed on a surface by wet chemical etching or dry etching techniques, such as plasma etching, reactive ion etching, and chemically-assisted ion beam etching, optionally in conjunction with a lithographic technique. In addition, a Fresnel lens or a holographic diffuser may be milled, scribed, or ablated into the surface. Stamping, an alternative method for forming an optical element, can also be used to form a Fresnel lens or a holographic diffuser on the surface of a semiconductor light emitter. Stamping includes pressing a stamping block against the surface of a light emitting diode. The stamping block has a shape and pattern that are the inverse of the desired optical element. Optionally, stamping can be done before, after, or concurrently with wafer-bonding. Alternatively, a material can be stamped and later bonded to the semiconductor light emitter.

Owner:LUMILEDS

Forming an optical element on the surface of a light emitting device for improved light extraction

Provided is a light emitting device including a Fresnel lens and / or a holographic diffuser formed on a surface of a semiconductor light emitter for improved light extraction, and a method for forming such light emitting device. Also provided is a light emitting device including an optical element stamped on a surface for improved light extraction and the stamping method used to form such device. An optical element formed on the surface of a semiconductor light emitter reduces reflective loss and loss due to total internal reflection, thereby improving light extraction efficiency. A Fresnel lens or a holographic diffuser may be formed on a surface by wet chemical etching or dry etching techniques, such as plasma etching, reactive ion etching, and chemically-assisted ion beam etching, optionally in conjunction with a lithographic technique. In addition, a Fresnel lens or a holographic diffuser may be milled, scribed, or ablated into the surface. Stamping, an alternative method for forming an optical element, can also be used to form a Fresnel lens or a holographic diffuser on the surface of a semiconductor light emitter. Stamping includes pressing a stamping block against the surface of a light emitting diode. The stamping block has a shape and pattern that are the inverse of the desired optical element. Optionally, stamping can be done before, after, or concurrently with wafer-bonding. Alternatively, a material can be stamped and later bonded to the semiconductor light emitter.

Owner:LUMILEDS

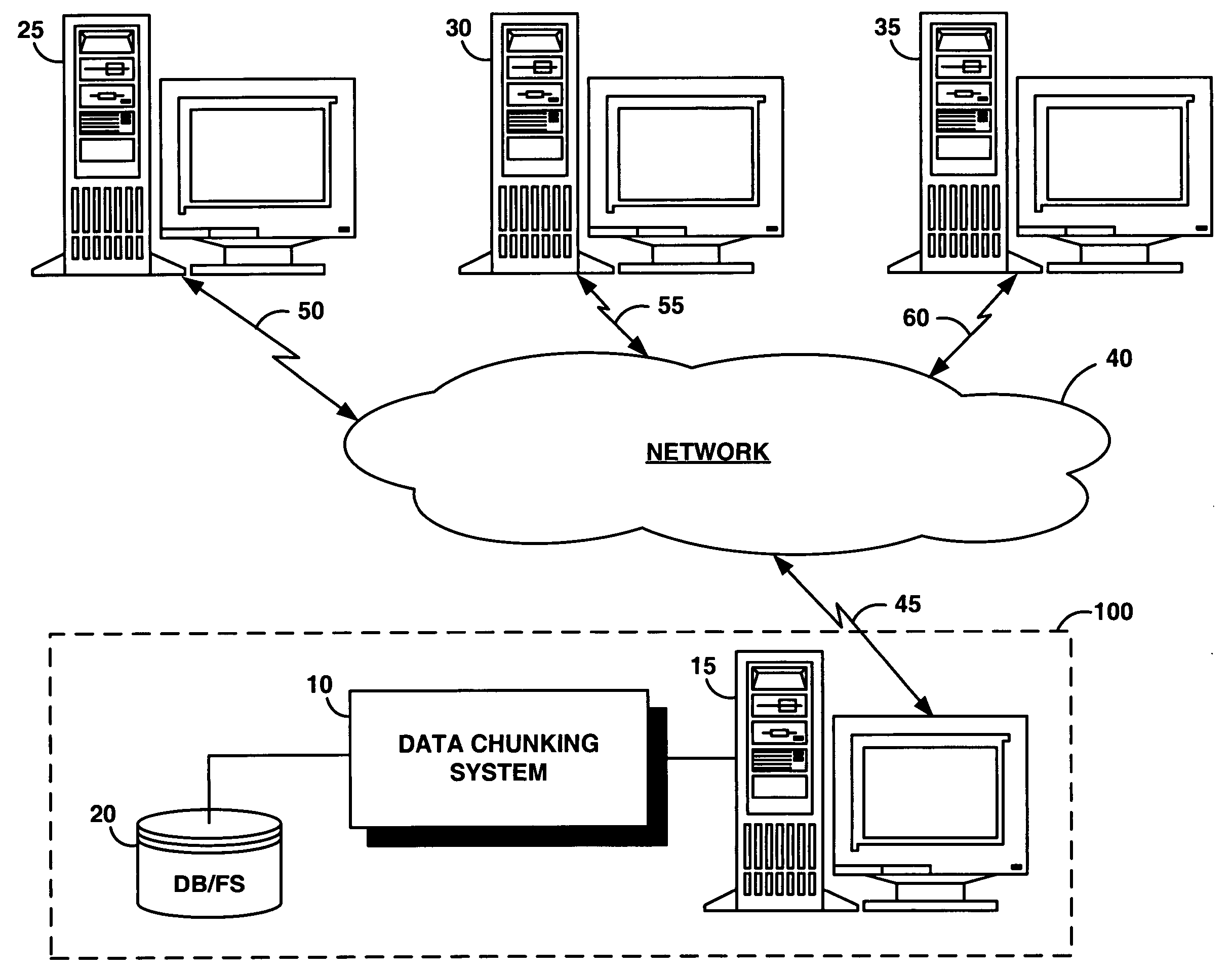

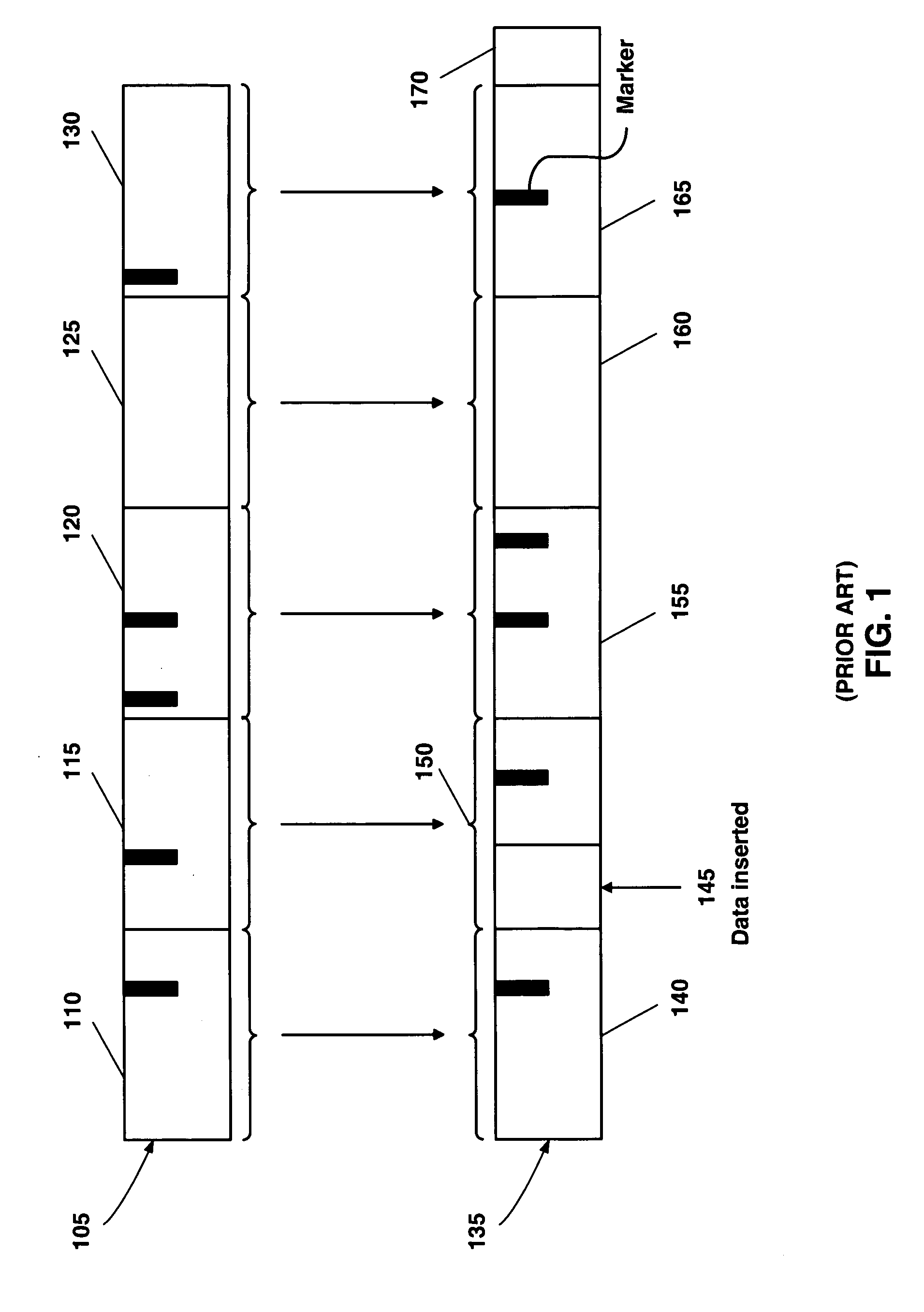

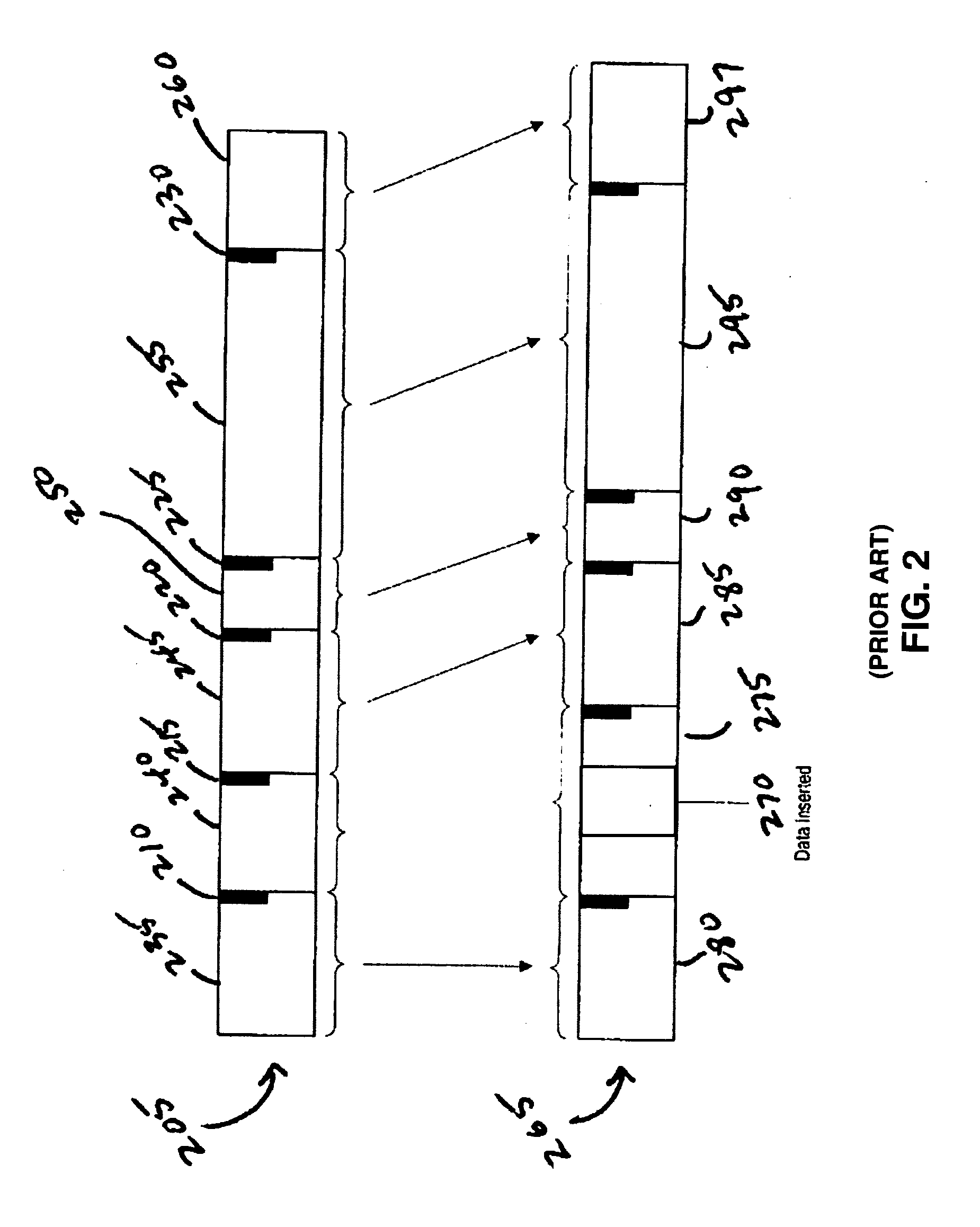

System and method for dividing data into predominantly fixed-sized chunks so that duplicate data chunks may be identified

InactiveUS20050091234A1Maximizes data storage efficiencyLow costData processing applicationsDigital data information retrievalData matchingTheoretical computer science

A data chunking system divides data into predominantly fixed-sized chunks such that duplicate data may be identified. The data chunking system may be used to reduce the data storage and save network bandwidth by allowing storage or transmission of primarily unique data chunks. The system may also be used to increase reliability in data storage and network transmission, by allowing an error affecting a data chunk to be repaired with an identified duplicate chunk. The data chunking system chunks data by selecting a chunk of fixed size, then moving a window along the data until a match to existing data is found. As the window moves across the data, unique chunks predominantly of fixed size are formed in the data passed over. Several embodiments provide alternate methods of determining whether a selected chunk matches existing data and methods by which the window is moved through the data. To locate duplicate data, the data chunking system remembers data by computing a mathematical function of a data chunk and inserting the computed value into a hash table.

Owner:IBM CORP

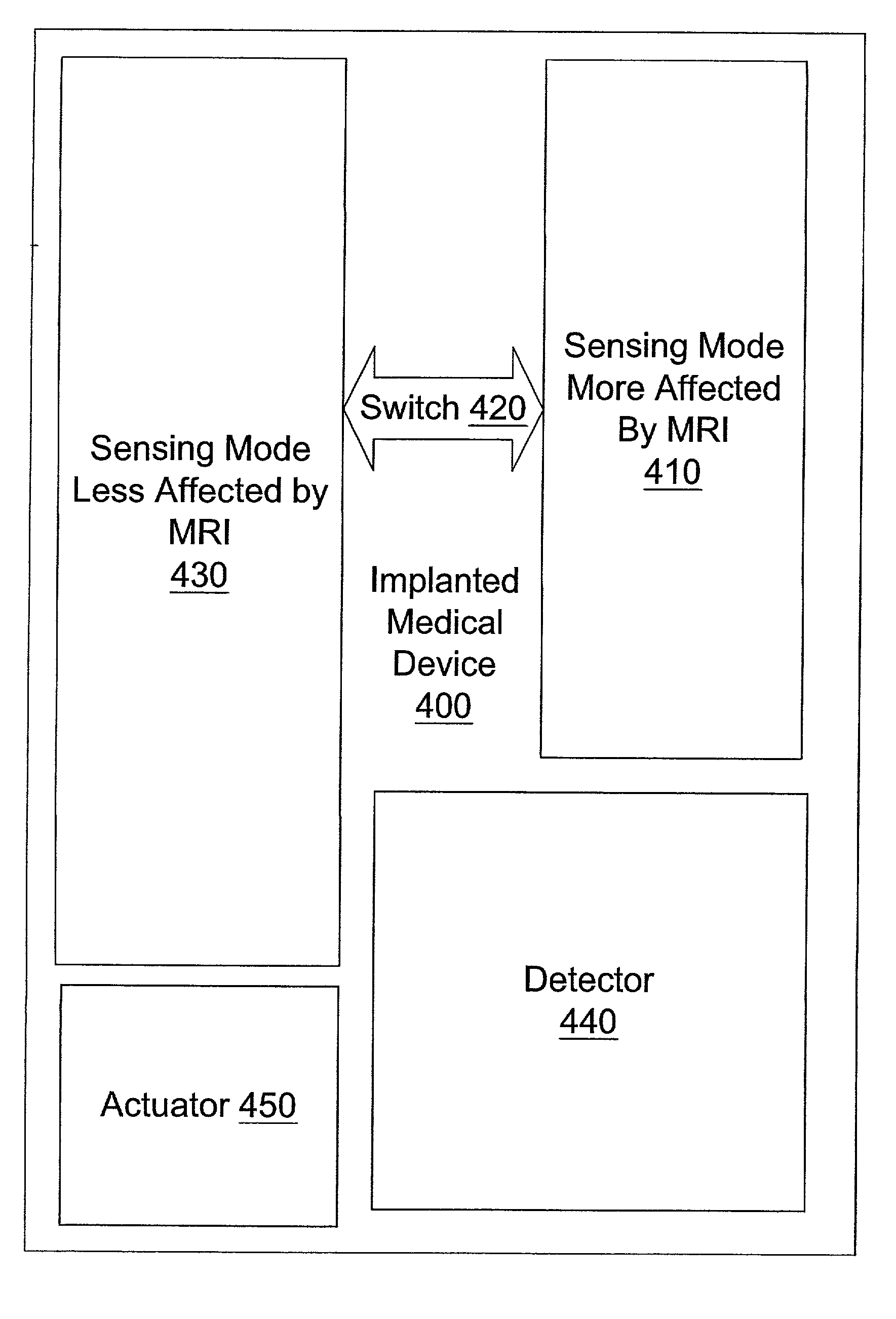

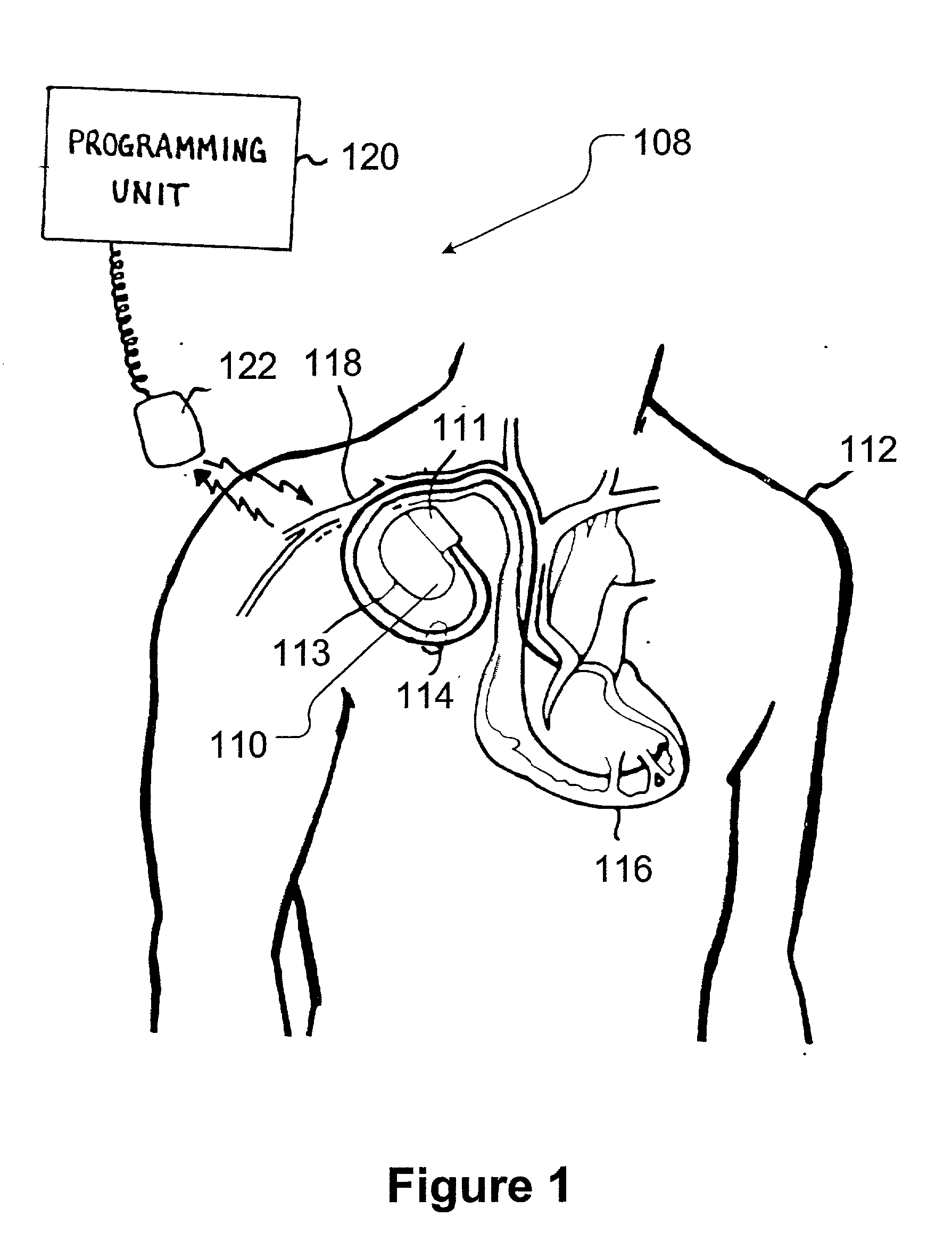

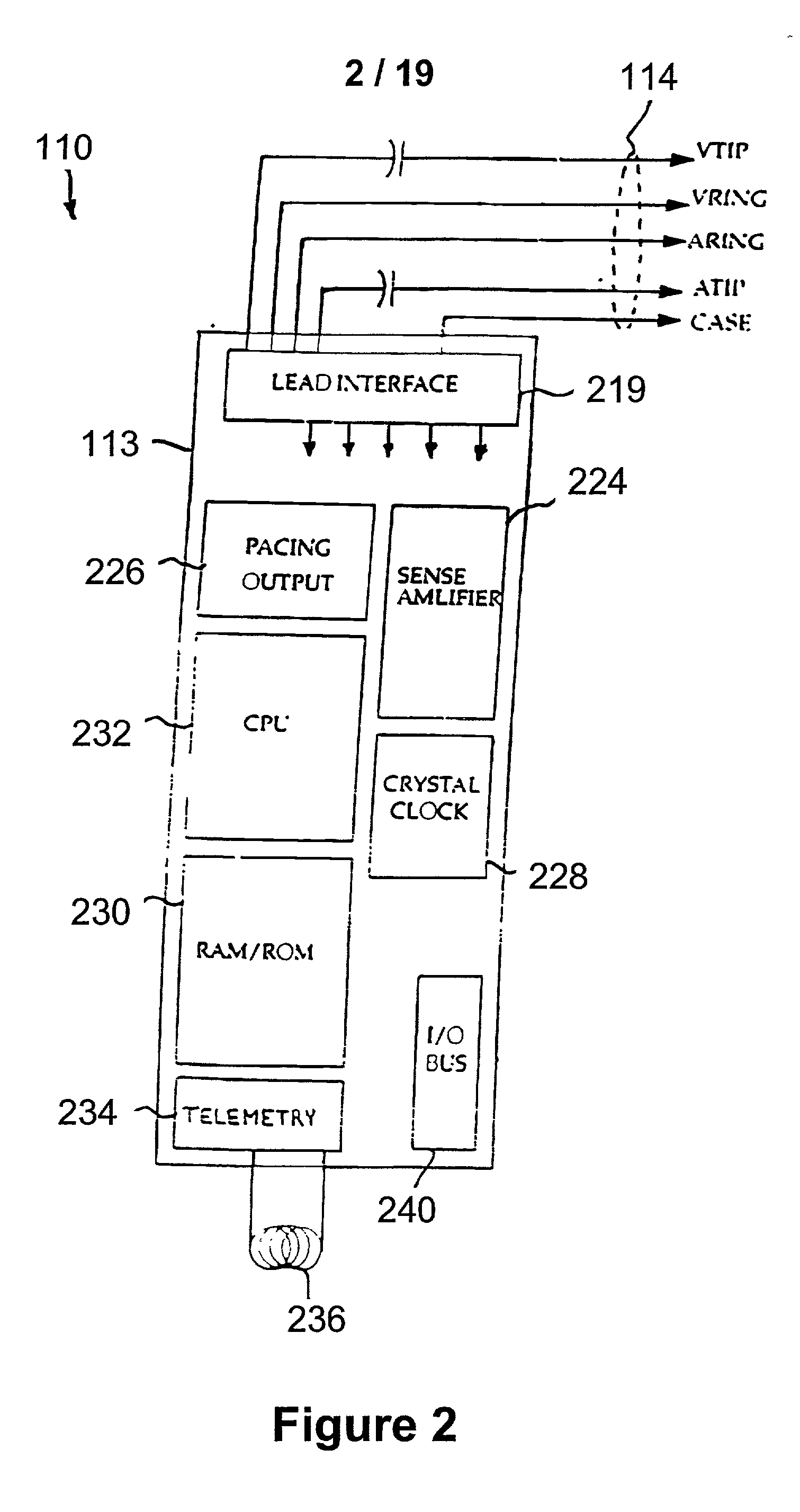

Alternative sensing method for implantable medical device in magnetic resonance imaging device

A method is provided, the method comprising detecting a magnetic resonance imaging (MRI) interference signal and enabling at least one preventive measure to protect an implantable medical device from interference by the magnetic resonance imaging (MRI) interference signal. The method also comprises switching from a first sensing mode more affected by the magnetic resonance imaging (MRI) interference signal to a second sensing mode less affected by the magnetic resonance imaging (MRI) interference signal.

Owner:MEDTRONIC INC

Percutaneous endoscopic access tools for the spinal epidural space and related methods of treatment

InactiveUS20060206178A1Increases volume of deviceIncrease spacingCannulasDiagnosticsAlternative methodsSpinal epidural

Several alternative spinal access devices are described. A number of alternative methods for performing therapies in the spinal region using the described spinal access devices are also described.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

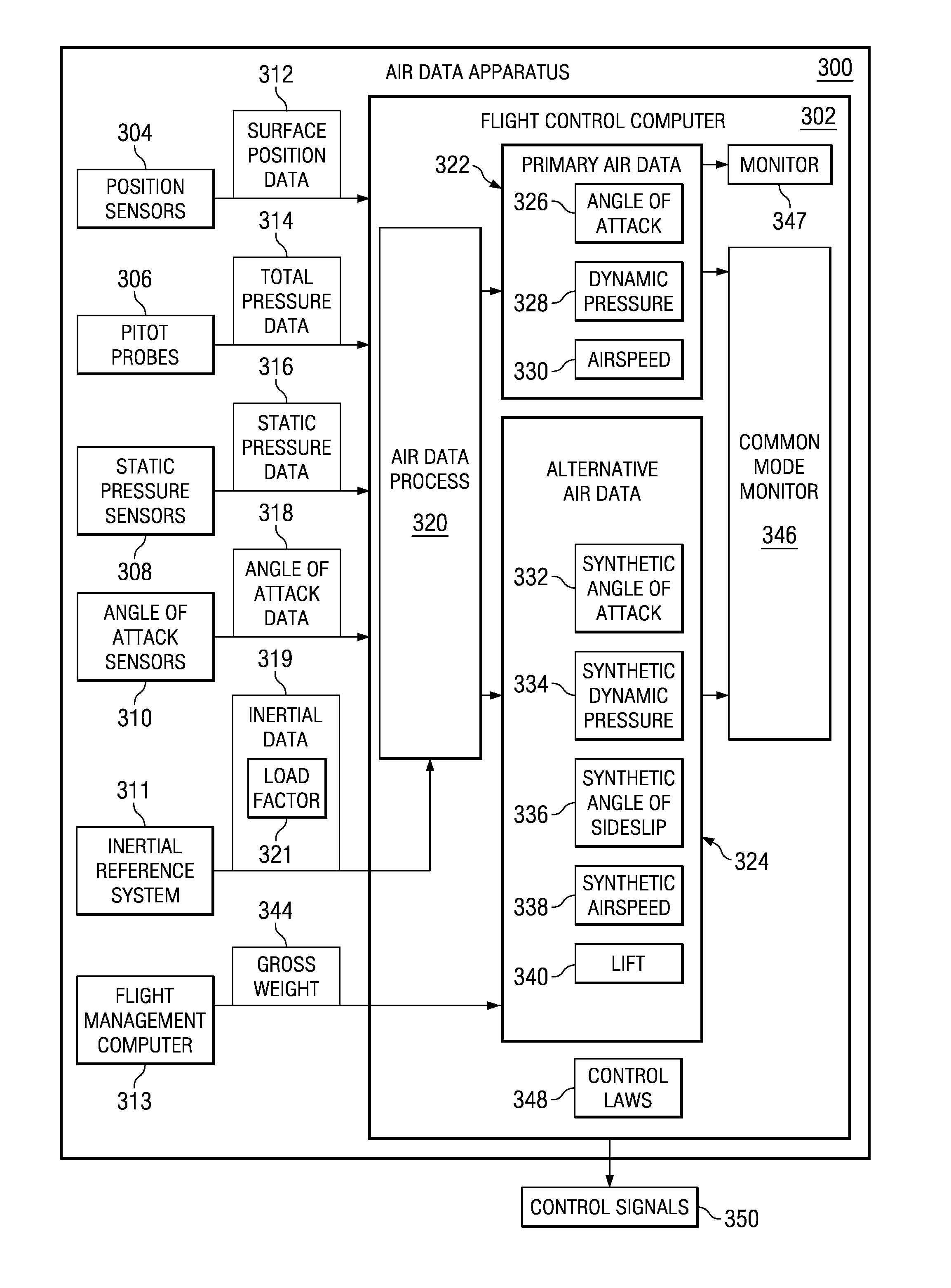

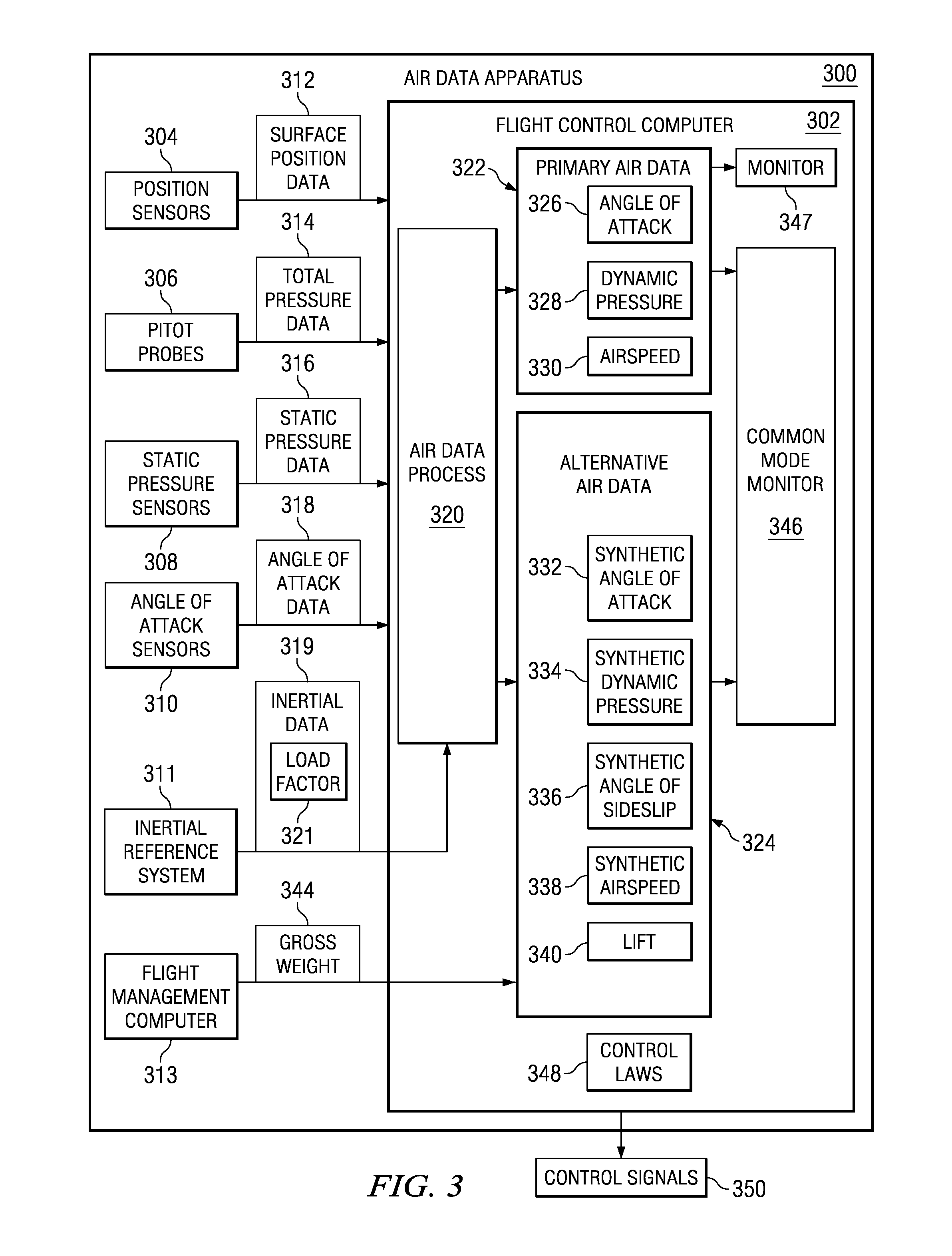

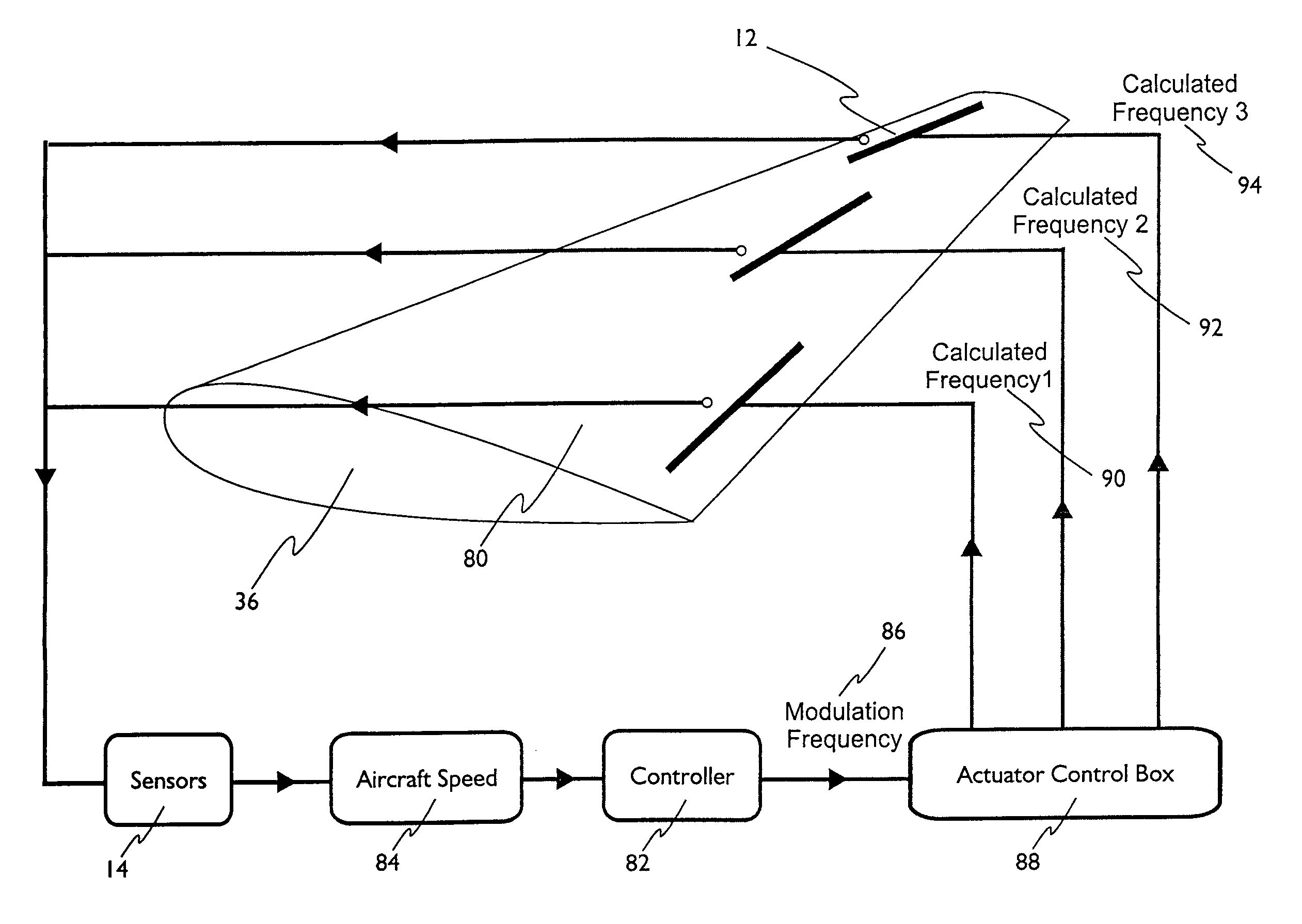

Alternative method to determine the air mass state of an aircraft and to validate and augment the primary method

ActiveUS20100100260A1Aircraft controlDigital data processing detailsFlight vehicleAlternative methods

A method, apparatus, and computer program product for identifying air data for an aircraft. The lift for the aircraft is identified. The number of surface positions for the aircraft is identified. The angle of attack during flight of the aircraft is identified. A synthetic dynamic pressure is computed from the lift, the number of surface positions, and the angle of attack.

Owner:THE BOEING CO

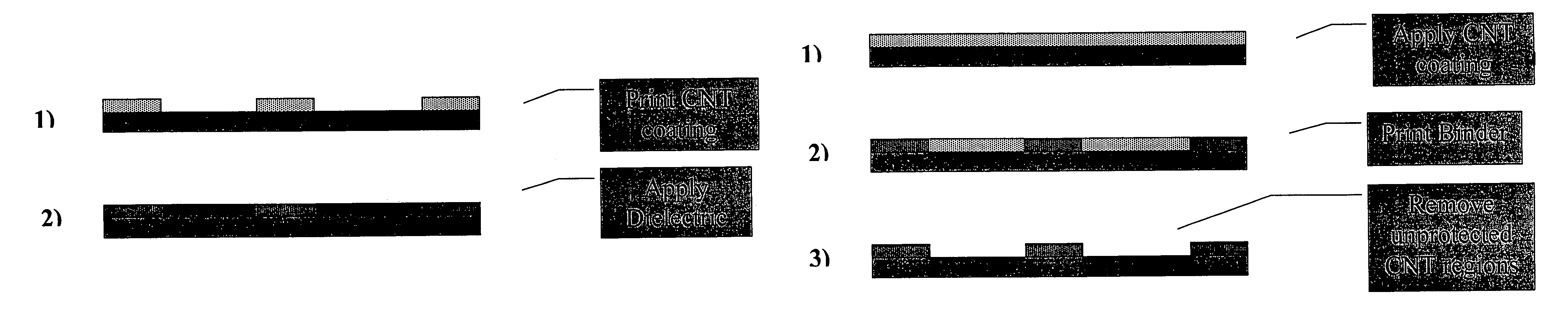

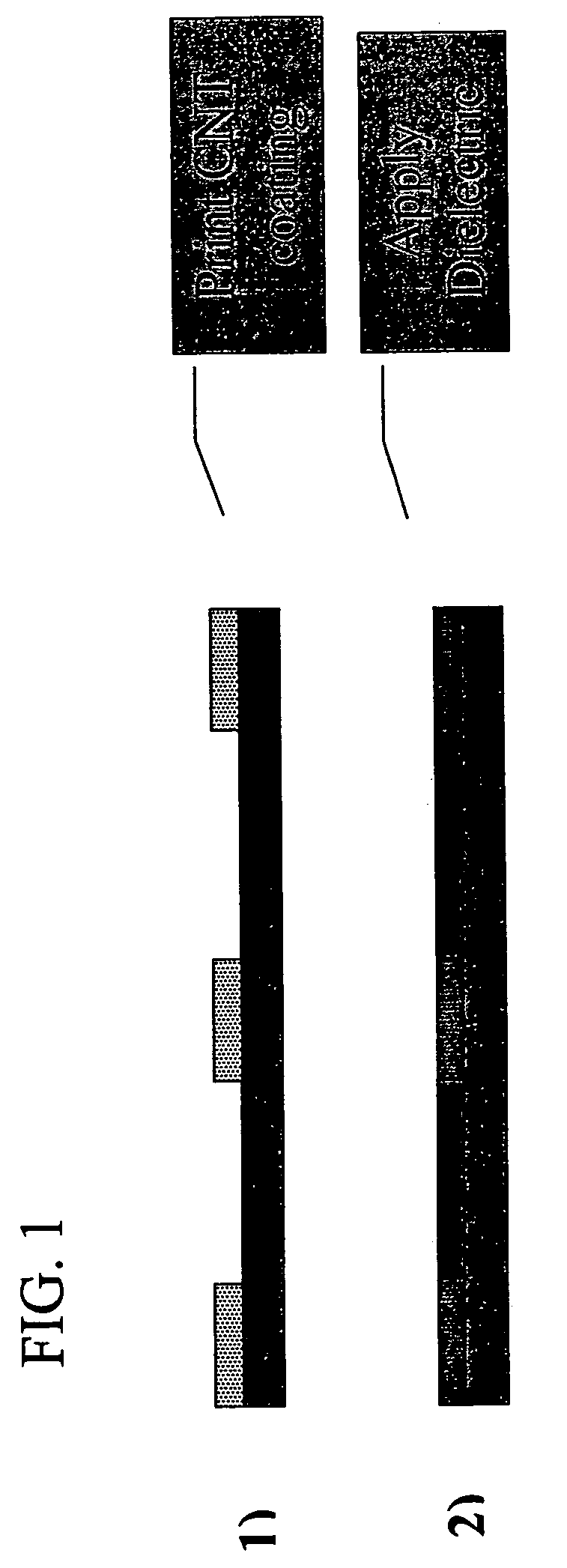

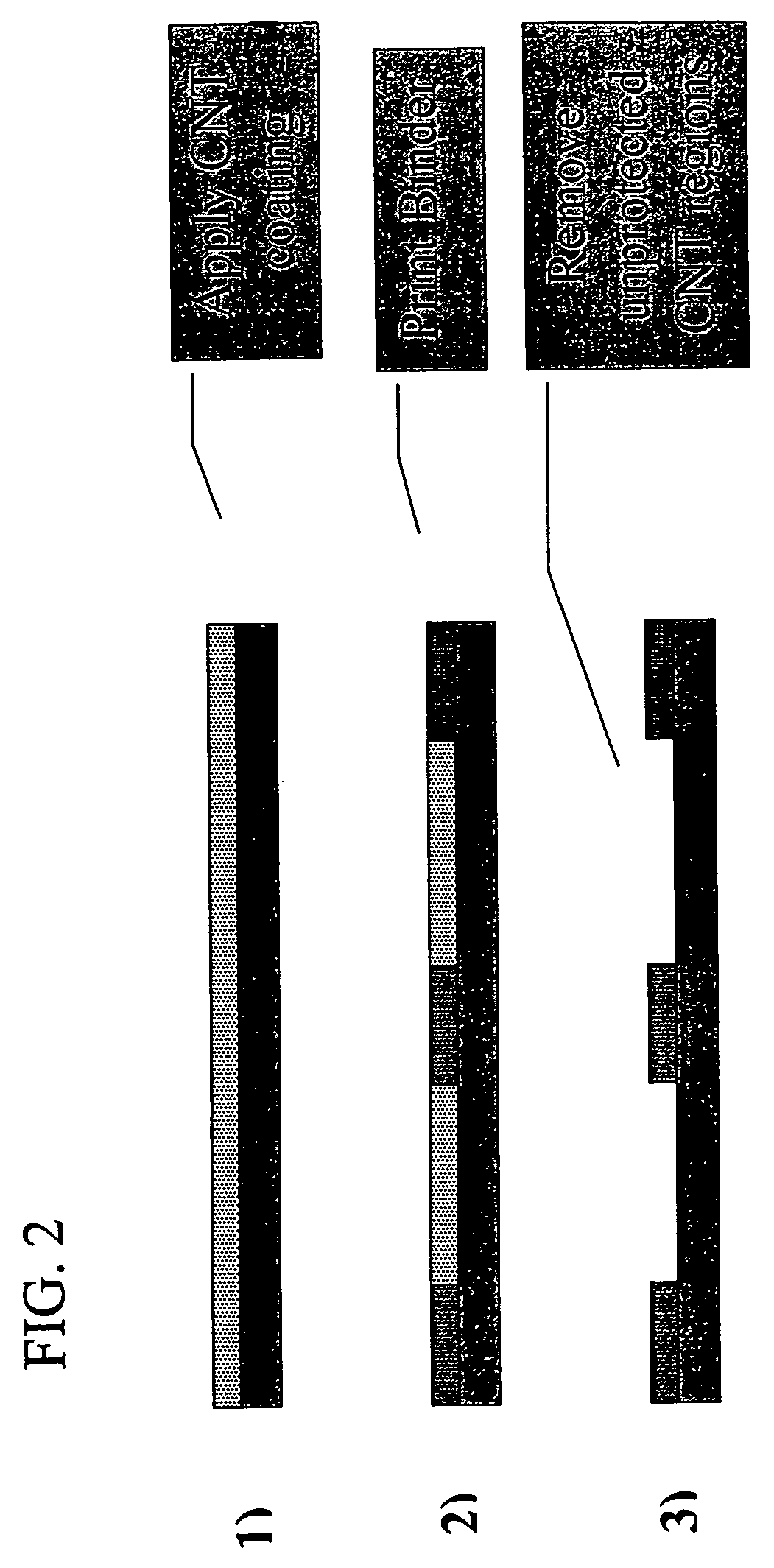

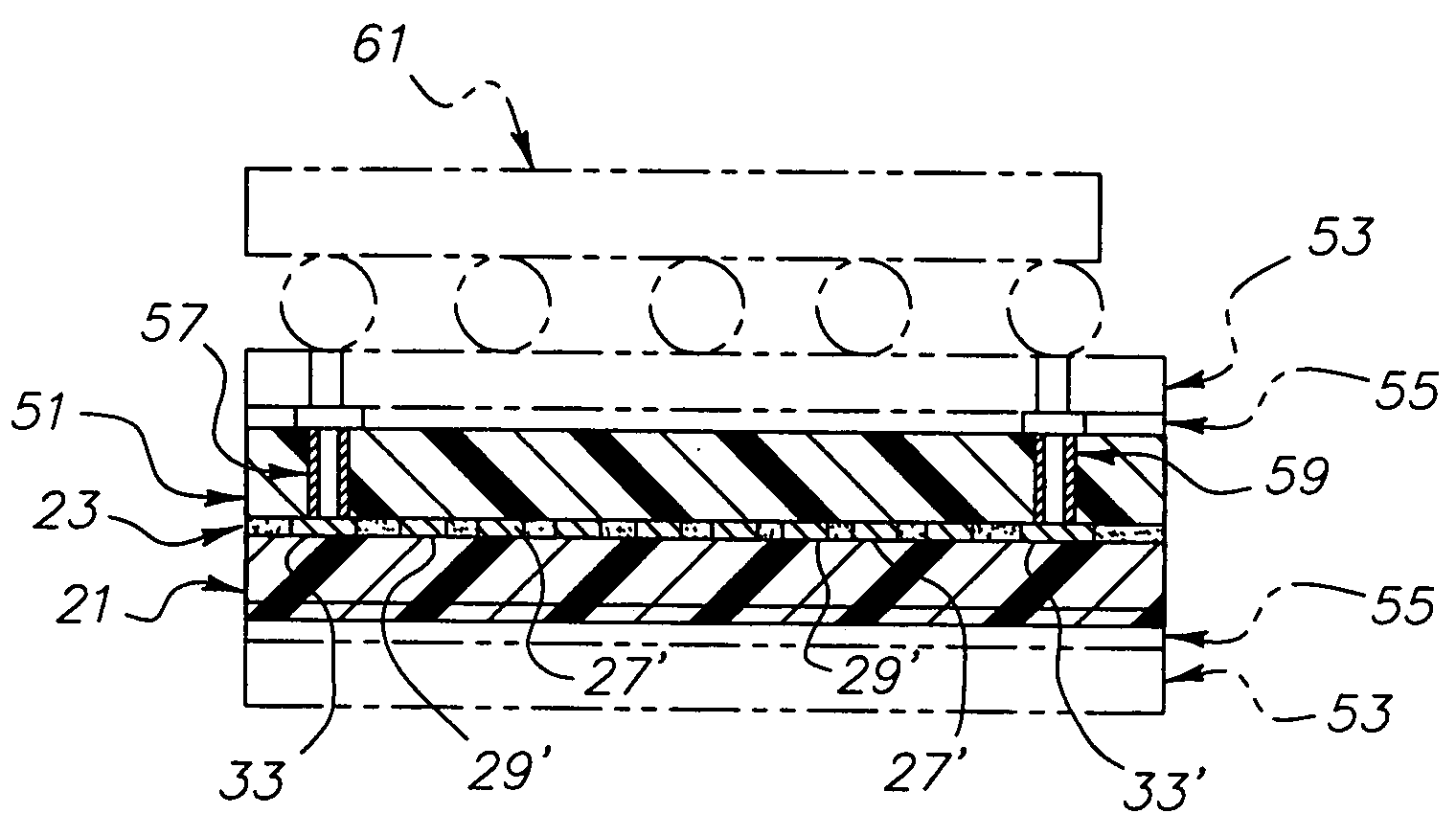

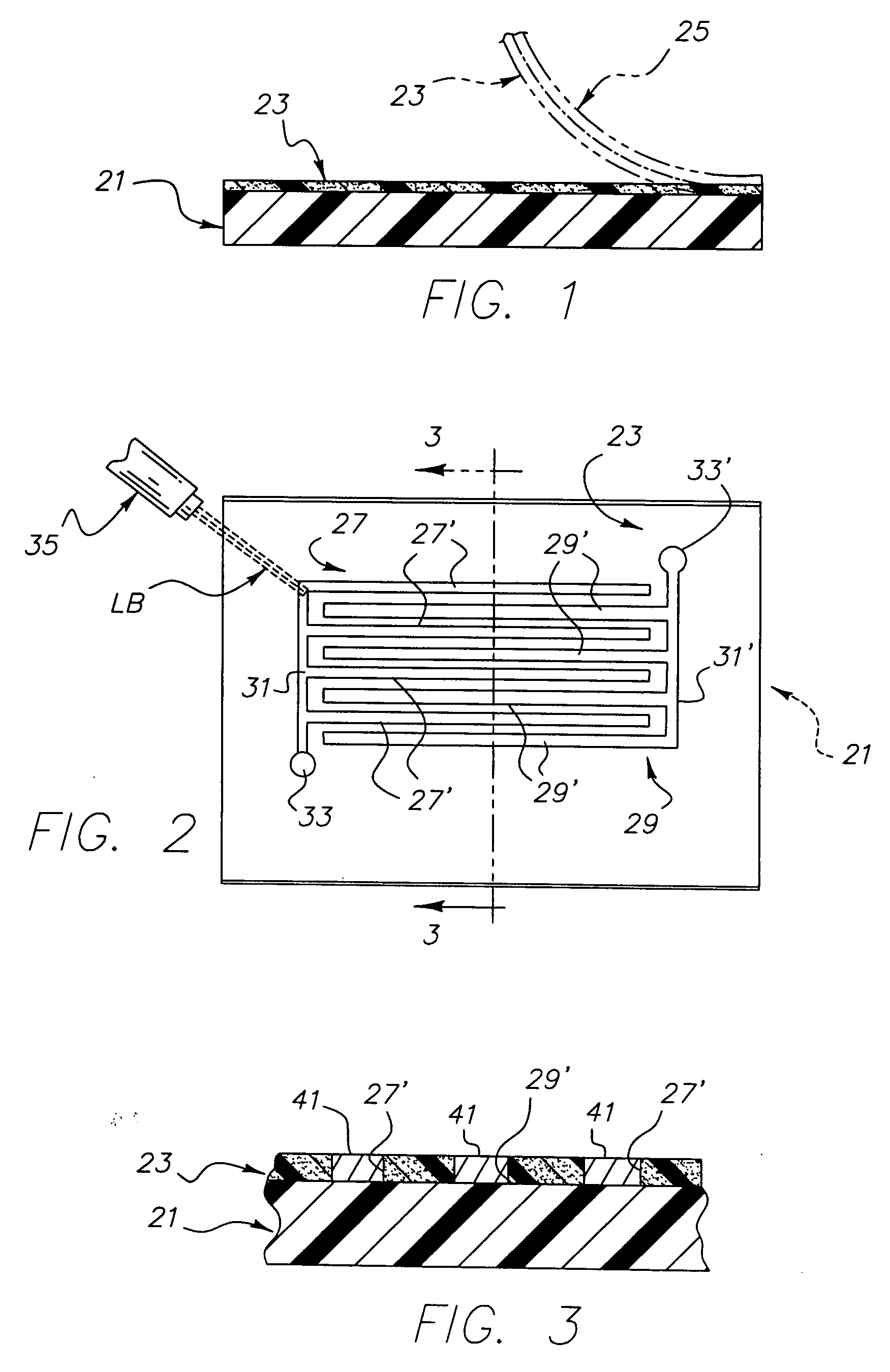

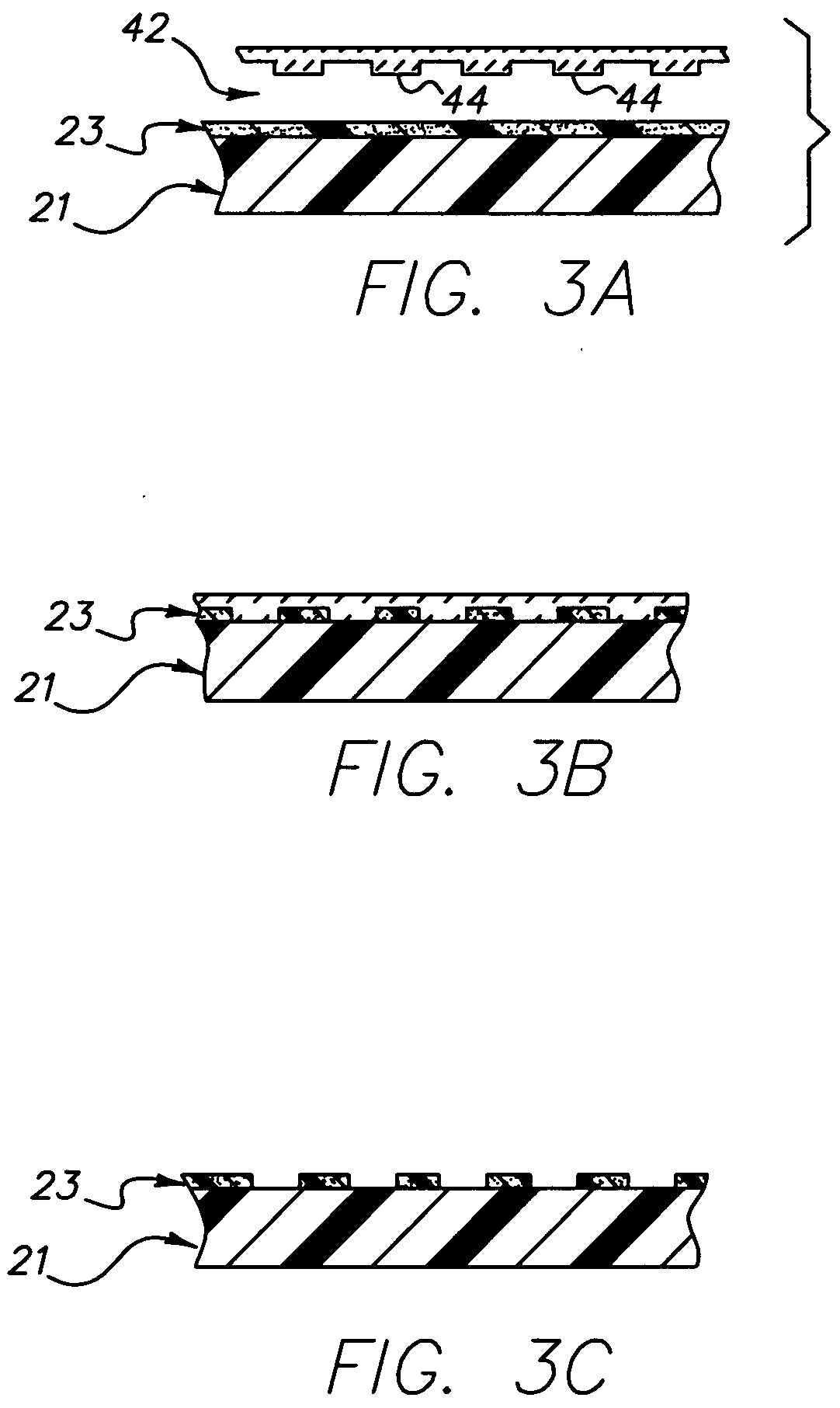

Method for patterning carbon nanotube coating and carbon nanotube wiring

A method for making a nanocomposite electrode or circuit pattern includes forming a continuous carbon nanotube layer impregnated with a binder and patterning the binder resin using various printing or photo imaging techniques. An alternative method includes patterning the carbon nanotube layer using various printing or imaging techniques and subsequently applying a continuous coating of binder resin to the patterned carbon nanotube layer. Articles made from these patterned nanocomposite coatings include transparent electrodes and circuits for flat panel displays, photovoltaics, touch screens, electroluminescent lamps, and EMI shielding.

Owner:EIKOS

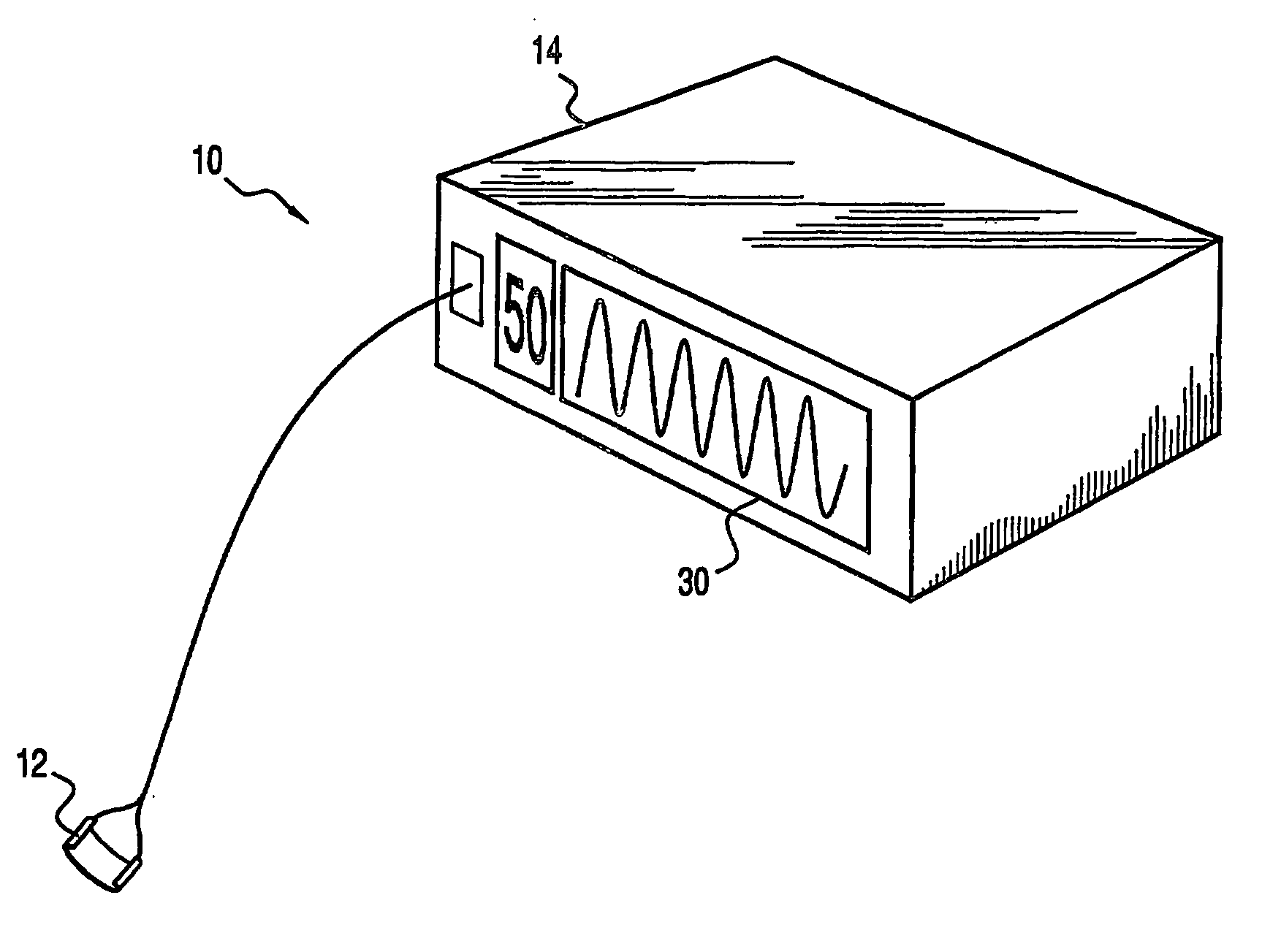

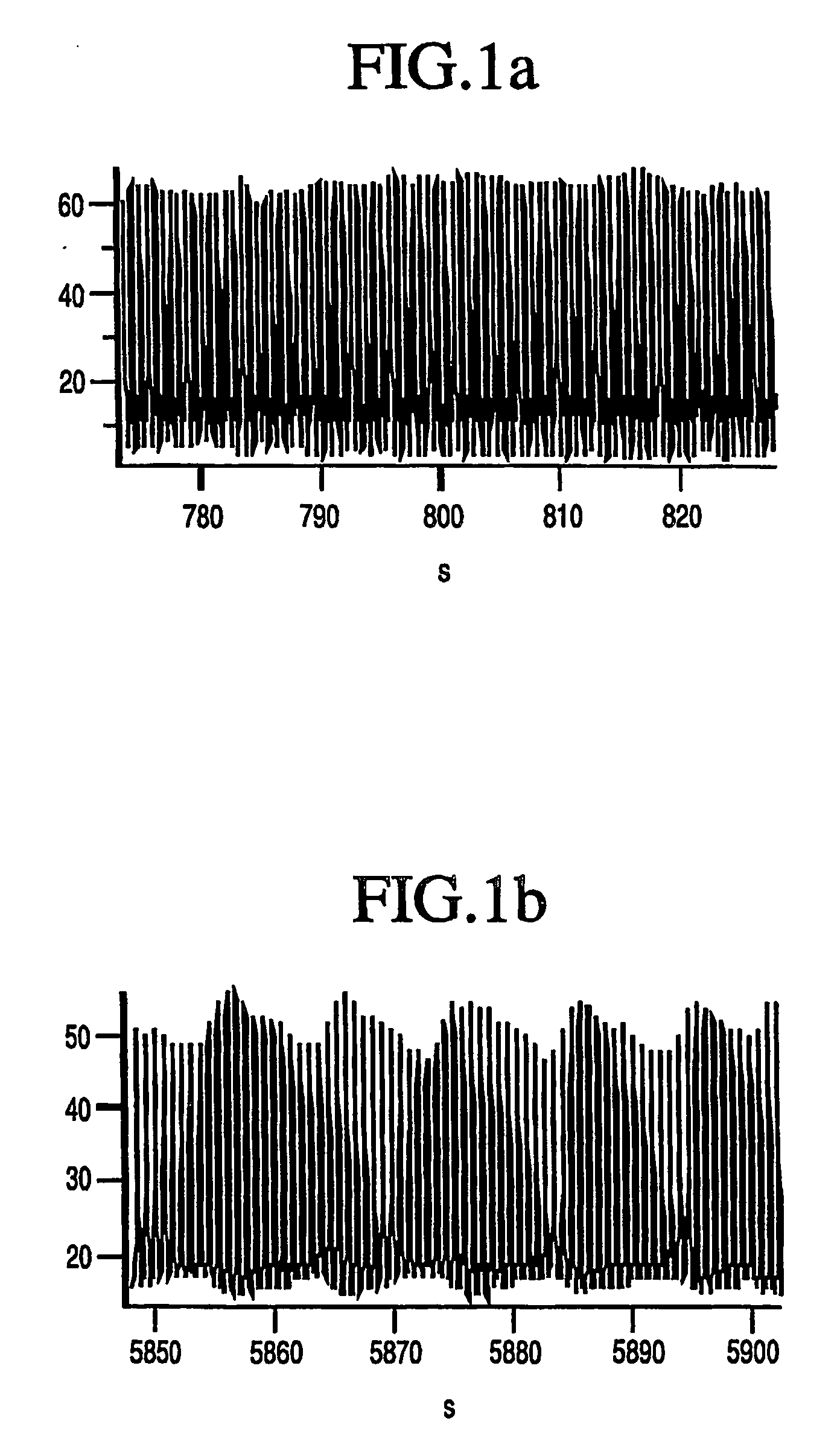

Method of assesing blood volume using photoelectric plethysmography

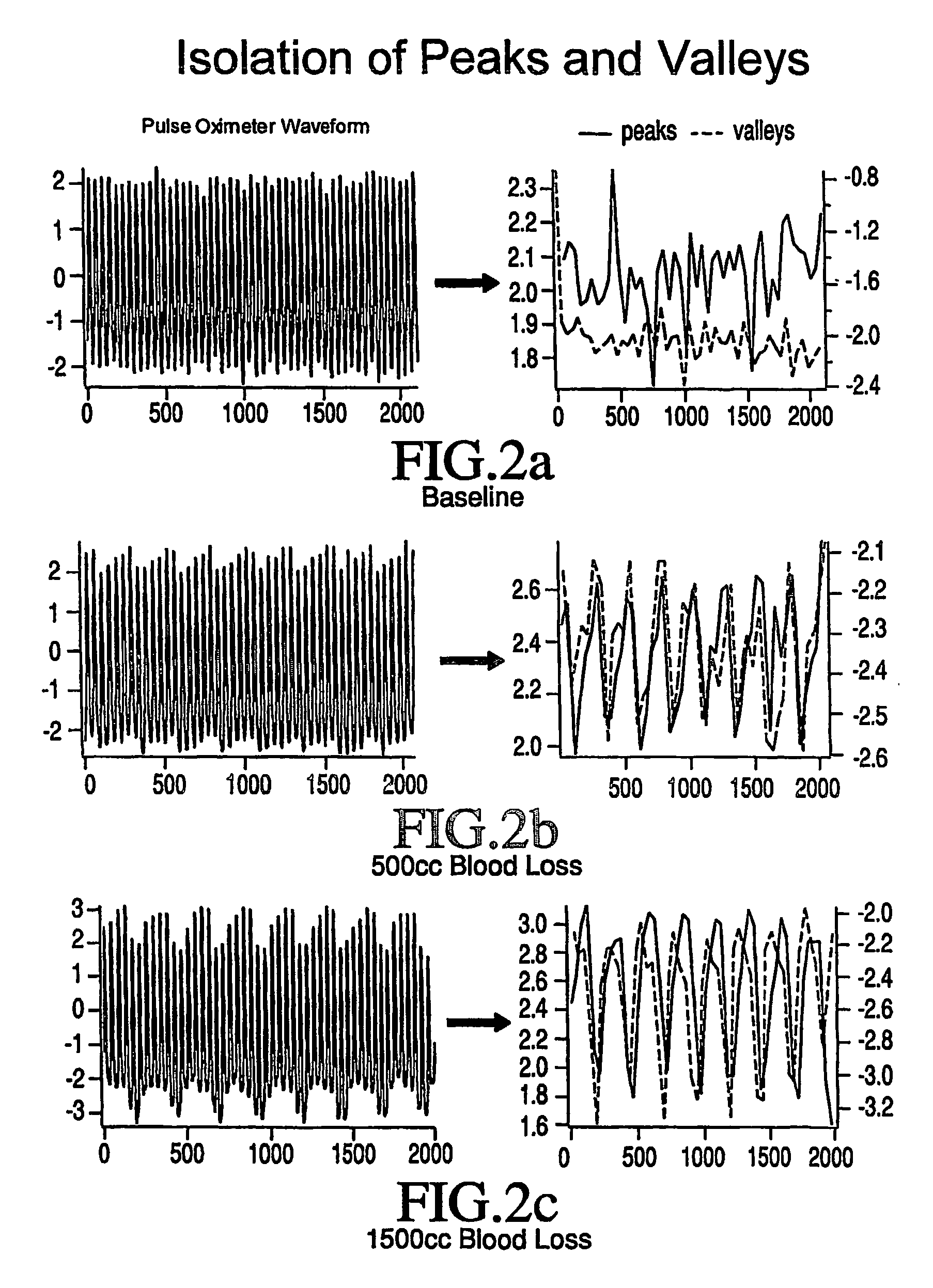

A method and system for assessing blood volume within a subject includes generating a cardiovascular waveform representing physiological characteristics of a subject and determining blood volume of the subject by analyzing the cardiovascular waveform. The step of analyzing includes generating a first trace of the per heart-beat maximums of the cardiovascular waveform, which is representative of the systolic pressure upon the cardiovascular signal, generating a second trace of the per heart-beat minimums of the cardiovascular waveform, which is representative of the diastolic pressure upon the cardiovascular signal, and comparing the respective first trace and the second trace to generate an estimate of relative blood volume within the subject. In accordance with an alternate method of analyzing harmonic analysis is applied to the cardiovascular waveform, extracting a frequency signal created by ventilation and applying the extracted frequency signal in determining blood volume of the subject.

Owner:SHELLEY KIRK H +2

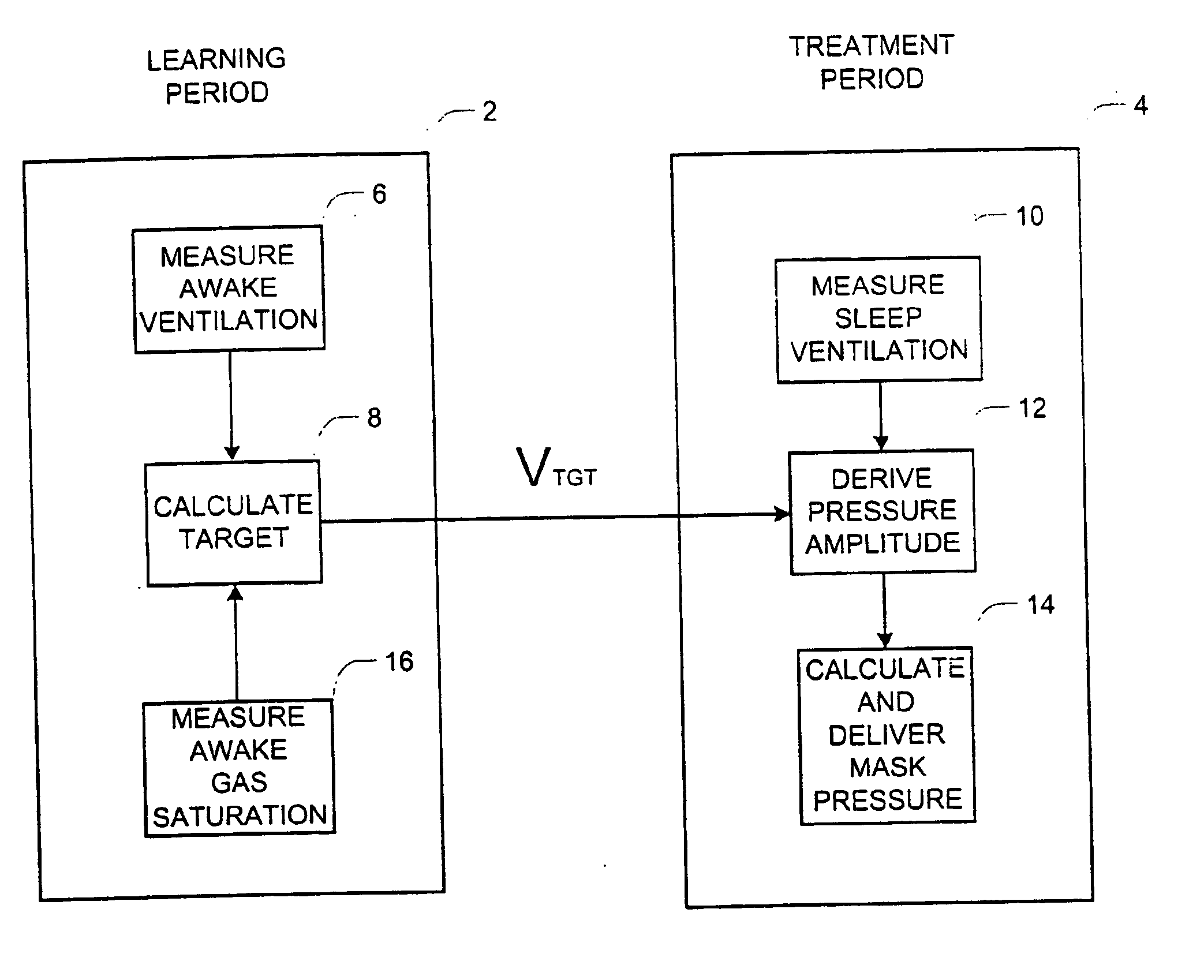

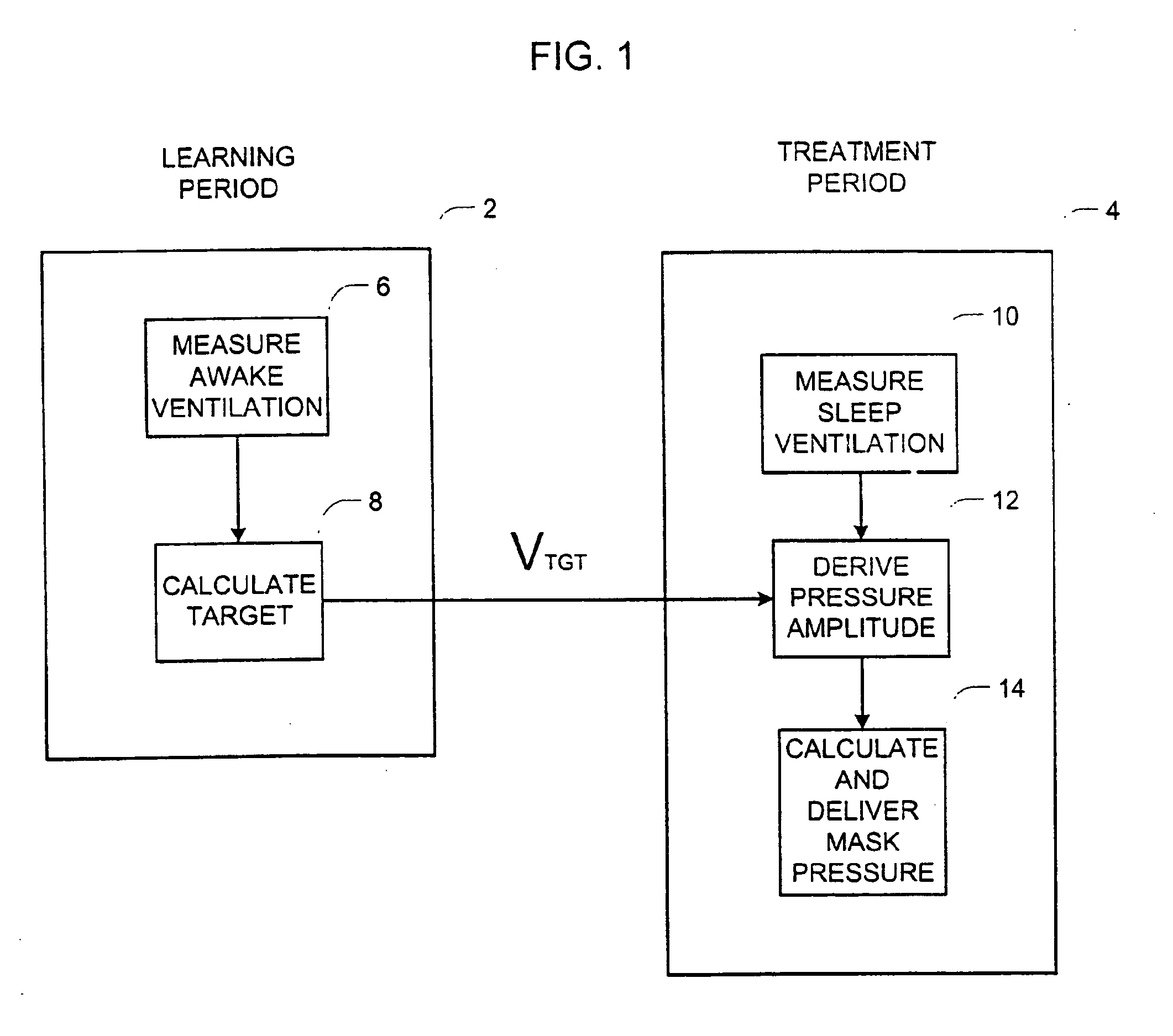

Determining suitable ventilator settings for patients with alveolar hypoventilation during sleep

InactiveUS6845773B2Well formedOperating means/releasing devices for valvesRespiratory masksAlveolar hypoventilationAlternative methods

A method and apparatus for determining suitable settings for a servo-ventilator to be used during sleep. Respiratory characteristics of a patient are measured during an awake learning period. With these measured characteristics, a target ventilation setting may be calculated by alternative methods. The calculated setting may then be used for enforcing a minimum ventilation during a treatment period where ventilatory support is provided with a servo-controlled ventilator.

Owner:RESMED LTD

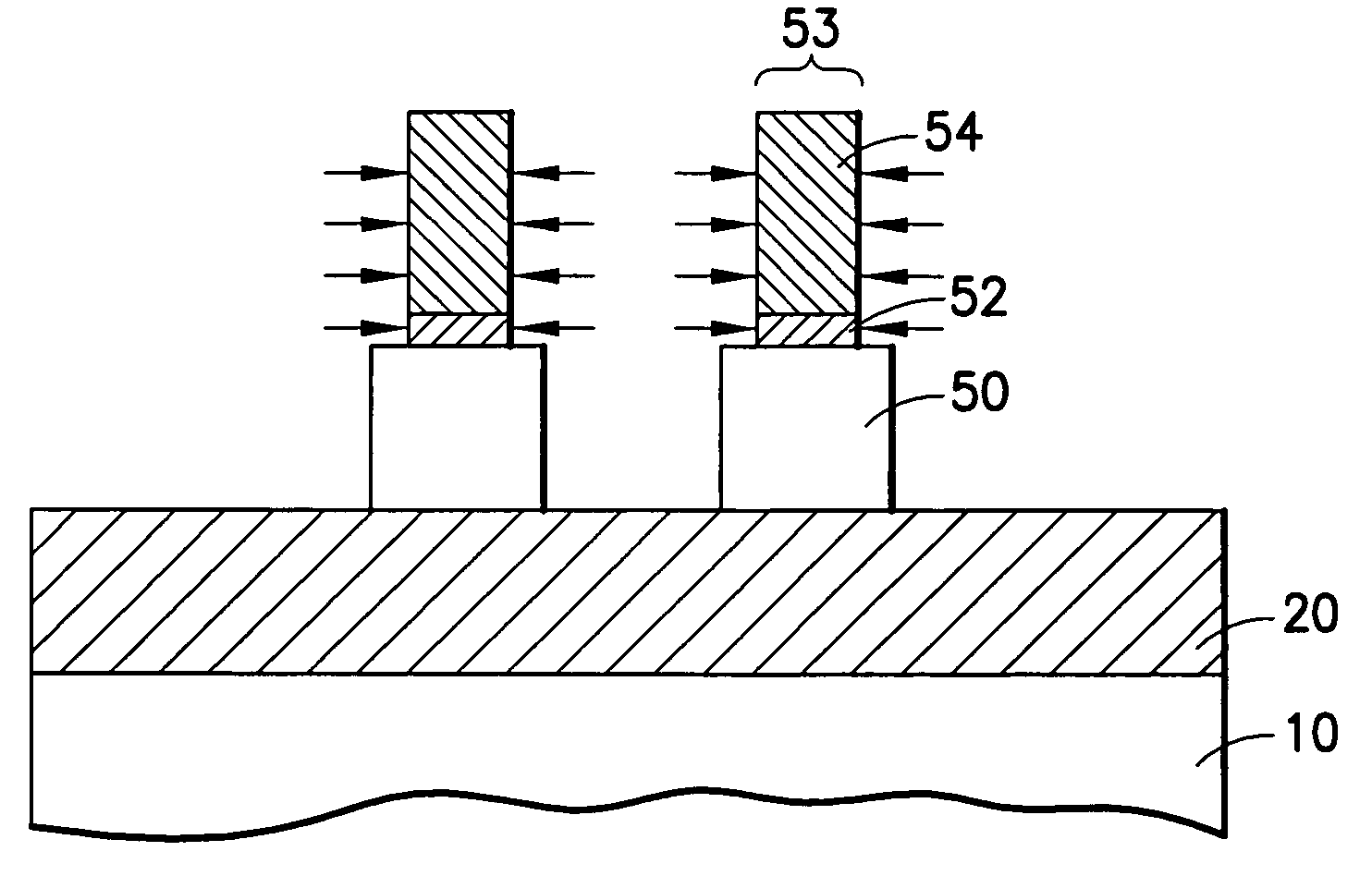

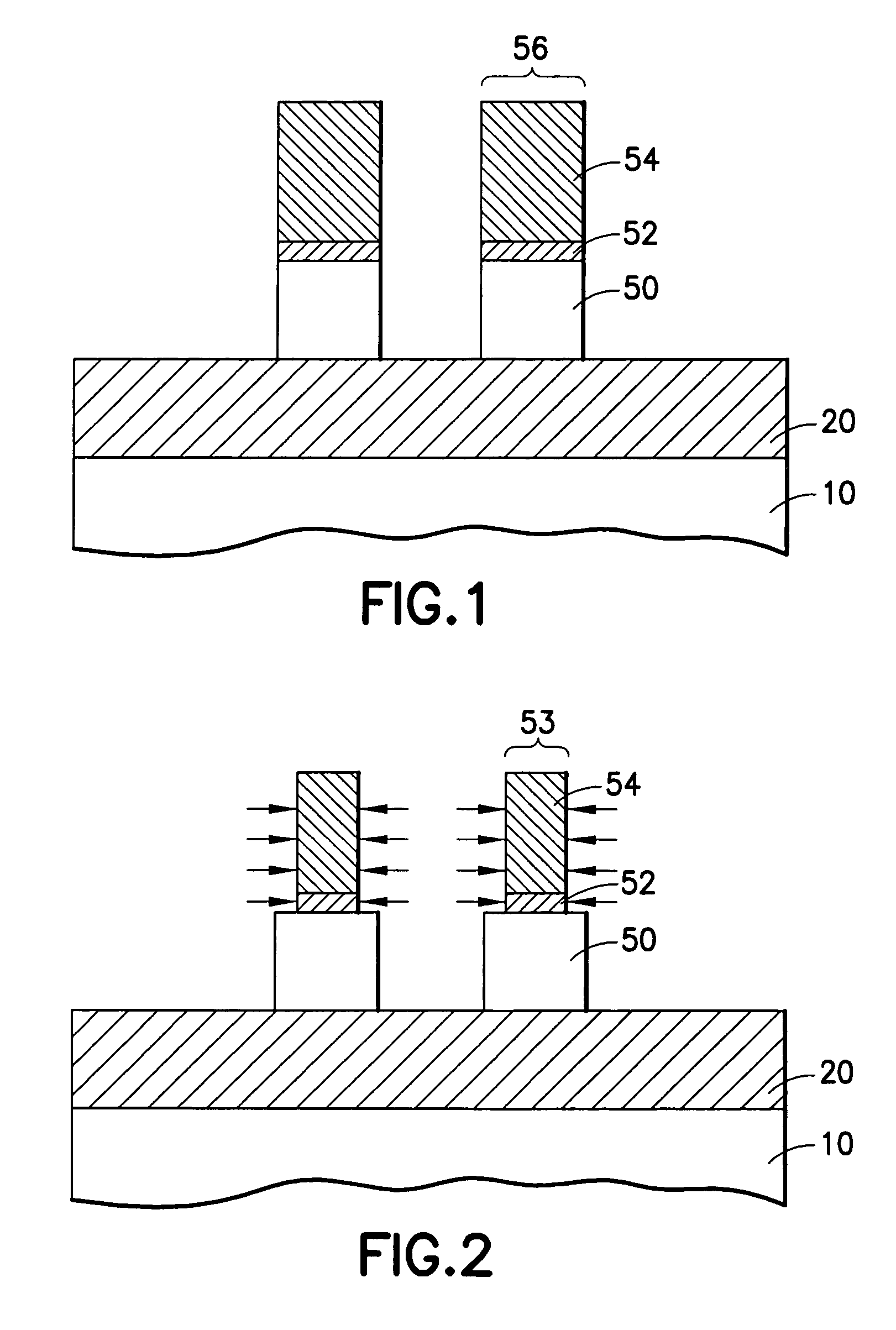

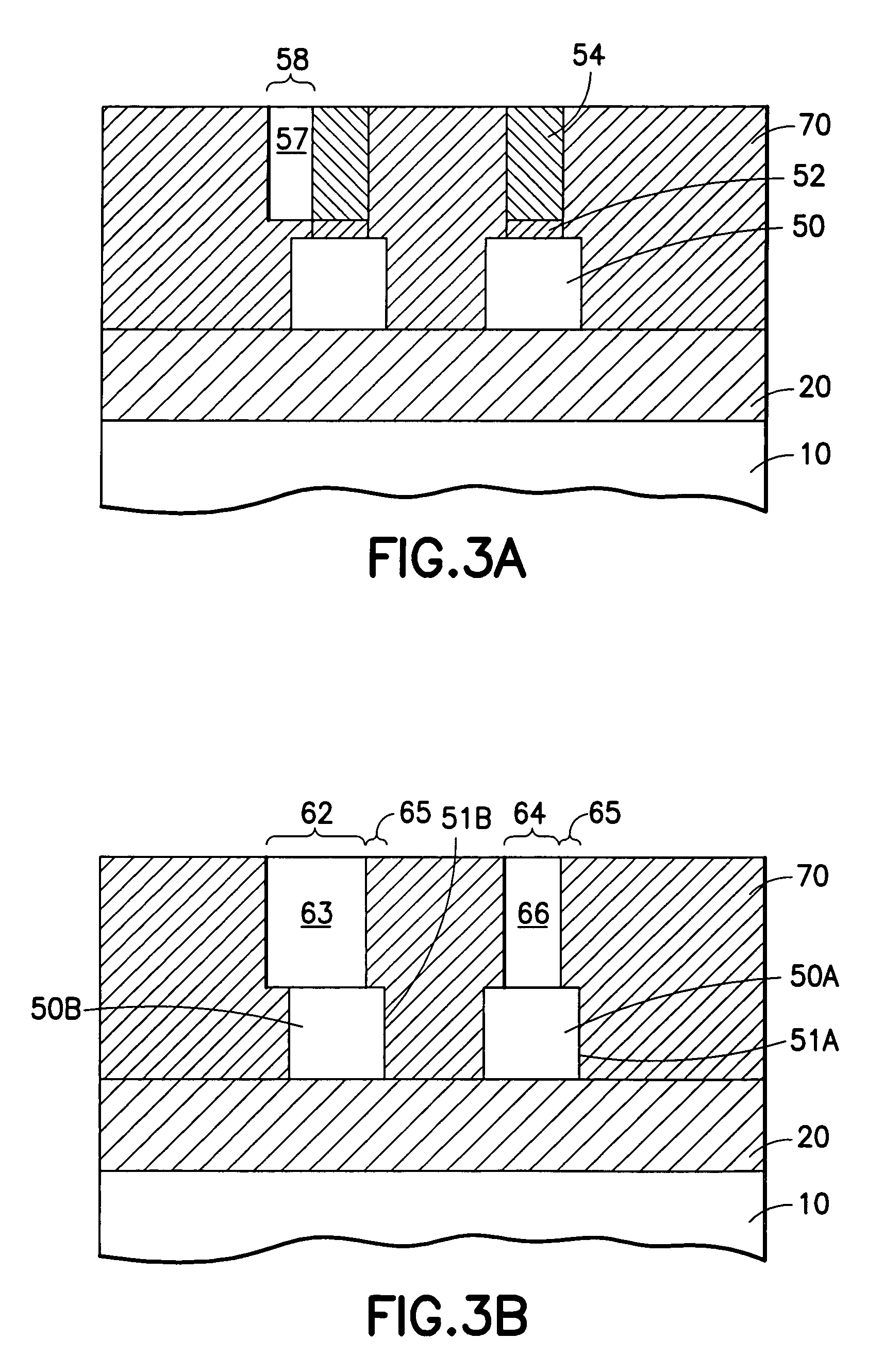

Layout decomposition for double patterning lithography

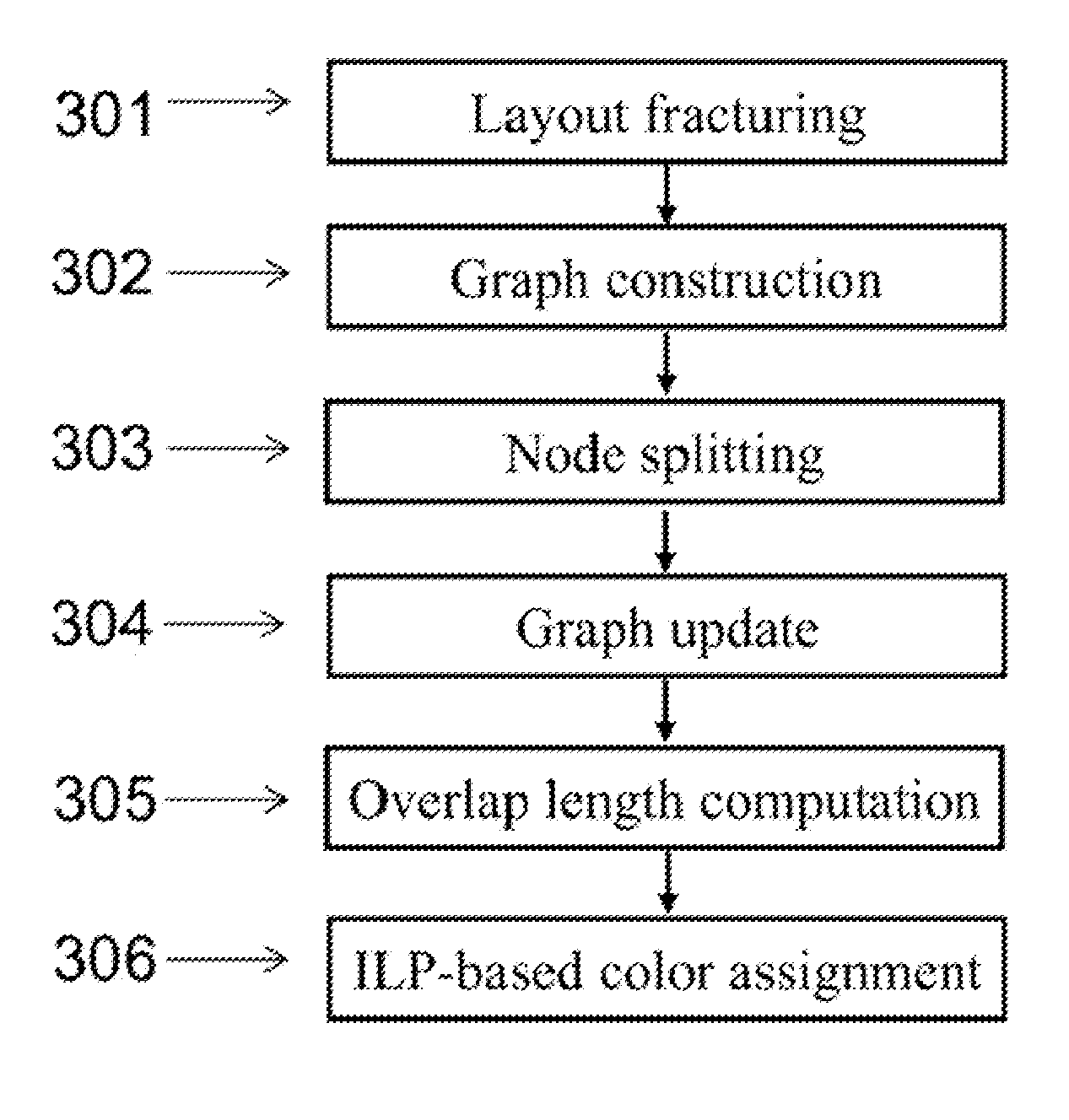

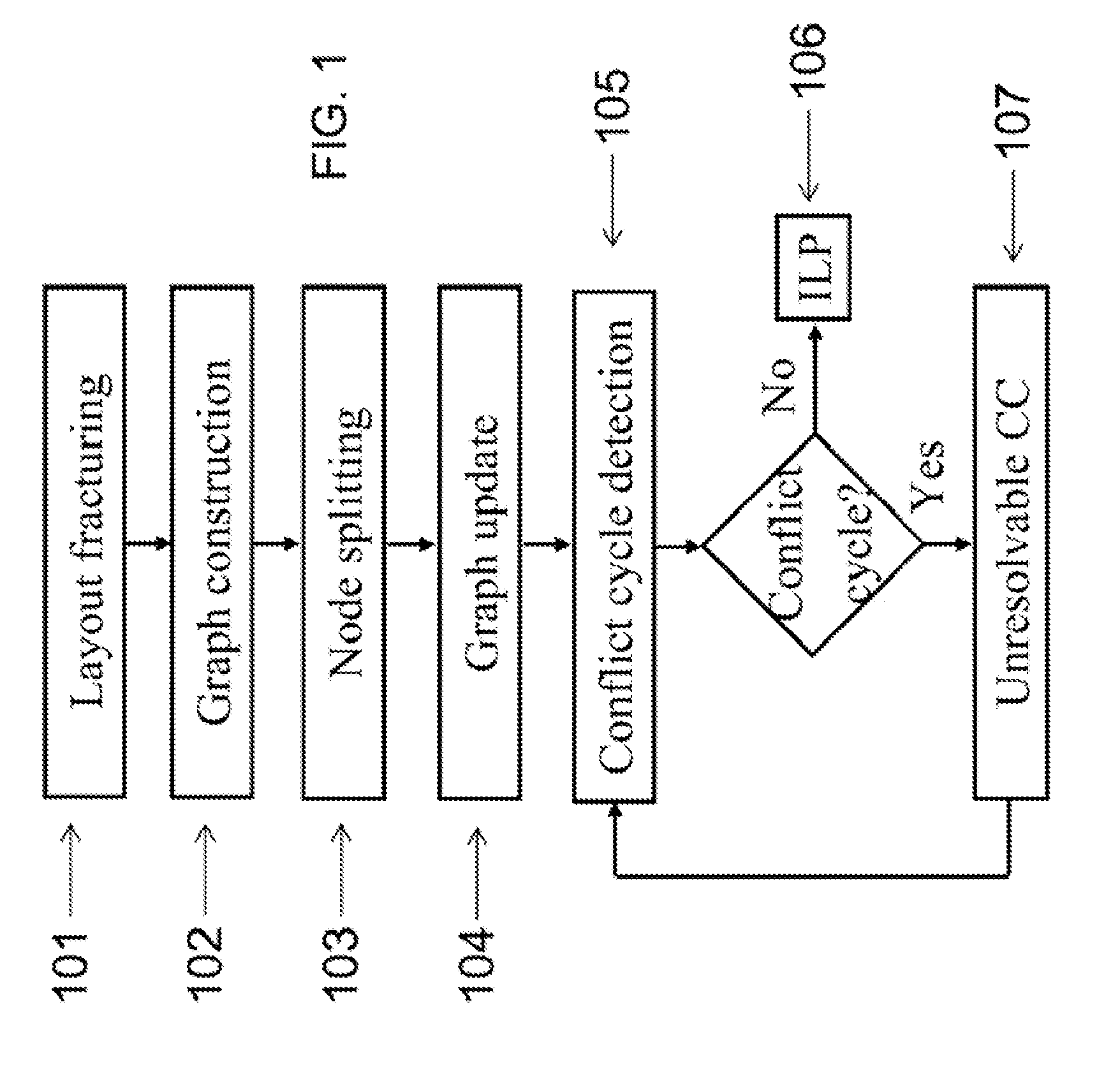

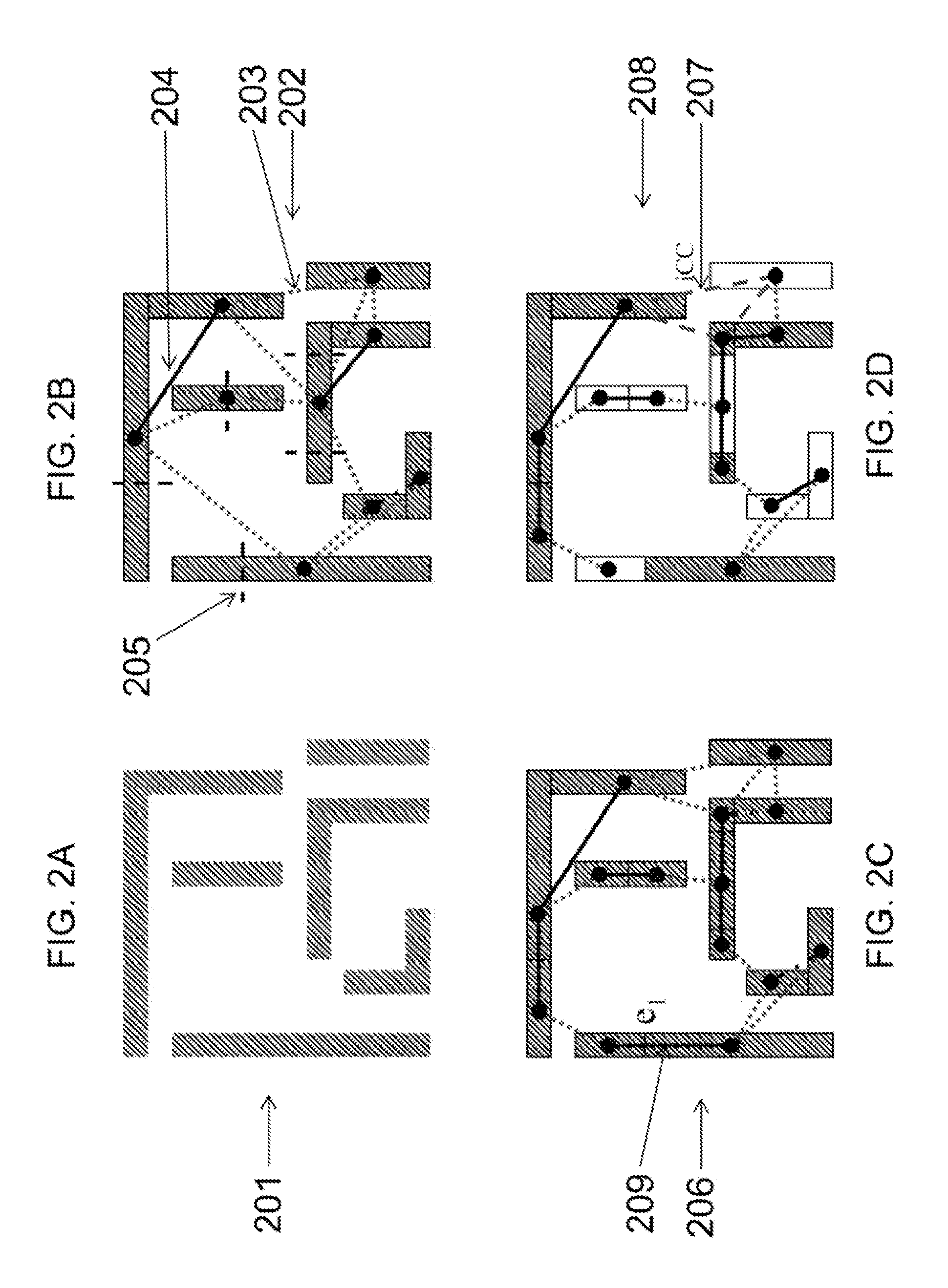

ActiveUS20110078638A1Low costAvoids small jogging line-endsOriginals for photomechanical treatmentComputer aided designLithographic artistDecomposition

The invention provides systems and methods for layout decomposition to produce exposure layouts that can be used to perform double patterning lithography (DPL). Preferred embodiment methods of the invention are executed by a computer and provide alternate methods for layout decomposition for double patterning lithography (DPL) using integer linear programming (ILP) formulations. Embodiments of the invention meet a key optimization goals, which is to reduce the total cost of layout decomposition, considering the abovementioned aspects that contribute to cost of prior conventional DPL techniques. Embodiments of the invention provide integer linear programming (ILP), phase conflict detection (PCD) and node election bipartization (NBD) formulations for the optimization of DPL layout decomposition, with a process-aware cost function that avoids small jogging line-ends, and maximizes overlap at dividing points of polygons. The cost function can also make preferential splits at landing pads, junctions and long runs.

Owner:RGT UNIV OF CALIFORNIA

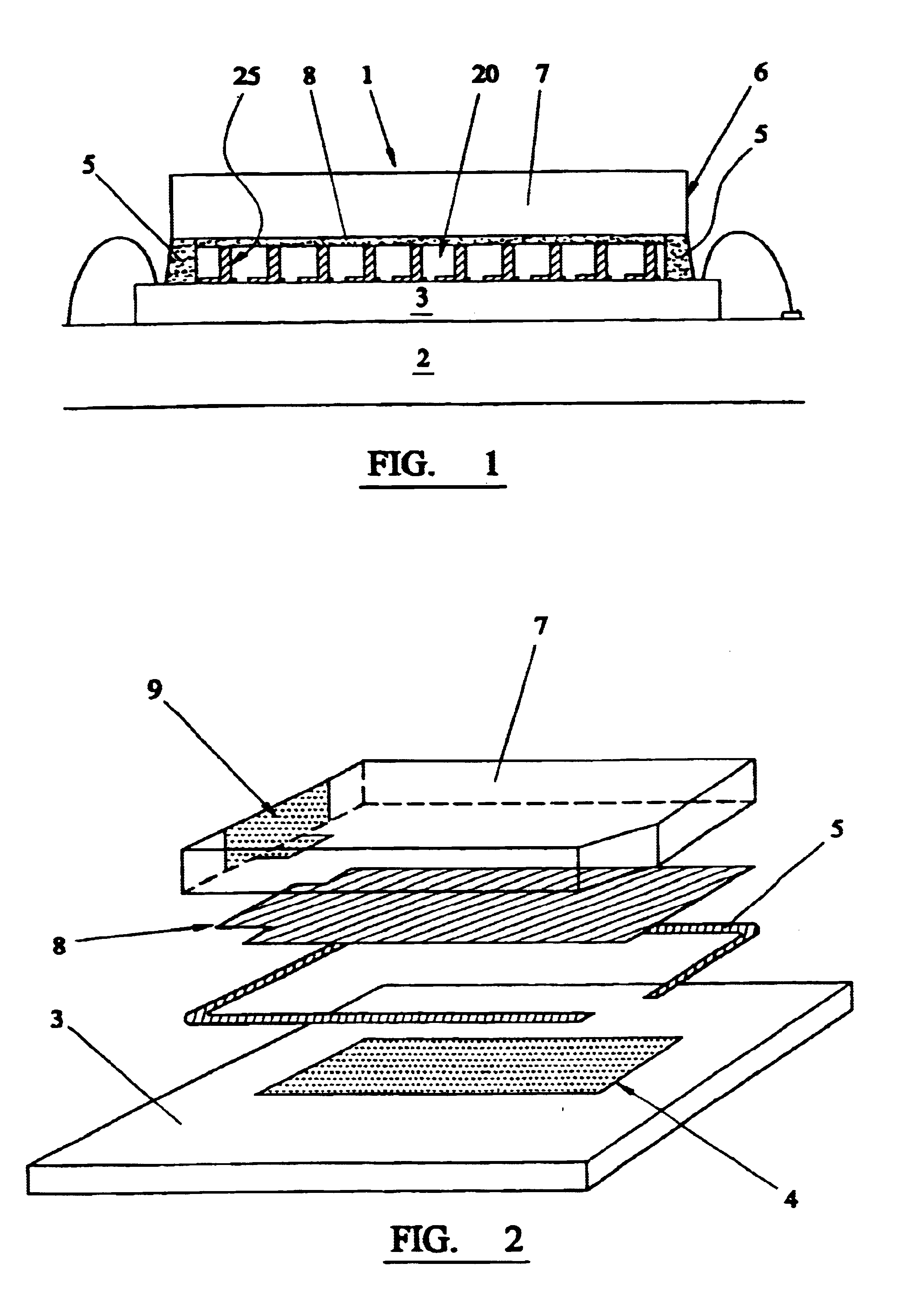

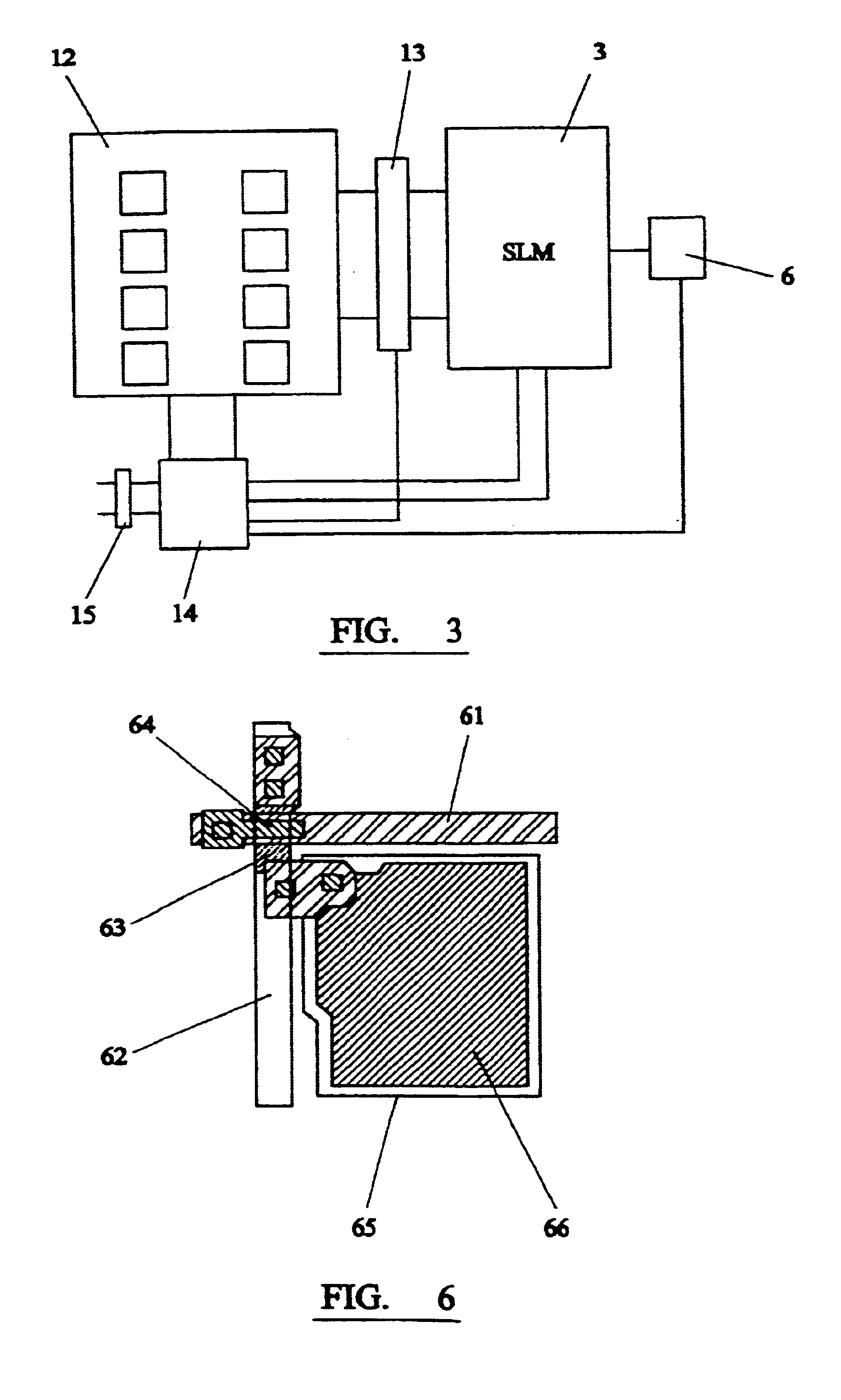

Methods of driving an array of optical elements

InactiveUS6762873B1Accurately determineStatic indicating devicesOptical elementsData setSubstitution method

Relates to writing an array of optical elements which are each switched between two states according to input data sets. In a first method, data is written in two steps in which different selected elements are respectively driven to one binary state and the other binary state. The selected elements of the two sets may be complementary, but are preferably only those which are required to change from their existing state. The latter criterion may be used in an alternative method using a single addressing of the array to turn elements in either direction as required. In a further method, as shown, selected elements only of a blank array are written in a first WRITE step so as to correspond with a set of data, and in a subsequent second ERASE step the selected elements are selectively erased to restore a blank array prior to writing and erasing another set of data. The methods have particular utility for maintaining a dc balance at pixels of a liquid crystal array.

Owner:QINETIQ LTD

Systems, methods, devices and device kits for fixation of bones and spinal vertebrae

InactiveUS8021401B2Avoid problemsMaintain alignmentInternal osteosythesisDiagnosticsIntervertebral spaceAlternative methods

Featured are methods for fixing adjacent vertebrate of a spine that utilize an implant member, which preferably is arcuate. Preferred methods of the invention for stabilizing adjacent vertebrae of the spine, include forming an aperture in each of the adjacent vertebrae and inserting an implant into the apertures formed in each of the adjacent vertebrae so that the implant extends between the adjacent vertebrae and through the intervertebral space. An alternative method for fixing adjacent vertebrae of a spine includes the step of forming a common channel in and between the adjacent vertebrae and inserting an implant in the channel so as to bridge between the adjacent vertebrae. Also featured are methods for stabilizing adjacent segments of a bone, fixation systems and fixation kits.

Owner:K2M

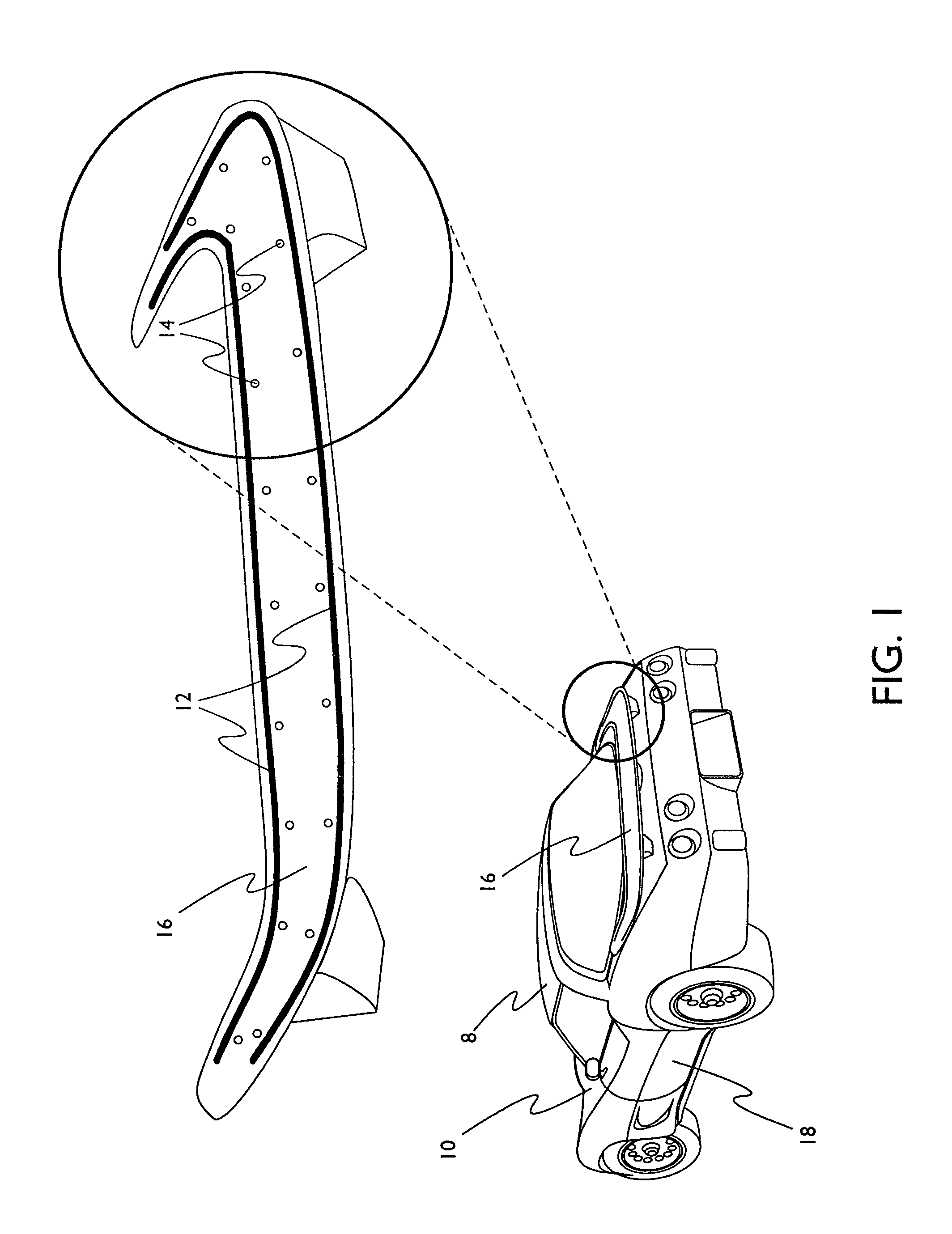

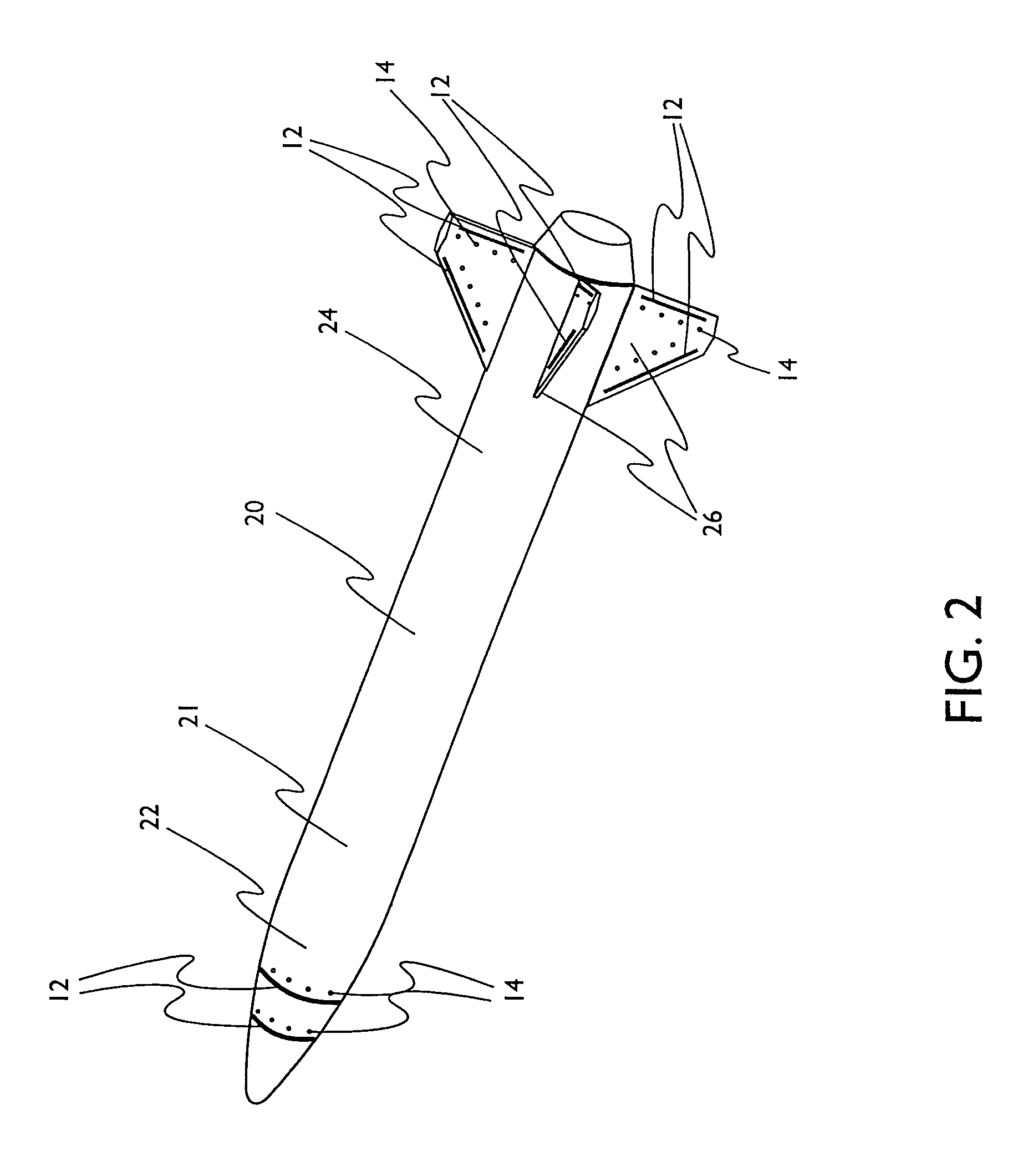

Method of controlling aircraft, missiles, munitions and ground vehicles with plasma actuators

ActiveUS7624941B1Improve efficiencyReduced Power RequirementsDirection controllersBoundary layer controlsJet aeroplanePlasma actuator

The present invention relates to a method of controlling an aircraft, missile, munition or ground vehicle with plasma actuators, and more particularly to controlling fluid flow across their surfaces or other surfaces, which would benefit from such a method. The method includes the design of an aerodynamic plasma actuator for the purpose of controlling airflow separation over a control surface of a aircraft, missile, or a ground vehicle, and more particularly to the method of determining a modulation frequency for the plasma actuator for the purpose of fluid flow control over these vehicles. The various embodiments provide the steps to increase the efficiency of aircraft, missiles, munitions and ground vehicles. The method of flow control provides a means for reducing aircraft, missile's, munition's and ground vehicle's power requirements. These methods also provide alternate means for aerodynamic control using low-power hingeless plasma actuator devices.

Owner:UNIV OF NOTRE DAME DU LAC +1

Methods of simultaneously cleaning and disinfecting industrial water systems

InactiveUS6840251B2Reduce Microbial ContaminationReduce removalDetergent bleaching agentsWater/sewage treatment by neutralisationChlorine dioxideOnline and offline

On-Line and Off-Line methods of simultaneously cleaning and disinfecting an industrial water system are described and claimed. The methods involve the addition to the water of the industrial water system of a Compound selected from the group consisting of the alkali salts of chlorite and chlorate and mixtures thereof; and an acid, followed by allowing the water in the industrial water system to circulate for several hours. The reaction of the alkali salts of chlorite and chlorate and acid produces chlorine dioxide in-situ in the water of the industrial water system. The chlorine dioxide kills microorganisms and the acid acts to remove deposits upon the water-contact surfaces of the equipment. An alternative method involves the use of a chelating agent and a biocide. Other possible cleaning and disinfection reagents may be added as needed including corrosion inhibitors, chelating agents, biocides, surfactants and reducing agents. These cleaning and disinfecting methods work in a variety of industrial water systems including cooling water and boiler water systems.

Owner:ECOLAB USA INC

Maximum likelihood decoding

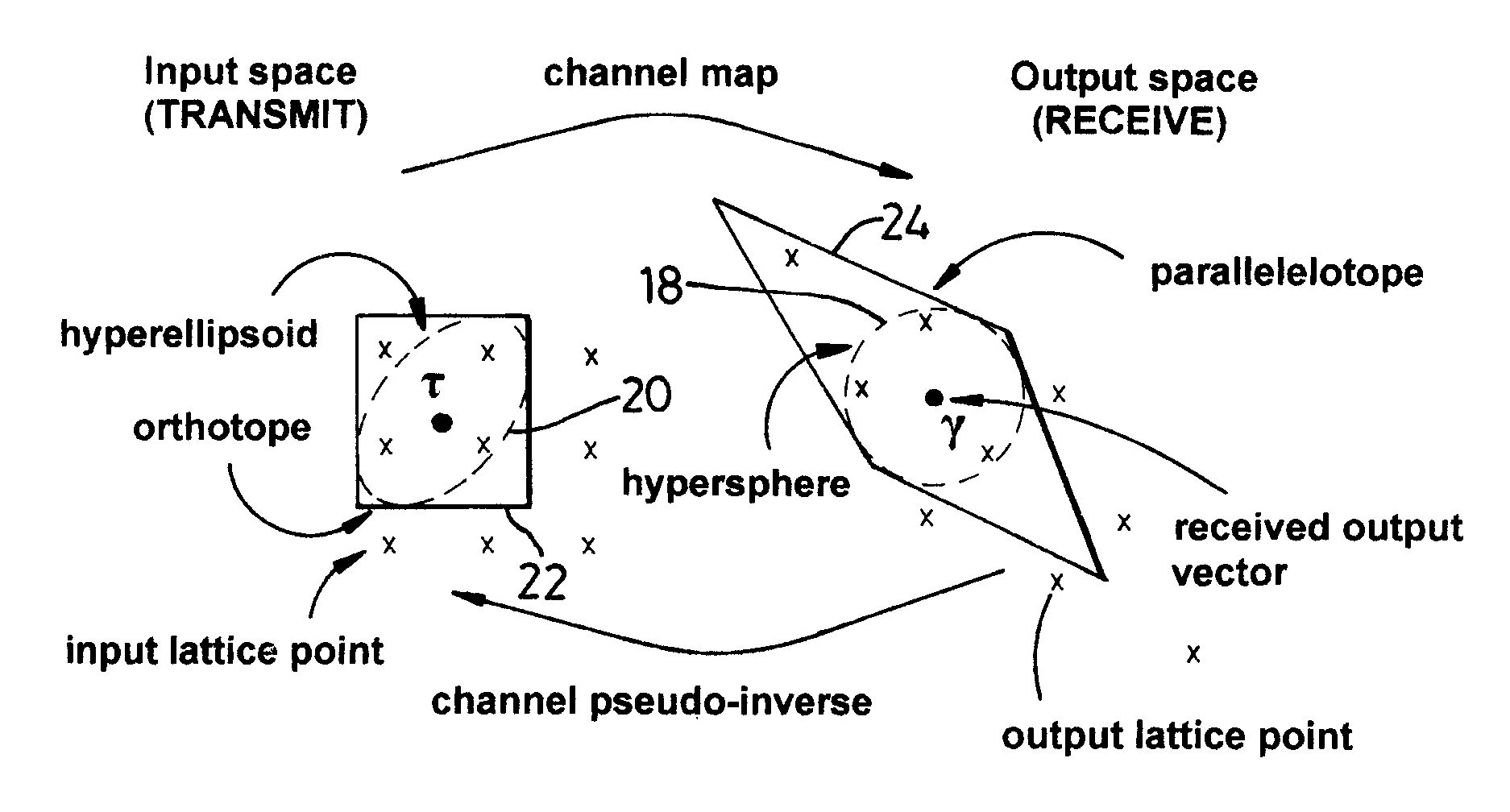

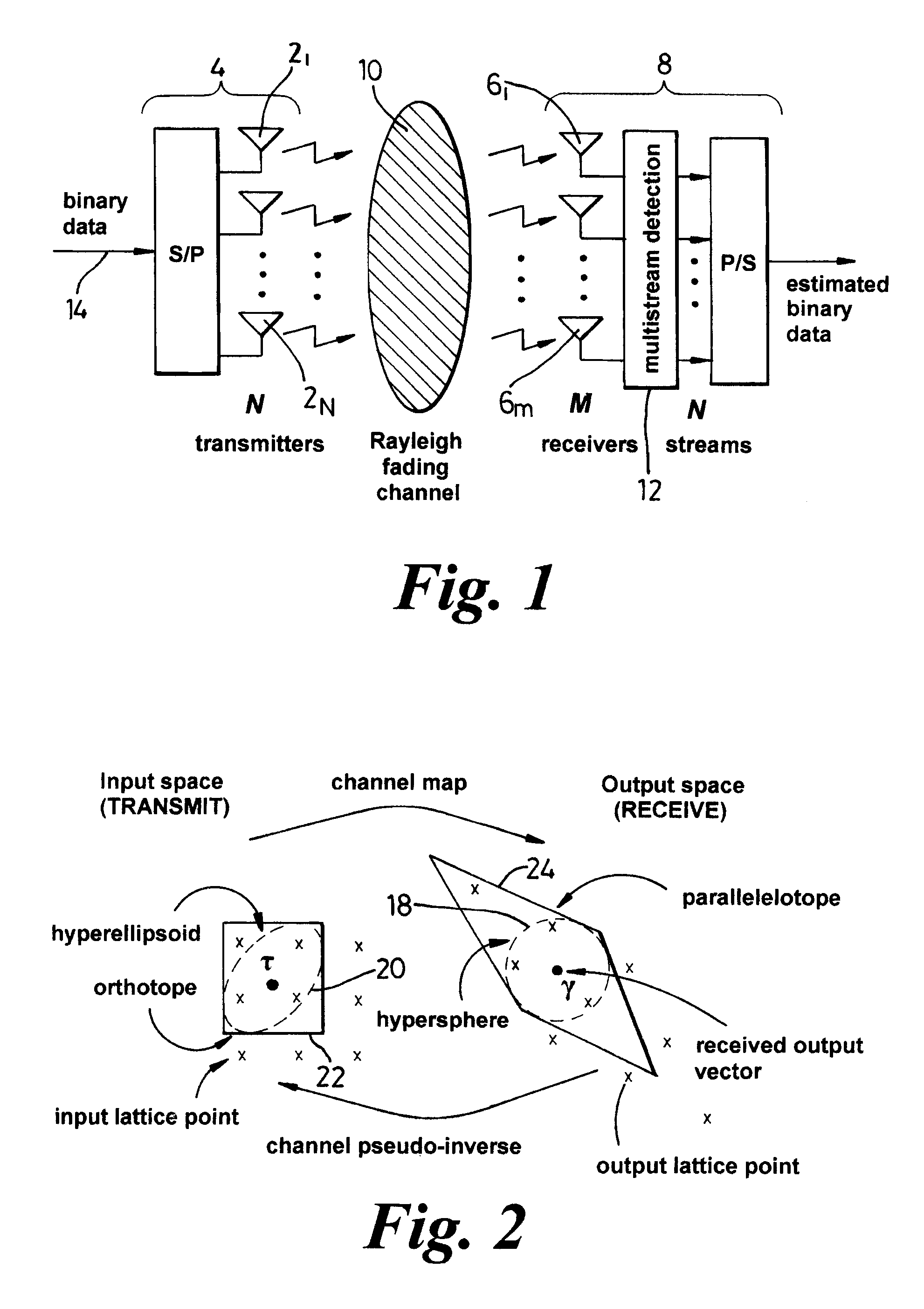

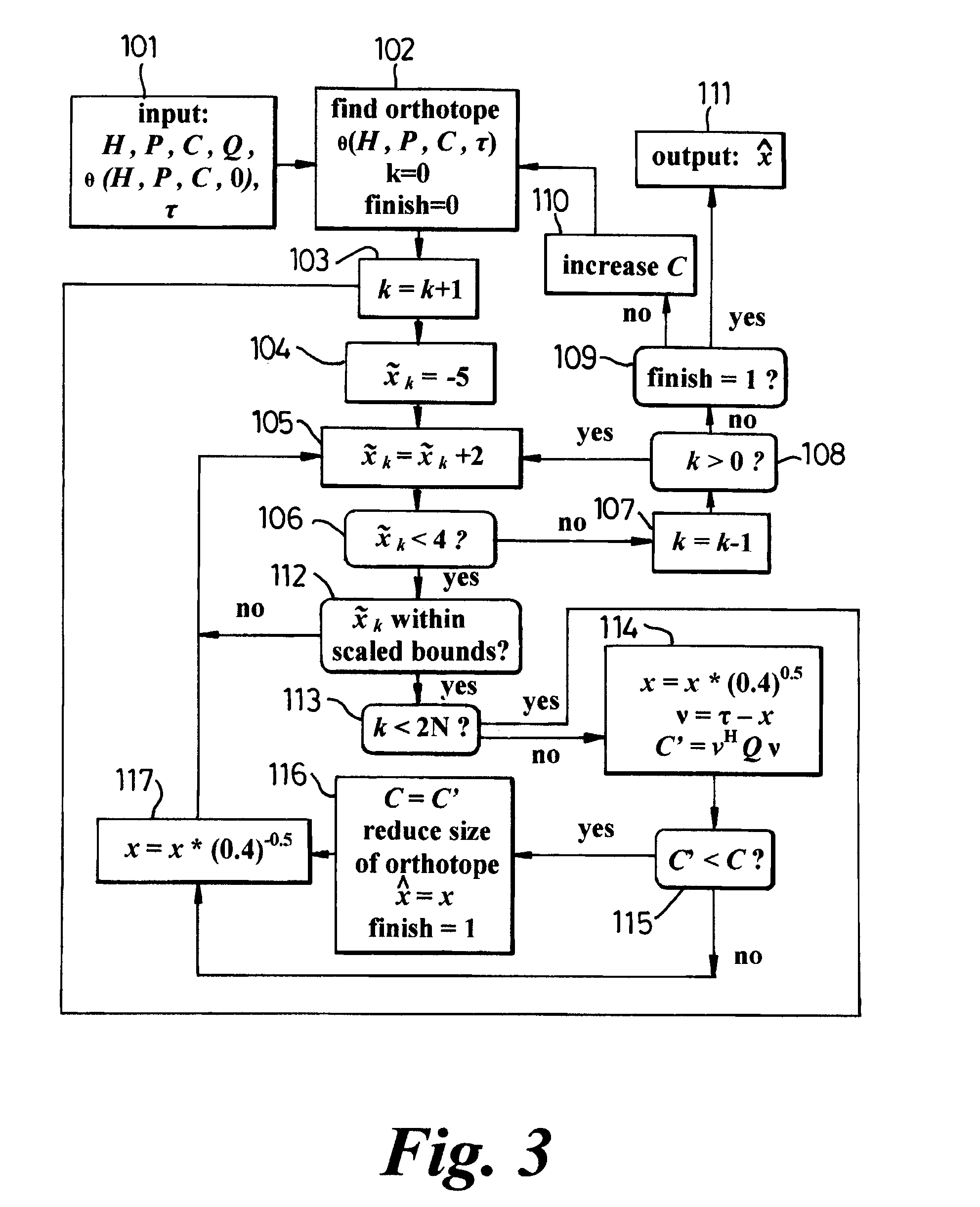

ActiveUS7233634B1Reduce complexityEasy to compareError preventionLine-faulsts/interference reductionCommunications systemHypersphere

A method of maximum likelihood decoding for detecting the signals transmitted over a Multiple-Input-Multiple-Output (MIMO) channel of a communication system in which there are N co-channel transmit antennas and M co-channel receive antennas. In a first method an orthotope (22) is generated in input signal space centred on an approximate transmit signal point τ which is an inverse mapping from an actual received signal point (y) in output signal space. Only possible transmit points located within the orthotope are considered as candidate points and are transformed into corresponding candidate receive signal points in output signal space. The Euclidean distance between the candidate receive signal points and the actual signal point is calculated and the closest candidate receive signal is selected as the detected received point. In an alternative method, the orthotope is constructed as the smallest such orthotope which can contain a hyperellipsoid (20) in input signal space, which hyperellipsoid is a transformation from output signal space of a hypersphere (18) centred on the actual received signal point (y). Those transmit signal points which lie within the orthotope (22) but outside of the ellipsoid (20) are discarded and the remaining points within the orthotope are considered as candidate points, in the same way as described above.

Owner:APPLE INC

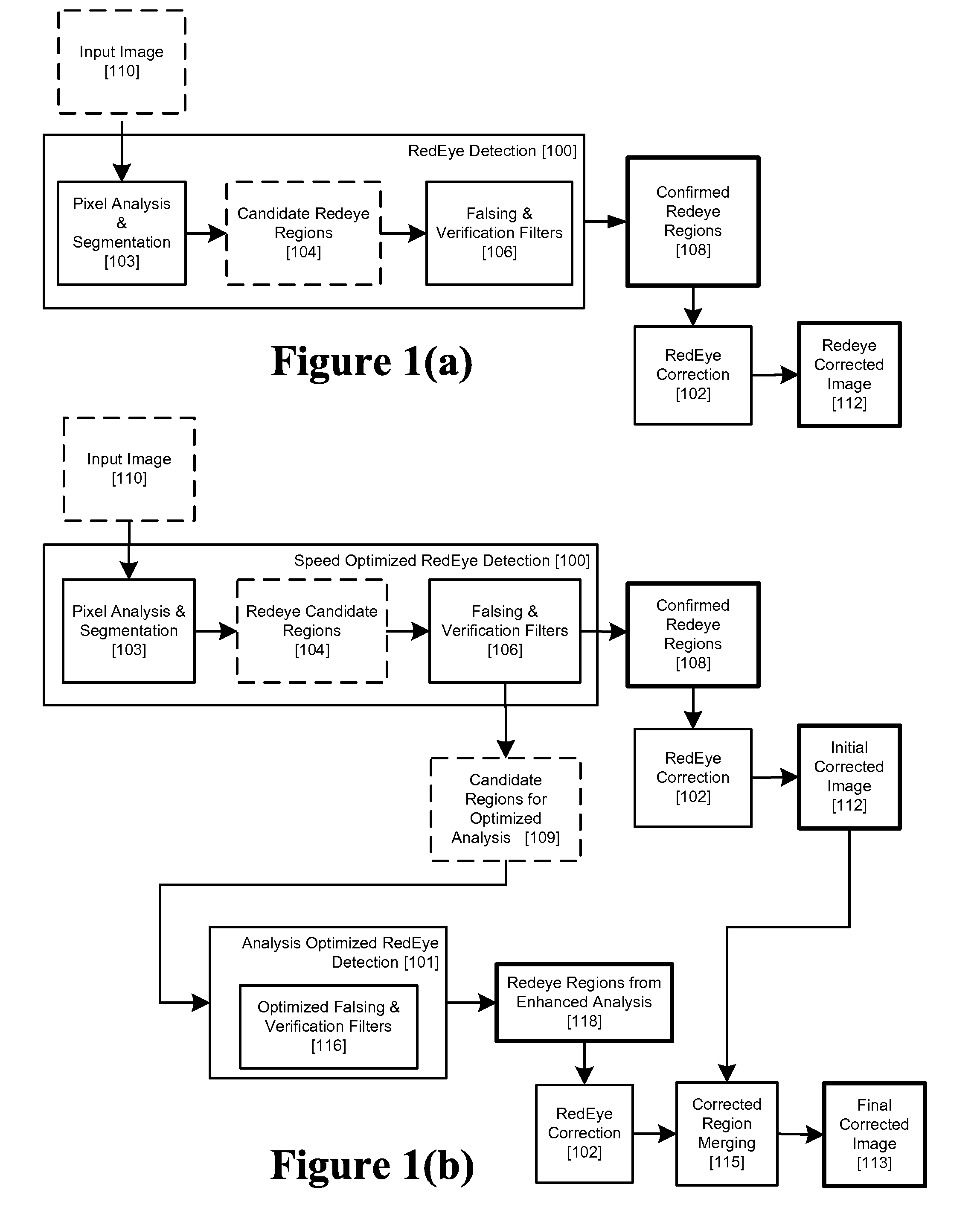

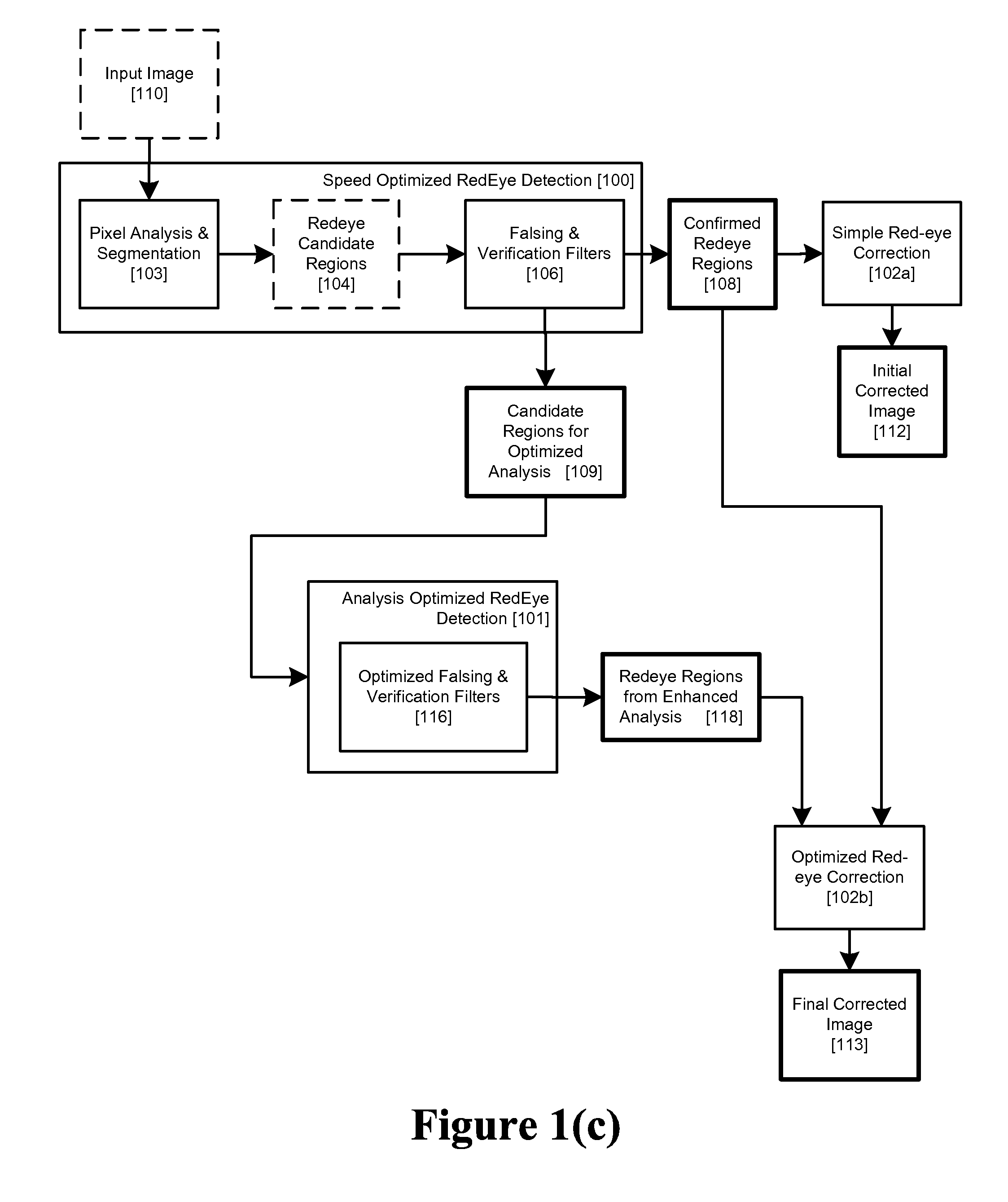

Two Stage Detection for Photographic Eye Artifacts

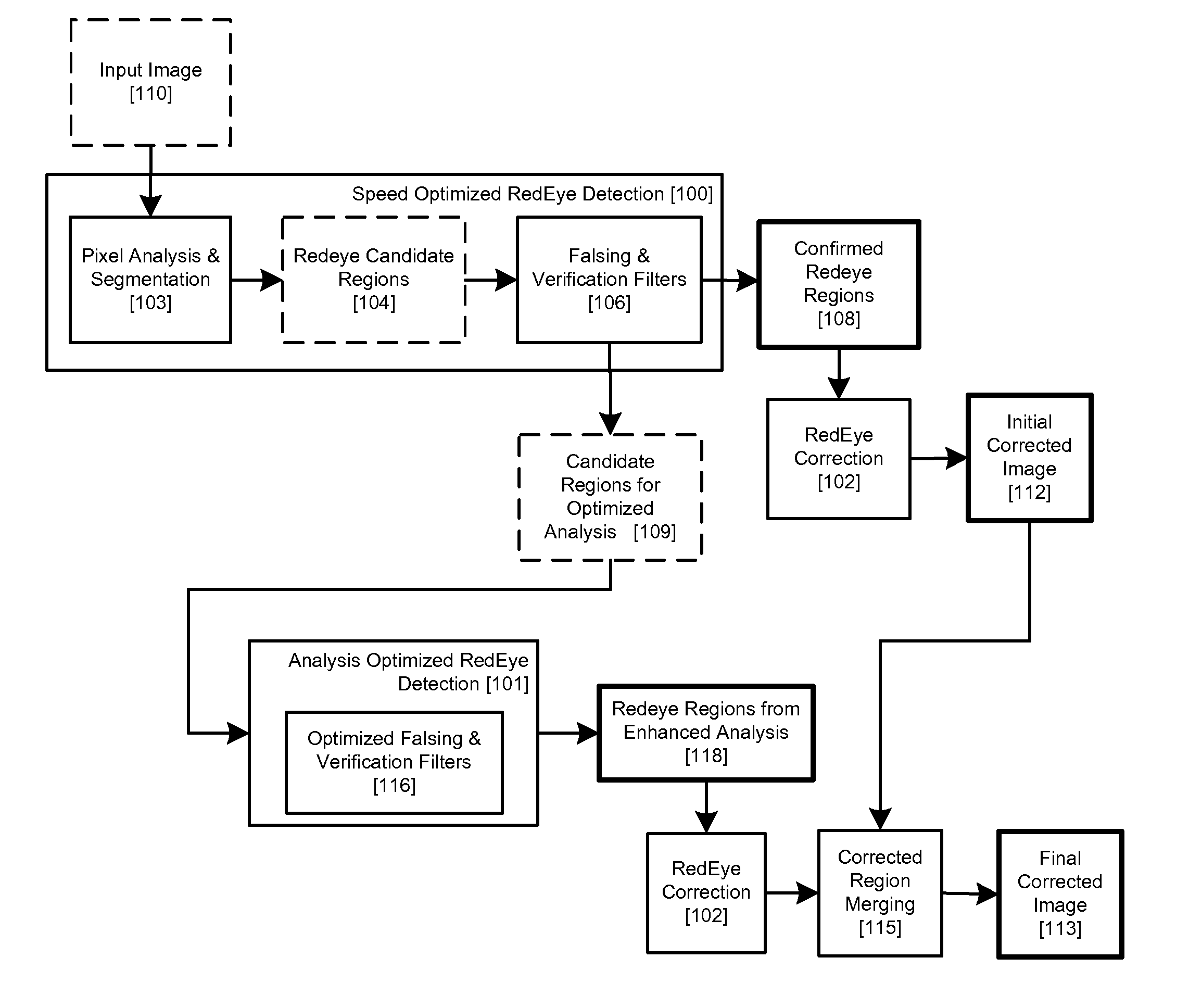

ActiveUS20080232711A1Optimized for speedAvoid the needAcquiring/recognising eyesCathode-ray tube indicatorsFilter systemAlternative methods

The detection of red-eye defects is enhanced in digital images for embedded image acquisition and processing systems. A two-stage redeye filtering system includes a speed optimized filter that performs initial segmentation of candidate redeye regions and optionally applies a speed-optimized set of falsing / verification filters to determine a first set of confirmed redeye regions for correction. Some of the candidate regions which are rejected during the first stage are recorded and re-analyzed during a second stage by an alternative set of analysis-optimized filters to determine a second set of confirmed redeye regions.

Owner:FOTONATION LTD

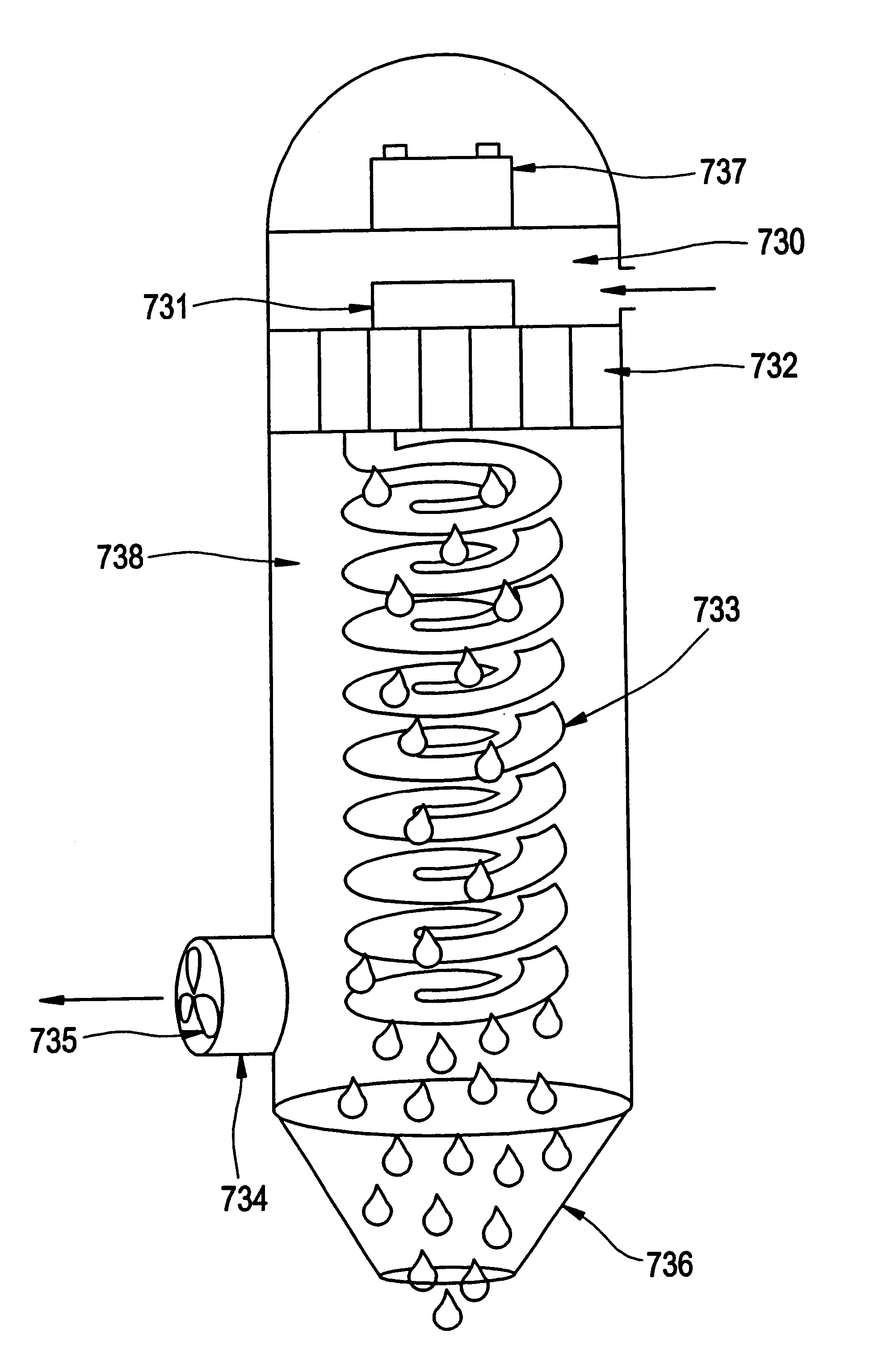

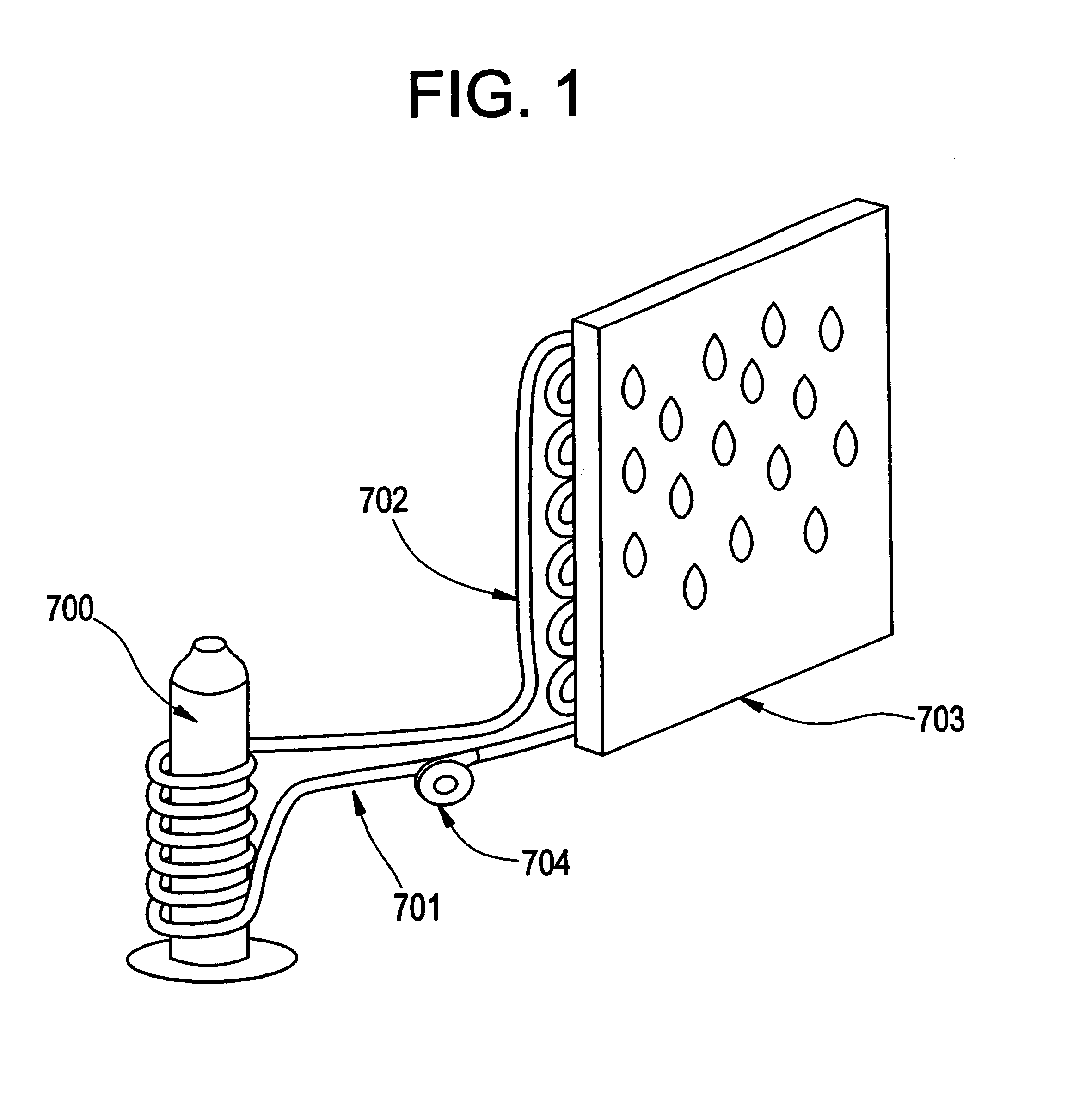

Production of potable water and freshwater needs for human, animal and plants from hot and humid air

InactiveUS6868690B2Reduces cargo spaceMinimize any benefitGeneral water supply conservationSeawater treatmentParticulatesFresh water organism

Systems and methods are disclosed for extracting freshwater from atmospheric humidity in extremely hot and humid climates and supplying freshwater to a small group of people, a building, a farm, or forestation area. The freshwater is treated to provide drinking water by disinfecting to eliminate microorganisms and filtration to remove suspended particulates from air, erosion or corrosion products, and disinfected waste. Compact units provide drinking water for individuals, passengers in cars, vans, trucks, or recreational boats, or crewmembers on a seagoing cargo ship whether from atmospheric humidity or from moisture-laden gases. Furthermore, systems are disclosed for the ample supply of freshwater with minimal treatment for small- to large-sized buildings in a manner that alleviates the heat load on buildings. Collection of freshwater from hot humid ambient air is also provided for other uses, such as irrigation and farm animal drinking. Various methods are used for condensation of water vapor suspended in the air as alternative to conventional refrigeration cycles using CFC refrigerants. Devices are disclosed using naturally occurring brackish cold water, circulation of cooling water cooled by thermoelectric cooling or thermoacoustic refrigeration as well as evaporative cooling and transpiration cooling. Water produced by the systems may flow under gravitational forces entirely or with the assistance of boasting pumps.

Owner:FAKIEH RES & DEV CENT

Method of texture-based color document segmentation

InactiveUS6993185B2Noise generatedCharacter and pattern recognitionNoise reductionAlternative methods

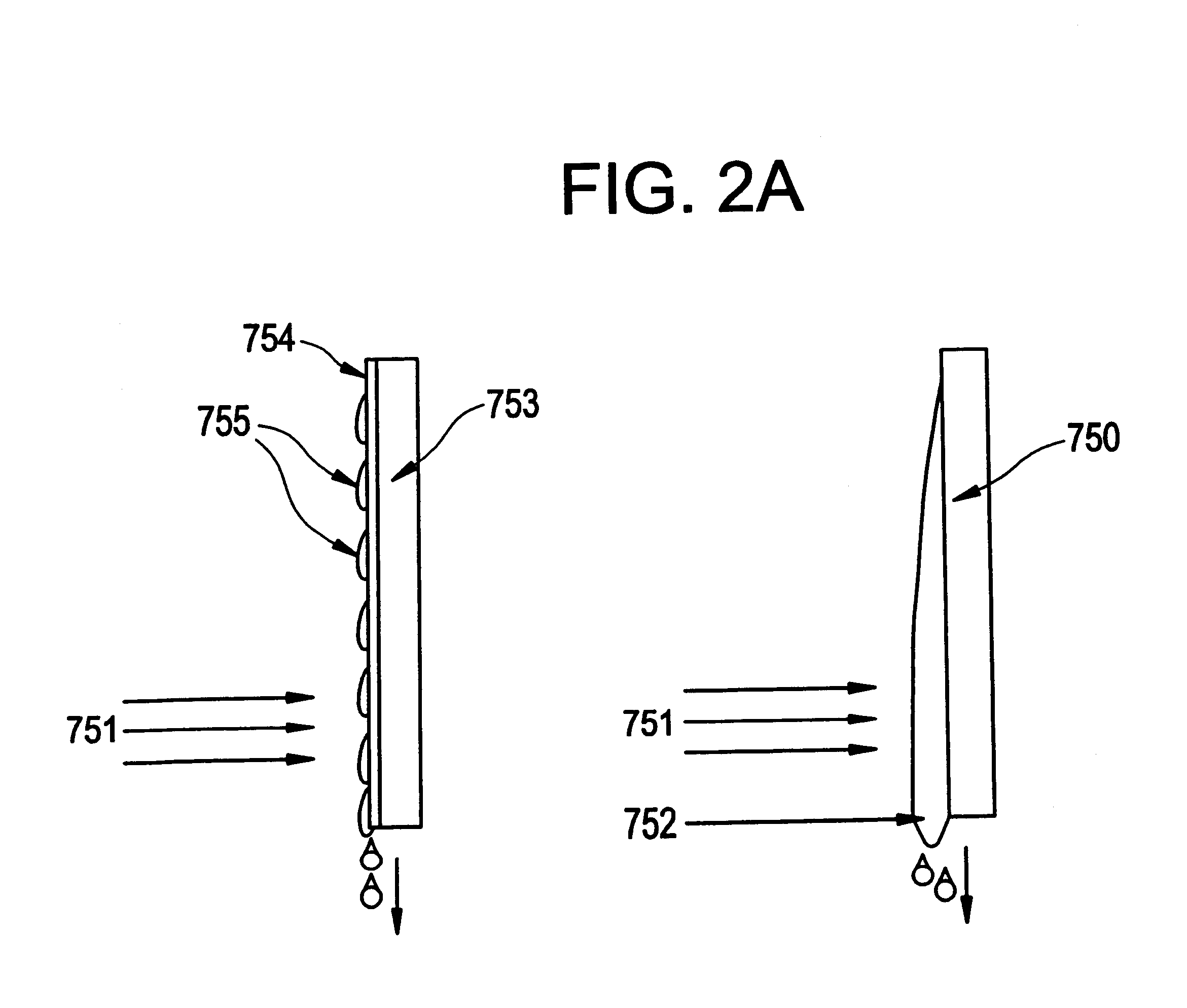

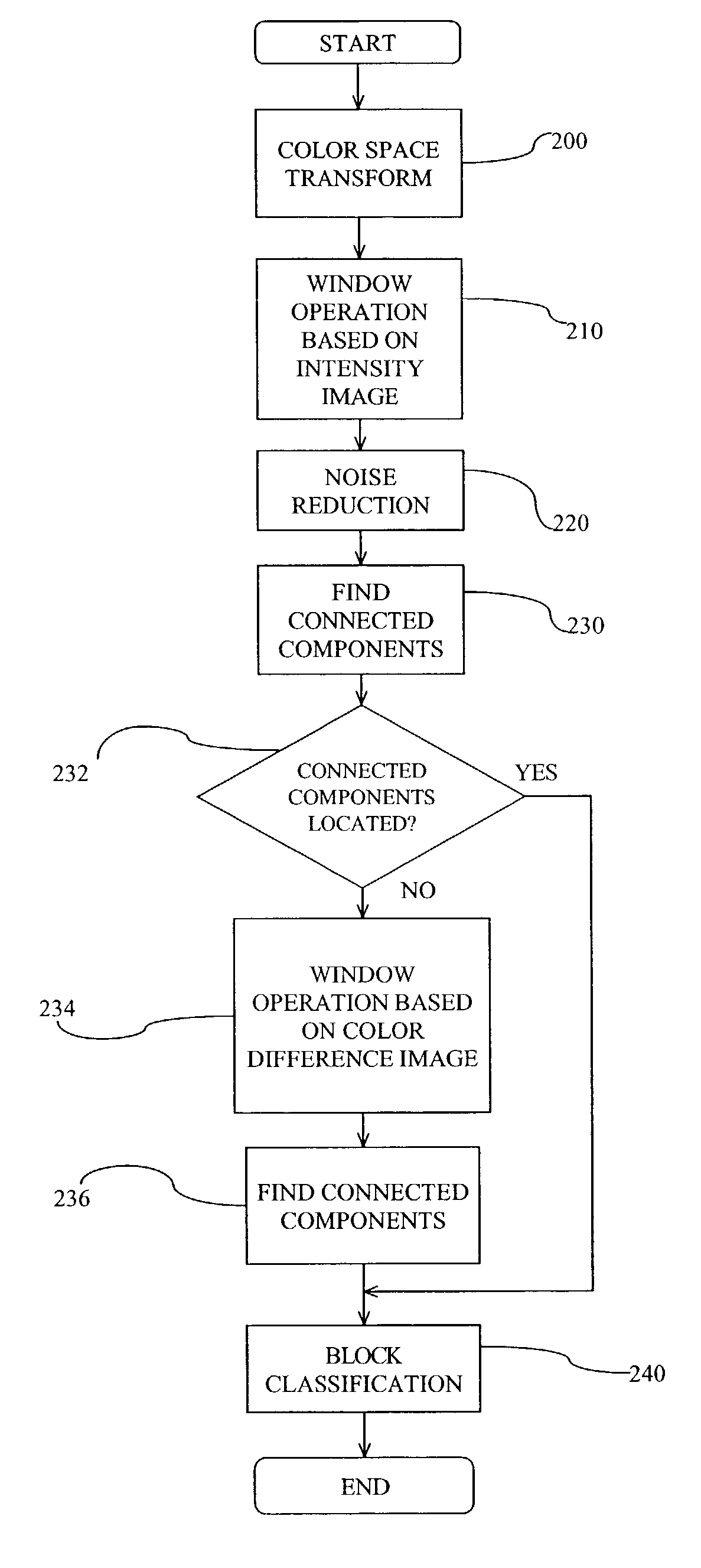

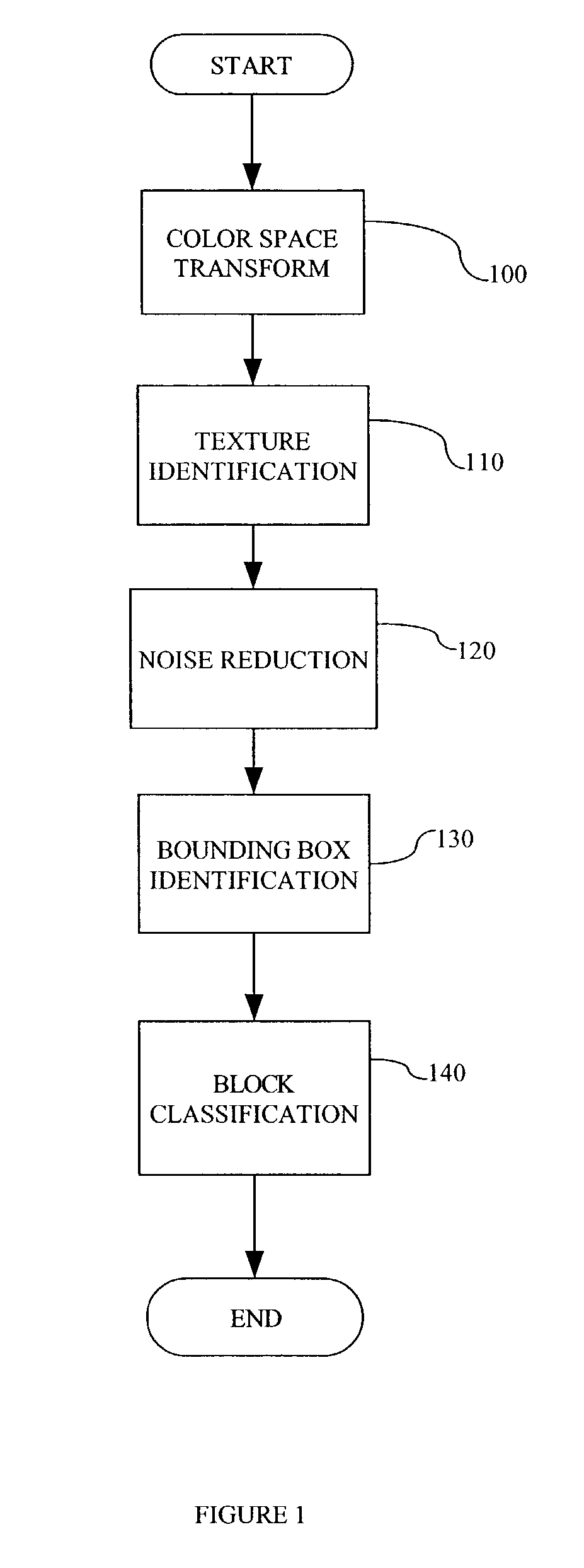

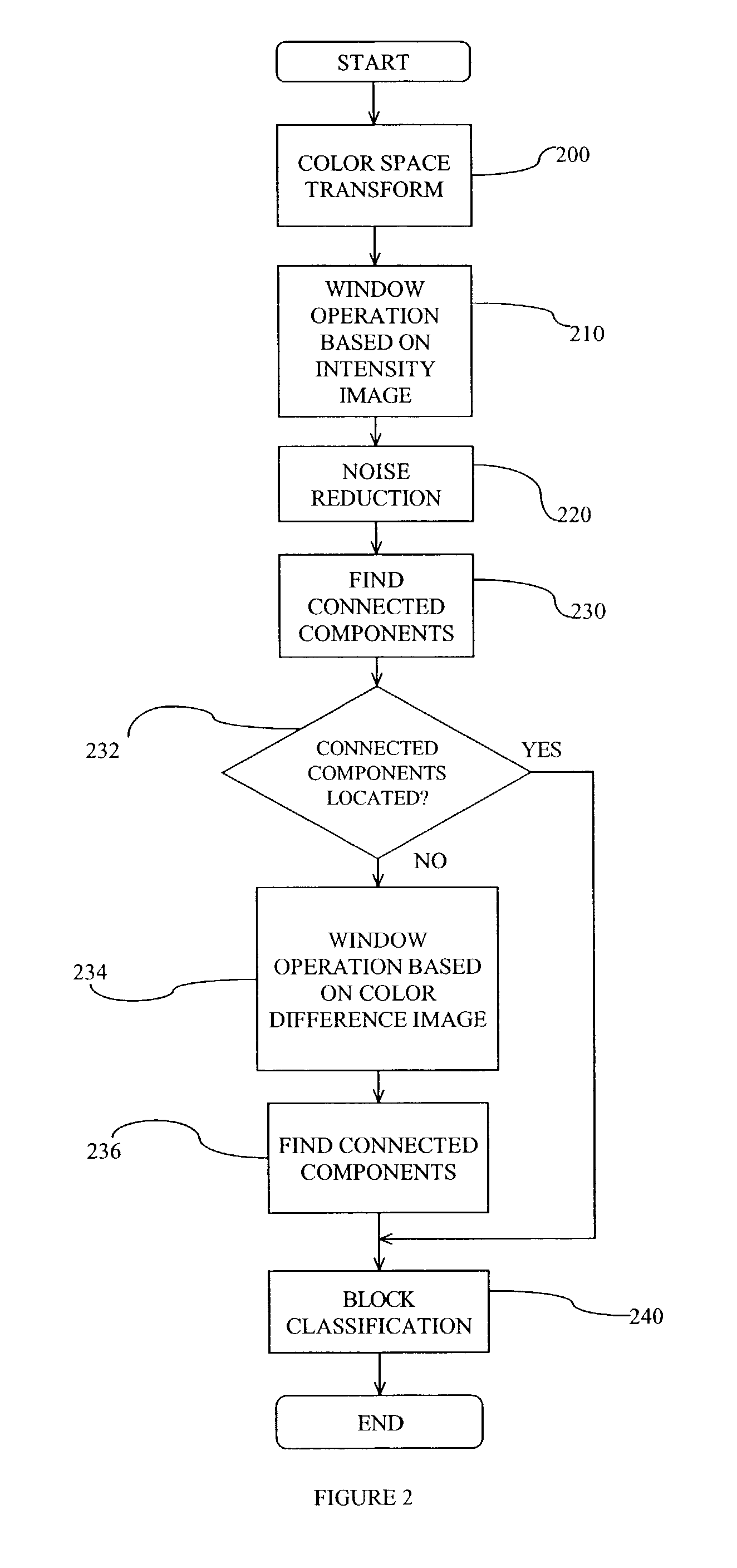

A method for segmenting a color document into regions of text and halftone discriminates between text and halftone by examining the texture of the document. A color document is digitized, and a color space transform is preferably applied to the digitized document. The texture of the document is identified and a noise reduction step is preferably applied. Bounding boxes (blocks) within the document are identified and then the areas within the bounding boxes are classified as either text or halftone. Two alternative methods are described for examining the document texture. In the first method, a windowing operation is applied to either an intensity image or a color difference image. In the second method, a wavelet transform step combined with Fuzzy K-Mean clustering is applied. Bounding boxes are classified as either text or halftone based upon the relative periodicity of a horizontal or vertical (or both) histogram of each bounding box.

Owner:PANASONIC CORP

Method of making a circuitized substrate having at least one capacitor therein

InactiveUS20080248596A1Enhance circuitized substrate artEnhance the circuitized substrate artThin/thick film capacitorPrinted circuit aspectsCapacitanceConductive materials

A method of making a circuitized substrate which includes at least one and possibly several capacitors as part thereof. In one embodiment, the substrate is produced by forming a layer of capacitive dielectric material on a dielectric layer and thereafter forming channels with the capacitive material, e.g., using a laser. The channels are then filled with conductive material, e.g., copper, using selected deposition techniques, e.g., sputtering, electro-less plating and electroplating. A second dielectric layer is then formed atop the capacitor and a capacitor “core” results. This “core” may then be combined with other dielectric and conductive layers to form a larger, multilayered PCB or chip carrier. In an alternative approach, the capacitive dielectric material may be photo-imageable, with the channels being formed using conventional exposure and development processing known in the art. In still another embodiment, at least two spaced-apart conductors may be formed within a metal layer deposited on a dielectric layer, these conductors defining a channel there-between. The capacitive dielectric material may then be deposited (e.g., using lamination) within the channels.

Owner:ENDICOTT INTERCONNECT TECH

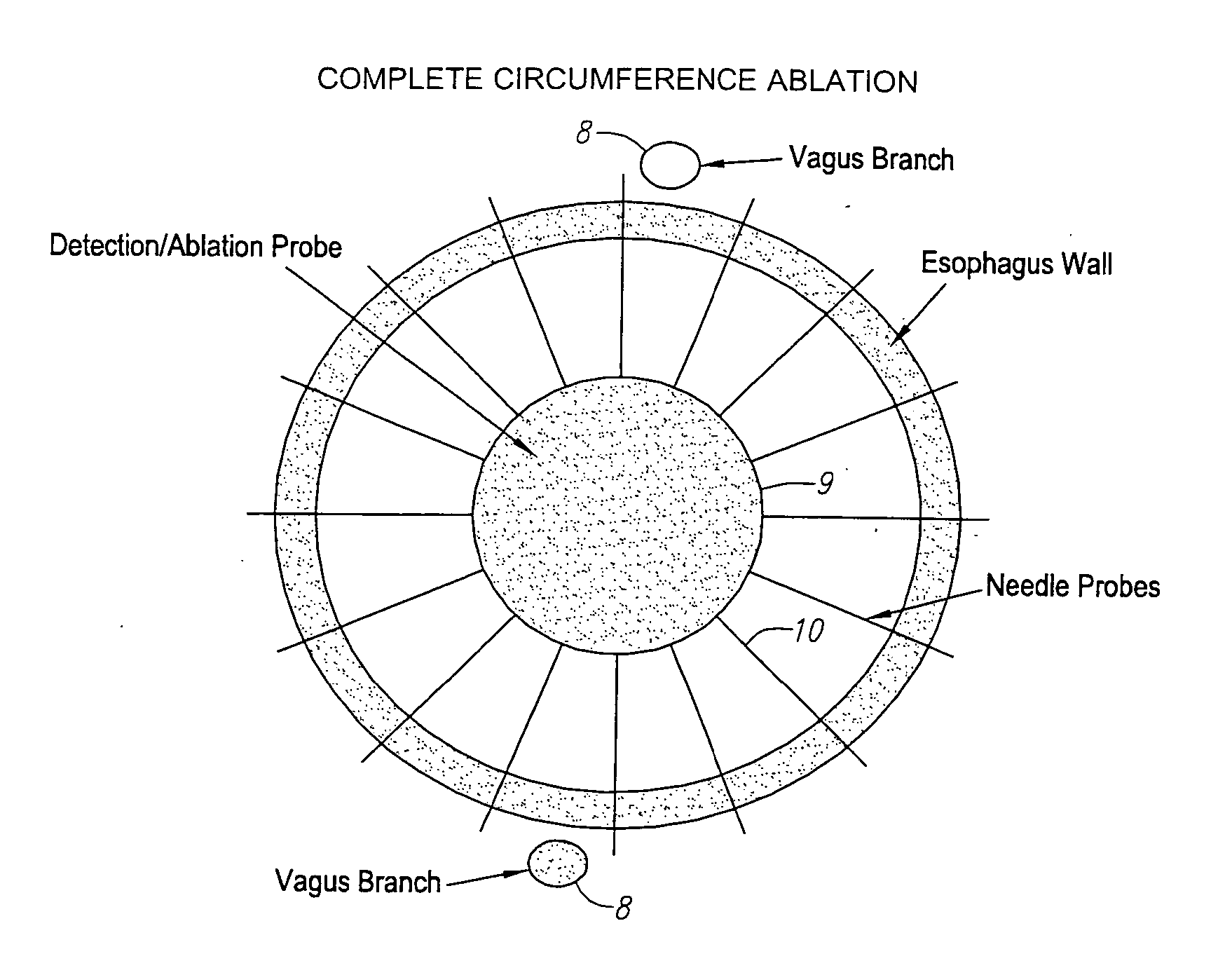

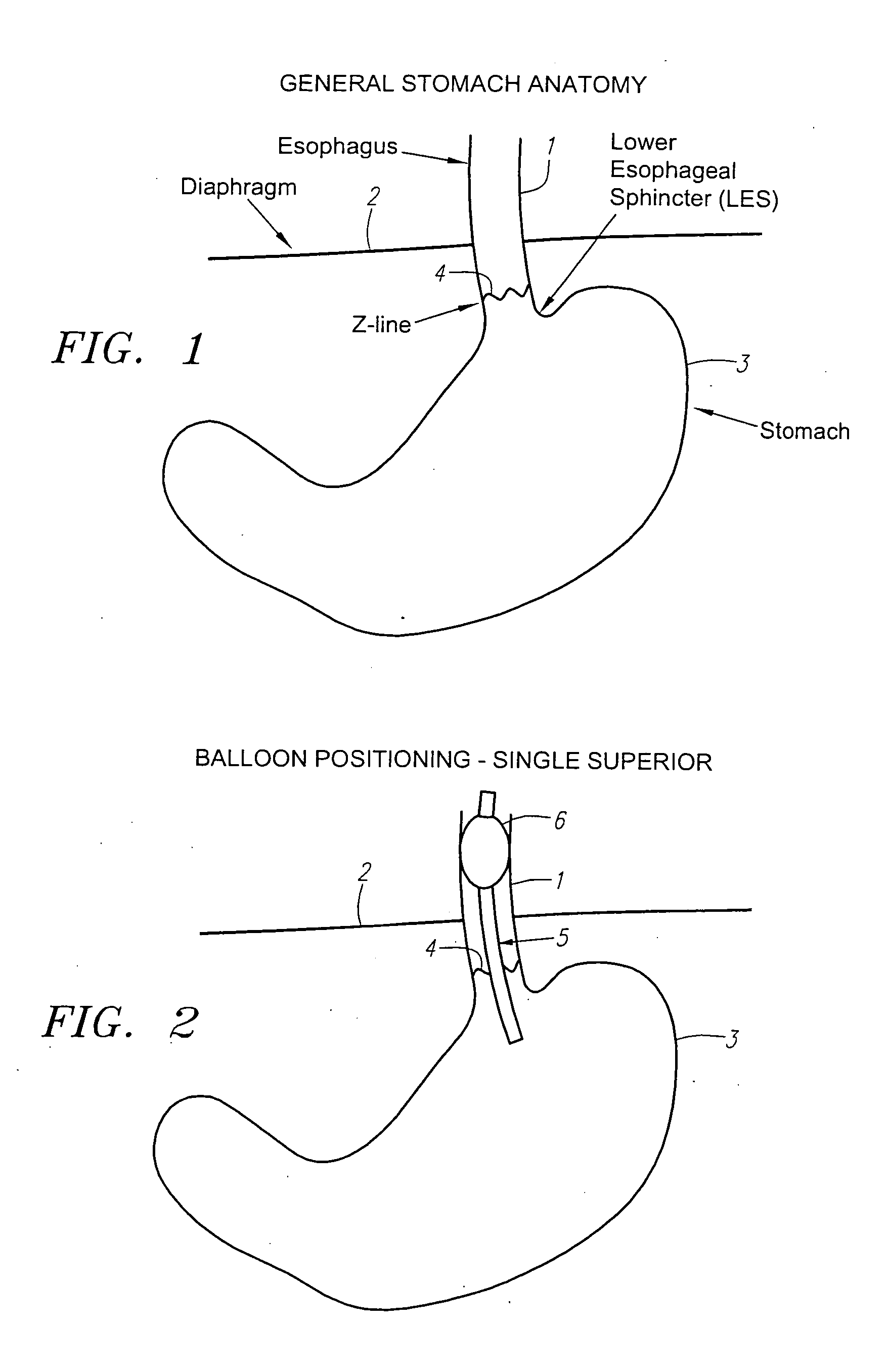

Methods and apparatus for testing disruption of a vagal nerve

InactiveUS20050240231A1Increase energy levelLower energy levelUltrasound therapyElectrotherapyOesophageal tubeHigh energy

Method and apparatus for disrupting a gastric vagal nerve in the gastroesophageal region and testing the function and disruption of the vagal nerve. In one example embodiment, a treatment device applies ultrasound at a high energy level, such as high intensity focused ultrasound, to a vagal nerve to disrupt it and then ultrasound at a lower energy level to another portion of the vagal nerve, preferably further from the stomach, so as to stimulate the vagal nerve. Alternative ways to test the function or disruption of the vagal nerve involve using PCP-GABA, a pancreatic polypeptide, pressure changes inside the stomach, the gastric mucusol pH, a dye agent in the stomach, and other tests.

Owner:ENDOVX

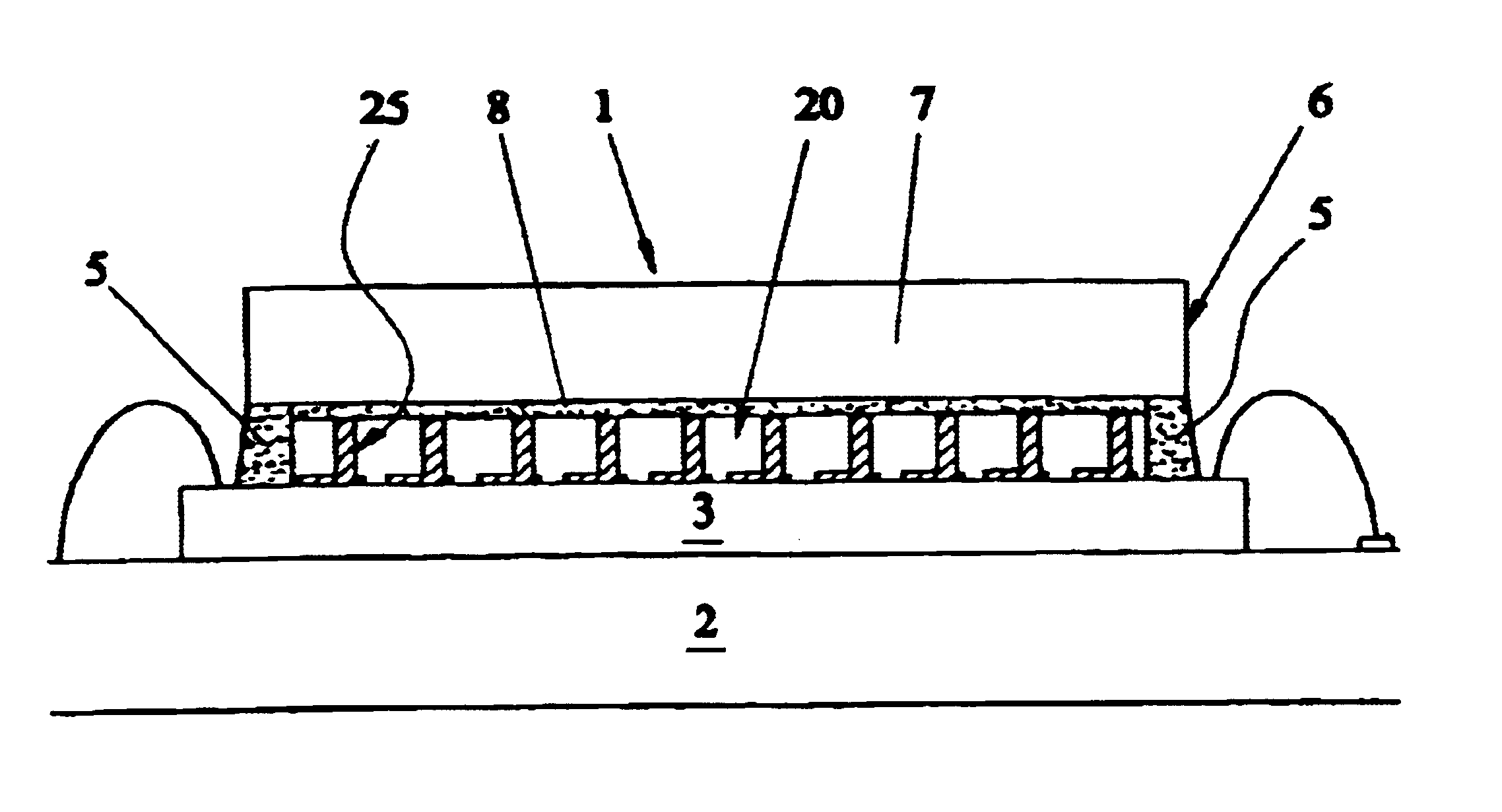

Light emitting device with phosphor wavelength conversion and methods of producing the same

ActiveUS20090134414A1Improve uniformityImprove coating uniformitySolid-state devicesOptical articlesEpoxyPhosphor

A method of fabricating a light emitting device comprises: mounting a light emitting diode chip in a package; heating the light emitting diode chip package assembly to a pre-selected temperature; and dispensing a pre-selected volume of a mixture of at least one phosphor and a light transmissive thermosetting material (silicone, epoxy) on a surface of the chip. The pre-selected volume and temperature are selected such that the phosphor / material mixture flows over the entire light emitting surface of the chip before curing. In an alternative method, using a light transmissive UV curable material such as an epoxy, the phosphor / material mixture is irradiated with UV radiation after a pre-selected time to cure the material. The pre-selected volume and pre-selected time are selected such that the phosphor / material mixture flows over at least the light emitting surface of the chip before curing.

Owner:INTEMATIX

Pull-back method of forming fins in FinFets

A method of forming integrated circuits having FinFET transistors includes a method of forming sub-lithographic fins, in which a mask defining a block of silicon including a pair of fins in reduced in width or pulled back by the thickness of one fin on each side, after which a second mask is formed around the first mask, so that after the first mask is removed, an aperture remains in the second mask having the width of the separation distance between the pair of fins. When the silicon is etched through the aperture, the fins are protected by the second mask, thereby defining fin thickness by the pullback step. An alternative method uses lithography of opposite polarity, first defining the central etch aperture between the two fins lithographically, then expanding the width of the aperture by a pullback step, so that filling the widened aperture with an etch-resistant plug defines the outer edges of the pair of fins, thereby setting the fin width without an alignment kstep.

Owner:INT BUSINESS MASCH CORP

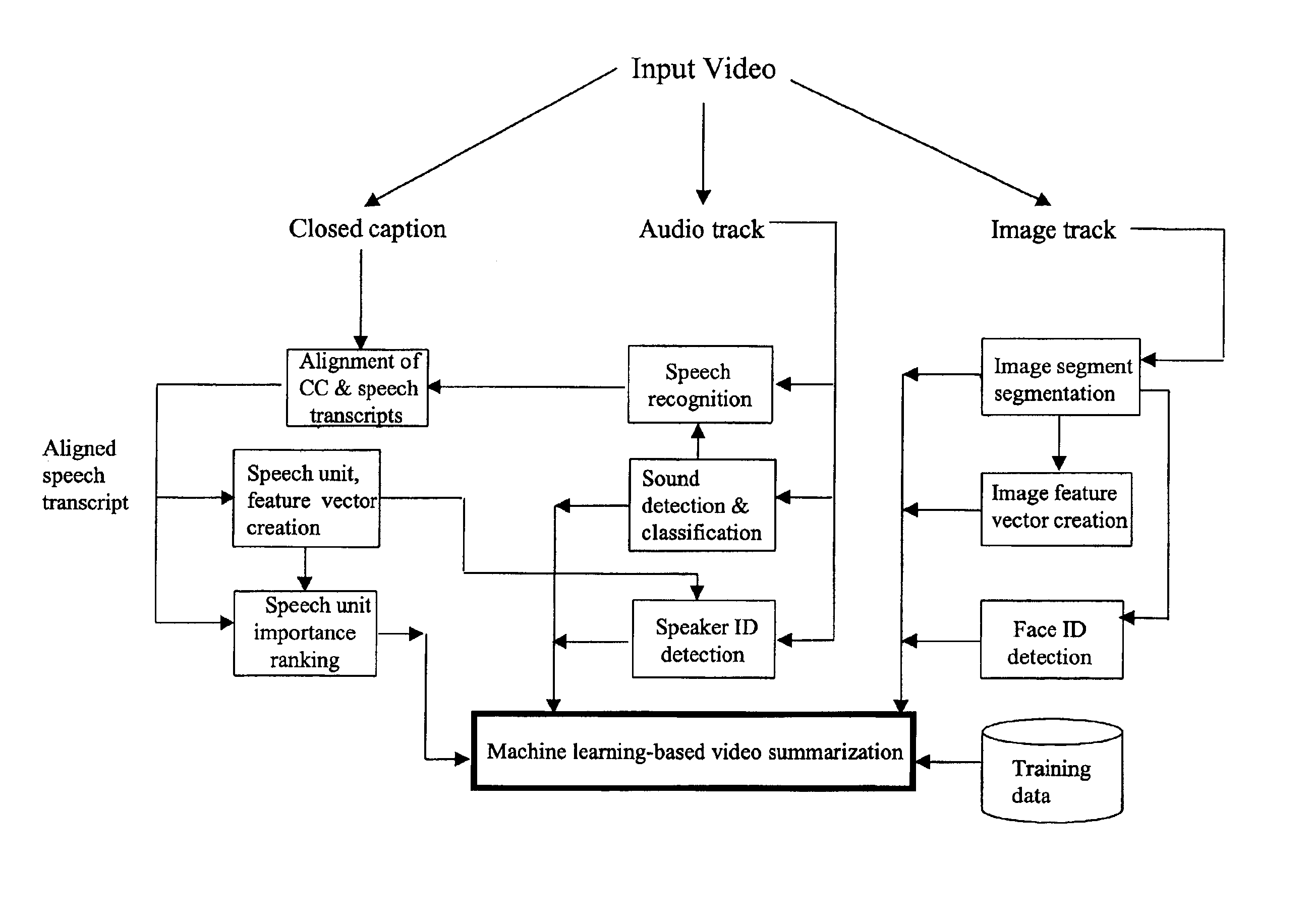

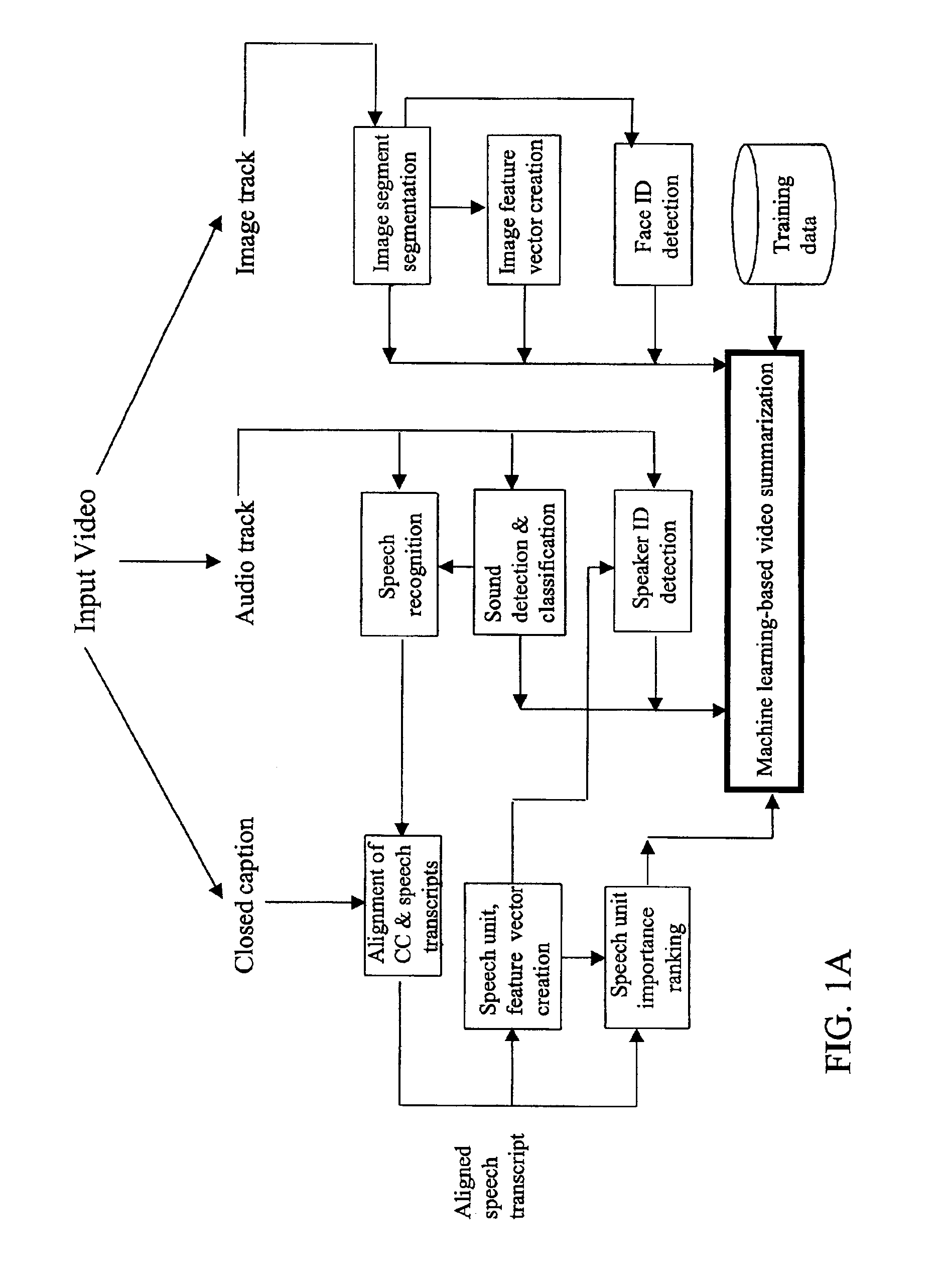

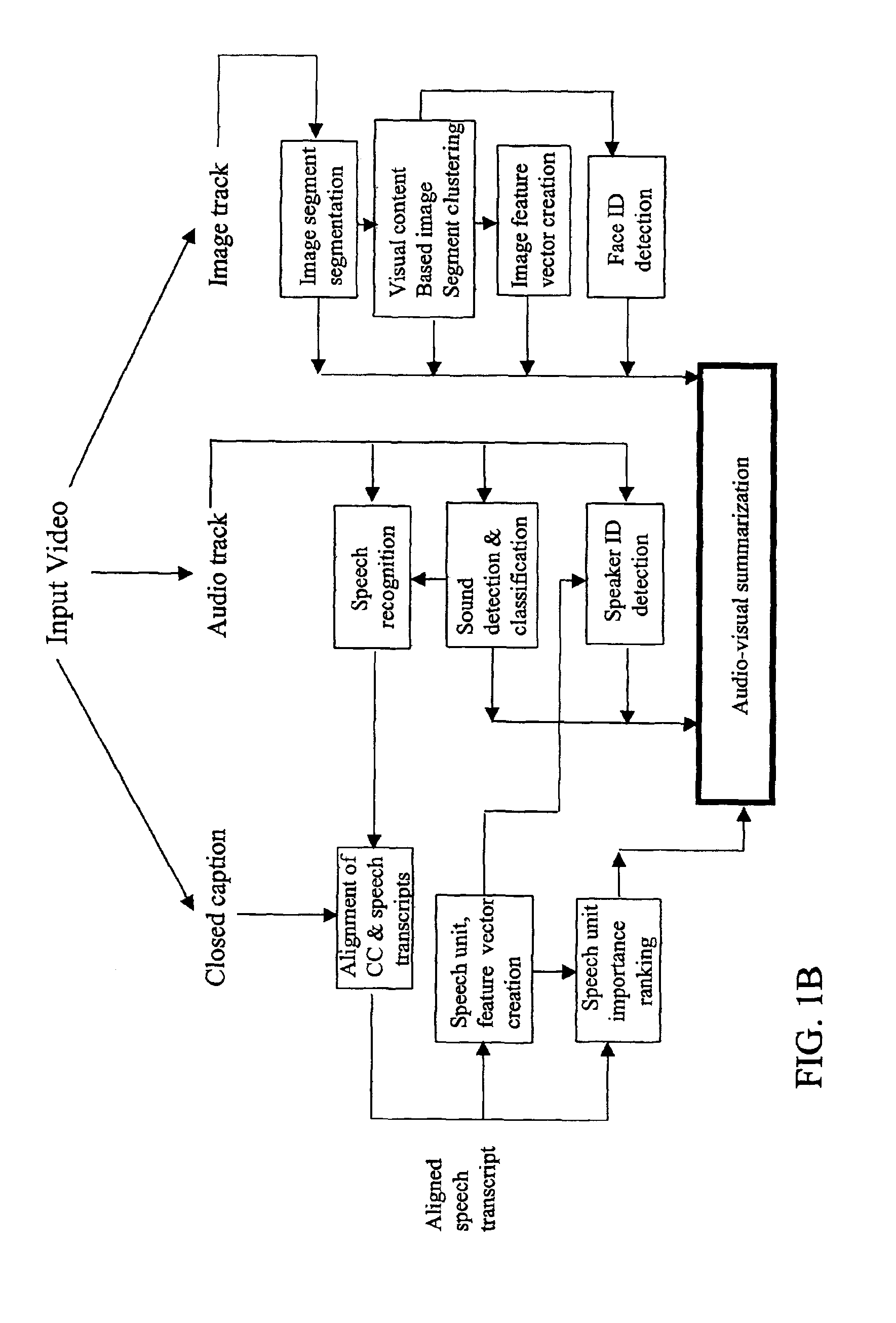

Creating audio-centric, image-centric, and integrated audio-visual summaries

InactiveUS6925455B2Increase the number ofQuick identificationTelevision system detailsPulse modulation television signal transmissionLearning basedProbabilistic method

Systems and methods create high quality audio-centric, image-centric, and integrated audio-visual summaries by seamlessly integrating image, audio, and text features extracted from input video. Integrated summarization may be employed when strict synchronization of audio and image content is not required. Video programming which requires synchronization of the audio content and the image content may be summarized using either an audio-centric or an image-centric approach. Both a machine learning-based approach and an alternative, heuristics-based approach are disclosed. Numerous probabilistic methods may be employed with the machine learning-based learning approach, such as naïve Bayes, decision tree, neural networks, and maximum entropy. To create an integrated audio-visual summary using the alternative, heuristics-based approach, a maximum-bipartite-matching approach is disclosed by way of example.

Owner:NEC CORP