3D NAND memory array common source forming method

A 3D NAND and memory technology, which is applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of photolithography deformation, complicated steps, and device performance degradation, etc., to prevent etching damage, high etching selectivity, and simplify The effect of the production process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

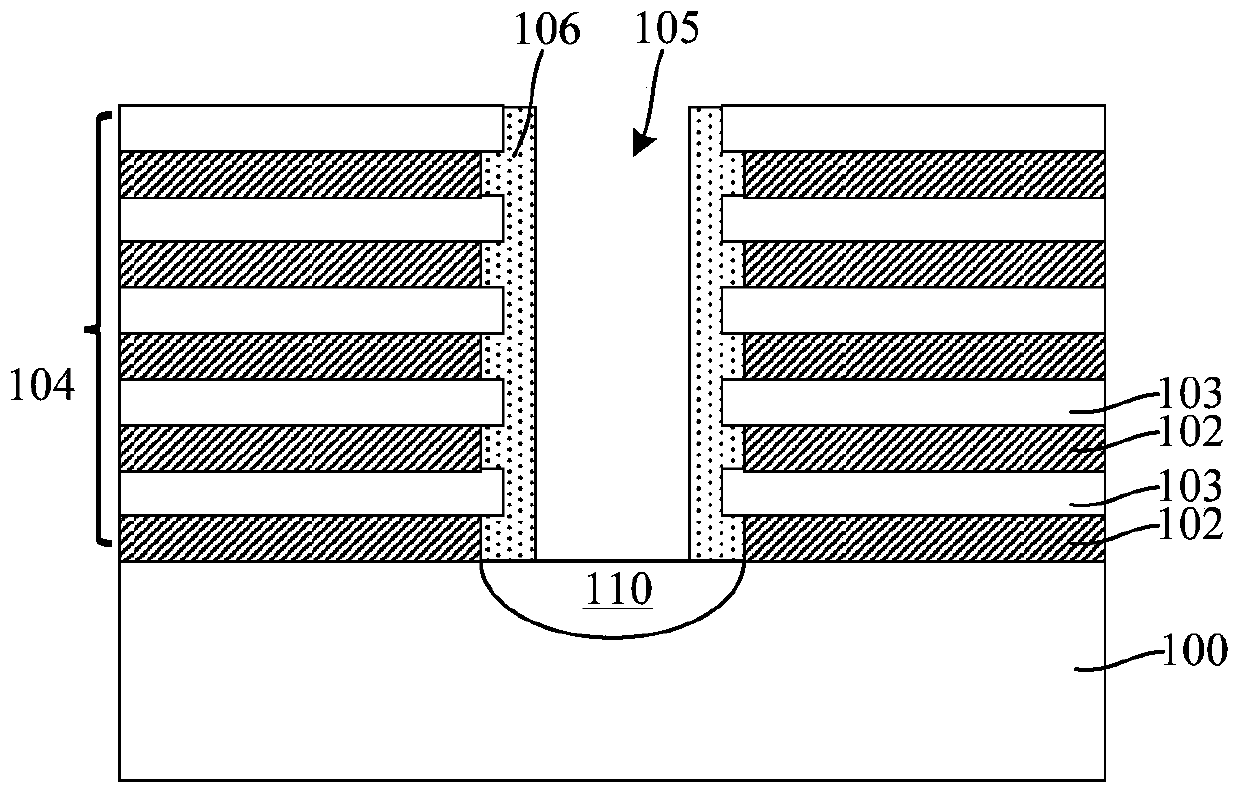

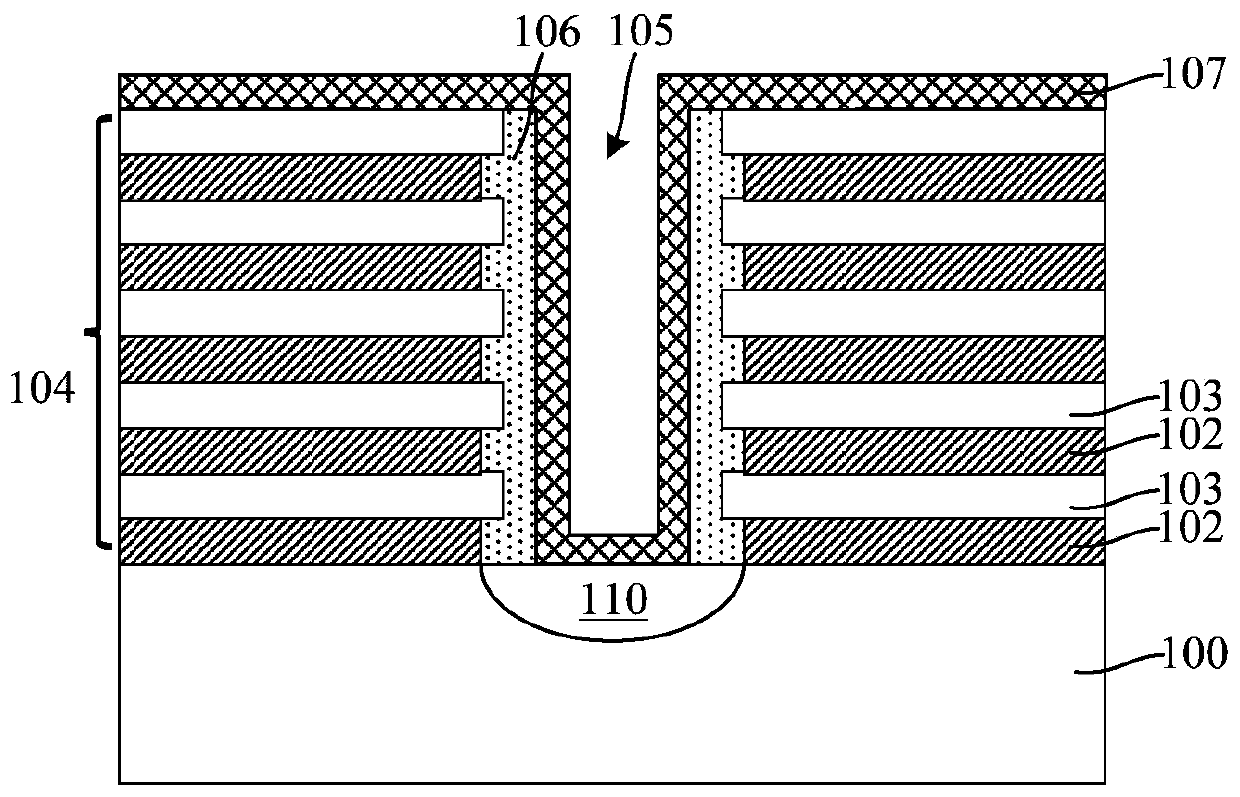

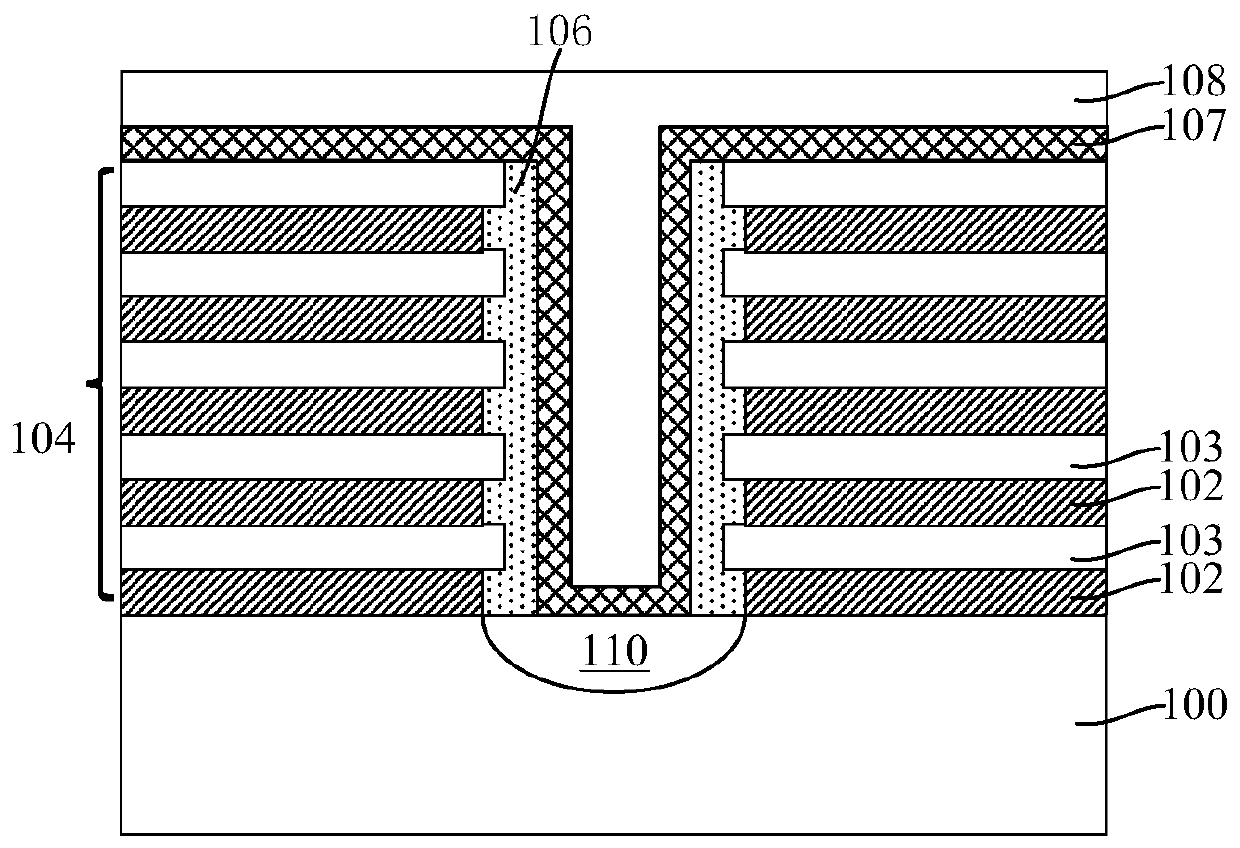

[0027] As mentioned in the background art, the existing steps of forming the array common source are relatively complicated, which increases the process cost.

[0028] It is found that the existing steps of forming the common source of the array include: providing a stack structure in which the control gate and the isolation layer are stacked on each other, and a gate spacer is formed in the stack structure; forming polysilicon on the surface of the gate spacer and the stack structure layer; then planarize (chemical mechanical polishing, CMP) the polysilicon layer until the surface of the stack structure is exposed; after the planarization step, etch back to remove the polysilicon layer with a partial thickness in the gate spacer; the polysilicon layer after etch back The surface of the layer is filled with metal to form a metal plug. The aforementioned steps of forming the common source of the array are relatively complicated, which increases the process cost.

[0029] For t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com