Multilayered medium etching method

A technology of multi-layer dielectric and etching gas, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as difficult to realize, thin dielectric layer, and affect the quality of etching structure, etc., to achieve the adjustment of etching rate , the effect of increasing the etching rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

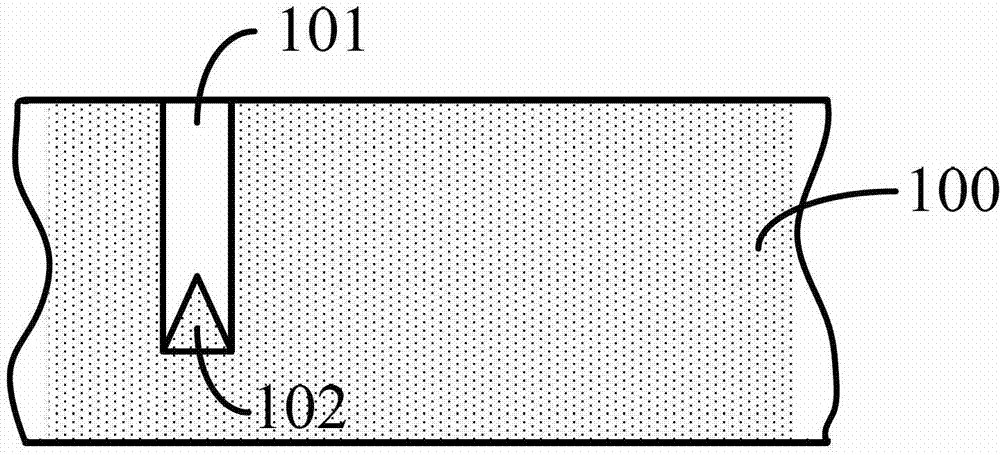

Image

Examples

Embodiment Construction

[0038] In order to make the purpose, technical solution and advantages of the present invention clearer, the following will further describe the implementation of the present invention in detail in conjunction with the accompanying drawings. Those skilled in the art can easily understand other advantages and effects of the present invention from the contents disclosed in this specification. The present invention can also be implemented or applied through other different specific implementation modes, and various modifications or changes can be made to the details in this specification based on different viewpoints and applications without departing from the spirit of the present invention.

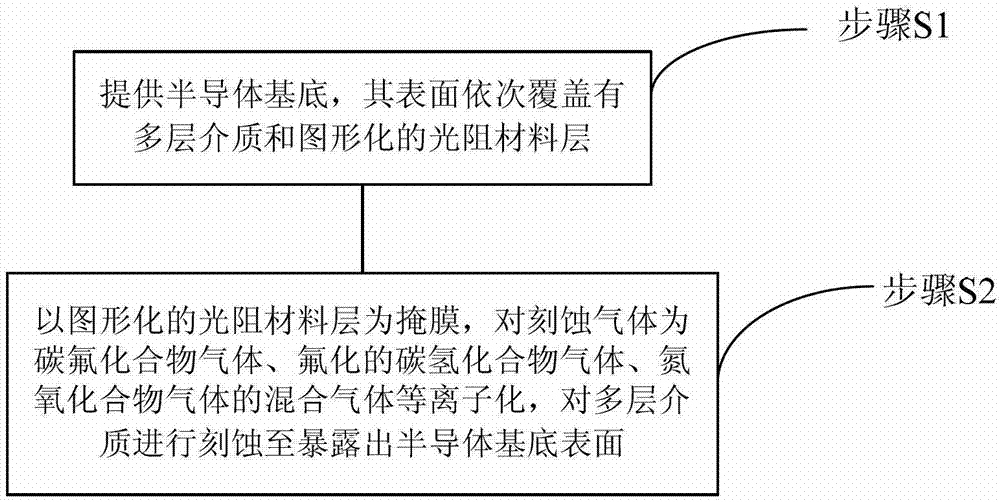

[0039] figure 2 It is a flow chart of the steps of the multilayer dielectric etching method provided by the present invention.

[0040] Such as figure 2 As shown, the multilayer dielectric etching method provided in this specific embodiment includes the following steps:

[0041] Step ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More