Patents

Literature

35results about How to "Control etch rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Photoresist stripping liquid

InactiveCN101295144AEfficient degreasing abilityControl etch ratePhotosensitive material processingOrganic solventCleansing Agents

The invention discloses a cleaning agent which has simple preparation method, low cost and low corrosion rate on substrate material and metallic wiring, and no pollution on environment and is used for removing the residues of photoresist. According to the weight percentage, the cleaning agent comprises the following raw materials: 1%-15% of surfactant, 5%-40% of organic amine, 5%-30% of organic solvent, 0.1%-5% of chelating agent, 0.01%-5% of corrosion inhibitor and residual quantity of pure water.

Owner:DALIAN SANDAAOKE CHEM

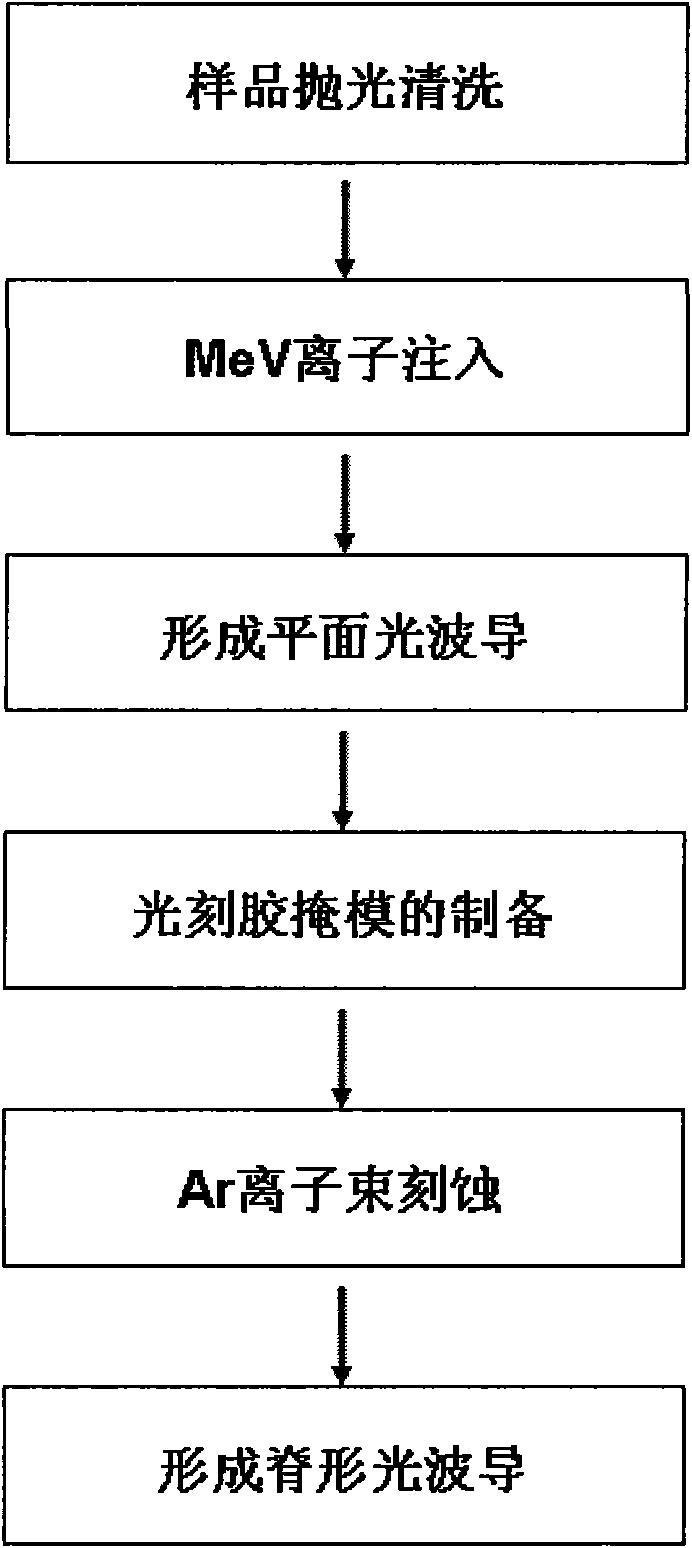

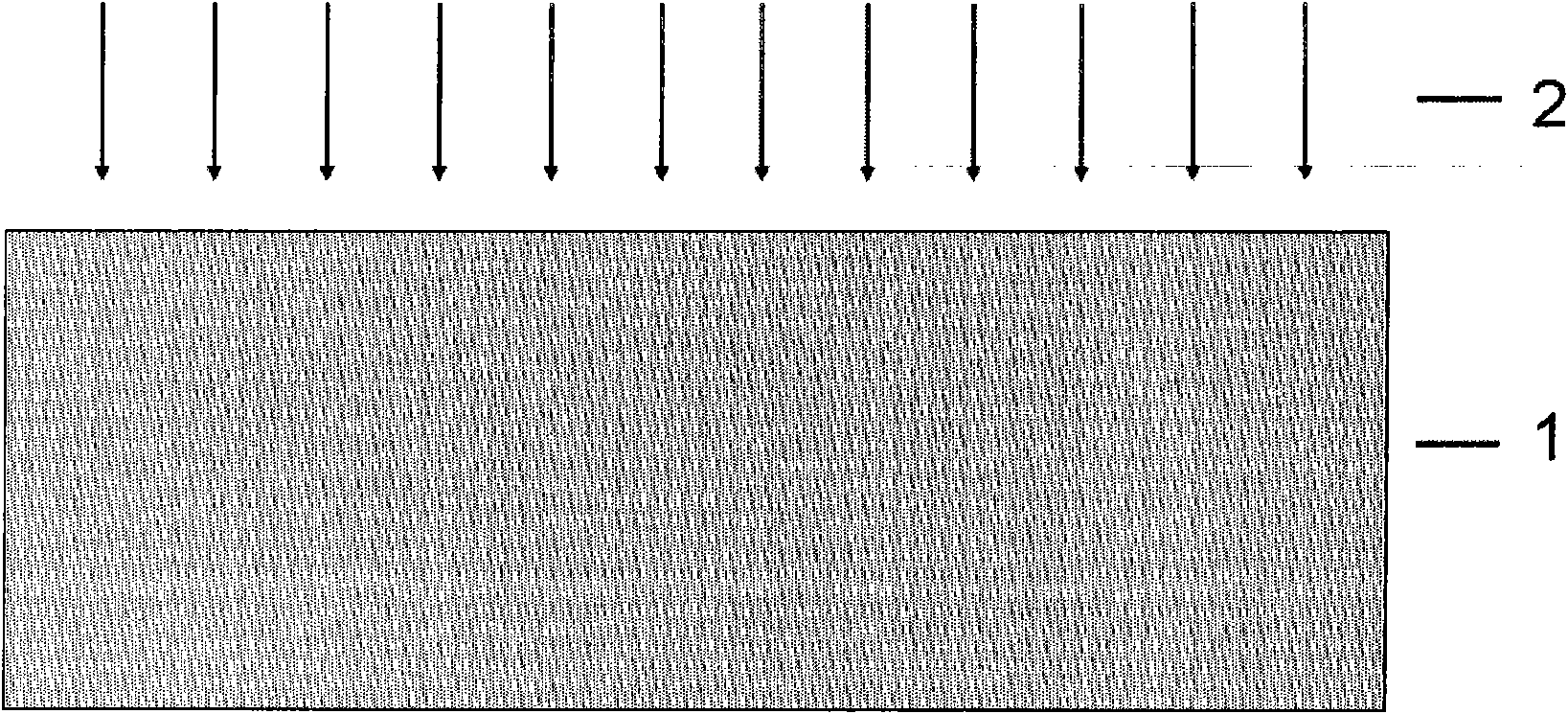

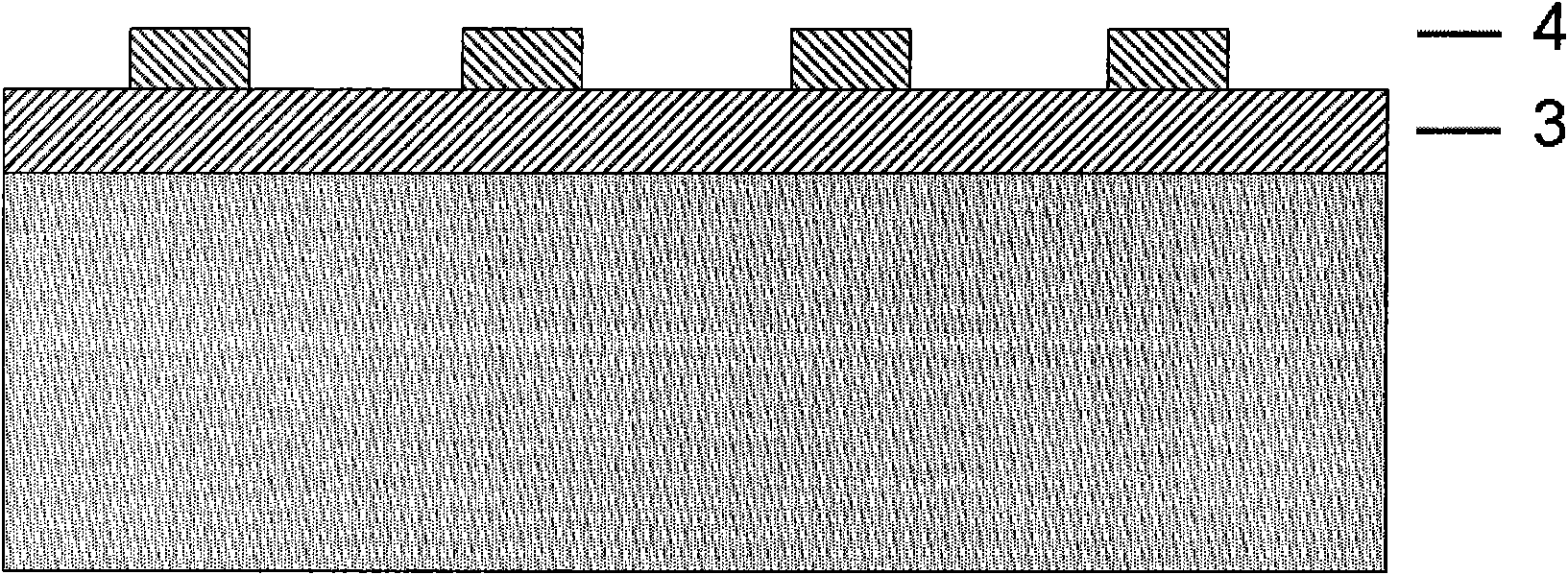

Method for preparing KTP rib optical waveguide by combining ion implantation with ion beam etching

InactiveCN101943768AControlling waveguide propertiesControl etch rateOptical light guidesOptical modulatorLight wave

The invention discloses a method for preparing a KTP rib optical waveguide by combining ion implantation with ion beam etching, and belongs to the technical field of preparation of photoelectronic devices. The preparation method comprises the following steps of: optically polishing the surface and two opposite end faces of a z-cut KTP crystal with the dimension of 10mm*10mm*1mm; cleaning samples by using acetone, deionized water and alcohol, and performing ion implantation to obtain a planar optical waveguide; coating a BP218 photoresist on the samples in a spinning mode, exposing a mask plate, and developing and hardening to form a bar-shaped mask of the photoresist; putting the samples into a target chamber of an ion beam etcher, vacuumizing to reach the pressure of 10<-4>Pa and performing ion beam etching; and cleaning the photoresist mask to prepare the rib optical waveguide. The prepared rib optical waveguide has the advantages of capacity of well keeping the nonlinear optical property of the KTP crystal, and potential application value in the preparation of optical switches and optical modulators and in other aspects.

Owner:SHANDONG UNIV

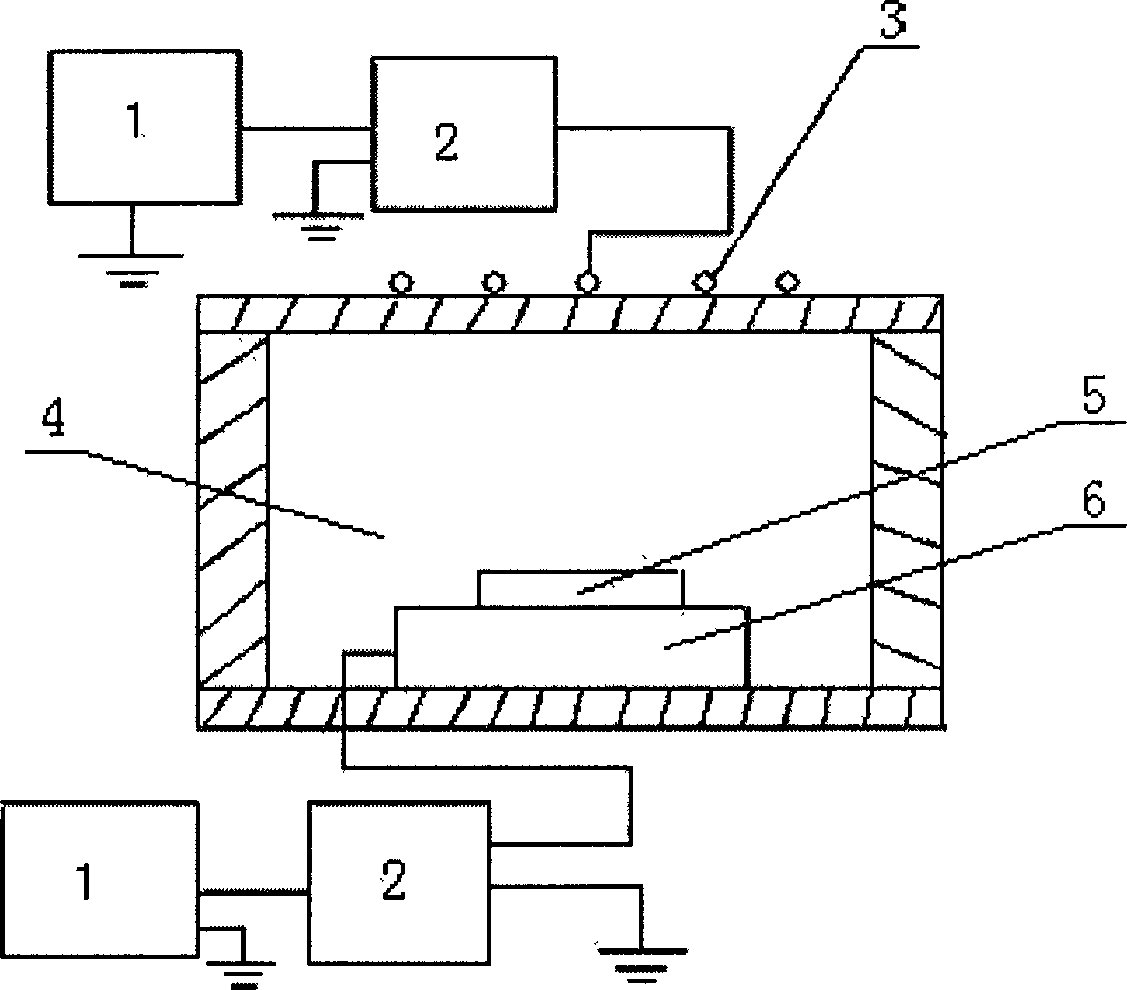

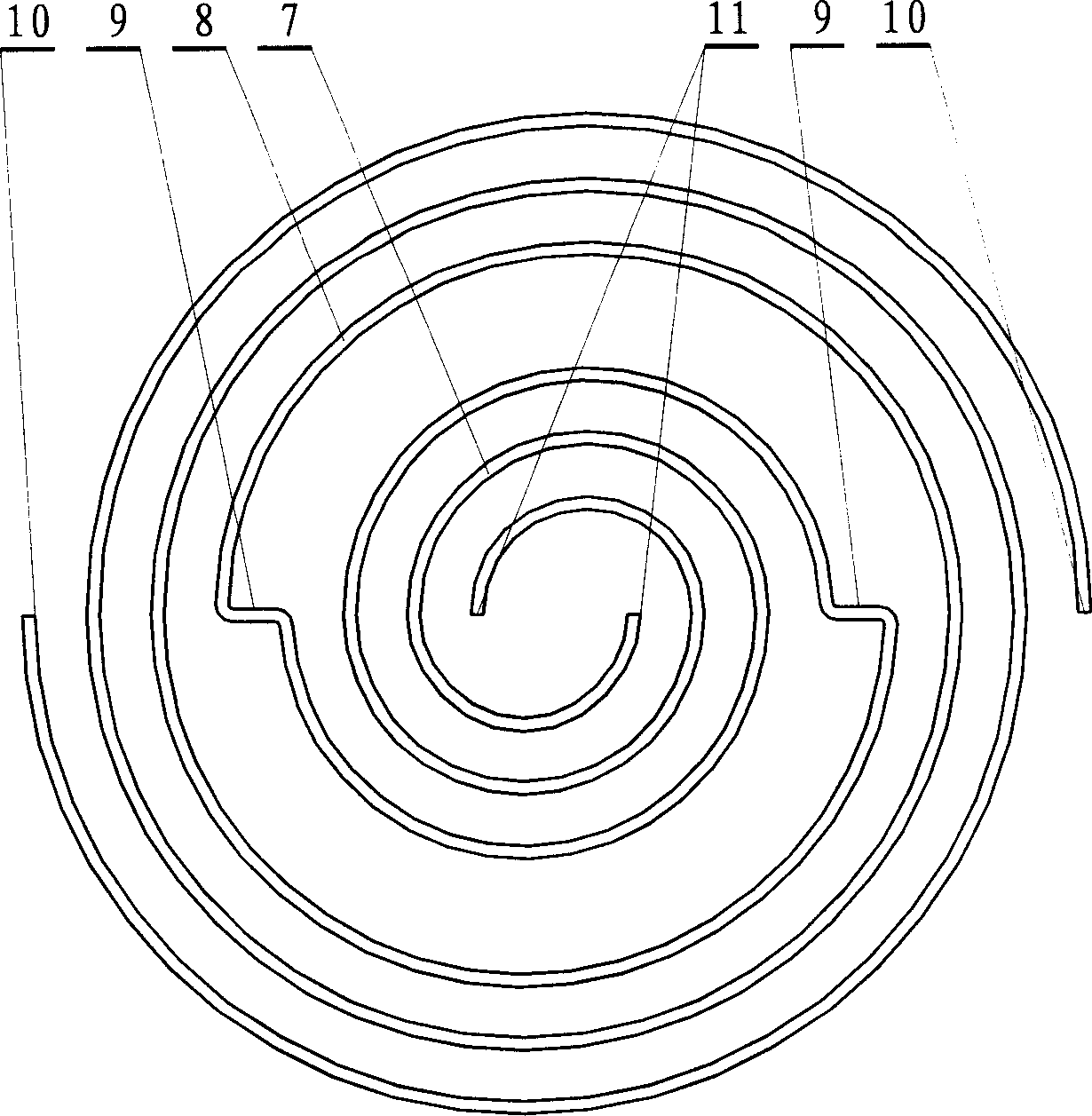

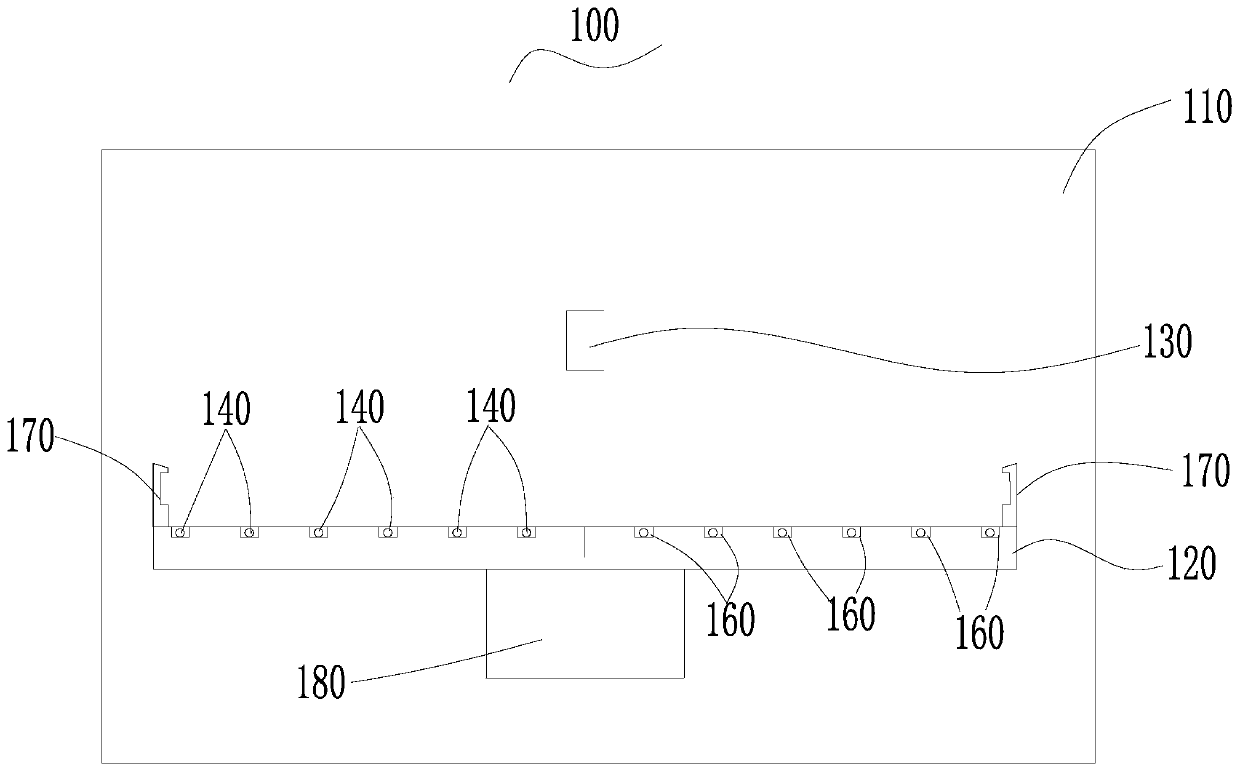

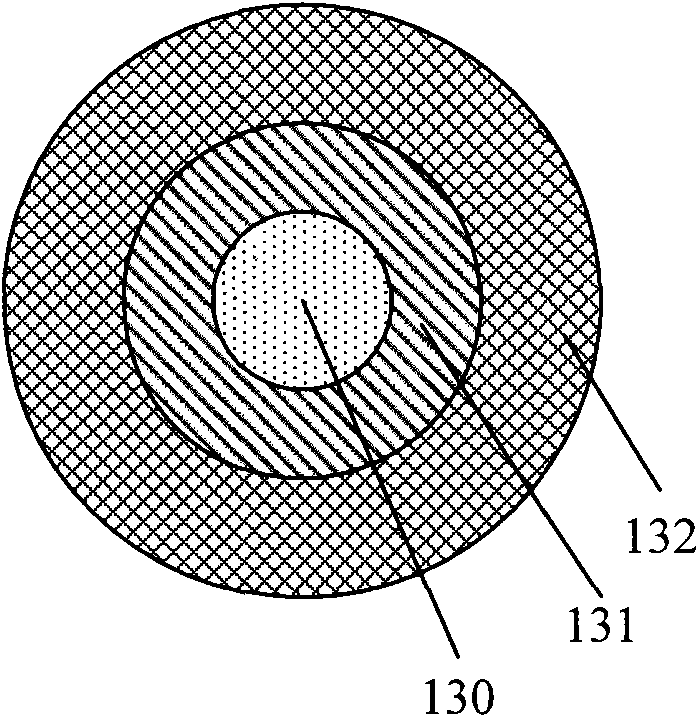

Inductance coupled coil and inductance coupled plasma device

ActiveCN1825505ASymmetrical distributionImprove distribution uniformitySemiconductor/solid-state device manufacturingPlasma techniqueInductively coupled plasmaElectromagnetic field

The invention is an inductance coupling coil, nested of two groups of involute coils, where the involute coil can be a segment of involute, or composed of inner and outer coils of an involute shape, and the two groups of involute coils are the same in shape and centro-symmetrically distributed. And the design of a completely symmetrical plane coil structure makes electromagnetic field distribution in a reaction chamber quite symmetrical, thus improving distribution uniformity of plasma in the reaction chamber so as to make etching rates of all points on the surface of a wafer closer. And an inductance coupled plasma device of this structure reduces the inductance of the inductance coupling coil, thus able to be very easy to obtain a large-area plasma and improve plasma uniformity in the large-area process. And it can improve the quality of etching wafer.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

Cleaning agent for polishing wafer

InactiveCN101289641AMeet polishing and cleaning requirementsControl etch rateOrganic detergent compounding agentsNon-ionic surface-active compoundsSurface-active agentsRaw material

The invention provides a cleaning agent for wafer polishing, which is simple in preparation method and low in cost, doest not pollute the environment and can meet the polishing and cleaning requirements of a wafer with a line width dimension of 90 nanometers or less than 90 nanometers. The compositions by weight percentage of raw materials are: 5 to 15 percent of surface active agent, 0.01 to 10 percent of organic alkali, 5 to 20 percent of pH regulator, 2 to 5 percent of osmotic agent, 0.1 to 2 percent of chelon, the balance being pure water.

Owner:DALIAN SANDAAOKE CHEM

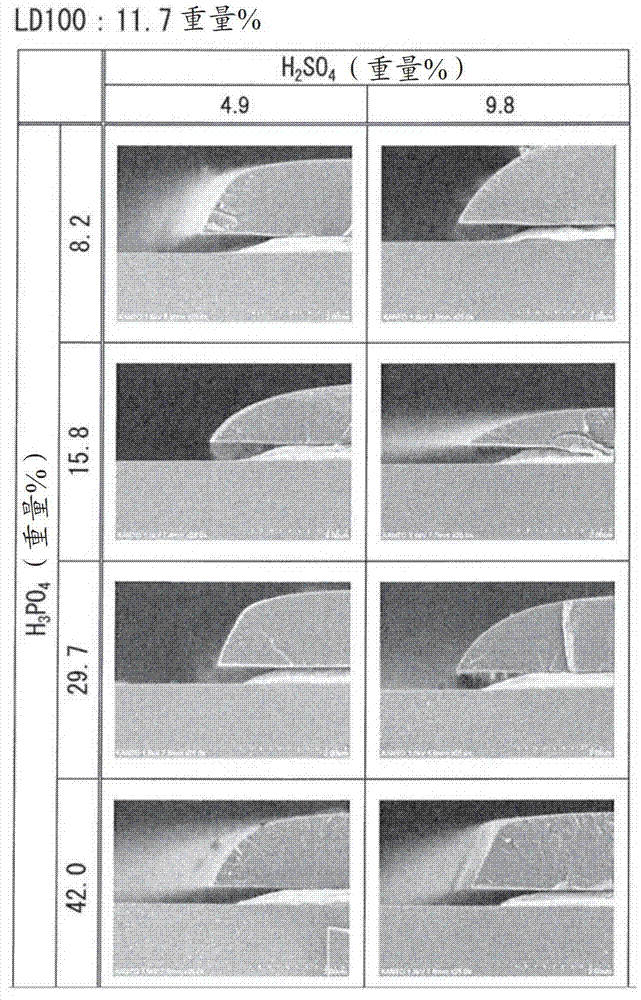

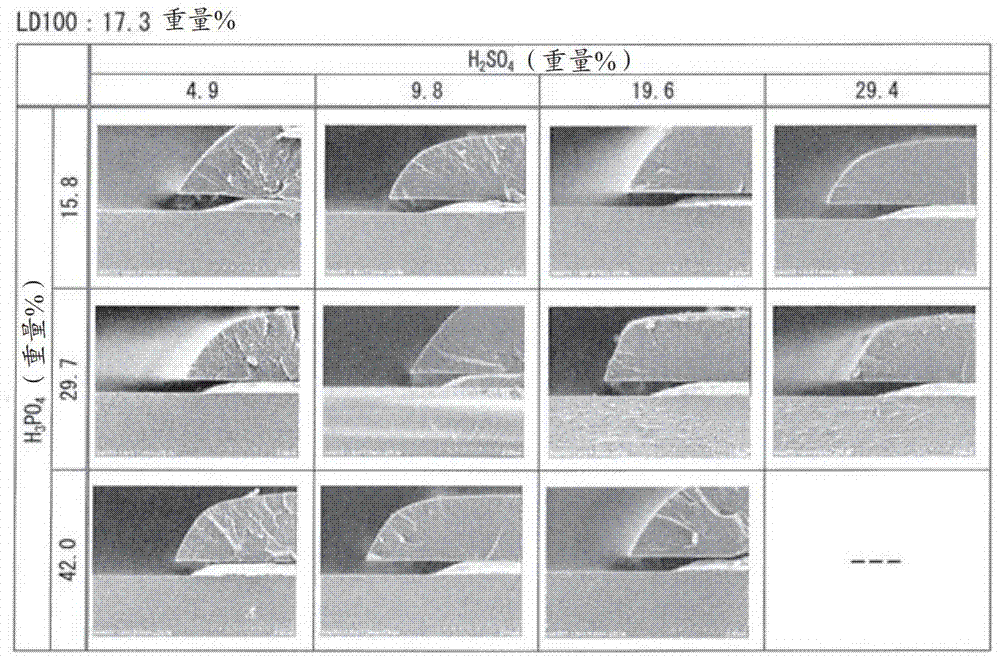

Etching solution composition and etching method for copper and copper alloy

InactiveCN102995021AHigh in-plane uniformity of suppressionControl etch rateSemiconductor/solid-state device manufacturingPhosphoric acidCopper oxide

The invention aims to provide an etching solution composition and an etching method for copper and copper alloy. A metal laminated film containing a copper layer and a copper oxide layer and / or a copper alloy layer is etched by the etching solution composition with good precision, thereby forming an excellent sectional shape, realizing excellent practicability and stability and achieving long service lifetime. The etching solution composition is used to etch the metal laminated film containing the copper layer and the copper oxide layer and / or the copper alloy layer. In addition, the etching solution composition contains 0.1-80 wt% of persulfate solution and / or persulfuric acid solution, 0.1-80 wt% of phosphoric acid and 0.1-50 wt% of nitric acid and / or sulfuric acid and is further added with chloride ions and ammonium ions, thereby making it easy to control the etching rate and the sectional shape.

Owner:KANTO CHEM CO INC

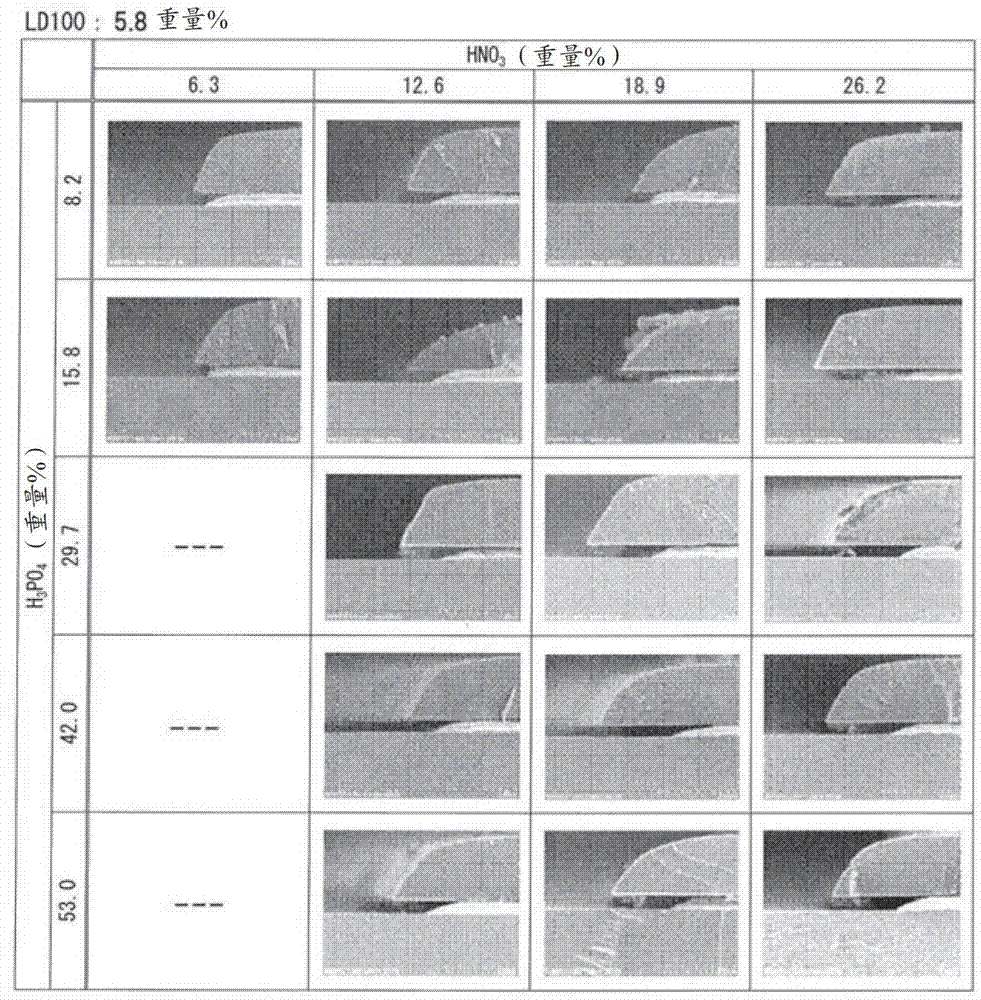

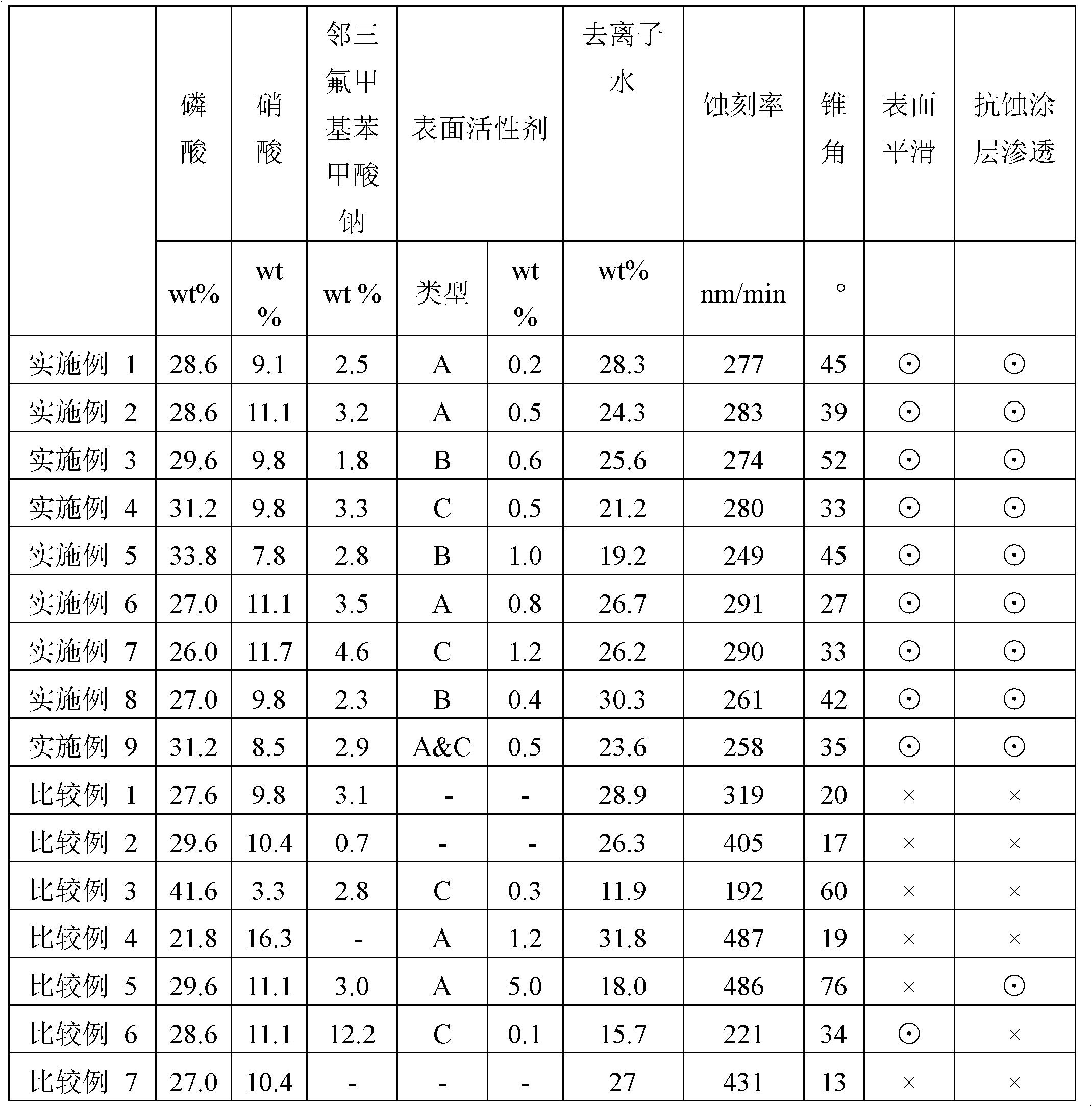

Aluminum film-containing etching solution for liquid crystal display screen

The invention discloses aluminum film-containing etching solution for a liquid crystal display screen. The etching solution comprises 20 to 42 weight percent of phosphoric acid, 0.65 to 20 weight percent of nitric acid, 0.01 to 5 weight percent of nonionic surfactant, 0.5 to 15 weight percent of organic acid salt and the balance of water. The etching solution can etch the aluminum film or the aluminum alloy film with excellent controllability to obtain the metal film with the proper conical shape and flat and smooth surface.

Owner:绵阳艾萨斯电子材料有限公司

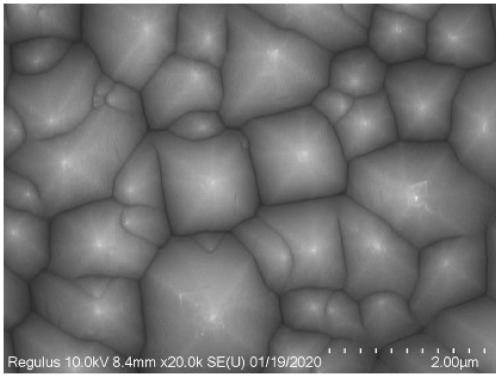

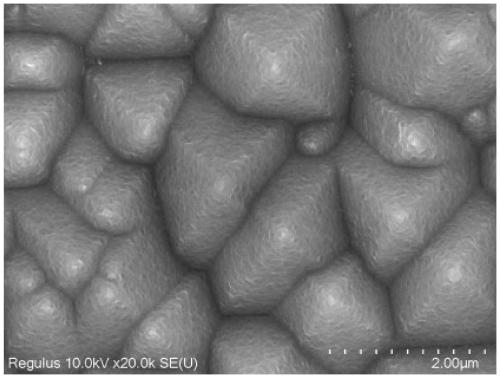

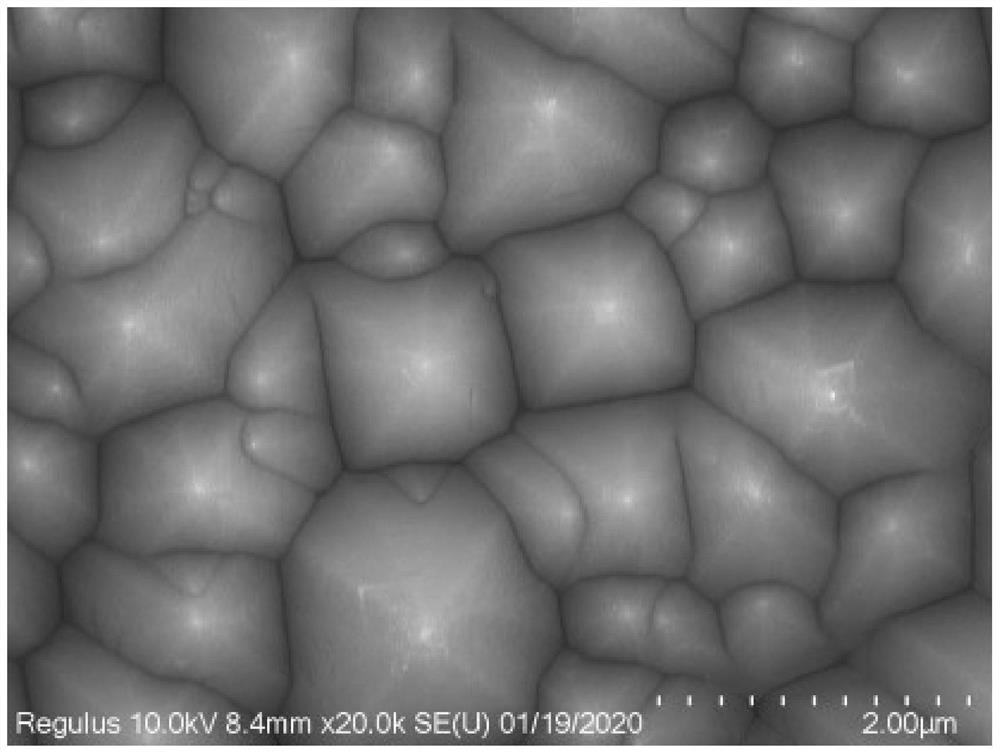

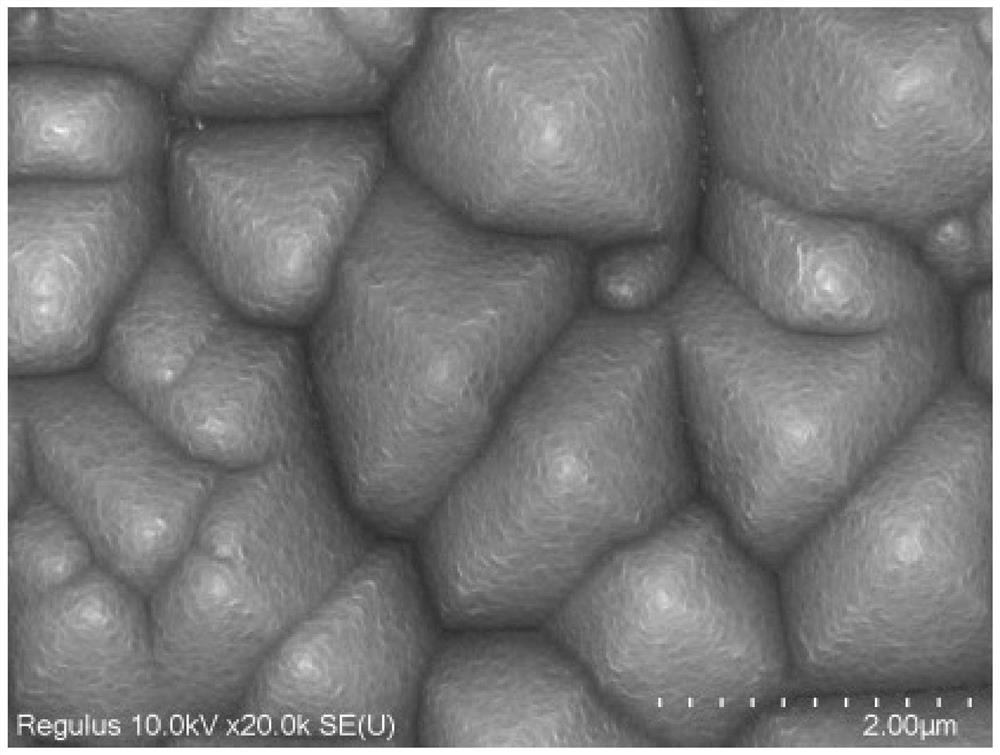

Additive for preparing porous pyramid structure by secondary texturing of monocrystalline silicon wafer and application thereof

ActiveCN111254497ALow cost methodSimple processPolycrystalline material growthAfter-treatment detailsActive agentSurface-active agents

The invention discloses an additive for preparing a porous pyramid structure by secondary texturing of a monocrystalline silicon wafer. The additive comprises the following components in percentage bymass: 0.1-10% of sodium polystyrenesulfonate, 2-20% of polyethylene glycol, 1-5% of a fluorocarbon surfactant and 20-30% of inorganic salt, with the balance being water. The additive disclosed by theinvention is added into texturing liquid for secondary texturing of the monocrystalline silicon wafer, so the porous pyramid structure can be formed on the surface of the monocrystalline silicon wafer. The method for preparing the porous pyramid structure of the monocrystalline silicon wafer is lower in cost and simpler in process.

Owner:CHANGZHOU SHICHUANG ENERGY CO LTD

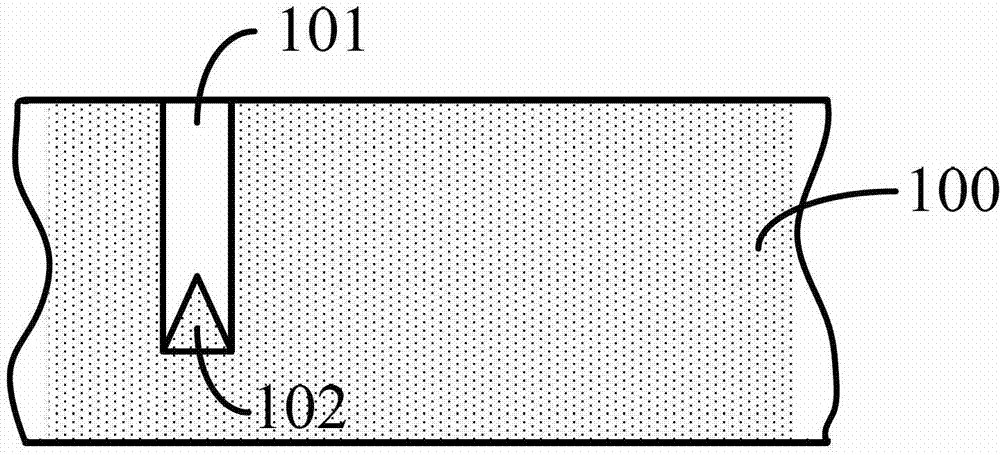

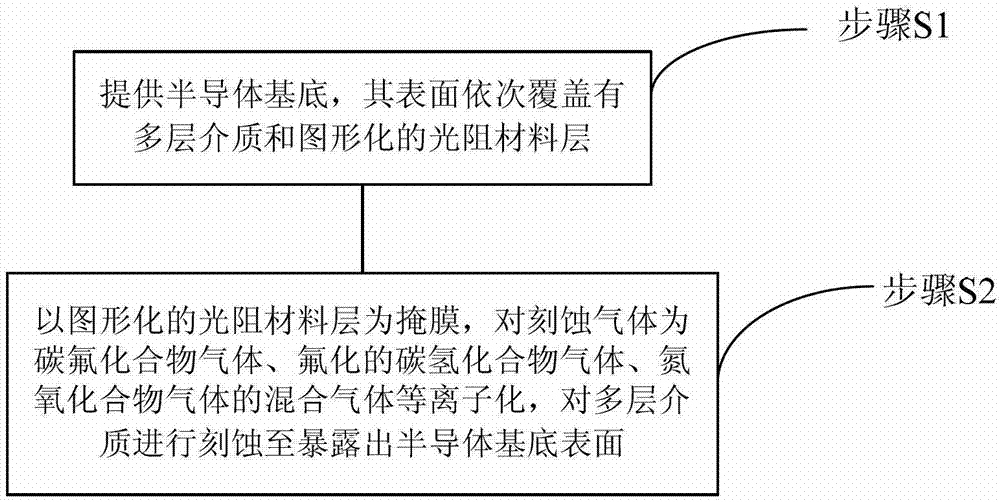

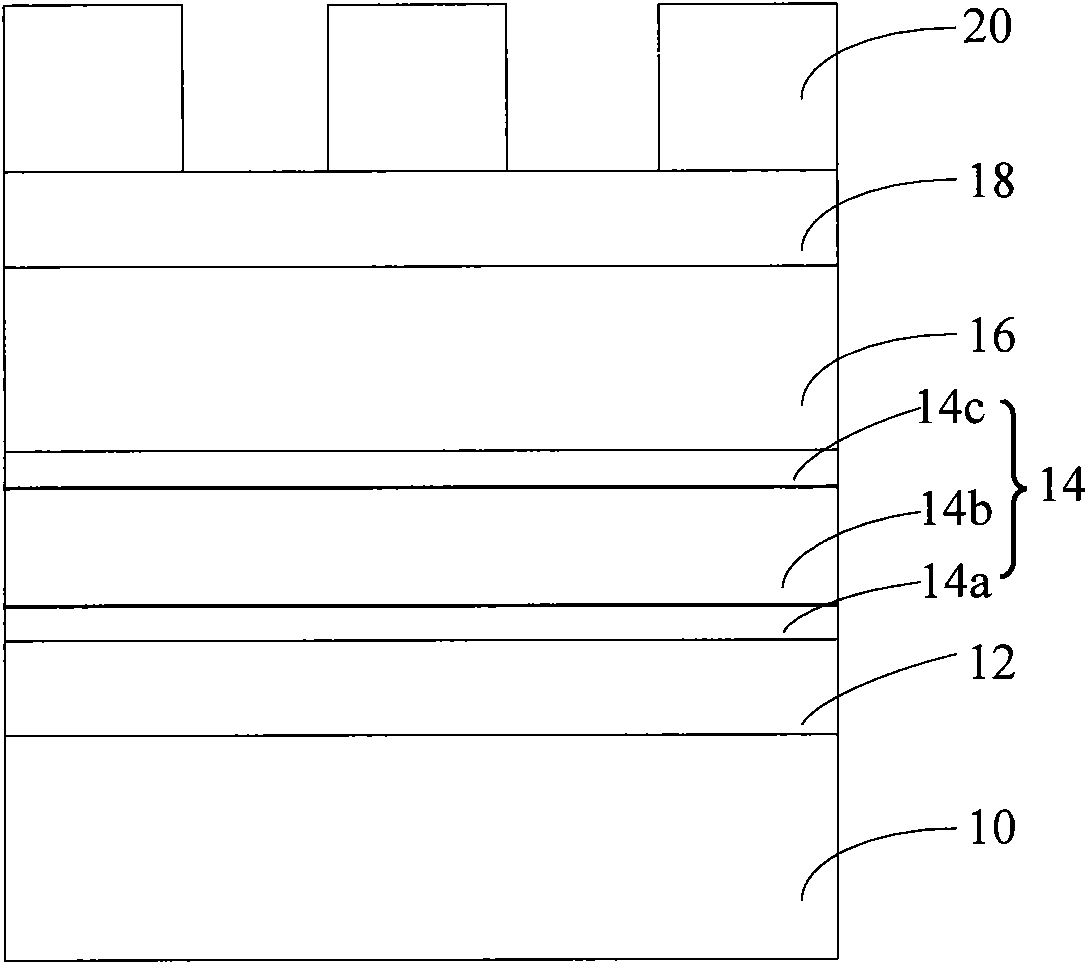

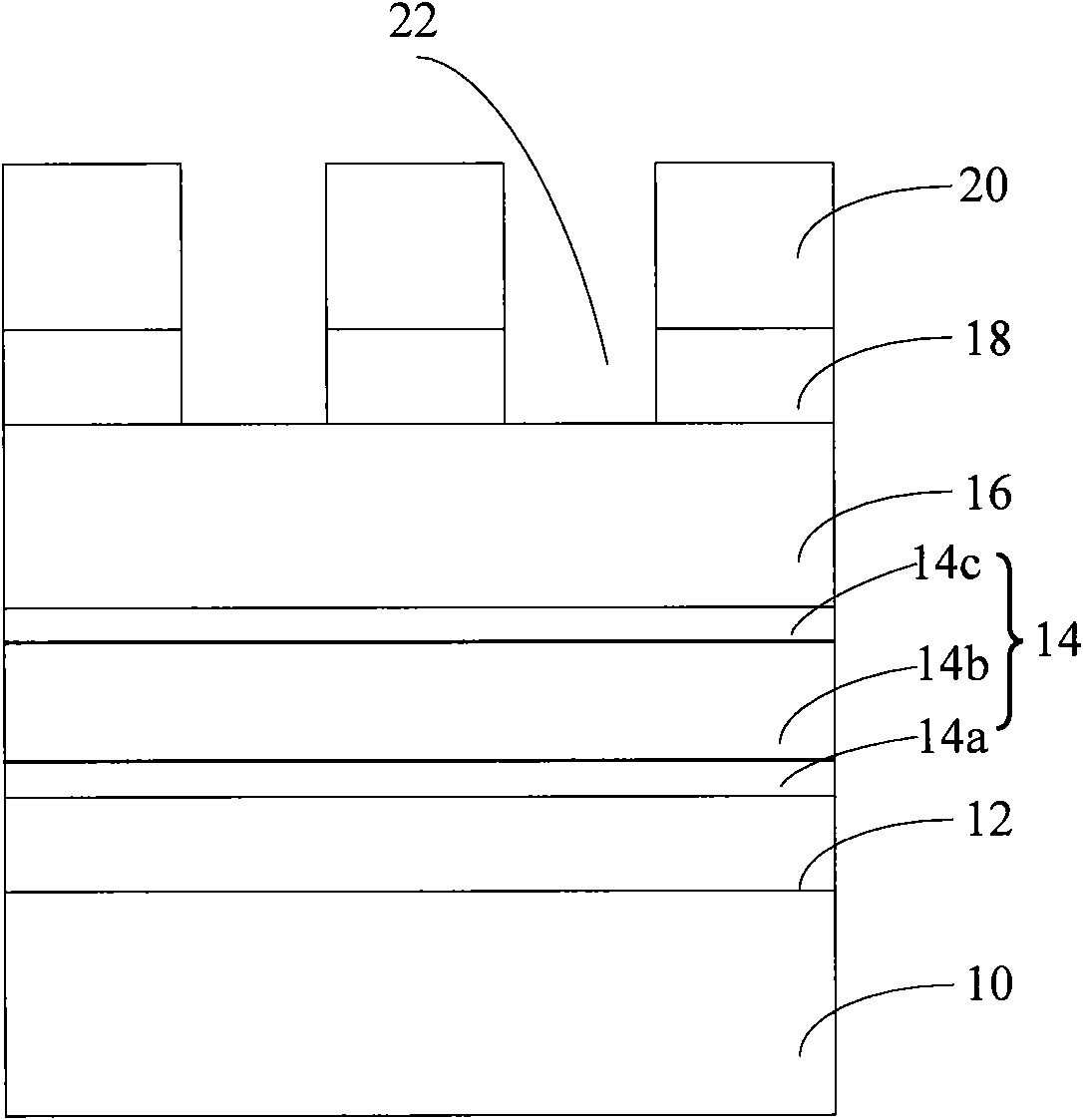

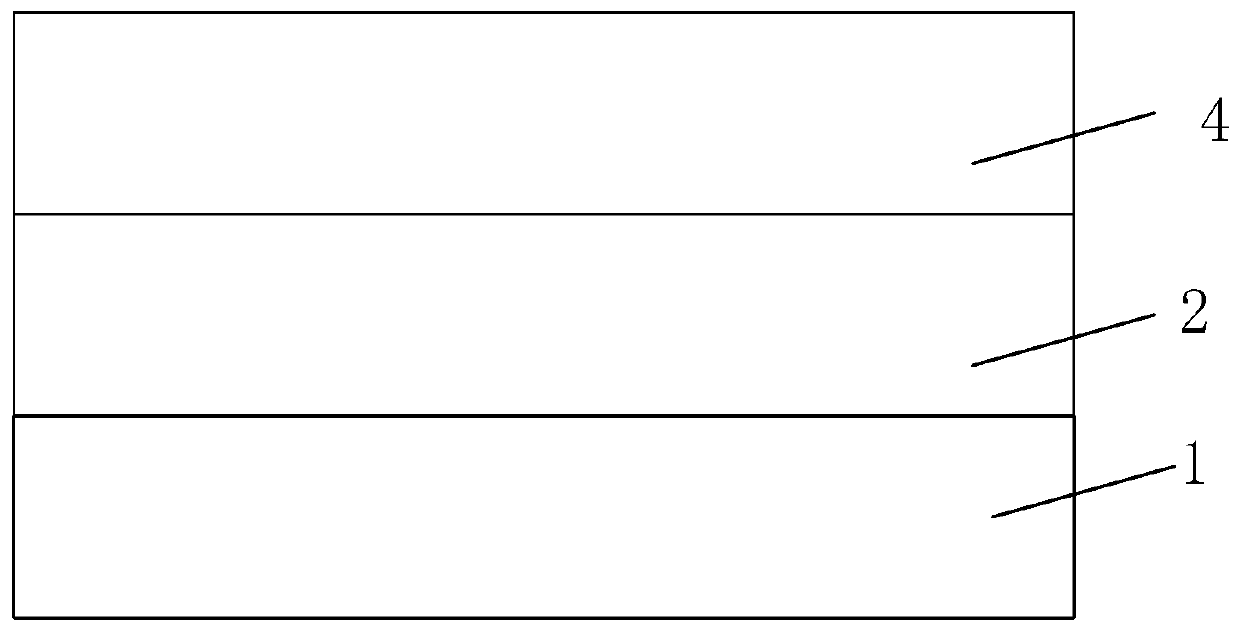

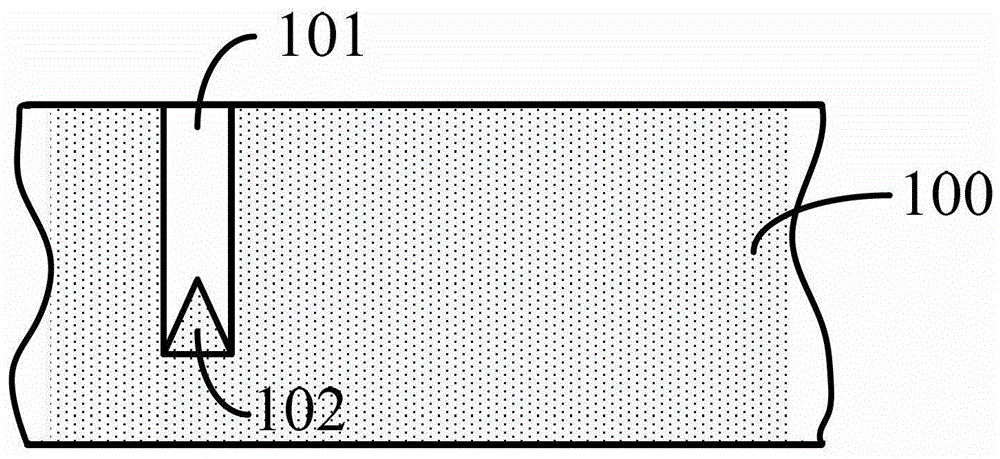

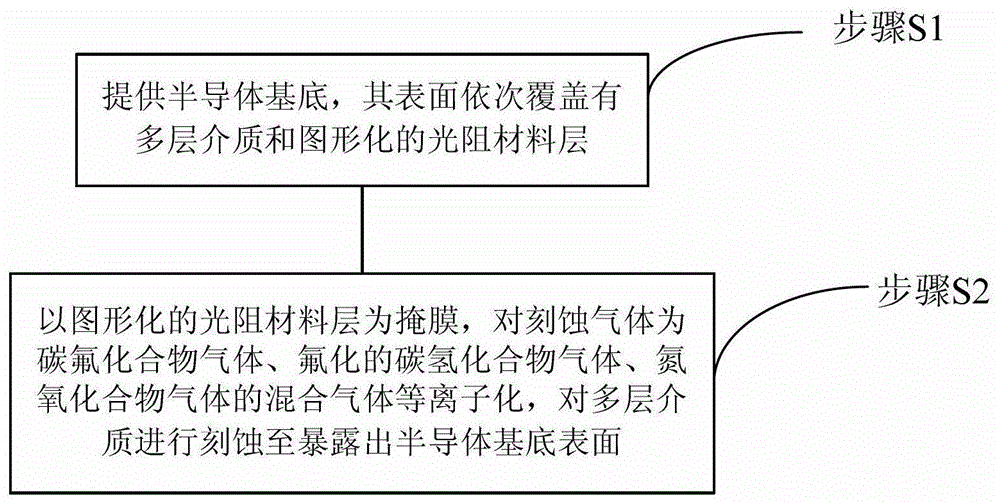

Multilayered medium etching method

ActiveCN103050396AIncrease etch rateAdjust densitySemiconductor/solid-state device manufacturingHydrogenNitrogen oxide

The invention relates to the technical field of a semiconductor, and discloses a multilayered medium etching method. The method comprises the following steps of: providing a semiconductor substrate, wherein the surface of the semiconductor substrate is sequentially coated with the multilayered medium and a graphic photoresist layer; and ionizing the etching gas which is the mixed gas such as fluorocarbon gas, fluorinated carbureted hydrogen gas and nitrogen oxide gas by taking the graphic photoresist layer as a mask, and etching the multilayered medium by the etching gas until the multilayered medium is exposed to the surface of the semiconductor substrate. The method takes the fluorocarbon gas and the fluorinated carbureted hydrogen gas with high C / F ratio as the main etching gas; and the nitrogen oxide gas in a certain flow is added, so that a purpose of etching the multilayered medium formed by different materials through one-step plasma etching primary is achieved, and the etching is not performed by many steps of layering the materials. The photoresist layer as the mask has a low etching rate.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

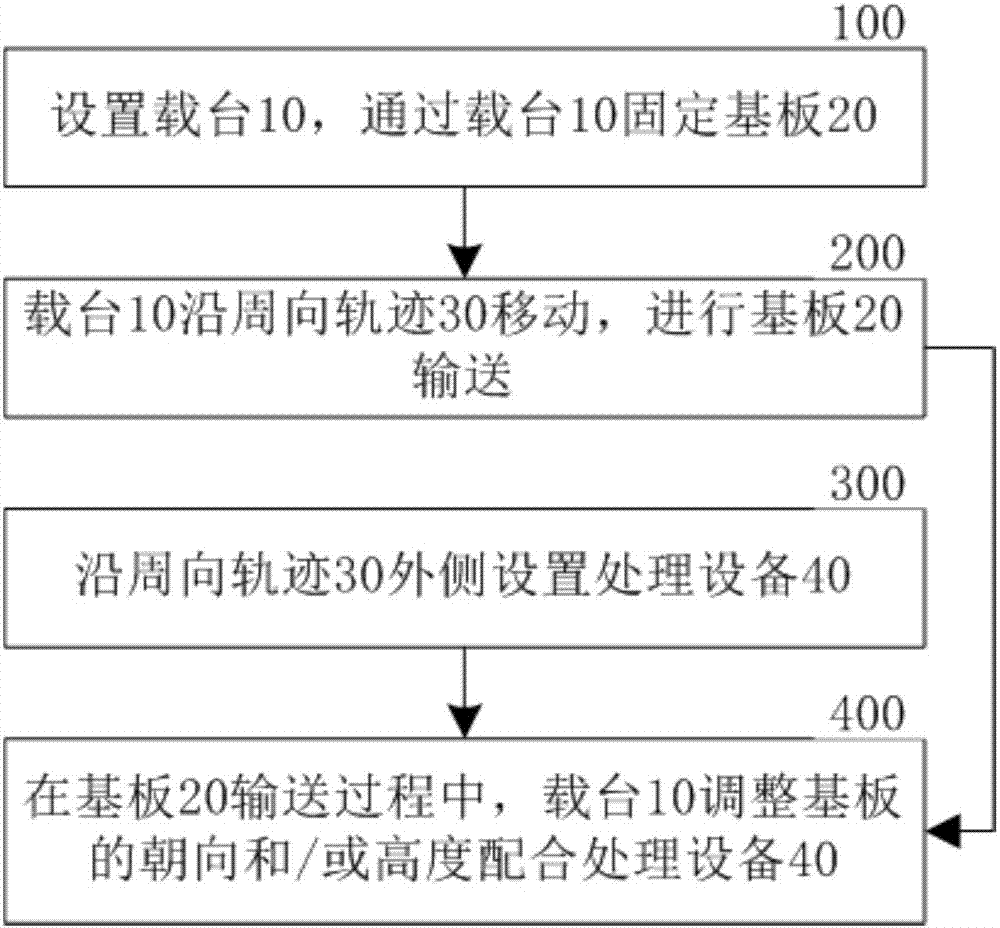

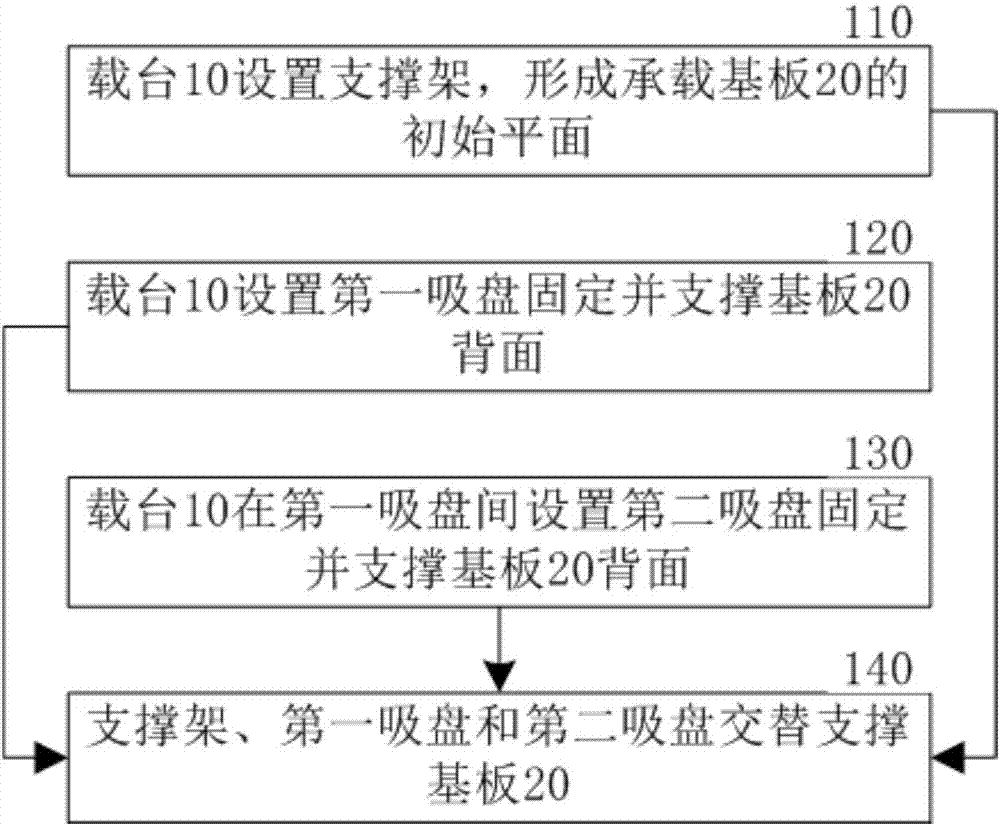

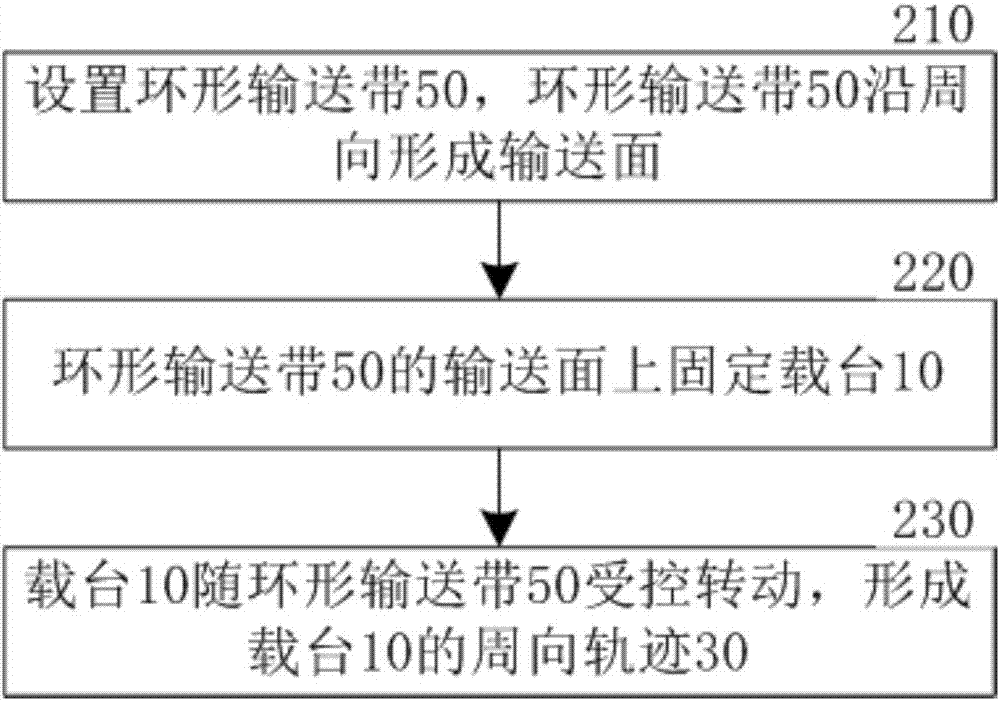

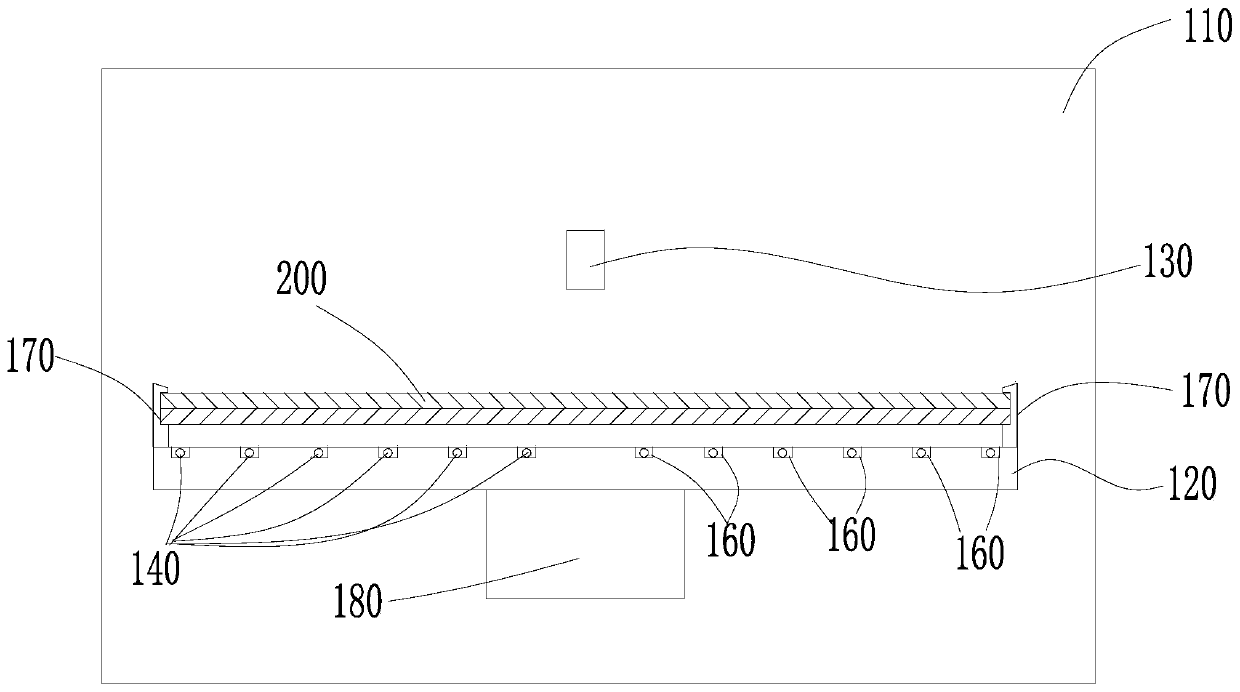

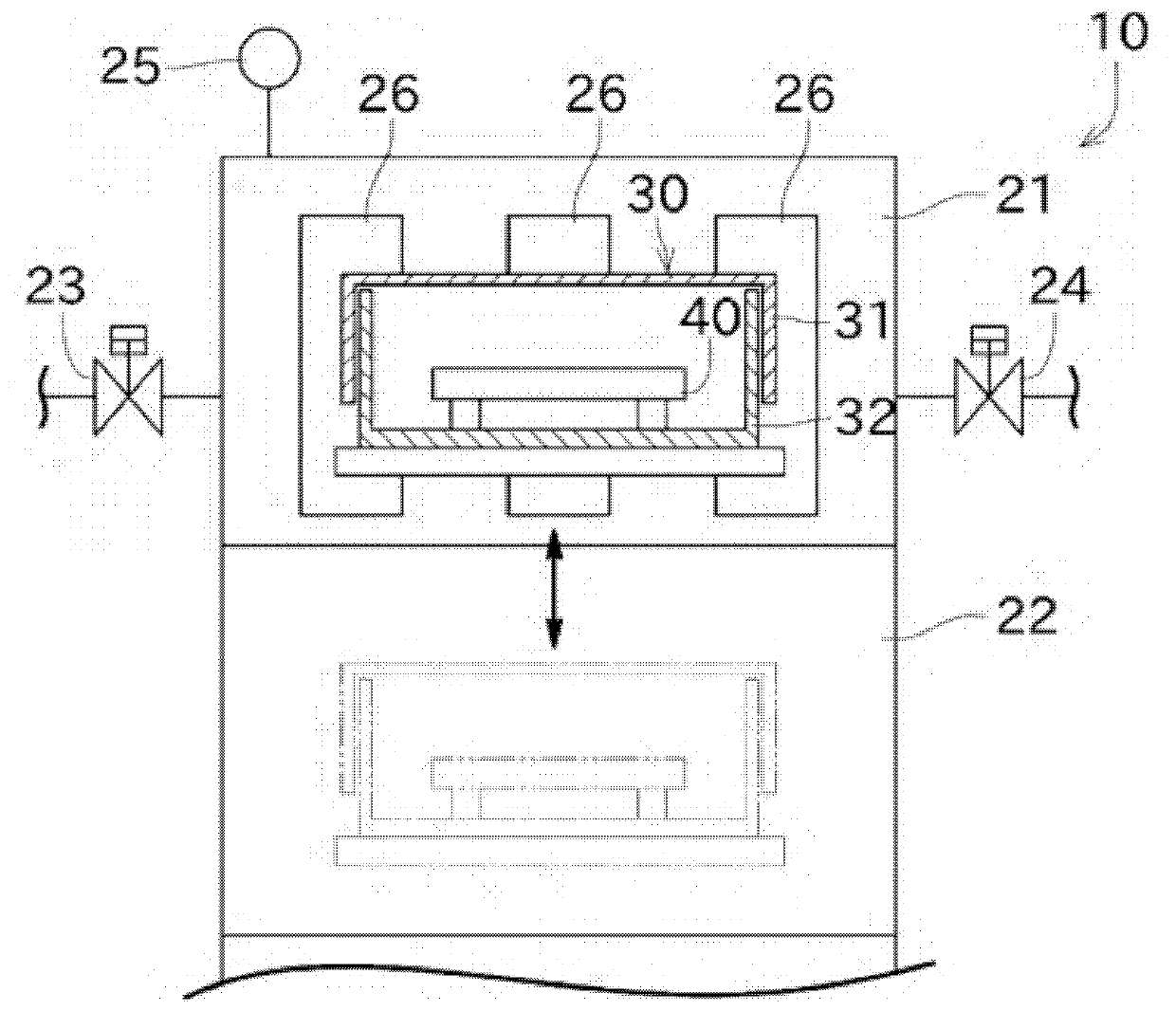

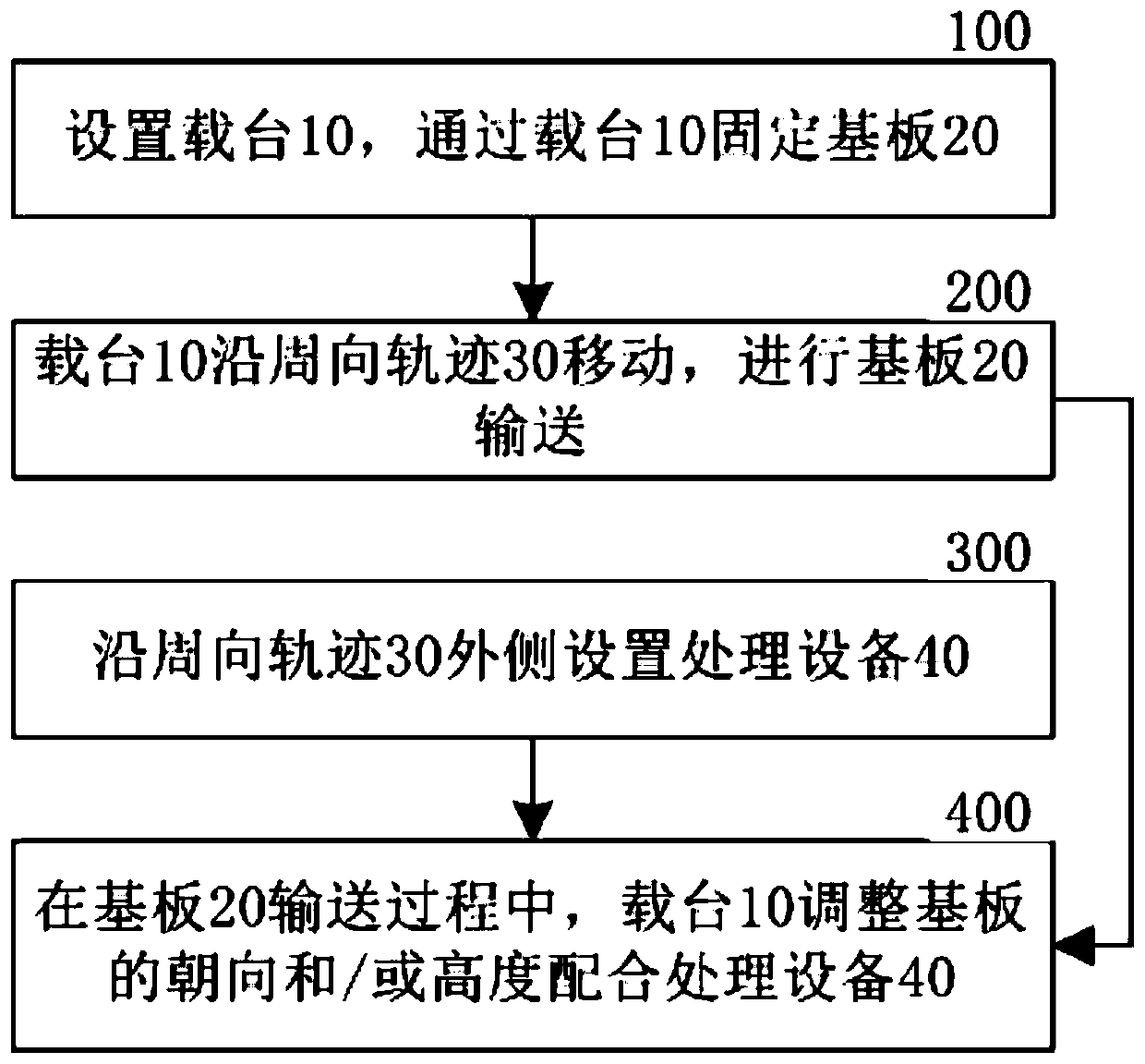

Substrate wet process technological method and substrate wet process technological apparatus

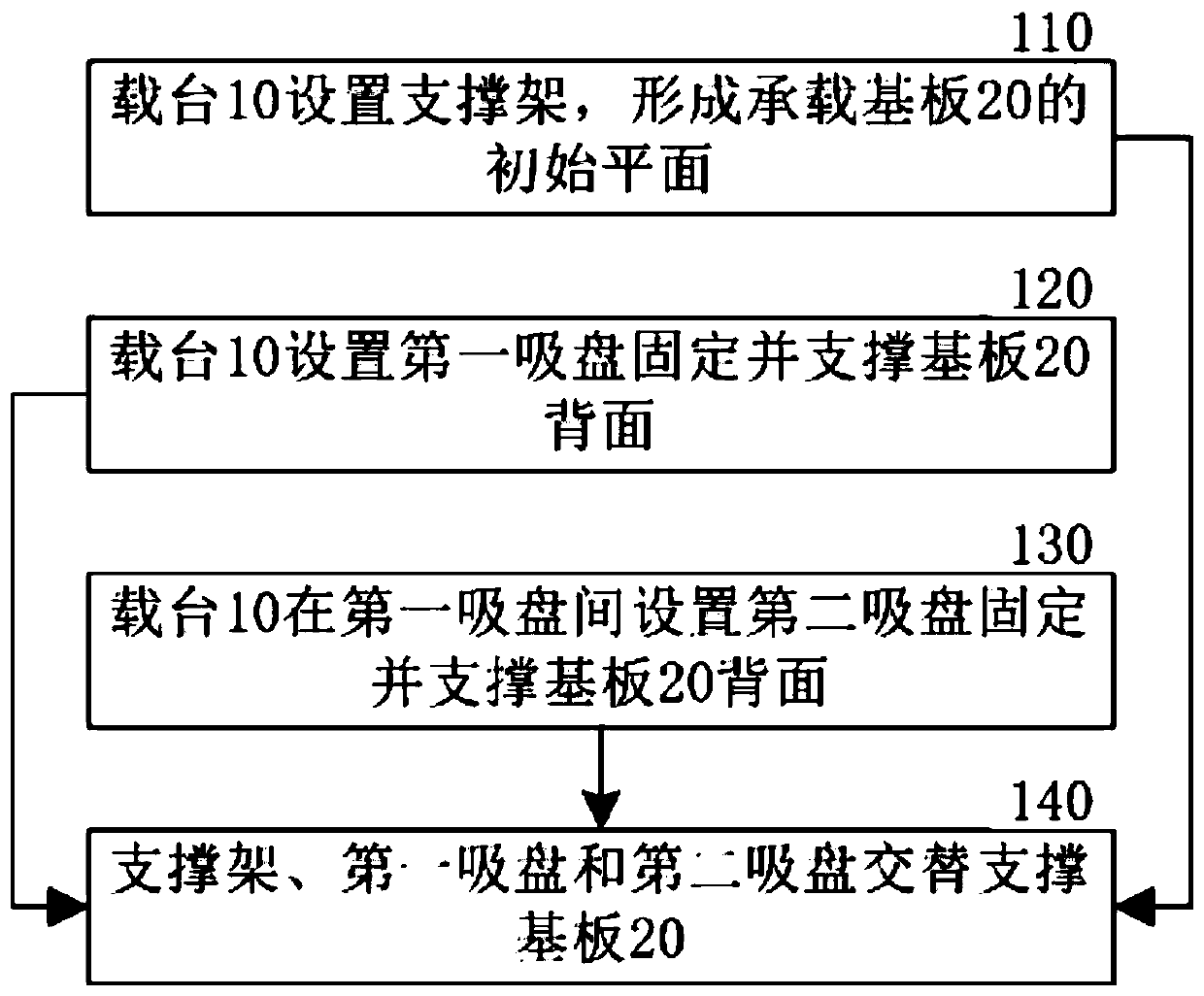

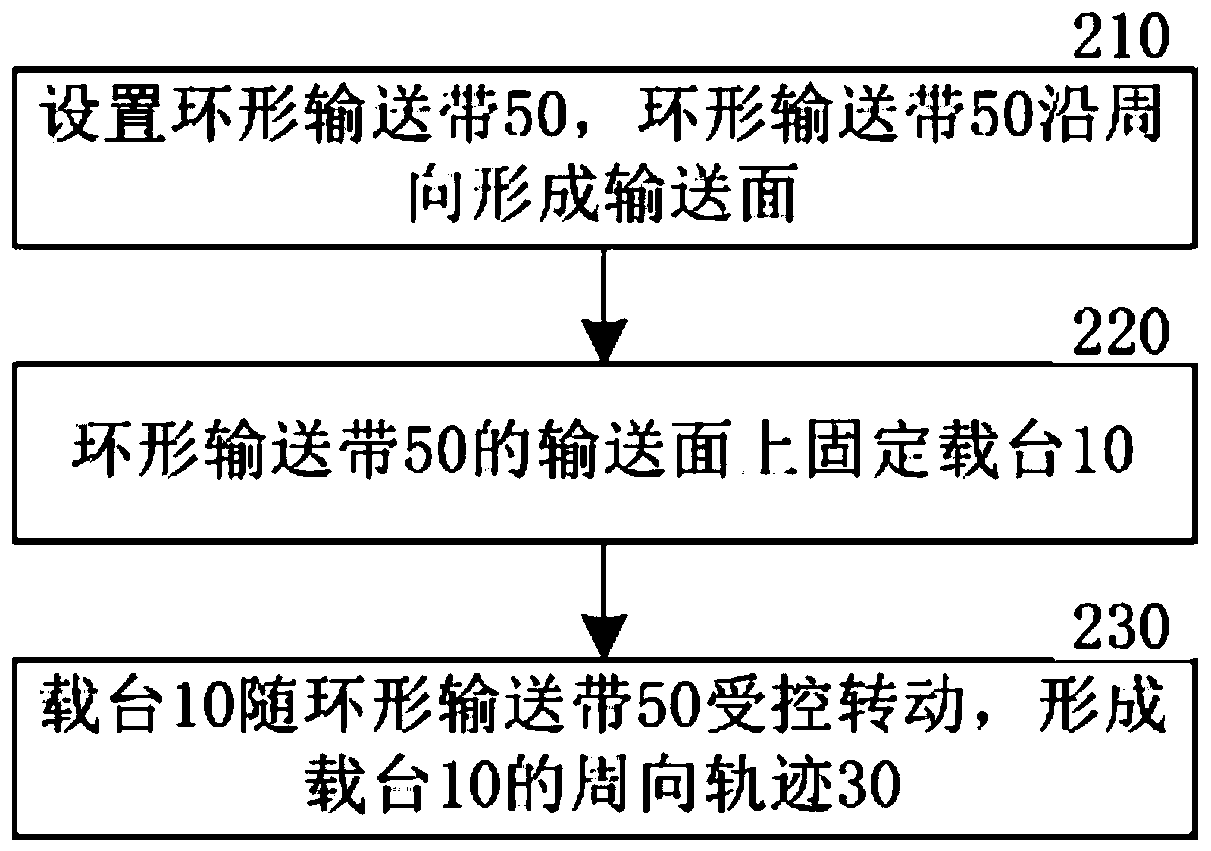

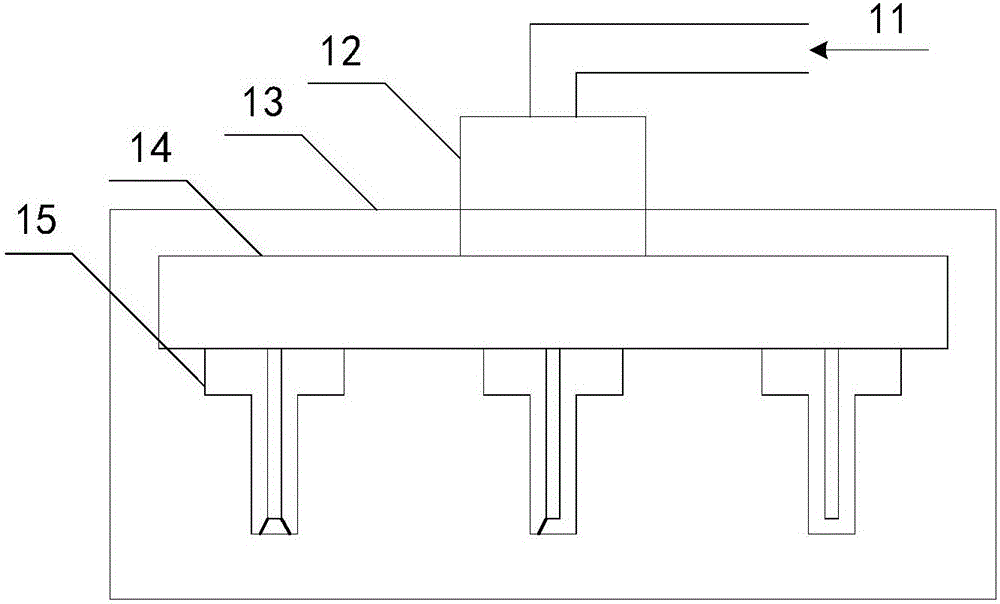

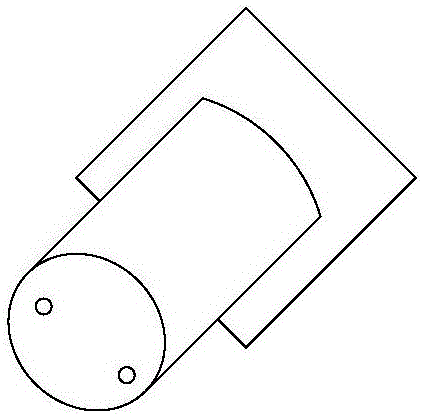

ActiveCN107170667AChange spray directionControl etch rateSolid-state devicesSemiconductor/solid-state device manufacturingEtching rateConveyor belt

The invention discloses a substrate wet process technological method, and aims to solve the technical problem of potential damage in the substrate processing process in the existing wet etching process. The technological method comprises the steps of setting a bearing platform and fixing a substrate through the bearing platform; moving the bearing platform along a circumferential track to convey the substrate; setting processing equipment along the outer side of the circumferential track; and in the substrate conveying process, adjusting the orientation and / or height of the substrate by the bearing platform to be matched with the processing equipment. The moving technological beat of the bearing platform along the circumferential track is controlled by an annular conveyor belt, so that consumed resource, manpower, time and other maintenance cost in replacing a huge number of rolling wheels periodically can be saved; the etching process and cleaning technological method are further improved; the jetting direction of the medicinal liquid and net water flow is changed; etching rate and medicinal liquid take-out amount are controlled effectively; and the cost is lowered while the etching quality can be effectively ensured. The invention also provides a substrate wet process technological apparatus.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

Etching solution composition for metal foil using silver as main composition

InactiveCN100347344CIncreased corrosion potentialHigh etch activityNon-linear opticsSurface treatment compositionsAcetic acidMetal foil

Owner:KANTO CHEM CO INC

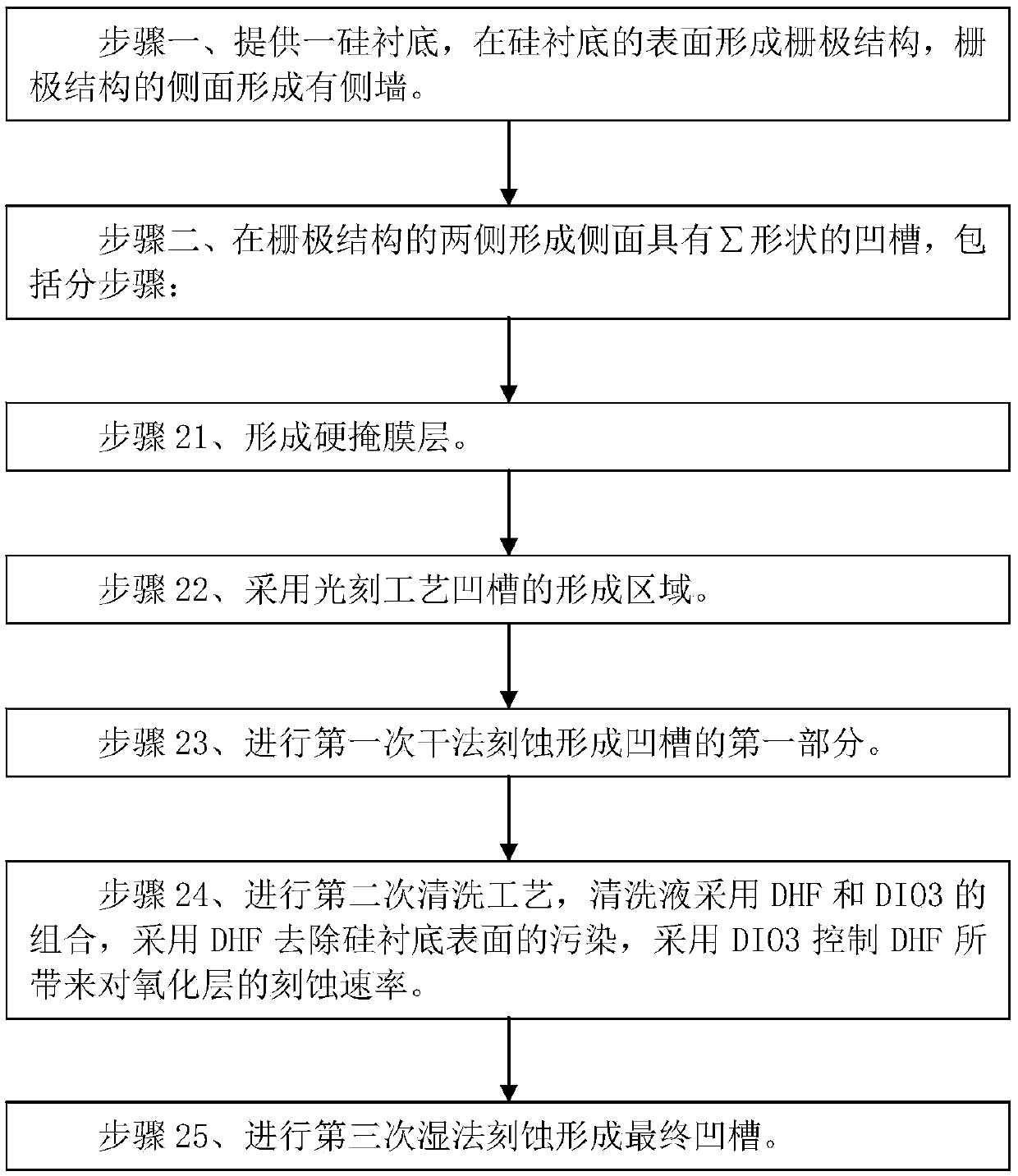

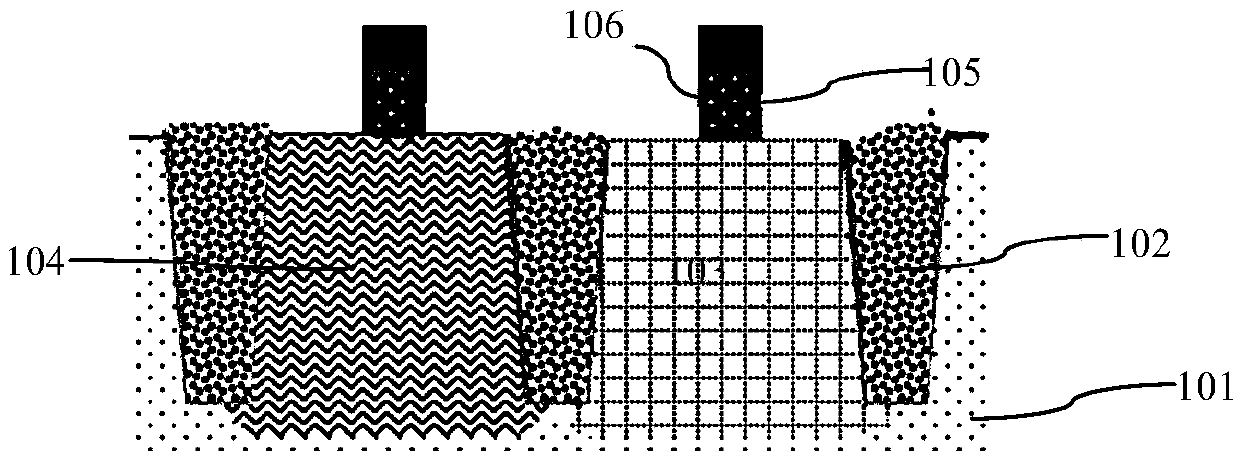

Method for manufacturing MOS transistor with germanium silicon source and drain

ActiveCN109545658AControl etch rateAvoid lossSemiconductor/solid-state device manufacturingEngineeringContamination

The invention discloses a method for manufacturing an MOS transistor with a germanium silicon source and drain. The method comprises steps that S1, a silicon substrate is provided, a gate structure isformed on a surface of the silicon substrate, and a side wall is formed on a side surface of the gate structure; and S2, a groove having the meandering shape is formed on two sides of the gate structure, including sub steps of S21, a hard mask layer is formed; S22, a formation region of the groove of the photolithography process is employed; S23, first dry etching is performed to form a first portion of the groove; S24, second cleaning process is performed, the cleaning solution adopts the combination of DHF and DIO3, the DHF is employed to remove contamination on the surface of the silicon substrate, the DIO3 is employed to control the etching rate of the oxide layer brought by the DHF, and S25, third wet etching is performed to form a final groove. The method is advantaged in that control of the cleaning process after the groove is dry can be realized, and loss of an oxide layer can be reduced or avoided while the contamination on the surface of the silicon substrate can be sufficiently removed.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

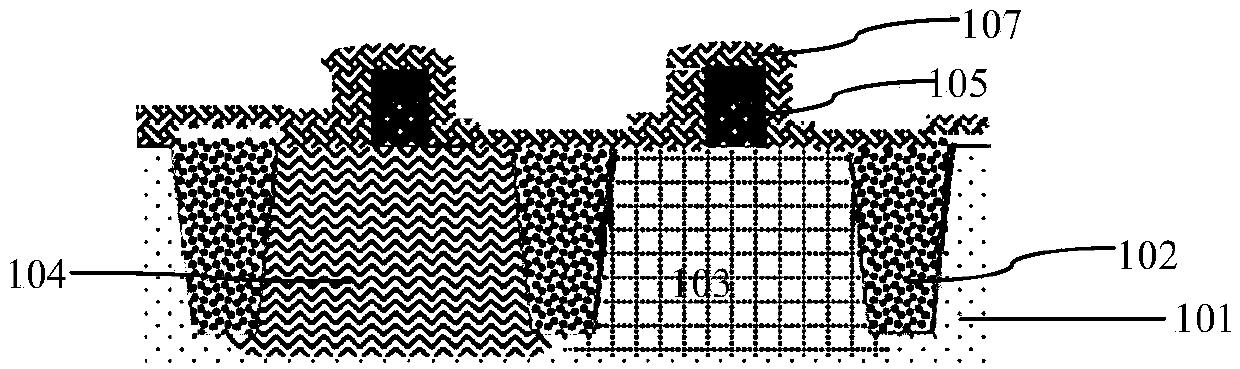

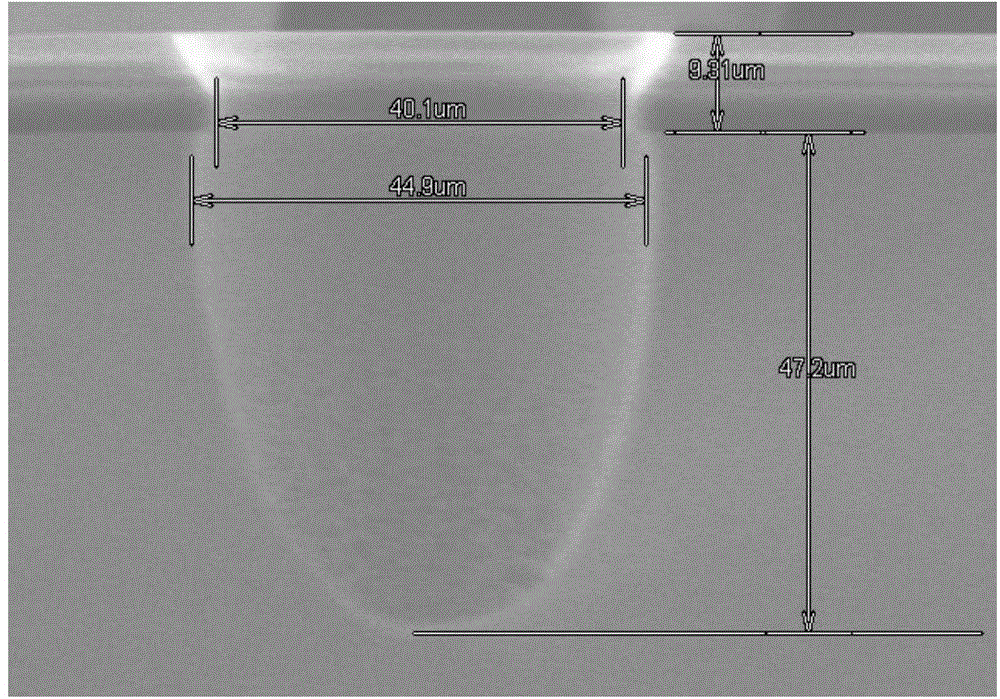

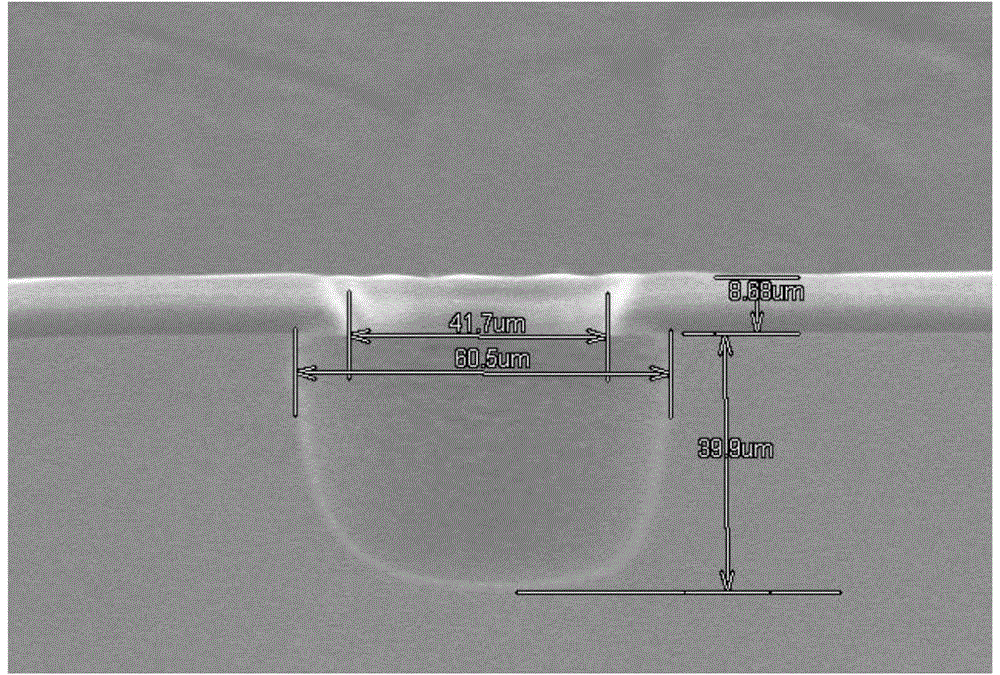

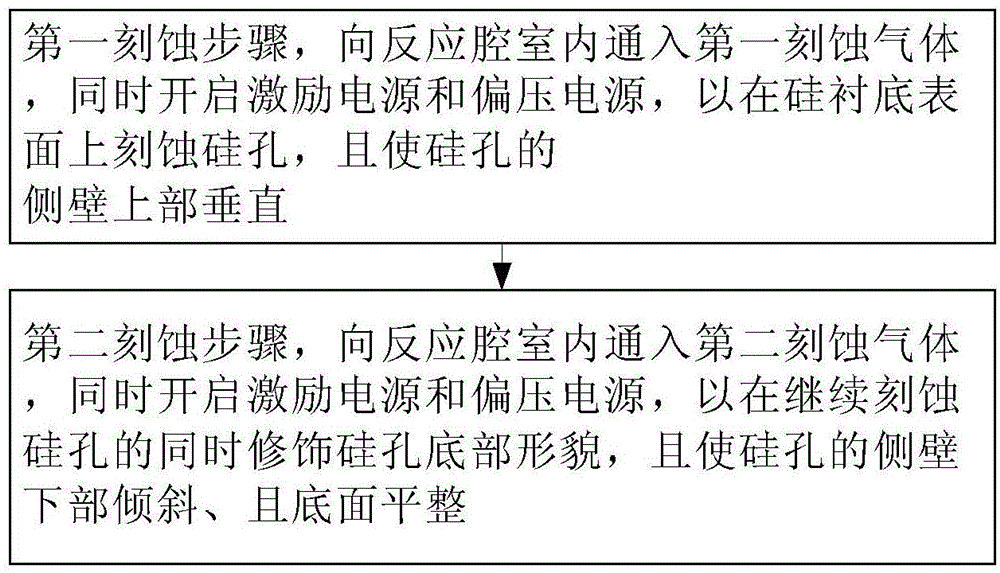

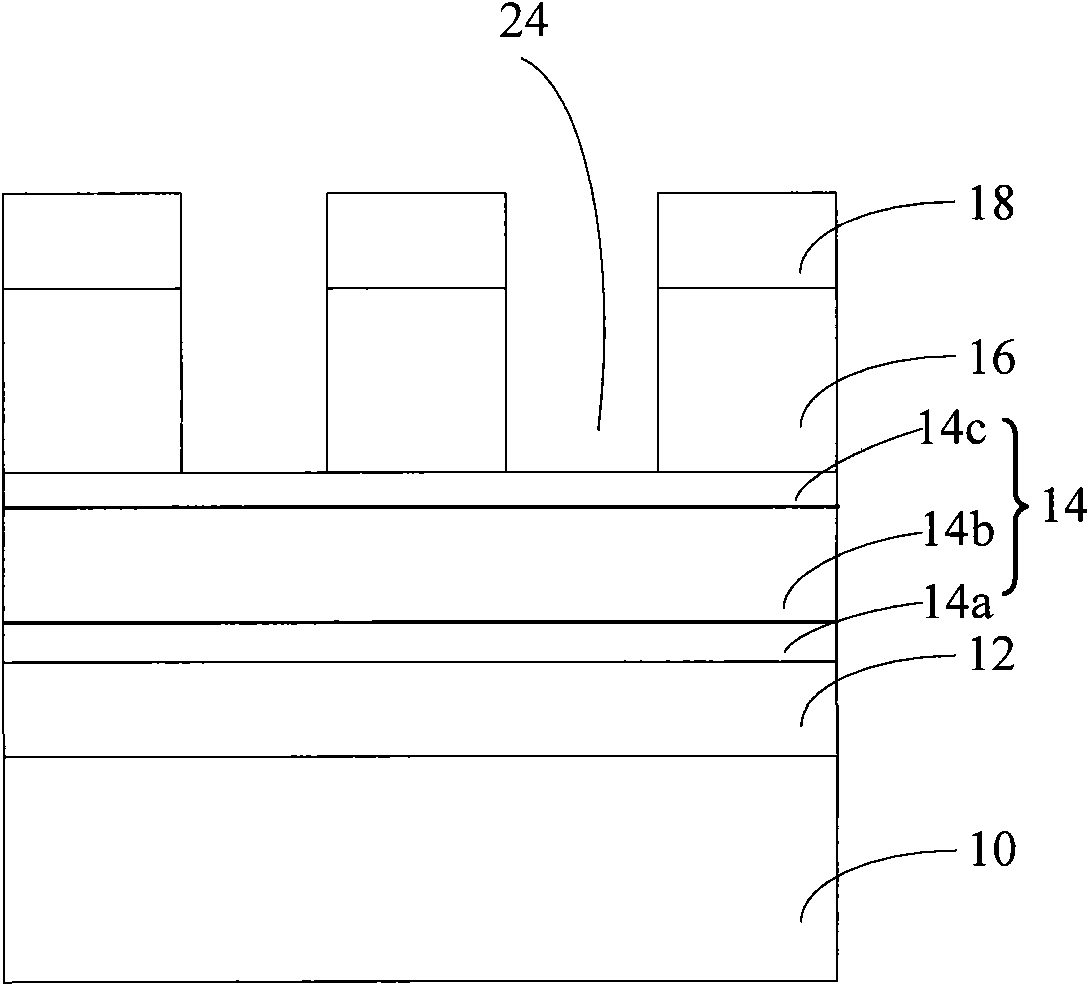

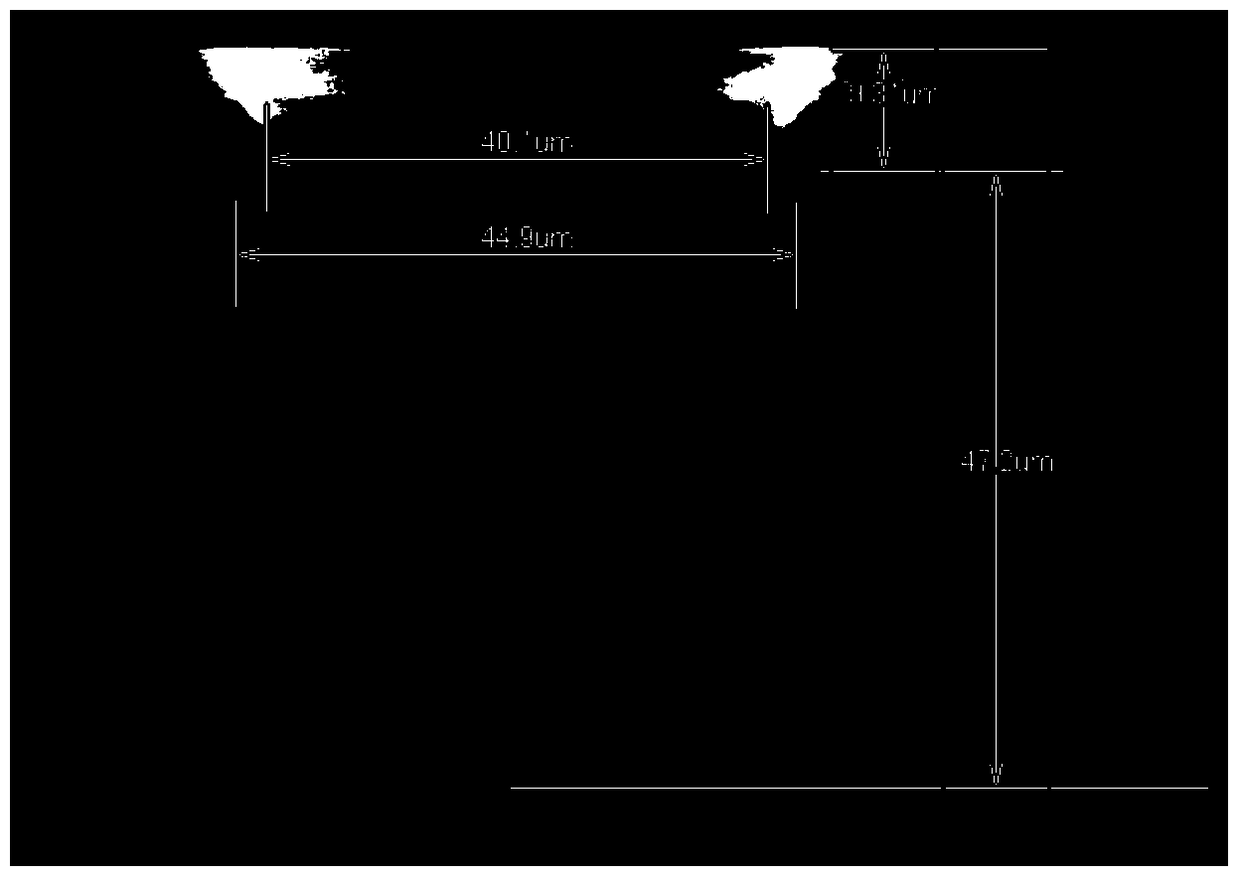

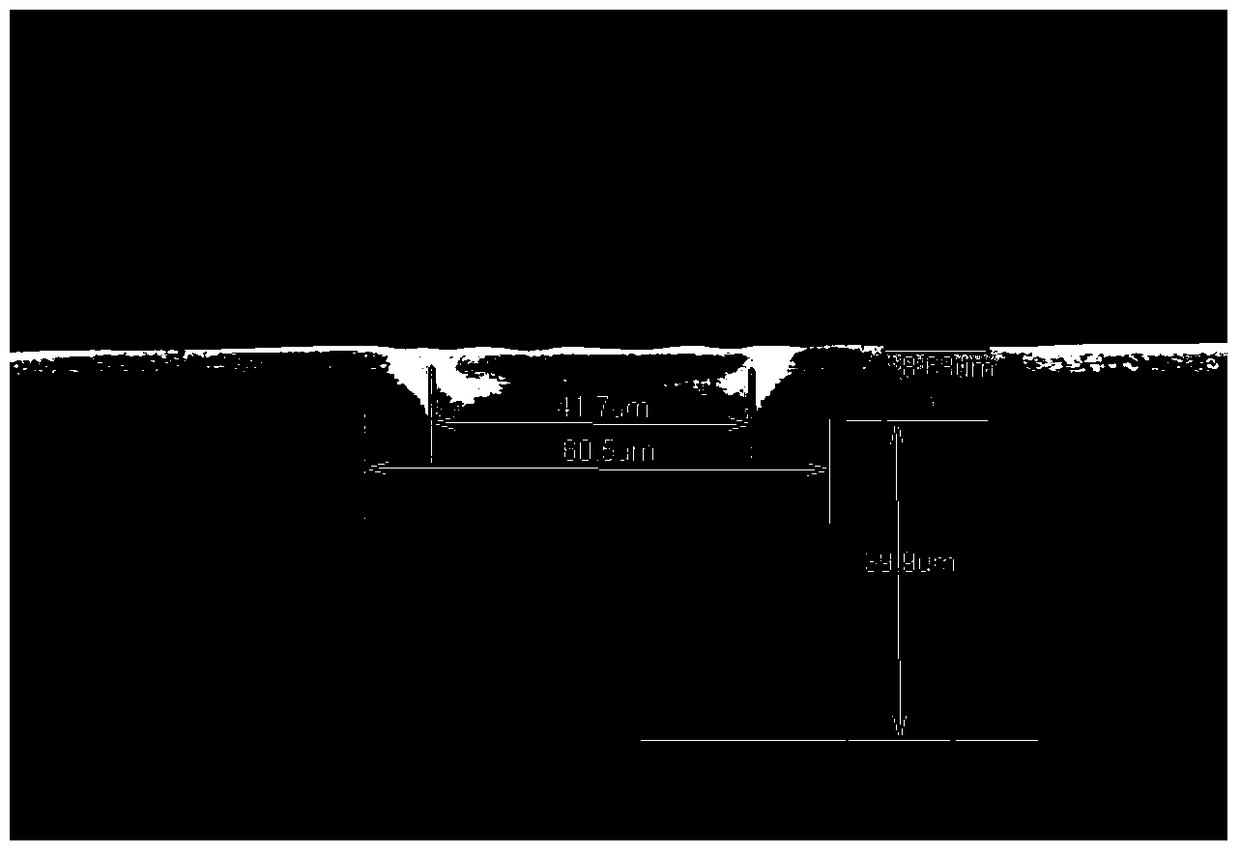

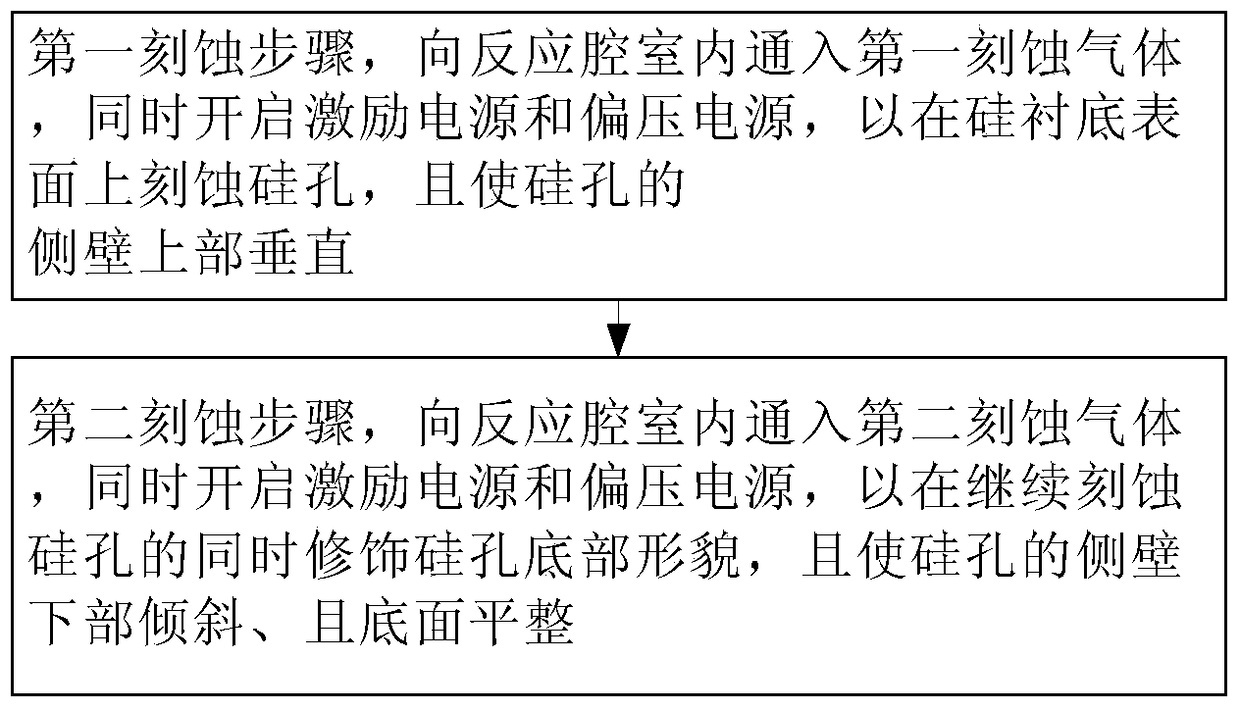

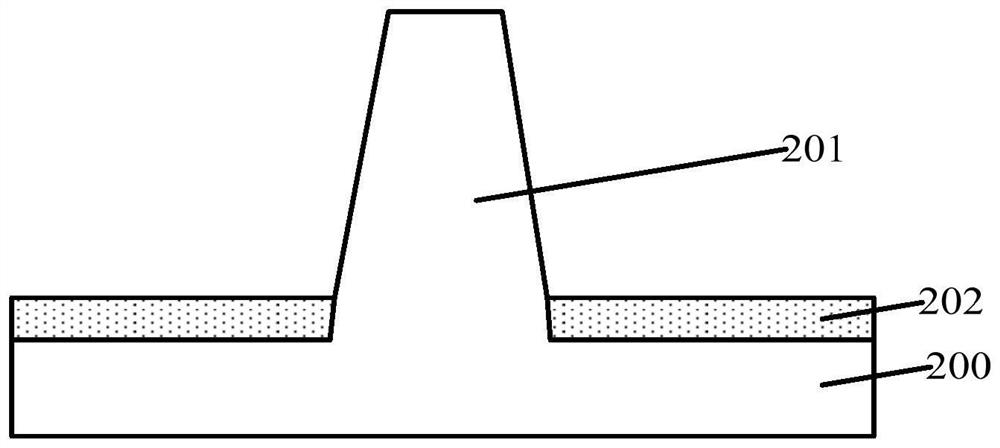

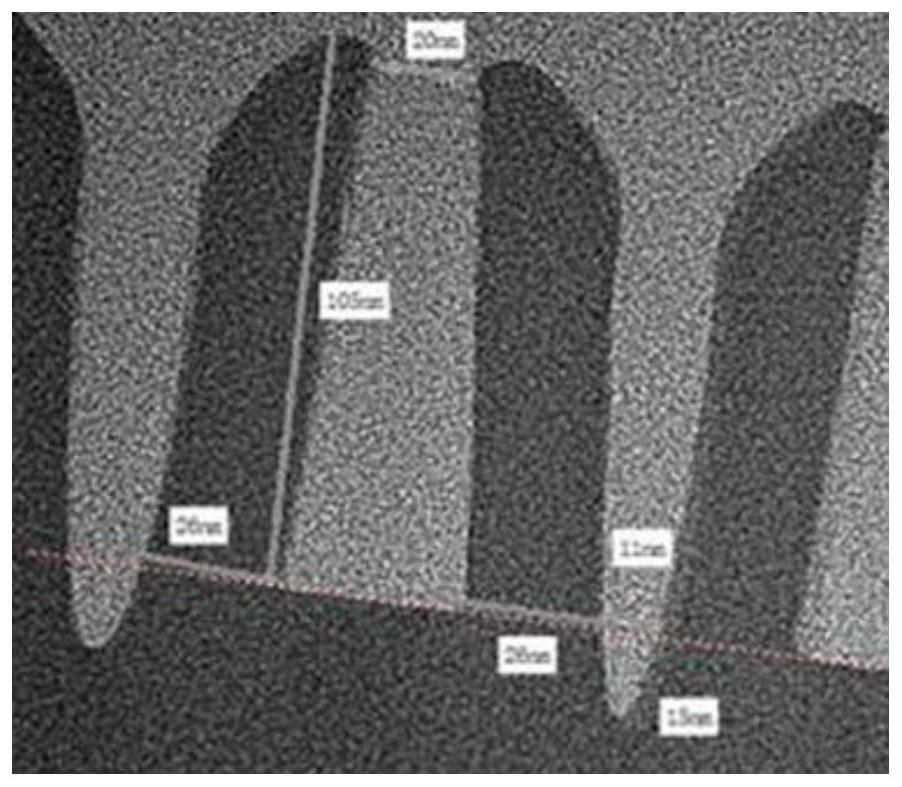

Deep silicon hole etching method

ActiveCN105720003AAdd depthGuaranteed to be verticalSemiconductor/solid-state device manufacturingEtchingMixed gas

The invention provides a deep silicon hole etching method, comprising a first etching step of inletting a first etching gas into a reaction chamber, and meanwhile switching on an excitation power supply and a bias power supply so as to etch a silicon hole in a silicon substrate, the first etching gas including a mixed gas of SF6 and O2, the gas flows of which are set to enable a vertical upper portion for the side wall of the silicon wall; and a second etching step of inletting a second etching gas into the reaction chamber, and meanwhile switching on the excitation power supply and the bias power supply so as to modify the morphology of the bottom of the silicon hole while continuing the etching of the silicon hole, the second etching gas including a mixed gas of SF6, C4F8, He and O2, the gas flows of which are set to enable the bottom width of the side wall of the silicon wall to shrink and the bottom of the silicon hole to be smooth. The invention can be used for obtaining a deep silicon hole of which the upper portion of the side wall is vertical, the bottom width of the side wall shrinks and the bottom is flat and smooth.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

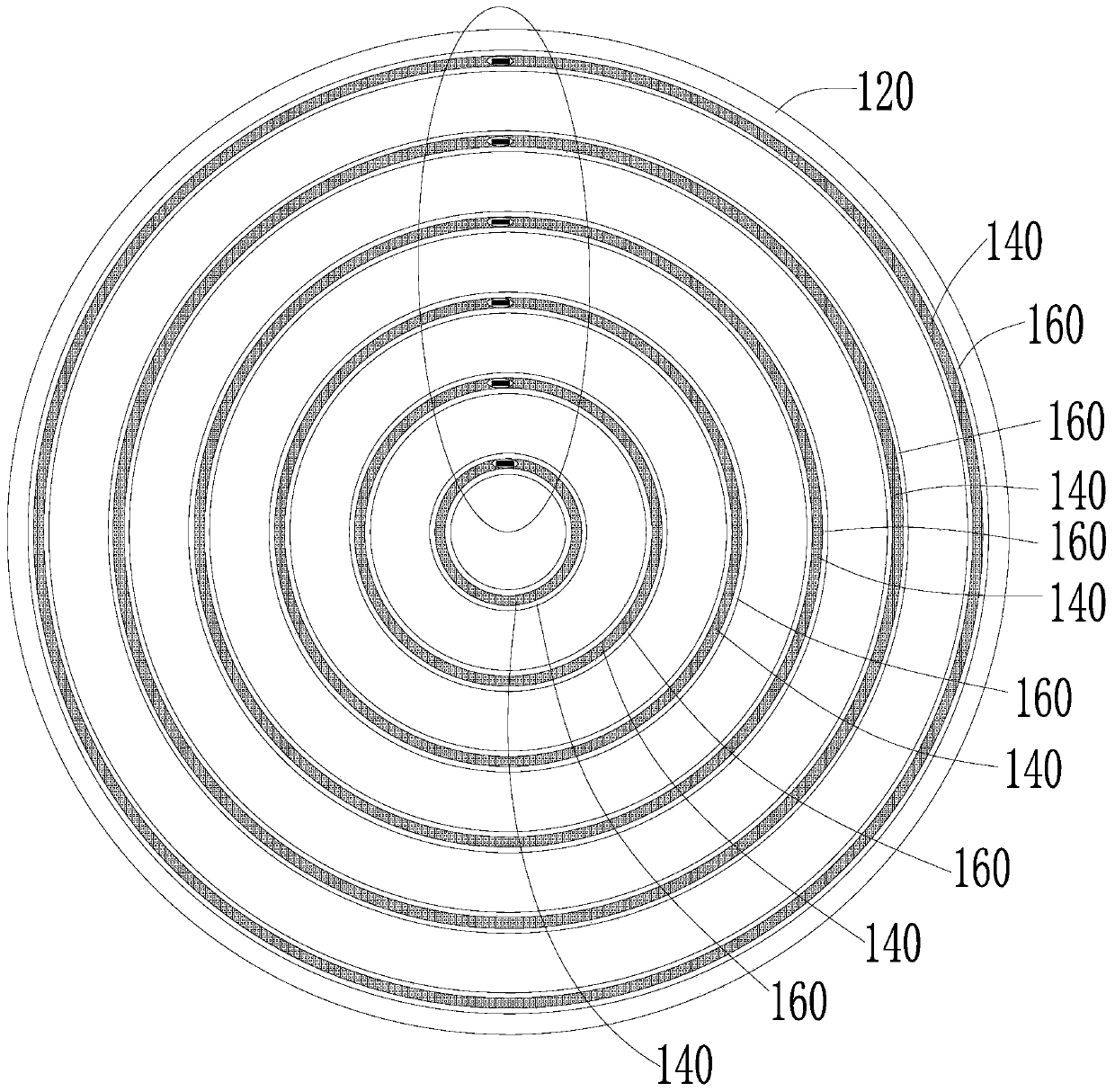

Etching device, etching system and etching method

InactiveCN110491803AImprove featuresReduce defective rateSemiconductor/solid-state device manufacturingEngineeringElectrical and Electronics engineering

The embodiment of the invention discloses an etching device. The etching device comprises an etching cavity; a bearing plate which is located in the etching cavity, wherein a wafer is placed on the bearing plate; a spray head which is located on the bearing plate, and is used for spraying etching liquid to the wafer; and a plurality of heating devices which are installed on the bearing plate and are used for heating the wafer, wherein each heating device is used for independently heating so as to change the etching rate of the etching liquid on each heating device. The embodiment of the invention further discloses an etching system and an etching method.

Owner:YANGTZE MEMORY TECH CO LTD

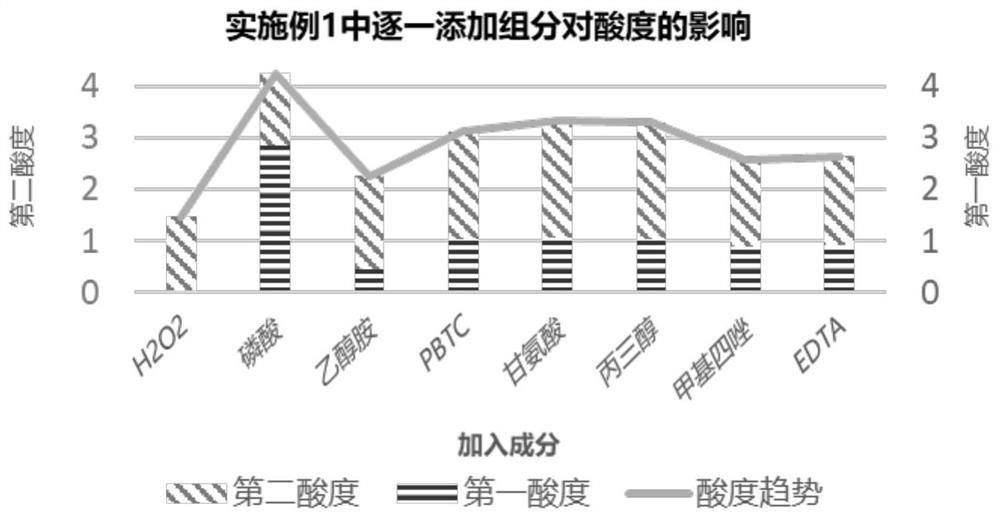

Etching solution composition and preparation method thereof

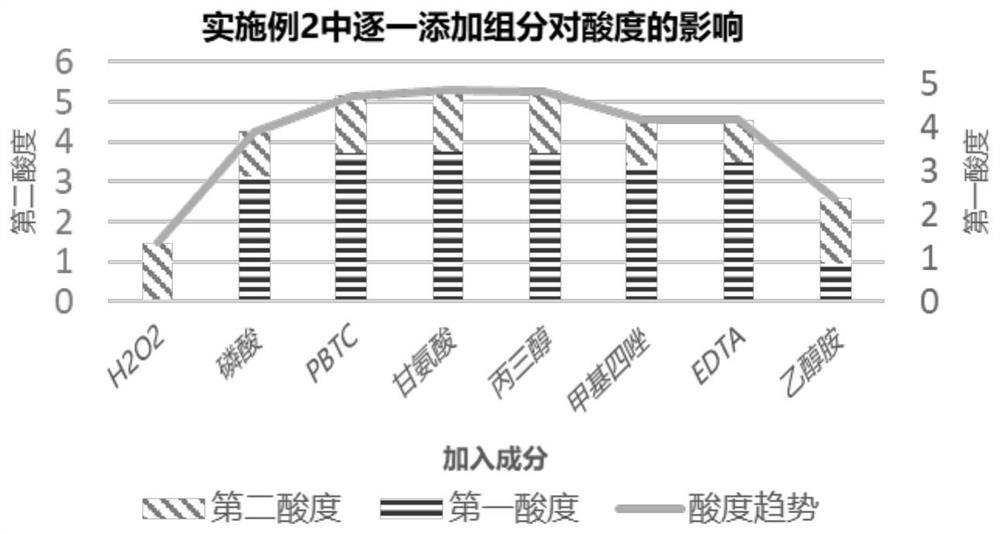

The invention relates to the technical field of etching, and provides an etching liquid composition. The cleaning agent comprises the following components in percentage by weight: 10-20% of hydrogen peroxide, 0.5-4% of inorganic acid, 1-4% of a compound with both amino and alcohol groups, 1-5% of a pH regulator, 1-5% of organic acid or amino acid, 1-5% of a metal ion chelating agent, 0.1-2% of a hydrogen peroxide stabilizer and the balance of water. And has a first acidity and a second acidity. The quality guarantee period of the etching liquid composition can reach one month, etching residues are avoided, etching broken lines are not prone to being generated, copper and copper alloy films of advanced-generation panels can be effectively etched, and the etching liquid composition can be used for etching transparent conductive films in panel display devices. The etching liquid composition can be prepared by two different preparation schemes, the shelf life of the obtained etching liquid composition can reach one month, but the line width loss difference of the etching liquid composition prepared by the first preparation scheme is obviously superior to that of the etching liquid composition prepared by the second preparation scheme.

Owner:SHENZHEN CAPCHEM TECH

Method for forming metal wiring groove

ActiveCN101958277ACritical Dimension ConsistencyImprove performanceSemiconductor/solid-state device manufacturingSilicon oxideCritical dimension

The invention relates to a method for forming a metal wiring groove, which comprises the following steps: providing a semiconductor substrate; sequentially forming an interlayer medium layer, a dielectric layer, a bottom antireflection layer, a low-temperature silicon oxide layer and a patterning photoresist layer on the semiconductor substrate; taking the patterning photoresist layer as a mask, and etching the low-temperature silicon oxide layer to expose the bottom antireflection layer to form a first groove pattern; taking the patterning photoresist layer and the low-temperature silicon oxide layer as masks, and etching the bottom antireflection layer along the first groove pattern to expose the dielectric layer to form a second groove pattern, wherein the etching gas is mixed gas of carbon dioxide and carbon monoxide; and taking the low-temperature silicon oxide layer and the antireflection layer as masks, and etching the dielectric layer along the second groove pattern to form the metal wiring groove. The invention can effectively control the critical dimension of the second groove pattern formed on the bottom antireflection layer to achieve a predetermined value, so that thecritical dimension of the sequentially formed metal wiring groove is the same as a predetermined value, and the performance of a semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Deep silicon hole etching method

ActiveCN105720003BAdd depthGuaranteed to be verticalSemiconductor/solid-state device manufacturingEtchingMixed gas

The invention provides a deep silicon hole etching method, comprising a first etching step of inletting a first etching gas into a reaction chamber, and meanwhile switching on an excitation power supply and a bias power supply so as to etch a silicon hole in a silicon substrate, the first etching gas including a mixed gas of SF6 and O2, the gas flows of which are set to enable a vertical upper portion for the side wall of the silicon wall; and a second etching step of inletting a second etching gas into the reaction chamber, and meanwhile switching on the excitation power supply and the bias power supply so as to modify the morphology of the bottom of the silicon hole while continuing the etching of the silicon hole, the second etching gas including a mixed gas of SF6, C4F8, He and O2, the gas flows of which are set to enable the bottom width of the side wall of the silicon wall to shrink and the bottom of the silicon hole to be smooth. The invention can be used for obtaining a deep silicon hole of which the upper portion of the side wall is vertical, the bottom width of the side wall shrinks and the bottom is flat and smooth.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

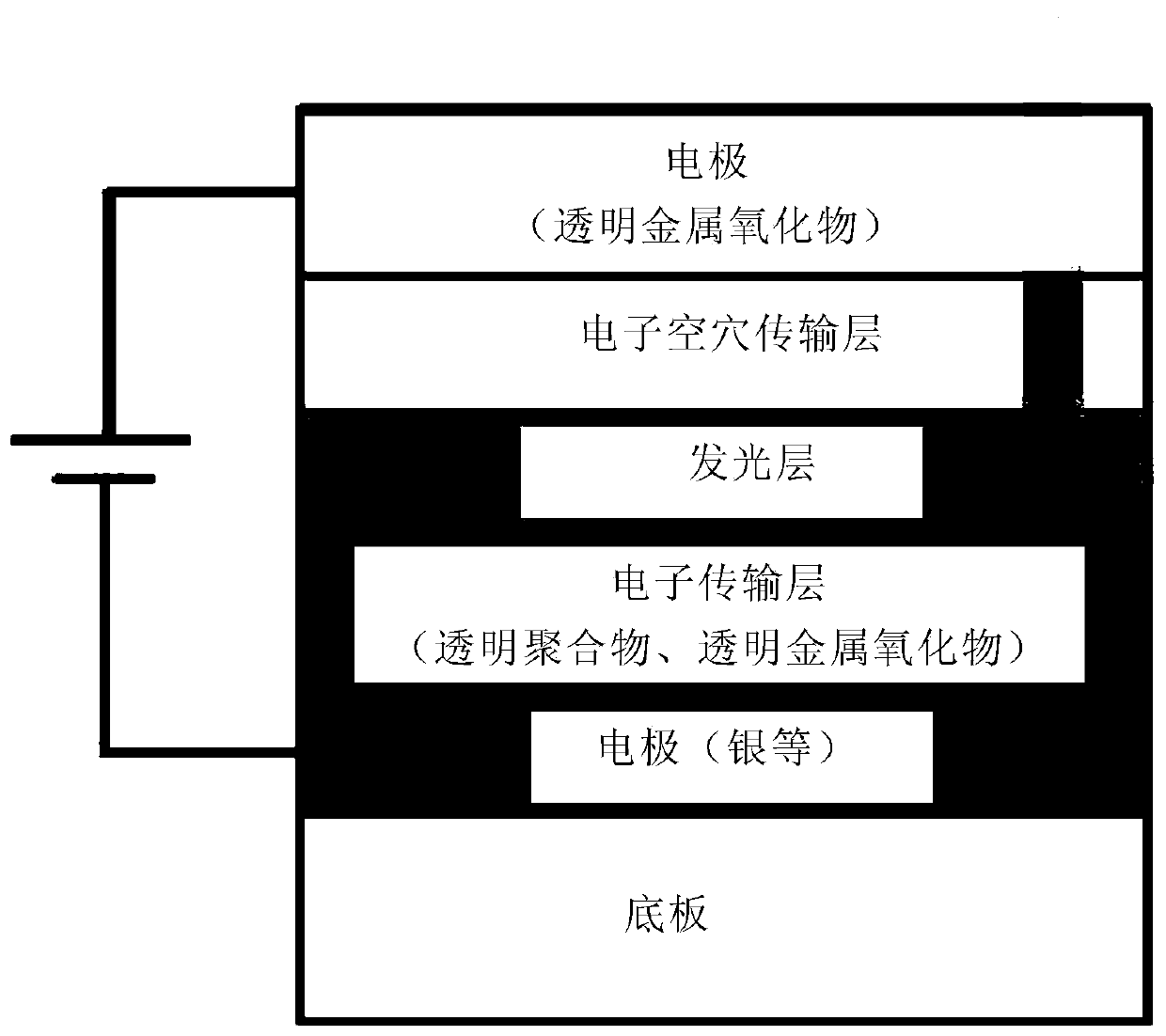

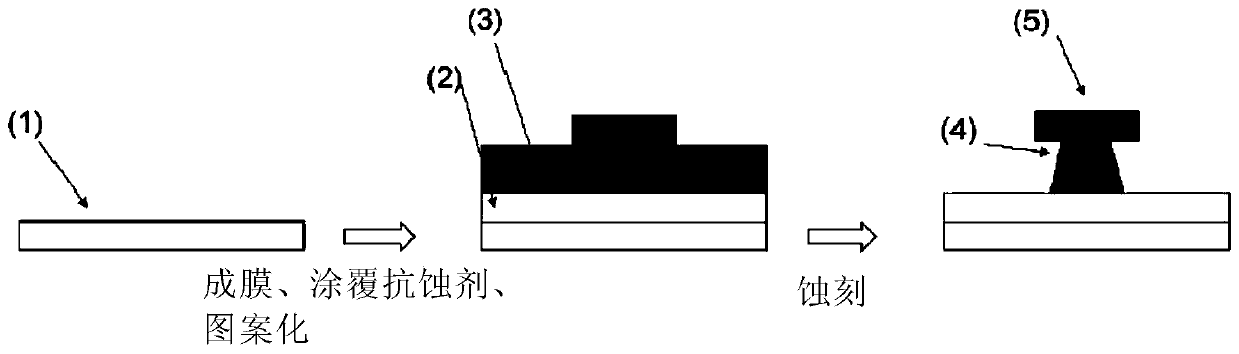

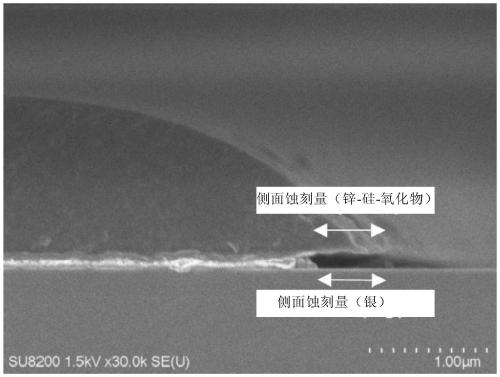

Etchant composition for simultaneous etching of multilayer film having zinc oxide and silver

ActiveCN111378453AControl etch rateReduce side etch differenceSemiconductor/solid-state device manufacturingPhotovoltaic energy generationEtchingPhysical chemistry

The object of the present invention is to provide an etching solution that can perform etching simply and economically while reducing the side etching difference of a laminated film adjacent to a zincoxide or a transparent metal oxide film containing zinc oxide and a silver or silver alloy film. combination. The present invention relates to an etching solution composition for simultaneously etching the above two films of a laminated film substrate where a zinc oxide or a transparent metal oxide film containing zinc oxide and a silver or silver alloy film are adjacent to each other, which includes (A) peroxide Hydrogen, (B) silver complexing agent, and (C) water.

Owner:KANTO CHEM CO INC

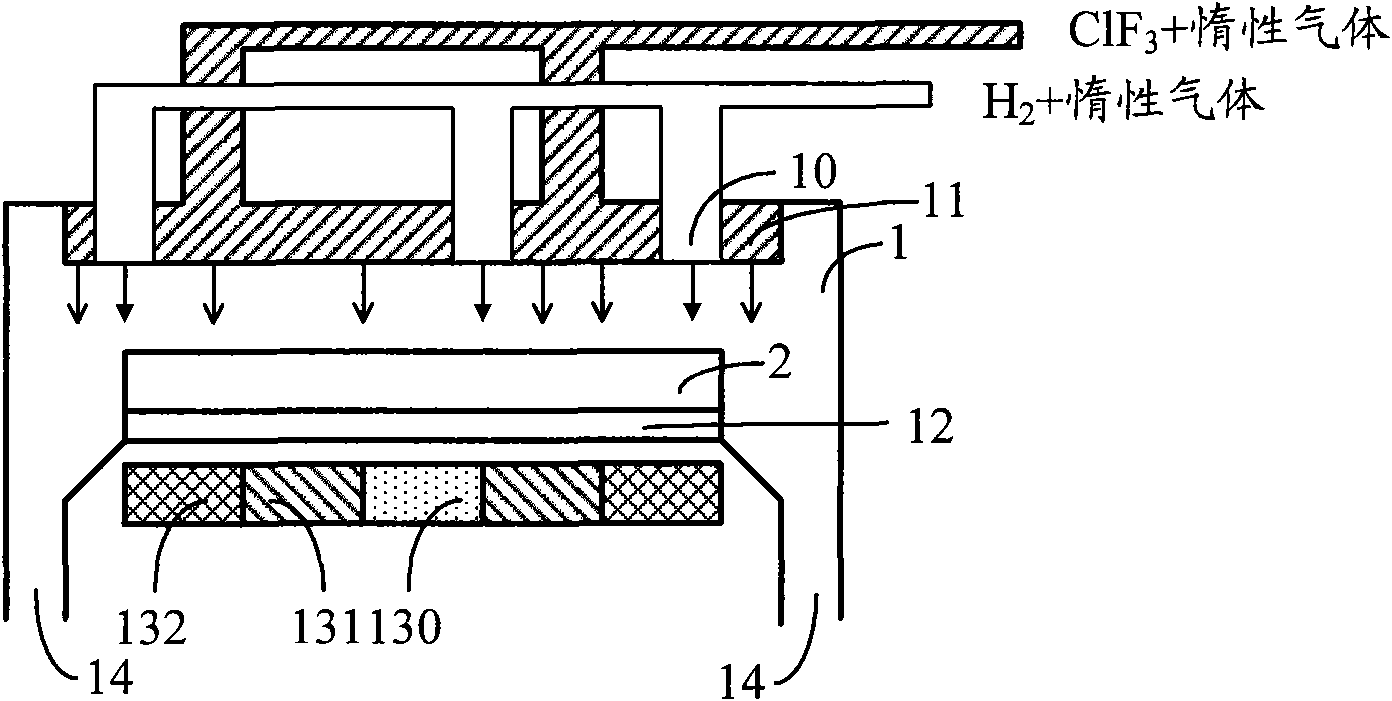

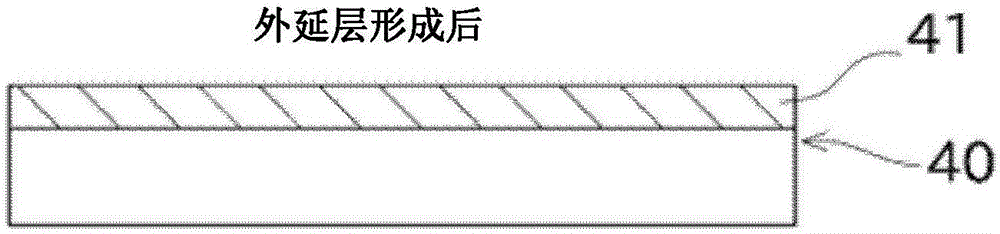

Surface treatment method of sic substrate, method of manufacturing sic substrate and semiconductor

ActiveCN106062929BControl etch ratePolycrystalline material growthAfter-treatment detailsThermal treatmentSic substrate

When etching the SiC substrate ( 40 ) by heating the machined SiC substrate ( 40 ) in a SiC atmosphere, the etching rate is controlled by adjusting the pressure of the inert gas around the SiC substrate ( 40 ). Thereby, when latent flaws and the like exist on the SiC substrate (40), the latent flaws and the like can be removed. Therefore, even if epitaxial growth, heat treatment, etc. are performed, the surface of the SiC substrate (40) will not be rough, so a high-quality SiC substrate can be manufactured.

Owner:TOYOTA TSUSHO

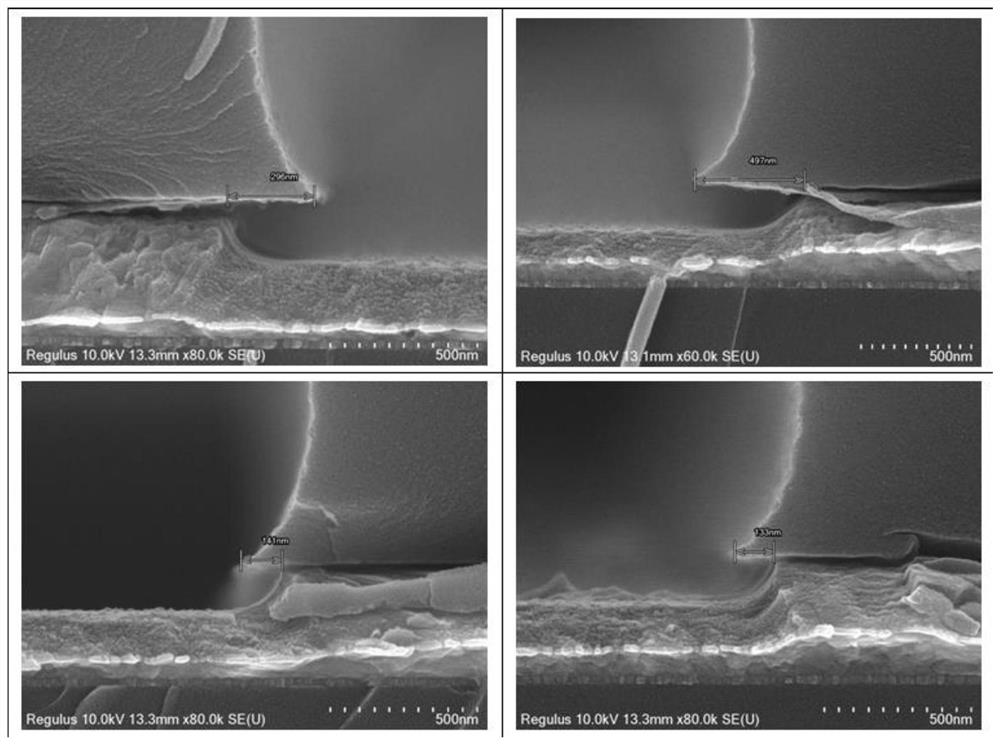

Fabrication method of nanowire structure

ActiveCN107342312BAvoid damageImprove uniformityNanotechnologySemiconductor devicesNanowireSemiconductor materials

The invention provides a method for manufacturing a nanowire structure. The method comprises the following steps: step S1, providing a substrate, and forming a first semiconductor material and a mask part, which are away from the substrate, on the substrate; step S2, performing surface treatment on the first semiconductor material, so that the surface part of the first semiconductor material forms a first surface layer; step S3, etching to remove the first surface layer, wherein the ratio of the removal rate of the first surface layer to the removal rate of the substrate is greater than 10; and repeating step S2 and step S3, until a first semiconductor material forms a nanowire. By adoption of the method, self-limiting etching is realized, and relatively small damage to the substrate in the etching process is guaranteed; and then the surface treatment is performed, and the etching is performed until the nanowire structure with a predetermined size is formed, and mover the repeatability and the uniformity of the formed nanowire structure are good.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

Multilayer dielectric etching method

ActiveCN103050396BIncrease etch rateAdjust densitySemiconductor/solid-state device manufacturingHydrogenNitrogen oxide

The invention relates to the technical field of a semiconductor, and discloses a multilayered medium etching method. The method comprises the following steps of: providing a semiconductor substrate, wherein the surface of the semiconductor substrate is sequentially coated with the multilayered medium and a graphic photoresist layer; and ionizing the etching gas which is the mixed gas such as fluorocarbon gas, fluorinated carbureted hydrogen gas and nitrogen oxide gas by taking the graphic photoresist layer as a mask, and etching the multilayered medium by the etching gas until the multilayered medium is exposed to the surface of the semiconductor substrate. The method takes the fluorocarbon gas and the fluorinated carbureted hydrogen gas with high C / F ratio as the main etching gas; and the nitrogen oxide gas in a certain flow is added, so that a purpose of etching the multilayered medium formed by different materials through one-step plasma etching primary is achieved, and the etching is not performed by many steps of layering the materials. The photoresist layer as the mask has a low etching rate.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

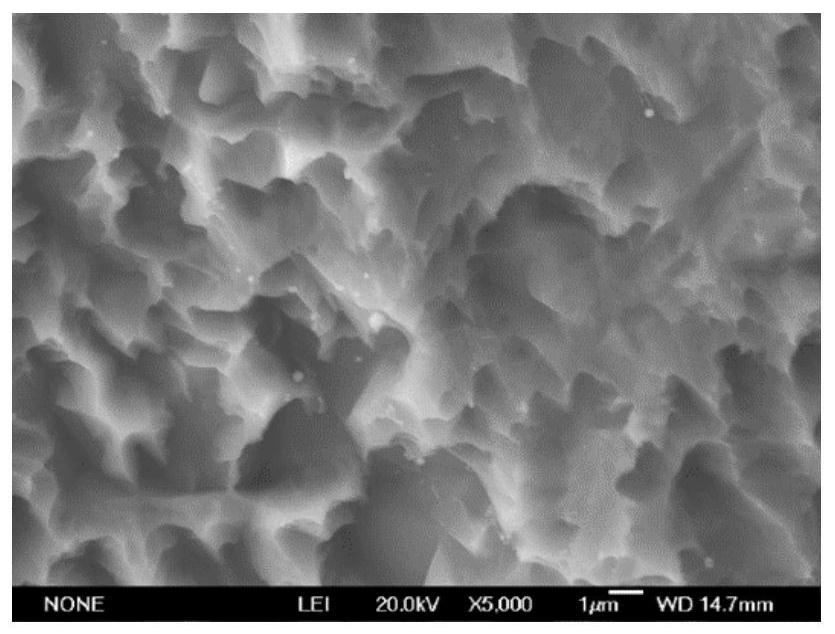

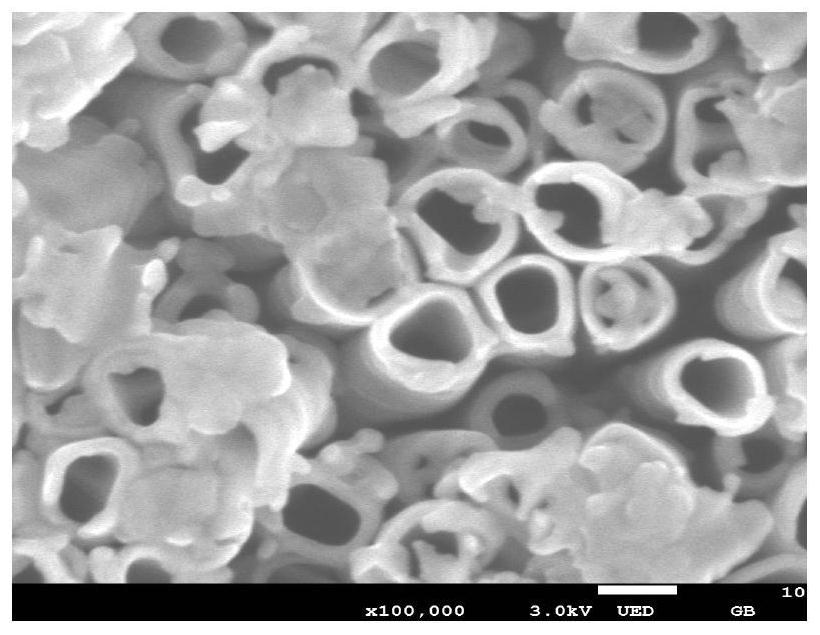

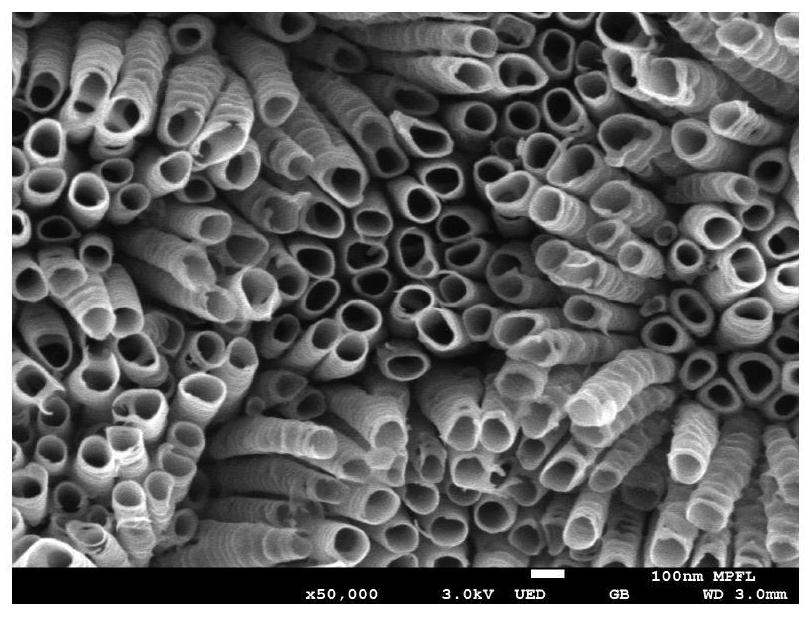

Pretreatment method of titanium substrate for electrode

The invention discloses a pretreatment method of a titanium substrate for an electrode. The method comprises the steps: boiling the titanium substrate in an acid or alkali solution for 10-60 minutes, cleaning the titanium substrate, carrying out anodic oxidation etching on the titanium substrate, and cleaning the titanium substrate after etching to obtain a titanium substrate of which the surface is provided with a regular titanium nanotube array structure. According to the method, after the titanium substrate is pretreated, the surface roughness of the titanium substrate is greatly improved, and a surface catalyst even can be diffused into a nanotube, so that the binding force between the surface of the titanium substrate and a catalyst layer is greatly improved, and the service life of the electrode is further prolonged.

Owner:陕西榆能集团能源化工研究院有限公司 +1

Substrate wet process process method and substrate wet process process device

ActiveCN107170667BChange spray directionControl etch rateSolid-state devicesSemiconductor/solid-state device manufacturingWater flowProcess engineering

The invention discloses a substrate wet process technological method, and aims to solve the technical problem of potential damage in the substrate processing process in the existing wet etching process. The technological method comprises the steps of setting a bearing platform and fixing a substrate through the bearing platform; moving the bearing platform along a circumferential track to convey the substrate; setting processing equipment along the outer side of the circumferential track; and in the substrate conveying process, adjusting the orientation and / or height of the substrate by the bearing platform to be matched with the processing equipment. The moving technological beat of the bearing platform along the circumferential track is controlled by an annular conveyor belt, so that consumed resource, manpower, time and other maintenance cost in replacing a huge number of rolling wheels periodically can be saved; the etching process and cleaning technological method are further improved; the jetting direction of the medicinal liquid and net water flow is changed; etching rate and medicinal liquid take-out amount are controlled effectively; and the cost is lowered while the etching quality can be effectively ensured. The invention also provides a substrate wet process technological apparatus.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

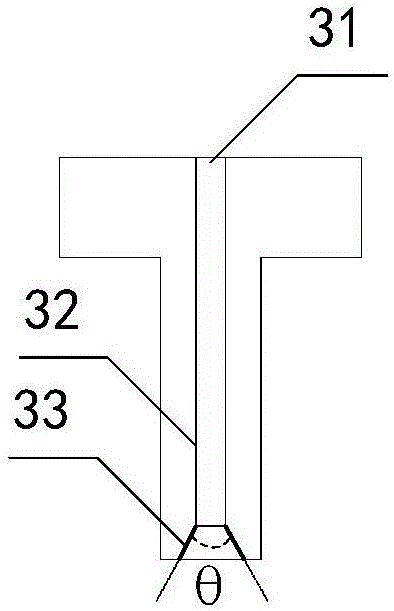

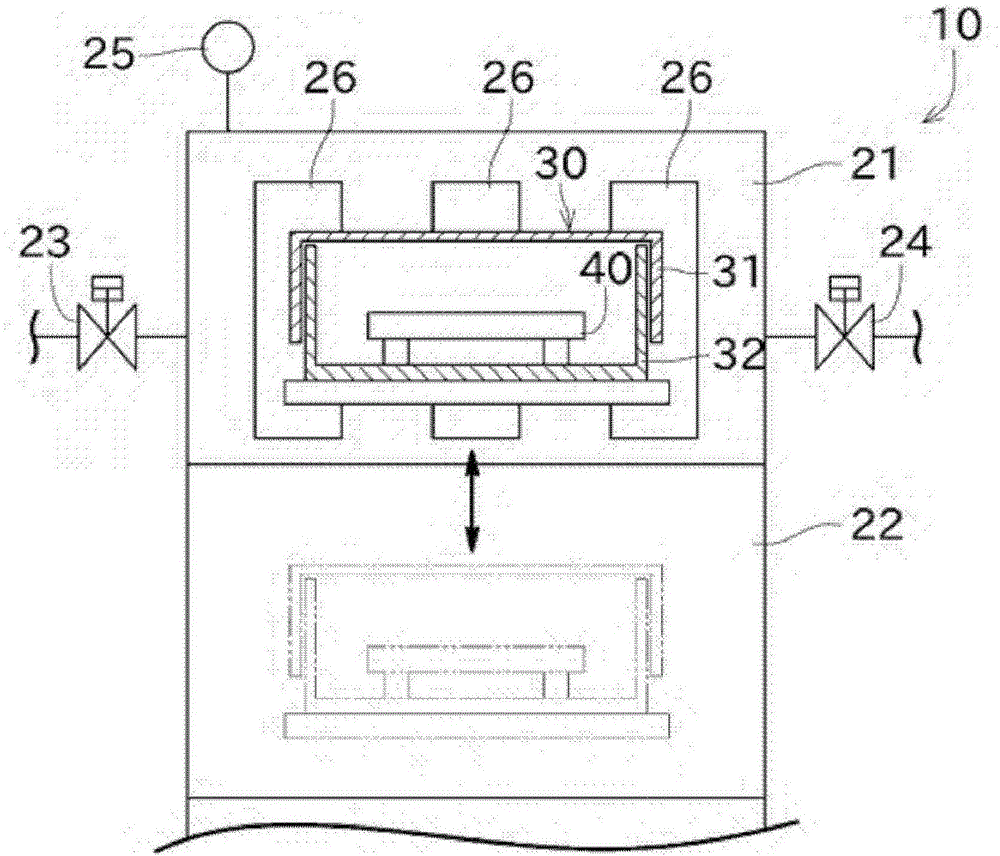

Dry etching reaction device and gas nozzle for dry etching reaction

InactiveCN106711066AControl UniformityImprove uniformityElectric discharge tubesSemiconductor/solid-state device manufacturingProduct gasDry etching

The invention discloses a dry etching reaction device and a gas nozzle for dry etching reaction. The dry etching reaction device comprises a reaction cavity; a gas pipeline arranged in the reaction cavity; and the gas nozzle, which comprises a gas inlet, a gas channel and at least two gas outlets, which are communicated in sequence. The gas inlet is communicated with the gas channel; and the gas output directions of the at least two gas outlets are not vertical with each other. Through the mode above, the dry etching reaction device and the gas nozzle for dry etching reaction can control uniformity of reaction gas in the reaction cavity, and improve uniformity of gas ions in the etching process to enable dry etching to be more uniform and to achieve an etching rate control purpose.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Additives for Porous Pyramid Structure Prepared by Secondary Texturing of Single Crystal Silicon Wafer and Its Application

ActiveCN111254497BReduce surface tensionPromote infiltrationPolycrystalline material growthAfter-treatment detailsCrystallographyInorganic salts

The invention discloses an additive for preparing a porous pyramid structure by secondary texturing of a single crystal silicon wafer. The mass percent content of each component is: sodium polystyrene sulfonate 0.1% to 10%, polyethylene glycol 2% ~20%, fluorocarbon surfactant 1%~5%, inorganic salt 20%~30%, and the balance is water. Adding the additive of the present invention to the texturizing liquid for the secondary texturing of the monocrystalline silicon wafer can form a porous pyramid structure on the surface of the monocrystalline silicon wafer. Moreover, the method for preparing the porous pyramid structure of the single crystal silicon chip of the present invention has lower cost and simpler process.

Owner:CHANGZHOU SHICHUANG ENERGY CO LTD

Etching device and method

InactiveCN101924011APosition controlControl etch rateSemiconductor/solid-state device manufacturingVacuum pumpingElectrical polarity

The invention discloses an etching device and an etching method. The etching device comprises a chamber with a plurality of gas inlets, wherein a wafer tray is arranged in the chamber for carrying a wafer; the chamber also comprises a plurality of etching control units which are positioned below the wafer tray; the etching control units are used for controlling voltage of corresponding to-be-etched positions of the wafer; and the polarity of the voltage is reverse to that of a charged etching gas introduced into the chamber through the gas inlets. The etching device is also provided with a plurality of gas outlets which are connected with a vacuum-pumping system through valves for controlling pressure during etching. The gas inlets are also connected with an inert gas source for providing an inert gas through conduction valves. Through the etching device and the etching method, the etching rate can be controlled well and the etching uniformity is high.

Owner:SEMICON MFG INT (SHANGHAI) CORP

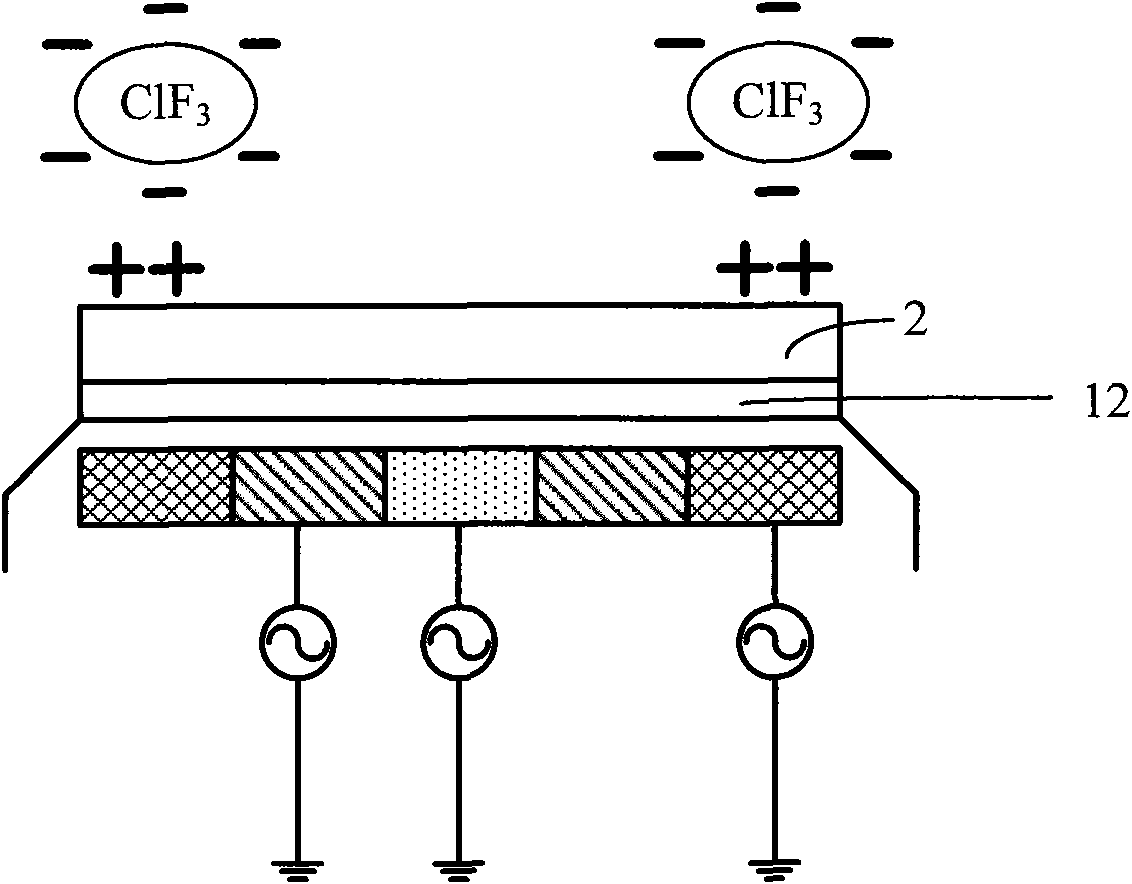

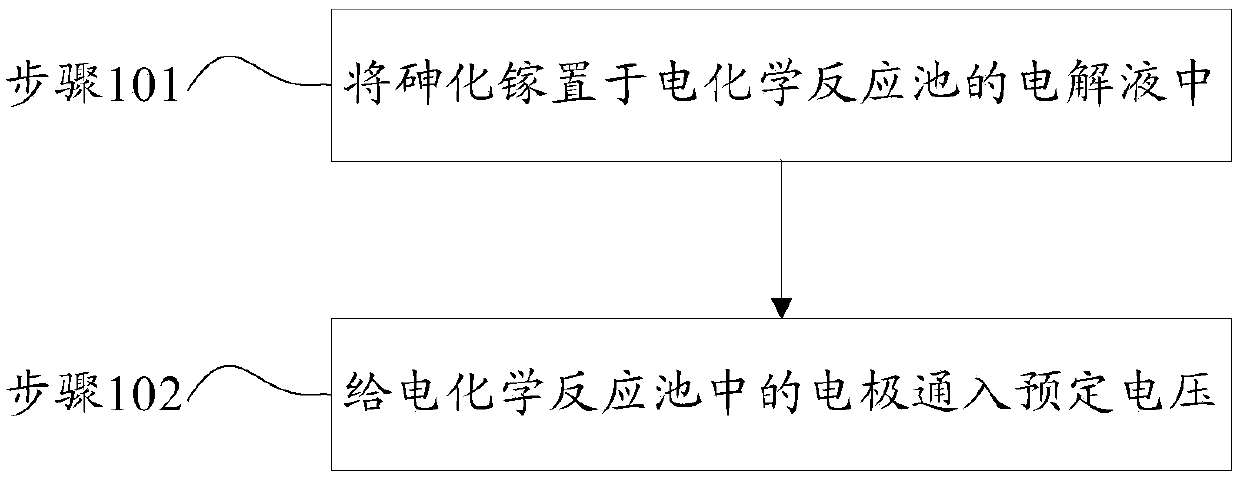

Gallium arsenide etching method

PendingCN111106004AEtching rate is easy to controlHigh precisionFinal product manufactureSemiconductor/solid-state device manufacturingElectrochemical responseBromide ions

The invention discloses a gallium arsenide etching method which comprises the steps: placing gallium arsenide in electrolyte of an electrochemical reaction tank, wherein the electrolyte comprises non-oxidizing acid, metal bromide and water; and inputting a predetermined voltage into an electrode in the electrochemical reaction tank, wherein the predetermined voltage is a voltage for keeping a predetermined etching rate when the pH value of the electrolyte and the concentration of the metal bromide are in a predetermined range. Bromide ions from the metal bromide can generate bromine gas through electrochemical reaction, and the bromine gas reacts with water to generate hypobromic acid; and gallium arsenide can react with hydrogen ions in the electrolyte after being oxidized by the hypobromic acid, and the purpose of etching the gallium arsenide in an electrochemical reaction mode is achieved. According to the gallium arsenide etching method, the etching rate of gallium arsenide can becontrolled by controlling the voltage, the etching rate is easy to control, and the control precision is high.

Owner:紫石能源有限公司

Surface treatment method for sic substrates, sic substrate, and semiconductor production method

ActiveCN106062929AControl etch ratePolycrystalline material growthAfter-treatment detailsSemiconductorMachining

When a SiC substrate (40), which has been subjected to machining, is subjected to heat treatment under a SiC atmosphere to etch the SiC substrate (40), the etching rate is controlled by adjusting the inert gas pressure around the periphery of the SiC substrate (40). As a result, in cases when latent scratches or the like are present in the SiC substrate (40), the latent scratches or the like can be removed. Accordingly, the surface of the SiC substrate (40) does not become rough, even if epitaxial growth and heat treatment are performed, and thus high-quality SiC substrates can be produced.

Owner:TOYOTA TSUSHO

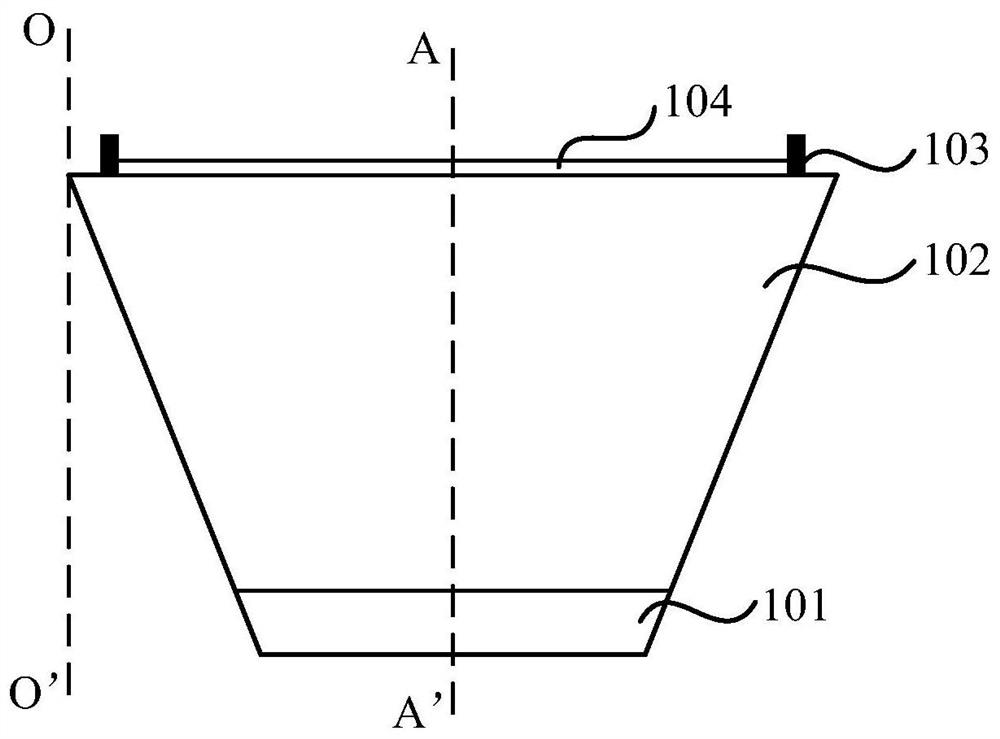

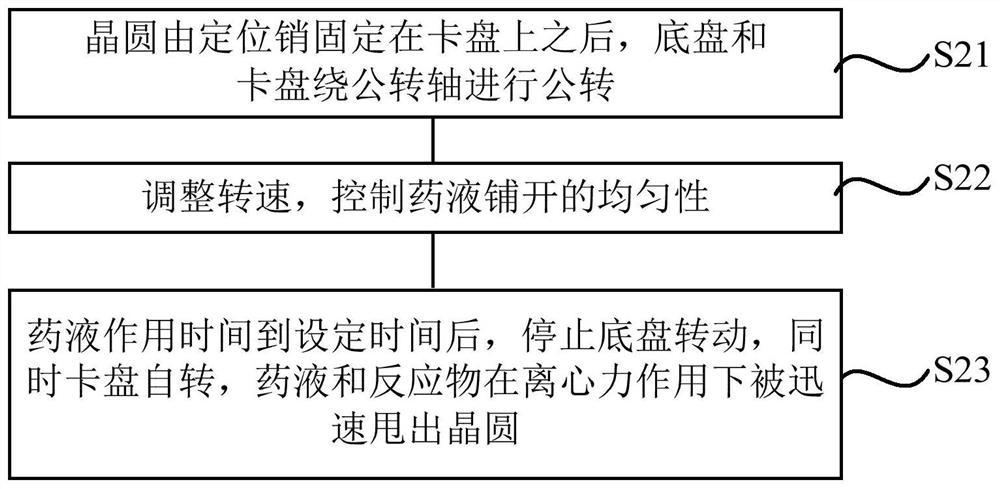

Wafer processing device and wafer processing method

PendingCN112509969AControl etch rateIncrease profitSemiconductor/solid-state device manufacturingWaferEngineering

The invention relates to a wafer processing device and a wafer processing method. The device comprises a wafer carrier which is used for bearing a wafer; a revolution driving device which can drive the wafer carrier to rotate along a revolution shaft, wherein the revolution shaft is located outside the wafer carrier; and an autorotation driving device which can drive the wafer carrier to rotate along an autorotation shaft, wherein the autorotation shaft is located at the circle center of the wafer carrier and is perpendicular to the surface of the wafer. The wafer processing method comprises acleaning step and a liquid medicine throwing step, wherein in the cleaning step, a wafer is driven to rotate along a revolution shaft by adopting a revolution driving device; in the liquid medicine throwing step, an autorotation driving device is adopted to drive the wafer to rotate along an autorotation shaft. The invention aims to etch the wafer by designing the wafer processing device into a mode of combining revolution and rotation, optimize the total thickness deviation and consistency of the wafer, control the etching rate of the wafer, improve the utilization rate of liquid medicine tothe maximum extent and reduce the manufacturing cost.

Owner:UNITED MICROELECTRONICS CENT CO LTD

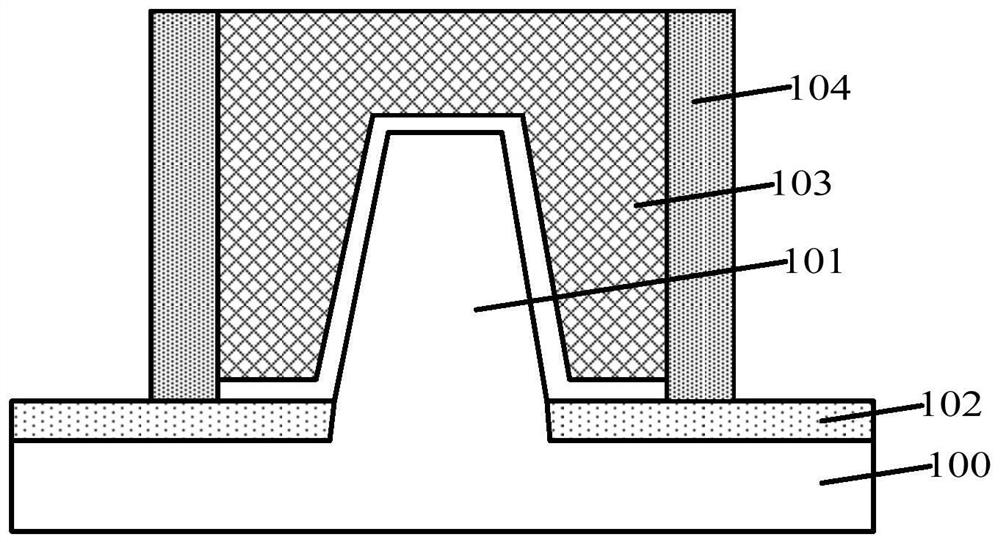

Semiconductor structure and forming method thereof

PendingCN112768360AImprove performanceAvoid short circuit conditionsSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureStructural engineering

The invention discloses a semiconductor structure and a forming method thereof. The method comprises the steps that a substrate which is provided with a fin structure is provided; a dummy gate layer crossing the fin structure is formed on the substrate, the dummy gate layer comprises a main body part and an extension part, the main body part crosses part of the side wall surface and part of the top surface of the fin structure, the top of the extension part is lower than the top surface of the fin structure, and the extension part is located at a corner formed by part of the side wall of the fin structure and the side wall of the main body part; and the extension part is removed by adopting a first cleaning process. The performance of the semiconductor structure formed by the method is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

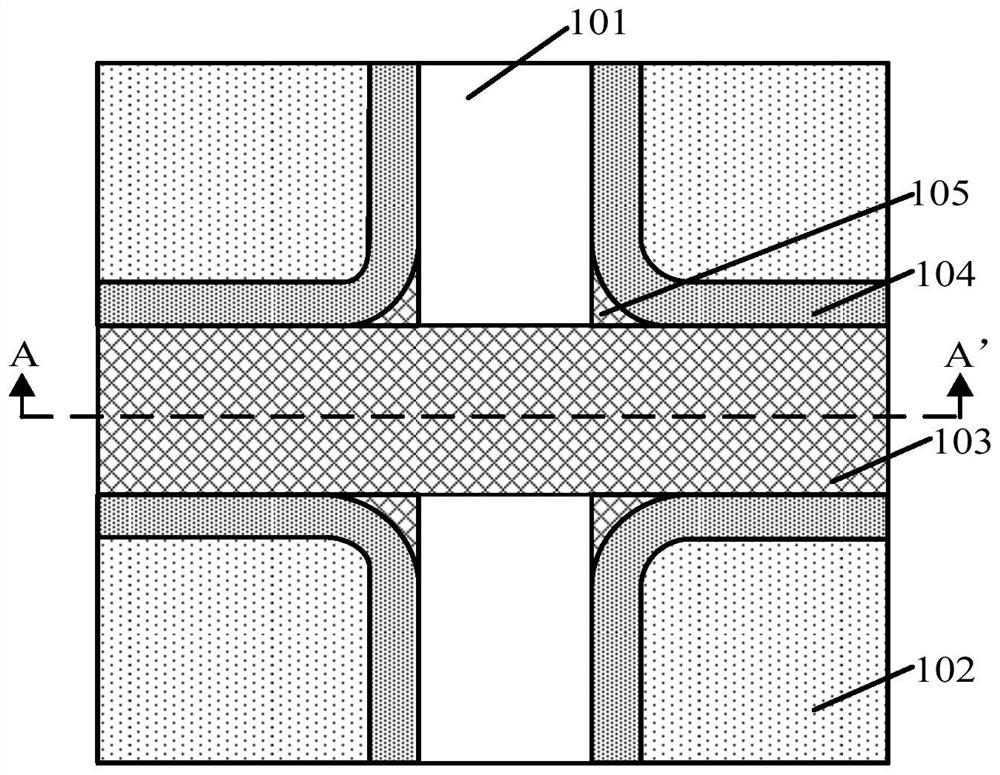

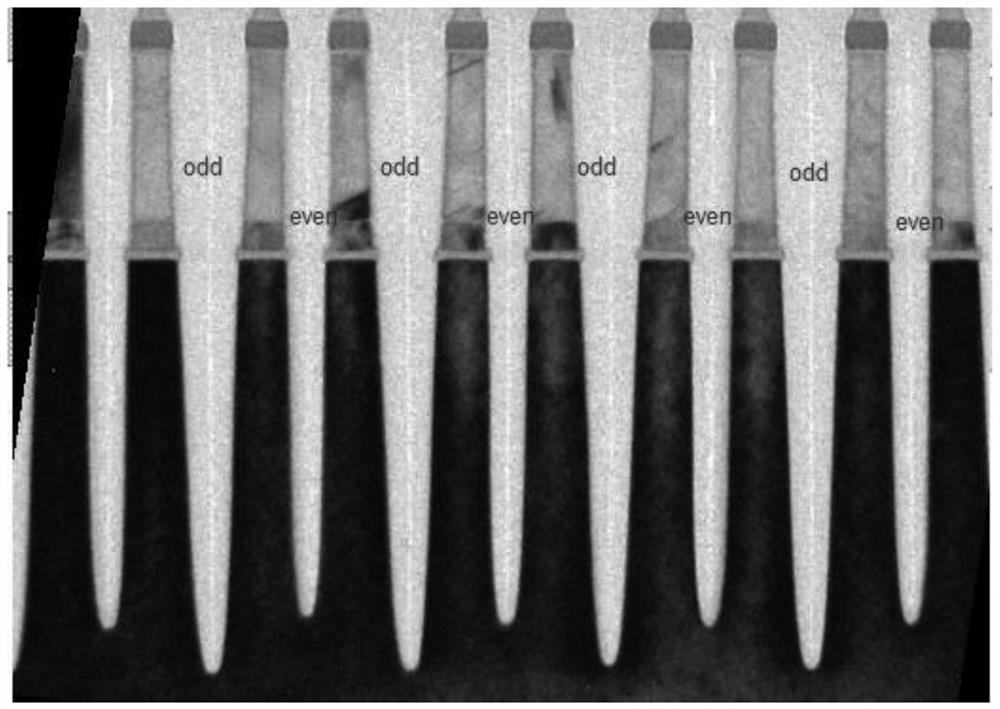

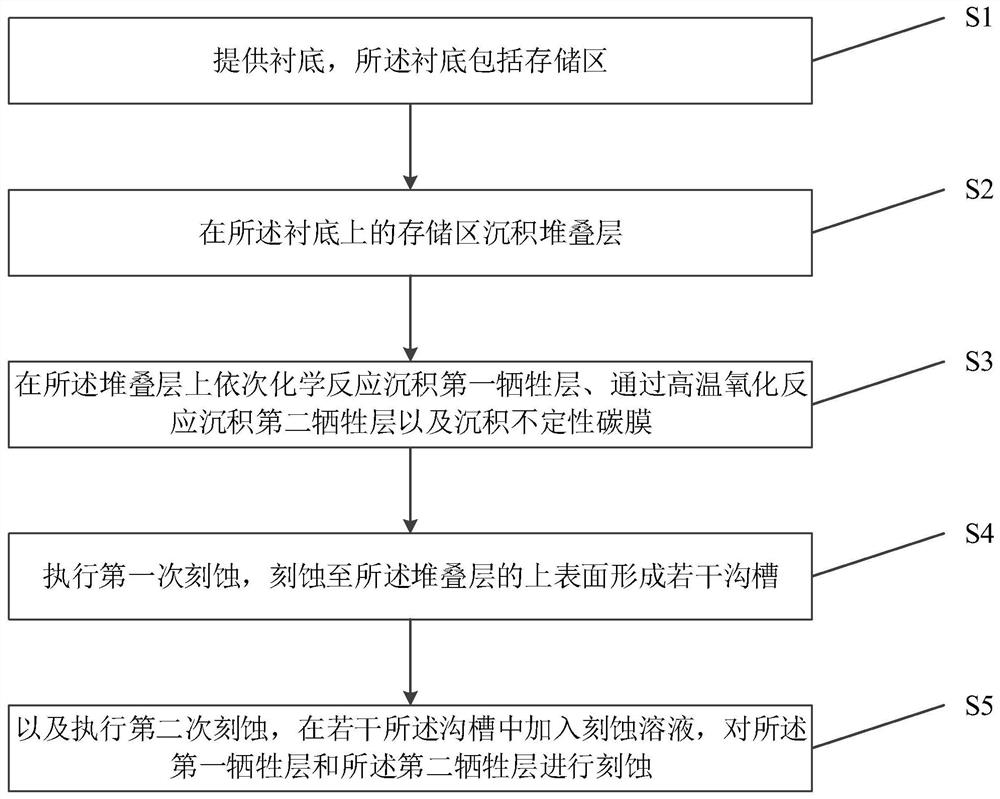

Double exposure method of nand flash memory structure

ActiveCN110085514BControl etch rateControl shapeSemiconductor/solid-state device manufacturingCarbon filmChemical reaction

The invention provides a double exposure method of a NAND flash memory structure, comprising the following steps: providing a substrate, the substrate including a storage area; depositing stacked layers on the storage area on the substrate; successively depositing stacked layers on the stacked layers Depositing the first sacrificial layer by chemical reaction, depositing the second sacrificial layer by high temperature oxidation reaction and depositing the indeterminate carbon film; performing the first etching, etching to the upper surface of the stacked layer to form several grooves; performing the second For secondary etching, an etching solution is added to several of the trenches to etch the first sacrificial layer and the second sacrificial layer. And by using two sacrificial layers with different formation methods, the etching rate of the first sacrificial layer and the second sacrificial layer can be controlled during the second etching, so as to control the morphology of the first sacrificial layer and the second sacrificial layer As well as critical dimensions, thereby reducing the possibility of uneven etching in subsequent etching.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP