Method for generating blocking metal layer

A metal layer and embolization technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve problems such as difficult circuit contact, instability, and high resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The direction of the present invention discussed here is a deposition process of a plug metal layer. In order to provide a thorough understanding of the present invention, detailed steps will be set forth in the following description. Obviously, the practice of the invention is not limited to specific details familiar to those skilled in the art of semiconductor devices. In other instances, well-known process steps have not been described in detail in order not to unnecessarily limit the present invention. The preferred embodiments of the present invention will be described in detail as follows, but in addition to these detailed descriptions, the present invention can also be widely implemented in other embodiments, and the scope of the present invention is not limited, it is subject to the scope of the patent later .

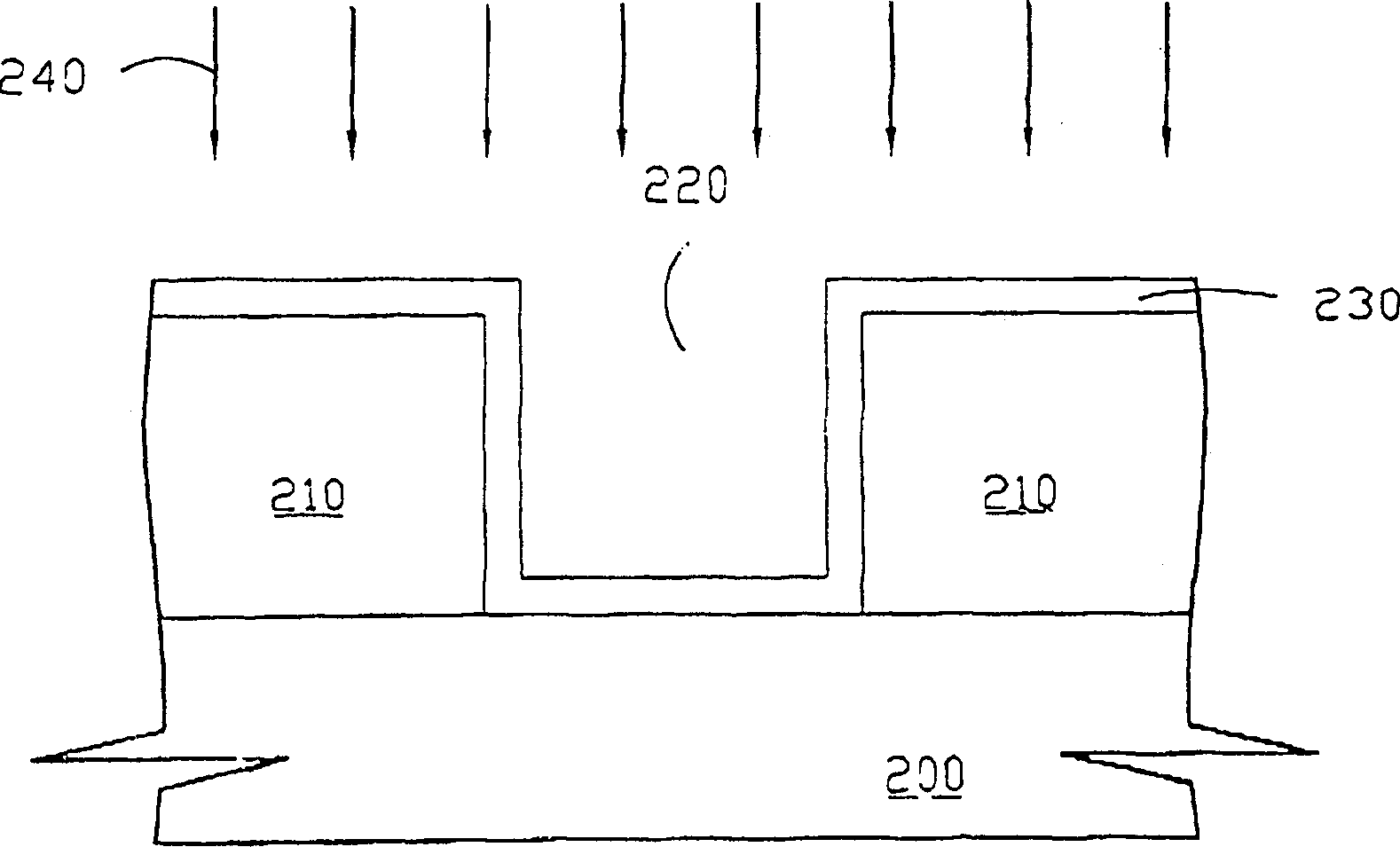

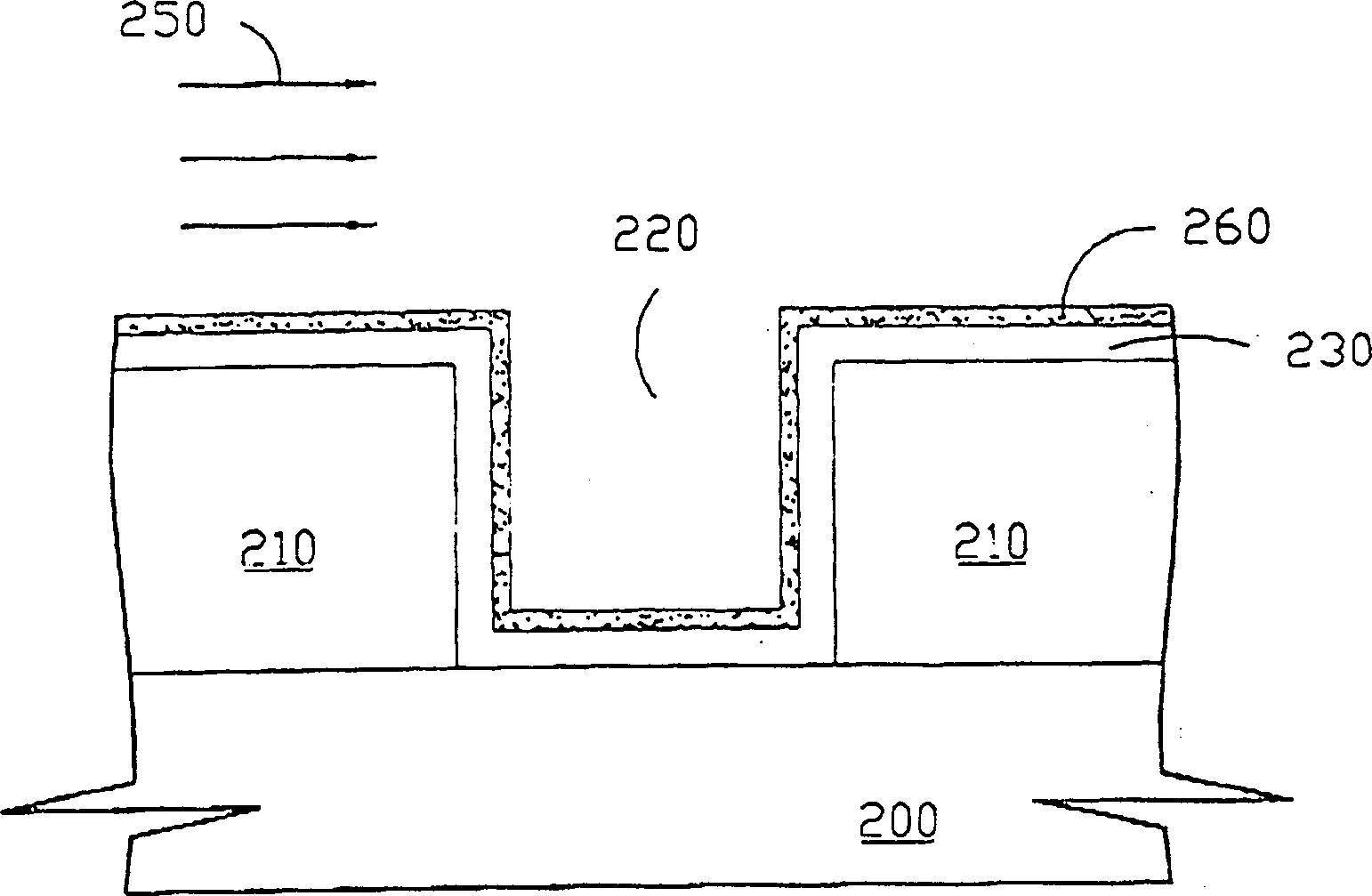

[0018] refer to Figure 2A to Figure 2CAs shown, in the first embodiment of the present invention, a semiconductor substrate 200 having a dielectric ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More