Semiconductor product insulation layer structure and preparation method thereof

A technology of semiconductor and insulating layer, applied in semiconductor/solid-state device manufacturing, semiconductor device, semiconductor/solid-state device components, etc., can solve the problem of difficult to achieve better radio frequency performance, poor thermal conductivity of insulating layer, poor circuit performance, etc. problem, to achieve the effect of reducing nucleation energy, high dielectric constant, and good insulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

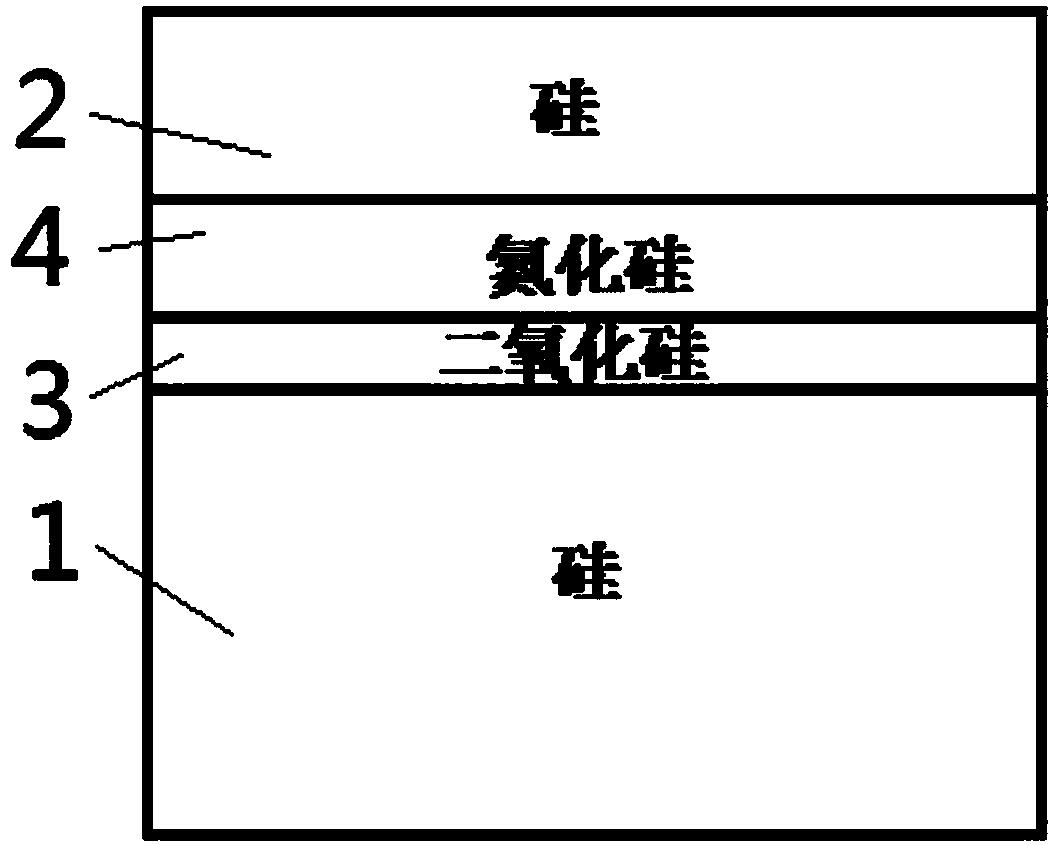

[0072] An insulating layer structure for a semiconductor product, which is composed as follows: a device substrate 1, a supporting substrate 2, and a film layer 3; wherein: the device substrate 1 and the supporting substrate 2 are both silicon wafers; Arranged on the substrate 1 and / or the supporting substrate 2; the thin film layer 3 is one of the following: a silicon dioxide layer, a silicon oxynitride layer, a silicon nitride layer, a polysilicon layer and an amorphous silicon layer;

[0073] One of the device substrate 1 and / or the supporting substrate 2 and the other are bonded together through at least one thin film layer 3 arranged on one of them to form a whole to form a multilayer SOI structure (that is: on an insulating substrate silicon structure).

[0074] The insulating layer structure for the semiconductor product satisfies the combination of the following requirements:

[0075] First, the resistivity of the silicon wafer used as the device substrate 1 or / and su...

Embodiment 2

[0123] The content of this embodiment is basically the same as that of Embodiment 1, the difference is that:

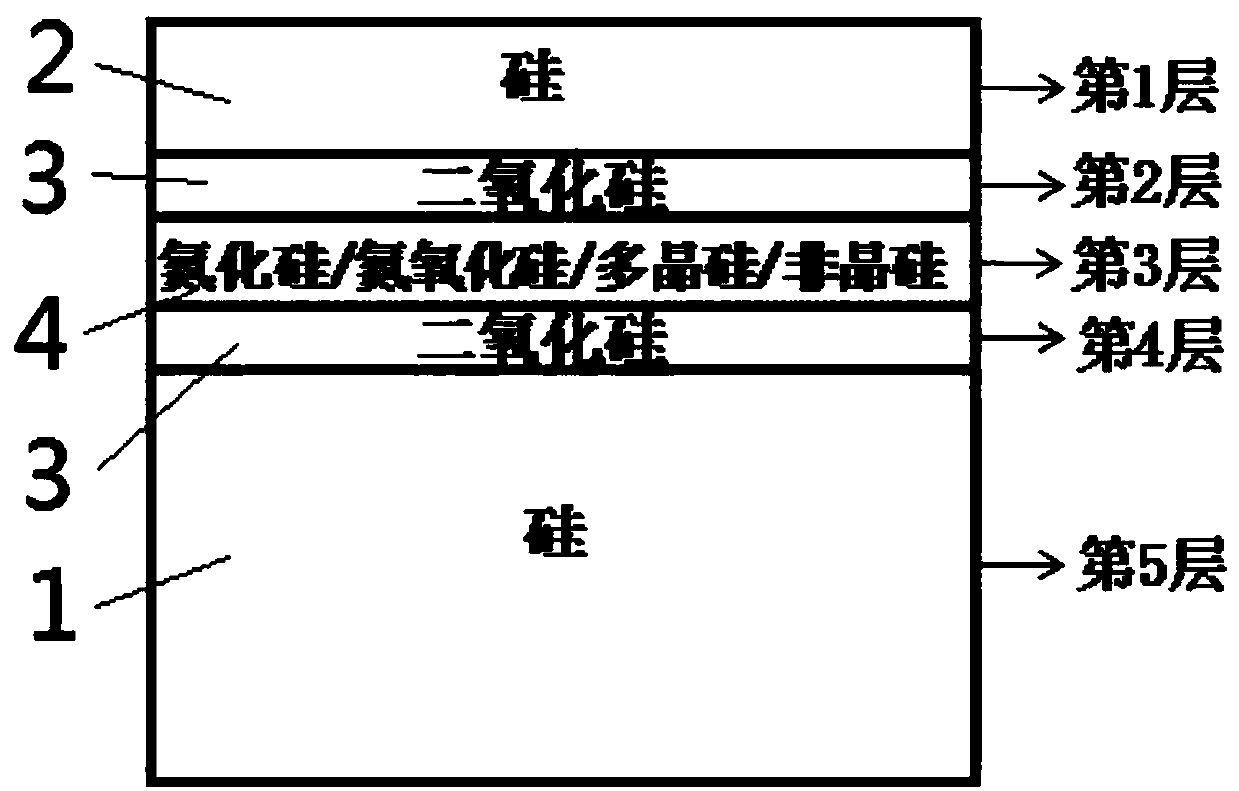

[0124] Insulating layer structures for semiconductor products such as figure 1 Said, the composition of insulating layer structure for semiconductor products is as follows: device substrate 1, supporting substrate 2, thin film layer 3; Wherein: both of device substrate 1, supporting substrate 2 are silicon wafers; Arranged on the substrate 1 and / or the supporting substrate 2; the film layer 3 is a silicon dioxide layer;

[0125] At least one intermediate layer 4 is arranged on the film layer 3 of at least one of the device substrate 1 and the supporting substrate 2, and the intermediate layer 4 is one of the following: silicon nitride oxide layer, silicon nitride layer , a polysilicon layer and an amorphous silicon layer;

[0126] An intermediate layer 4 is arranged on at least one of the film layer 3 of the device substrate 1 and / or the support substrate 2; both th...

Embodiment 3

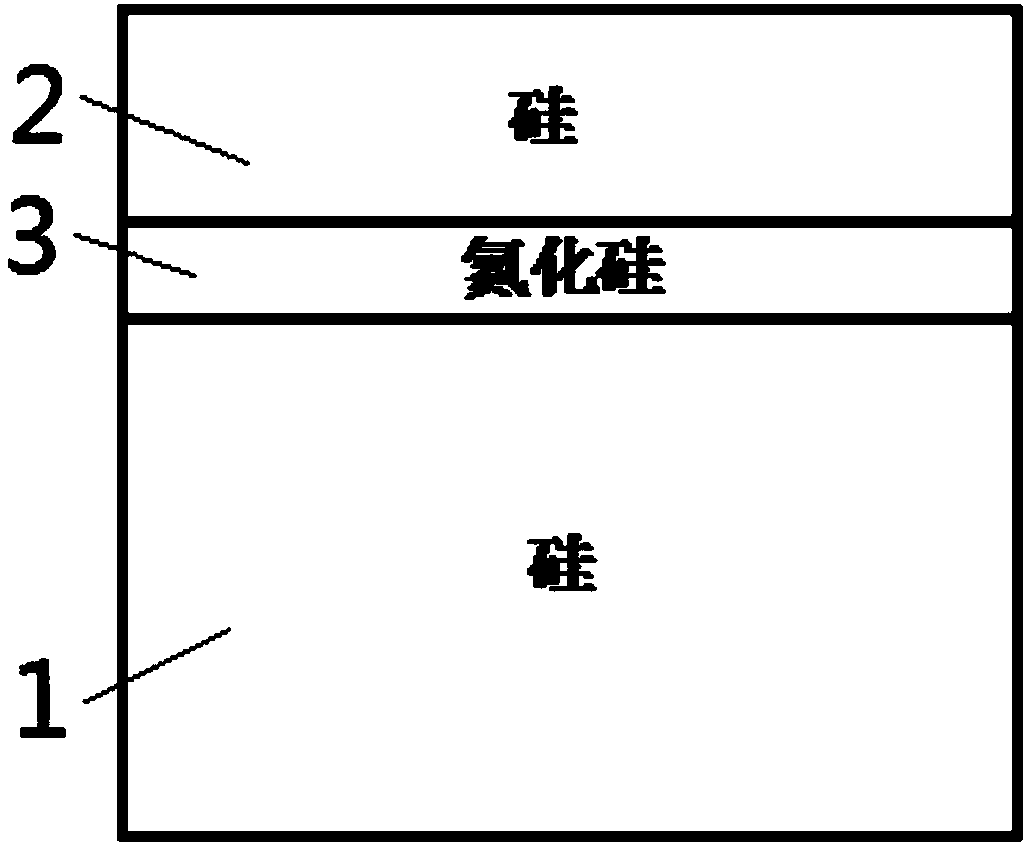

[0128] The content of this embodiment is basically the same as that of Embodiment 1, the difference is that:

[0129] Insulating layer structures for semiconductor products such as figure 2 Said, the composition of insulating layer structure for semiconductor products is as follows: device substrate 1, supporting substrate 2, thin film layer 3; Wherein: both of device substrate 1, supporting substrate 2 are silicon wafers; Arranged on the substrate 1 and / or the supporting substrate 2; the film layer 3 is a silicon nitride layer; one of the device substrate 1 and / or the supporting substrate 2 and the other pass at least one of the thin films arranged on one of them The layers 3 are bonded together to form a whole to form a multilayer SOI structure (ie: a silicon-on-insulator structure).

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Single layer thickness | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More